Mario Saric, BSc Matr. Nr. 01428305

# Simulation-based Testing of Failsafe Industrial Peripheral Modules

## **Diploma Thesis**

Master's degree programme: Energy Systems and Automation Technology

submitted to

# Vienna University of Technology

Supervisor

Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Thilo Sauter

Institute of Computer Technology

Vienna, March 2019

# Eidesstattliche Erklärung

Hiermit erkläre ich, dass die vorliegende Arbeit gemäß dem Code of Conduct-Regeln zur Sicherung guter wissenschaftlicher Praxis (in der aktuellen Fassung des jeweiligen Mitteilungsblattes der TU Wien), insbesondere ohne unzulässige Hilfe Dritter und ohne Benutzung anderer als der angegebenen Hilfsmittel, angefertigt wurde. Die aus anderen Quellen direkt oder indirekt übernommenen Daten und Konzepte sind unter Angabe der Quelle gekennzeichnet. Die Arbeit wurde bisher weder im In- noch im Ausland in gleicher oder in ähnlicher Form in anderen Prüfungsverfahren vorgelegt.

| Datum | Unterschrift |

|-------|--------------|

# **Acknowledgment**

This thesis was written in SIEMENS AG Development House in Graz, which is why I would like express my gratitude to Herbert Tanner for this opportunity and all the resources and patience I got during the writing process. A very special thanks to my colleague Joachim Wahrbichler for the generous technical support and knowledge he shared with me. I would also like to thank my colleague, Nermin Kajtazović, for his support, suggestions and discussions during this time. By all means, I would like to thank my supervisor Prof. Thilo Sauter for his professional and academic support.

Finally, I can not express how much I am grateful to my family: my father Ivan, mother Jadranka and sisters Magdalena and Marijana. It is for their support and sacrifice that I was able to do my studies in Croatia and Austria. They were always there for me, day or night. Thank you!

# **Abstract**

Nowadays, programmable logic controllers (PLCs) are a common technology used for automating industry processes and plants. Their scope of application ranges from simple emergency stop systems to more advanced systems, such as those used in hydro power plants for monitoring turbine rotation. Some of these PLCs and their corresponding peripheral I/O devices are used in the so-called "critical" environments, where in case of failures such systems may pose harm to humans or cause damage to the equipment. Thus, these so-called safety-critical systems must be developed rigorously with a high degree of quality assurance. If such system detects a failure in hardware or software it automatically goes into safe state, usually by de-energizing the outputs of the peripheral I/O modules. To ensure functional safety, the modules are developed in accordance with the IEC 61508 standard. For the software part, the use of the V-model is highly recommended by the IEC 61508. One of the common issues in terms of verification is a large gap between module/unit tests, which are normally performed in software for each software module separately, and hardware/software integration tests, which are performed when the system is integrated and functional. In order to bridge this gap, intermediate levels of integration are required between these two test phases. Simulation-based hardware-software testing is therefore presented in this thesis. Except for a host machine, this approach does not require any hardware. Instead, simulationbased testing is conducted using simulated hardware and an instruction set simulator. The simulation-based components are integrated into the legacy test environment. The tests are compiled and run redundantly on two different tool-chains, resulting in a test report and a coverage report. The new method is applied in a specific use-case: a traditional hardware-software integration test case is implemented in the simulation. The results show that it is possible to execute traditional integration tests without the hardware prototype and obtain a test coverage overview in addition. Consequently, the new method proves that it can be used as a supplement to traditional integration tests.

# Kurzfassung

Speicherprogrammierbare Steuerungen (SPS) sind heutzutage eine weit verbreitete Technologie in der industriellen Prozessautomatisierung. Ihr Anwendungsgebiet reicht von simplen Not-Aus Systemen bis hin zu sehr komplexen Anlagen, wie z.B. die Uberwachung der Turbinen in einem Wasserkraftwerk. Manche dieser SPS (samt den zugehörigen E/A Peripheriemodulen) werden in sogenannten "kritischen" Umgebungen eingesetzt, wo der Ausfall dieser Systeme eine Gefahr für Menschen bedeutet sowie ökonomische anrichten kann. Aus diesem Grund besitzen sogenannte sicherheitskritischen Systeme eine sehr rigorose Entwicklung und hohe Qualitätsansprüche. Wenn das System einen Fehler in Hardware und/oder Software detektiert, so schaltet es automatisch in den sicheren Zustand, der üblicherweise das Abschalten der Peripherieausgänge zur Folge hat. Um funktionale Sicherheit zu gewährleisten werden die Module gemäß IEC 61508 Standard entwickelt. Für die Software empfiehlt der Standard die Verwendung des V-Modells. Eines der Probleme bei der Verifikation ist, dass eine große Lücke zwischen Modultests, welche in Software ausgeführt werden und jede Komponente einzeln betrachten, und den Hardware/Software-Integrationstests welche im Systemverband getestet werden besteht. Um diese Lücke zu schließen sind Zwischenstufen im Test nötig. Aus diesem Grund wird eine simulationsbasierte Hardware-Software Testmethode in dieser Arbeit vorgestellt. Dieser Ansatz benötigt außer einem Hostsystem keine zusätzliche Hardware. Stattdessen wird beim Testen nur simulierte Hardware mit einem Befehlssatz-Simulator eingesetzt. Die simulationsbasierten Komponenten wurden in die bestehende Testumgebung integriert. Die Tests werden übersetzt und laufen redundant auf zwei verschiedenen Tool-chains und resultieren in einem Testbericht und einem Codeabdeckungsbericht. Die neue Methode wurde an einem bestehenden Use-Case; einem gewöhnlichen HW/SW-Integrationstest angewendet. Das Ergebnis zeigte, dass es möglich ist gewöhnliche Integrationstestfälle ohne Hardwareprototyp auszuführen und zusätzlich eine Übersicht über die Codeabdeckung zu erhalten. In Folge dessen wird die neue Methode ergänzend zu den bestehenden Integrationstests verwendet.

# **Contents**

| Αb | strac | ct                                  | iv          |

|----|-------|-------------------------------------|-------------|

| Αŀ | brevi | iations                             | хi          |

| 1. | 1.1.  | Motivation                          | 1<br>1<br>4 |

| 2. |       | safe Programmable Logic Controllers | <b>5</b>    |

|    | 2.1.  |                                     | _           |

|    | 2.2.  | Failsafe PLC Peripheral Module      | 6           |

|    | 2.3.  | PROFIsafe                           | 9           |

| 3. | Test  | ting Embedded Systems               | 12          |

|    | 3.1.  | 3                                   | 13          |

|    | 3.2.  | · ·                                 | 15          |

|    |       |                                     | 15          |

|    |       | ě                                   | 17          |

|    | 3.3.  | <u> </u>                            | 20          |

|    |       |                                     | 20          |

|    |       |                                     | 20          |

|    |       | 3.3.3. HW/SW Integration Test       | 22          |

|    |       |                                     | 22          |

|    | 3.4.  |                                     | 23          |

|    | 3.5.  |                                     | 24          |

| 4. | Mod   |                                     | 26          |

|    | 4.1.  | Abstraction Levels                  | 26          |

|    | 4.2.  | Abstraction Pyramid                 | 27          |

|    | 4.3.  | System Level Modeling               | 29          |

|    |       | 4.3.1. Single-Language Approach     | 29          |

# Contents

|    |      | 0 0 11                                            | 30 |

|----|------|---------------------------------------------------|----|

|    | 4.4. |                                                   | 30 |

|    |      | 1                                                 | 31 |

|    |      | v                                                 | 31 |

|    |      | ,                                                 | 33 |

|    | 4.5. | Į                                                 | 34 |

|    |      |                                                   | 34 |

|    |      |                                                   | 34 |

|    |      | · ·                                               | 35 |

|    | 4.6. |                                                   | 35 |

|    | 4.7. | Conclusion                                        | 36 |

| 5. | Syst | em Design                                         | 39 |

|    | 5.1. | Simulated Hardware                                | 39 |

|    |      | 5.1.1. Generic I/O Pin Model                      | 39 |

|    |      | 5.1.2. Generic Register Model                     | 42 |

|    |      |                                                   | 42 |

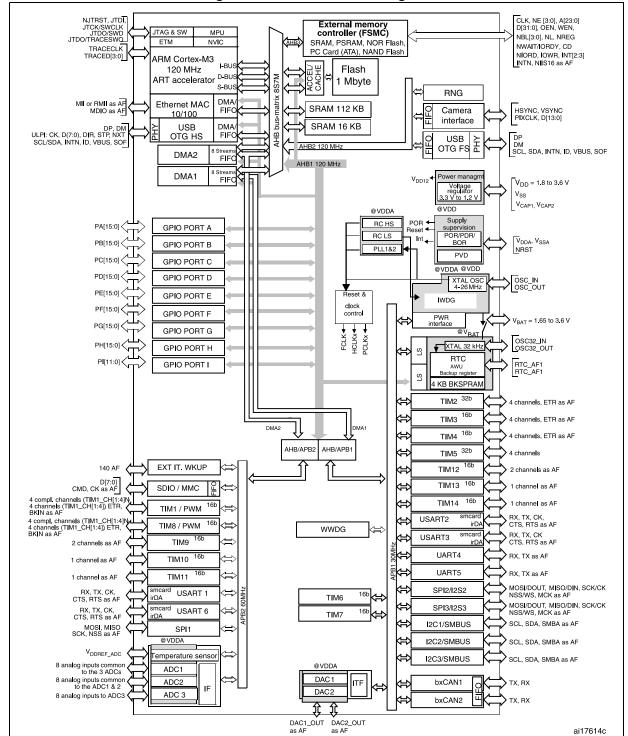

|    |      | 5.1.4. STM32F2xx Peripherals                      | 42 |

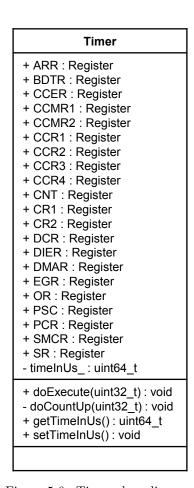

|    |      | 5.1.5. Timer                                      | 43 |

|    |      | 5.1.6. Other Hardware                             | 43 |

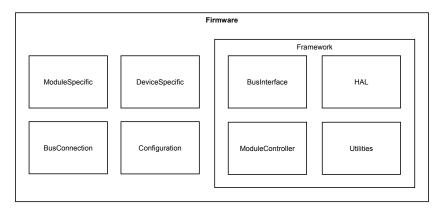

|    | 5.2. | Firmware                                          | 46 |

|    | 5.3. | Middleware                                        | 48 |

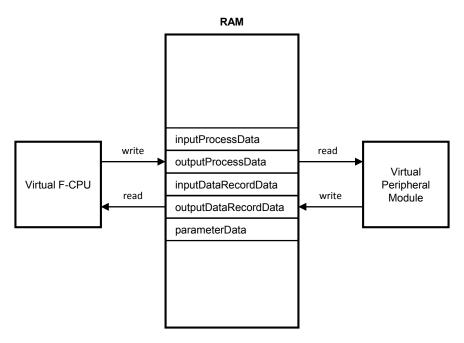

|    |      | 5.3.1. F-CPU and PROFIsafe Simulation             | 48 |

|    |      | 5.3.2. Simulation Event Manager                   | 48 |

|    | 5.4. | Test Environment                                  | 50 |

| 6. | Impl | ementation 5                                      | 54 |

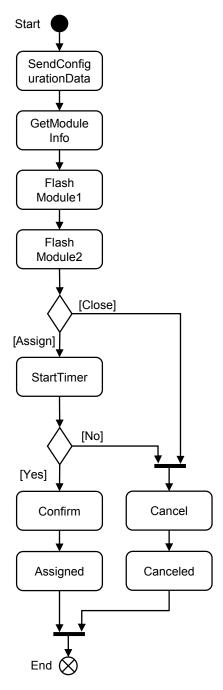

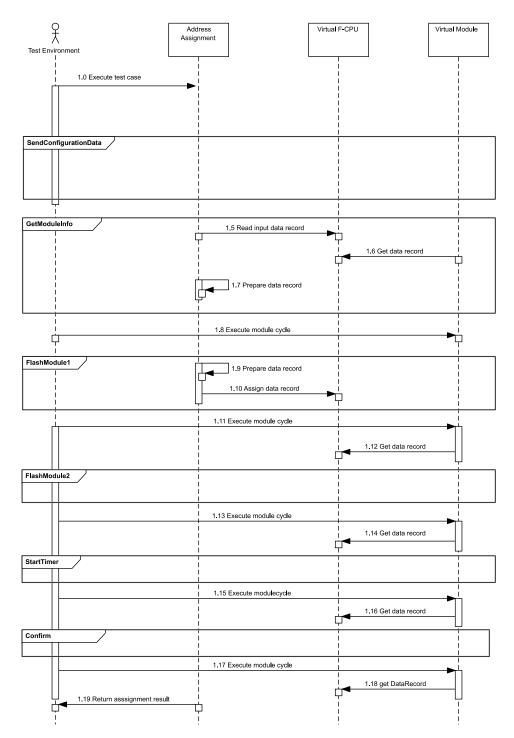

|    | 6.1. | PROFIsafe Address Assignment                      | 54 |

|    |      |                                                   | 55 |

|    |      | 6.1.2. Address Assignment via Engineering Station | 55 |

|    |      |                                                   | 56 |

|    | 6.2. |                                                   | 61 |

|    | 6.3. | 9                                                 | 64 |

| 7. | Resi | ılts and Evaluation 6                             | 66 |

|    |      | Test Coverage                                     |    |

|    | 7 2  |                                                   | 62 |

# Contents

|     | 7.3.   | Discussion           | 68 |

|-----|--------|----------------------|----|

| 8.  | 8.1.   | Summary              |    |

| Bil | oliogi | aphy                 | 72 |

| ΑĮ  | pen    | dix 7                | 78 |

| Α.  | STN    | 32F2xx Block Diagram | 79 |

# List of Figures

| 1.1.<br>1.2. | Typical V-model [3]                                                                    | 2  |

|--------------|----------------------------------------------------------------------------------------|----|

| 1.2.         | Traditional development (top) vs. development using a simulation platform (bottom) [5] | 3  |

| 2.1.         | SIMATIC PLC system: S7-1500 CPU with ET 200SP (Image                                   |    |

|              | courtesy of SIEMENS)                                                                   | 6  |

| 2.2.         | PLC program execution                                                                  | 7  |

| 2.3.         | Generic failsafe I/O peripheral module block diagram                                   | 8  |

| 2.4.         | r j                                                                                    | 8  |

| 2.5.         | ± [ ]                                                                                  | 10 |

| 2.6.         | PROFIsafe layer structure [8]                                                          | 10 |

| 2.7.         | PROFIsafe message format [8]                                                           | 11 |

| 3.1.         | 0[]                                                                                    | 13 |

| 3.2.         | 1                                                                                      | 13 |

| 3.3.         | Safety V-model [4]                                                                     | 14 |

| 3.4.         | Black-box testing                                                                      | 16 |

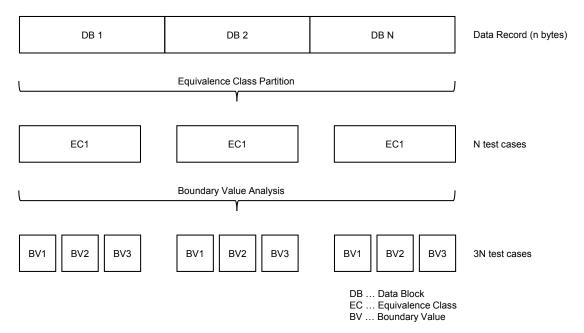

| 3.5.         | Equivalence class partition                                                            | 16 |

| 3.6.         | Boundary value analysis                                                                | 17 |

| 3.7.         |                                                                                        | 21 |

| 3.8.         | Top down integration strategy [15]                                                     | 21 |

| 3.9.         | Bottom up integration strategy [15]                                                    | 22 |

| 3.10.        | Simulation techniques in the development of modern ECUs [17]                           | 24 |

| 3.11.        | SiL simulation diagram                                                                 | 25 |

| 4.1.         | Y-chart diagram [19]                                                                   | 27 |

| 4.2.         |                                                                                        | 28 |

| 4.3.         | Single-language approach [21]                                                          | 29 |

| 4.4.         |                                                                                        | 30 |

| 4.5.         |                                                                                        | 32 |

| 4.6.         | SystemC language architecture [26]                                                     | 33 |

# List of Figures

| 4.7.  | Level of abstraction vs. performance in modeling timing behavior                                                         |    |

|-------|--------------------------------------------------------------------------------------------------------------------------|----|

|       | $[46] \dots \dots$ | 37 |

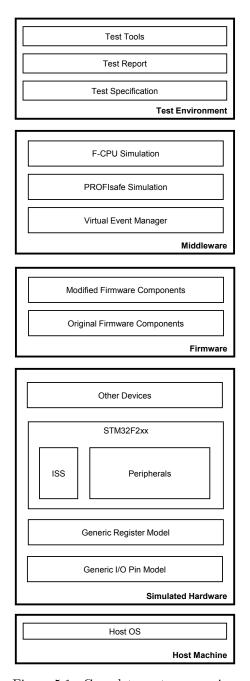

| 5.1.  | Complete system overview                                                                                                 | 40 |

| 5.2.  | Pins class diagram                                                                                                       | 41 |

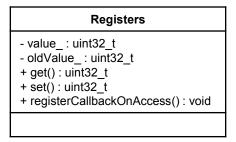

| 5.3.  | Generic register class diagram                                                                                           | 42 |

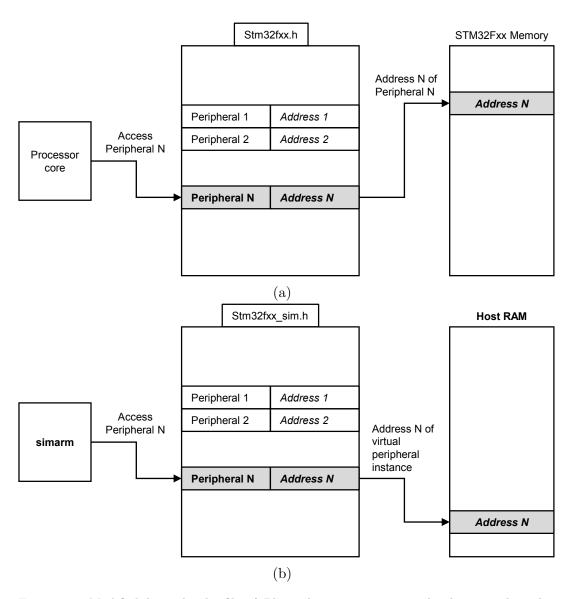

| 5.4.  | Modified device header file: a) Physical processor accessing hard-                                                       |    |

|       | ware perihperals b) Accessing modeled peripherals using the                                                              |    |

|       |                                                                                                                          | 44 |

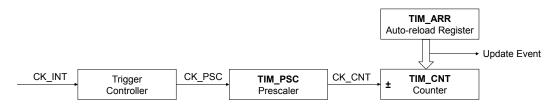

| 5.5.  |                                                                                                                          | 45 |

| 5.6.  | O .                                                                                                                      | 45 |

| 5.7.  |                                                                                                                          | 47 |

| 5.8.  |                                                                                                                          | 49 |

| 5.9.  | Code instrumentation in module controller                                                                                | 50 |

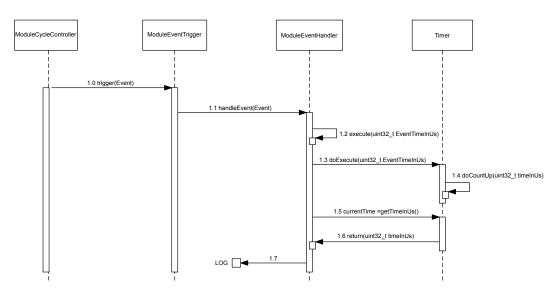

|       | Simulation event manager time sequence diagram                                                                           | 51 |

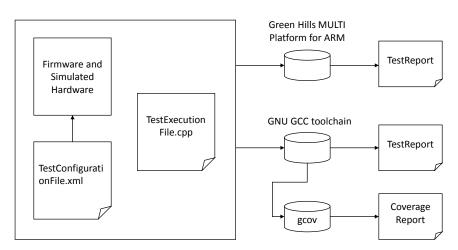

| 5.11. | Test environment configuration                                                                                           | 52 |

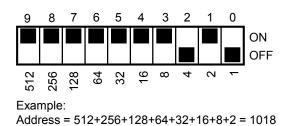

| 6.1.  | Setting the failsafe address using a hardware switch                                                                     | 55 |

| 6.2.  | Implementation configuration in TIA Portal                                                                               | 56 |

| 6.3.  | Step 1 of the address assignment in TIA Portal                                                                           | 57 |

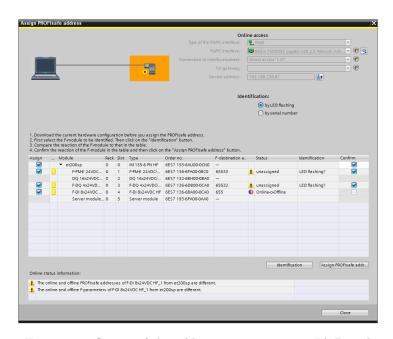

| 6.4.  | Step 2 of the address assignment in TIA Portal                                                                           | 58 |

| 6.5.  | Step 3 of the address assignment in TIA Portal                                                                           | 58 |

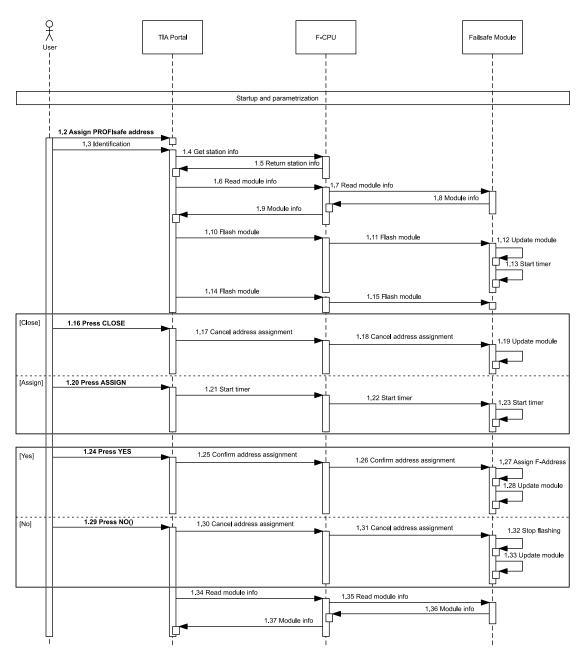

| 6.6.  | TIA Portal address assignment time sequence diagram                                                                      | 59 |

| 6.7.  | v 0                                                                                                                      | 62 |

| 6.8.  |                                                                                                                          | 63 |

| 6.9.  | Additional test cases derived from data records                                                                          | 65 |

# **Abbreviations**

1002D One-Out-Of-Two-Diagnostic

ADC Analog-to-Digial Converter

**BCET** Best Case Execution Time

CRC Cyclic Redundancy Check

**DIP** Dual-In-line-Package

**DUT** Device Under Test

ECU Engine Control Unit

ESL Electronic System Level

F-CPU Failsafe CPU

FMEA Failure Mode and Effects Analysis

**HDL** Hardware Description Language

HiL Hardware-in-the-Loop

I2C Inter-Integrated Circuit

IP Intellectual Property

**ISS** Instruction Set Simulator

MiL Model-in-the-Loop

**OVP** Open Virtual Platforms

PiL Processor-in-the-Loop

#### Abbreviations

PL Performance Level

**PLC** Programmable Logic Controller

SIL Safety Integrity Level

SiL Simulation-in-the-Loop

**SLDL** System-Level Design Language

${f TLM}$  Transaction-Level Modeling

WCET Worst Case Execution Time

Nowadays, programmable logic controllers (PLCs) are the most widely used industrial automation technology [1]. They are used for production and process control in various industrial systems. Their application ranges from simple automation tasks such as conveyor systems to complex control systems such as nuclear plants. The latter is considered a safety-critical environment. Failure in such environments can cause damage to the property or environment, which in turn, either directly or indirectly, leads to physical injury or damage to the human health [2]. Moreover, the failure can also induce serious economic consequences. The root of the failure can be caused by any functional part of the system, including the programmable logic controllers. Given the fact, that the PLCs are becoming more and more complex in terms of hardware and software, a number of guidelines and standards have been introduced lately, in order to ensure functional safety and make them as reliable as possible. In the context of industrial application, the international standard IEC 61508 has emerged [2]. IEC 61508 covers the system development of failsafe programmable electronic systems. It has seven parts that are focused on different development aspects and features a set of methods and recommendations to support the development and ensure functional safety.

## 1.1. Motivation

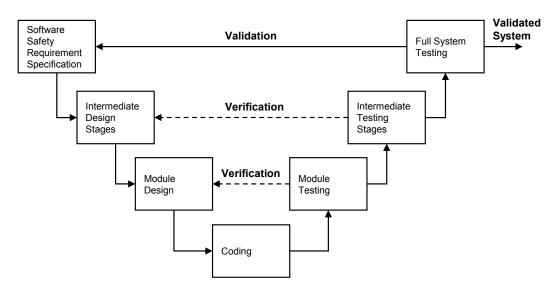

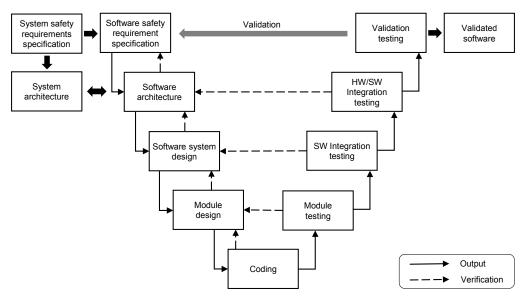

This thesis focuses on the software part of the development of failsafe PLC peripheral modules. This is covered in the Part 3 of the IEC 61508 [4]. The software design is largely based on the use of the V-model approach. A typical V-model is shown in the Figure 1.1. The principle of the V-model is a top-down approach for development and testing. Each development level has a corresponding test level. The focus of this thesis is further narrowed to the right side of the V-model: testing and verification. Two major problems arise from testing the software with using the V-model approach. One is that software

Figure 1.1.: Typical V-model [3]

testing heavily depends on hardware architecture and the other is that there is a large gap between module/unit tests, which are normally conducted in software for each software module in isolation, and hardware/software integration tests, which are conducted when a system is integrated. To be more appropriate, an intermediate levels of integration are required between these two test phases, since on the one side, unit testing can help to identify the potential systematic faults with reasonably good coverage in isolated software modules, and on the other side, hardware/software integration allows to verify functions of the integrated system, but lacks in achieving high test coverage.

#### Hardware-dependent Software Testing

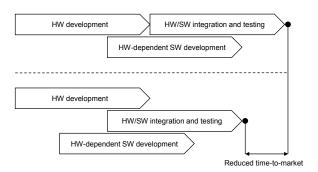

Software development can be conducted as detached from the hardware only to some extent. It is feasible to develop and test software components with little or no interaction with the hardware. However, when developing software modules which closely interact with the hardware (e.g., drivers), a hardware prototype is essential. Ideally, one would be completely independent from hardware development and have an executable software without the need of hardware. A potential solution to this would be to introduce virtual hardware components by introducing a simulation-based platform. With this new platform, the software developer is not only able to execute hardware-dependent test cases before

Figure 1.2.: Traditional development (top) vs. development using a simulation platform (bottom) [5]

actually getting the hardware, but also to use it to develop and test new functionalities. This leads to a reduced time-to-market, as illustrated in Figure 1.2.

#### **Integration Testing Gap**

In the most optimal scenario, the software should be fairly tested. However, there are two problems with software testing. First, it is difficult to determine what it means that the system is completely tested. Second, even if the exact determination would be possible, there is still only a limited number of resources for testing. IEC 61508 partially handled that problem and introduced a formal metric to measure to which degree the system has been tested. This metric is called test coverage. Ideally, 100% of statements, methods and branches shall be covered. If that is not possible, a valid explanation has to be supplemented. Furthermore, the statement about the code coverage is relatively easy to generate for isolated software units and software integration tests, since there is a transparent overview over the software architecture at these levels. However, when moving to hardware-software integration test, the source code is no longer available and thus, there is no feedback from the software part. Hardwaresoftware integration tests are used for functional verification but they lack an overview about the code coverage. This thesis introduces a simulation-based hardware-software integration test approach, which provides a code-coverage overview for traditional hardware-software integrations tests.

#### Thesis Contributions

To tackle the problems above, this thesis will focus on introducing a simulation-based hardware-software testing platform. In accordance with the IEC 61508 and based on the traditional software development using a V-model approach, a simulation-based testing approach is introduced for testing failsafe peripheral modules. The platform will not have any hardware components. The goal is to execute traditional hardware-software integration test cases on the simulation platform.

### 1.2. Thesis Structure

The thesis is organized in eight chapters. After this introductory chapter, subsequent three chapters deal with theoretical background, literature review and related work. Chapter 2 introduces the SIEMENS SIMATIC PLC system to the reader. The presented peripheral module is a safety-critical embedded system. In order to get the target system certified, it has to be comprehensively tested. Chapter 3 gives a brief overview of testing methods used for embedded systems in general, as well as those specifically used for the target system. One of the testing techniques applied is also software simulation. To implement a simulation in the testing life-cycle, a software model of the embedded system is necessary. Chapter 4 focuses on modeling an embedded system on a system level. System-modeling state-of-the art is presented and backed up with the related work. After providing theoretical fundamentals, Chapter 5 describes the final system. In Chapter 6, the system is implemented in a specific use-case. The results of the implementation and detailed evaluation of the system are presented in the Chapter 7. Finally, Chapter 8 offers a brief summary of the thesis after which some future work is presented.

# 2.1. SIMATIC PLC System

A brief description on how a PLC works is explained through an example of the SIEMENS SIMATIC PLC system depicted in the Figure 2.1. The CPU (1) and the peripheral I/O modules (2) are mounted on a mounting rail (6) and supplied with a supporting power supply. Optionally an interface module (5) is used in a distributed system to connect the distributed I/O group with the CPU. Automation application runs on either a regular CPU or a failsafe CPU (F-CPU). The system supports both Ethernet, PROFINET and PROFIBUS communication. The data between CPU and peripheral modules is exchanged cyclically and acyclically. Cyclic data exchange is used for process data (e.g. input data from sensors) and acyclic for other communication (e.g. parametrization of the module). For exchanging the safety relevant process data, the PROFIsafe protocol is applied. Peripheral I/O modules form an interface between the controller and the plant. They handle physical input or output signals obtained from sensors and provided to actuators. Depending on the signal type, I/O modules can be generally divided into following categories:

- Digital input (DI)

- Digital output (DQ)

- Analog input (AI)

- Analog output (AQ)

For safety-critical plants, the yellow-labeled modules (3) in Figure 2.1, are used. These are a special SIMATIC I/O module product family for safety integration.

Figure 2.1.: SIMATIC PLC system: S7-1500 CPU with ET 200SP (Image courtesy of SIEMENS)

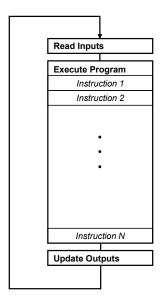

#### **PLC Program Cycle**

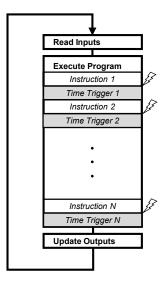

The main application is implemented as an infinite loop with instructions executed in a specified order and interrupted with time-critical tasks in form of interrupts. This is illustrated in Figure 2.2. Each cycle starts by reading the input values from sensors and ends with setting the output data for actuators. In-between, instructions are executed to provide functionality of the loaded application. Total cycle time depends on the complexity of the application and performance of the used CPU. However, the cycle time must be short enough to ensure that the system operates almost in real time. Typical time values range from 1ms to 20ms [1].

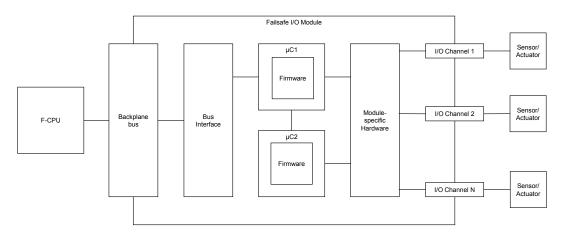

# 2.2. Failsafe PLC Peripheral Module

Fail-safe modules cover a number of functional safety measures from various international standards (e.g. IEC 61508). Furthermore, the modules have to get certified by an accredited functional safety certification organization (e.g.  $T\ddot{U}V$ ). They are designed for safety-related use up to SIL (Safety Integrity

Figure 2.2.: PLC program execution

Level) 3 according to IEC 62061 and PL (Performance Level) "e" according to ISO 13849 [6].

The general internal block structure of a failsafe module is shown in Figure 2.3. The module is connected to the F-CPU via bus interface. On the other side, sensors/actuators in the plant are connected via different I/O channels. The data is redundantly processed on two identical micro-controllers, which run the same firmware images and are constantly being synchronized. Each module has a group of module-specific hardware. The peripheral analog modules, for example, feature a third-party ADC hardware component.

#### **Functional Safety Measures**

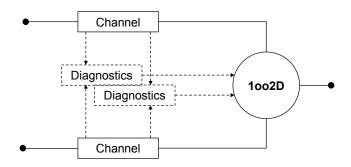

The failsafe peripheral module essentially realizes functionality as regular modules do: exchange process data between the plant and controller. However, to ensure failsafe operation, several functional safety measures according to the IEC 61508 are integrated into the failsafe modules. Most important is the use of one-out-of-two-diagnostic (1002D) architecture. This means that the process data is evaluated using two identical microprocessors running the same firmware images. Supplementary, a number of diagnostic monitoring measures are implemented.

Figure 2.3.: Generic failsafe I/O peripheral module block diagram

Figure 2.4.: 1002D architecture [7]

#### 1002D Architecture

The sensor values are processed and evaluated using a dual channel structure, depicted in Figure 2.4. The channels are connected in parallel. If there is a diagnostic fault in one of channels or a discrepancy between the two of them, then the module goes to the safe state [7].

#### **Diagnostic Monitoring**

As recommended by IEC 61508, a number of monitoring functions are implemented to ensure the correct operation of the peripheral modules. Examples of such monitoring functions are voltage monitoring, temperature monitoring, RAM Comparison, watchdog monitoring etc. If one of the monitored values does not match the reference or expected values, the module goes into the

failsafe state.

#### 2.3. PROFIsafe

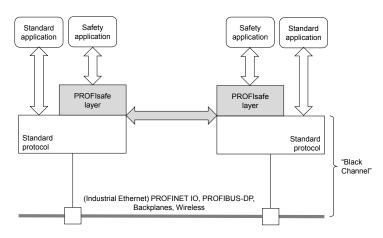

PROFIsafe [8] is a safety communication technology defined as an international standard in IEC 61784-3-3. PROFIsafe protocol can be used for safety applications up to SIL3 according to IEC 61508. It allows a failsafe communication on existing standard networks such as PROFIBUS and PROFINET without any impacts on them. Both standard and failsafe messages are transmitted on the same cables. However, from the perspective of a PROFIsafe profile, the underlying bus system and other network components (switches and routers i.e.) are seen as "black channel". This concept is shown in Figure 2.5. A safety communication profile must deliver updated and correct data (data integrity) to the intended destination (authenticity) just-in-time (timeliness). To meet these tasks, [8] includes following safety measures:

- 1. Consecutive numbering of PROFIsafe messages: a 24-bit consecutive number is used to assure that the receiver obtained the complete message within the correct sequence.

- 2. Time expectation with acknowledgment: in the safety critical systems, it not only matters if the received message is complete as mentioned above, but it is just as important that the message arrives within a fault tolerant time. This is solved by utilizing a watchdog timer.

- Codename between sender and receiver: to avoid misdirecting messages, both sender and receiver have a unique network-wide identification in a form of failsafe address.

- 4. Data integrity checks (CRC): A cyclic redundancy check is used for detecting corrupted bits. PROFIsafe uses 24-bit and 32-bit CRC generator polynomial to calculate the CRC signatures.

#### **PROFIsafe** services

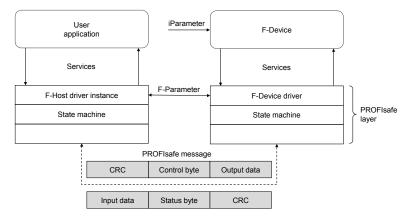

As previously shown in Figure 2.5, the PROFIsafe layers are located above the "black channel" and are implemented in software as drivers with a central state machine controlling message processing, CRC error handling and exceptions such as startup and power on/off. Figure 2.6 shows the service interaction between the host (e.g. F-CPU) and the device (peripheral module).

Figure 2.5.: PROFIsafe "black channel" concept [8]

Figure 2.6.: PROFIsafe layer structure [8]

| F-Input/Output data        | Status/Control byte | CRC signature |  |  |

|----------------------------|---------------------|---------------|--|--|

| Maximum of 12 or 123 bytes | 1 byte              | 3 or 4 bytes  |  |  |

Figure 2.7.: PROFIsafe message format [8]

#### **Host Services**

The main services implement the exchange of input/output process data. In case of errors, the process values are replaced by failsafe values which are by default zero in order to force the receiver in safe state. There are devices in which the de-energize is not the only possible state. Instead, an alternative state during which the device is put to low speed is also possible. This is also covered by the host services. After the devices switches to the safe state, it is usually not allowed to return to normal operation without human interaction. PROFIsafe provides additional service for operator acknowledgment.

#### **Device Services**

The PROFIsafe services for the device technology cover the same aspects mentioned above, but from the perspective of the device itself. Beside services for reporting faults, a special service is used for passing over the diagnostic information. Last but not least, the device uses PROFIsafe services for parametrization. There are two groups of parameters: I-parameters which are technology-specific device parameters and F-parameters containing information for the PROFIsafe layer (i.e. failsafe address).

#### **PROFIsafe Message Format**

Figure 2.7 shows the default PROFIsafe message format. The main part is the input/output data. Factory automation and process automation have different requirements: one deals with short signals, the other involve longer process values. Consequently, there are two different lengths of data structure: one limited to maximum of 12 bytes with 3-byte CRC signature and the other limited to 123 bytes requiring a 4-bye CRC signature. The CRC signature ends the PROFIsafe data message. The above mentioned consecutive number is not transmitted within the message. Instead, the counter values of sender/receiver and synchronized via the control/status byte.

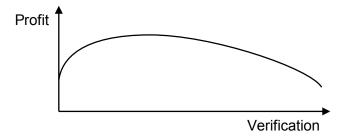

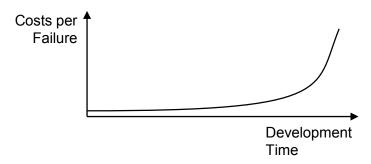

Previous chapter introduced the failsafe PLC system. The failsafe peripheral module is basically an embedded system. Testing embedded systems covers testing not just the software the hardware as well. For the modules to go to production, they need to be developed in accordance to the international functional safety standard IEC-61508 and pass a national certification process. However, this thesis solely focuses on th software part. As mentioned before, these modules are usually used in safety critical industrial systems. A failure or malfunction in the PLC module could potentially have catastrophic consequences for the environment and/or the people. In the best-case scenario, a failure would result in the temporary shut down of the production, which would nevertheless cause massive financial losses and bad reputation for the manufacturer of the automation system. The best solution therefore is to reduce the number of potential failures to a bare minimum. This is archived by thoroughly testing the system including the embedded software. Even though it is practically impossible to release a fault-free software, by applying a systematic testing approach it is possible to discover and eliminate as many faults as possible. This approach requires a lot of resources. The relation between the profit and the invested verification effort is shown in Figure 3.1. If insufficient resources are allocated for the testing and verification, the system is much more likely to fail in operation and, as a result, cause immense profit loss. On the other hand, if the system is tested to extensive measures, it may result in a better, more fault-free product but the overall profitability is questionable. Additionally, Figure 3.2 shows that a failure is likely to cost more if discovered in later development stages. Testing and verification of the software is as important as developing. It is a complex, repetitive and resource-consuming process. This chapter is used as a general introduction to embedded software testing based on the V-model according to IEC 61508.

Figure 3.1.: Profit vs. verification effort in software testing [9]

Figure 3.2.: Cost vs. development time in software testing [10]

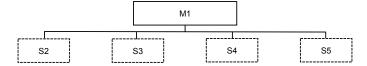

# 3.1. Safety V-Model Life-cycle

Software testing and verification are parts of the general software development process. Software life-cycle models are used for a more structured and methodical approach on the software development. The main idea is to break down the whole software development process into multiple and distinct phases. There are numerous software life-cycle models nowadays. The failsafe peripheral embedded software is developed based on the V-model recommended by the IEC 61508-3 [4] and depicted in Figure 3.3. Compared to a standard V-model life-cycle used in standard software development, the V-model recommended by IEC 61508 additionally handles safety-critical requirements derived from the general system safety requirements specification. The phases of this model form a shape in the form of "V", which explains its name. Development phases are placed at the left side of the "V". Each development phase has an associated testing phase on the opposite side. The goal of each testing phase is to verify the opposite development phase. The abstraction level is represented by the horizontal axis while the vertical axis represents the total time of the development. The

Figure 3.3.: Safety V-model [4]

#### V-model includes following phases:

- Software safety requirement specification: The objective here is to specify the requirements for safety-related software. These requirements are derived from the general system safety requirements specification,

- Software architecture: Software architecture, derived from the general system architecture is created to fulfill the above specified safety-related requirements.

- Software system design: Technical implementation of the software architecture. A set of tools, languages, compilers, user interfaces etc. is selected to be used in further development process. Major elements and subsystems of the software architecture are also defined.

- Module design: The software system submodules are refined in individual software modules with more implementation detail.

- Coding: Actual coding of the previous developed modules.

- Module testing: The goal is to verify if every module is delivering the specified functionality.

- **SW** integration testing: Used to verify the interaction of multiple modules as defined by the software system design.

- HW/SW integration testing: Verifies that the interface between the

software and hardware is working properly.

• Validation testing: The system is tested to certify that it meets the set requirements and functionality.

#### **Test Driven Development**

Another approach to software testing is the test driven development. It was introduced as part of agile development process. In this approach, the developer writes new functionalities and corresponding test cases at the same time. In some cases tests are written even before writing the code. The test cases are derived from the system requirements. However, there needs to be a clear relationship between the written code and the requirements specification. This is not always possible [11].

## 3.2. Testing Techniques

Different testing techniques are used for different test levels. A white-box approach is usually applied for lower level tests such as unit tests. Black-box approach is used for testing at a higher level (e.g., HW/SW integration tests). Both are described in more detail in the following sections.

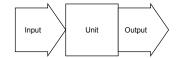

## 3.2.1. Black-box Testing

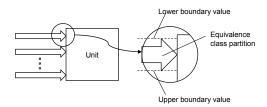

A black-box testing technique verifies the components functionality without knowledge about the component's internal structure. In the example of an object-oriented class, a black-box test is conducted without the original source code. The only important resource is the components design specification as we use it as a test reference to verify the proper functionality of the component. A component is represented as a black-box with inputs and outputs 3.4. To completely test the functionality of the component, a combination of all possible inputs and outputs shall be tested. This is of course, practically impossible, as it would be heavily time and resource consuming. To achieve a reasonable amount of test possibilities, methods like equivalence class partitioning and boundary value analysis techniques are used. A major disadvantage of black-box testing is that it does not provide insight about the test coverage.

Figure 3.4.: Black-box testing

Figure 3.5.: Equivalence class partition

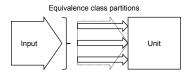

#### **Equivalence Class Partitioning**

One way of reducing the number of inputs to a reasonable amount is partitioning the input range into finite number of partitions. This is illustrated on the example shown in Figure 3.5. The input is partitioned in three input equivalence classes. A partition or equivalence class has a representative member of that class. The test cases can be generated under the assumption that all members of an equivalence class are processed in an equivalent way. Identifying the equivalence classes is the main challenge here. To effectively identify the groups following guidelines by [12] are used:

- 1. If an input condition specifies a range of values, one valid equivalence class and two invalid equivalence classes must be identified.

- 2. If an input condition specifies several values, again, one valid equivalence class and two invalid equivalence classes must be identified

- 3. If an input condition specifies a set of input values and the software handles each differently, a valid and an invalid equivalence class must be identified for each.

If there is a "must-be" situation specified, one valid and one invalid equivalence class must be identified. The valid equivalence classes represent all valid inputs to the program while the invalid classes represent all other possible states, such as erroneous inputs. Although equivalence partitioning covers a decent amount of test cases, it still overlooks some test cases. One example are the boundary values of the appropriate equivalence classes.

Figure 3.6.: Boundary value analysis

#### **Boundary Value Analysis**

Boundary value analysis is a supplementation method for the equivalence class partitioning. When testing equivalence classes, one usually selects a typical test input value, while overlooking atypical values. These values are often found on lower and upper boundary values. Consequently, test cases using those values shall also be written [11]. Figure 3.6 shows an example of applying the boundary value analysis one equivalence class defined above where the upper and lower boundary values are selected as test case inputs.

#### Other Black-box Techniques

The above-mentioned techniques cover most of the unit test cases. Additional test cases can be designed by using one of the following black-box techniques:

- Cause-Effect graphing: Formal language used to yield test cases which explore combinations of different inputs.

- Error guessing: The tester/developer uses his intuition, testing experience and existing knowledge to write additional uncategorized test cases.

# 3.2.2. White-box Testing

A white-box testing approach uses the knowledge of the internal structure of a component to derive test-cases and ensure that all elements of the unit are functioning properly. The source code of the components is usually available at the unit test level. The code contains structural elements such as statements and branches. White-box tests are focused on the degree to which these elements are executed. Test coverage defines the proportion of structural elements which are exercised in the test. Table 3.1 by [13] shows an overview of selected coverage

types with an "•" indicating which coverage criteria is applied. IEC 61508-3 [4] recommends different code coverage metrics for different safety integrity levels. For SIL 3, a 100% coverage for entry points, statements and branches is highly recommended. One should be careful: archiving a high code coverage does not mean that the code is fault free! It can, however, give an overview of which code has been overlooked during testing.

#### **Statement Coverage**

The simplest method to evaluate the test coverage is the statement coverage. The goal is to check if every statement in the program is executed at least once. The minimum requirement for most programs is the decision coverage which in most cases satisfy statement coverage. Consequently, statement coverage is rather an unpopular criterion [14].

#### **Decision Coverage (Branch Coverage)**

To achieve complete decision coverage, each decision element (if-else, switch-case and do-loop) must execute all possible outcomes at least once. The advantage of decision coverage is that it includes the statement coverage as well [15].

#### **Condition Coverage**

The decision coverage may be stronger than the statement coverage, but it is still considered to be weak because it does not cover all possible condition outcomes in a decision. This is covered by the condition coverage. Condition coverage, however, does not require that all decisions take all possible outcomes. This is covered by the next test coverage.

#### **Decision/Condition Coverage**

If, in addition to 100 % decision coverage, every condition outcome is also required, then it is called decision/condition coverage. The problem with this coverage is that certain conditions mask other conditions.

Table 3.1.: Coverage criteria overview: 1) Statement coverage 2) Decision coverage 3) Condition Coverage 4) Decision/Condition Coverage 5) Modified Condition/Decision Coverage [13]

| Coverage Criteria                                                                           | 1 | 2 | 3 | 4 | 5 |

|---------------------------------------------------------------------------------------------|---|---|---|---|---|

| Every point of entry and exit in the program has been invoked at least once                 |   | • | • | • | • |

| Every statement in the program has been invoked at least once                               | • |   |   |   |   |

| Every decision in the program has taken all possible outcomes at least once                 |   | • |   | • | • |

| Every condition in a decision has taken all possible outcomes at least once                 |   |   | • | • | • |

| Every condition in a decision has been shown to independently affect that decisions outcome |   |   |   |   | • |

#### **Modified Condition/Decision Coverage**

MC/DC criteria requires that each condition is shown to independently affect the outcome of the decision. This ensures that each condition is tested in relation to the other condition. MC/DC, however, requires considerably more test cases [13].

#### Other Coverage Criteria

The above coverage criteria are widely used and are highly recommended criteria. There are also some other optional techniques mentioned in IEC 61508-7 [16] like LCSAJ (Linear Code Sequence and Jump) coverage, data-flow coverage and path coverage. However, these techniques are not used in testing failsafe peripheral modules and, thus not covered in the scope of this thesis.

Table 3.2.: Brief overview of test levels and their purpose in the life-cycle

| Test level        | Purpose                                          |

|-------------------|--------------------------------------------------|

| SW unit           | Testing SW components in isolation               |

| SW integration    | Testing interaction between SW components        |

| HW/SW integration | Testing interaction between HW and SW components |

| Validation        | Testing that the system works as specified       |

#### 3.3. Test Levels

The V-model software life-cycle covers different test levels. Table 3.2 shows a brief overview and the main objective of each level.

#### 3.3.1. Unit Test

Unit test is the first testing activity after coding. The software components which were defined and programmed in the previous development phase are now being tested. Unit testing ensures that the component is functioning properly in isolation. It is decisive to ensure that the individual components are tested properly before moving onto the integration test. How to define a component under test? A component should be a smallest meaningful unit which can be tested individually and has a specified function. If a fault is detected, it is then assigned to the tested component. A good example is a class as unit-under-test in object-oriented programming.

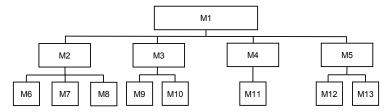

## 3.3.2. SW Integration Test

Precondition for the software integration test is that all the modules are fully tested. This should ensure the correct functionality of the individual modules. Integration tests are used in order to show that all software modules interact correctly. The integration test strategy is explained on the example from [15] as shown in in Figure 3.7. A group of modules is represented as rectangles named from M1 to M13. A line from an upper module to a lower means that the upper calls the lower. To test all the submodules, there are basically two

Figure 3.7.: Integration test strategy example [15]

Figure 3.8.: Top down integration strategy [15]

main approaches: from bottom to top and from top to bottom.

#### **Top-down Integration Test**

Top-down integration starts with the top module. In the example shown in Figure 3.8, M1 is the highest-level module. To write test cases, stubs for modules M2, M3 and M4 are used. The next modules which are integrated are the subordinate modules of the top module. One stub at a time is replaced by the actual module until all modules at this level are tested (M2, M3 and M4). After that, the lowest-level modules are integrated by the same principle as for the higher-level modules. In some cases, testing can be done in parallel. For example, while one tester is testing M2 and its subordinates, the other can test the M3 subsystem. The top-level module is tested first in this type of integration. This can be quite useful for more complex modules which need more time for testing. Furthermore, it can also be advantageous if major flaws are found in the top-level module.

#### **Bottom-up Integration Test**

Bottom-up integration is explained on the same example as above. It begins with testing the lowest-level modules. These are the modules which do not include any other modules. In the example above, these are the modules from M6 to M13. After testing the lowest module, the next step is to integrate the modules on the upper level. The upper level module, which was used as a driver

Figure 3.9.: Bottom up integration strategy [15]

for the lower level modules, is now replaced by the actual module. At this stage, this module needs a driver. The same procedure is followed for all other modules until the highest-level module is reached. Lowest level modules are tested well at the beginning of the process. This can be useful if flaws occur toward the bottom of the program. However, due to the lack of time at the later process of integration, the top module may not be well tested. This can be quite risky if the top module is safety-critical. Another major disadvantage of the bottom-up integration is that the program does not exist until the last module is integrated.

Neither of the methods have a clear-cut advantage. Thus, in many cases a combination of the two approaches is used. Also, risk factors and complexity are taken into consideration. Safety-critical modules should be tested adequately and earlier in the integration process. Another aspect to consider is the availability of the modules: not all modules will be available at any time. The software integration is completed after all software modules are integrated. The next step is to test the interaction between software and hardware.

# 3.3.3. HW/SW Integration Test

After all of the software modules have been integrated, the next step is to integrate the software subsystems into hardware. The goal here is to verify the interaction and interfaces between the software and hardware.

## 3.3.4. Validation Testing

While previous test phases focus on discovering faults in the system, validation testing validates if the system fulfills all the requirements. Primary goal of the validation is to show that the system delivers specified functionality and is good enough in terms of performance and reliability. Validation tests usually include requirements-based testing, scenario testing and performance tests. Typical

test cases are derived from system specifications and use a black-box approach [11].

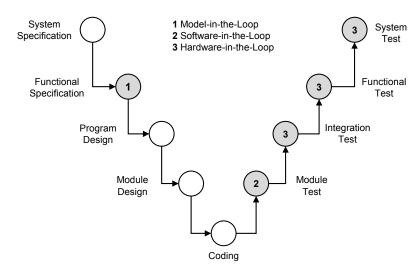

# 3.4. Simulation Techniques in Testing

Table 3.3 is an extended version of Table 3.2. Added columns specify which components of a system are used as experimental, prototyped or real on different testing levels. It is evident that different parts of the embedded system are simulated through different test levels. To cover that, the general term X-in-the-loop has been established in the literature [10]. The term X-in-the-loop covers a group of simulation techniques: model-in-the-loop, software-in-the-loop, hardware-in-the-loop and processor-in-the-loop. Following is a brief description of the x-in-the-loop techniques:

- Model-in-the-Loop (MiL): Except the host PC where the simulation is executed, the MiL approach does not include any hardware components. This technique is used at an early stage of safety life-cycle and is not covered in this thesis.

- Software-in-the-Loop (SiL): In some literature the term SiL is often referred to as MiL because, just like MiL, no real hardware is used. The only difference is that the model of the embedded software is replaced by the real prototyped software. The software is compiled on an ISS (Instruction Set Simulator) and a simulation of hardware components is used. This is the simulation technique covered in this thesis.

- Processor-in-the-Loop (PiL): PiL is like SiL with one key difference: the software is compiled and run on the target processor instead of using the ISS. The PiL is important because it can reveal faults caused specifically by the target architecture.

- Hardware-in-the-Loop (HiL): HiL approach is used at later stages of the software development for validation purposes. The target embedded software is compiled on the target processor and hardware. The environment of the embedded system is simulated.

The example of development of automotive ECUs, [17] offered a good overview how different x-in-the-loop techniques are implemented in different phases of the V-model. This is illustrated in Figure 3.10. Early in the development phase, the functional specification phase is supported by a MiL simulation. In the

Figure 3.10.: Simulation techniques in the development of modern ECUs [17]

testing phase, SiL simulation is used in module testing. The later test stages such as integration, functional and system testing are supported by a HiL simulation.

## 3.5. Conclusion

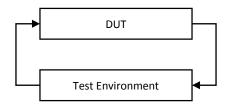

Software development of peripheral failsafe modules directly follows the V-model life-cycle, especially in the testing phase. Traditional testing only carried out tests on levels mentioned in Table 3.2. However, the need to discover faults and test new functionalities as early in development phase as possible, combined with the need to have more transparent overview of the HW/SW integration test, led to an idea to use simulated hardware components. Consequently, a set of test levels was introduced which can be found emphasized in Table 3.3. It is important to note that the proposed test levels are not meant to substitute existing test levels but rather to supplement them. From the x-in-the-loop approach, these tests are closest to a SiL simulation, because the hardware is not being used. Basic SiL simulation block diagram is shown in Figure 3.11. The device under test (DUT) is the virtual peripheral module which includes the software code compiled on an ISS (Instruction Set Simulator) and simulated hardware. Test environment controls the simulation, provides input to the DUT

## 3. Testing Embedded Systems

Figure 3.11.: SiL simulation diagram

and gets output data from it. Finally, to successfully implement and fully utilize the proposed testing levels, software models of the target hardware is needed. Therefore, the subsequent chapter elaborates how to model the hardware of an embedded system.

Table 3.3.: Test levels and simulation

| Test level            | Software     | Hardware  | Processor |

|-----------------------|--------------|-----------|-----------|

| SW unit               | experimental | prototype | real      |

| SW unit (S)           | experimental | simulated | simulated |

| SW integration        | experimental | prototype | real      |

| SW integration (S)    | experimental | simulated | simulated |

| HW/SW integration     | real         | prototype | real      |

| HW/SW integration (S) | real         | simulated | simulated |

| Validation            | real         | real      | real      |

In the previous chapter, simulation-based testing was introduced which requires simulated hardware. It was established that, software models of the hardware are needed in particular. Modeling in general and specifically modeling embedded systems is by no means a straightforward and streamlined process. By using one of the many modeling methodologies and frameworks, the challenge is not the modeling process by itself, but rather the preparation. Before modeling, ofollowing questions arise: what is the main task that the model should be used for and, in respect to that task, how much detail is needed. Furthermore, a model can be realized on different abstraction levels. Optimal modeling effort is achieved by choosing the right abstraction level.

## 4.1. Abstraction Levels

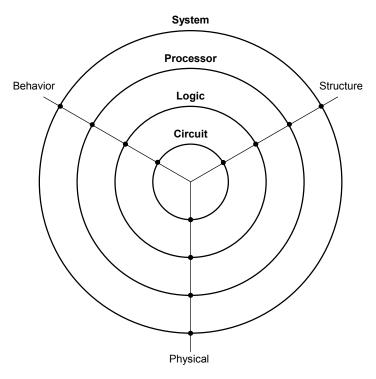

One approach to categorize abstraction levels in the embedded systems is the Gajski-Khun Y-Chart, invented in 1983 [18]. It was originally introduced to deal with the classification and structuring of design process by using a set of well-defined abstraction levels. Four different abstraction levels are represented: system, processor, logic and circuit level. They are graphically represented as concentric circles shown in Figure 4.1. The levels are defined by the components derived on the specified level. On every abstraction level, three different aspects are considered: behavioral, structural and physical. Behavioral aspect covers the functionality of the design. The design is considered as set of interconnected components in the structural aspect. Finally, physical aspect adds dimension specifications to each component. Gajski [19] also lists the typical components found on each abstraction level, which helps in identifying the right level. These components, sorted by levels, are:

- Circuit level: cells consisted of P/N-type transistors

- Logic level: registers, register files, ALUs and multipliers

- **Processor level:** processors, memory controllers, bridges and different interface components

- System level: embedded systems made of processors, memories, buses and other components.

Figure 4.1.: Y-chart diagram [19]

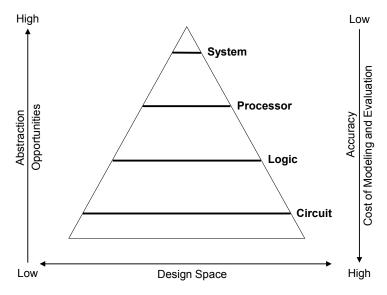

# 4.2. Abstraction Pyramid

To choose the right abstraction level always requires the trade-offs to be made. This involves mainly three different issues: the modeling effort, evaluation effort and the model accuracy. To put those aspects into the perspective of the system level design, the abstraction pyramid was introduced by [20]. Abstraction levels presented in the previous section are placed in the context of the abstraction pyramid shown in Figure 4.2.

Level of Detail. Concentric circles from the previously introduced Y-Chart diagram are directly mapped as horizontal lines on the abstraction pyramid.

Cost of Modeling. Moving down in the pyramid means moving down to lower abstraction levels. This results in a more detailed architecture where more details need to be considered and which consequently results in an increasing amount of effort. This is indicated on the axis on the right side of the pyramid.

Opportunity to Change. Different design choices lead to lower abstraction levels. At that point, to consider another architecture becomes costlier. Consequently, the exploration opportunity at that level is low.

**Accuracy.** The accuracy of the models is represented by the axis on the left side of the pyramid. The model accuracy increases with lower abstraction levels.

Cost of Evaluation. Placed on the same axis as the cost of the modeling is the cost of evaluation. It was already mentioned that the modeling effort increases proportionally with the amount of modeling detail involved. This also means an increasing evaluation effort.

Figure 4.2.: Abstraction pyramid [20]

With a specific modeling task in mind and in respect to the abstraction pyramid above, it is time to consider the abstraction level. Since the main task is simulation-based testing and not hardware synthesis, level of detail and accuracy is traded for simulation speed and effort of modeling. This puts the target model on a system abstraction level which by definition handles embedded system components such as processors, memories, peripherals etc.

# 4.3. System Level Modeling

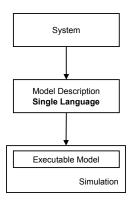

After choosing the right abstraction level, the next decision to make is how to approach the modeling process. According to [21], there are basically two different modeling approaches used to model a system: homogeneous/single-language modeling and heterogeneous/multi-language modeling. By using the homogeneous approach, a single-language is used to model the complete system including the hardware and software. This approach is often not applicable to complex systems. In such cases the heterogeneous approach is applied, where multiple languages are used for different domains of the system.

# 4.3.1. Single-Language Approach

By using a single-language approach, the intent is to find possibly one general language to describe the complete system. Homogeneous modeling approach results in a single, executable system. Only one simulator is needed to execute and verify the model and simulation handling is therefore much easier. However, it is hard to find a system which is simple enough to be described by just one language. Most of the systems require different languages for different domains. To tackle such systems, a multi-language approach is introduced. This is illustrated on Figure 4.3

Figure 4.3.: Single-language approach [21]

# 4.3.2. Multi-Language Approach

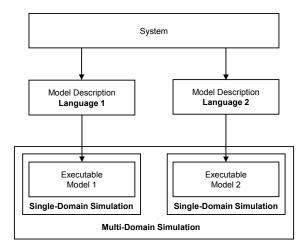

Multi-language approach uses different modeling languages for different domains simultaneously. This results in multiple execution models with different simulation environments. A major problem here is the coupling of these simulation environments. One of the possible solutions is to use a common intermediate language. This way, different models are converted into a common language which is later executed in a single simulation environment. This method is an extension of the single-language approach but provides more flexibility and makes modeling of the complex systems possible. Another option is to skip the intermediate common language altogether and combine the respective execution models and corresponding simulation environments into a multi-domain simulator. Every model is simulated separately and at the final stage synchronized with a common simulator. Although the formal verification of the complete system is hardly achievable, the approach provides a platform for developing complex simulations which can be executed efficiently. Multi-language approach is shown in the Figure 4.4.

Figure 4.4.: Multi-language approach [21]

# 4.4. Existing System-Level Modeling Languages

After choosing the right modeling approach, the designer faces one more challenge: to select the modeling language or platform. In early stages of hardware

modeling, dealing with gate level and register-transfer-level design, hardware-description-languages (HDLs) such as VHDL and Verilog were introduced. Although, these languages were suitable for modeling hardware on lower abstraction levels, the transition to the system level modeling resulted in new requirements such as modeling parts of the system implemented in software. Additionally, a system-level language must be executable, modular and complete [22]. This lead to an introduction of system-level design languages (SLDL) based on C/C++ [19].

# 4.4.1. SpecC

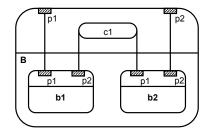

One of the system-level design languages is SpecC [23], which is based on C programming language. Thus, it covers the complete set of C constructs. Additionally, it supports constructs covering the system level design requirements. One of those requirements is modularity, which is required to separate the behavior of the system from its structure. With behavioral hierarchy the system behavior is decomposed in multiple sub-behaviors, whereas structural hierarchy allows decomposing a system into multiple interconnected components. A SpecC program typically consists of a set of behaviors, channels and interfaces [22]. A behavior describes a functionality and consists of ports, component instantiations, variables and functions and a main function. Channels encapsulate the communication while the interfaces represent a link between behaviors and channels. An example of a SpecC system is shown in Figure 4.5. The system realizing a behavior B is hierarchically decomposed into two sub-behaviors b1 and b2 which communicate via channel c1. The sub-behaviors can be executed either sequentially or concurrently [23]. A special SpecC compiler is needed to compile the program. The compilation results in an intermediate C++ model, which can be then compiled using a standard C++ compiler [22].

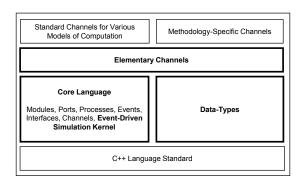

# 4.4.2. SystemC

Another system-level modeling language is SystemC [24], which is basically a set of C++ classes. It allows fast simulation at different abstraction levels, from system to register-transfer-level. Another great feature of the SystemC is the model interoperability, which was introduced with the Transaction Level Modeling (TLM) [25]. SystemC meets the imposed requirements set by ESL design. These include the abstraction span on several levels, a standardized

Figure 4.5.: Basic structure of a SpecC model [23]

language, proper simulation speeds and performance and support of TLM concepts. For that reason, SystemC is rapidly adopted in the industry [26].

Figure 4.6 describes SystemC as a set of blocks and layers. The base layer on the bottom shows that SystemC is built and based on the standard C++ language. The bold emphasized group of blocks are parts of the SystemC standard which includes the simulation kernel and core language elements. Alongside the core language is the data-type group. The elementary channels layer above the core language and data-types include models such as signals, timers and FIFO buffers. Unlike the emphasized layers, the topmost layers are not part of the SystemC standard but represent other models, libraries and extensions to support additional features [27]. A study by [28] used SystemC to model a safety-critical embedded system. A co-design and a simulation of fault injection in train on-board safety-critical odometry system has been proposed. The goal was to develop a simulation environment to implement fault-injection techniques in multiple steps of the design process, as recommended by IEC 61508. This approach resulted in preventing late discovered faults. The study demonstrated advantages of SystemC such as describing both hardware and software in common language and execution of concurrent processes.

#### SystemC and VHDL Comparison

A case study [29] directly compared traditional hardware-definition-language VHDL with SystemC by modeling a simple load-store processor on a register-transfer-level. The comparison relied upon the simulation time and modeling effort. In terms of simulation time, SystemC is much faster compared to VHDL, reaching a difference in an order of magnitude. Although hardware-software co-simulation is possible in VHDL, it requires external tools and libraries. SystemC uses the same language for hardware description and for co-simulation. Hence,

Figure 4.6.: SystemC language architecture [26]

the modeling effort with SystemC is much lower compared to VHDL. In conclusion, SystemC is much better suited for higher abstraction levels.

# 4.4.3. **C/C++** Modeling

A methodology for hardware/software co-verification in C/C++ presented by [30] provides several advantages of C/C++ based methodologies over HDLbased methodologies. In traditional hardware-software co-simulations the hardware is usually described in an HDL whereas the software is mainly C/C++based. Data is transferred between software and hardware written in different languages. By using just one language, the data transfer can be made much efficiently. Productivity can be further improved by eliminating the transition to a HDL and reusing test benches written in C/C++. Avoiding the translation to a HDL not only improves the efficiency of the simulation but also removes bugs produced by this translation. The programmers, which are already proficient in using C/C++ save time and effort by not learning a new language. Instead, they can focus on writing better functional models. [31] discussed the use of C++ in modeling digital systems and came to the conclusion that C++ is a well-suited language for system modeling. Without introducing new syntax or compiler, it allows the writing of modeling primitives based on C++ mechanisms such as classes, templates and operator overloading. The main drawbacks of C/C++ modeling are lack of concurrency, missing the ability to entail structural information and constraints and lack of support for timing constraints. However, these drawbacks can be neglected when using functional models on a system level and are not relevant for hardware synthesis [32].

# 4.5. System-Level Modeling Platforms

### 4.5.1. Commercial Tools

There are several commercial virtual prototyping tools available. Wind River Simics [33] is a full-system simulation tool which can simulate the processor and dedicated peripherals in such detail that it can run the target software. It features very fast bit-accurate instruction set simulators which can emulate targets such as PowerPC, MIPS, MIPS64, ARM, x86 or SPARC without any special host hardware and software. Alongside the processors, Simics offers a number of models for flash memories, I2C buses, timers and other components. If a specific target model needs to be developed and it is not available by Simics, a specific language called DML is created for writing new models [5]. Synopsis [34] also offers a virtual prototyping solution covered by Platform Architect, Virtualizer Studio and according to their website, the largest portfolio of TLM models. Virtual System Platform by Cadence [35] is another commercial tool for virtual prototyping. Just like Wind River and Synopsis, Cadence also offers a library of TLM IP models. Additionally, they also offer support for Imperas OVP fast processor models (which is covered later). Another great feature is an automatic TLM 2.0 code generation, which reads a custom text-based language called IP-XACT and produces a TLM 2.0 model without requiring TLM 2.0 knowledge. There are many other commercial virtual prototyping commercial tools. This section only mentioned the most popular ones. These tools have high licence fees. However, there are a number of open-source alternatives covered below.

### 4.5.2. **OVPSim**

Imperas Open Virtual Platforms [36] offer open source software for developing virtual platforms: an API, a simulator and a library of free open source processor and peripheral modules. All OVP models are fully SystemC and TLM 2.0 compatible by using APIs and TLM 2.0 wrappers. However, every model needs to be redesigned individually. [37] offered a much easier way to integrate OVP models in SystemC using a SystemC bridge. In [38] OVP was used in a SiL simulation of an embedded control application.

### 4.5.3. **QEMU**

QEMU [39] is a generic and open source machine emulator and virtualizer. Two emulation modes are available: full-system and user-mode. In the user-mode, QEMU can launch processes compiled for one CPU on another CPU. Fullsystem mode is used to emulate the processor and its peripherals. QEMU offers and provide support for systems based on following architectures: x86, ARM, PowerPC and MIPS. Unlike OVP, there is no native support for integration of System C models. However, [37] developed a System C bridge for integrating QEMU in SystemC. Moreover, a number of co-simulations have worked on that. [40] added a set of plug-ins that enabled to integrate SystemC modules in QEMU as peripherals to the emulated platform. The connection between was implemented using TLM channels. [41] offered a different approach by integrating QEMU in a SystemC. The QEMU virtualizer is treated as a standard SystemC module. In modeling cyber-physical systems, [42] used SystemC and QEMU for modeling hardware of the micro-controller. [43] developed a simulator for networked embedded systems. The simulation framework is based on QEMU and SystemC, where QEMU was used for the execution of target software while SystemC was used for accurate modeling of network protocols and topologies. The simulator was then applied for robustness testing of the communication layers in a embedded fire alarm system. The test results only confirmed the benefits of using a virtual prototype such as test automation, exploration of unlikely test scenarios and increased observability. [44] presented another approach in connecting QEMU and SystemC using a TLM-2.0 interface. [45] used QEMU, SystemC with other commercial ESL simulation tools.

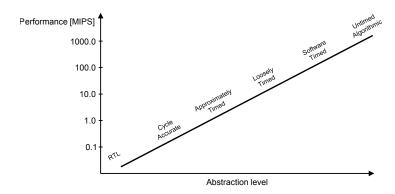

# 4.6. Modeling Timing Behavior

Timing is an important aspect to cover in system modeling. When considering integrating timing behavior in a virtual prototype, the same universal modeling principles apply: making design decisions in terms of abstraction level and simulation performance. [46] illustrated that in Figure 4.7. Below the approximately timed (AT) abstraction level are clocked levels. This means that the simulation is clock-driven. Above the AT level, simulation is advanced by transactions (data transfer e.g.). The diagram shows that the simulation performance differs by one or two orders of magnitude between two levels. Additionally, the time

required to develop the model is also increasing with lower abstraction level. Levels below the AT are typically used in the domain of hardware developers. In scope of system modeling, higher abstraction levels are interesting.

#### **Code Instrumentation**

[47] introduces a basic approach for integrating timing behavior into a system: code instrumentation. The base idea is to instrument the code by timing statements with a dedicated time values. The main advantage of this approach are very fast simulation times. However, the determination of execution time requires detailed code analysis and is very time consuming. There are basically two approaches in determining execution times: analytical and simulative. Analytical approaches use detailed code analysis and WCET/BCET (Worst Case Execution Time/Best Case Execution Time). The result is an approximate mean value of execution times which gives a rough impression of the behavior of the system. Simulative approaches use a simulation on a target ISS and simulated hardware peripherals to obtain timing behavior. [48] presented a hybrid approach by combining the two. First, they used a static analysis of code. The extracted timing information is then back-annotated in the simulation code. This considers the aspects not covered by static approaches. Moreover, the approach showed significant simulation speeds while maintaining good accuracy.

As a conclusion, to accurately integrate timing behavior in the simulation, one needs a cycle-accurate processor model. The simulation however, is at a system level and the timing information is only used for logging and diagnosis purposes. Thus, for the implementation of the target system a software-timed model is preferred. The timing will be implemented using the code instrumentation method.

# 4.7. Conclusion

The chapter concludes with a decision about what kind of a system modeling platform/language is used for modeling the target system. Virtual prototyping commercial tools would be a great choice because they offer a number of toolboxes, large database of IP models and even support importing of additional SystemC-TLM models. However, commercial tools are not available without

Figure 4.7.: Level of abstraction vs. performance in modeling timing behavior [46]

paying high license fees, thus they are not taken into consideration. Alternatively, there are open-source platforms such as OVP and QEMU. Even though, they both offer support for a great number of processors, including the target ARM processor, they lack a database of our target peripheral IP models. This means, that one would have to manually create, not only the SystemC models, but also wrappers and bridges to connect them to the simulation. This would lead to an excessive modeling effort. When it comes to system-level modeling languages, literature research above showed a massive use of SystemC. SystemC in a combination with a instruction set simulator would indeed be a good choice if the sole purpose of this thesis was to create a virtual prototype of the target hardware. However, this thesis deals with modeling failsafe programmable systems in accordance with the international standards. IEC 61508 also covers the aspect of software tools used during the software development life-cycle and according to [49], all software tools used during the software development life-cycle are divided in three classes: