http://www.ub.tuwien.ac.at/eng

FAKULTÄT FÜR !NFORMATIK

Faculty of Informatics

# Time-predictable Memory Hierarchy

## DISSERTATION

zur Erlangung des akademischen Grades

## Doktor der technischen Wissenschaften

eingereicht von

#### Bekim Chilku

Matrikelnummer 0928443

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Peter Puschner

Diese Dissertation haben begutachtet:

(Prof.Dr. Björn Lisper)

(Ao.Prof.Dr. Martin Schöberl)

Wien, 20.08.2018

(Bekim Chilku)

**Faculty of Informatics**

# Time-predictable Memory Hierarchy

## DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

#### Doktor der technischen Wissenschaften

by

Bekim Chilku

Registration Number 0928443

to the Faculty of Informatics at the Vienna University of Technology

Advisor: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Peter Puschner

The dissertation has been reviewed by:

(Prof.Dr. Björn Lisper)

(Ao.Prof.Dr. Martin Schöberl)

Wien, 20.08.2018

(Bekim Chilku)

## Erklärung zur Verfassung der Arbeit

Bekim Chilku Schottenfeldgasse 1/20, 1070 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasserin)

## Acknowledgements

This thesis is the result of my academic research at the Institute for Computer Engineering, Department for Real-Time System, at Vienna University of Technology.

At first I would like to express my gratitude to my supervisor Peter Puschner, who gave me the opportunity to do my research in the area of Real-Time Systems. The discussions and suggestions from him have been very encouraging and supportive during my research.

Next, I would like to thank Martin Schöberl and his team for the insightful discussions and the friendly work environment I received during my stay at Technical University of Denmark. Their constructive comments incented me to further widen my research.

Furthermore, I would like to thank my fellow colleagues from the Institute of Computer Engineering for the support, collaboration and the positive work atmosphere they provided during my stay at the Institute. I also want to thank Daniel Prokesch, who implemented the single-path code analysis as part of the toolchain.

And last but not least, I want to praise my family and friends for their support during my years of studies in Vienna. Especially, I would like thank my parents for the emotional and spiritual support throughout writing this thesis.

## Abstract

Computing the Worst-Case Execution Time (WCET) of a task becomes mandatory when timing guarantees on task completion deadlines have to be given. Unfortunately WCET computation is a complex undertaking, especially for systems that use caches, out-of-order pipelines, and control speculation. The state-of-the-art WCET tools are avoiding the complexity problem by substituting the real hardware with abstracted models. However, abstraction leads to lots of unclassified model states, which in turn results in overly pessimistic WCET bound and poor processor utilization.

Single-path code is another alternative to eliminate complexity on timing analysis by transforming the conventional code into a code that has single execution trace. The approach converts all input-dependent alternatives of the code into pieces of sequential code as well as loops with input-dependent termination condition into loops with constant execution count, thus eliminating all control-flow induced variations in execution time. For obtaining the information about the timing of the code, it is sufficient to run the code once and measure the time. The major drawback of the single-path approach is its potential to end up with a quite long execution time.

In this work we address the problem of long execution time of single-path code. In particular, we focus on narrowing the speed gap between processor and main memory, by proposing a new prefetcher that brings instructions into the cache before they are required. The prefetcher exploits the time-predictable properties of single-path code to accurately predict the target of each prefetch request without polluting the cache at any moment. Another advantage of the prefetcher is its efficiency by issuing prefetch request for every possible cache miss that can occur during the runtime of the code.

In order to make the system design composable and compositional, we propose a new memory hierarchy that provides stable timing through the execution of the code. Although single-path code always runs through the same sequence of instructions, the timing of instructions can vary due to dependencies on the memory hardware states. In order to achieve stability on execution time we need to have repeatability on the history of the hardware states on each layer of the memory hierarchy. Therefore, we have defined a new memory-hierarchy organization that forces the sequence of the hardware states in the memory hierarchy to be repeatable for any iteration of the code. The memory hierarchy is also adapted to allow fetching and prefetching processes to work in parallel without interfering with each other in order to reach the best performance.

To demonstrate the applicability of the new concept, we have implemented the architecture of the system with the new memory hierarchy on an FPGA board and run experimental evaluation. The results prove the benefits that can be achieved in timing performance for single-path code.

## Kurzfassung

Die Berechnung der maximalen Ausführungszeit (WCET) eines Tasks ist unumgänlich, wenn Zeitgarantien für die Beendigung von Tasks gegeben werden müssen. Leider stellt eine WCET-Berechnung ein komplexes Unterfangen dar, insbesondere für Systeme die Caches, Out-oforder-Pipelines und spekulative Ausführung nutzen. Die neuesten WCET-Tools vermeiden das Komplexitätsproblem indem sie die Hardware durch abstrakte Modelle ersetzen. Allerdings führt Abstraktion zu vielen nicht klassifizierten Modellzuständen, die wiederum überpessimistische WCET-Schranken und eine schlechte Ausnutzung des Prozessors ergeben.

Single-Path-Code ist eine Alternative, die die Komplexität der Zeitanalyse beseitigt, indem konventioneller Code in einen Code mit einem einzigen Ausführungspfad umgewandelt wird. Diese Herangehensweise wandelt alle eingabeabhängigen Alternativen des Codes in Teile eines sequentiellen Codes um und transformiert alle Schleifen mit eingabeabhängigen Abbruchbedingungen in Schleifen mit konstanter Anzahl von Ausführungen, so dass folglich alle von Kontrollflüssen bedingten Schwankungen in der Ausführungszeit eliminiert werde. Um Informationen über die Laufzeit des Codes zu erhalten, genügt eine einmalige Ausführung und Messung der Zeit. Der große Nachteil des Single-Path-Ansatyes besteht in einer potenziell sehr langen Ausführungszeit des resultierenden Codes.

Diese Arbeit beschäftigt sich mit dem Problem der langen Ausführungszeit von Single-Path-Code. Insbesondere wird ein neuer Prefetcher vorgestellt, der Instruktionen in den Cache lädt bevor diese gebraucht werden, um den Geschwindigkeitsunterschied zwischen Prozessor und Hauptspeicher zu verringern. Der Prefetcher nutzt die vorhersagenden Eigenschaften von Single-Path-Code, um das Ziel der nächsten Prefetch-Anfrage genau vorherzubestimmen, ohne den Cache zu korrumpieren. Ein weiterer Vorteil des Prefetchers ist die effiziente Verhinderung jedes möglichen Cache-Miss der während der Laufzeit des Codes auftreten kann.

Um das Systemdesign zusammensetzbar und kompositionell zu gestalten wird eine neue Speicherhierarchie vorgeschlagen, die stabiles Zeitverhalten während der Codeausführung liefert. Obwohl Single-Path-Code immer dieselbe Anweisungssequenz ausführen, kann die Laufzeit aufgrund der Abhängigkeit vom Zustand der Speicher schwanken. Um eine stabile Ausführungszeit zu erhalten, benötigt man die Wiederholbarkeit in der Folge der Hardwarezustände auf jeder Schicht der Speicherhierarchie. Deshalb wird in dieser Arbeit auch eine neue Speicherhierarchie definiert, die erzwingt, dass die Sequenzen der Hardwarezustände in der Speicherhierarchie für jede Iteration des Codes wiederholbar sind. Die Speicherhierarchie ist auch so adaptiert, dass sie die parallele Arbeit der Fetching und Prefetching Prozesse ohne gegenseitigen Beeinträchtigung erlaubt, um die beste Performance zu erzielen. Zur Demonstration der Anwendbarkeit des neuen Konzeptes wird die Architektur eines Systems mit der neuen Speicherhierarchie auf einen FPGA-Board implementiert und experimentelle Evaluierungen ausgeführt. Die Ergebnisse beweisen die erzielbaren Vorteile in der Ausführungsperformance für Single-Path-Code.

## Contents

| 1 | 1.1<br>1.2<br>1.3<br>1.4                      | oduction       1         Introduction to Hard Real-Time Systems       1         Motivation       2         Contribution       5         Structure of the Thesis       6           |

|---|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | <b>Wor</b> 2.1                                | st Case Execution Time Analysis vs. Single-path Conversion9Worst-Case Execution Time Analysis9                                                                                    |

|   | 2.1                                           | WCET Analysis Issues on Modern Hardware                                                                                                                                           |

|   | 2.3                                           | Single-path Approach                                                                                                                                                              |

|   | 2.4                                           | Chapter Summary                                                                                                                                                                   |

| 3 | Bac                                           | kground on Memory Hierarchy 21                                                                                                                                                    |

| - | 3.1                                           | The Concept of Memory Hierarchy                                                                                                                                                   |

|   | 3.2                                           | Memory technologies                                                                                                                                                               |

|   | 3.3                                           | Cache Memory                                                                                                                                                                      |

|   | 3.4                                           | Scratchpad Memories                                                                                                                                                               |

|   | 3.5                                           | Main Memory                                                                                                                                                                       |

|   | 3.6                                           | Prefetching                                                                                                                                                                       |

|   | 3.7                                           | Chapter Summary         39                                                                                                                                                        |

| 4 | Tim                                           | e-predictable Instruction Prefetching 41                                                                                                                                          |

|   | 4.1                                           | Towards Effective and Time-predictable Prefetching                                                                                                                                |

|   | 4.2                                           | Prefetching Algorithm for Single-path Code                                                                                                                                        |

|   | 4.3                                           | Architecture Model of the Single-path Code Prefetcher                                                                                                                             |

|   | 4.4                                           | Compact Representation of Code Behavior Information                                                                                                                               |

|   | 4.5                                           | Chapter Summary                                                                                                                                                                   |

| 5 | <b>Tim</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5 | e-predictable Memory Hierarchy67Memory Hierarchy for Single-path Code67Organization of the On-chip Memory69Organization of the Main Memory71Prefetch Filtering72Chapter Summary73 |

|   | 5.5                                           | Chapter Summary                                                                                                                                                                   |

| 6                       | Impl            | lementation and Evaluation                                      | 75 |  |  |  |  |  |  |  |  |  |  |

|-------------------------|-----------------|-----------------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|

|                         | 6.1             | T-CREST platform and Patmos Processor                           | 75 |  |  |  |  |  |  |  |  |  |  |

|                         | 6.2             | Implementation of the single-path code prefetcher               | 76 |  |  |  |  |  |  |  |  |  |  |

|                         | 6.3             | Implementation of the cache                                     | 79 |  |  |  |  |  |  |  |  |  |  |

| 6.4 Evaluation Platform |                 |                                                                 |    |  |  |  |  |  |  |  |  |  |  |

|                         | 6.5             |                                                                 |    |  |  |  |  |  |  |  |  |  |  |

|                         | 6.6             | Chapter Summary                                                 | 86 |  |  |  |  |  |  |  |  |  |  |

| 7                       | Related Work    |                                                                 |    |  |  |  |  |  |  |  |  |  |  |

|                         | 7.1             | Static Analysis of Conventional Cache Memory                    | 87 |  |  |  |  |  |  |  |  |  |  |

|                         | 7.2             | Scratchpad Memories as an alternative in Hard Real-time Systems | 89 |  |  |  |  |  |  |  |  |  |  |

|                         | 7.3             | Cache Locking Techniques for Predictability Improvement         | 90 |  |  |  |  |  |  |  |  |  |  |

|                         | 7.4             | Instruction Cache with Time-predictable Architecture            | 91 |  |  |  |  |  |  |  |  |  |  |

|                         | 7.5             | Memory with WCET-aware Instruction Prefetcher                   | 92 |  |  |  |  |  |  |  |  |  |  |

|                         | 7.6             | Chapter Summary                                                 | 93 |  |  |  |  |  |  |  |  |  |  |

| 8                       | Con             | clusion and Future Work                                         | 95 |  |  |  |  |  |  |  |  |  |  |

|                         | 8.1             | Conclusion                                                      | 95 |  |  |  |  |  |  |  |  |  |  |

|                         | 8.2             | Future Work                                                     | 96 |  |  |  |  |  |  |  |  |  |  |

| Bi                      | Bibliography 97 |                                                                 |    |  |  |  |  |  |  |  |  |  |  |

## **List of Figures**

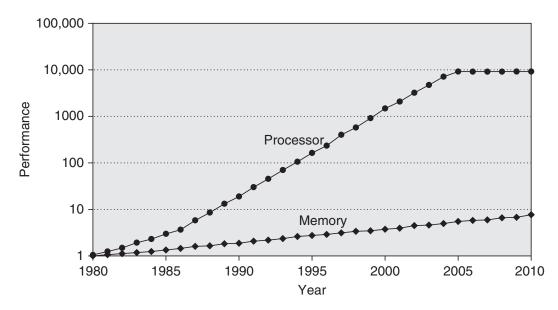

| 1.1                                    | Performance gap between processor and DRAM memory over the years [50]                                                                                                                                                           | 4                                |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2.1<br>2.2<br>2.3                      | Distribution of the execution time for conventional and converted single-path code .<br>Conversion of branch code into serial code with predicated instructions<br>Conversion of conventional loop into a loop with stable time | 16<br>17<br>18                   |

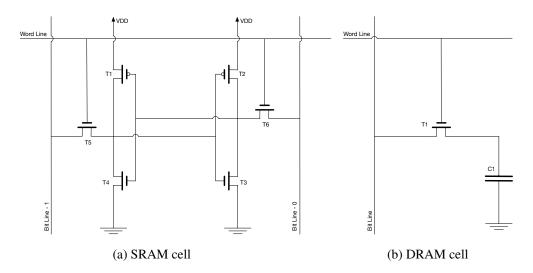

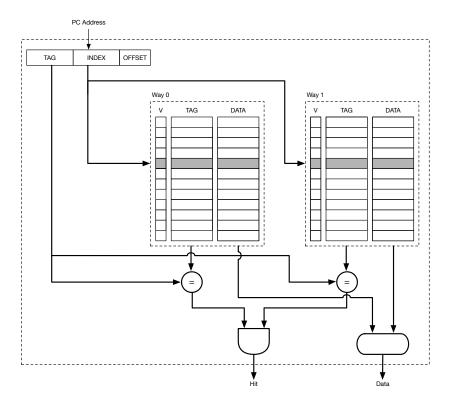

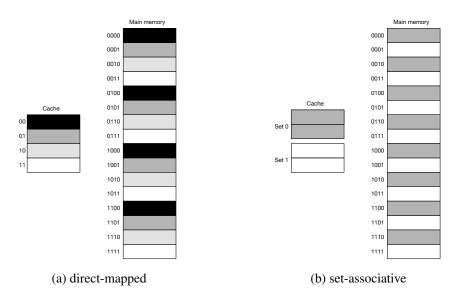

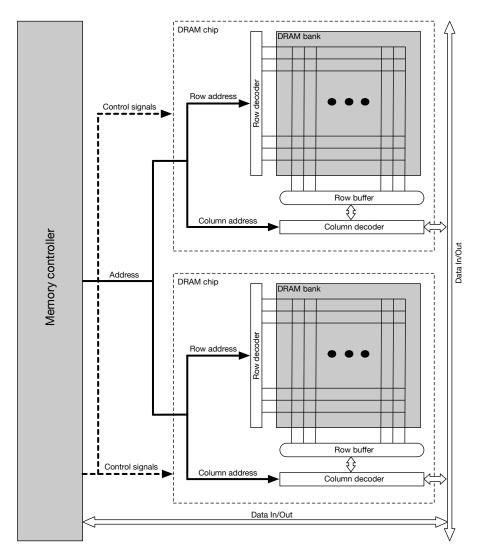

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6 | Levels of memory hierarchy in embedded system                                                                                                                                                                                   | 22<br>23<br>24<br>26<br>28<br>32 |

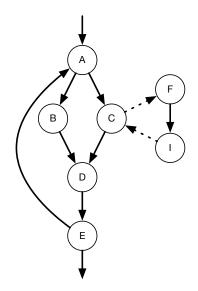

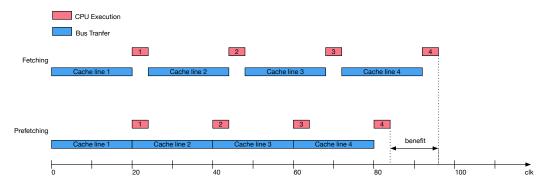

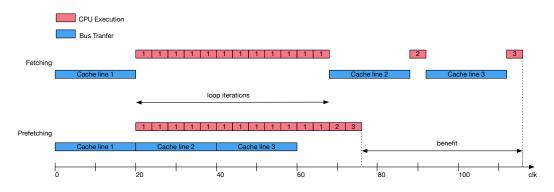

| 4.1<br>4.2<br>4.3                      | Control flow graph of single-path code consisted of <i>if-branch</i> , <i>loop-branch</i> , <i>call-branch</i> and <i>return-branch</i><br>Conversion of nested loops<br>Reducing the cache miss latency through prefetching    | 46<br>47<br>49                   |

| 4.4<br>4.5                             | Reducing the cache miss rate through prefetching                                                                                                                                                                                | 50<br>51                         |

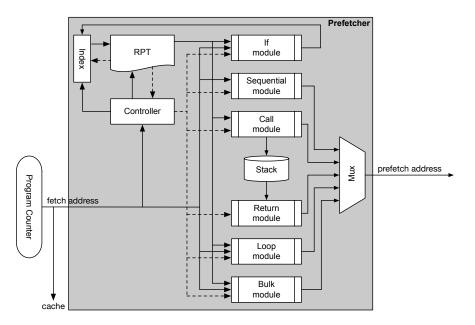

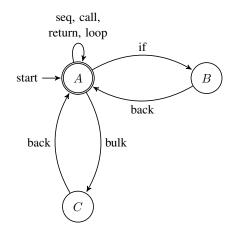

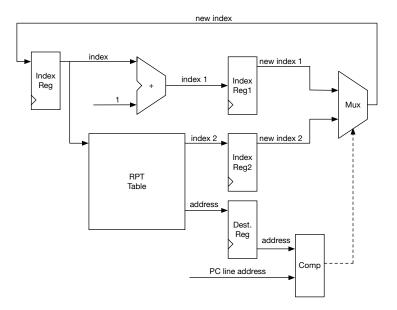

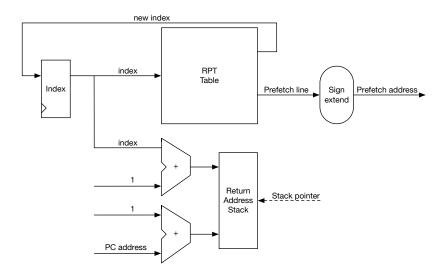

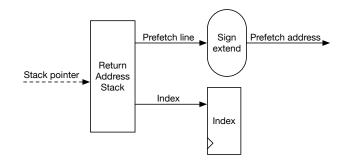

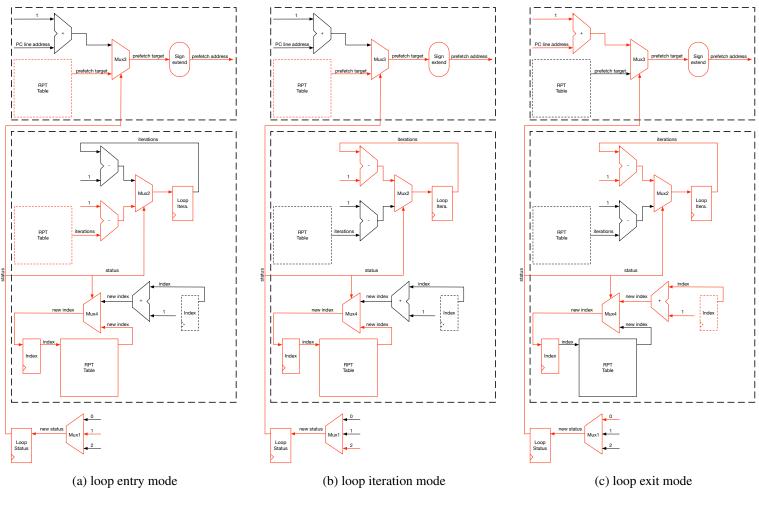

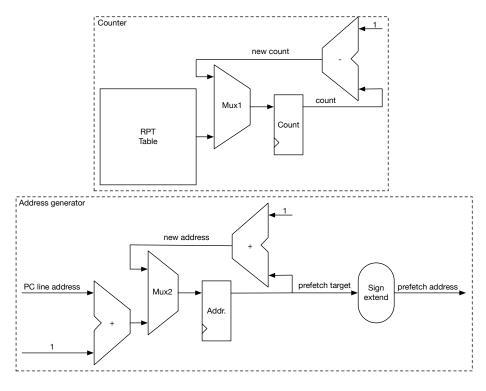

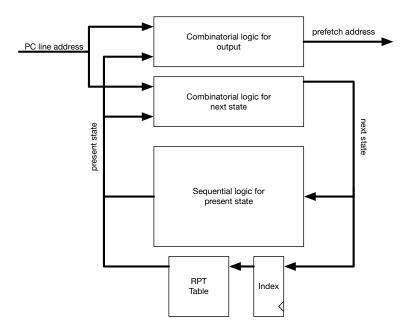

| 4.6<br>4.7<br>4.8                      | State machine diagram of the prefetch controller       Sequential module         Sequential module       If-module                                                                                                              | 54<br>55<br>56                   |

|                                        | Call-module                                                                                                                                                                                                                     | 56<br>57<br>58                   |

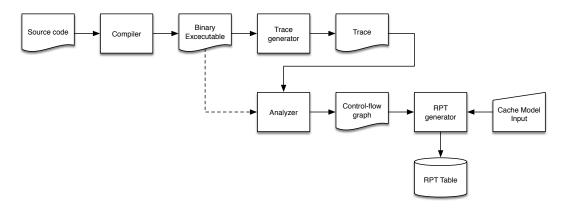

|                                        | Bulk-module       RPT generation process                                                                                                                                                                                        | 60<br>61                         |

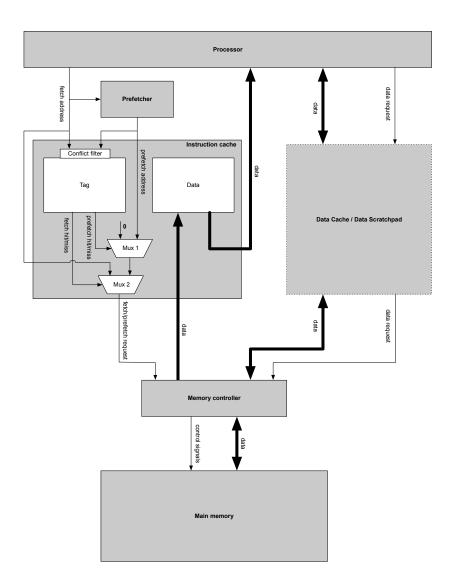

| 5.1<br>5.2                             | Time-predictable memory hierarchy for single-path code                                                                                                                                                                          | 68<br>70                         |

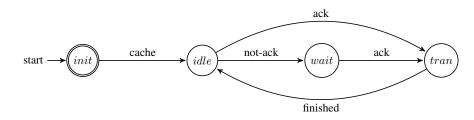

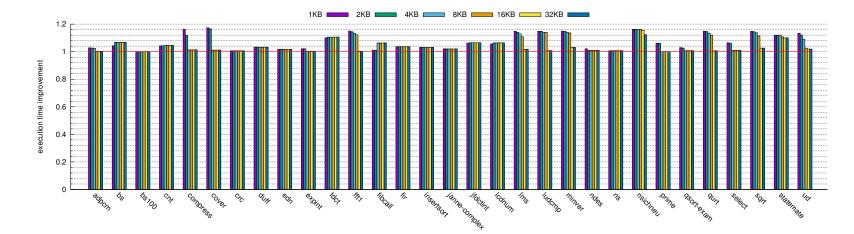

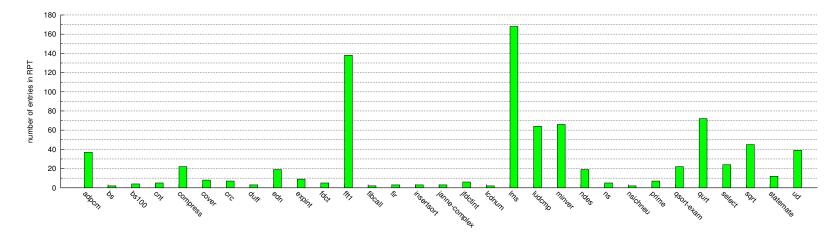

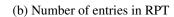

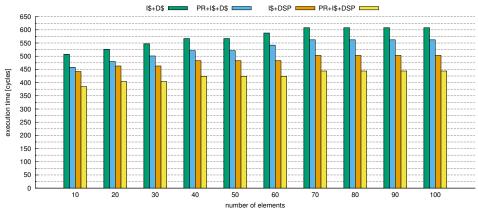

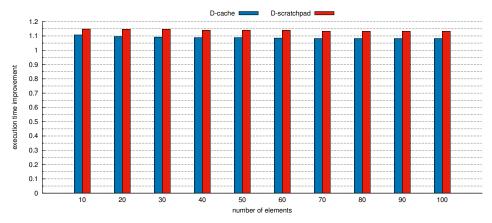

| 6.1<br>6.2<br>6.3<br>6.4               | Representation of the single-path code prefetcher as state-machineState-machine diagram of the cache back-endPerformance evaluation of Mälardalen WCET benchmarksPerformance evaluation for diverse cache organization          | 77<br>80<br>83<br>85             |

6.5 Execution of binary sort algorithm on system with different memory configurations

(I\$ - instruction cache, D\$ - data cache, PR - prefetcher, DSP - data scratchpad) . . 86

## **List of Tables**

| 4.1 | <b>Reference Prediction Table</b> |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 4 | 53 |

|-----|-----------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|----|

|     |                                   |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |    |

#### CHAPTER

## Introduction

In this chapter we introduce embedded systems and describe how these systems deal with timing when they are employed for safety-critical applications. The chapter starts with an introduction on embedded systems and then continues by reasoning about the need for WCET analysis when time is a critical asset of the system. Next, the chapter enumerates the issues that emerge when WCET bounds of the tasks need to be estimated and how these issues can be overcome with the use of single-path approach. In this chapter, we also discuss the main motivation of the thesis for building a time-predictable memory hierarchy which provides predictability and performance improvement for a system that runs single-path code. The list of contributions that has been achieved during this work is discussed as well. At the end, the chapter gives a brief description on the structure of the thesis.

#### **1.1 Introduction to Hard Real-Time Systems**

By definition, any self-contained information processing system that is embedded into an enclosing product is called *embedded system* [74]. The price, size and efficiency that embedded systems have achieved made them the widest spread class of computers, with a range of use from home appliances and multimedia systems to nuclear plants and space mission systems [50].

Embedded systems are composed of a processing core, memory component and interfaces used for communication with the external environment. Usually, embedded systems are hidden from the end user and accessed only through interfaces which are acting as remote controller. The software that runs on embedded systems is called *embedded software*. Compared to general-purpose systems, embedded systems differ in many aspects. General purpose systems are designed to run a wide variety of applications where each one has different performance requirements from the rest, while embedded systems are running a single application or a set of applications related to a single function during their whole lifetime. Such an advantage of knowing in advance the purpose of the system gives embedded system designers the opportunity to build systems that are substantially optimized. Depending on the usage, the optimization

can be on power consumption, cost, reliability, etc. Systems of larger scale can even integrate a few embedded systems within, where each one has a particular function. In some cases they can be interconnected in order to interact with each other, but this is not always required. For instance, the modern car is a case of a system that integrates several embedded systems where each one has a particular task, like one for monitoring and controlling the airbags, one for anti-lock brakes, another one for fuel injections and so forth [62].

In several application domains, embedded systems are required to perform in timely manner. In such a system the correctness of the outputs depends not only on the logical results of the computation, but also on the physical instant at which the results are produced [58]. These systems are called *real-time systems*. The time instants when the results must be produced are called *deadlines*. However, whether the deadlines are met or not is not always crucial. There are embedded systems where the miss of the deadline will affect only the system performance but not the functionality of the system itself. These types of systems are known as *soft real-time* systems. For example, video streaming is a real-time system with soft deadlines, because missing of a few frames will only reduce the quality of service, but the service is still useful. Conversely, there are systems where the miss of a single deadline can lead the whole system to catastrophic failure. These systems are called hard real-time systems. An example of a system with hard timing deadlines is the fly-by-wire controller which is part of the aircraft flying system that moves the aircraft surfaces for achieving the desired flight path [13]. The fly-by-wire controller consists of a set of tasks that are running in a predetermined sequential order. Their purpose is to periodically scan the inputs from the pilot and the surface sensors, to calculate the actual position of the surface parts and, based on these estimations, to release new outputs to the actuators for their new position. Considering that the fly-by-wire controller has a crucial safety function in preventing the aircraft from going outside of its safe operating range, it is important that in such a system each task must respond within a certain timing period that is given in the aircraft specification. Failure to do so can cause the aircraft to go off-course at the best or crash at the worst. Guarantees for task deadlines can be given only if *timing analysis* of the tasks is performed. However, when a task is executed, its execution time can take various values across the range of times due to dependencies on input data and the initial hardware state. For hard realtime systems, validation process has to consider the maximum length of the execution time of that task which is known as *worst case execution time* (WCET), while the analysis that estimates the WCET value is called WCET analysis [120]. The WCET analysis of the task is performed under the assumption that the task is not interrupted during its execution. In this thesis we will consider only the group of real-time systems whose deadline is hard.

#### **1.2** Motivation

Performing WCET analysis on safety-critical embedded systems is a challenging issue, especially for systems that use caches, pipelines, control speculation and out-of-order execution. The chase for better performance makes the presence of these features almost inevitable for the used computer systems, caches aim to bridge the speed gap between processor and main memory, the pipeline has the goal of overlapping the execution of instructions, the branch predictor speculates on the outcome of branch instructions to keep the pipeline full with correct instructions and out-of-order execution minimizes the stall of the pipeline [102]. On the other hand, these features are the main source of complexity when the WCET of the system needs to be assessed. The complexity emerges due to execution-history dependency that these features impose on the execution time of the instructions [49,98]. For instance, the cache can vary the execution time of an instruction from one to hundred of clock cycles, depending if the cache access for that instruction results in a hit or miss [119]. Additionally, these features are also interdependent, which means that the analysis gets even more complex when a timing effect that occurs between these features as a result of interference has to be considered as well [47]. For example, a wrong speculation on a branch outcome will entitle the processor to fetch wrong instructions which also affects the state of the cache. Another example is the interdependency between cache and pipeline, where a cache miss stalls the pipeline and affects the timing of the other ongoing pipelined instructions. Thus, for a software that runs on such architectures, a high-quality WCET estimation can be performed only if the analysis covers all the possible system states that can emerge during the runtime. Such an approach of exploring all the possible hardware states of the system will lead the WCET analysis quickly into an unmanageable state-space explosion.

The state-of-the-art WCET tools avoid the problem of complexity by substituting the real hardware model with an abstracted one [120]. Abstract interpretation is a static program analysis method that executes an abstract version of the program on a set of abstract values [24]. In case of WCET analysis, abstract domain and abstract transition functions are defined to reduce the complexity of hardware modeling and with that to reduce the set of states that need to be analyzed. The abstraction is considered successful if the set of abstract states can represent compactly the real hardware states at any program point. However, abstraction leads to information loss, which in turn results in lots of unclassified model states and with that in a pessimistic computation of the WCET value. This affects the task CPU-time reservation, since pessimistic estimates will lead to poor processor utilization and overly pessimistic results on schedulability tests.

A technique to eliminate the complexity problem of WCET analysis is the use of *single-path conversion* [88]. The approach transforms the conventional code into a code with single execution trace called *single-path code*. This is achieved by serializing all input-dependent alternatives of the code into code with sequential segments. The approach also converts loops with input-data dependent termination conditions into loops with constant iteration counts. Thus, the newly generated code, whose execution is fully independent from the input data, forces the execution to always follow the same sequence of instructions for any set of inputs. The WCET analysis process for such a code becomes trivial since the whole procedure is turned into a simple single execution time measurement. Another advantage of single-path conversion is the property of composability and scalability that the software gains with the use of single-path code has one major drawback because the conversion may generate code which can end up with a quite long execution time, especially if the original code has many input-data dependent control decisions.

The main motivation of this thesis is to present a solution that improves the performance of the system running single-path code. It is well known that over the past decades the speed of processors has been rapidly increased, while the development of main memory was more focused

Figure 1.1: Performance gap between processor and DRAM memory over the years [50]

on increments of the storage density. The speed gap between these two units (Figure 1.1) became one of the major factors in limiting system performance [122]. Although the employment of the cache is crucial in bridging this gap, its presence as part of the memory hierarchy cannot be considered as a complete solution yet. Caches improve the memory performance by holding a copy of code fractions near to the processor. Thus, whenever a fetch request results into cache hit, it will be serviced immediately, without any delay. However, this solution reduces only the frequency of main memory accesses, but not the time that is required for main memory access. If a cache miss occurs, the processor still has to be stalled and wait for the missed instruction to be brought from the main memory into the cache [50]. In such cases, prefetching has been shown to be an effective solution. Its objective is to mask the large latency of memory accesses by bringing memory blocks into caches before they are referenced [104]. The scheme can be implemented as a software or hardware solution and the prefetched blocks can contains instruction or data. However, employment of a prefetcher into the memory hierarchy does not mean success by default. Prefetching requires prediction of the future stream of execution, which is not trivial in most cases. Thus, the presence of a prefetcher as part of the hierarchy can interfere with the normal cache operation by keeping the ports of the cache, the memory bus and the main memory itself busy with useless traffic [111]. In such cases, the prefetcher will do more harm on performance than providing improvements. A full utilization of prefetcher benefits can be achieved only if the prefetch requests are issued at the right moment and have the correct target address. Any deviation from these two parameters will not only underuse the capacity of the prefetcher but also reduce the system performance.

Furthermore, a system that runs single-path code should be composable and compositional by providing stable execution times. To achieve that, the memory hierarchy must force repeatability through all the layers of the hierarchy, which means that the sequence of memory states through the execution of the code should be the same for any iteration of the code. However, this is not trivial to achieve with conventional memory hierarchy solutions. First, not every cache organization guarantees that the sequence of cache states will be repeatable through different iterations, even though the sequence of instructions is the same. Second, the interference that occurs between instruction and data path when main memory is accessed can change the timing of instructions in an unpredictable way. Third, the asynchronism between DRAM refresh and memory access can impose unpredictable timing variation on instruction level. All these occurrences are affecting the execution time of instructions by imposing jitter on the execution time.

#### **1.3** Contribution

The major contribution of this work is a new memory hierarchy that makes systems with singlepath code become useful and competitive for applications with real-time properties. To achieve that, the memory has to provide performance improvements by reducing the execution timing of single-path code as well as predictability on temporal behavior through all layers of the hierarchy. In this thesis, we have build and evaluated a memory design that exploits the pre-runtime knowledge about the execution traces of single-path code to prefetch instructions into the cache before they are required. Such properties enable the prefetcher to behave predictably and work efficiently through the whole runtime of the single-path code without polluting the cache at any moment. To reach the best performance on the whole memory, other levels of the memory needs to be adapted as well. Therefore, we propose a modified cache design that allows regular instruction fetching and prefetching to work in parallel without interference. Moreover, we also have proposed a new organization of the hierarchy in order to eliminate execution jitter and provide stable timing. Such an approach enables the system designer to build a time-predictable system that has better performance and still preserve the properties of simplicity and scalability gained for the single-path code. The contribution in this work is mainly focused on the instruction path of the memory hierarchy with small changes in the data path.

In the following we emphasize the major contributions accomplished with the implementation of the new memory hierarchy:

- Accuracy The calculation of every prefetch target is always accurate, which also eliminates the possibility for cache pollution and useless memory traffic.

- **Redundancy** All issued prefetch requests are sent to cache and not directly to the main memory in order to avoid redundancy to prefetch instructions that are already in the cache.

- Miss penalty time reduction Prefetching is performed in parallel with execution by utilizing the free bus cycles in order to reduce the timing of cache-miss penalties.

- **Miss rate reduction** In cases when loops fit in the cache, the prefetcher continues with filling the cache with more than one cache line without interfering with the loop content. This eliminates the cache misses of the instructions following after the loop exit and reduces the cache miss rate.

- **Cache conflict avoidance** The prefetcher preserves temporal locality of the cache by avoiding to prefetch instructions that are mapped in the actual cache lines accessed by the fetch stage. This is active only when the cache is organized as direct-mapped cache.

- **Optimized reference table** The use of an indexed table for pointing to the next prefetch target eliminates the need to have a fully associative table. This simplifies the hardware and reduces the table access time.

- **Independent from other components** Having a hardware solution makes the prefetcher fully autonomous, without requiring any changes on the CPU itself or the compiler.

- **Repeatability** All layers of the memory hierarchy are organized to provide repeatability of instruction timing through any iteration of the code.

- Stability The execution of the single-path code has the same time for any iteration which means it is jitter free.

#### **1.4** Structure of the Thesis

The thesis has the following structure:

**Chapter 2** - compares the advantages and disadvantages of the single-path code approach with techniques that are nowadays used for WCET tools. The chapter introduces the state-of-the-art techniques for WCET estimation, describes the issues that occur due to complexity when these techniques are employed and then continues with a description of single-path transformation rules and shows how this approach overcomes the problems of complexity.

**Chapter 3** - gives a background on all levels of memory hierarchy by showing memory elements of each level of the hierarchy, how they can be organized and what type of technology is used for their implementation. The chapter starts by describing the concept of hierarchical memory and then explains in detail each component starting from cache, scrachpad and main memory. This chapter also describes locking and prefetching as cache techniques for performance improvement.

**Chapter 4** - presents the time-predictable instruction prefetcher, by enumerating the requirements that a prefetcher should have to be efficient and time-predictable and how these properties are accomplished in the new single-path code prefetcher. The presentation of the time-predictable prefetcher starts with a description of the algorithm and then continues with its architecture. A part of this chapter is also the generation and organization of the table that guides the prefetcher through the execution.

**Chapter 5** - goes through all layers of the memory hierarchy and shows the configuration that each component needs to have in order to achieve repeatability of instruction timing for any iteration of the code and with that stability on code execution timing. This chapter shows also the modifications that are required to be implemented in the cache in order to enable the fetching and prefetching process to be overlapped without interfering each other.

**Chapter 6** - presents hardware implementation algorithms for prefetcher and cache memory, as well as their integration in the Patmos processor. The chapter describes the evaluation process

and the benchmarks that are used for that purpose. At the end, the results of the evaluation are presented.

**Chapter 7** - presents the related work. It starts by describing the state-of-the-art approach for cache analysis and then continues with techniques used to improve predictability of the on-chip memories. Next, time-predictable on-chip memory with prefetcher are also described.

**Chapter 8** - summarizes the thesis with a conclusion and potential future work that can be done in this direction.

# CHAPTER 2

## Worst Case Execution Time Analysis vs. Single-path Conversion

In this chapter, we compare the process of estimating the worst-case execution time (WCET) bound on conventional code and on single-path code. The chapter starts with a brief description of the state-of-the-art strategies that are used nowadays in timing analysis, followed by a list of issues and obstacles that these techniques have when they are employed in systems with modern hardware. The chapter continues with a description of the single-path strategy and how this approach overpasses all these problems. At the end, a summary is given on the advantages and benefits brought by the code with a single execution path when employed in real-time systems.

#### 2.1 Worst-Case Execution Time Analysis

Any structured method or tool that obtains information about the execution time of a code or part of it can be considered for *execution-time analysis* [62]. In general, performing execution-time analysis of a piece code is not possible due to the halting problem. To make the problem tractable, the program is restricted with code that is free of recursive structures and has loops whose number of iterations is boundable in order to guarantee that the program always terminate. [120]. Despite these restrictions, the execution time analysis process is not trivial. Dependency on input data and initial hardware states force the execution to vary through a range of values. The smallest value within that range is called *best-case execution time* (BCET), the largest one *worst-case execution time* (WCET). For a hard real-time system the WCET is the only subject of interest when timing guarantees have to be provided. However, to estimate a precise WCET value, the analysis needs to go through all the possible execution states, which in practice is almost infeasible due to the amount of memory and the computation time that is required for such an approach.

The state-of-the-art WCET analysis tools are designed to overcome this problem by deriving an estimated  $WCET_{est}$  value, which in fact represents a conservative approximation of the real

$WCET_{real}$ . In order to be valid, the estimated  $WCET_{est}$  should be *safe* and *tight* [70]. A WCET bound is considered safe if the estimated value is greater or equal to the real bound  $WCET_{est} \ge WCET_{real}$ . Overestimation guarantees that the  $WCET_{est}$  has covered all the possible WCET cases. For the second requirement, the  $WCET_{est}$  bound is considered tight if the margin of uncertainty  $\varepsilon$  of the estimated value is within an acceptable range  $WCET_{est} \in [WCET_{real} - \varepsilon, WCET_{real} + \varepsilon]$ . For instance, if the  $WCET_{est}$  bound is highly overestimated, it will lead to a system with underutilized resources. Tools that are used nowadays for WCET analysis are mainly divided into three major groups: *measurement-based*, *static analysis* and *hybrid approaches*.

The measurement-based approach is the most common way used in industry. It derives the WCET bound by executing the task on real hardware or a simulator and measuring end-to-end the execution time of the program. The estimation is derived either by augmenting the program with an additional code that would read the hardware timer at predefined points, or through additional hardware that observes the signals of the relevant pins [109]. Since the code consists of many execution paths, it is required for the approach to perform many measurements of the same code but with different input vectors in order to trigger different paths. The outcome from all measurements is compared and the one with the longest execution time is selected for  $WCET_{est}$ . The set of input vectors that are used to trigger different paths can be generated randomly or with the help of an evolutionary algorithm [114]. In practice, the initial input vector is generated randomly or as a set of carefully selected inputs that are supposed to trigger a case with quite long execution time and then through the use of algorithms the input vector evolves to trigger a path with long execution time. The process is repeated until the maximal predefined number of iterations is reached or all available resources are consumed. However, finding an input vector that would trigger the  $WCET_{real}$  is very difficult. To ensure that such a vector has been found, measurements for all possible combinations of input vectors for that program must be performed, which in practice is infeasible. Thus, the values derived with measurement-based approach are always considered to be underestimated compared with the real WCET. This is one of the main disadvantages of the measurement-based WCET approach. The second problem is instrumentation of the code for measurement purposes. The augmented code is useful only during the validation process, but the validation restriction considers the code for valid only if it remains unchanged. This means that the system in use has to use the same code, including the instrumented parts, although they are not required for further use. The usual practice in industry with measurement-based method is to do few measurements, determine the longest measured execution time from that set and then to add a safety margin to that value. However, such a solution is not always safe since in many cases it may generate still an underestimated bound and in some cases it may convert the bound from underestimated to highly overestimated.

The static analysis is the only solution when strong evidence on WCET are required. Unlike the measurement method, static analysis does not rely on the execution of the code, but combines the information extracted from the code with mathematical model of the system architecture to derive the WCET bound [70]. The whole analysis process is divided into three phases [120]: *control-flow analysis, processor-behavior analysis*, and *estimate calculation*.

• **Control-flow analysis** collects information on possible execution paths of the code. Realtime programs by construction have to guarantee termination of the program for any input data. This means that this type of programs have always a finite number of possible execution paths. However, finding the exact set of paths is in general undecidable. Therefore, control-flow analysis defines a superset of paths which is considered as a safe approximation of the real set. On the other hand, the superset should be as narrow as possible in order to have small overestimations. The analysis firstly builds the *control-flow graph*, which reflects the program structure. Next, it derives information on the bound of the loops, functions that are called, dependencies between conditions and so on. The bound on maximal number of iterations that a loop can have is determined through loop bound analysis [34, 48]. To narrow the set of possible paths, and with that to reduce the pessimism of the estimated WCET bound, the analysis tries to identify and exclude infeasi*ble paths.* As infeasible are considered those paths which according to the control-flow graph structure are executable, but not feasible when the semantics of the code and the set of possible input data are taken into account [34]. To increase the accuracy of loop bounds and infeasible paths, the analysis also performs value analysis, which determines the range of possible values that the registers can have at any point in the program. All this flow information can be extracted from the source level of the code or from its executable binary. Extracting information from the source code is easier but not always practical since not all changes that happen during the compile time can be mapped into the graph. On the other hand, extracting information from executable binary is more difficult but the outcome includes all optimization changes which are performed through compiling. Furthermore, flow information can be provided manually by the programmer or through automatic flow analysis. Manually extracted flow information can be error-prone, while the use of automatic approach is not always possible.

**Processor-behavior analysis** determines execution time bounds of instructions or basic blocks on a given architecture. For systems with simple hardware, this is an easy and straightforward process since the execution time of each instruction is static. A problem emerges when the program executes on a processor that has cache, pipeline and branch predictor, where the effects generated from these features impose variability on the execution time of instructions. In such a system, the execution time of a single instruction is dependent on the state of the hardware, while the information about the hardware state at that moment is itself strongly dependent on the history of the previous hardware states. Therefore, for precise timing estimation, the processor-behavior analysis has to consider all the possible hardware states that lead the execution to that instruction [119]. To avoid the problem of state space explosion, most of the hardware analyses employ timing models that are based on abstract interpretation [62]. The benefit of abstraction is that it simplifies the analysis by substituting the real hardware model with a simplified abstract model, which reduces the number of states that need to be considered and the calculation efforts. However, the abstract model can run into a situation where estimation on timing for a particular state cannot be derived. In this case the model uses conservative approximation under the assumption that such an approach is safe to be used. For instance, if the analysis cannot determine if the cache reference of a particular instruction will result into a hit or a miss, then a safe assumption is considered to classify that instruction as miss in any cache context. In contrast to control-flow analysis, which can be performed in source or binary

code, the processor-behavior analysis requires access to binary code, since it analyses the time on instruction level.

**Estimate calculation** is the last stage of static analysis which estimates the WCET upper bound of the whole task, by combining the program flow information derived from control-flow analysis with the outcome from processor-behavior analysis. There are three possible methods to perform the calculation phase: tree-based calculation, path-based calculation and implicit path-enumeration technique [120]. Tree-based (structure-based) estimation generates the WCET bound by performing bottom-up traversal through the syntax tree of the program [9,22]. As it traverses through the tree, the analysis merges the nodes to a single one and at the same time it also estimates the time for that node. All transformation are done in accordance with the rules for tree-based transformations. However, the problem of this approach is that not every control flow can be easily expressed within a syntax tree. The second technique, path-based calculation, estimates the upper bound by representing the possible execution paths of the task explicitly and then search through that set for paths to find the one with longest execution time, which is also considered as the WCET of that task [108]. The approach is straightforward for codes with single loops, but becomes complex when loops are nested. The complexity is also related exponentially with the number of paths that need to be examined, which makes the approach not so suitable for codes that have a large number of paths. The last estimate calculation technique, called IPET, transforms the WCET estimation into an integer linear programing problem where the structure of the program and the execution-flow information are represented in form of constraints [67,92]. The WCET bound of the task is obtained by maximizing the objective function  $WCET = \sum_{n=1}^{N} B_i \times C_i$ , where  $B_i$  is the longest execution time that the basic block i can have and  $C_i$  is the execution frequency of that block. Unlike the previous two methods, IPET is able to handle different types of flow information. The only problem with IPET is that flow information are represented in form of constraints, while the size of complexity of estimation grows with the number of constraints. Even though ILP is not the most suitable technique to estimate the WCET bound it still remains as the most used approach because of its power compared to tree-based and path-based methods.

Hybrid approaches combine measurement with static complementing each other. The goal is to substitute the complex low-level analysis used in static analysis with a simple measurementbased solution. The approach uses firstly the static analysis to construct the model of the program and next it partitions the code into small segments. In most cases the size of the partitioned segments is the size of the basic blocks. When the set of all possible segments is defined, the tool performs measurements by executing the segments on real hardware or in a cycle-accurate simulator. If the segment contains data-input branches, then the input data for complete coverage of that segment should also be given. The measured values are then used as input to static analysis to produce the WCET bound. Although the hybrid approach includes all the possible paths, it still cannot be considered as a solution that derives a safe WCET bound since determining the worst-case initial state for each segment is difficult or even impossible in some cases [120]. The context problem is usually attacked by running more measurements of the same segment with different initial states in order to decrease the uncertainty.

To summarize, all three methods have their pros and cons. Static analysis has in favor the fact that it covers all the possible context dependencies and gives guarantees, and that the estimated WCET bound is always safe. In favor of static analysis is also the use of abstraction, which simplifies complex hardware models and eliminates the need for real code execution. However, abstraction causes loss of information, which is also reflected in the diminished WCET bound accuracy. So far, static analysis still misses a general abstraction model that could be employed on any hardware configuration. Abstracted models, which are used nowadays, are valid only for small set of hardware configurations. Even for these configurations, if the hardware experiences a small change it makes the analysis not valid anymore. Adapting the model for the new hardware configuration is also a difficult process. In contrast to static analysis, the measurement-based approach is much simpler to apply since no timing model for the hardware is needed. However, the main disadvantage of this approach is the scarcity of input vectors that would guarantee WCET bounds. Even if somehow the input vector that triggers the real WCET is found, this does not mean that the same input vector will trigger the WCET of the same program on other hardware platforms [7]. Hybrid analysis on one side tries to simplify the complexity of hardware by replacing the abstract processor analysis with measurements, but on the other side gives less precise WCET estimation by integrating the measured values into the static analysis. The main advantage of this approach is that it requires less effort when a new hardware is used. It still cannot give guarantees on the estimated bound.

#### 2.2 WCET Analysis Issues on Modern Hardware

In theory, the estimation of WCET bounds is a decidable problem, because the software and hardware that are used for real-time systems are by design restricted to have a countable state space. However, in practice this is not the case. The complexity imposed from the software and the hardware of the modern system expands the state space to the scale that is tedious or in some cases even infeasible to be analyzed. The WCET research community tries to diminish this problem by proposing timing models that would derive approximated WCET bounds. The efficiency of these models is strongly related to the accuracy of the estimated WCET bound and the computation effort that is needed to calculate these bounds [56]. Hence, to be acceptable the WCET analysis should provide timing models and analysis methods that are affordable, tractable and derive precise results [121]. Despite the advances that have been made during the last decades in improving the efficiency and the correctness of the models for WCET analysis, there are still issues that the analysis has to deal with. In the following we describe some of these issues that the WCET analysis has to deal with.

On the software level, the analysis faces the issue of complexity when information on dynamic behavior of the code needs to be extracted. Although there are a number of techniques that can derive loop bounds [35, 48, 57] and infeasible paths [46, 110] automatically, they are not always successful. When they fail, flow information needs to be provided manually by the programmer, which is a tedious and error-prone process [55]. The situation gets more aggravated with the low-level analysis. The demand for powerful processing forces the embedded systems to adopt techniques that were developed for general purpose systems like cache, pipeline, branch predictor and out-of-order execution [61]. On the other hand, these features are the main source of complexity when the analysis has to be done and not all of them have adequate timing models that can be used for estimation of the WCET bound [98, 121]. In the following, we describe the current problems that the static analysis has to deal with when features like these are employed on the system.

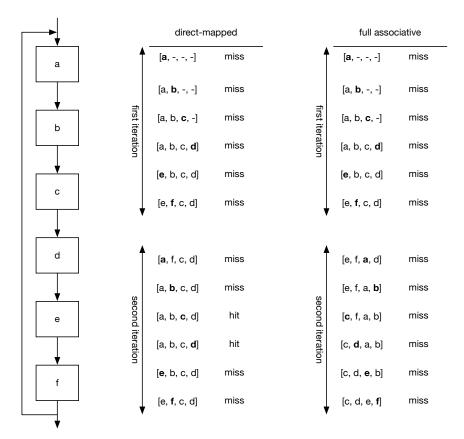

Cache analysis has the goal of classifying each memory access as a hit or miss. Running exhaustive exploration through all the possible states that the cache can have during program execution is not feasible due to the enormous size that the cache state space can have. Abstract interpretation is considered a well established approach that simplifies the complexity of the cache analysis by aggregating states of different paths into a single abstracted state. However, the precision of the results derived from the abstracted models are strongly dependent on the architecture of the cache and its replacement policy [49]. For example, the abstracted model for LRU replacement policy achieves better predictability compared to the FIFO or PLRU policy. since the updates of the abstract states for caches with LRU behave in more regular fashion than those with non-LRU [73]. Cache with non-LRU policies are also more sensitive to the initial states, which means that the abstract model requires a longer sequence of memory accesses to evict all unknown cache states from analysis [94]. The uncertainty of cache analysis gets even higher when subject of analysis are data caches. Before classifying the cache access, cache analysis needs to know in advance the reference address of that memory access. Unlike instructions where each address is often available during the compile stage, the addresses for dynamic data structures can only be known at the run-time. Memory access with unknown address destroy the history trace of the cache states up to that moment and with that also the predictability of the analysis [100]. For some cases, value analysis can be used to reduce the set of possible target addresses which are part of indirect addressing [73]. The same problem remains for unified caches, since the uncertainty on data accesses will destroy the predictability not only for data accesses but also for instructions. All of this shows that the current abstract model used for cache analysis cannot be considered a mature solution yet.

*Pipeline analysis* models the behavior of a program through the processors pipeline. For an ideal pipeline, modeling the transition of instructions would be easy, since the execution time latency of instructions would be equal with the length of the pipeline stage. Unfortunately, with real pipelines the execution suffers from data, control, or structural hazard due to instruction dependencies on data or shared resources [50]. When such hazards occur, the pipeline is stalled until the dependency conflict is solved. However, even if most of the pipeline processors have forwarding techniques implemented, they still are not able to fully eliminate the stall penalty time. Interdependency between pipelined instructions. Instead, the analysis considers all current pipelined instructions collectively in order to identify all potential pipeline stalls that can occur and include them into the timing model. Dependencies within a basic block causes delays to instructions of the other basic blocks which are not immediate successors [33]. Such dependencies are called *long timing effects*. They are the main reason for preventing the pipeline analysis to be performed

on the level of isolated basic blocks.

*Branch prediction analysis* has the purpose to analyze the behavior of the branch predictor. The easiest way to deal with this feature is to disable it or to assume that all branches are mispredicted. However, such an assumption would result in a highly pessimistic bound considering that mispredicted branches can be very expensive for architectures with deep pipelines. Another reason is that the rate of prediction of modern dynamic branch predictors is quite high. Therefore, inclusion of branch-prediction analysis is important when tight WCET bounds are required. The branch-prediction analysis integrates estimated information about branch misses into the global WCET analysis by adding penalty cost for mispredicted branches [23] or by bounding the number of mispredicted branches through ILP constraints as part of IPET approach [66]. The first solution uses tree-based computation and has implementation only for local branch predictor, while the second one is implemented for global dynamic branch predictor and is more precise since it considers not only the number of miss-predicted branches but also the effect of the branch predictor on the cache states. Although the last approach achieves a high precision, its employment can increase the complexity very fast to a level that makes the analysis to become not affordable anymore [14].

Powerful out-of-order processors are suffering from *timing anomalies*. This phenomenon invalidates the intuitive assumption that a local pessimistic assumption will lead to the global WCET. Anomalies can emerge when the processor speculates with execution on wrong direction (*speculation-caused anomalies*), or when a sequence of instructions are scheduled differently on the hardware resources (*scheduling anomalies*) [72]. Speculative execution is used to avoid pipeline stalls caused from branch instructions, but if the speculation is incorrect the processor will prefetch wrong instructions, which will also change the cache content. Changes done from wrong speculation sometimes can cost more to undo than the cost of a cache miss. Hence, the local assumption of a cache miss can lead to a globally shorter time. The second type of anomaly can occur in multi-issue out-of-order processor when a cache hit can take longer than cache miss due to a dependency of instructions and the way how these instructions are allocated to the resources. In addition, it has been demonstrated that timing anomalies can also occur in multi-issue in-order processors [118].

#### 2.3 Single-path Approach

The single-path approach uses a code transformation strategy that converts conventional code with multiple-execution paths to a code that has a single execution trace [88]. The idea behind the strategy is the elimination of all input-data dependences of the code by serializing input-dependent alternatives into sequential code segments. The outcome from this transformation is a new generated code that has preserved the same semantic as the original code, but its execution always follows the same sequence of instructions regardless of the program input values. For a code with such a behavior, the WCET analysis becomes a simple process. To determine the WCET, it is sufficient to run the code and measure the execution time for only one execution.

The whole concept of single-path transformation is based on so called *if-conversion* which converts control dependences of the code to data dependences [4]. This technique was firstly applied only on the body of the most inner loops in order to convert them into non-branching

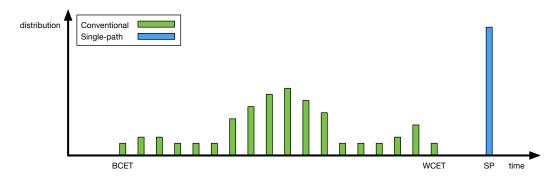

Figure 2.1: Distribution of the execution time for conventional and converted single-path code

code and with that to avoid the stall of the pipeline, especially for processors with deep pipelines. The single-path approach extends this strategy through the whole code by covering all inputdependent control flows, loops and functions of the code. The strategy can be applied on any conventional code whose WCET can be bounded.

To achieve input-data independent execution, the transformation needs to transform all input dependent control flow instructions. Identification of those instructions can be done automatically by data-flow analysis. On the other hand, control flow branches that are input data independent can be preserved as they are or they can also be subject to if-conversion. In both cases the code will be single-path and will have the same semantic. The difference is only in the amount of computation time that is required for their execution. If input independent branches are preserved, then the code will contain mutual alternatives whose patterns of execution will be always the same regardless of the input data. If they are converted it means that the alternatives will be serialized and with that also the execution stream of instructions.

Figure 2.1 shows the distribution of the execution time for conventional and single-path code. While a conventional code has different times for different input data, the single-path converted code of the same program has the same execution time for any input value. However, the benefits to have a jitter-free code comes at the cost of the execution time. As can be seen from the figure, the execution time of single-path code can take much longer than the WCET of conventional one due to its behavior to force the execution through all instructions of the code.

In the following we describe predicated instruction as a requirement that the system should support in order to perform single-path execution, the set of rules that are applied on conventional code for its conversion into a single-path one and the beneficial timing properties that are gained from the conversion.

#### Hardware Requirements for Execution of Single-path Code

The execution of single-path code requires from the hardware to support *predicated instruction* in order to preserve the semantic of the original code. Predicated instructions are instructions whose semantics are controlled by a predicate (guard), which can be implemented through a specific predicate flag or a register in the processor [79]. Instructions whose predicate value is evaluated as "true" are executed normally, while those with "false" predicates are nullified

in order to prevent the processor from modifying its state. Predicates of instructions should be calculated before entering the code segment and the value of the predicate should be kept unchanged through the whole segment. Since the single-path conversion is spread through the entire code, the compiler has to take into account interdependencies of the predicates within nested code structures. In such cases the predicate of the outer structures is passed to the inner one and then using the boolean algebra they are combined with the inner predicates. For instance, if a piece of code has two nested loops where  $L_1$  is the outer and  $L_2$  is the inner loop, and if their exit conditions are associated with predicates  $p_1$  and  $p_2$  then the body in the inner loop is also associated with the outcome of  $p_1 \wedge p_2$ .

#### **Single-path Conversion Rules**

Single-path conversion is performed on the executable binary after optimization transformations have been conducted by compiler [84]. However, to be more lucid with the concept of the single-path transformation, we demonstrate the transformation rules as they would have been performed in the source-level of the code. The rules are applied on those parts of the code which generate variability in execution time. Code structures that are transformed are input-dependent conditional branches, loops and function calls [90].

Input-dependent branches of *if* or *case* structures are conditional statements whose semantic consists of two or more mutually exclusive alternatives where only one of them can be executed. The decision about which particular alternative will be executed depends on the outcome of the branch condition that precedes those alternatives. The single-path conversion serializes all the alternatives of the branch into sequential code and with that forces the execution to pass through the whole branch [87]. The responsibility of predicates is to control which instructions can do register-state changes and which will act as null. In cases when conversion is nested, the predicates of all nested conditions are combined into a conditional assignment. Figure 2.2 illustrates an example on how the if-else conversion eliminates the input data dependent branch instruction. Variant (*a*) is a conventional code with an *if* branch instruction, where only one statement is executed. The decision on which one will be executed depends on the outcome of the condition *cond*. Variant (*b*) executes both statements, but only one of them will change the hardware states and this depends on the value of the predicate *pred*.

|     | if (cond) goto L2       | pred<-cond                   |

|-----|-------------------------|------------------------------|

| L1: | statement_1             | (!pred) statement_1          |

|     | goto L3                 | ( pred) statement_2          |

| L2: | statement_2             |                              |

| L3: |                         |                              |

|     | (a) Branch instruction. | (b) Predicated instructions. |

Figure 2.2: Conversion of branch code into serial code with predicated instructions.

A loop is a code structure that is continually repeated until a certain exit condition has been reached. If the exit condition is input dependent then the loop can exit after any iteration, depend-

ing on the current program input. Such a exit condition generates variability in execution time of the loop for different loop iterations. The single-path approach transforms input-dependent loops into loops with constant iteration count where each iteration has a constant execution time [86]. The conversion sets the iteration count of the new generated loop to the value of the loop bound derived form the original loop, while the exit condition of the original loop is used to calculate the value of the predicate related to the body of the new loop. Figure 2.3 illustrates the transformation of a *while* loop. As can be seen from the figure, the loop is transformed into a *for* loop structure with constant iteration count. The body of the new loop includes predicated instructions. The predicate is responsible in preventing hardware states to be changed after the exit condition from the original loop has been satisfied. The value of the predicate is set at the beginning, before entering the loop, and then is controlled with *statement\_cond*. Once this condition is fulfilled, the value of predicate is changed to *false*. The loop will iterate until it reaches *max*. Thus, although the number of loop iterations is constant on each invocation, the semantic of the transformed loop will still be the same as the original one.

|                        | pred<-cond                             |

|------------------------|----------------------------------------|

| while (cond) do        | for 1 to max                           |

| statement_1            | (pred) statement_1                     |

| statement_2            | (pred) statement_2                     |

|                        |                                        |

| statement_cond         | (pred) pred<-statement_cond            |

| (a) Conventional loop. | (b) Loop with predicated instructions. |

Figure 2.3: Conversion of conventional loop into a loop with stable time.

A function is a reusable block of code that is executed whenever it is called. Input-dependent calls invoke the function in dependence to the program input. Single-path conversion transforms the code in a way that each function of the code is called unconditionally, and with that also a predicate related to the function call is passed to the called function. Hence, if the predicate is evaluated as *false*, even though the execution will pass to the function, there will be no changes in the hardware states. The function predicate that is passed to the function represents the initial precondition for all statements within the function.

#### **Predictable Properties of Single-path Code**

Single-path converted code, except that it is free of input data-dependent control condition, it also inherits beneficial properties from transformation that help the process of hard real-time system design to be simpler and easier. In the following we enumerate the main properties that the code gains after its transformation [21,90,91]:

• *Simplicity* - One of the most important properties of single-path code is its simplicity. By making the execution independent from input data, the single-path conversion also simplifies the process of WCET analysis. Instead of performing complex WCET static analysis, for single-path code it is sufficient to do a single end-to-end measurement of the execution time of the code and with that to determine the exact WCET value. The measured WCET is safe and valid for any context of the code.

- *Stability* From a software point of view, single-path code has no variability in execution time for any input data. Such a property eliminates the possibility for overallocation of the hardware resources. The only source for execution-jitter in a system with single-path code can emerge from hardware features due to their temporal behavior that are based on execution history. However, in a well designed system this execution-jitter can also be eliminated.

- *Composability* Having a single execution trace allows the programmer to add or remove segments from the code without affecting the timing of the other code segments. Hence, each software component can be developed autonomously with respect to the timing and then added to the main code. This makes the single-path converted code timing composable.

- *Compositionality* The timing of code composites can be derived from the timing of the components with a simple formula. This allows the construction of the system to be performed hierarchically by keeping the design and development of complex composites to be simple. In such an approach the timing of the whole system can be calculated straightforward from its components.

- *Predictability* Although there is no precise definition on what predictability is, the proposed ones [44,56] classify the single-path code as time-predictable since the timing analysis for such a code calculates the WCET with full accuracy.

All these properties support the design process of a real-time system. The use of hierarchical development allows the designer to dismantle the complexity of the whole system from system level to the level of sub-component and then treat each sub-component as a smaller sub-problem. After building all sub-components, their integration into a whole system is performed. This step is quite simple due to composable and compositional properties that the system components have.

The only drawback for single-path code is that transformation can produce codes with long execution time, since every alternative of the code is executed. This is especially pressing if the code consists of lots of input-data dependent control flows.

#### 2.4 Chapter Summary

Complexity in timing analysis emerges as the result of highly-integrated analyses that state-ofthe-art analysis approaches are using. The analyses simultaneously keep track of all hardware features whose performance enhancement are based on the program execution history. Each of these features increases drastically the hardware state space that needs to be analyzed. Additionally, most of these features are also highly interdependent and this effect on timing analysis must be included in WCET analysis as well. Abstraction is proposed as an option to mitigate the complexity of the analysis by reducing the state space. However, the approach provides acceptable solution only for a small set of features, while for the rest an appropriate model still needs to be found.

With the single-path approach, the process of timing analysis gets simple and easy. The strategy eliminates the complexity of the analysis by generating code that has a single execution path. In a well designed system, the timing of instructions through all hardware features is the same whenever it is executed, since the state transitions of the hardware features are always the same and with that also the path to reach that instruction. Hence, an end-to-end measurement of the execution is sufficient for WCET estimation. Furthermore, the single-path property of stable time gives the opportunity for building composable systems whose timing can be easily derived.

# CHAPTER 3

### **Background on Memory Hierarchy**

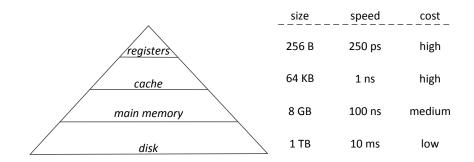

Since the invention of the microprocessor the density of transistors per chip area has been doubling roughly every year. Whereas microprocessors have used this advantage to increase the rate of executed instructions, memory technology was focused on increasing the capacity. Such divergent development has led to a wide performance gap between processor and memory. To overcome this issue, the concept of *memory hierarchy* has been proposed. A good understanding of the memory hierarchy architecture and the memory technologies is necessary for designing and analyzing real-time systems.

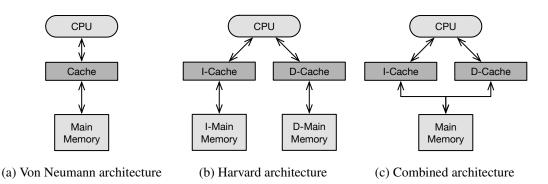

In this chapter we describe the architectural concept of the memory hierarchy, memory hierarchy components and the technologies that are used in nowadays systems to bridge the speed gap between processor and main memory.

#### **3.1** The Concept of Memory Hierarchy