# Real-Time Monitoring for Correctness and Robustness

## DISSERTATION

zur Erlangung des akademischen Grades

## Doktor der Technischen Wissenschaften

eingereicht von

Stefan Jakšić, MSc

Matrikelnummer 01429719

| an der Fakultät für Informatik                                        |                       |                          |

|-----------------------------------------------------------------------|-----------------------|--------------------------|

| der Technischen Universität Wien                                      |                       |                          |

| Betreuung: Univ.Prof Radu Grosu,<br>Zweitbetreuung: Dr. Dejan Ničkovi |                       |                          |

| Diese Dissertation haben begutac                                      | htet:                 |                          |

|                                                                       |                       |                          |

|                                                                       |                       |                          |

|                                                                       | Prof. Saddek Bensalem | Prof. Jyotirmoy Deshmukh |

|                                                                       |                       |                          |

| Wien, 20. September 2018                                              |                       |                          |

|                                                                       |                       | Stefan Jakšić            |

|                                                                       |                       |                          |

# Real-Time Monitoring for Correctness and Robustness

## DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

## Doktor der Technischen Wissenschaften

by

Stefan Jakšić, MSc

Registration Number 01429719

| to the Faculty of Informatics                                          |                       |                          |

|------------------------------------------------------------------------|-----------------------|--------------------------|

| at the TU Wien                                                         |                       |                          |

| Advisor: Univ.Prof Radu Grosu, Dr<br>Second advisor: Dr. Dejan Ničkovi |                       |                          |

| The dissertation has been reviewe                                      | d by:                 |                          |

| -                                                                      |                       |                          |

|                                                                        | Prof. Saddek Bensalem | Prof. Jyotirmoy Deshmukh |

| Vienna, 20 <sup>th</sup> September, 2018                               |                       |                          |

|                                                                        |                       | Stefan Jakšić            |

# Erklärung zur Verfassung der Arbeit

| Stefan Jakšić | s, MSc |      |      |

|---------------|--------|------|------|

| Barichgasse   | 35/7,  | 1030 | Wien |

| Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quel- |

|------------------------------------------------------------------------------------------------------|

| len und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit - einschließlich  |

| Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder            |

| dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich        |

| gemacht habe.                                                                                        |

| Wien, 20. September 2018 |               |

|--------------------------|---------------|

|                          | Stefan Jakšić |

## Acknowledgements

This thesis represents the accomplishements of the research conducted in order to obtain PhD degree at TU Wien. I am very grateful that I had the chance to work with TU Wien and Austrian Institute of Technology (AIT) for three and a half years.

I would like to thank my supervisor professor Radu Grosu and co-supervisor Dr. Dejan Ničković for their mentoring and support. During my studies, I frequently collaborated with professor Ezio Bartocci, Dr. Konstantin Selyunin and Dr. Thang Nguyen. I would like to thank them all for the fruitful collaboration we had.

Two most important figures in my life encouraged me along the way. I want to thank my mother Borislava and my wife Ivana for inspiring me and giving me the strength to complete this challenging journey. Thank you for always believing in me. My entire family was always there for me, and I cannot thank them enough. However, I must specifically acknowledge my cousin Nikola Jeličić for being a true friend in need.

I would also like to thank the professors from the Faculty of Electrical Engineering, University of Belgrade, who supported my idea to pursue a PhD: professor Boško Nikolić, professor Zaharije Radivojević and professor Slavko Gajin. At AIT I enjoyed a friendly working environment for which I want to thank my colleagues: Niveditha Manjunath, Cristinel Mateis, Thorsten Tarrach, Andreas Fellner, Willibald Krenn, Stefan Zelenbaba, Mario Klima and Dieter Holzer.

Last, but definitely not the least, are all the friends that shared so many important moments with me: Đorđe Žegarac, Vuk Miljković, Filip Dojčinović, Veljko Stamenković, Adam Miladinović, Marko Janković, Vuk Batanović, Đorđe Grozdić, Mihailo and Nenad Ivanović, Andrija Bogojević, Jelena Vukmirović, Davor Ostojić, Srđan Rajković, Nikola Zečević and Rohit Dureja.

The research was funded by a national Austrian grant from FFG (Österreichische Forschungsförderungsgesellschaft) under the program IKT der Zukunft, for which I am grateful.

## Kurzfassung

Ziel dieser Dissertation ist es, ein Framework für die Echtzeitüberwachung von Designs industrieller Größenordnungen zu entwickeln, um die Korrektheit und Robustheit zur Laufzeit zu überwachen. Wir glauben, dass die Laufzeitverifikation, die auf temporaler Logik basiert, eine rigorose, systematische und effiziente Lösung für die Herausforderungen der Echtzeitüberwachung bietet.

Um unsere Monitore in moderne Hardware-in-the-Loop (HiL) - Prüfstände zu integrieren, präsentieren wir einen Algorithmus zur Synthese qualitativer Monitore in Hardware aus Sicherheitseigenschaften, welche in Signal Temporal Logic (STL) ausgedrückt werden. Indem wir den Monitor aus grundlegenden temporalen Testern zusammensetzen, können wir die Berechnung des Korrektheitsurteils parallelisieren. Somit minimieren wir die Rechenverzögerung und erhalten reaktionsfähige Monitore, die Echtzeit-Korrektheitsbeurteilungen liefern.

Binäre Korrektheitsurteile sind möglicherweise nicht ausreichend für Eigenschaften, die Verhaltensweisen mit reellen Werten bewerten. Die Korrektheitsrelation kann durch ein metrikbasiertes quantitatives Urteil ersetzt werden, welches ein feineres Maß dafür liefert, wie robust ein Verhalten einer Spezifikation entspricht. In der Regel wird die Entwicklung solcher Urteile von einer bestimmten Art von Anforderungen und Verhaltensweisen bestimmt. Dies führte zu einer Fülle von Urteilen, jedes mit seiner eigenen Definition und seinem eigenen Algorithmus. Unser Ziel ist es, einen einheitlichen Ansatz zur präzisen Robustheitsüberwachung zu definieren, indem wir einen regulären Formalismus für reguläre Spezifikationen über große, geordnete Alphabete verwenden: symbolische Automaten (SA). Durch die Verwendung von algebraisch definierten Gewichten in SAs erhalten wir einen generischen Algorithmus zur Überwachung sowohl der Korrektheit als auch der Robustheit. Es liefert Urteile, die an die gewünschte Klasse von Verhaltensweisen angepasst werden können, indem einfach die entsprechenden algebraischen Operationen ausgewählt werden. Da der Algorithmus auf dynamischer Programmierung basiert, berechnet er Urteile in Echtzeit und ermöglicht eine direkte Implementierung in Hardware.

Ein typisches CPS nutzt digitale Verarbeitungseinheiten, um Prozesse in einer physischen Umgebung zu kontrollieren. Während der Ausführung zeigt ein CPS ein komplexes Verhalten und generiert Ablaufprotokolle. Um die Konformität von CPS-Ablaufprotokollen mit der Spezifikation zu bewerten, müssen wir die Diskrepanzen im Wert- und Zeitbereich berücksichtigen. Um Einflüsse aus beiden Domänen angemessen darzustellen, definieren wir einen Robustheitsgrad basierend auf Weighted Edit Distance (WED). Wir demonstrieren einen Echtzeitalgorithmus für

die Berechnung des Robustheitsgrads von Ablaufprotokollen eines seriellen Protokolls SENT, das aus der Automobilindustrie stammt.

Wir führen eine große Fallstudie durch, um die Vorteile der Verwendung von Laufzeitmonitoren in einem industriellen Umfeld zu bewerten und die Wiederverwendung von Monitoren auf verschiedenen Abstraktionsebenen und Produktdesignphasen zu fördern. Um die Monitore auf eine Klasse von asynchronen, seriellen Protokollen anzuwenden, die häufig in der Industrie verwendet werden, rüsten wir sie mit einem Verfahren zur Regenerierung nach Fehlern und Protokollierung aus. Die Fähigkeit zur Selbstregenerierung ermöglicht die Überwachung langer Datenströme auch nach mehreren Anforderungsverletzungen.

## **Abstract**

The objective of this thesis is to develop a framework for real-time monitoring of Cyber-Physical System (CPS) designs for correctness and robustness and to offer verification methods applicable to real-scale industrial designs. We believe that runtime verification based on temporal logic provides a rigorous, systematic and efficient solution to the challenge of real-time monitoring.

In order to integrate our monitors with modern Hardware-in-the-Loop (HiL) testbenches, we provide an algorithm for synthesizing qualitative monitors in hardware from safety properties expressed in Signal Temporal Logic (STL). By composing the monitor from basic temporal testers, we are able to parallelize the computation of the satisfaction verdict. Thus, we minimize computational delay and obtain responsive monitors which provide real-time correctness verdicts.

Binary satisfaction verdicts may not be sufficient for properties evaluated against real-valued behaviors. The satisfaction relation can be replaced by a metric-based quantitative verdict which gives a finer measure of how *robustly* a behavior satisfies a specification. Typically, the development of such verdicts is driven by a specific type of requirements and behaviors. This resulted in a plethora of verdicts, each with its own definition and algorithm. We aim to define a uniform approach to precise robustness monitoring, by leveraging a common formalism for regular specifications over large ordered alphabets: symbolic automata (SA). By introducing algebraically-defined weights into SA, we obtain a generic algorithm for monitoring both correctness and robustness. It provides verdicts which can be adapted to the desired class of behaviors simply by selecting the appropriate set of algebraic operations. Since the algorithm is based on dynamic programming it computes verdicts in real-time and admits direct hardware implementation.

A typical CPS exploits digital processing units to control processes in physical environment. During the execution, a CPS exhibits complex behavior and generates execution traces. For evaluating conformance of CPS traces with the specification, we must consider trace discrepancies in value and time domain. In order to appropriately represent influences from both domains we define a robustness degree based on Weighted Edit Distance (WED). We demonstrate a real-time algorithm for computing WED-based robustness degree of traces of a serial protocol SENT, taken from the automotive domain.

We conduct a large case study to assess benefits of using runtime monitors in an industrial setting and promote monitor reuse on different abstraction levels and product design phases. In order to apply the monitors to a class of asynchronous serial protocols, frequently used in the industry, we equip them with a procedure for error recovery and logging. The ability to self-recover allows to continue monitoring long data streams even after multiple requirement violations occur.

## **Contents**

xiii

| Kı | urzfas  | ssung         |                                      | ix    |

|----|---------|---------------|--------------------------------------|-------|

| A۱ | bstrac  | et            |                                      | xi    |

| Co | ontent  | ts            |                                      | xiii  |

| Li | st of I | Figures       |                                      | xvii  |

| Li | st of T | <b>Fables</b> |                                      | xxi   |

| Li | st of A | Algorith      | nms                                  | xxiii |

| Tł | nesis I | Publicat      | ions                                 | XXV   |

| 1  | Intr    | oductio       | n                                    | 1     |

|    | 1.1     | Exhaus        | stive Verification Methods           | 2     |

|    |         | 1.1.1         | Model Checking                       | 2     |

|    |         | 1.1.2         | Verification of Hybrid Systems       | 3     |

|    | 1.2     | System        | natic Testing                        | 3     |

|    |         | 1.2.1         | Coverage Driven Verification         |       |

|    |         | 1.2.2         | Falsification Testing                | 5     |

|    | 1.3     | Runtin        | ne Verification                      | 5     |

|    |         | 1.3.1         | Assertion-Based Verification         | 6     |

|    | 1.4     | Motiva        | ation                                | 7     |

|    |         | 1.4.1         | Emerging Verification Challenges     | 8     |

|    |         | 1.4.2         | Hardware-Accelerated Verification    | 8     |

|    |         | 1.4.3         | An Abundance of Quantitative Metrics | 10    |

|    |         | 1.4.4         | Beyond Runtime Verification          | 10    |

|    |         | 1.4.5         | Fostering RV Methods in the Industry | 11    |

|    | 1.5     | Contril       | butions                              |       |

|    |         | 1.5.1         | Hardware Correctness Monitors        | 12    |

|    |         | 1.5.2         | Monitors with Recovery               | 12    |

|    |         | 1.5.3         | Unification of RV Approaches for CPS | 12    |

|    |         | 1.5.4         | Novel Quantitative Semantics for STL | 13    |

|    |         |               |                                      |       |

|            | 1.6                                     | 1.5.5<br>Structu                                                                                                   | Monitoring for Automotive Applications                                                                                                                                                                                                                                                                                                                                                                                                               | 14<br>14                                                                                      |

|------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 2          | State                                   | e of the .                                                                                                         | Art                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17                                                                                            |

|            | 2.1                                     |                                                                                                                    | Work on Correctness Monitors                                                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                                                            |

|            |                                         | 2.1.1                                                                                                              | Relevant Case Studies                                                                                                                                                                                                                                                                                                                                                                                                                                | 18                                                                                            |

|            | 2.2                                     | Related                                                                                                            | Work on Robustness Monitors                                                                                                                                                                                                                                                                                                                                                                                                                          | 19                                                                                            |

|            |                                         | 2.2.1                                                                                                              | Quantitative Semantics for Temporal Logic                                                                                                                                                                                                                                                                                                                                                                                                            | 19                                                                                            |

|            |                                         | 2.2.2                                                                                                              | Edit Distance                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20                                                                                            |

|            | 2.3                                     | Related                                                                                                            | l Work on Automata-Based RV                                                                                                                                                                                                                                                                                                                                                                                                                          | 21                                                                                            |

| 3          | Sign                                    | als and                                                                                                            | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                                                            |

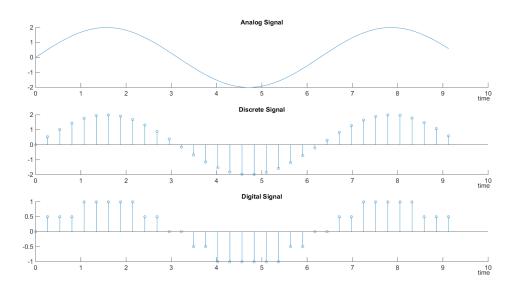

|            | 3.1                                     | Signals                                                                                                            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23                                                                                            |

|            |                                         | 3.1.1                                                                                                              | Sampling and Quantization                                                                                                                                                                                                                                                                                                                                                                                                                            | 23                                                                                            |

|            | 3.2                                     | Specific                                                                                                           | cation Languages                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25                                                                                            |

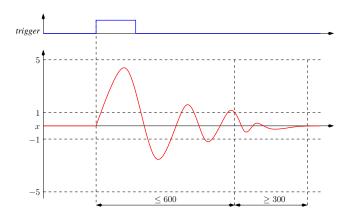

|            |                                         | 3.2.1                                                                                                              | Signal Temporal Logic                                                                                                                                                                                                                                                                                                                                                                                                                                | 25                                                                                            |

|            |                                         | 3.2.2                                                                                                              | Derived STL Operators                                                                                                                                                                                                                                                                                                                                                                                                                                | 26                                                                                            |

|            |                                         | 3.2.3                                                                                                              | Rewriting Rules for STL                                                                                                                                                                                                                                                                                                                                                                                                                              | 27                                                                                            |

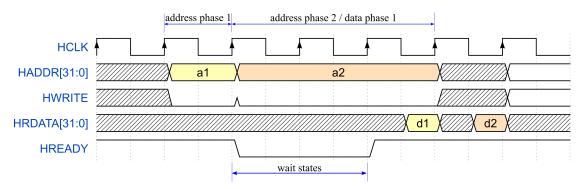

|            |                                         | 3.2.4                                                                                                              | An AHB Read Transfer in STL                                                                                                                                                                                                                                                                                                                                                                                                                          | 28                                                                                            |

|            |                                         | 3.2.5                                                                                                              | Timed Regular Expressions                                                                                                                                                                                                                                                                                                                                                                                                                            | 30                                                                                            |

|            |                                         | 3.2.6                                                                                                              | An AHB Read Transfer in TRE                                                                                                                                                                                                                                                                                                                                                                                                                          | 32                                                                                            |

|            |                                         | 3.2.7                                                                                                              | Usability of STL and TRE for different types of requirements                                                                                                                                                                                                                                                                                                                                                                                         | 33                                                                                            |

|            |                                         |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               |

| 4          | Auto                                    | mata                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35                                                                                            |

| 4          | <b>Aut</b> o 4.1                        |                                                                                                                    | ites                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>35</b> 35                                                                                  |

| 4          |                                         | Predica                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               |

| 4          | 4.1                                     | Predica<br>Weight                                                                                                  | ed Symbolic Automata                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35                                                                                            |

| 4          | 4.1<br>4.2                              | Predica<br>Weight                                                                                                  | ed Symbolic Automata                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35<br>36                                                                                      |

| 4          | 4.1<br>4.2                              | Predica<br>Weight<br>Algebra<br>4.3.1                                                                              | ed Symbolic Automata                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35<br>36<br>39                                                                                |

| 4          | 4.1<br>4.2<br>4.3                       | Predica<br>Weight<br>Algebra<br>4.3.1                                                                              | ed Symbolic Automata                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35<br>36<br>39<br>40                                                                          |

| 4          | 4.1<br>4.2<br>4.3                       | Predica<br>Weight<br>Algebra<br>4.3.1<br>Tempor                                                                    | ed Symbolic Automata                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35<br>36<br>39<br>40<br>41                                                                    |

| 4          | 4.1<br>4.2<br>4.3                       | Predica<br>Weight<br>Algebra<br>4.3.1<br>Tempor<br>4.4.1                                                           | ed Symbolic Automata                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35<br>36<br>39<br>40<br>41<br>41                                                              |

| 4          | 4.1<br>4.2<br>4.3                       | Predica<br>Weight<br>Algebra<br>4.3.1<br>Tempor<br>4.4.1<br>4.4.2                                                  | red Symbolic Automata aic Structures  Metric Space and Distance ral Testers  Formal Definition  Basic Temporal Testers for Past Time STL                                                                                                                                                                                                                                                                                                             | 35<br>36<br>39<br>40<br>41<br>41<br>44                                                        |

| <b>4 5</b> | 4.1<br>4.2<br>4.3<br>4.4                | Predica<br>Weight<br>Algebra<br>4.3.1<br>Tempor<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4                                | ed Symbolic Automata aic Structures  Metric Space and Distance ral Testers  Formal Definition  Basic Temporal Testers for Past Time STL  Basic Temporal Testers for Future Time STL                                                                                                                                                                                                                                                                  | 35<br>36<br>39<br>40<br>41<br>41<br>44<br>47                                                  |

|            | 4.1<br>4.2<br>4.3<br>4.4                | Predica<br>Weight<br>Algebra<br>4.3.1<br>Tempor<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4                                | ed Symbolic Automata aic Structures  Metric Space and Distance ral Testers  Formal Definition  Basic Temporal Testers for Past Time STL  Basic Temporal Testers for Future Time STL  From Temporal Testers to Acceptors                                                                                                                                                                                                                              | 35<br>36<br>39<br>40<br>41<br>41<br>44<br>47<br>49                                            |

|            | 4.1<br>4.2<br>4.3<br>4.4                | Predica<br>Weight<br>Algebra<br>4.3.1<br>Tempor<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4                                | ed Symbolic Automata aic Structures  Metric Space and Distance ral Testers  Formal Definition  Basic Temporal Testers for Past Time STL  Basic Temporal Testers for Future Time STL  From Temporal Testers to Acceptors  Monitors in Hardware                                                                                                                                                                                                        | 35<br>36<br>39<br>40<br>41<br>41<br>44<br>47<br>49                                            |

|            | 4.1<br>4.2<br>4.3<br>4.4                | Predica<br>Weight<br>Algebra<br>4.3.1<br>Tempor<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>rectness<br>Hardwa          | ed Symbolic Automata aic Structures  Metric Space and Distance ral Testers  Formal Definition  Basic Temporal Testers for Past Time STL  Basic Temporal Testers for Future Time STL  From Temporal Testers to Acceptors  Monitors in Hardware are Monitor Synthesis                                                                                                                                                                                  | 35<br>36<br>39<br>40<br>41<br>41<br>44<br>47<br>49<br><b>51</b><br>52                         |

|            | 4.1<br>4.2<br>4.3<br>4.4                | Predica<br>Weight<br>Algebra<br>4.3.1<br>Tempor<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>Pectness<br>Hardwa<br>5.1.1 | ded Symbolic Automata aic Structures  Metric Space and Distance ral Testers  Formal Definition  Basic Temporal Testers for Past Time STL  Basic Temporal Testers for Future Time STL  From Temporal Testers to Acceptors  Monitors in Hardware are Monitor Synthesis  Monitoring Past-Time STL Specifications                                                                                                                                        | 35<br>36<br>39<br>40<br>41<br>41<br>44<br>47<br>49<br><b>51</b><br>52<br>53                   |

|            | 4.1<br>4.2<br>4.3<br>4.4                | Predica Weight Algebra 4.3.1 Tempor 4.4.1 4.4.2 4.4.3 4.4.4  Pectness Hardwa 5.1.1 5.1.2 5.1.3                     | ed Symbolic Automata aic Structures  Metric Space and Distance ral Testers  Formal Definition  Basic Temporal Testers for Past Time STL  Basic Temporal Testers for Future Time STL  From Temporal Testers to Acceptors  Monitors in Hardware are Monitor Synthesis  Monitoring Past-Time STL Specifications  From Bounded Future to Past STL Specifications                                                                                         | 35<br>36<br>39<br>40<br>41<br>41<br>44<br>47<br>49<br><b>51</b><br>52<br>53<br>56             |

|            | 4.1<br>4.2<br>4.3<br>4.4<br>Corr<br>5.1 | Predica Weight Algebra 4.3.1 Tempor 4.4.1 4.4.2 4.4.3 4.4.4  Pectness Hardwa 5.1.1 5.1.2 5.1.3                     | ded Symbolic Automata aic Structures  Metric Space and Distance ral Testers  Formal Definition  Basic Temporal Testers for Past Time STL  Basic Temporal Testers for Future Time STL  From Temporal Testers to Acceptors  Monitors in Hardware are Monitor Synthesis  Monitoring Past-Time STL Specifications  From Bounded Future to Past STL Specifications  Correctness Monitors from TRE specifications                                          | 35<br>36<br>39<br>40<br>41<br>41<br>44<br>47<br>49<br><b>51</b><br>52<br>53<br>56<br>58       |

|            | 4.1<br>4.2<br>4.3<br>4.4<br>Corr<br>5.1 | Predica Weight Algebra 4.3.1 Tempor 4.4.1 4.4.2 4.4.3 4.4.4  rectness Hardwa 5.1.1 5.1.2 5.1.3 Hardwa              | ded Symbolic Automata aic Structures  Metric Space and Distance ral Testers  Formal Definition  Basic Temporal Testers for Past Time STL  Basic Temporal Testers for Future Time STL  From Temporal Testers to Acceptors  Monitors in Hardware are Monitor Synthesis  Monitoring Past-Time STL Specifications  From Bounded Future to Past STL Specifications  Correctness Monitors from TRE specifications are Implementation                       | 35<br>36<br>39<br>40<br>41<br>41<br>44<br>47<br>49<br><b>51</b><br>52<br>53<br>56<br>58       |

|            | 4.1<br>4.2<br>4.3<br>4.4<br>Corr<br>5.1 | Predica Weight Algebra 4.3.1 Tempor 4.4.1 4.4.2 4.4.3 4.4.4  rectness Hardwa 5.1.1 5.1.2 5.1.3 Hardwa 5.2.1        | ded Symbolic Automata aic Structures  Metric Space and Distance ral Testers  Formal Definition  Basic Temporal Testers for Past Time STL  Basic Temporal Testers for Future Time STL  From Temporal Testers to Acceptors  Monitors in Hardware are Monitor Synthesis  Monitoring Past-Time STL Specifications From Bounded Future to Past STL Specifications  Correctness Monitors from TRE specifications are Implementation  Implementation Phases | 35<br>36<br>39<br>40<br>41<br>41<br>44<br>47<br>49<br><b>51</b><br>52<br>53<br>56<br>58<br>58 |

|   |      | 5.3.1     | Mixed Signal Bounded Stabilization                           | 63  |

|---|------|-----------|--------------------------------------------------------------|-----|

|   |      | 5.3.2     | Serial Peripheral Interface                                  | 64  |

| 6 | Alge | ebraic A  | Approach to Runtime Verification                             | 67  |

|   | 6.1  | Algebi    | raic Approach to Distance                                    | 68  |

|   | 6.2  |           | raic Monitors for Correctness and Robustness                 | 70  |

|   |      | 6.2.1     | From Specifications to Weighted Symbolic Automata            | 70  |

|   |      | 6.2.2     | Valuation-Predicate Distance Computation                     | 71  |

|   |      | 6.2.3     | Trace Value Computation                                      | 73  |

|   |      | 6.2.4     | Translation Size and Algorithm Complexity                    | 75  |

|   |      | 6.2.5     | Instantiating Monitors                                       | 75  |

|   |      | 6.2.6     | Implementing Monitors                                        | 76  |

|   | 6.3  | Evalua    | ation                                                        | 77  |

|   |      | 6.3.1     | Autonomous Vehicle Control Stack                             | 77  |

|   |      | 6.3.2     | Comparison with S-TaLiRo and Breach                          | 78  |

|   |      | 6.3.3     | Automatic Transmission System                                | 80  |

| 7 | Qua  | ntitativ  | re Monitoring with Weighted Edit Distance                    | 83  |

|   | 7.1  | Weigh     | ted Edit Distance                                            | 84  |

|   |      | 7.1.1     | Sampling, Quantization and Weighted Edit Distance            | 86  |

|   |      | 7.1.2     | Normalized Weighted Edit Distance                            | 88  |

|   | 7.2  | Weigh     | ted Edit Robustness for STL                                  | 89  |

|   |      | 7.2.1     | Robustness Degree                                            | 89  |

|   |      | 7.2.2     | From STL to Weighted Edit Automata                           | 90  |

|   |      | 7.2.3     | Computing the Value of a Signal in a Weighted Edit Automaton | 93  |

|   |      | 7.2.4     | WED-based robustness and TRE specifications                  | 95  |

|   | 7.3  | Evalua    | ation                                                        | 95  |

|   |      | 7.3.1     | Benchmarks for Automotive Systems                            | 96  |

| 8 | Indi | ıstrial c | ease study: SENT protocol                                    | 101 |

|   | 8.1  | Forma     | lization of the SENT Protocol                                | 102 |

|   |      | 8.1.1     | Single Edge Nibble Transmission Protocol                     | 102 |

|   |      | 8.1.2     | SENT requirements in STL                                     | 103 |

|   |      | 8.1.3     | SENT requirements in TRE                                     | 105 |

|   | 8.2  | Runtin    | me Monitoring with Recovery                                  | 106 |

|   |      | 8.2.1     | STL Monitors with Recovery                                   | 107 |

|   |      | 8.2.2     | TRE Monitors with Recovery                                   | 107 |

|   | 8.3  | Runtin    | me Monitoring of the SENT protocol                           | 109 |

|   |      | 8.3.1     | From Requirements to Hardware Monitors                       | 109 |

|   |      | 8.3.2     | FPGA Implementation                                          | 111 |

|   | 8.4  | Monito    | oring SENT with WED                                          | 112 |

|   |      | 8.4.1     | Formalized Requirements                                      | 113 |

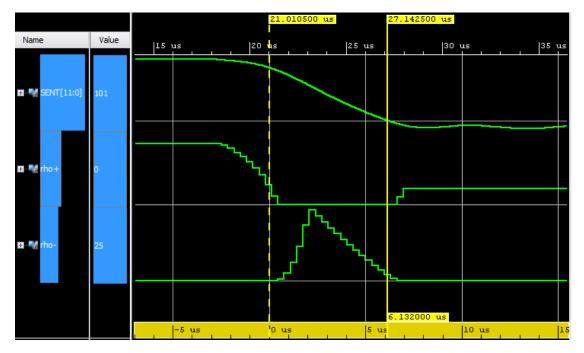

|   |      | 8.4.2     | Evaluation Results                                           | 114 |

| 9  | Con          | clusion and Future Work                          | 119 |  |

|----|--------------|--------------------------------------------------|-----|--|

|    | 9.1          | Summary                                          | 119 |  |

|    | 9.2          | Research Motivation Revisited                    | 120 |  |

|    | 9.3          | Future Work                                      | 122 |  |

| A  | The          | orem Proofs                                      | 125 |  |

|    | A.1          | Theorem Proofs: Algebraic Runtime Verification   | 125 |  |

|    | A.2          | Theorem proofs: Quantitative Monitoring with WED | 129 |  |

|    |              | A.2.1 Proof of Theorem 4                         | 131 |  |

| В  | Har          | dware Monitors in Verilog                        | 135 |  |

| Ac | ronyı        | ns                                               | 139 |  |

| Bi | Bibliography |                                                  |     |  |

# **List of Figures**

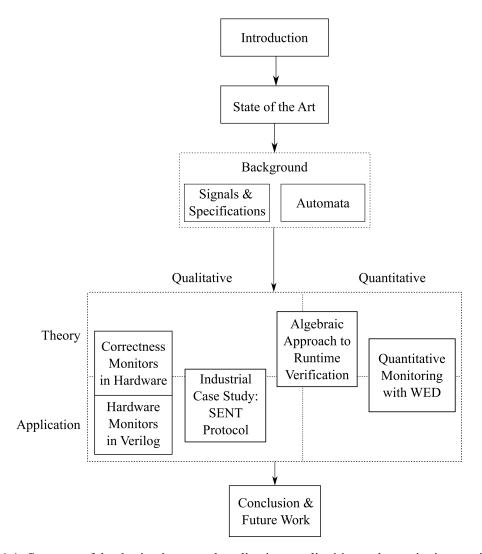

| 1.1  | ring                                                                                                           | 15 |

|------|----------------------------------------------------------------------------------------------------------------|----|

| 3.1  | Analog, discrete and digital signal                                                                            | 24 |

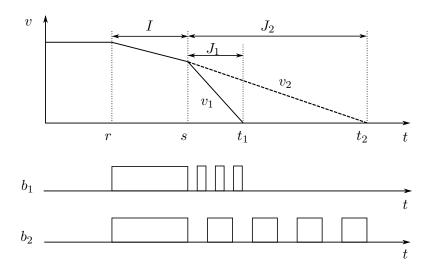

| 3.2  | An example of bounded stabilization property [Nič08]                                                           | 28 |

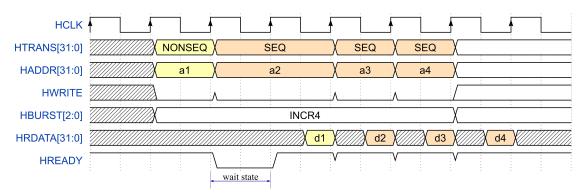

| 3.3  | AHB Read transfer with two wait states inserted by the slave                                                   | 29 |

| 3.4  | Braking patterns for different stopping distances with ABS                                                     | 31 |

| 3.5  | AHB Burst of four read transfers with incrementing addresses                                                   | 33 |

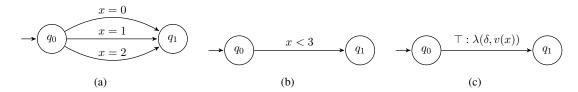

| 4.1  | From automata transitions to WSA transitions                                                                   | 38 |

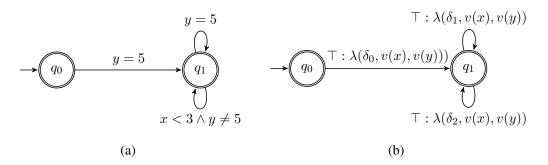

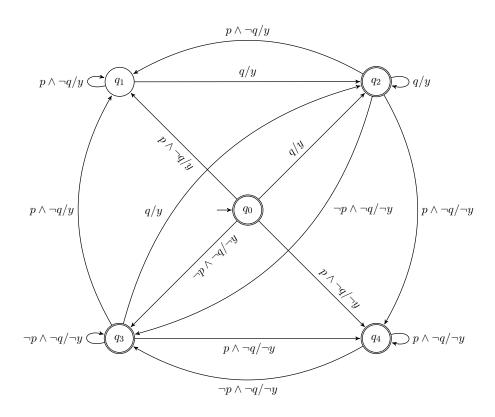

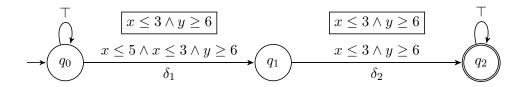

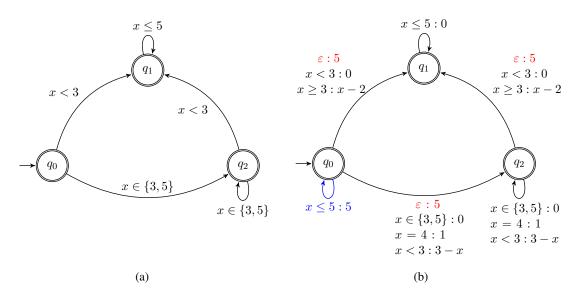

| 4.2  | An acceptor and a weighted symbolic automaton for formula $\square(x < 3 \text{ S } y = 5)$ .                  | 38 |

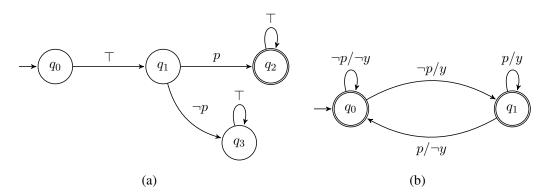

| 4.3  | An acceptor and a temporal tester for $\bigcirc p \dots \dots \dots \dots \dots$ .                             | 42 |

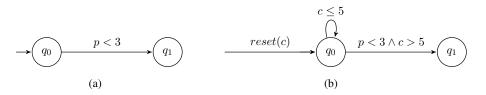

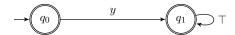

| 4.4  | Adding clock constraints to transitions                                                                        | 42 |

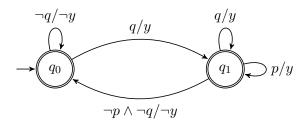

| 4.5  | Temporal tester for $p  \mathbb{S} q$                                                                          | 45 |

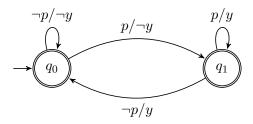

| 4.6  | Temporal tester for $\bigcirc p$                                                                               | 45 |

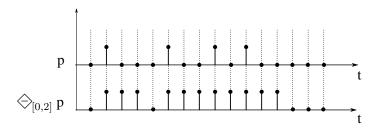

| 4.7  | Timing diagram produced by a temporal tester for $\diamondsuit_{[0,2]}p$                                       | 46 |

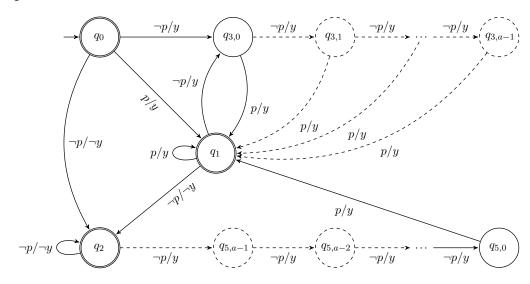

| 4.8  | Temporal tester for $\diamondsuit_{[0,a]}p$ with enumerated time                                               | 46 |

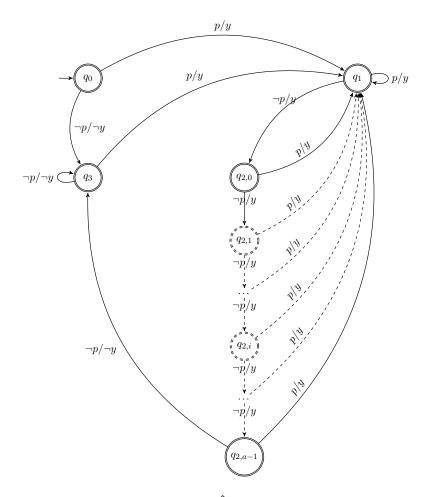

| 4.9  | Temporal tester for $\diamondsuit_{[0,a]}^{}p$ with symbolic representation of time                            | 47 |

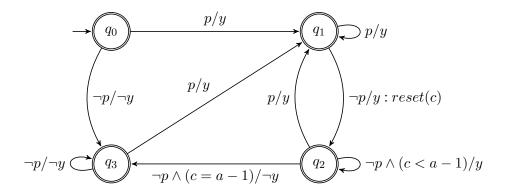

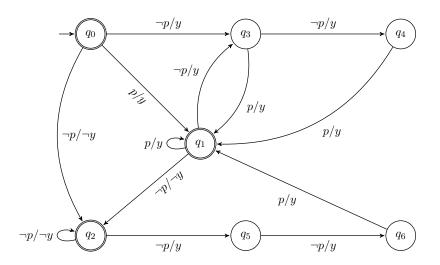

| 4.10 | Temporal tester for $\diamondsuit_{[0,2]}p$                                                                    | 48 |

| 4.11 | Generalized temporal tester for $\bigcirc_{[0,a]} p$ , for $a \ge 1$ , with enumerated time                    | 48 |

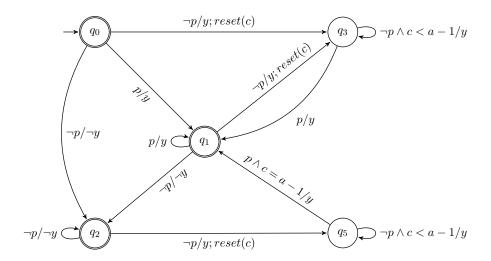

| 4.12 | Generalized temporal tester for $\diamondsuit_{[0,a]}p$ , for $a \geq 1$ ; implementation with discrete clocks | 49 |

| 4.13 | Temporal tester for $pUq$ .                                                                                    | 50 |

| 4.13 | •                                                                                                              | 50 |

| 7.17 | temporal tester used for tester-to-acceptor conversion.                                                        | 50 |

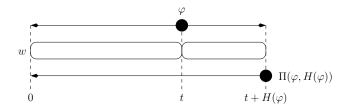

| 5.1  | From bounded future $\varphi$ to past $\Pi(\varphi,b)$                                                         | 53 |

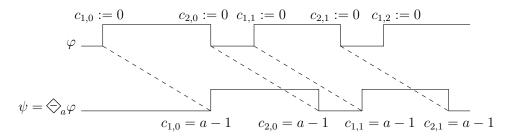

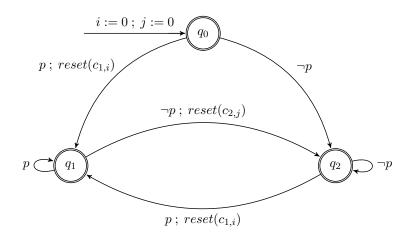

| 5.2  | Computing $\diamondsuit_a \varphi$ with discrete clocks                                                        | 55 |

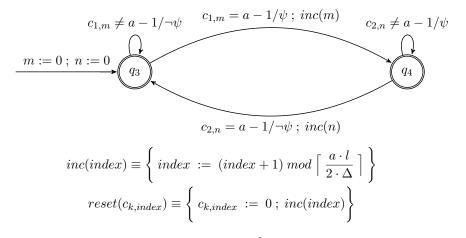

| 5.3  | General structure of temporal tester $\diamondsuit_{\{a\}} p$ for inputs of $(\Delta, l)$ variability          | 55 |

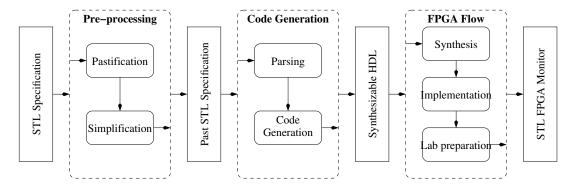

| 5.4  | Implementation flow                                                                                            | 58 |

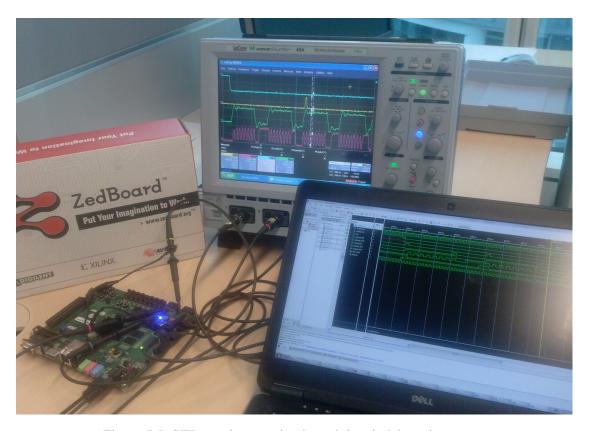

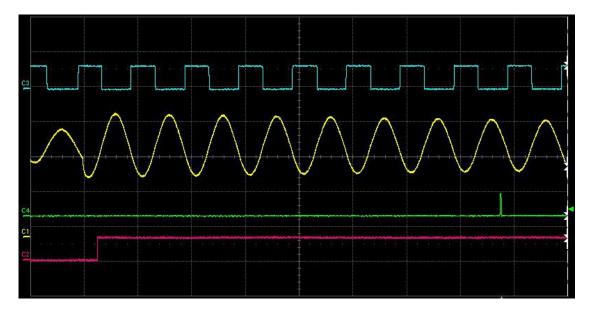

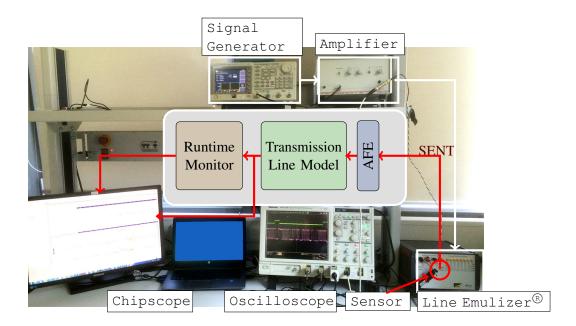

| 5.5  | STL monitor running in real time in lab environment                                                            | 59 |

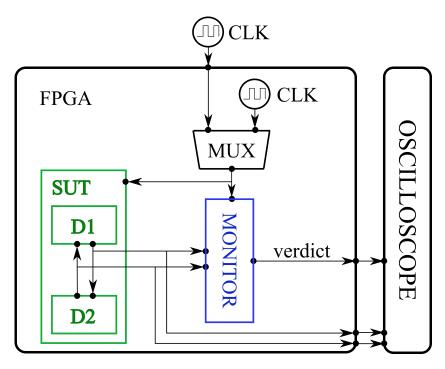

| 5.6  | Self-contained architecture - a monitor and a SUT on the same FPGA                                             | 61 |

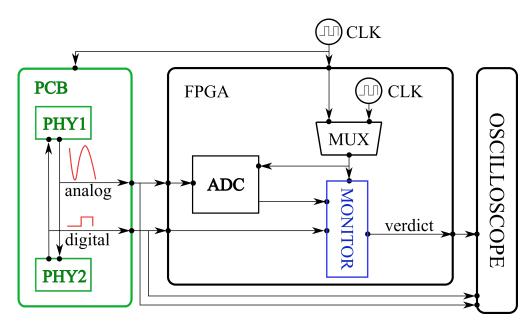

| 5.7  | Integration of a FPGA monitor to an external device                                                            | 62 |

| 5.8  | Stabilization property signals observed in our lab environment                                                 | 64 |

|      |                                                                                                                |    |

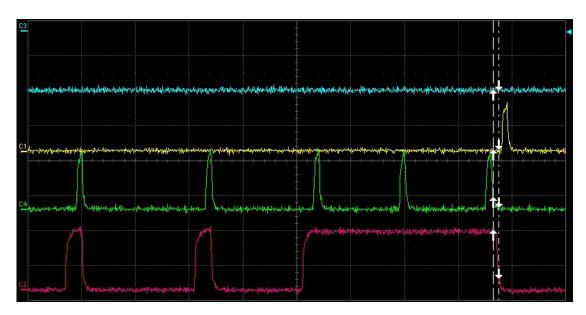

| 5.9  | Nested pulse property for <i>data available</i> (depicted in red) and <i>fifo read enable</i> (depicted in green) signals                                            | 66    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 5.10 | SPI clock division property observed in our lab environment.                                                                                                         | 66    |

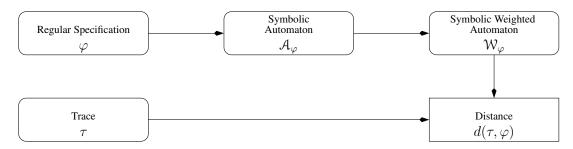

| 6.1  | Computation of $d(\tau,\varphi)$                                                                                                                                     | 70    |

| 6.2  | Weighted symbolic automaton $W$ that accepts the language of $\varphi_1$ and $\varphi_2$                                                                             | 71    |

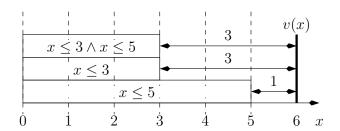

| 6.3  | Example of a distance between $v$ and $\psi$                                                                                                                         | 73    |

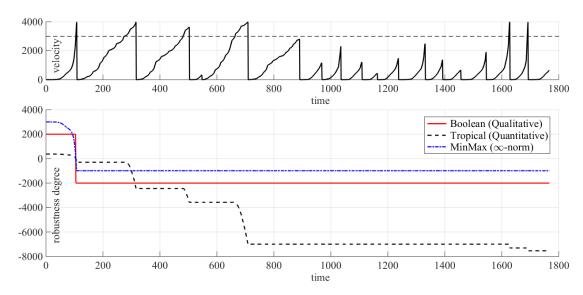

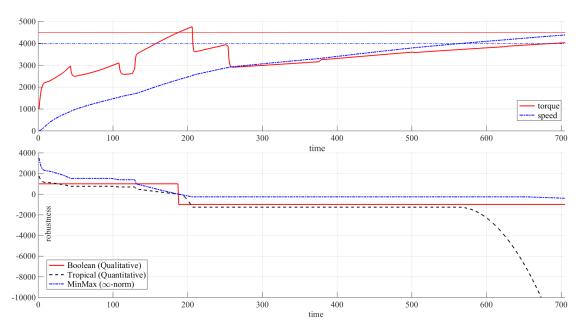

| 6.4  | Robustness degree $\rho(\tau_{[0,t]}, \varphi_1)$ , where $\varphi_1 = \Box(v_{ego} \leq v_{limit})$ , based on three                                                |       |

|      | different semiring instantiations                                                                                                                                    | 78    |

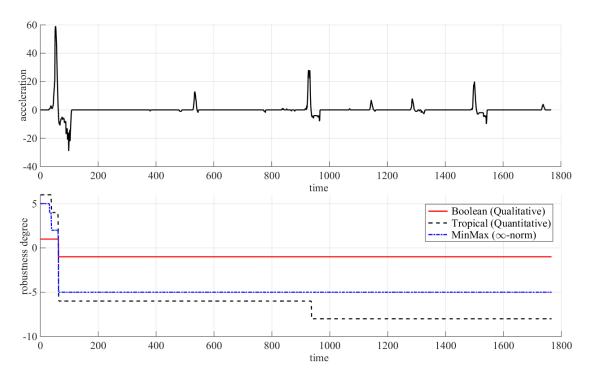

| 6.5  | Robustness degree $\rho(\tau_{[0,t]}, \varphi_2)$ , where $\varphi_2 = \Box((a_x \geq \theta) \rightarrow \Box_{(0,\epsilon]} \neg (a_x \leq 0))$ ,                  |       |

|      | based on different semiring instantiations                                                                                                                           | 79    |

| 6.6  | Robustness degree $\rho(\tau_{[0,t]}, \varphi_3)$ , where $\varphi_3 = \Box((\omega \leq \omega_{max}) \land (v \leq v_{max}))$ , based                              |       |

|      | on different semiring instantiations.                                                                                                                                | 81    |

| 7.1  | Measuring similarity $d_{i,i}(s_1, s_2)$ between a reference $s_1$ vand a measured $s_2$ behavior                                                                    |       |

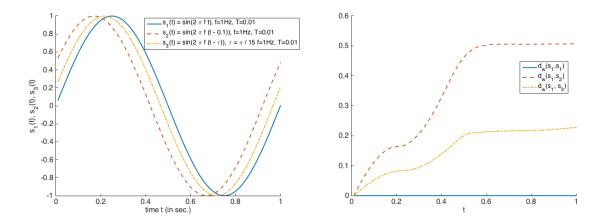

|      | - single versus multiple deviations                                                                                                                                  | 86    |

| 7.2  | Measuring similarity $d_{i,i}(s_1, s_2)$ between a reference $s_1$ and a measured $s_2$ behavior                                                                     |       |

|      | - phase shifts                                                                                                                                                       | 87    |

| 7.3  | Measuring similarity $d_{i,i}(s_1, s_2)$ between a reference $s_1$ and a measured $s_2$ behavior - magnitude of deviations.                                          | 88    |

| 7.4  | Weighted edit distances $d_W(s_1, s_2)$ and $d_W(s_1, s_3)$ , where $s_1(t) = \sin(2\pi f t)$ ,                                                                      |       |

|      | $s_2(t) = \sin(2\pi f(t-0.1)), s_3(t) = \sin(2\pi f(t-\tau)), T = 0.01, f = 1Hz$ and                                                                                 |       |

|      | $\tau = \pi/15. \ldots \ldots$                | 89    |

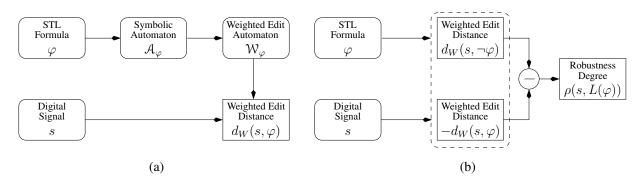

| 7.5  | Computation of (a) Weighted Edit Distance $d_W(s,\varphi)$ and (b) Robustness Degree $\rho(s,\varphi)$                                                               | ). 90 |

| 7.6  | (a) A Symbolic Automaton $\mathcal{A}_{\varphi}$ accepting $L(\varphi)$ (b) a Weighted Edit Automaton $\mathcal{W}_{\varphi}$ .                                      | 91    |

| 7.7  | Example - computation of $v(s, \mathcal{W}_{\varphi})$                                                                                                               | 95    |

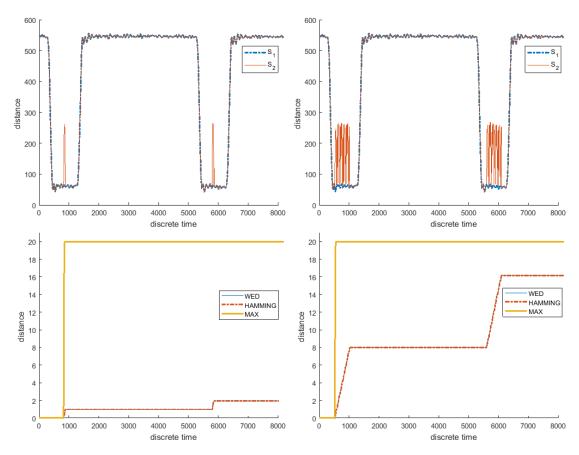

| 7.8  | A simulation trace $s$ from the Automatic Transmission model and $d_W(s, \neg \varphi_6)$ .                                                                          | 97    |

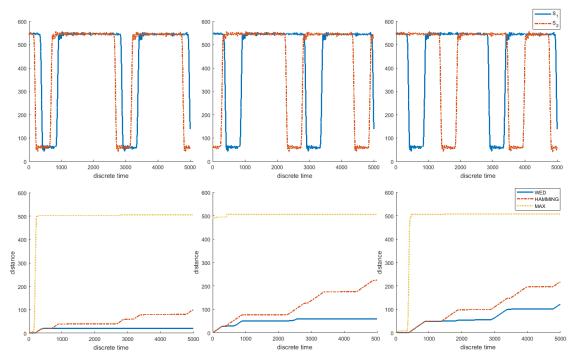

| 7.9  | Calculated positive and negative robustness for obtained air-to-fuel ratio $\lambda$                                                                                 | 99    |

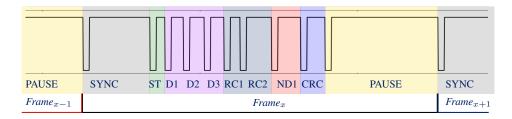

| 8.1  | A SENT frame starts with a mandatory synchronization pulse (SYNC), followed by                                                                                       |       |

|      | a status nibble (ST), data nibbles (D1, D2, D3), rolling counters (RC1, RC2), bit                                                                                    |       |

|      | inverse of D1 (ND1), cyclic redundancy check (CRC), and finishes with an optional                                                                                    |       |

|      | pause                                                                                                                                                                | 102   |

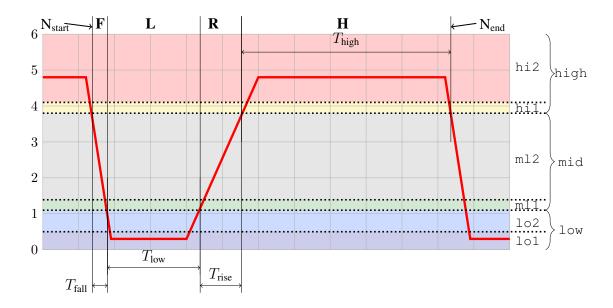

| 8.2  | SENT nibble pulse: A pulse starts ( $N_{\text{start}}$ ) with a falling edge F, followed by a low region L, followed by a rising edge R, followed by a high region H | 103   |

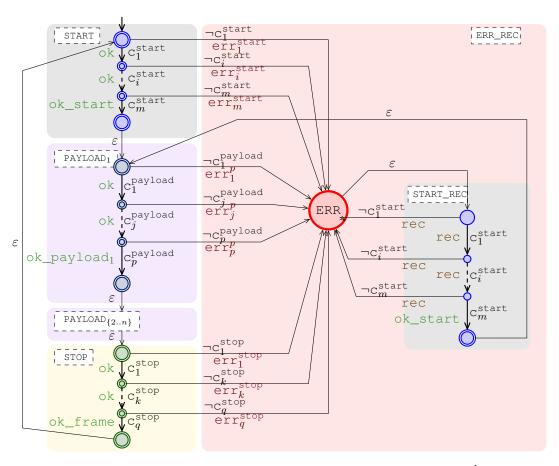

| 8.3  | General procedure for obtaining monitors with recovery <sup>1</sup>                                                                                                  | 108   |

| 8.4  | Runtime Monitoring of the SENT: Hardware Setup                                                                                                                       | 111   |

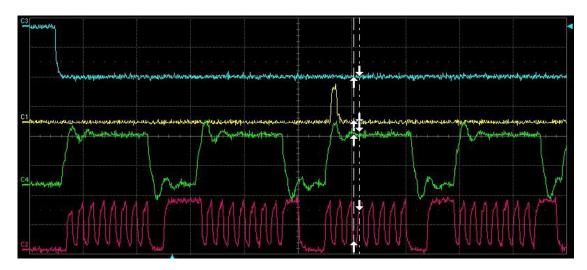

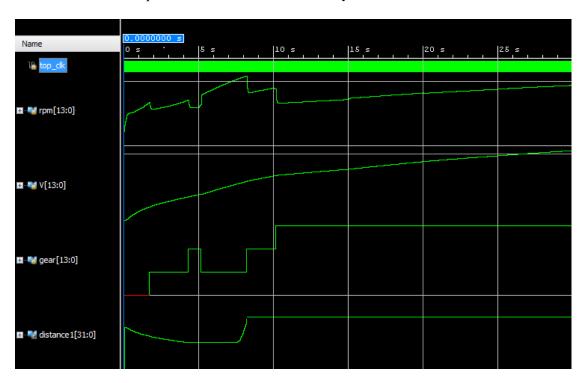

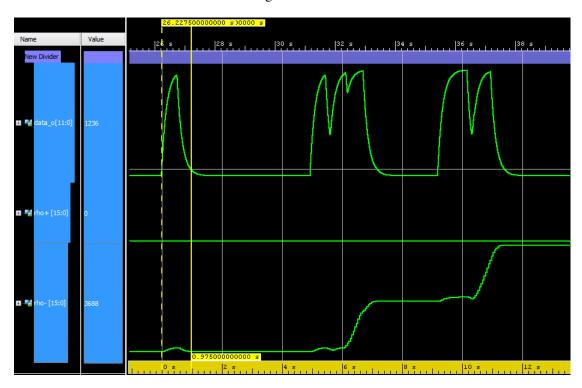

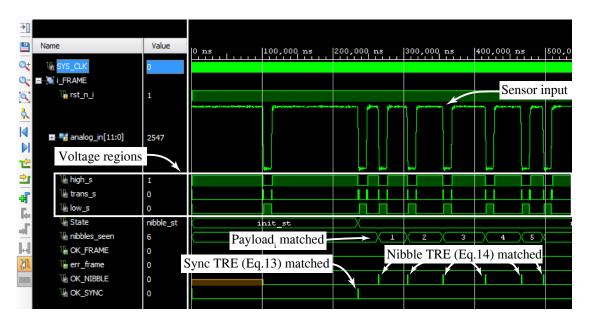

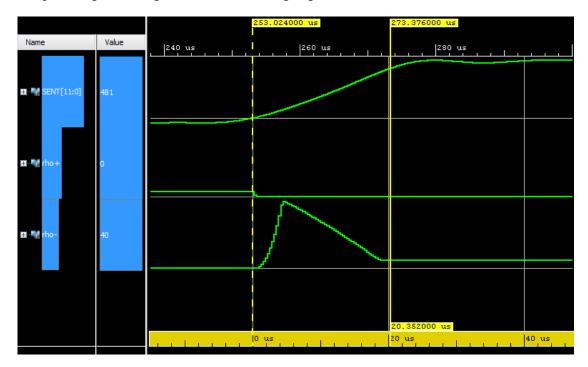

| 8.5  | Runtime TRE monitoring: Vivado RTL functional simulation                                                                                                             | 112   |

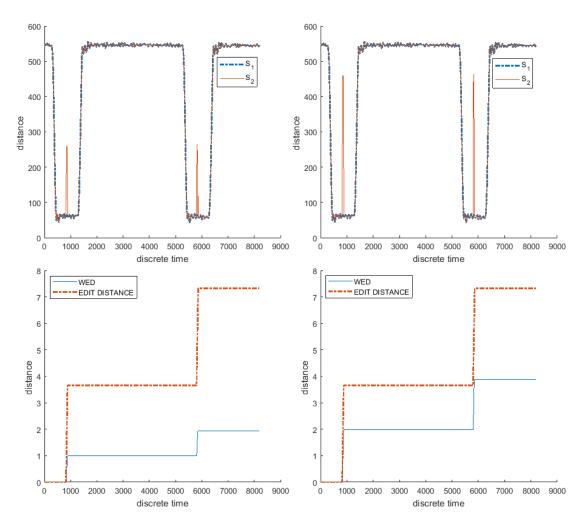

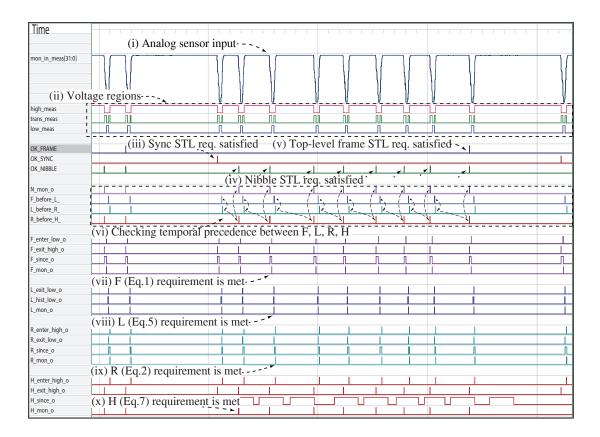

| 8.6  | Runtime monitoring of the STL requirements                                                                                                                           | 114   |

| 8.7  | Calculated positive and negative robustness for SENT pulse falling edge which                                                                                        | 117   |

| J.,  | satisfies $T_{fall}$ requirement                                                                                                                                     | 115   |

| 8.8  | Calculated positive and negative robustness for SENT pulse rising edge which violates                                                                                | ="    |

|      | $T_{rise}$ requirement                                                                                                                                               | 116   |

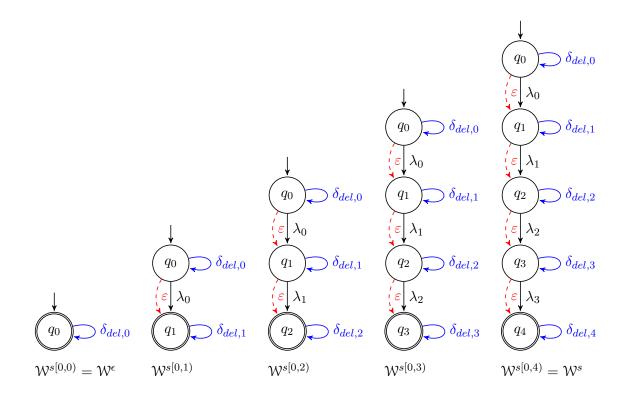

| A.1 | An array of SWWAs $W^{s[0,j)}$ that model all possible edit operations on each prefix |     |

|-----|---------------------------------------------------------------------------------------|-----|

|     | $s[0,j) \in P(s)$ of $s \in L(\varphi)$                                               | 132 |

|     |                                                                                       |     |

## **List of Tables**

| 3.1<br>3.2<br>3.3                 | AHB read transfer correctness requirements specified in STL                                                                                                                                                                                                                                                                                                        | 30<br>32<br>33 |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4.1                               | Examples of semirings                                                                                                                                                                                                                                                                                                                                              | 39             |

| 5.1                               | Resource benchmark results for untimed past STL formulas. We report on the number of flip-flops consumed by the resulting monitor (#FF), number of lookup tables consumed (#LUT) and achieved maximum circuit frequency in MHz                                                                                                                                     | 61             |

| 5.2                               | Resource benchmark results for bounded past STL formulas. We report on the number of flip-flops (#FF), lookup tables consumed (#LUT) and achieved maximum circuit frequency in MHz                                                                                                                                                                                 | 62             |

| 5.3                               | Resource benchmark results for bounded future STL formulas. We report on the number of flip-flops (#FF), lookup tables consumed (#LUT) and achieved maximum                                                                                                                                                                                                        | 02             |

|                                   | circuit frequency in MHz                                                                                                                                                                                                                                                                                                                                           | 63             |

| 6.1                               | $val(\tau, W)$ computed on WSA from Figure 6.2 with different semirings                                                                                                                                                                                                                                                                                            | 76             |

| 6.2                               | Precision comparison between the syntactic-based tools and the semantic approach. We compare the robustness degree results obtained from S-TaLiRo, Breach and ARV.                                                                                                                                                                                                 | 80             |

| 7.1                               | Automatic Transmission properties [BHF15]                                                                                                                                                                                                                                                                                                                          | 96             |

| <ul><li>7.2</li><li>7.3</li></ul> | Evaluation results for the Automatic Transmission benchmark. We report on the resulting robustness degree $\rho$ , the number of states $ Q $ and transitions $ \Delta $ of Weighted Edit Automata $\mathcal{W}_{\varphi}$ and $\mathcal{W}_{\neg\varphi}$ , as well as the number of flip-flops (#FF) and lookup tables (#LUT) consumed to implement the monitors | 98             |

|                                   | $ \Delta $ of Weighted Edit Automata $\mathcal{W}_{\varphi}$ and $\mathcal{W}_{\neg\varphi}$ , as well as the number of flip-flops (#FF) and lookup tables (#LUT) consumed to implement the monitor                                                                                                                                                                | 100            |

| 8.1                               | SENT Electrical Interface Requirements given in natural language, together with their TRE formalization.                                                                                                                                                                                                                                                           | 103            |

| 8.2                               | SENT Transmission Requirements of Synchronization & Nibble Pulse in natural language and formalized in TRE                                                                                                                                                                                                                                                         | 104            |

|                                   |                                                                                                                                                                                                                                                                                                                                                                    |                |

|                                   |                                                                                                                                                                                                                                                                                                                                                                    | xxi            |

| 8.3 | Monitor Synthesis from STL and TRE formalizations. We provide FPGA synthesis results: flip-flops (#FF) and lookup tables (#LUT) consumed and minimum clock |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | frequency achieved. In addition, we provide time and memory consumed by HLS                                                                                |

|     | procedure                                                                                                                                                  |

| 8.4 | Evaluation results for SENT protocol properties. We report on the resulting robustness                                                                     |

|     | degree $\rho$ , the number of states $ Q $ and transitions $ \Delta $ of Weighted Edit Automata                                                            |

|     | $W_{\varphi}$ and $W_{\neg \varphi}$ , as well as the number of flip-flops (#FF) and lookup tables (#LUT)                                                  |

|     | consumed to implement the monitors                                                                                                                         |

# **List of Algorithms**

| 1 | $rpd(v,\psi)$              | 72 |

|---|----------------------------|----|

| 2 | $\wedge	ext{-min}(v,\psi)$ | 72 |

| 3 | $val(	au,\mathcal{W})$     | 74 |

| 4 | ob(	au,arphi)              | 74 |

| 5 | /al $(s,\mathcal{W})$      | 94 |

| 6 | $nitVal(\mathcal{W})$      | 94 |

## **Thesis Publications**

The thesis is based on the following research papers, published in proceedings of international conferences and journals.

- Stefan Jakšić, Ezio Bartocci, Radu Grosu, Reinhard Kloibhofer, Thang Nguyen, Dejan Ničković: From signal temporal logic to FPGA monitors. *In 13. ACM/IEEE International Conference on Formal Methods and Models for Codesign, MEMOCODE 2015, Austin, TX, USA*, September 21-23, 2015, pp.218–227, 2015.

- Stefan Jakšić, Ezio Bartocci, Radu Grosu, Dejan Ničković: Quantitative Monitoring of STL with Edit Distance. In Runtime Verification - 16th International Conference, RV 2016, Madrid, Spain, September 23-30, 2016, Proceedings, pp.201–218, 2016.

- Thang Nguyen, Ezio Bartocci, Dejan Ničković, Radu Grosu, Stefan Jakšić, Konstantin Selyunin: The HARMONIA Project: Hardware Monitoring for Automotive Systems-of-Systems. In Proceedings of the 7<sup>th</sup> International Symposium on Leveraging Applications of Formal Methods, Verification and Validation: Discussion, Dissemination, Applications (ISoLA 2016) Corfu, Greece pp.371–379, October 10-14, 2016.

- Konstantin Selyunin, Stefan Jakšić, Thang Nguyen, Christian Reidl, Udo Hafner, Ezio Bartocci, Dejan Ničković, Radu Grosu: Runtime Monitoring with Recovery of the SENT Communication Protocol. In Proceedings of CAV 2017: the 29th International Conference on Computer Aided Verification, Heidelberg, Germany pp.336–355, July 24-28, 2017.

- Stefan Jakšić, Ezio Bartocci, Radu Grosu, Thang Nguyen, Dejan Ničković: Quantitative Monitoring of STL with Edit Distance. In International Journal on Formal Methods in System Design, 2018.

- Stefan Jakšić, Ezio Bartocci, Radu Grosu, Dejan Ničković: An Algebraic Framework for Runtime Verification. *International Conference on Embedded Software* EMSOFT 2018 (to appear).

CHAPTER 1

## Introduction

Modern society is ever more dependent on computer systems in all aspects of life. Computer systems admit wide range of applications such as transportation, medical, banking and many more. Computational and networked systems that interact with the physical environment, called Cyber-Physical System (CPS), typically deploy digital controllers to react to stimuli originating from physical environment. CPS in which a failure can result in catastrophic consequences, such as loss of human lives, are commonly designated as safety-critical. The design constraints for such systems often depend on their level of criticality. Poorly implemented vehicle cruise control software will always have more impact than a malfunctioning microwave. In order to comply with safety standards the manufacturers have to ensure very low failure rates [ISO]. Verification is the process of ensuring CPS reliability and compliance.

Devices which implement interaction between analog components and digital components, such as CPS, impose a significant verification challenge for simulation-based methods which are still frequently used in the industrial practice. Rigorous verification of mixed-signal CPS requires simulating the complex dynamics of the system, typically defined by a set of differential equations. Thus, the verification of such devices is time consuming. In case of complex CPS verification usually takes more time than the design process. Reducing verification time allows a company to release a product before the competition and to gain a crucial advantage on the market.

Verification is an inevitable process which also determines the feasibility of a system. Over the past years, several catastrophes highlighted the importance of verification. A hidden bug inside a CPS design is very costly: the cost of 2011 Intel Sandy Bridge processor recall is estimated at stunning 1 billion US dollars [Shi11]. NASA space mission crashes [Dow97], Ariane 5 failure [Dow97], a blackout which leaves millions without electricity [ADF<sup>+</sup>05] and many similar cases [LT93, Pri95, KK13] are a clear indicator about the importance of verification.

In spite of all the complexity of the verification problem, our cars still deploy electronic systems when necessary, planes are flying and pacemakers allow many people to continue with their lives. These are witnesses that the industry is able to respond to many verification challenges, with

more or less effort. Our research is aiming to improve CPS verification by increasing rigor, speed and automation and proliferate theoretical novelties into industrial practice.

In order to explain the context of our research, in the following sections we provide a scientific and an industrial point-of-view on verification. Exhaustive verification methods originate from scientific community and aim to provide firm correctness guarantees for all possible executions of the system. In an industrial setting, verification teams favor a simulation-based approach which can achieve usable results in domains such as digital semiconductor design and CPS testing.

Finally we present a lightweight formal verification method, Runtime Verification (RV), which is focused on observing and evaluating individual behaviors. In semiconductor industry this approach is also known as Assertion-Based Verification (ABV) and is used to complement the CDV methods. RV is an integral part of Falsification Testing as well.

## 1.1 Exhaustive Verification Methods

To present the exhaustive verification methods, we focus on hybrid systems verification and model checking. These methods offer full correctness guarantees, but the price is paid with limited usability due to scalability issues.

## 1.1.1 Model Checking

Model checking [CE81, QS82, BKL08] is an exhaustive verification technique aiming to explore the model of a system in order to check whether *all* the possible executions of a system, defined by a Kripke structure, conform to the specification. Model checking aims to guarantee correctness, or find counterexamples which are typically described by temporal patterns. Conversely to CDV which adopts a black-box approach, model checking directly leverages the knowledge of the structure of the model. Model checking is applicable when we have access to the model of a SUT, when the size of the model can be handled, and when the results of model checking are guaranteed to hold for real system as well.

Model checking has evolved from explicit state model checking to symbolic model checking [BCM<sup>+</sup>92] and bounded model checking [BCC<sup>+</sup>03]. The latter applies a different strategy: instead of exhaustive model exploration, it tries to incrementally explore finite length paths of a model in order to find the counterexample. The problem of checking a requirement over finite paths is encoded as boolean satisfiability problem (SAT) problem. Although efficient in practice, bounded model checking cannot guarantee the absence of bugs. Introduction of Counterexample-guided Abstraction Refinement (CEGAR) [CGJ<sup>+</sup>00] approach led to further reducing the size of the space by allowing to abstract away the irrelevant parts of the model. Model checking did contribute to proliferation of formal methods in the industrial practice [WBKW07, Lev04].

Due to scalability issues, model checking can be applied to formally prove absence of bugs only in critical parts of complex devices (e.g. floating point arithmetic in a Central Processing Unit (CPU)). Recent advances show that with sufficient effort it is possible to verify a complex processor pipeline control [RCD<sup>+</sup>16]. An other important concern for verification teams is the

return of investment. Formal verification techniques based on model checking have significant ramp-up time and limited re-usability. Only certain cases for limited number of features have shown to scale successfully so far.

#### 1.1.2 Verification of Hybrid Systems

Systems which operate in different modes with continuous dynamics, defined by differential equations, can be modeled with hybrid automata [ACHH93, MMP91]. A hybrid automaton can either make a discrete transition between the locations, or stay in the location and evolve according to a particular differential equation specified for that state. The evolution of a location is memorized in a variable, which will be tested as a condition whether to take a discrete transition or not.

Full safety verification of hybrid systems is an undecidable problem [HKPV95, ACH<sup>+</sup>95]. Therefore, the mainstream approach to verification of hybrid systems is reachability analysis. The solution paradigm moved from computing the exact reachable set to computing over-approximations of the reachable set of states. It is possible to trade complexity of dynamics for the size of the automata to achieve better scalability. With breakthrough in models for representing approximations of reachable states, namely Zonotopes and support functions, modern tools for hybrid systems verification can now handle hundreds of continuous state variables. Many of these concepts are implemented in a tool SpaceEx [FGD<sup>+</sup>11]. However, the formal methods for verification of hybrid systems [DDM04, FKR06, LWJ<sup>+</sup>10, SH08, ARK<sup>+</sup>13] still do not scale well enough due to the state-space explosion. The compositional-based method described in [ABB16] shows good scalability results for linear hybrid systems, but suffers from false positives.

## 1.2 Systematic Testing

The industrial verification methods extensively rely on testing which include systematic generation of input stimuli according to a specific metric. In the world of digital design, Coverage Driven Verification (CDV) achieved significant success and has been established as a de-facto standard. Falsification Testing (FT), which proved very useful for systems with complex dynamics, uses *robustness degree* as metric to select optimal test parameters.

### 1.2.1 Coverage Driven Verification

Digital hardware industry has a long tradition in developing verification methodologies based on own experience and trials. These methodologies fall into Coverage Driven Verification (CDV) approach. The main motivation which brought about the development of CDV, was the very high cost of failure of semiconductor products [Shi11].

Due to processing power increase over the last decades, simulation has become computationally cheaper. Major semiconductor solution vendors put CDV in focus and offer a palette of Verification IPs, adherent to the principles of CDV. VIPs are protocol-specific verification blocks which can be directly integrated into an existing verification environment. Verification teams usually