DIPLOMA THESIS

# Comparison of Verification and Productive Firmware for a Wireless Low-power System-on-Chip

Submitted at the Faculty of Electrical Engineering and Information Technology, TU Wien in partial fulfilment of the requirements for the degree of Diplom-Ingenieur

under supervision of

Univ.Prof. Dipl.-Ing. Dr.techn. Axel Jantsch Institute number: 384 Institute of Computer Technology

and

Dipl.-Ing. Michael Rathmair Institute number: 384 Institute of Computer Technology

by

Christian Tauber, BSc 0928877 Fasangartengasse 64/9 1130 Wien

23 May 2017

#### Kurzfassung

Steigende System-on-Chip (SoC) Komplexität und damit verbundener Aufwand für funktionale Verifikation begründen die Nachfrage für innovative Ideen um den Ressourceneinsatz und Time-to-Market zu verringern. An einem aktuellen Pre-Silicon Entwicklungsprojekt eines ARMbasierten drahtlosen Sensor-SoC wurde die Kombination eines Hardware Abstraction Software Designs für System-level Verifikation und einer produktiven Programmierbibliothek untersucht. Die vorgeschlagene Ansatz ist ein drei schichtiger Hardware Abstraction Layer (HAL), unter Einhaltung des ARM Cortex Microcontroller Software Interface Standard (CMSIS), wobei die unteren zwei Schichten gemeinsam genutzt, und die oberste die individuelle Implementierung des Anwendungsfalls beinhaltet. Um das vorgestellte Konzept zu untersuchen wurden exemplarisch die Implementierungen zweier Hardware Module mit einem vorgeschlagenen Set an passenden Metriken für Bare-Metal Software untersucht. Basierend auf batteriebetriebenem Einsatz des Chips und den damit verbundenen Anforderungen an geringen Stromverbrauch, wurde der Teil des HALs für die Power Management Unit untersucht. Als zweites Modul wurde die Schnittstelle zum dem auf dem Chip integriertem Transceiver gewählt, aufgrund der Schlüsselfunktion drahtloser Kommunikation. Die umfassende Auswertung zeigte, dass ungefähr 80% des HAL Quellcodes von der Pre-Silicon Verifikation ohne Veränderung für die darauffolgende produktive Programmierbibliothek weiterverwendet werden können. Jedoch müssen die genauen Schnittstellendefinitionen im Vorfeld festgelegt werden und bedürfen der Achtsamkeit des Trade-Offs hinsichtlich Performance und Speicherbelegung. Abschließend an die Anwendbarkeit der kombinierten Entwicklung, wird ein detaillierter Ausblick auf weitere zukünftige Forschungsfragen zu diesem Thema gegeben.

#### Abstract

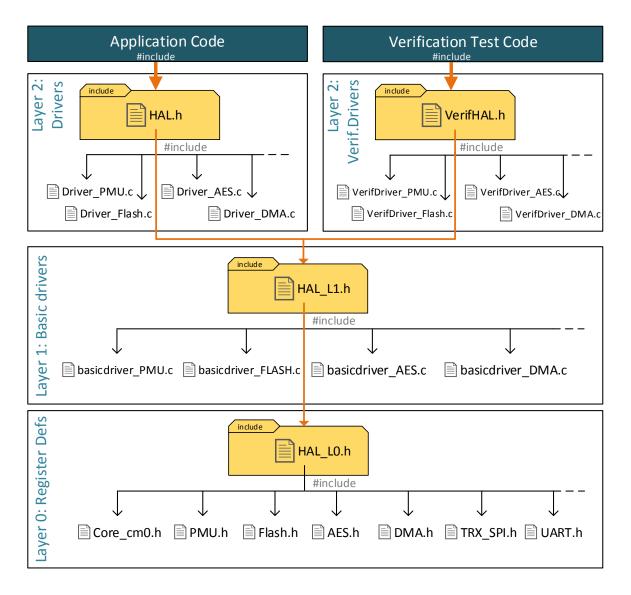

Rising system-on-chip complexity and therewith functional verification effort drives the demand for innovative ideas to decrease required resource usage and shorten time-to-market. On a current pre-silicon development project of an ARM-based wireless sensor system-on-chip, the combination of hardware abstraction software design for system-level verification and a productive programming library was evaluated. The suggested approach is a three layer Hardware Abstraction Layer (HAL), in accordance to ARM Cortex Microcontroller Software Interface Standard (CMSIS), where the bottom two layers are used in common, and the upper one is providing the particular usecase implementation. To survey the proposed concept, the implementations on two example hardware modules were evaluated with a proposed set of appropriate metrics for bare-metal software. Based on the battery-driven chip operation and therewith important low power requirements, the part of HAL regarding the custom developed power management unit was evaluated. As second module, the interface to the on-chip transceiver was selected, by the chip key functionality of wireless communication. The comprehensive evaluation showed that reuse of about 80% of HAL source code from pre-silicon verification could be achieved without any modification necessary, for the followed productive programming library development. However, the straight layer interface definitions have to be defined a-priori and need awareness for trade-offs regarding performance and memory utilization. Concluded with the applicability of combined development, a detailed outlook on reasonable extended future research on this topic is given.

#### Acknowledgements

After an intensive but interesting period of 8 months of working on this diploma thesis and the achieved personal growth & development, I would like to thank everyone who has supported me.

First I have to thank my colleagues from Infineon Technologies AG for the enjoyable, instructive collaboration. Christian Hambeck and Johannes Schweighofer continuously and dedicatedly helped me during the challenging tasks of the development project. At TU Wien, I would like to say thank you to my supervisor Michael Rathmair and Prof. Jantsch for their guidance to finish my diploma thesis.

I would especially like to thank my parents and my sister supporting me throughout my studies and give me the confidence to get where I am now. Finally, thanks to all my friends that accompanied me during the enjoyable time at university and the great time in Vienna.

# Table of contents

| 1. Introduction                                                  |

|------------------------------------------------------------------|

| 1.1 Motivation                                                   |

| 1.2 Problem Statement                                            |

| 1.3 Task Setting                                                 |

| 1.4 Methodology                                                  |

| 2. State of the Art and Related Work                             |

| 2.1 Functional Hardware Verification                             |

| 2.2 ARM Architecture                                             |

| 2.3 Hardware Abstraction Layer                                   |

| 2.4 CMOS Power Consumption and Management Strategies             |

| 2.5 Software Metrics                                             |

| 2.6 Related Work                                                 |

| 3. Proposed Concept                                              |

| 3.1 ARM-based SoC with a custom Transceiver Module               |

| 3.2 Hardware Abstraction Layer for Processor-driven Verification |

| 3.3 Evaluation of Verification and Productive HAL Variants       |

| 4. Implementation                                                |

| 4.1 HAL Implementation in C                                      |

| 4.2 Development and Simulation Environment                       |

| 4.3 Tools for Metric Evaluation                                  |

| 5. Benchmarking and Results                                      |

| 6. Conclusion                                                    |

| Literature                                                       |

| Internet References                                              |

| Image References                                                 |

# Abbreviations

| AES      | Advanced encryption standard                       |  |  |

|----------|----------------------------------------------------|--|--|

| AHB      | Advanced high-performance bus                      |  |  |

| AMBA     | Advanced microcontroller bus architecture          |  |  |

| ANSI     | American national standards institute              |  |  |

| APB      | Advanced peripheral bus                            |  |  |

| API      | Application programming interface                  |  |  |

| CAN      | Controller area network                            |  |  |

| CLK      | Clock                                              |  |  |

| CMOS     | Complementary metal-oxide-semiconductor            |  |  |

| CMSIS    | Cortex microcontroller software interface standard |  |  |

| CPU      | Central processing unit                            |  |  |

| DAP      | Debug access port                                  |  |  |

| DMA      | Direct memory access                               |  |  |

| DSP      | Digital signal processing                          |  |  |

| FCLK     | Free-running processor clock                       |  |  |

| FPGA     | Field programmable gate array                      |  |  |

| GND      | Ground                                             |  |  |

| GPIO     | General-purpose input / output                     |  |  |

| GUI      | Graphical user-interface                           |  |  |

| HAL      | Hardware abstraction layer                         |  |  |

| HCLK     | High-speed clock                                   |  |  |

| I2C      | Inter-Integrated circuit                           |  |  |

| IoT      | Internet of things                                 |  |  |

| IP       | Intellectual property                              |  |  |

| ISO      | International organization for standardization     |  |  |

| ISR      | Interrupt service routine                          |  |  |

| JPEG     | JPEG file interchange format, ISO/IEC 10918-1      |  |  |

| JTAG     | Joint test action group                            |  |  |

| LED      | Light-emitting diode                               |  |  |

| LOC      | Lines of code                                      |  |  |

| McCabeCC | MyCabe cyclomatic complexity                       |  |  |

| MCI      | Memory card interface                              |  |  |

| MCU      | Microcontroller unit                               |  |  |

| MISRA    | Motor industry software reliability association    |  |  |

| MOSFET   | Metal-oxide-semiconductor field-effect transistor  |  |  |

| NAND     | Not-and                                            |  |  |

|          |                                                    |  |  |

| NMOS            | N-type metal-oxide-semiconductor                           |

|-----------------|------------------------------------------------------------|

| NVIC            | Nested vector interrupt controller                         |

| OOP             | Object-oriented programing                                 |

| PCLK            | Peripheral clock                                           |

| PDT             | Processor-driven verification                              |

| PLL             | Phase-locked loop                                          |

| PMOS            | P-type metal-oxide-semiconductor                           |

| PMU             | Power management unit                                      |

| RAM             | Random-access memory                                       |

| RFID            | Radio-frequency identification                             |

| ROM             | Read-only memory                                           |

| RTL             | Register-transfer level                                    |

| SAI             | Serial audio interface                                     |

| SCLK            | System clock                                               |

| SEL             | Select                                                     |

| SFR             | Special function register                                  |

| SLOC            | Source lines of code                                       |

| SoC             | System-on-chip                                             |

| SPI             | Serial peripheral interface                                |

| TLOC            | Total lines of code                                        |

| TRX-IF          | Transceiver interface                                      |

| U(S)ART         | Universal (synchronous/) asynchronous receiver/transmitter |

| UHF             | Ultra-high frequency                                       |

| UPF             | Unified power format                                       |

| USB             | Universal serial bus                                       |

| V <sub>dd</sub> | Positive power supply                                      |

| WB              | Wishbone bus                                               |

| WIC             | Wakeup interrupt controller                                |

| XML             | Extensible markup language                                 |

|                 |                                                            |

# **1. Introduction**

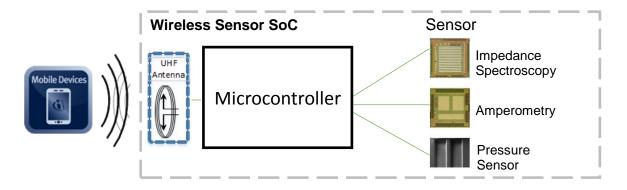

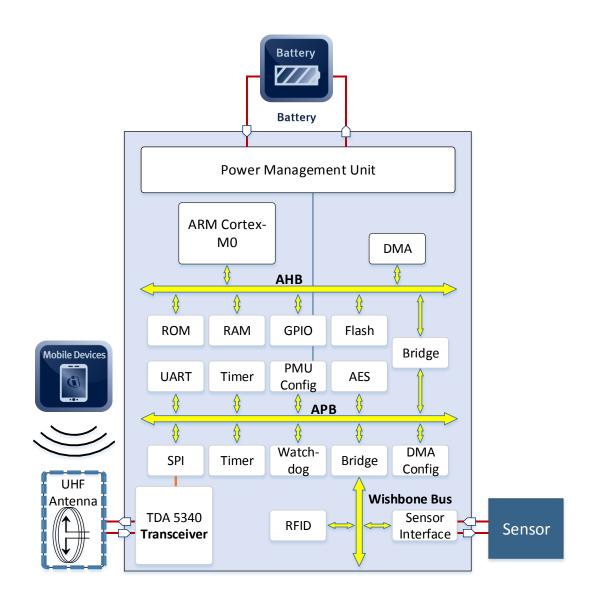

Next generation wireless sensor networks put the requirements on secure and flexible configuration together with high-performance while satisfy the demand on low power consumption for longest possible application lifetime. A system-on-chip (SoC) development project by Infineon on a sub-GHz transceiver chip with integrated ARM Cortex-M0 processor and a flash memory combined with efficient power management strategies shall meet these requirements. Figure 1.1 shows this wireless sensor SoC, by the extension of microcontroller architecture with an application specific sensor and a transceiver to communicate with other devices. The de-facto standard of ARM architecture benefits compatibility, code reuse and integration of well-tested IPs. With the focus on performance and flexibility, the request for intelligent Internet of Things (IoT) network nodes can be satisfied. The development of an efficient power management, the incorporation of versatile wireless interfaces and the goal of minimal chip size integration are thus major challenges in the current presilicon development stage.

Figure 1.1: Wireless Sensor System-on-Chip

Target firmware applications will be able to access the functionality of the modular hardware structure by simple, slight interfaces, provided by a Hardware Abstraction Layer (HAL). Within this context, this thesis presents a concept for combining verification and productive purpose in the HAL design, motivated by potential reduction of the development efforts, a challenging field in research according to the raising system-on-chip complexity and consequently verification efforts. With the research on state-of-the-art software metrics and the treatise on the applicability on embedded baremetal software an evaluation on two example hardware module implementations will allow an indepth conclusion about the proposed HAL and the code reuse over different software design goals.

## **1.1 Motivation**

In a current SoC development project by Infineon the upwards trend in project effort was identified to be surveyed in the pre-silicon stage. A potential strategy for reduction in firmware development and hardware verification is treated by this diploma thesis by examining overlapping tasks in software design, and providing a contribution to a more efficient development process. In combination with the contemporary requirements of IoT wireless nodes, driving node intelligence and longest lifetime, this survey subject is positioned on current topics of research and development.

The design flow of a SoC starts from the specification, goes over to the co-development of hardware and software, where the latter is quite important to verify the functional correctness of the chip, before it is sent to the fab for a first prototype production. This so-called "tape-out" and the associated mask design for the production process is a quite expensive task in SoC development, justifying an excessive effort in ensuring functional correctness. Post hoc design changes result in single or up to total redesign of all masks and maybe in a project fail by financial unfeasibility. An industrial study from 2014 [Fos15] claimed that in SoC development projects 57% of the total project time is spent on verification, with an ongoing trend upwards. In addition, 61% of these projects are behind schedule and thus, are not able to finish the project within the proposed time plan. Approaches and contributions in efficient verification can therefore decrease the development effort and as a consequence time and money resources.

## **1.2 Problem Statement**

The overall rising complexity in systems design and the associated verification effort forces the creation of new innovative strategies and approaches in functional verification. On state-of-the-art SoC development projects this task consists of assertion-based verification in hardware description languages (HDL including VHDL, Verilog, etc.) and processor-driven verification, where a C or Assembler test facilitates the processor and bus system to check the functionality of a module-undertest on system level. The development of firmware therefore is done for verification purpose and in addition to realise a productive firmware, generally in form of a HAL. This software is then provided for 3<sup>rd</sup> party application engineering when using this SoC chip for custom application development. Obviously, in pre-silicon development at the semiconductor manufacturer there is an overlapping between verification and productive firmware development that could contain potential for improvements in development effort reduction, by identifying redundant programming tasks and the resulting parts of code.

Since power management is a major topic to enable longest lifetime with the hard limited amount of energy from battery or energy harvesting, and the connection of the power management unit (PMU) to almost all other components in the system to drive for example sleep or power down states, the verification task is a formidable challenge.

# 1.3 Task Setting

The proposed SoC development project is divided into several development domains, where the delimitation to the thesis survey topic is quite important. The hardware development state includes digital and analog design. While the digital components are controlled and in direct interaction with the central processing unit (CPU) subsystem and the executed software instructions, the analog domain, including clock oscillators, power supply, or input/output pads, is connected to software via digital interfaces. The digital hardware design is closely linked to the domain of software development, with the application of verification firmware to ensure the functional correctness on system level besides HDL module assertion tests. Therefore it is mandatory that the digital domain is explained in detail to understand the chip architecture. However, the digital design itself and detailed questions about it are not part of this thesis, but important to describe the actual task setting.

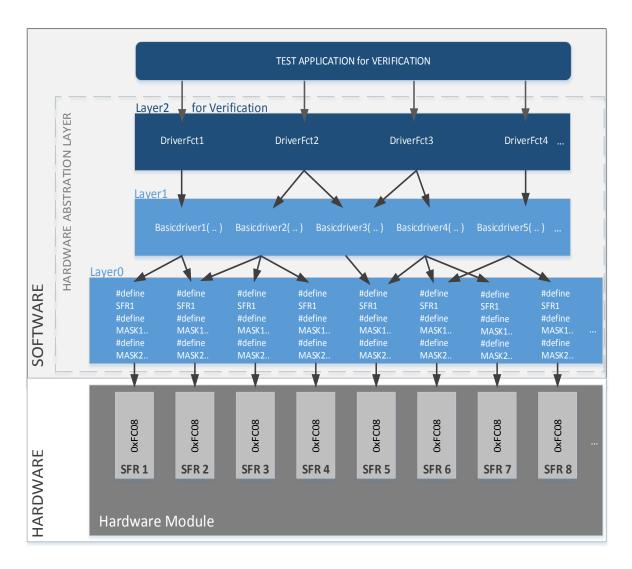

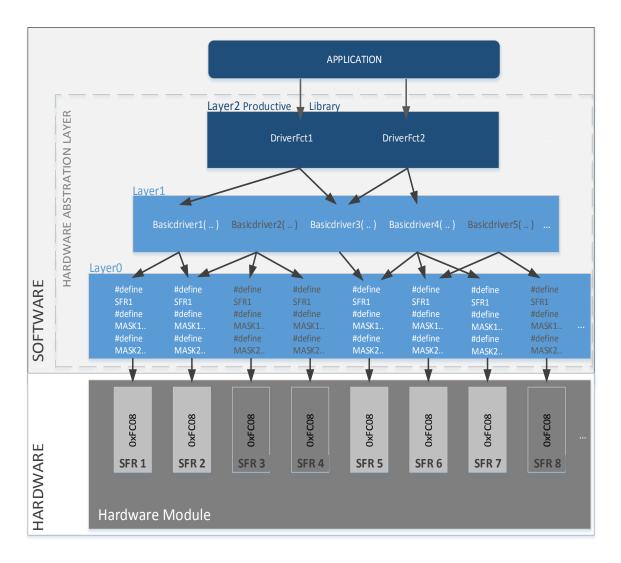

Already mentioned, to present the software task intersection of verification and productive development purpose, the combination through a particular HAL design was examined. To make both variants comparable, suitable metrics qualify the software attributes.

With the important role of the power management unit as all-connecting to the other modules and the risk to bring the system into critical states, the verification of this component is devoted a major focus in this thesis. Through evaluation of the two firmware variants with appropriate, state-of-theart metrics for embedded software, allowed a comprehensive conclusion about the proposed analysis, with a proof-of-concept presented on the example of the power management module and the transceiver interface.

Shortly summarized, the tasks of this thesis were:

- State-of-the-art survey on combined verification and productive firmware, plus as key subject on power management tests

- Survey on software metrics and examination of applicability in the context of bare-metal software and HAL benchmarking

- Design and implementation of the combined HAL in C

- Functional verification of the hardware components with the developed HAL and deployment of the productive variant

- Evaluation of the proposed concept on the example of two hardware modules with the selected set of appropriate metrics

- Discussion of results and contribution on development and verification effort

## 1.4 Methodology

The de-facto standard of ARM in microcontroller design includes the hardware environment and the Cortex Microcontroller Software Interface Standard (CMSIS), a HAL design guideline with provided core-drivers and templates which was used as basis for the proposed software design.

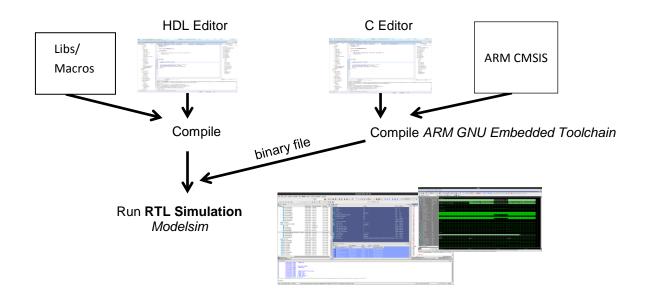

The verification of hardware modules can be done on different abstraction levels and various methods. Single digital components often tested by assertion-based HDL tests which can get complex on bigger design. Hardware Verification Languages (HVLs) therefore are designed to support the verification task. However, on microcontroller system level the interaction of a component with the other blocks, especially the CPU, via a common bus interface is a proper use-case. As a consequence functional verification is in addition done by C-test, facilitating the microcontroller (MCU) system. In the current development project, a combination of HDL-based tests and system-level tests was applied, where the latter one is further discussed in this thesis. To realise the surveyed comparison of the verification firmware variant to the productive application library, software metrics were used to measure the quality of several meaningful attributes. A broad selection from the review on state-ofthe-art metrics was sorted out by the discussion about applicability for each metric and resulted in a reasonable set for hardware abstraction layer measurements. These metrics evaluate characteristics (i) of the source code itself only, to examine internal attributes and (ii) software within the environment, in particular by executing the software on the target MCU system. In this context, the execution was in the current pre-silicon development stage done in register-transfer level (RTL) simulation, where the software binaries are loaded into memory behaviourals. As a consequence unrestricted white-box testing of software and hardware was possible in the RTL simulation environment. For the source code and binaries analysis, several tools were applied to calculate metric results.

# 2. State of the Art and Related Work

Verification, the answer to the question "Does it work?" was historically side-by-side in an evolutional process to the development tools and design process models. In SoC development both, hardware and software are nowadays co-developed and have to be constantly checked against. With raising system complexity far beyond single and manageable HDL digital designs towards processorbased microcontroller system architectures, assertion-based hardware verification methods were extended by system-level tests, to test convincing use cases in interaction with the system environment itself. To clarify the context of this thesis, the term of verification in general and processorbased verification are explained, with power management verification in detail. Subsequently, the popular ARM architecture is due to its market and technological dominance discussed, by explaining the modular structure and interaction of components. On the subject area of software, to fit to the developed hardware and allow abstraction for simplified access of hardware functionality, the common hardware-abstraction layered design approach benefits flexibility and code reusability. ARM provides a HAL design guideline, including core drivers and templates. To adjust this model for a proper customized design, experiences from literature research shall allow a better understanding for particular design decisions. Next, the focus to mobile low-power applications can best be discussed by looking at the technical causes for power dissipation, and common minimization techniques. To compare the developed HAL variants for verification and productive purpose a broadly based summary on state-of-the-art software metrics is presented. Finally, related work is discussed to point out the positioning of the thesis contribution.

# 2.1 Functional Hardware Verification

IEEE 1012-2012 Standard for System and Software Verification and Validation [1] defines verification as "the process of evaluating a system or component to determine whether the products of a given development phase satisfy the conditions imposed at the start of that phase".

Validation in contrary is explained by the IEEE Standard 15288-2008 [2] as "confirmation, through the provision of objective evidence, that the requirements for a specific intended use or application have been fulfilled". To put it simply, verification answers the question "Does it work" and validation "Do we build the right thing?"

Hardware Verification in particular refers to the tools and techniques, used to ensure that a system does not have critical hardware bugs and performs correctly in response to outside stimuli like executing software. Setting up a system, run it and check if it fails is called testing, and is differentiated to verification by being less comprehensive [And05]. While in the early stages independent hardware and software development were quite conventional, rising complexity and therewith higher development cost substantiated new approaches. Hardware/Software Co-development parallels the

sequential development process by starting software implementation while still evolving and verifying the corresponding hardware components. Hardware/Software Co-Verification is the process of verifying embedded system software runs correctly on the hardware design before the design is committed for fabrication [And05]. This is resulting in shorter time-to-market and an additional stimulus in addition to HDL test benches for the hardware developers.

A few years ago the term *Processor-driven Verification/Test* (PDT) also known as *Software-driven verification* [Bai14] [Goe14] was introduced and addresses the problem that test-benches for single IP modules do not cover the interaction in systems with an embedded processor. In PDT the tests are stored in memory, and the results evaluated after execution [Lus16]. A major advantage is the reusability of tests during the overall project lifecycle, since the C or assembly test programs could run on all stages of development from RTL- and Gate-level-simulations to FPGA implementation or up to the fabricated device.

Kenney proposed a detailed PDT methodology [Ken06] in 2004, with these advantages but described PDT as just simple block tests written in C and not firmware per se. A similar approach was shown in [Kom06] connecting several IPs around an Advanced Microcontroller Bus Architecture bus (AMBA), and demonstrating that functional verification could be mainly achieved by software tests in C. In [Hun03] the authors proposed a three-layer-architecture (HAL - API – Operating System) to use high level software test programs and showed the success in hardware abstraction, but conclude a big overhead in debugging and simulation as a major disadvantage. A "Hardware Abstraction Layer Generator" as part of STMicroelectronics "Spirit Assisted Verification Environment (SAVE)" was presented in [Lin10] to address the problem that test case coding is a critical phase during functional verification and the challenge is to write bugless lowest-level C or assembly test cases. In contrast to [Hun03] the architecture was reduced to two layers, to decrease the overhead. A major idea was to automate the process of HAL generation to write and read the registers, and make C test case coding much easier. A time reduction in the verification process of 33% is proposed, and obviously an increase in test execution time. However, there is no information available on the ongoing status of this project. Moreover, the idea of HAL generation could be easily found on the web from several digital design global players, but without specific conjunction with the topic of functional verification.

Block-level verification is nowadays a widely solved problem, whereas the challenges at SoC level are very different [Goe14]. The difficult task is the integration of various blocks and to make sure that they all work properly together. Consequently PDT is a potential field of research by examining methodology to balance high coverage and verification quality with delimitation of development costs and time-to-market.

#### **Power Management Verification**

Wireless sensors have the requirement of low-energy to ration the limited amount of energy by a battery or harvesting system to accomplish the goal of longest lifetime. Formats like the Unified Power Format (UPF) [12] enable the modelling of power supply and control intent and thus extend pre-silicon simulation and described in [Mba12] and [Kar13].

The central component is a power management unit that controls with a mix of power consumption reduction techniques the other system modules, which are grouped together to power domains. A

system-on-chip consists of several domains, for example the CPU-subsystem, the peripherals and the PMU itself. Whenever the CPU-subsystem and peripherals are switched to a power saving mode, the PMU domain is still supplied to wake-up the domains when for example an external event is detected on a preconfigured general-purpose input/output (GPIO) pin.

[Pin08] defines power management verification as the functional verification at pre-silicon stage and involves functional correctness testing in a simulation environment. The challenge of power management verification is based on its very global functions, involving interactions with a lot of other blocks. Thus tests should be system-like; the functional verification of the PMU component itself is claimed as only around 30% of effort.

[Win12] divides the debug and verification of a power management system into hardware and software section, while the latter is divided further into two layers: (i) firmware layer regarding hardware functionality to manage power states without application interaction, such as shut down of components after a certain idle time, (ii) application layer that contains four states with functionality of configuration, operation, sleep and hibernation. With these two layers a fertile approach for a prestage of abstracting power management tests from the particular hardware is presented.

One of the latest publications on this topic by [Mac16] shows a verification approach by performing (i) syntactic checks, more precisely language syntax checks regarding to power management, (ii) run-time checks that could not be revealed by a SystemC compiler, (iii) static analysis, to validate semantic conditions like the number of power domains used, (iv) equivalency checking with UPF and (v) assertion-based verification to check lower-level control sequences.

The literature on the broad topic of power management verification shows that common understanding is not yet established. Therefore, rising system-complexity and the requirement to low-power application design will make further research on this topic necessary. Innovative verification techniques in general combined with a proper understanding and focus on power management verification will be essential to meet the requirements of fast evolving trends in the wireless, low power IoT domain.

# 2.2 ARM Architecture

The ARM microprocessor architecture, developed by ARM Limited [3] is a reduced instruction set computer (RISC) architecture and nowadays very popular due to its industrial leadership and was first introduced in 1985. The designs are developed by ARM and can be licensed by semiconductor vendors to implement them into own custom products. ARM launched the very successful Cortex-M3 processor in 2004. While in 2007 the microcontroller market was shared among 40 vendors in 50 different architectures and a per vendor share of maximum 5% [Pow10], in 2009, based on "Gartner - Market Share Analysis - Preliminary Total Semiconductor Revenue, Worldwide 2008", ARM already had included 6 of the top 10 worldwide semiconductor companies as licensees [Spe09]. In early 2015 ARM already reached a total market share of 24% in microcontrollers and smartcards, and 70% in 32 bit MCUs [York15].

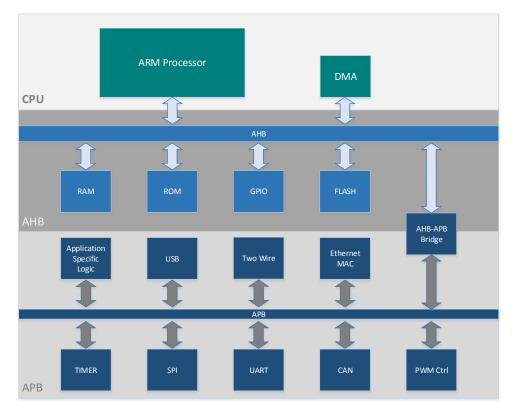

Figure 2.1 shows a typical ARM-based SoC. The ARM architecture not just includes the processor core but also a great number of commonly integrated SoC components and appropriate interconnection buses. The ARM processor core is connected to the 32+ bit wide *Advanced high-performance*

bus (AHB), to access memory modules such as *read-only memory* (ROM), *random-access memory* (RAM), Flash, additionally a graphics processing unit or other components that need high data rate connections. When a *direct memory access* (DMA) controller is used, the bus is commonly implemented as matrix, to available parallel access by paying this with higher gate count due to necessary scheduling functionality. A DMA controller can then process data transfers between memory and/or peripheral units, to relieve the core processing unit. Slower peripherals are connected via the *Advanced Peripheral Bus* (APB), such as a *universal asynchronous receiver/transmitter* (UART), timers or the *Serial Peripheral Interface bus* (SPI), and accessible via a transparent-operating bridge between the two bus segments. This segmentation over different bus systems is not visible to the CPU, all component access-operations are done in the same way, realized by a particular address range of the AHB mapped to the APB bus domain. Both AHB and APB are part of the *Advanced Microcontroller Bus Architecture* (AMBA). With the success of the ARM architecture, AMBA became a de-facto standard for on-chip communication among functional blocks.

A debug controller in addition provides access to the microcontroller via JTAG or Serial Wire interfaces.

Figure 2.1: ARM System-on-Chip block diagram [3]

The ARM processor family provides processor systems for all kind of application requirements, from highest performance to serve rich operating systems (Cortex-A Series), over fast response requirements for hard real-time applications (Cortex-R), to smallest/lowest power optimized microcontrollers (Cortex-M) or resistant security applications (SecurCore). In every domain again multiple processor cores are available; distinguish from another again by performance, efficiency, power and area consumption. In the category of smallest cores, the Cortex-M family and particularly the aforementioned first in 2004 released Cortex-M3 raised a significant market position in the embedded ecosystem. Five years later, in 2009, the by now smallest family member Cortex-M0 was introduced, aiming lowest gate count and power consumption. In 40nm technology process, a total floorplan area of 0.007 mm2 is achieved but by providing a full 32-bit processor core [4].

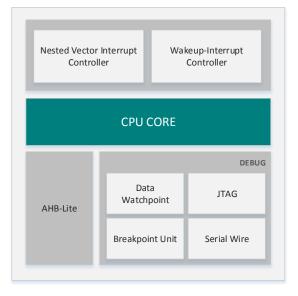

Figure 2.2: Main parts of a Cortex-M0 processor [4]

Figure 2.2 shows schematically the main components of the Cortex-M0 processor. The CPU is equipped with the *Nested Vectored Interrupt Controller* (NVIC) that receives events from peripherals and triggers on input an interruption of the program execution by calling and executing the assigned *interrupt service routine* (ISR). Cortex-M0 therefore supports up to 32 Interrupts. The *Wakeup Interrupt Controller* (WIC) handles this functionality in combination with a *Power Management Unit* (PMU) when the core is in power saving deep sleep mode, to buffer the requests while waking-up the core and then forwarding the interrupts. The WIC is a lightweight implementation with only combinatorial logic, to provide the minimal necessary functionality for wake-up, to be itself as power-efficient as possible. The AHB-Lite interface connects the processor to the other components on chip, such as the memories and the peripherals.

For efficient application development, a *Data Watchpoint* is provided to monitor variables or expressions. In addition with a Breakpoint Unit and the JTAG/Serial Wire access ports (*Debug Access Port* – DAP) debug functionality of the Cortex-M0 is served. The JTAG/Serial Wire access allows a complete access to the CPU core registers and the bus system, thus all system components. It can also be used to flash the system, besides popular implementation facilitating the simple UART or SPI interface.

### 2.3 Hardware Abstraction Layer

The increase of SoC design and therewith software complexity drives the demand of code reusability to hold the development time of a new application in an acceptable range. An answer is the concept of decoupling the interfaces between software and addressed hardware, by dividing the software in a hardware-dependent and hardware-independent part to challenge the requirement of portability [Jer05] [Pos03]. However, the term of hardware abstraction layer is a widespread and abstract treated topic of study in literature. By the ongoing evolving field of SoC development, and lately dominance of ARM in a former field of many share proprietary hardware architectures (see Chapter 2.2), the subject literature still has to find concrete consolidations in many aspects to avoid ambiguity. [Sun03] describes the hardware abstraction layer as all the software that is directly dependent on the underlying hardware, including boot code, context switch code and providing configuration and access to hardware resources. Thus, parts of this software have to be changed, whenever the hardware architecture is changed. The question of one standard in hardware abstraction for SoCs is clearly negated in this publication, reasoned by the application-specific hardware architecture design. However the possibility of a generic set of specific application programming interfaces (APIs) combined with a common HAL is considered or a possible focus on a suited HAL for specific application domains.

A more detailed approach on HAL definition is presented by [Han05] in a specific tree-layer hardware abstraction architecture design for wireless sensor networks, including a *Hardware Presentation Layer* (HPL) that interacts directly with the Hardware, a *Hardware Abstraction Layer* (HAL), the core component that abstracts specific devices into domain models (like alarm or analog-digital converter) and a *Hardware Interface Layer* (HIL) that provides the hardware-independent "typical" hardware service interfaces to applications.

In a now standard reference book on this topic, "Hardware-dependent software" [Eck09] a HAL is defined as a software layer that provides an abstract interface to access hardware resources, and typically divided into access, register, and functional shielding. Furthermore the code is divided into processor specific software code, e.g. enable interrupt vectors, and device drivers to access peripherals or power management. The proposed services are ANSI C integration to provide standard-C functions such as *printf()* or *fopen()*, the device drivers, a consistent interface to this services for the application layer, as well as system and device initialization. The overall advantage of using hardware abstraction to increase reusability and flexibility is shown on a proof-of-concept of a JPEG application, ported to different processors by using hardware abstraction.

This definition of the term hardware definition, as software stack that abstracts the hardware access from the application layer, is compliant to the following interpretation in the subchapter of standards and classification for HAL, as well as to the nowadays dominant ARM architecture, which will be topic of subchapter 2.3.2.

#### **Standards and Classifications**

[Bha13] presented an approach on separation of hardware abstraction in the following categories: (i) industry-standard, (ii) vendor-definied or (iii) user-definied. Industry-standards are rare, but for ex-

ample exist in the field of test and measurement equipment as part of the *Interchangeable Virtual Instruments* (IVI) standard, driven by an industry consortium called *IVI Foundation* [5]. IEEE Standards Association has an active project (P2415) on low power design and verification standard in development that "addresses energy proportionality through tight interplay between energy-oriented hardware and energy-aware software." [6] The project authorization request was approved in 2014 and expires in 2018. The overall goal is to provide a standard for well-connected energy oriented design flow.

Vendor-defined HALs are developed by hardware vendors, for reusing the application software on different projects, for example the Infineon *Automotive Open System Architecture* (AUTOSAR) which provides a standard for all layers of software in the automotive area, including the input/output hardware abstraction [7]. Another category of vendor-defined HALs, from the perspective of software, is operating system dependent ones. Software companies create their own abstraction designs, to use the operating system on all variations of hardware architectures, such as *Windows Embedded Compact* (former Windows CE) [12].

User-defined HALs follow in principle no specific design rules, but a consideration on various design aspects might seem expedient. The intended goal is a thin software component, that just encapsulates all functionality that is hardware-dependent, and an appropriate interface to provide it to the upper layers. In [Hel10] the authors describe a HAL design in two separated layers, the lower level device specific code and above an application specific layer, which provides functions for the application interface. According to [Ben15], the focus in development should be on core feature identification, avoiding an all-encompassing HAL, and be aware of an iteration process in development.

#### **Cortex Microcontroller Software Interface Standard (CMSIS)**

To abstract the complexity of the ARM architecture and make developing applications much easier, ARM provides the C-implemented hardware abstraction library CMSIS, vendor-independent and expanded broadly in related areas such as debugger interfaces, a real-time system operating API or a DSP library. The goal is better industry collaboration as well as accelerating software development projects that make use of ARM microcontrollers [9]. It is checked against MISRA C, a set of programming guidelines for critical systems, published by the *Motor Industry Software Reliability Association* (MISRA) [10].

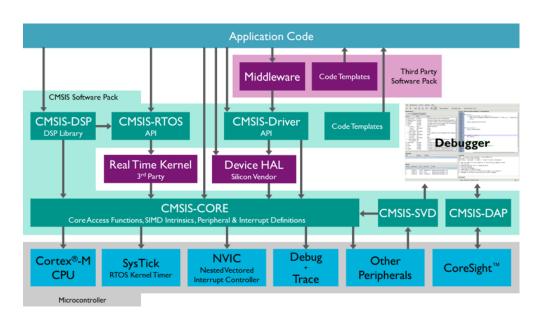

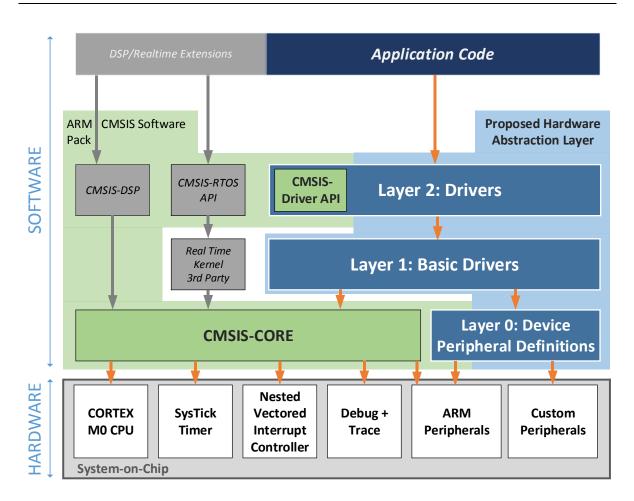

Figure 2.3: ARM CMSIS [9]

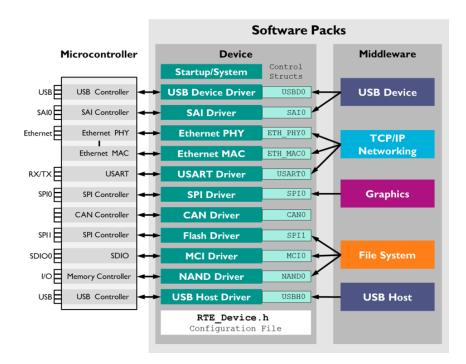

In figure 2.3 the components of the ARM CMSIS, as well as the interfaces and interconnection between them is visualized. On the bottom, the CMSIS-CORE block allows the hardware access by abstracting from writing bits to register addresses to name mappings. On the same level right-hand connected is the CMSIS-SVD (System View Description) block, which allows abstract description of peripheral devices in XML format for integration into the CMSIS Device family packs [11]. CMSIS-DAP (Debug Access Port) provides a standard communication between Debugger and ARM Cortex device via a USB to JTAG/SerialWire debug unit, which runs the DAP firmware for CoreSight Debug Access Port. Bottom-up arranged is the device HAL implemented by the silicon vendor, and optionally a (usually 3<sup>rd</sup> party) real time kernel when a real time operating system (RTOS) is in use. The CMSIS software pack in addition optionally serves a digital signal processing (DSP) library, containing basic signal processing functions, such as filters, matrix functionality or complex math functions. The CMSIS-RTOS API provides easy access to real-time features and makes middleware easier to adapt to the actual real-time kernel. The CMSIS-Driver API specifies standardized peripheral driver interfaces for applications or middleware, to promote reusability and abstract the actual peripheral implementations used, by categorizing in currently 11 different devices. Figure 2.4 simply illustrates the abstraction from physical components on the microcontroller up to middleware access and the logical abstracted units such as USB Device or Networking.

Figure 2.4: Peripheral driver Interfaces [11]

At last, beyond in Figure 2.3 complex systems may use additionally 3<sup>rd</sup> party middleware and code templates. Based on this hierarchical architecture, the application layer in the top is able to access the devices, independently from the actual physical hardware blocks implemented. In conclusion, this HAL design and features are consequently in line with the definition of hardware abstraction in the initial part of this chapter.

# 2.4 CMOS Power Consumption and Management Strategies

For wireless applications, power consumption is a major topic when for example a coin cell or energy harvesting determines low power requirements on the system-on-chip design to allow a longstanding lifetime. Apart from wireless applications, high integration density such as in modern multicore processors makes awareness to power consumption inevitable too. Dependent on the application, the behavior in uptime and sleep modes, as well as on technology reasons the strategy for power-saving can differ. With greater integration density, and decreasing sizes the dominant parts in dissipation changes. This chapter outlines the two fundamental parts of power dissipation in complementary metal-oxide-semiconductor (CMOS) technologies and the determining components, followed by an overview of common techniques to minimize power loss in low power design.

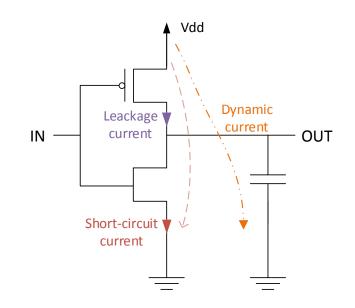

There are basically two parts that determine CMOS power dissipation. A static component, which does not exist in the ideal CMOS but has an impact in reality, describes the constant leakage when the CMOS component is not switched. Secondly, a dynamic dissipation appears when CMOS is switching states. The total dissipation is expressed in equation 1. Often read in literature, the dynam-

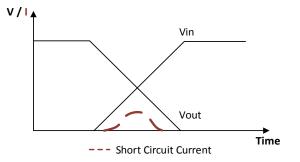

ic dissipation is further broken down in the short circuit current between  $V_{dd}$  and Ground and the loss of power in the dynamic load of the capacitance, see Figure 2.5.

$$P_{total} = P_{static} + P_{dynamic} = P_{static} + (P_{short} + P_{switch})$$

(1)

Figure 2.5: The three main components in CMOS power dissipation [Pan10]

#### **CMOS Static Power Dissipation**

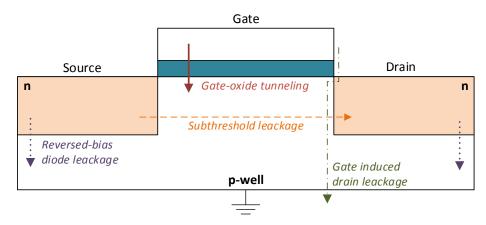

In theory CMOS has the major advantage over other technologies that power dissipation does not occur when the component is not switched, due to the complementary design with a P-type MOS (PMOS) and a N-type MOS (NMOS) transistor. This ideal behavior is shattered in reality by multiple parasitic leakage effects that cause current flow and therewith power dissipation. Figure 2.6 shows schematically the dominating effects that occur between the partly overlapping, different doped junction areas on an NMOS transistor.

Figure 2.6: NMOS Static Leakage: (i) Gate-oxide tunnelling (ii) Subthreshold leakage between source and drain; (iii) Reverse-biased diode leakage across parasitic diodes; (iv) Gate induced drain leakage between drain and substrate [Pan10]

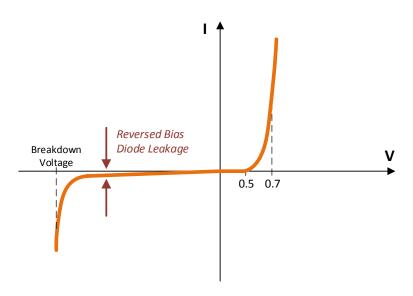

Reversed Bias Diode Leakage

The diodes formed between the diffusion regions and the substrate float a parasitic current based on the reverse bias of p-n junctions. The effect is shown graphically in Figure 2.7, represented by the offset current between 0V and the breakdown voltage. Overall the contribution to leakage is small compared to the other components, thus often neglected in power calculations.

Figure 2.7: Current-voltage characteristic of a p-n junction diode. The difference from the ideal zero current in reverse mode is the reversed bias diode leakage

Subthreshold Leakage

The weak-inversion effect describes the flow of current when the gate voltage is below the threshold voltage and therefore the transistor operates not in saturation mode. As a result free load carriers can move between drain and source. This effect is caused by diffusion, and becoming most significant with higher gate voltage, near to the threshold voltage. In addition there are several effects that are directly influencing the subthreshold voltage. *Drain-Induced Barrier Lowering* (DIBL) is a parasitic effect that explains the dependency and decrease of the threshold voltage on high drain voltage, while *direct punch-through* describes the approaching and "touching" of the depletion regions, thus is a subsurface version of DIBL.

Gate Oxide Tunneling

The downsizing of MOSFET and as a consequence smaller gate-oxide layers increases the electron tunneling rate through the physical energy barrier. With further ongoing downsizing this component is effecting in a higher contribution to the total share of static power dissipation.

Gate Induced Drain Leakage

In the overlap region of gate and drain region a current is generated caused by band-to-band tunneling. To limit this effect, restrictions are set on the oxide thickness and power supply voltage.

#### **CMOS Dynamic Power Dissipation**

This component of CMOS power loss occurs during switching activity, and described by the following two main causes:

Switching Power

Energy is dissipated by loading and unloading parasitic capacitances of the MOS transistors where a major part dissipates in heat. The derivation of switching power loss is as follows. Since

$$\mathrm{d}\mathbf{Q} = \mathbf{C} \cdot \mathrm{d}\mathbf{U} \tag{2}$$

and the relation between shifting of a load between two points with voltage difference U and the energy is

$$dE = U \cdot dQ \tag{3}$$

Inserting equation (2) in (3) and integrating over the supply (load) voltage leads to the energy supplied by the power source for charging:

$$E_{Load} = C \cdot V_{dd} \cdot \int_0^{V_{dd}} dV = C \cdot V_{dd}^2$$

(4)

The energy stored in the capacitance is the integration of the instantaneous charge during the load process, thus

$$E_{Capcity} = C \cdot \int_0^{V_{dd}} V \cdot dV = \frac{C \cdot V_{dd}^2}{2}$$

(5)

Comparing equation (4) and (5) shows a difference of  $E_{dissipation} = \frac{C \cdot V_{dd}^2}{2}$  that was dissipated in heat during the charge process.

To obtain the dissipation power the energy term is multiplied by the clock frequency f. Due to the fact that not all logic gates in a digital circuit switch in each clock period, an activity factor  $\alpha$  in the range from 0 to 1 is added to express the probability of switching the state.

$$P_{dissipation} = \frac{C \cdot V_{dd}^2}{2} \cdot f \cdot \alpha \tag{6}$$

Short-circuit current

Another dynamic dissipation effect is based on the finite rise and fall times of switching behavior in the used nMOS and pMOS transistor. As a consequence, for a short period both are ON at the same time, establishing a direct current path connecting the positive supply voltage ( $V_{dd}$ ) and Ground (GND).

Figure 2.8: Short-circuit current in CMOS caused by the finite switching time behaviour [Pan10]

#### **Techniques to reduce Power Consumption**

After working out the causes of power dissipation in CMOS technology, the question on how to minimize the effects is coming up. Several, nowadays standard techniques evolved which are consecutively explained.

Power Gating

The dissipation effects described in the previous chapter showed altogether a relation to the supply by a power source. To address the simple solution of "where is no power, there is no loss", power gating explains the deactivation of CMOS cells or in bigger scope of components in an MCU system, to fully disable power consumption in inactive mode, thus effectively get rid of all dissipation effects. When the component is needed again for operation the supply is being restored. Splitting up a SoC to shut down components is regularly realized by forming power domains, thus an always-powered-on domain and one or multiple domains for temporarily shut down.

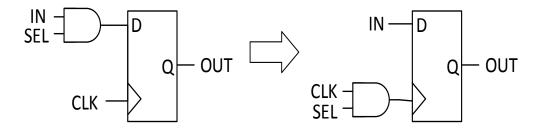

Clock Gating

As another approach to reduce dynamic power dissipation, clock gating addresses the problem that flip-flops are connected to the CLK and thus dissipate energy on every clock cycle. The simplest way to overcome this loss when the input data is not changed is by grouping flip-flops to functional units and transform the connection of the flip flop as seen in Figure 2.9 by AND connecting the SEL and CLK wire, thus only on activation the grouped flipflops dissipate power. A reduction of about 5-10% is possible [Pan10].

Figure 2.9: CLK passing to logic block only when selected [Pan10]

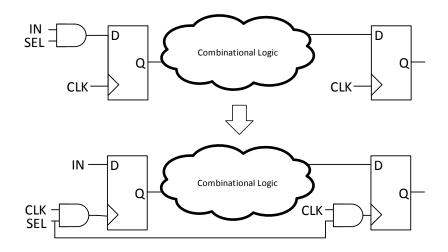

By adding more combinatorial logic to the design a more complex but higher reduction potential could be achieved. In a so called pipelined design an input change of the first stage determines the activation of the clock signal for the following flip-flops, see Figure 2.10.

Figure 2.10: Higher effectiveness of clock gating on pipelined designs [Pan10]

Voltage and Frequency Scaling

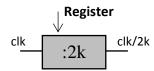

The dynamic switching power is squared proportional to the power supply voltage, thus a reduction in voltage can make significant decrease of power consumption possible. Frequency is direct proportional, but also has a direct proportion to voltage, thus both can be lowered together resulting in a cubic proportional power reduction. However the circuit delay will increase and must be considered to meet the system constraints. A common approach is to settle at design time, by adjusting voltage and frequency just to meet the necessary constraints and fixate for application. A regulative approach but less sophisticated is dynamic frequency scaling, see Figure 2.11, which is quite popular in embedded systems design, allowing for setting the CLK speed during execution, and adjusting just the frequency to the current work load and needed response time of the system. For example a system that just waits for an signal edge on an input pin and the processing is not time critical, a lower frequency could still be satisfying while lowering the overall power consumption.

Figure 2.11: A 2k clock divider to scale down frequency, configurable via a register

*Dynamic Voltage and Frequency Scaling* (DVFS) expresses the dynamic scaling during runtime to achieve lowest power consumption, while concurrently analyzing and meeting the systems performance constraints, for example by adaptive control, where previous configurations and the current system measurements are determining the next frequency and voltage configuration. DVFS for microcontrollers is mostly not suitable because of PLL instabilities and where peripherals use the (constant) processor clock in operation [Yiu15]. However, multiple supply voltage domains can still meet these requirements, but then additional level-shifters are needed to convert the signals between the different voltage levels.

#### **ARM** architectural Low-power Management

The ARM Cortex-M0 is designed for ultra-low power consumption, to be suitable for small and wireless applications. Besides the low gate count, ARM provides two built-in power modes to disable parts of the system, but leave the particular implementation details in the design of the particular system-on-chip. The predefined standard modes are (i) SLEEP, to stop the processor clock (HCLK) and (ii) DEEPSLEEP which stops the HCLK as well as turning off PLL and flash memory. The *deepsleep* bit in the system control register defines whether SLEEP or DEEPSLEEP mode is triggered when the associated sleep instructions WFI (wait for interrupt) or WFE (wait for event) are called. When the system is in sleep mode, the WIC takes over the basic functionality served by the disabled NVIC to power up the system again on allowed interrupt input. The WIC has only combinational logic therewith does not allow additional configuration. The interrupt mask is therefore copied to the WIC before the CPU system switches into a sleep mode.

For applications that just react on time distributed events, and shall then go back to sleep as fast as possible, the *System Control Register* provides the flag *sleep-on-exit*. After completing the handling of interrupts, the processor enters immediately sleep mode again.

### **2.5 Software Metrics**

A detailed background research on software measurements will found the knowledge for firmware comparability that is treated as a key topic within this thesis. Therefore the definition and delimitation of the terminology is quite important: (i) software testing addresses activities to find potential errors, defects bugs and failures in the software, (ii) source code analysis collects and examines information about possible future errors that are mostly classified as warnings but can result in hazards, and (iii) software metrics addresses the information collection regarding software characteristics, with measurements such as *Total Lines of Code* (TLoC) or complexity estimations [Zou10]. While the first two are related and were also part of the implementation tasks of this thesis, the benchmark and results is dependent on the survey of appropriate software attributes. The following literature review and a detailed insight on software attributes will allow a differentiated understanding and the ability to determine the necessary subset of metrics for embedded software.

Measuring all aspects of software and its interaction to the environment is still a challenging broad subject area. While single terms are differently used under the hypernym of software metrics, a commonly accepted classification and applicability yet accrued. From the comprehensive perspective of software project development [Vie14] [Gwa06] metrics can be divided into three categories:

- Product metrics measure the software quality by performance, complexity or size of the program. They can be further divided into internal (static) metrics that examine attributes of the product itself (code/binary) and external (dynamic) ones, including the interaction and execution within the hardware environment and user.

- Process metrics address testing, detection and fix of defects and can be used to improve software quality.

- Project metrics pertain to the quality of the project including the quantification of cost, productivity and the project schedule.

Product metrics can be divided into internal metrics, which only depend on the software itself and not on the execution, and external metrics that can only be measured with respect of the environment, in particular the machine environment and the user. While the first ones are usually easier and objectively measurable, the latter ones depend on subjective user perception and on sometimes difficult possibilities of accomplish measurements within the environment. In addition to mention, internal metrics are often used in early development stages, while external are evaluated (normally) on an almost completed product [Fen14]. ISO/IEC 9126 [14] addresses the development of a common understanding of project objectives by qualifying four parts: (i) a quality model with six abstract objectives (functionality, reliability, usability, efficiency, maintainability and portability), connected to (ii) internal metrics, (iii) external metrics and (iv) quality-in-use metrics for the final product deployment. The relation of this metrics is that in ideal the internal determine external metrics, and external determine the quality-in-use metrics.

Internal, static product attributes can be divided into five categories [Oli08]:

- (i) Coupling counts the links of a software module to other elements, is positive (min. 0 connections), does not increase on multiple module relations, and is additive: merging two modules results in the sum of the single coupling values. Metrics describing this attribute allow conclusions on encapsulation, reuse and maintainability, in particular by examining function calls and the number of instances to measure the relationship between components. *Afferent couplings* (Ca) counts number classes in other packages that depend on classes in the current package, and *Efferent Couplings* (Ce) number of classes on which classes from the current package depend, and can be used in modular programming, first proposed by [Mar02]. In this context, packages are groups of classes in object oriented programming languages. In addition, *Instability* describes the ratio of efferent coupling to the sum of couplings (Ca + Ce), where zero represents total stability of a package.

- (ii) Cohesion, determines the degree of interaction within one module. It is commonly a normalized value between 0 to 1, where 0 means that all contents are not linked, adding links is positive monotone, and the result of merging two modules cannot be greater than the maximum of the single module values. Metrics can give information weather modules (e.g. classes) should be separated in subclasses. For example, *Lack of Cohesion of Methods* (LCOM) was first introduced by Chidamber and Kemerer by forming pairs of methods and shared data [Chi94]. A high number indicates a poor design, and motivating the question of splitting a module. This metric can be found in multiple variations.

- (iii) Extendibility and reuse measurements qualify the degree of extension feasibility and the ease of using parts of the software in other projects. It includes *Abstractness* which is the ratio of the number of abstract classes to total number of classes in a package. Another metric is *Distance from the Main Sequence* [Mar02], describing the balance of abstractness to stability of a package by calculating

$$D = |A + I - 1|$$

(7)

with *Abstractness* A and *Instability* I and a favored result against zero, indicating that the package is exactly on the main sequence.

Population (size) metrics include the popular Total Line Of Code metric, Number of Attributes, Classes, Interfaces, Methods, Packages, Parameters, Static Attributes or Static Methods which strongly determine performance and memory footprint.

A substantial attribute of code is the size of the program code, which can be commonly counted in *Lines of Code* (LOC). This metric has to be differentiated, in particular of what to do with blank and comment lines, with headers and multiple statements in one line. The commonly accepted approach on comments and blank lines is to neglect them, and counting the *Source Lines of Code* (SLOC). This seems reasonable to decide how much space a program allocates in memory, but in terms of measuring effort for example, commented lines are also carrying programming efforts [Fen14]. The count of commented lines is the *Comment Lines of Code* (CLOC) and is related to the other numbers by

$$Total Lines Of Code (TLOC) = SLOC + CLOC$$

(8)

Furthermore, the SLOC without headers and footers (incl. *define* and *import* statements, brackets) is known as *None-Commented Lines of Code* (NCLOC) or *Effective Lines of Code* (ELOC). *Logical SLOC* (LLOC) is tied to specific programming languages and counts the number of executable statements, to solve the problem how to proceed with multiple statement lines.

Another benchmark to determine software size is *Function Point Analysis* (FPA), by considering amount of functionality as indicator. It quantifies functionality of the software with the focus on the value for the users, by extracting functions, classifying and assigning weights.

(v) Complexity, quantifies the degree of internal code interactions. The popular *McCabe Cyclomatic Complexity* algorithm [McC83], calculates the flow through code by incrementing a count variable each time a branch occurs. It computes a control flow graph of a software code, where the nodes represent program statements and the directed edges the relation that the second statement is executed after the first one. Control structures, such as IF, ELSE, FOR etc. create multiple independent paths through the program, which can be counted as complexity M

$$Complexity M = E - N + 2P \tag{9}$$

with number of edges E, the number of Nodes N and the number of connected components P.

The *Halsted Complexity Metrics* [Hal77] proceed from the assumption that code can be interpreted as a sequence of operators and operands, and includes eight metric calculations. First the *Number of Operators* (N1), *Number of Operands* (N2), *Number of unique Operands* (N2), *Number of unique Operators* (n1) and *Number of unique Operands* (n2) are counted. Operators are all operators defined in the C-standard (!, !=, +, -, etc.), storage and type qualifiers and reserved keywords. Control structures (if, else, switch, for, etc.) are treated differently,

by describing the alternative program flows. Operands are identifiers, type names, type specifiers (bool, int, etc.) and constants.

The Vocabulary Size (n) is the sum of distinct operators and distinct operands.

$$Vocabulary \ size \ (n) = n1 + n2 \tag{10}$$

The Program Length (N) is the total sum of operators and operands.

$$Program \, length(N) = N1 + N2 \tag{11}$$

The *Program Volume* (V) is the program length two times the logarithm of vocabulary size and represents the implementation content of the program. Per function this metric should result in a value between 20 and 1000, a greater number means the function ought to be divided up; the volume of a parameter-less empty function is 20.

Program volume (V) = N

$$* \log 2$$

(n) (12)

The *Difficulty Level* (D) or error proneness is driven by the new operators and repeated operands.

Difficulty level (D) =

$$\left(\frac{n1}{2}\right) * \left(\frac{N2}{n2}\right)$$

(13)

The *Program Level* (L) is the inverse of the *Difficulty Level*. A more difficult (error prone) program is equal to a low programming level.

Program level (L) =

$$\frac{1}{D}$$

(14)

The Implementation Effort (E) is the proportion of difficulty and program volume.

Implementation Effort (E) =

$$V * D$$

(15)

The *Implementation Time* can be determined by dividing the implementation effort with a constant of 18. Halstead proposed this approximation for time in seconds.

Implementation Time (T) =

$$\frac{E}{18}$$

(16)

The *Effort* of a program directly affects the number of bugs in software.

Number of delivered bugs (B) =

$$\frac{E^{\frac{2}{3}}}{3000}$$

(17)

Additional complexity metrics are *Nested Block Depth* and *Weighted Methods per Class* to indicate alternative execution flows, element granularity and nested execution. Fenton et.al propose the importance of understanding that a single number cannot identify the complexity of a whole system, but the combination of multiple metrics can together accomplish in an encompassing understanding [Fen14].

External, dynamic product attributes describe the quality of software and are related to the environment, in particular the machine environment and the user. As a consequence, this embeddedness and interaction makes measurements much more complex as on the internal attributes which only describe the software itself. The common external attributes of software are

(i) Functionality is defined by ISO/IEC 9126 as "A set of attributes that bear on the existence of a set of functions and their specified properties. The functions are those that sat*isfy stated or implied needs.*" The proper functionality is related to the defects that are included in code, and often seen as the one and only major topic by developers in the hypernym of software quality. Therefore *Defect Density* is the ratio of detected defect count to total size of software

$$Defect densit = \frac{Number of detected defects}{Software size}$$

(18)

This information can be used to decide if software is ready for deployment, or on a long-term release to assess post hoc the quality level of the release.

(ii) Efficiency addresses the consumption of resources and in term of software can be measured by the execution performance on the target hardware environment.

ISO/IEC 25010 2011 defines: "*Efficiency is resources expended in relation to the accuracy and completeness with which users achieve goals*".

In this context where software is executed on a hardware system, physical metrics determine the resource consumption. Therefore, the count of program and data memory determines the memory footprint of the software during runtime. Obviously there is a relation to the static code size population metrics, examined in [Oli08]. For embedded applications the *Energy Consumption* and the *Cycles for Execution* are additional meaningful numbers to evaluate software efficiency.

(iii) Usability describes the interaction of the software with the user and defined in ISO/IEC 25010 2011: "Usability is the degree to which a product or system can be used by specified users to achieve specified goals with effectiveness, efficiency and satisfaction in a specific context of use."

A simple metric to determine the effectiveness of software can be realized by setting a set of tasks to multiple users, and calculating

$$Effectiveness = \frac{\text{Number of tasks successfully completed}}{\text{Total number of tasks}} \cdot 100\%$$

(19)

Efficiency can be calculated by measuring the time users take to complete given tasks and relate this result to the time experts take. Satisfaction, as subject sensation is commonly identified by questionnaires.

- (iv) Maintainability addresses the change of software after deployment, and defined in ISO/IEC 25010 2011: "Maintainability is the degree of effectiveness and efficiency with which a product or system can be modified by the intended maintainers". One measurement is to address ratio of implementation attributes to code, number of module or methods implemented. To indicate the changes by comparing a priori and post hoc status, internal metrics are applied on the code modifications. In this context, size and complexity are major features where McCabe suggested the guideline, that for proper maintainability the cyclomatic number of a module is not allowed to be greater than 10 [McC83]. The Maintainability Index (MI) represents, by including LOC, McCabe CC and the Halstead Metric, the ease of maintaining the software code.

- (v) Reliability is the property of a system that indicates how safe the providing of functionality is for a time period. ISO/IEC 25010 2011 defines: *"Reliability is the degree to*

which a system, product or component performs specified functions under specified conditions for a specified period of time".

It is a well-studied quality attribute, by the common important interest of software quality in high reliability by often ignoring other attributes. Based on probability theory and prediction models, various measures can be determined. The *Rate of Occurrence of Failures* (ROCOFs) is the number of failures in a given time interval. To describe how long a system runs successfully between the occurrences of failures, *Mean Time between Failures* (MTBF) is

$$MTBF = MTTF + MTTR$$

(20)

with *Mean Time to Failures* (MTTF), the expected value of the failure distribution function, and *Mean Time to Repair* (MTTR), an estimated or empirically determined value how long it takes to locate the error and repair the system. The *Availability* of a system is then simply calculated by

Availability =

$$\frac{\text{MTTF}}{\text{MTTF+MTTR}} \cdot 100 \%$$

(21)

(vi) Portability qualifies how easy the software can be ported to another hardware or user environment. ISO/IEC 25010 2011 defines: "Portability degree of effectiveness and efficiency with which a system, product or component can be transferred from one hardware, software or other operational or usage environment to another".

ISO/IEC 9126 [14] describes potential portability compliance metrics as a measure of transfer ability to another environment by assessing applied standards in the software to total available ones.

Summed up, the list of potential metrics for the comparison of the HAL variants is taken together in Table 2-1. In general these metrics can be applied to any type of software. However, the particular application characteristics, the hardware environment, the type of user interaction and of course the objectives of interest will result in a subset of this comprehensive list.

|                     | Name                                                                                                                                              | Attribute             |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|                     | Lines Of Code (LOC)                                                                                                                               | Code Size             |

|                     | Number of<br>Parameters (NOP), Methods (NOM), Classes (NOC), Interfaces (NOI), Packages (NOP),<br>Static Attributes (NOSA), Static Methods (NOSM) | Code Population       |

|                     | Function Point Analysis                                                                                                                           | Code Size             |

|                     | Halstead Metrics                                                                                                                                  | Code Size, Complexity |

|                     | McCabe Cyclomatic Complexity (McCabe CC)                                                                                                          | Complexity            |

|                     | Method Lines Of Code (MLOC)                                                                                                                       | Complexity            |

| Metrics W<br>A<br>E | Nested Block Depth                                                                                                                                | Complexity            |

|                     | Weighted Methods per Class (WMC)                                                                                                                  | Complexity            |

|                     | Afferent Coupling (Ca)                                                                                                                            | Coupling              |

|                     | Efferent Coupling (Ce)                                                                                                                            | Coupling              |

|                     | Instability (I): Ce / (Ca + Ce)                                                                                                                   | Coupling              |

|                     | Lack Of Cohesion Of Methods (LCOM)                                                                                                                | Cohesion              |

|                     | Abstractness                                                                                                                                      | Extendibility / Reuse |

|                     | Depth of Inherence Tree (DIT)                                                                                                                     | Extendibility / Reuse |

|                     | Number Of Overridden Methods (NOVM)                                                                                                               | Extendibility / Reuse |

| External<br>Metrics | Defect Density                                                                                                                                    | Functionality         |

|                     | Maintainability Index                                                                                                                             | Maintainability       |

|                     | Effectiveness Metrics                                                                                                                             | Usability             |

|                     | Efficiency Metrics                                                                                                                                | Usability             |

|                     | Satisfaction Metrics                                                                                                                              | Usability             |

|                     | Rate of Occurrence of Failures (ROCOF)                                                                                                            | Reliability           |

|                     | Mean Time Between Failure (MTTF)                                                                                                                  | Reliability           |

|                     | Portability Compliance Metrics                                                                                                                    | Portability           |

|                     | Program Memory                                                                                                                                    | Efficiency            |

|                     | Data Memory                                                                                                                                       | Efficiency            |

|                     | Energy Consumption                                                                                                                                | Efficiency            |

|                     | Clock Cycles                                                                                                                                      | Efficiency            |

Table 2-1: State-of-the-art software metrics

# 2.6 Related Work