## DISSERTATION

## Optoelectronic Circuits in 40nm CMOS Technology

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

Univ. Prof. Dr.-Ing. Horst Zimmermann am Institute of Electrodynamics, Microwave and Circuit Engineering

> eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

> > von

M.Sc. Mohammed Hassan

Matrikelnummer: 1028247 Wexstrasse 22/2/8, 1200 Wien, Österreich aus Kairo, Ägypten

## **Declaration of Authorship**

I, Mohammed Hassan, declare that this thesis titled, 'Optoelectronic Circuits in 40nm CMOS Technology' and the work presented in it is my own and the work done by other authors is appropriately cited.

Signed:

Date: Wien, im March 18, 2015

"He who performs not practical work nor makes experiments will never attain to the least degree of mastery."

Jabir-Ibn-Hayyan

## Abstract

The rapidly increasing interest in high speed access networks and large capacity communication encouraged the advancement of low-cost optical transmission systems. The tendency to design highly integrable and low cost broadband optical systems, makes it desirable to realize optoelectronic circuits such as transimpedance amplifiers (TIAs) and laser diode drivers (LDDs) in CMOS technology. Since advanced CMOS technology introduces challenges regarding the design of such circuits, the need of lower power dissipation and higher integrability motivates further research on new circuit topologies.

This dissertation shows that nanometer CMOS technology can be used to design two of the most vital blocks in a typical optical transmission system, namely, the TIA in the optical receiver and LDD in the optical transmitter. Main focus of this thesis is to propose new topologies to overcome the technology limitations and allow the implementation of low power compact TIAs and a high voltage LDD. The circuits are all designed in standard 40nm CMOS technology.

On the receiver side, three novel different inductorless TIAs are presented. For measurement purposes, the TIAs are integrated with a chain of voltage amplifiers and a 50 $\Omega$  output buffer. The first TIA is implemented using a push pull current mirror (PPCM) with a feedback resistor. Experimental results show that this TIA achieves a power efficiency of 0.324 mW/Gb/s from a 1.2V supply at a maximum data rate of 10Gb/s. The whole design occupies an active area of 51×96  $\mu m^2$ . The second TIA is implemented using a common drain active feedback (CDAF). Measurement results show that this TIA acquires a power efficiency of 0.3 mW/Gb/s from a 1.2V supply at a maximum data rate of 8Gb/s. The full design occupies an active area of 33×101  $\mu m^2$ . The third TIA introduces a regulated cascode TIA with an active feedback (RGCAF). Experimental results show that the TIA achieves a power efficiency of 0.24mW/Gb/s from a 1.2V supply at a maximum data rate of 10Gb/s. The whole design occupies an active area of 33×101  $\mu m^2$ . Supply at a maximum data rate of 8Gb/s. The full design occupies an active area of 0.24mW/Gb/s from a 1.2V supply at a maximum data rate of 10Gb/s. The whole design occupies an active area of 44×89  $\mu m^2$ . In comparison with the state-of-the-art the proposed TIAs show a competitive power efficiency while occupying minimum chip area.

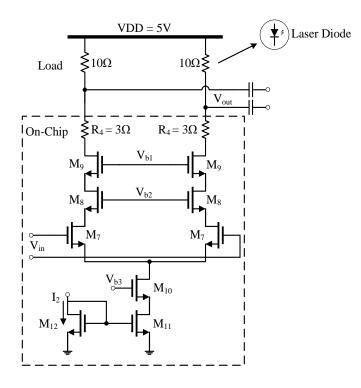

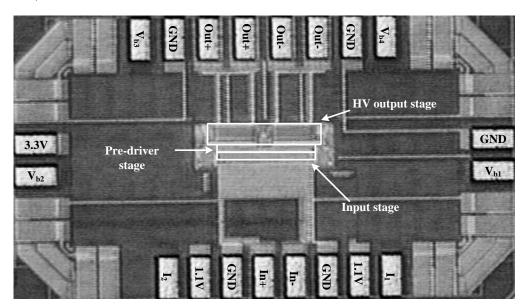

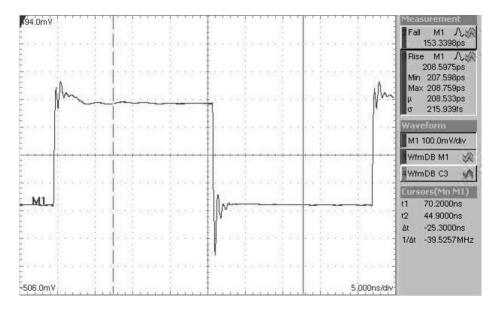

On the transmitter side, a high voltage LDD is implemented. An open drain double cascode fully differential structure is used to provide a high modulation current of up to 80mA and to guarantee a reliable operation of the devices under high voltage condition. To reduce power consumption, the LDD is supplied by 1.1V for the pre-driver and 5V for the output stage. Measurement results show a step response with rise and fall times (10%- 90%) of 209ps and 153ps, respectively. Therefore the LDD can operate at a data rate of 3Gb/s.

## Kurzfassung

Das ansteigende Interesse an Hochgeschwindigkeitsnetzwerken und Kommunikation mit hohen Kapazitätsanforderungen animiert die Weiterentwicklung von preiswerten, optischen Übertragungssystemen. Die Tendenz solche hochintegrierbaren Übertragungssysteme anzuwenden, macht es wünschenswert optoelektronische Schaltungen wie Transimpedanzverstärker (TIAs) und Laserdiodentreiber (LDDs) in CMOS-Technologie zu entwerfen. Da diese Nanometer-CMOS-Technologie neue Herausforderungen bezüglich Design solcher Schaltungen mit sich bringt, wird weiterführende Forschung an neuen Schaltungstopologien wegen kleiner werdender Leistungsaufnahme und höherer Integrierbarkeit vorangetrieben.

Diese Dissertation zeigt auf, dass in einer Nanometer-CMOS-Technologie mit einem TIA in der optischen Empfängereinheit und einem LDD in der optischen Sendeeinheit zwei essentielle Blöcke in einem typischen optischen Übertragungssystem entwickelt werden können. Ferner konzentriert sich diese Arbeit auf Vorschläge neuer Schaltungstopologien um Technologielimits zu überwinden und die Implementierung von kompakten und sparsamen TIAs und Hochvolt-LDDs zu ermöglichen. Die Schaltungen sind in einer standard 40nm CMOS-Technologie realisiert.

Auf der Empfängerseite werden drei verschiedene, spulenlose TIAs präsentiert. Zu Messzwecken sind die TIAs in einer Kette von Spannungsverstärker mitsamt einem 50 $\Omega$ Ausgangstreiber integriert. Der erste TIA ist als push-pull Stromspiegel (PPCM) mit einem Rückkopplungswiderstand ausgeführt. Messergebnisse zeigen einen Wirkungsgrad von 0.324 mW/Gb/s bei einer Versorgungsspannung von 1.2V und einer maximale Datenrate von 10Gb/s. Das gesamte Design benötigt eine aktive Fläche von 51×96 $\mu$ m<sup>2</sup>. Der zweite TIA wurde als 'common drain' aktives Feedback (CDAF) verwirklicht. Der Wirkungsgrad liegt laut Messungen bei 0.3 mW/Gb/s. Die Versorgungsspannung beträgt 1.2V und ergibt eine maximale Datenrate von 8Gb/s. Die TIA-Schaltung benötigt eine aktive Fläche von 33×101 $\mu$ m<sup>2</sup>. Im Vergleich mit dem heutigen Stand der Technik zeigen alle TIAs einen konkurrenzfähigen Wirkungsgrad bei minimaler Chipfläche.

Seitens des Senders wurde ein Hochvolt-LDD implementiert. Um sowohl eine hohe Aussteuerung von bis zu 80mA, als auch einen verlässlichen Betrieb unter Hochvoltbedingungen gewährleisten zu können, wurde eine komplett differenzielle, 'open drain' -Doppelkaskodenstruktur verwendet. Zur Stromeinsparung wird der LDD mit 1.1V für die Vorstufe und mit 5V für die Endstufe versorgt. Die Messergebnisse zeigen eine Sprungantwort mit Anstiegs- bzw. Abfallzeiten (10% - 90%) von 209ps bzw. 153ps. Dadurch kann der LDD mit einer Datenrate von 3Gb/s betrieben werden.

## Acknowledgements

It is my pleasure to take this opportunity to express my heartfelt gratitude to the people who have helped and supported me during my PhD. studies. Without their support, my research would not have been successfully completed on time.

I gratefully acknowledge my supervisor Univ.Prof.Mag.rer.nat.Dr.techn. Horst Zimmermann for his advice in crucial and serious issues in this thesis. It has been a unique privilege to be in his group, and undoubtedly the credibility and prestige of his name will continue to open doors for me in the future.

I would like to record my gratitude and thanks to Dr. Reinhard Enne, Dr. Bernhard Goll, Dr. Mohammed Atef and Dr. Vladimir Milovanovic for their valuable guidance in design and measurements throughout my thesis. Their strong experience in analog circuit design have allowed them to focus in the critical and interesting issues of any problem.

I would also like to offer my regards and thanks to all my colleagues in the circuit engineering group at the Institute of Electrodynamics Microwave and Circuit Engineering for their technical support and the helpful discussions.

This work was funded by the Austrian Federal Ministry for Transport, Innovation and Technology (BMVIT) and Lantiq Austria GmbH. In this context special gratitude goes to the involved organizations which made the necessary investigations for this doctoral thesis possible.

I would like to extend my appreciation to my parents especially my father, mother and sisters for their unconditional love, support and continuous encouragement throughout my thesis.

I would also like to express my sincere gratitude to my brothers and closest friends Mohammed Hamouda and Yahia Hassan for their support and advice not only through this thesis but also throughout my life.

Finally, I would express my gratitude to my fiancèe Yara for her encouragement and motivation to finish this thesis.

## Contents

| Declaration of Authorship<br>Abstract<br>Kurzfassung<br>Acknowledgements |     |                                      |    |  |                 |       |               |    |  |  |

|--------------------------------------------------------------------------|-----|--------------------------------------|----|--|-----------------|-------|---------------|----|--|--|

|                                                                          |     |                                      |    |  | List of Figures |       |               |    |  |  |

|                                                                          |     |                                      |    |  | Li              | st of | <b>Fables</b> | xv |  |  |

|                                                                          |     |                                      |    |  | 1               | Intr  | oduction      | 1  |  |  |

|                                                                          | 1.1 | Motivation                           | 1  |  |                 |       |               |    |  |  |

|                                                                          | 1.2 | Optical Link Architecture            | 2  |  |                 |       |               |    |  |  |

|                                                                          | 1.3 | Thesis Objectives                    | 3  |  |                 |       |               |    |  |  |

|                                                                          | 1.4 | Thesis Outline                       | 4  |  |                 |       |               |    |  |  |

| 2                                                                        | Fun | lamentals of Optoelectronic circuits | 7  |  |                 |       |               |    |  |  |

|                                                                          | 2.1 | Transimpedance Amplifiers            | 7  |  |                 |       |               |    |  |  |

|                                                                          |     | 2.1.1 General Concept                | 7  |  |                 |       |               |    |  |  |

|                                                                          |     | 2.1.2 Open Loop TIA                  | 9  |  |                 |       |               |    |  |  |

|                                                                          |     | 2.1.2.1 Transfer Function            | 9  |  |                 |       |               |    |  |  |

|                                                                          |     | 2.1.2.2 Noise Analysis               | 11 |  |                 |       |               |    |  |  |

|                                                                          |     | 2.1.3 Shunt Shunt Feedback TIA       | 12 |  |                 |       |               |    |  |  |

|                                                                          |     | 2.1.3.1 Transfer Function            | 12 |  |                 |       |               |    |  |  |

|                                                                          |     | 2.1.3.2 Noise Analysis               | 14 |  |                 |       |               |    |  |  |

|                                                                          | 2.2 | Laser Diode Drivers                  | 16 |  |                 |       |               |    |  |  |

|                                                                          |     | 2.2.1 General Concept                | 16 |  |                 |       |               |    |  |  |

|                                                                          |     | 2.2.2 LDD Circuit Concept            | 18 |  |                 |       |               |    |  |  |

|                                                                          |     | 2.2.2.1 Output Stage                 | 18 |  |                 |       |               |    |  |  |

|                                                                          |     | 2.2.2.2 Predriver                    | 19 |  |                 |       |               |    |  |  |

|                                                                          |     | 2.2.2.3 Back Termination             | 20 |  |                 |       |               |    |  |  |

| 3 | State of the Art              | <b>21</b> |

|---|-------------------------------|-----------|

|   | 3.1 Transimpedance Amplifiers | 21        |

|   | 3.2 | Laser            | Diode Dr   | ivers                                         | 28 |

|---|-----|------------------|------------|-----------------------------------------------|----|

| 4 | CM  | OS Te            | chnolog    | y a                                           | 33 |

|   | 4.1 | Scalin           | g in CMC   | OS Technology                                 | 33 |

|   |     | 4.1.1            | Constan    | t Electric Field Theory                       | 33 |

|   |     | 4.1.2            | Nanome     | ter CMOS Scaling                              | 35 |

|   | 4.2 | Challe           | enges of N | anometer CMOS Technology in Analog Circuits   | 36 |

|   | 4.3 | $40 \mathrm{nm}$ | CMOS T     | echnology                                     | 38 |

|   |     | 4.3.1            | MOSFE      | T Transfer Characteristics                    | 39 |

| 5 | Rea | lizatio          | n of Op    | toelectronic Circuits 4                       | 13 |

|   | 5.1 | Transi           | impedanc   | e Amplifiers                                  | 43 |

|   |     | 5.1.1            | Push Pu    | Ill Current Mirror TIA                        | 43 |

|   |     |                  | 5.1.1.1    | PPCM Theory                                   | 43 |

|   |     |                  | 5.1.1.2    | PPCM Complete Optical Receiver                | 47 |

|   |     |                  | 5.1.1.3    | Simulation Results                            | 50 |

|   |     |                  | 5.1.1.4    | Chip Layout                                   | 52 |

|   |     |                  | 5.1.1.5    | Measurement Results                           | 53 |

|   |     |                  | 5.1.1.6    | Summary                                       | 55 |

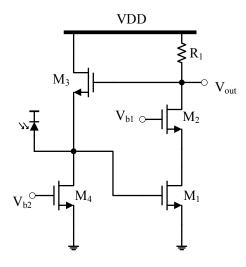

|   |     | 5.1.2            | Commo      | n Drain Active Feedback (CDAF) TIA            | 56 |

|   |     |                  | 5.1.2.1    | CDAF TIA Theory                               | 56 |

|   |     |                  | 5.1.2.2    | CDAF Complete Optical Receiver                | 59 |

|   |     |                  | 5.1.2.3    | Simulation Results                            | 60 |

|   |     |                  | 5.1.2.4    | Chip Layout                                   | 62 |

|   |     |                  | 5.1.2.5    | Measurement Results                           | 63 |

|   |     |                  | 5.1.2.6    | Summary                                       | 66 |

|   |     | 5.1.3            | Regulat    | ed Cascode with Active Feedback (RGCAF) TIA 6 | 67 |

|   |     |                  | 5.1.3.1    | RGCAF Theory                                  | 67 |

|   |     |                  | 5.1.3.2    | RGCAF Complete Optical Receiver               | 70 |

|   |     |                  | 5.1.3.3    | Simulation Results                            | 71 |

|   |     |                  | 5.1.3.4    | Chip Layout                                   | 74 |

|   |     |                  | 5.1.3.5    | Measurement Results                           | 75 |

|   |     |                  | 5.1.3.6    | Summary                                       | 77 |

|   |     | 5.1.4            | Compar     | $\operatorname{ison}$                         | 79 |

|   | 5.2 | Laser            | Diode Dr   | iver                                          | 80 |

|   |     | 5.2.1            | High Vo    | ltage Laser Diode Driver                      | 80 |

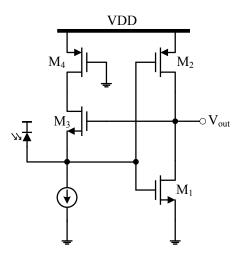

|   |     |                  | 5.2.1.1    | Proposed Laser Driver Design                  | 80 |

|   |     |                  | 5.2.1.2    | Input Stage and Predriver                     | 81 |

|   |     |                  | 5.2.1.3    | LDD's Output Stage                            | 82 |

|   |     |                  | 5.2.1.4    | Measurement Results                           | 33 |

|   |     |                  | 5.2.1.5    | Summary                                       | 85 |

| 6 | Con | clusio           | n          | ٤                                             | 37 |

89

# List of Figures

| 1.1  | Optical link architecture                                               | 3  |

|------|-------------------------------------------------------------------------|----|

| 2.1  | TIA using a simple resistor.                                            | 8  |

| 2.2  | Common gate TIA.                                                        | 9  |

| 2.3  | Common gate TIA small signal model                                      | 10 |

| 2.4  | Noise model of CG TIA                                                   | 11 |

| 2.5  | Shunt shunt feedback TIA.                                               | 13 |

| 2.6  | CMOS Shunt shunt feedback TIA.                                          | 14 |

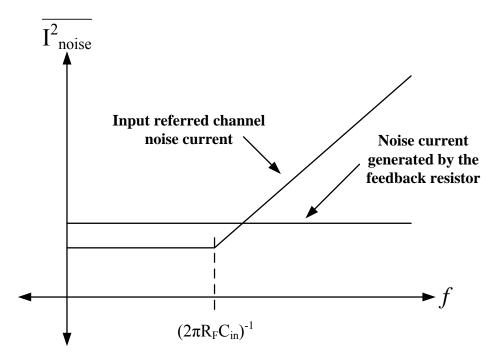

| 2.7  | NMOS channel noise and feedback resistor noise spectrums                | 16 |

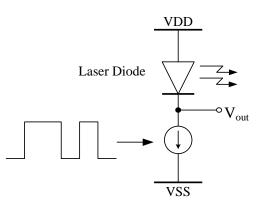

| 2.8  | Ideal model of laser diode driver as a switching current source.        | 17 |

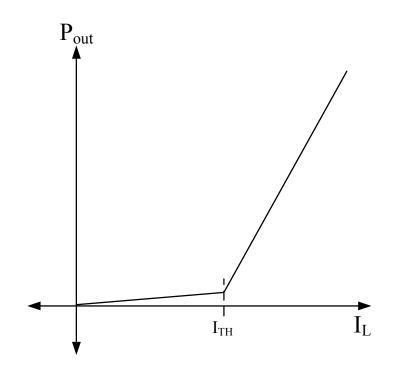

| 2.9  | The power/current characteristic curve of the laser diode               | 17 |

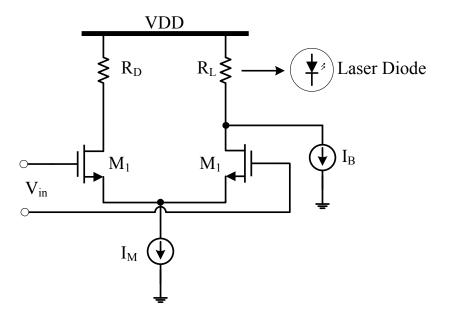

| 2.10 | Simple laser diode driver circuit.                                      | 18 |

| 3.1  | Regulated Cascode CMOS TIA                                              | 21 |

| 3.2  | The pseudo differential TIA with a RGC input stage proposed in [7]      | 22 |

| 3.3  | Common gate feedback TIA presented in [19]                              | 23 |

| 3.4  | A feedback common gate (CG) TIA introduced in [25]                      | 24 |

| 3.5  | A RGC TIA with gain reuse introduced in [12]                            | 25 |

| 3.6  | A current mode TIA with active feedback [26].                           | 25 |

| 3.7  | TIA in parallel configuration for bandwidth enhancement [31].           | 26 |

| 3.8  | The low power RGC TIA present in [1].                                   | 27 |

| 3.9  | Laser diode driver (LDD) proposed in [47].                              | 28 |

| 3.10 | LDD using active inductive peaking and pre-emphasis techniques in [6].  | 29 |

| 3.11 | LDD with a push-pull source follower preamplifier proposed in [24]      | 29 |

| 3.12 | The proposed LDD architecture in [11].                                  | 30 |

| 3.13 | 10Gb/s LDD presented in [23].                                           | 31 |

| 3.14 | LDD output stage with thick oxide cascode transistors shown in [28]     | 31 |

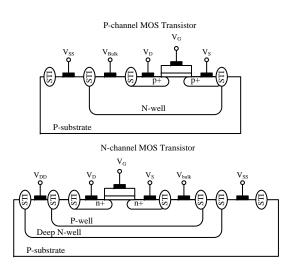

| 4.1  | Cross section of NMOS and PMOS transistors in 40nm triple well technol- |    |

|      | ogy                                                                     | 37 |

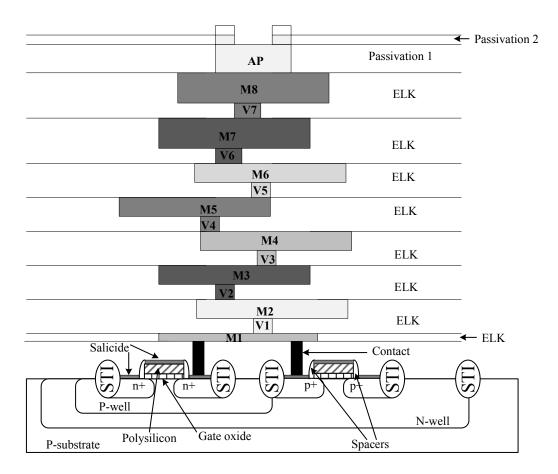

| 4.2  | Cross section of low power 40nm CMOS technology                         | 38 |

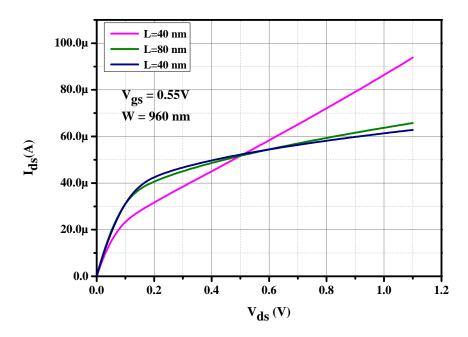

| 4.3  | NMOS output transfer characteristics for various gate length L          | 39 |

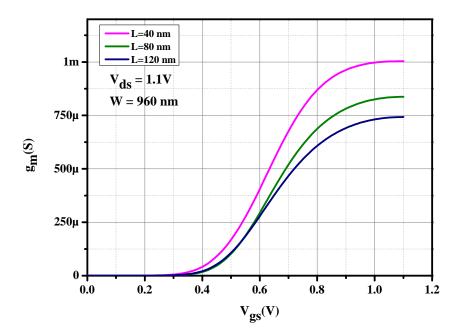

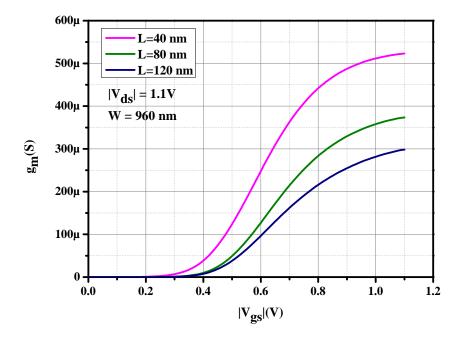

| 4.4  | NMOS transconductance $g_m$ for various gate length L                   | 40 |

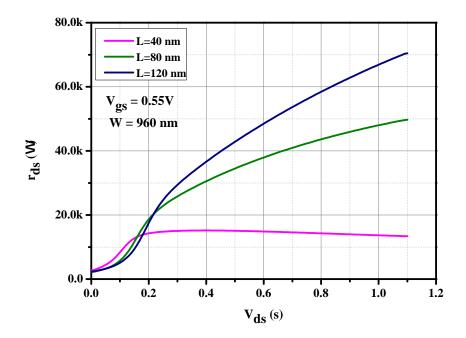

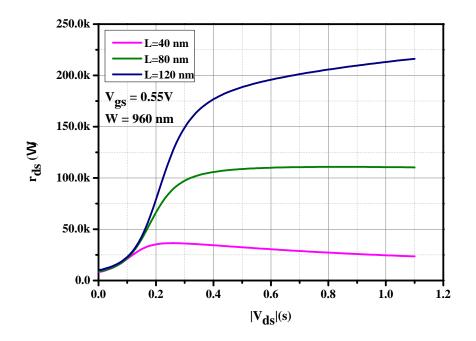

| 4.5  | NMOS output resistance $R_{ds}$ for various gate length L               | 40 |

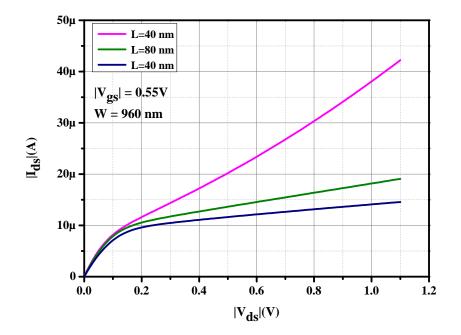

| 4.6  | PMOS output transfer characteristics for various gate length L          | 41 |

| 4.7  | PMOS transconductance $g_m$ for various gate length L                   | 41 |

| 4.8  | PMOS output resistance $R_{ds}$ for various gate length L               | 42 |

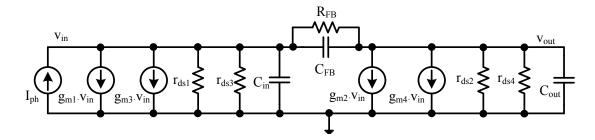

| 5.1  | NMOS current mirror TIA.                                                | 44 |

| 5.2         | Push pull current mirror (PPCM) TIA                                                                                                          | 44       |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.3         | Small signal model of the PPCM TIA                                                                                                           | 45       |

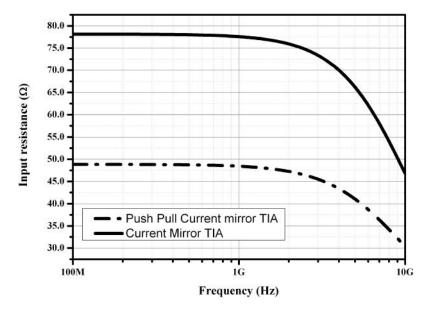

| 5.4         | Comparison of the input resistance of the two current mirror TIAs                                                                            | 46       |

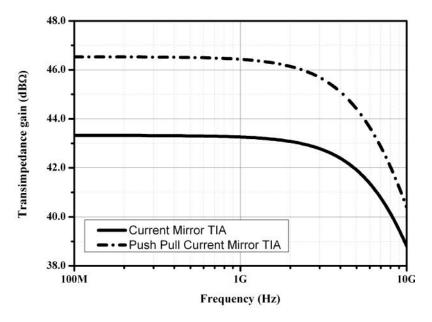

| 5.5         | Comparison of the transimpedance gains of the two current mirror TIAs.                                                                       | 46       |

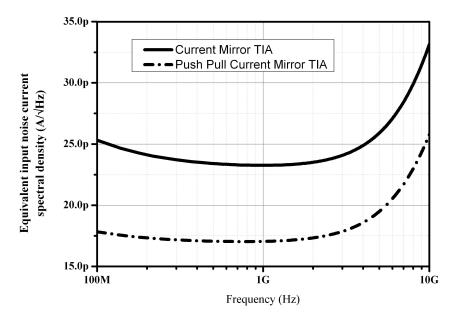

| 5.6         | Comparison of the input referred noise current spectral density of the two                                                                   |          |

|             | current mirror TIAs                                                                                                                          | 47       |

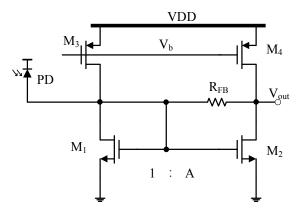

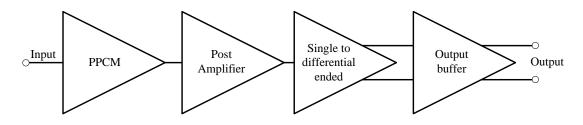

| 5.7         | The architecture of the PPCM complete optical receiver                                                                                       | 47       |

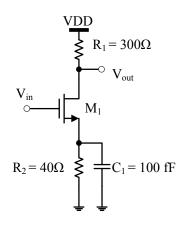

| 5.8         | CS amplifier with resistive-capacitive degeneration.                                                                                         | 48       |

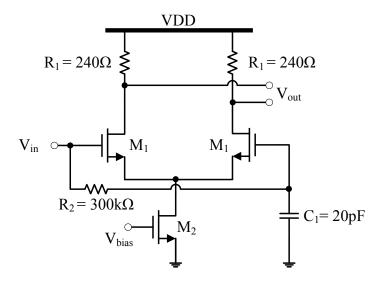

| 5.9         | Single-ended to differential-ended signal converter.                                                                                         | 49       |

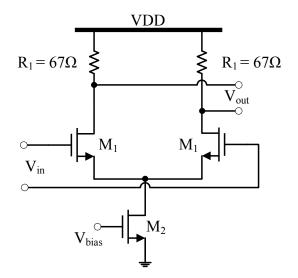

| 5.10        | $50\Omega$ output buffer                                                                                                                     | 49       |

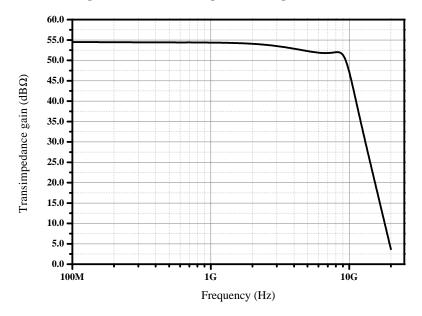

| 5.11        | Simulated transimpedance frequency response of PPCM optical receiver                                                                         | 50       |

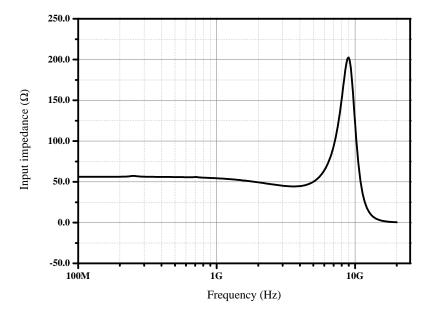

|             | Simulated input impedance of PPCM TIA.                                                                                                       | 50       |

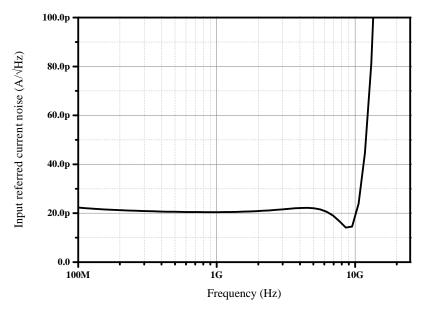

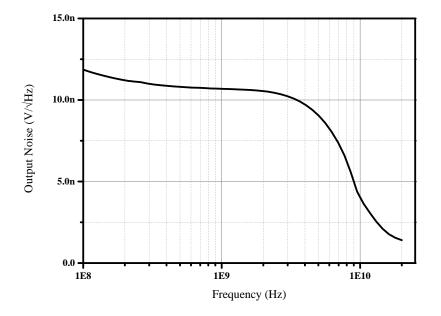

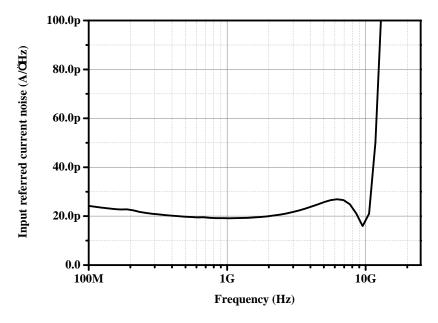

| 5.13        | The input referred noise current spectral density of the PPCM optical                                                                        |          |

|             | receiver.                                                                                                                                    | 51       |

|             | The output noise voltage spectral density of the PPCM optical receiver                                                                       | 51       |

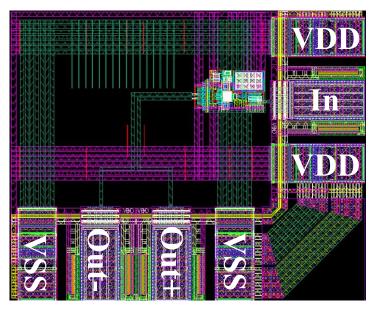

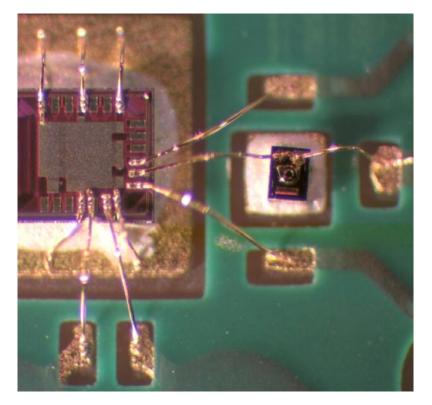

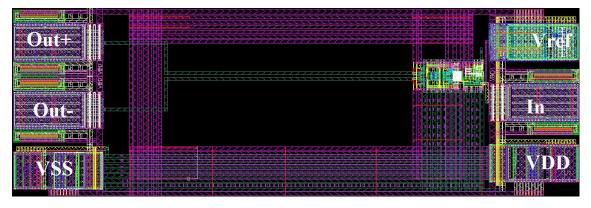

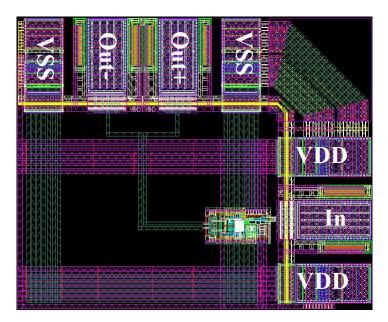

|             | The layout of the PPCM optical receiver.                                                                                                     | 52       |

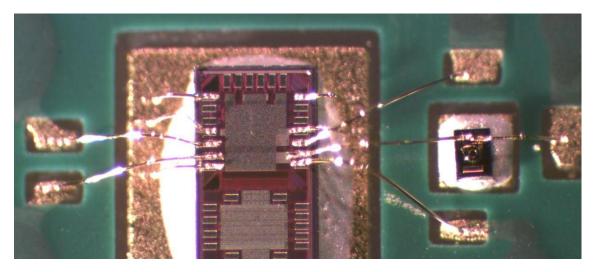

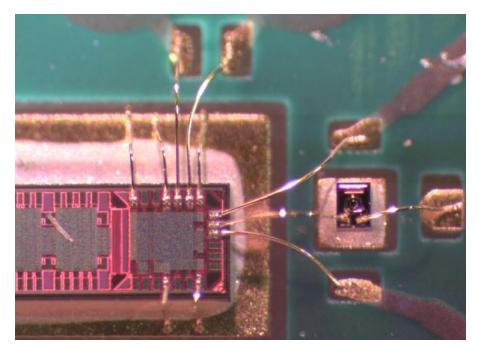

|             | Chip photo of the PPCM optical receiver bonded to an external photodiode.                                                                    | 52       |

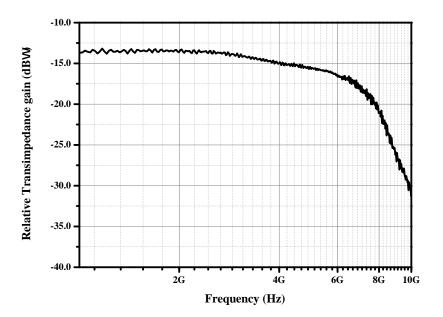

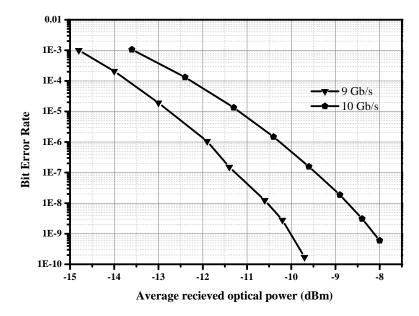

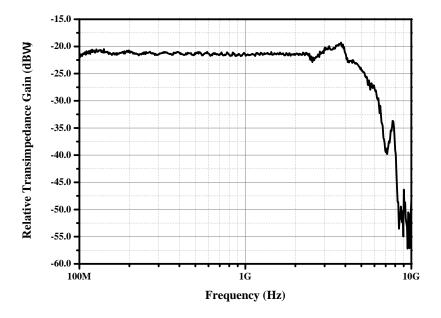

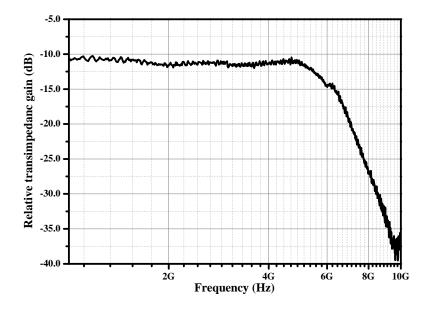

|             | Measured frequency response of PPCM optical receiver.                                                                                        | 53       |

| 5.18        | BER for different input power levels at 9Gb/s and 10Gb/s for a wavelength                                                                    |          |

| <b>F</b> 10 | of $1.55\mu$ m                                                                                                                               | 54       |

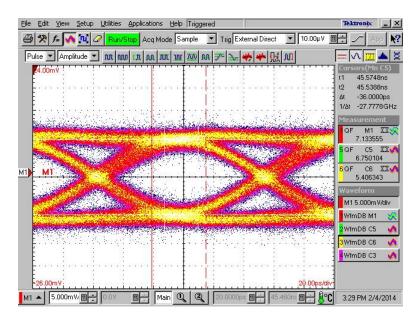

| 5.19        | Eye diagram for average optical input power of $-10$ dBm at a data rate of $-0$ Cl ( f = DDD = $10^{-9}$ (U = i = t + 1) = $20 = (110^{-9})$ |          |

|             | 9Gb/s for a BER= $10^{-9}$ . (Horizontal scale: 20 ps/div., vertical scale: 5 mV/div.)                                                       | 54       |

| 5 20        | mV/div.)                                                                                                                                     | 54       |

| 5.20        | $10$ Gb/s for a BER= $10^{-9}$ . (Horizontal scale: 20 ps/div., vertical scale: 5                                                            |          |

|             |                                                                                                                                              | 55       |

| 5.21        | Common drain active feedback TIA in [3].                                                                                                     | 56       |

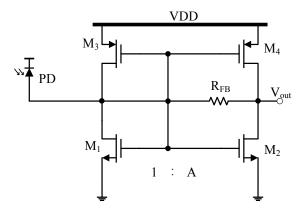

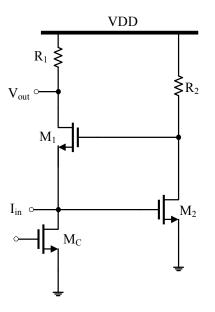

|             | The proposed CDAF TIA.                                                                                                                       | 57       |

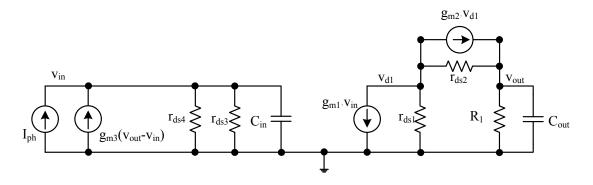

|             | The small signal model of the proposed CDAF TIA.                                                                                             | 57       |

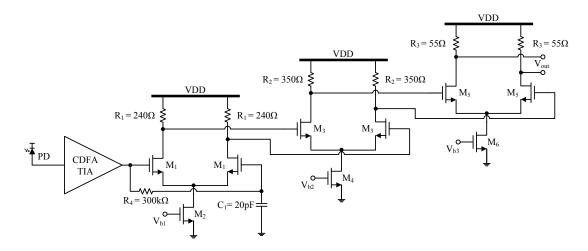

|             | CDAF complete optical receiver.                                                                                                              | 59       |

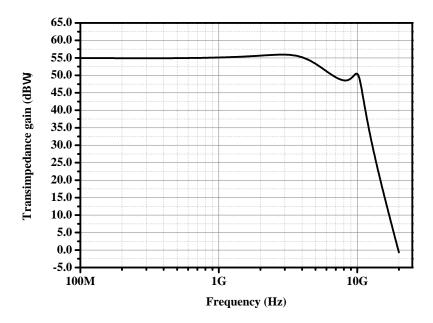

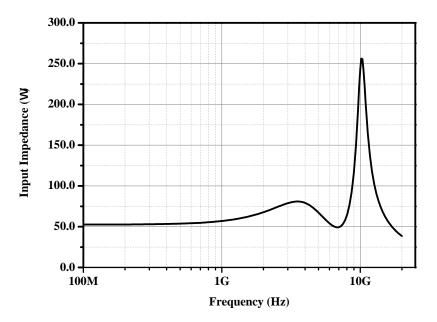

|             | Simulated frequency response of the CDAF optical receiver.                                                                                   | 60       |

|             | Simulated input impedance of the CDAF optical receiver.                                                                                      | 60       |

|             | Simulated input referred current noise spectral density of the CDAF optical                                                                  |          |

|             | receiver.                                                                                                                                    | 61       |

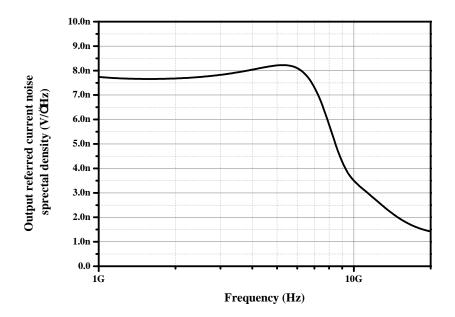

| 5.28        | Simulated output noise voltage spectral density of the CDAF optical receiver.                                                                | 61       |

| 5.29        | Layout of the CDAF complete optical receiver.                                                                                                | 62       |

| 5.30        | Chip photo of the CDAF optical receiver bonded to an external photodiode.                                                                    | 62       |

| 5.31        | Measured frequency response of the CDAF optical receiver.                                                                                    | 63       |

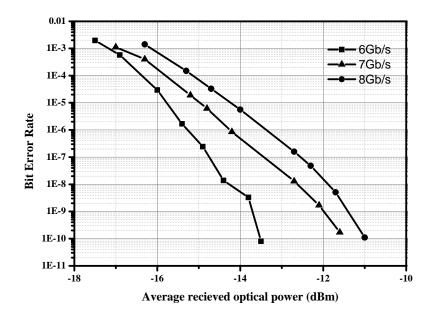

| 5.32        | Measured BER vs different input average optical power levels for data                                                                        |          |

|             | rates at 6Gb/s, 7Gb/s and 8Gb/s for $\lambda = 1.55 \mu m.$                                                                                  | 64       |

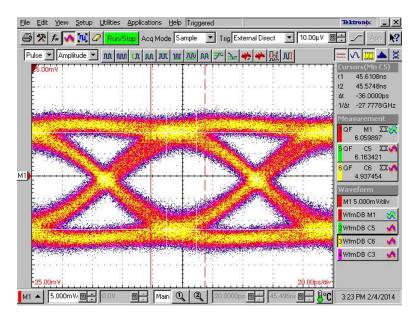

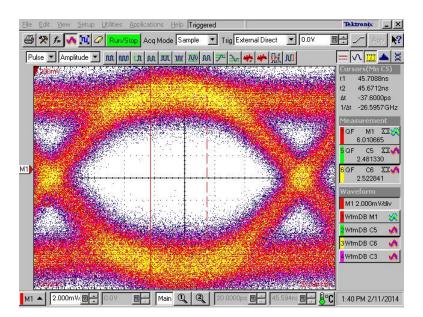

| 5.33        | Measured eye diagram for 6Gb/s at input optical power of -10.1dBm with                                                                       |          |

|             | BER= $10^{-9}$ .(Horizontal scale: 20 ps/div., vertical scale: 2 mV/div.)                                                                    | 64       |

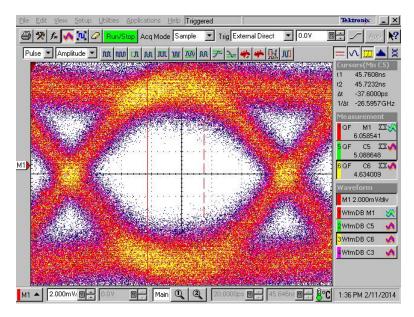

| 5.34        | Measured eye diagram for 7Gb/s at input optical power of -9.9dBm with                                                                        |          |

|             | $BER=10^{-9}.(Horizontal scale: 20 \text{ ps/div.}, \text{ vertical scale: } 2 \text{ mV/div.}) \dots$                                       | 65       |

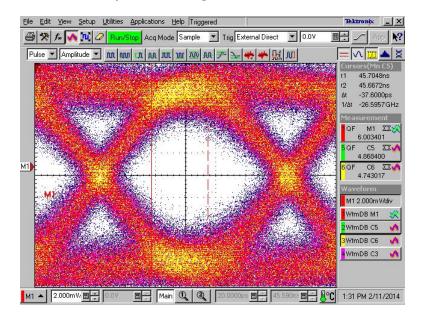

| 5.35        | Measured eye diagram for 8Gb/s at input optical power of $-9.9$ dBm with                                                                     | <b>~</b> |

|             | $BER=10^{-9}.(Horizontal scale: 20 \text{ ps/div.}, \text{ vertical scale: } 2 \text{ mV/div.}) \dots$                                       | 65       |

| 5.36        | Classical RGC TIA.                                                                                                                           | 67       |

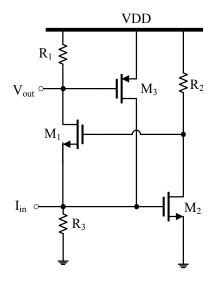

| 5.37 | The proposed RGCAF TIA                                                                                                                        | 68 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

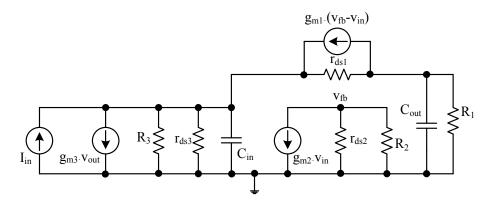

| 5.38 | Small signal model of the RGCAF TIA.                                                                                                          | 68 |

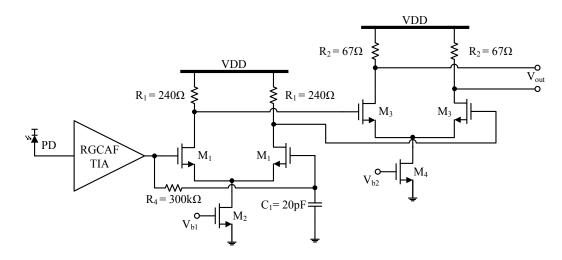

| 5.39 | RGCAF complete optical receiver.                                                                                                              | 70 |

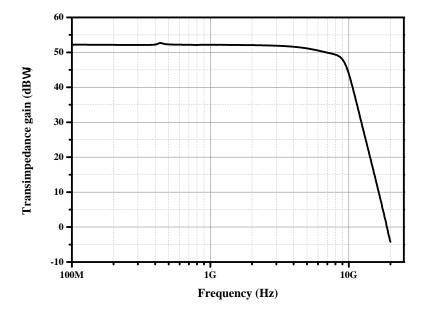

| 5.40 | Simulated frequency response of the RGCAF optical receiver                                                                                    | 71 |

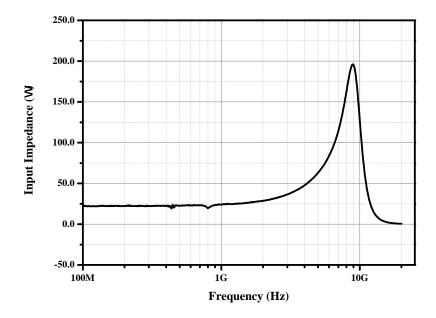

| 5.41 | Simulated input impedance of the RGCAF optical receiver.                                                                                      | 72 |

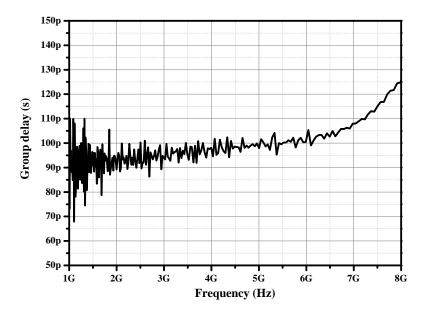

| 5.42 | Simulated group delay of the RGCAF optical receiver.                                                                                          | 72 |

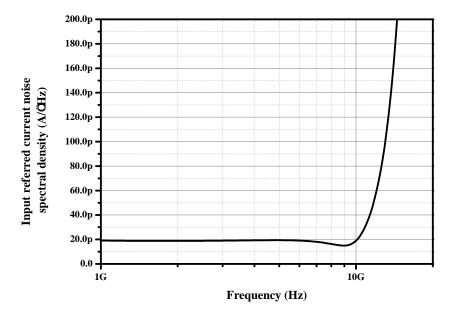

| 5.43 | Simulated input referred current noise spectral density of the RGCAF                                                                          |    |

|      | optical receiver.                                                                                                                             | 73 |

| 5.44 | Simulated output noise voltage spectral density of the RGCAF optical                                                                          |    |

|      | receiver.                                                                                                                                     | 73 |

|      | The layout of the RGCAF optical receiver.                                                                                                     | 74 |

|      | Chip photo of the RGCAF optical receiver bonded to an external photodiode.                                                                    | 74 |

|      | Measured frequency response of RGCAF optical receiver.                                                                                        | 75 |

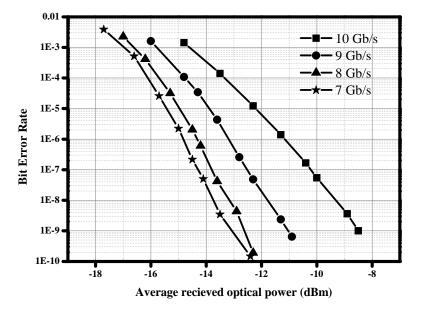

| 5.48 | Measured BER vs average optical power for data rates of 7Gb/s, 8Gb/s,                                                                         |    |

|      | 9Gb/s and 10Gb/s for $\lambda = 1.55 \mu \text{m.}$                                                                                           | 75 |

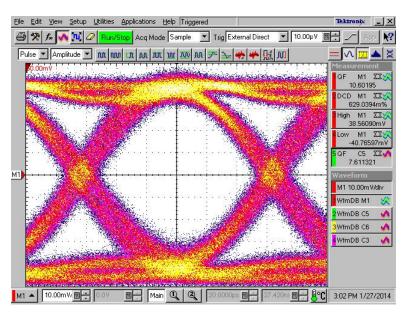

| 5.49 | Measured eye diagram for 8Gb/s at input optical power of -5dBm with $DED = 10^{-9}$ (II = 10 - 10 - 10 - 10 - 10 - 10 - 10 - 10               | 70 |

| F F0 | $BER=10^{-9}.(Horizontal scale: 20 ps/div., vertical scale: 10 mV/div.) \dots$                                                                | 76 |

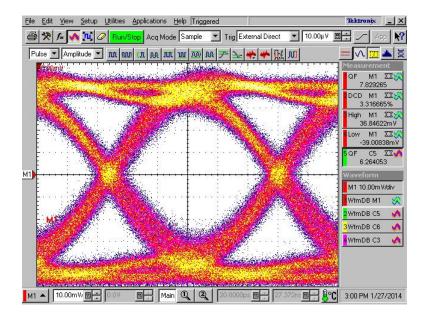

| 5.50 | Measured eye diagram for 9Gb/s at input optical power of -6dBm with $BER=10^{-9}$ .(Horizontal scale: 20 ps/div., vertical scale: 10 mV/div.) | 76 |

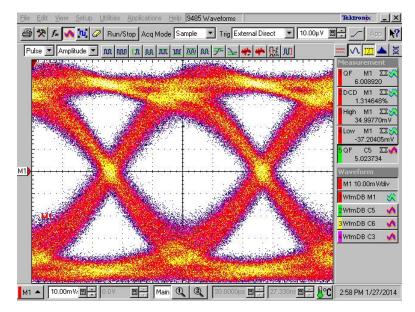

| 5 51 | Measured eye diagram for 10Gb/s at input optical power of -8dBm with                                                                          | 10 |

| 0.01 | $BER=10^{-9}$ .(Horizontal scale: 20 ps/div., vertical scale: 10 mV/div.)                                                                     | 77 |

| 5 52 | Output stage of a LDD using the single cascode transistor concept.                                                                            | 80 |

|      | Simple block diagram of the LDD.                                                                                                              | 81 |

|      | The 50 $\Omega$ input stage, inverter and pre-driver operating at 1.1V supply                                                                 | 01 |

| 0.01 | voltage.                                                                                                                                      | 82 |

| 5.55 | Output stage of the LDD operating at 5V supply voltage.                                                                                       | 83 |

|      | Off-chip 50 $\Omega$ matching output circuitry.                                                                                               | 83 |

|      | Micrograph of the high voltage LDD.                                                                                                           | 84 |

|      | Electrical step response of the laser diode driver.(Horizontal scale: 5                                                                       |    |

|      | ns/div., vertical scale: 100 mV/div.)                                                                                                         | 85 |

|      |                                                                                                                                               |    |

# List of Tables

- 5.1 TIAs performance summary and comparison with the state-of-the-art. . . 78

- 5.2 LDDs performance summary and comparison with the state-of-the-art. . . 86

To my

Mother and Father

## Chapter 1

## Introduction

## 1.1 Motivation

In the past years, the speed of data processing and computation have been increasing rapidly and will continue to do so in future. The processing and computing power are not determined only by the microprocessor's speed but equally important is the speed at which data is transferred to and from the core processor. That means that the required bandwidth of the input and output (IO) channels must cope with the microprocessor's speed [20]. It is strongly believed in future that these channels will be the speed bottle-neck for the whole system.

Until recently, for short and medium distance the data communication links are implemented by electrical connections such as printed-circuit transmission lines, twisted pairs or coaxial cables. Electrical transmission medium has severe problems at high speeds such as signal losses due to skin effect resulting in bandwidth limitation, poor matching which leads to distorted signals and significant Electro-Magnetic noise generation which deteriorates the performance of the whole system [19]. In order to overcome these problems, equalization techniques may be used or parallel Gb/s links are added to achieve the desired data rates. Both solutions, increase the complexity of the system and hence the cost, without a significant improvement in the capacity of communication links. Instead of increasing the complexity of the transmission links, a more efficient way is to use optical transmission medium [44].

Better Signal-to-Noise-Ratio (SNR), higher bandwidth, decreased number of amplifiers in the signal path and effectively low cost, have made optical fibre communication the technology of choice to potentially close the gap between the interconnect speed and the data processing speed. Additionally, parallel optical signalling at short distance is simpler than electrical IOs. It's either implemented by using optical fibre bundles or free space to send parallel light beams from one chip to another. The cross talk between beams in both cases are considerably lower than in electrical IOs [9].

Optical fibres can support very large data rates for short distances due to their negligible frequency dependent loss and dispersion, therefore it is not the data rate limiter. The maximum data rate of an optical link is limited by the operation speed of the optical transmitter (TX) and receiver (RX) [30].

In this thesis we aim to study and investigate the challenges in the design of vital blocks in both the TX and RX ends and introduce a number of solutions to ease the implementation of low cost and high performance optical IOs. In order to achieve this goal a new simple, low power and highly integrable circuit topologies are presented.

## **1.2** Optical Link Architecture

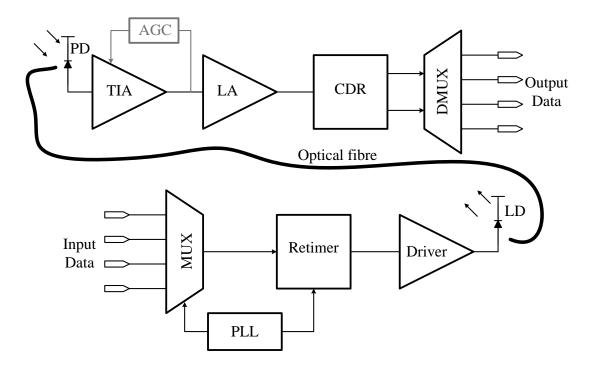

A simplified optical transmission system is shown in figure 1.1. It consists of a TX, transmission medium (optical fibre) and a RX. The TX converts electrical signal into optical and transmits it through a low cost optical fibre then the electrical signal is attained again at the RX end [39].

The TX consists of three main modules: a serializer, a driver and a light emitter. The serializer consists of a multiplexer (MUX), a phased-locked loop (PLL) and a retimer. The MUX combines the synchronous parallel digital input signal into a single high speed bit stream. Nonidealities such as jitter and intersymbol interference (ISI) introduced by the MUX are absorbed by the retimer. Both the MUX and the retimer need clock signals, which are generated by the PLL. The retimer is followed by a driver which delivers a high modulation current to the light emitter. The light emitter converts the electrical data into optical pulses. Laser diode (LD) is usually used as light emitter because it produces high light intensity to compensate the attenuation that will experienced by light as it travel through the optical fibre.

On the RX side, the same process happens in a reverse manner. The RX is divided into three modules: photodetector, front-end and a deserializer. The front-end consists of a transimpedance amplifier (TIA), limiting amplifier (LA) and an automatic gain control (AGC). The deserializer consists of two blocks: clock and data recovery block (CDR) and a demultiplexer (DMUX).

The transmitted light signal is received by the photodetector which is a photodiode (PD) in most cases. The PD converts the optical signal into a proportional output

FIGURE 1.1: Optical link architecture

photocurrent. Because the transmitted light is attenuated by the optical fibre, the PD should be highly sensitive to light. The weak photocurrent is converted into an amplified voltage by the TIA. The TIA's output voltage is further amplified to provide logical levels by a high gain LA. An AGC is employed to a TIA to decrease its gain for high input signal amplitudes to allow a linear operation for a wide range of input signal amplitudes. At that point, the output voltage is strong enough. Finally, this voltage is fed into the deserializer, where the CDR extracts the clock signal and retimes the data signal. The CDR is followed by a DMUX where the fast serial bit stream is demultiplexed to a parallel digital output signal.

## 1.3 Thesis Objectives

Although Hot Electron Mobility Transistors (HEMT), Heterojunction Bipolar Transistors (HBT) and Silicon (Si) bipolar transistors were favourable technologies for high speed optical transceivers due to their noise and speed advantages, they result in a high cost product [26]. Therefore, Complementary Metal Oxide Semiconductor (CMOS) technology is possibly the best choice for low cost, low power and high integration density optical transceivers. On the other hand, the low intrinsic voltage gain and low power supply of nanometer CMOS devices lead to design difficulties which must be overcome to compete with other technologies [38].

The main objective of this thesis is to introduce new circuit ideas to implement low power high speed inductorless TIAs and high voltage laser diode driver (LDD) in standard 40nm CMOS technology.

Usually CMOS TIAs use inductors to achieve data rates of 10 Gb/s or higher. However, using inductors have a number of disadvantages [31]:

- 1. The chip area increases significantly, leading to a higher cost.

- 2. High substrate coupling, results in higher cross talk.

- 3. Poor group delay linearity.

Therefore, to achieve low cost compact TIA designs the use of inductors are avoided leading to more design challenges to achieve the desired data rate.

With the shrinking of the CMOS transistor feature size, the supply voltage is reduced to ensure reliability of the device. This reduction in supply voltage results in some difficulties in LDD design, because there is a large change in the voltage drop over the LD between logical 0 and 1, which makes it difficult to reduce the supply voltage of the LDD below 3.3V. Red lasers have voltage drops larger than 2V. Therefore, it is desirable to introduce new circuit topologies of CMOS LDDs to sustain high supply voltages and provide large modulation current [15].

## 1.4 Thesis Outline

The thesis consists of three main parts: theoretical background, the circuits implementation and the results discussion and conclusion. The thesis is organized as following:

- Chapter 2 provides the theoretical background of LDD and TIA. The chapter reviews the traditional circuit techniques for both blocks. The analysis, advantages and limitations of each technique will be stated and discussed.

- Chapter 3 presents the state of the art of high voltage CMOS LDDs and high speed CMOS TIAs. The chapter begins with explaining the latest high performance CMOS TIAs, then the most recent high voltage CMOS LDDs will discussed.

- **Chapter 4** states briefly in the beginning the physical effects and drawbacks of nanometer CMOS technology. Then the chapter will show the characteristics of both the p-channel metal oxide semiconductor (PMOS) and the n-channel metal oxide semiconductor (NMOS) transistors in 40nm CMOS technology.

Chapter 5 introduces three solutions for high speed inductorless CMOS TIAs and a high voltage CMOS LDD. The chapter will include a theoretical analysis and discussion of each design. Then the simulation and measurement results will be presented and compared with one another and with the state of the art.

Chapter 6 concludes and highlights the main achievements of the proposed solutions.

## Chapter 2

# Fundamentals of Optoelectronic circuits

In this chapter, two of the most critical blocks in an optical link will be discussed. The main focus will be on the TIA on the RX side and the LDD on the TX side. The basic idea, performance requirements and technology independent circuit concepts of both circuits will be explained in details. Finally, the most important points will be summarized in the chapter's conclusion.

## 2.1 Transimpedance Amplifiers

#### 2.1.1 General Concept

Since the PD converts the transmitted light to a weak output photo-current and since the successive processing occurs in the voltage mode. Therefore, the photo-current must be transformed to voltage. This function is performed by the transimpedance amplifier (TIA), it transforms the input current into amplified output voltage. The TIA's amplification factor is called the transimpedance gain and it is defined as the derivative of the output voltage as a function of the input current  $(Z_T=dV_o(I_{PD})/dI_{PD})$ . TIA is the most vital block in an optical front-end as it defines the receiver's data rate, linearity and most importantly the sensitivity [49].

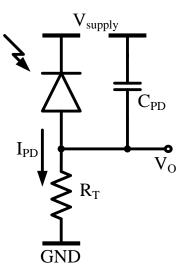

The simplest TIA uses a resistor  $(R_T)$  as shown in figure 2.1. The transimpedance gain is equal to the resistance value of  $(R_T)$ . The bandwidth (BW) is defined by the resistor  $(R_T)$  and the parasitic capacitance of the PD  $(C_{PD})$ , BW=1/ $2\pi C_{PD}R_T$ , showing a clear trade-off between the transimpedance gain and bandwidth.

FIGURE 2.1: TIA using a simple resistor.

Another important aspect is noise which is directly related to the sensitivity of the RX. The thermal noise in the resistor  $R_T$  [39] is :

$$\overline{I_{noise}^2} = \frac{4kT}{R_T},\tag{2.1}$$

where k is the Boltzmann constant and T is the absolute temperature.

The total output integrated noise is:

$$\overline{V_{o,noise}^2} = \frac{4kT}{R_T} \int_0^\infty \left[ R_T \parallel \frac{1}{2\pi j C_{PD} f} \right]^2 df$$

(2.2)

$$=\frac{4kT}{R_T}\int_0^\infty \frac{R_T^2 df}{4\pi^2 R_T^2 C_{PD}^2 f^2 + 1} \approx \frac{kT}{C_{PD}}$$

(2.3)

Equation 2.3 shows that the total integrated output voltage noise is independent of the resistance value  $R_T$ . Decreasing  $R_T$  increases  $\overline{I_{noise}^2}$  but the transimpedance gain  $R_T^2/(4\pi^2 R_T^2 C_{PD}^2 f^2 + 1)$  decreases with the same amount keeping  $\overline{V_{o,noise}^2}$  constant.

For understanding of the dependence of noise on the transimpedance gain, the noise must be referred to the input. The input referred noise is

$$\overline{I_{in,noise}^2} = \frac{\overline{V_{o,noise}^2}}{R_T^2}$$

(2.4)

$$=\frac{kT}{R_T^2 C_{PD}}.$$

(2.5)

Equation 2.5 shows that maximizing the  $R_T$  is essential to decrease the input referred noise current.

The fundamental trade-offs between transimpedance gain, bandwidth and input referred noise current suggest that the resistive/diode combination is not suitable for high performance applications.

The analysis of the simple resistive TIA shown in figure 2.1 proved that resistance  $R_T$  directly couples the bandwidth and noise equations. Therefore, more complex configurations are needed to provide large bandwidth (low input resistance), high gain and minimum noise for a given photodiode parasitic capacitance. Two main categories of TIAs are known to achieve high performance noise-bandwidth-gain requirement: open-loop TIAs and feedback TIAs.

## 2.1.2 Open Loop TIA

#### 2.1.2.1 Transfer Function

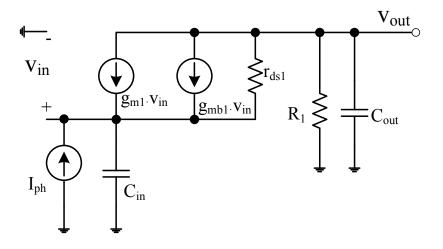

Common gate (CG) amplifier is a well known low input resistance amplifying stage. Figure 2.2 shows CG amplifying stage including the input capacitance  $C_{in}$  and the output capacitance  $C_{out}$ .  $C_{in}$  is the summation of photodiode capacitance  $(C_{PD})$ , gate-source capacitance of  $M_1$  ( $C_{gs_1}$ ), gate-drain capacitance of  $M_2$  ( $C_{gd_2}$ ) and drain-bulk capacitance of  $M_2$  ( $C_{db_2}$ ).  $C_{out}$  includes the input capacitance of the subsequent stage, gate-drain capacitance of  $M_1$  ( $C_{gd_1}$ ) and drain-bulk capacitance of  $M_1$  ( $C_{db_1}$ ).

FIGURE 2.2: Common gate TIA.

From the small signal model shown in figure 2.3, the parameters of the CG TIA could be derived. In the following analysis body effect and channel-length modulation are included [39].

FIGURE 2.3: Common gate TIA small signal model.

The input resistance can be derived from the equations extracted from figure 2.3,

$$-V_{in} = I_{ph}R_1 + (r_{ds_1}I_{ph} + (g_{m_1} + g_{mb_1})V_{in}), \qquad (2.6)$$

$$R_{in_{CG}} = \left| \frac{V_{in}}{I_{ph}} \right| = \frac{r_{ds_1} + R_1}{1 + r_{ds_1}(g_{m_1} + g_{mb_1})}.$$

(2.7)

Since  $r_{ds_1}(g_{m_1} + g_{mb_1}) \gg 1$ ,

$$R_{in_{CG}} = \frac{r_{ds_1} + R_1}{r_{ds_1}(g_{m_1} + g_{mb_1})}.$$

(2.8)

If  $r_{ds_1}$  approaches  $\infty$ ,  $R_{in_{CG}} \approx 1 / (g_{m_1} + g_{mb_1})$ . In short-channel devices, the output resistance  $r_{ds_1}$  is comparable to  $R_1$ , leading to a higher input resistance.

The input impedance of CG TIA is the parallel connection of  $R_{in_{CG}}$  and  $C_{in}$ ,

$$R_{in_{CG}}(s) = \frac{r_{ds_1} + R_1}{r_{ds_1}(g_{m_1} + g_{mb_1}) + sC_{in}(r_{ds_1} + R_1)}.$$

(2.9)

The first step to derive the CG TIA's transimpedance gain is to state the voltage gain of the CG stage,

$$A_{CG}(s) = \frac{V_{out}}{V_{in}} = (g_{m_1} + g_{mb_1}) \left(\frac{R_1}{1 + sC_{out}R_1}\right).$$

(2.10)

The transimpedance gain is the multiplication of 2.9 and 2.10,

$$Z_{T_{CG}}(s) = \frac{V_{out}}{V_{in}} \cdot \frac{V_{in}}{I_{ph}} = \frac{V_{out}}{I_{ph}}.$$

(2.11)

$$Z_{T_{CG}}(s) = \frac{(r_{ds_1} + R_1)(g_{m_1} + g_{mb_1})R_1}{(r_{ds_1}(g_{m_1} + g_{mb_1}) + sC_{in}(r_{ds_1} + R_1))(1 + sC_{out}R_1)}.$$

(2.12)

The DC transimpedance gain of the CG stage is

$$Z_{T_{CG}}(0) = R_1 \left[ 1 + \frac{R_1}{r_{ds_1}} \right].$$

(2.13)

From equation 2.12, CG TIA has two poles: the input pole  $(g_{m_1} + g_{mb_1})/C_{in}$  and the output pole  $(C_{out}R_1)^{-1}$ . The input pole is the dominate pole, since the photodiode parasitic capacitance is quite large.

To maximize the bandwidth, the quantity  $(g_{m_1} + g_{mb_1})$  must be maximized, either by increasing the width of  $M_1$  or the biasing current of the CG TIA. However, increasing the width of  $M_1$  with increase the gate-source capacitance and hence lead to bandwidth limitation. Increasing the biasing current of the CG stage will increase the voltage drop over  $R_1$ , resulting in the decrease of the overhead voltage of  $M_1$  and  $M_2$ , requiring a higher supply voltage. If  $R_1$  is decreased to have the same voltage drop, the transimpedance gain will decrease and the TIA's noise current will increase. If the width of  $M_2$  is increased to accommodate the decrease of the overhead voltage, then both the noise and drain capacitance will increase.

The previous analysis shows achieving a wideband performance will lead to a low transimpedance gain, resulting in significant noise contribution for this stage and subsequent stages.

#### 2.1.2.2 Noise Analysis

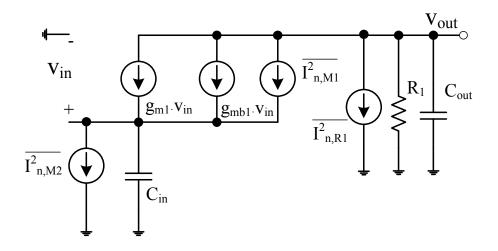

FIGURE 2.4: Noise model of CG TIA.

Figure 2.4 shows the small signal noise model of the CG TIA. It includes the thermal noise of  $R_1$  and the noise current of  $M_1$  and  $M_2$ .

The spectral output noise voltage of CG TIA [39] is

$$\overline{V_{out,noise}^2} = \frac{R_1^2}{(R_1 C_{out} s)^2 + 1} \left[ \frac{\overline{I_{n,M1}^2 (sC_{in})^2 + \overline{I_{n,M2}^2} (g_{m_1} + g_{mb_1})^2}}{(sC_{in})^2 + (g_{m_1} + g_{mb_1})^2} + \overline{I_{n,R1}^2} \right].$$

(2.14)

The total integrated output noise voltage from s=0 to  $s=\infty$  [39] is

$$\overline{V_{out,int,noise}^2} = \frac{kT}{C_{out}} \left[ \frac{g_{m_1}R_1C_{in}\gamma}{C_{in} + (g_{m_1} + g_{mb_1})R_1C_{out}} + 1 \right] + \frac{2kT(g_{m_1} + g_{mb_1})g_{m_2}R_1^2\gamma}{C_{in} + (g_{m_1} + g_{mb_1})R_1C_{out}}.$$

(2.15)

Since the dominate pole is located at the input  $C_{in}/(g_{m_1}+g_{mb_1}) >> R_1 C_{out}$

$$\overline{V_{out,int,noise}^2} \approx \frac{kT}{C_{out}} \left[ g_{m_1} R_1 C_{in} \gamma + 1 \right] + \frac{2kT(g_{m_1} + g_{mb_1})g_{m_2} R_1^2 \gamma}{C_{in}}.$$

(2.16)

Dividing equation 2.16 by the  $R_1^2$  results in the integrated input referred noise current:

$$\overline{I_{in,int,noise}^2} \approx \frac{kT}{C_{out}R_1^2} \left[ g_{m_1}R_1C_{in}\gamma + 1 \right] + \frac{2kT(g_{m_1} + g_{mb_1})g_{m_2}\gamma}{C_{in}}.$$

(2.17)

For short channel MOS transistors,  $\gamma > 1$ , which shows that input referred noise current increases as the CMOS technology is scaled down.

Equation 2.17 shows that  $g_{m_1}$  can be lowered to decrease noise at the cost of bandwidth. Decreasing  $g_{m_2}$  is the only parameter that can decrease noise without affecting the bandwidth. However, it will decrease the voltage headroom for a given biasing current, showing that CG TIA has limited flexibility from noise perspective. Therefore, it is ill suited for low noise applications.

#### 2.1.3 Shunt Shunt Feedback TIA

#### 2.1.3.1 Transfer Function

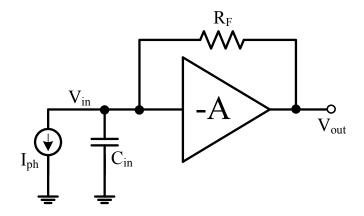

The basic topology of a shunt shunt feedback TIA is shown in figure 2.5, where the feedback resistor  $R_F$  is connected between the input and the output of an inverting voltage amplifier.  $R_F$  converts the input photodiode current to output voltage. The inverting voltage amplifier guarantees low noise at high frequencies [49].

$C_{in}$  is the total capacitance at the input node of the TIA. It includes the photodiode capacitance, input capacitance of the amplifier, pad capacitance and parasitic capacitance associated with  $R_F$ . Since  $C_{in}$  introduces loss at high frequencies, it is important to keep  $C_{in}$  as small as possible to achieve high noise performance.

FIGURE 2.5: Shunt shunt feedback TIA.

The inverting voltage amplifier is assumed to have a single pole lowpass behaviour A(s) with a DC gain  $A_{DC}$  and a single pole at  $f_o$ ,

$$A(s) = \frac{A_{DC}}{1 + \frac{s}{2\pi f_o}}.$$

(2.18)

Applying Kirchhoffs laws to the TIA in figure 2.5 results in:

$$I_{ph} = -sV_{in}C_{in} - \frac{V_{in} + V_{out}}{R_F}.$$

(2.19)

Knowing that  $V_{out} = A(s)V_{in}$ , the transimpedance gain is

$$Z_T(s) = \frac{V_{out}}{I_{ph}} = -\frac{A(s)R_F}{A(s) + 1 + sR_FC_{in}}.$$

(2.20)

Substituting 2.19 in equation 2.20, the transimpedance gain can be expressed as

$$Z_T(s) = -\frac{2\pi f_o A_{DC} C_{in}^{-1}}{s^2 + s \left(\frac{2\pi f_o R_F C_{in} + 1}{R_F C_{in}}\right) + \frac{2\pi f_o (A_{DC} + 1)}{R_F C_{in}}}.$$

(2.21)

The low frequency (s=0) transimpedance gain is

$$Z_T(0) = -\frac{A_{DC}}{A_{DC} + 1} R_F.$$

(2.22)

From control theory, for a second order transfer function with a denominator equal to  $s^2 + s2\zeta\omega_n + \omega_n^2$ , the damping factor  $\zeta$  has to be equal to  $\sqrt{2}/2$ , to avoid ringing in the TIA's step response.

The TIA's natural frequency  $\omega_n$  and damping factor  $\zeta$  are

$$\omega_n = \sqrt{\frac{2\pi f_o(A_{DC}+1)}{R_F C_{in}}},\tag{2.23}$$

$$\zeta = \frac{1}{2} \frac{2\pi f_o R_F C_{in} + 1}{\sqrt{2\pi f_o R_F C_{in} (A_{DC} + 1)}}.$$

(2.24)

For critical damping  $\zeta = \sqrt{2}/2$ , the -3dB bandwidth of the voltage amplifier is

$$f_o \approx \frac{1}{\pi} \frac{A_{DC}}{R_F C_{in}}.$$

(2.25)

To derive the -3dB bandwidth of the feedback TIA, we equate the magnitude of equation 2.21 to  $\sqrt{2}/2$  resulting in

$$f_{-3dB} \approx \frac{1}{2\pi} \frac{\sqrt{2}A_{DC}}{R_F C_{in}}.$$

(2.26)

Equations 2.25 and 2.26 show that the -3dB bandwidth of the voltage amplifier should be approximately 1.5 times the -3dB bandwidth of the TIA to achieve a criticallydamped response. If  $f_o > 1.5 \times f_{-3dB}$ , the feedback exhibits over-damping response. If  $f_o < 1.5 \times f_{-3dB}$ , the step response exhibits under-damping, creating inter symbol interference (ISI).

#### 2.1.3.2 Noise Analysis

FIGURE 2.6: CMOS Shunt shunt feedback TIA.

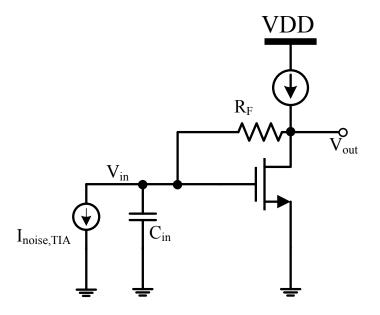

In this subsection we analysis the noise performance of a shunt shunt feedback TIA. The analysis will be limited to MOSFET input device, since bipolar technology is beyond the scope of this work. Figure 2.6 shows a simple CMOS shunt shunt feedback TIA.

The input referred noise current is mainly dominated by two noise sources: the noise from the feedback resistor  $\overline{I_{R_F,noise}^2}$  and the noise from the NMOS input device  $\overline{I_{M_N,noise}^2}$ .

These noise sources are usually uncorrelated. Therefore, they can be summed as follows

$$\overline{I_{in,noise}^2}(f) = \overline{I_{R_F,noise}^2}(f) + \overline{I_{M_N,noise}^2}(f).$$

(2.27)

The noise generated from the feedback resistor is thermal-noise. For a certain frequency band (f), it is formulated as follows

$$\overline{I_{R_F,noise}^2}(f) = \frac{4kT}{R_F}.$$

(2.28)

Equation 2.28 shows that the feedback resistor should be as high as possible to optimize the noise of the TIA.

The noise sources in the NMOS input device are the noise generated by gate leakage current and channel noise. The noise generated by the gate leakage current [41] is

$$\overline{I_{M_N,G,noise}^2}(f) = 2qI_G, \qquad (2.29)$$

where  $I_G$  is the gate leakage current and q is the charge of an electron. This noise source contributes directly to the input referred noise current of the TIA. This noise component increases as the minimum channel length of the MOSFET decreases.

The most important noise source in a MOS transistor is the channel noise,

$$\overline{I_{M_N,C,noise}^2}(f) = 4kT\Gamma g_m, \qquad (2.30)$$

where  $g_m$  is the transconductance of the transistor and  $\Gamma$  is the channel noise factor. In a MOS transistor,  $\Gamma$  varies from 0.7 to 3.0, where the high numbers correspond to the short channel transistors [39]. Unlike the previously mentioned noise sources, this noise source is not directly contributing to the input referred noise current. To refer the channel noise to the input,  $\overline{I^2_{M_N,C,noise}}$  should be divided by the transfer function from  $\overline{I^2_{in,noise}}$  to  $\overline{I^2_{M_N,C,noise}}$ . This transfer function can be shown to be [41]:

$$T(f) = \frac{g_m R_F}{1 + 2\pi f R_F C_{in}}.$$

(2.31)

Using the transfer function in 2.31, the input referred channel noise is

$$\overline{I_{M_N,C,in,noise}^2}(f) = \frac{4kT\Gamma}{g_m R_F^2} + \frac{4kT\Gamma(2\pi f C_{in})^2}{g_m}.$$

(2.32)

Equation 2.32 explains the phenomena of the  $f^2$  noise component. This noise component rises from the white noise, which increases due to the lowpass characteristic of the transfer function of 2.31 with a cutoff frequency of  $1/2\pi R_F C_{in}$ .

FIGURE 2.7: NMOS channel noise and feedback resistor noise spectrums.

The total input referred noise current spectrum is the summation of all the previously mentioned noise sources:

$$\overline{I_{in,noise}^2}(f) = \frac{4kT}{R_F} + 2qI_G + \frac{4kT\Gamma}{g_m R_F^2} + \frac{4kT\Gamma(2\pi fC_{in})^2}{g_m}.$$

(2.33)

Integrating equation 2.33 results in the total integrated input referred noise current in bandwidth B, resulting in the following equation

$$\overline{I_{tot,in,noise}^2} = \int_0^B \overline{I_{in,noise}^2}(f) df = \frac{4kT}{R_F} B + 2qI_G B + \frac{4kT\Gamma B}{g_m R_F^2} + \frac{4kT\Gamma (2\pi C_{in})^2 B^3}{3g_m}.$$

(2.34)

Equation 2.34 shows that for high speed front ends the value of the feedback resistor decreases resulting in a significant contribution of noise from both the amplifier and the resistor, worsening the noise performance of the amplifier.

## 2.2 Laser Diode Drivers

## 2.2.1 General Concept

Laser diode drivers (LDD) can be modelled as a switching current source that turns the laser diode on and off depending on the modulating input data, as shown in figure 2.8. If the temperature of the laser diode varies during operation, large fluctuation in

FIGURE 2.8: Ideal model of laser diode driver as a switching current source.

the output power can occur. To reduce this effect, the output power is defined as a function of current (figure 2.9) instead of voltage. For this reason, and because of current switching speed advantages, laser diodes are driven by current [41].

FIGURE 2.9: The power/current characteristic curve of the laser diode.

In general, the electro-optical interface in most optical systems defines the maximum bandwidth of the system. The laser driver is a very vital block in determining the performance of the optical transmitter. Therefore, the driver must fulfil the following criteria:

1: Sufficient switching speed to modulate the output optical power with minimal inter-symbol interference.

- 2: Provide high output current to generate the adequate output optical power.

- 3: Tolerant to the voltage swing across the laser diode.

The above criteria makes the design of laser drivers very difficult. As the transistor's minimum feature size scale down to acquire high speeds, the unavoidably lower breakdown voltage makes it increasingly difficult to tolerate the high voltage swing across the laser diode. The large output current required to be delivered by the laser driver obligates the use of wide transistors, thus leading to large input and output capacitances for the laser driver.

#### 2.2.2 LDD Circuit Concept

#### 2.2.2.1 Output Stage

FIGURE 2.10: Simple laser diode driver circuit.

The output stage of most LDDs is based on the differential pair shown on figure 2.10. The differential pair steers the tail current  $I_M$  between the laser diode  $R_L$  and the dummy load  $R_D$ . To achieve full switching between  $R_L$  and  $R_D$ , the differential input voltage swing  $V_{in}$  must be large enough.  $V_{in}$  depends on the tail current and the transistor's size, to steer large  $I_M$  with a moderate voltage swing, wide transistors are required. This current steering approach has a number of advantages [41]:

1: The differential design has important advantages over single-ended design. First, it is less sensitive to common-mode noise and has better power supply rejection, to achieve drivers with low jitter. Second, it averts the use of input reference voltage, thus avoids pulse-width distortion which results from the error in this reference voltage.

- 2: It provides constant power supply current, no matter a high or low logic value is transmitted. As a result, the power and ground bounces generated from parasitic inductance is minimized.

- 3: The current overshoots and variations which result from the charging of the parasitic capacitor across the tail current source is minimized, because the voltage across the tail current source is constant as it is defined by the input common mode voltage of the input devices.

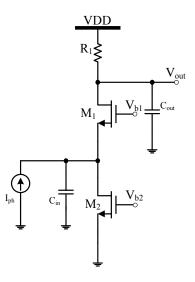

### 2.2.2.2 Predriver

As explained previously, the input transistors of the output stage are made to be quite wide to be able to switch hundreds of milliamperes. As a result, the input capacitance of the output stage is large. An on-chip block, such as  $50\Omega$  input matching circuitry, may not be able to drive the output stage at the desired frequency. Furthermore, driving the output stage from off chip, may lead to unacceptable degradation of input mismatch parameter due to the large input capacitance of the output stage. Another concern is that the input voltage swing should be large enough to switch the output stage on and off. To solve this issue, a predriver is needed to drive the output stage. The predriver must have enough voltage gain to ensure sufficient voltage swing at the input of the output stage, to guarantee full switching operation. In addition, the prediver should be able to drive large capacitance while maintaining low input capacitance and low output resistance.

The desired voltage gain of the predriver can be achieved by multiple gain stages especially in short channel MOSFET technologies. For the predriver to be able to drive the large input capacitance of the output stage several broadband techniques are used and they are listed as follows [41]:

- Load reduction techniques

- Intermediate stage buffers such as source followers and super source followers.

- Negative capacitance such as negative Miller capacitance and negative impedance converter capacitor.

- Inductive techniques

- Shunt inductive peaking.

- Series peaking and T-coil network placed between stages of the predriver.

- Distributed amplifiers.

- Feedback techniques

- Series feedback such as source degeneration and  $f_T$  doubler.

- Cascode transistor.

- Shunt shunt feedback.

### 2.2.2.3 Back Termination

The laser diode is usually connected to the output stage with a transmission line. To avoid unwanted reflections from the load into the output stage, the characteristic impedance of the transmission line should match the impedance of the laser diode. To match the transmission line with a laser diode, which typically has a resistance of  $5\Omega$ , a  $20\Omega$  resistor is connected in series with the laser diode to match the diode with a  $25\Omega$  transmission line or a  $45\Omega$  resistor is connected in series with the laser diode to match the diode to match the diode with a  $50\Omega$  transmission line.

For low supply voltage design, a transmission line with lower characteristic impedance is preferred since the power dissipation is lower. The best case from power perspective, is not to use transmission lines and matching resistors and connect the laser diode directly to the output stage.

Since the laser diode resistance is bias dependant, matching with a transmission line can't be guaranteed for all operating conditions, leading to undesired reflections. When these reflections propagate back to the output stage, they see a high impedance and propagate back unattenuated to the load. These reflections are called double reflections and may lead to degradation in the driver's jitter performance and extinction ratio. The problem of double reflections can be solved by using an output stage with back termination. There are two types of back termination: passive and active [41].

The concept of back termination is to create a low impedance node at the output stage, where the reflection from the laser diode is absorbed. In passive back termination this is done using a termination resistor, leading to higher power consumption due to the voltage drop over this resistor. This problem is solved in active back termination where under normal operation the voltage drop over the termination is zero and no power is dissipated in this resistor.

### Chapter 3

# State of the Art

### 3.1 Transimpedance Amplifiers

Despite the fact that there are many papers on TIAs in micron, submicron and nanometer CMOS technology. In this section only TIAs in submicron and nanometer CMOS technology are summarized.

TIAs using regulated cascode (RGC) topology as an input stage were previously reported in [35, 36, 42]. The RGC circuit, shown in figure 3.1, amplifies the input photo-current and converts it to voltage at the drain of  $M_1$ . The local feedback common source amplifier  $(M_2 \text{ and } R_2)$  reduces the input impedance by the factor of its voltage gain, increasing the bandwidth.

FIGURE 3.1: Regulated Cascode CMOS TIA.

The use of a local feedback also enhances the RGC's input transconductance, reducing the high frequency noise contribution related with the high input parasitic capacitance of the photodiode.

In [36], the proposed TIA with RGC input stage was implemented in 0.6 $\mu$ m digital CMOS technology. The TIA achieved a 58dB $\Omega$  and a -3dB bandwidth of 860MHz for 1pF photodiode parasitic capacitance. The measured average spectral noise density is 6.3 pA/ $\sqrt{Hz}$  and sensitivity of -20dBm for a data rate of 1.25 Gb/s and a bit error rate of 10<sup>-12</sup>. The chip consumes 17mA current and dissipates 85mW from 5V supply.

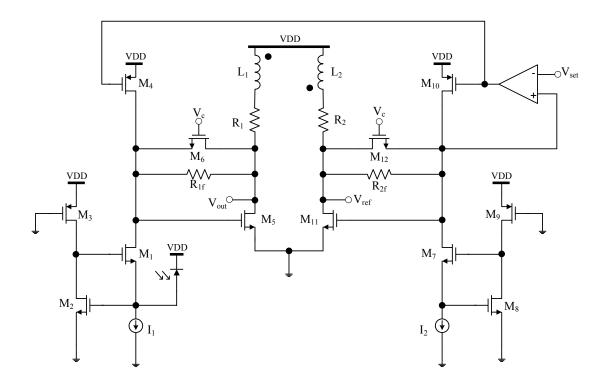

In [7], a pseudo differential TIA with a RGC input stage  $(M_1-M_4 \text{ and } M_7-M_{10})$  followed by a common source with a shunt feedback resistor  $(M_5, M_{11}, R_1, R_2, R_{1f}, R_{2f}, L_1 \text{ and} L_2)$  was presented. The input common mode voltage of the shunt feedback common source amplifier is set  $(V_{set})$  by local feedback amplifier as shown in figure 3.2. To enhance the bandwidth of the TIA, a three dimensional (3-D) transformer is used. The 3-D transformer is formed of an inductor pair  $(L_1-L_2)$  with an inductance of 2.85nH each. The quality factor of the 3-D transformer is 4.5 at 7 GHz. As a result of the use of 3-D transformer, the TIA consumes a chip area of  $330\mu m \times 550\mu m$ . The front-end is implemented in 0.18  $\mu m$  CMOS technology. It provides a conversion gain of 87dB $\Omega$  and a -3dB bandwidth of 7.6 GHz. The measured sensitivity is -12dBm at a data rate of 10 Gb/s and a bit error rate of  $10^{-12}$ . The chip dissipates 210mW from 1.8V supply.

FIGURE 3.2: The pseudo differential TIA with a RGC input stage proposed in [7].

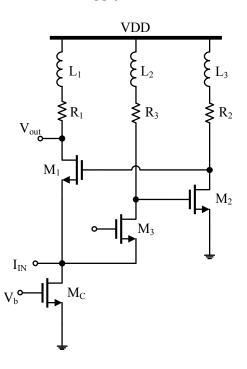

A common gate feedback TIA was introduced in [19]. The TIA shown in figure 3.3 is a modified version of the conventional RGC TIA shown in figure 3.1. The modification is the insertion of  $M_3$ .  $M_3$  acts a level shifter. The use of this concept allows the gate voltage of  $M_2$  to be as low as one transistor  $V_{GS}$  instead of two transistor gate-source voltages as in RGC TIA. The feedforward technique increases the input transconductance and reduces the input impedance of this topology resulting in bandwidth increase. As shown in figure 3.3, three spiral inductors are used to further enhance the bandwidth. Each inductor is 2.2nH, with eight turns and occupies a chip area of  $18\mu m \times 18\mu m$ . The TIA is implemented in 80nm digital CMOS technology. The measured transimpedance gain of the TIA is 52dB $\Omega$  and -3dB bandwidth of 13.4 GHz for a photodiode capacitance of 320fF. The measured input referred noise current spectral density is  $28 \text{ pA}/\sqrt{Hz}$  at 3 GHz and sensitivity of -8 dBm for a bit error rate of  $10^{-12}$  at a data rate of 20 Gb/s. The TIA dissipates 2.2mW from 1V supply.

FIGURE 3.3: Common gate feedback TIA presented in [19].

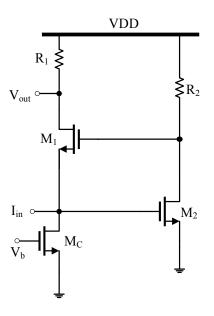

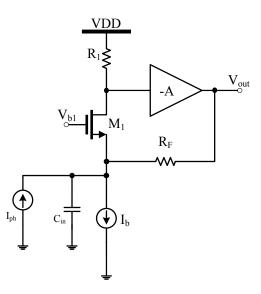

In [25], a feedback common gate (CG) TIA was introduced. As shown in figure 3.4, the CG stage is followed by an amplifying stage and  $R_F$  connected between the output and the source of  $M_1$  forming a negative feedback. Although, the feedback formed by  $R_F$  decreases the input resistance, it increases the input referred noise current. It was mathematically proven in [25] that the presented topology can achieve a lower input resistance than a conventional CG TIA without increasing the input referred noise current, if A > 1 and  $R_F > MR_1/(M-1)$  where M is the scaling factor of the transistor width of  $M_1$  and the biasing current  $I_b$ . The TIA was implemented in 90nm digital CMOS technology and it was designed for 40 Gb/s application.

FIGURE 3.4: A feedback common gate (CG) TIA introduced in [25].

In [12], a gain reuse RGC compensation was introduced. Figure 3.5 shows the proposed topology. The main concept of this topology is to reuse the amplified voltage at the drain of  $M_1$ - $M_2$  and feeding it back through a source follower  $M_3$ - $M_4$ . The cross coupled connection from the source of  $M_3$  to  $M_2$  and  $M_4$  to  $M_1$  maintain the negative feedback. This technique makes the TIA less sensitive to  $C_{in}$  and achieve a higher gain bandwidth while sacrificing a minor reduction in transimpedance gain. The TIA was fabricated in 130nm CMOS technology. This design achieved a transimpedance gain of 400 $\Omega$  and a -3dB bandwidth of 2.8GHz for an input capacitance of 2pF. The TIA consumes 8mA from 1.8V supply.

The novel [26] shows the design mechanism of current mode TIA with active feedback. The TIA is shown in figure 3.6. The input transistor  $M_1$  is in a common gate configuration and the active feedback transistor is a PMOS transistor in a common source configuration. This topology have the same input impedance as the RGC TIA. The presented TIA broadens the bandwidth on the expense of transimpedance gain. Therefore, it is desirable to use large  $R_1$ , small  $M_1$  and small  $M_2$  to maximize the gain. Moreover,  $M_2$ 's channel thermal noise adds directly to the input referred noise current. Therefore, it is desired to keep the width of  $M_2$  small. The TIA is followed by two capacitively degenerated common source voltage amplifiers to achieve high gain. An input series spiral inductor is used for bandwidth extension. The chip is fabricated in 180nm CMOS process. The overall measured transimpedance gain is 55dB $\Omega$  and a -3dB bandwidth of 7 GHz for a total input parasitic capacitance of 300fF. The measured average input referred noise current is 17.5pA/ $\sqrt{Hz}$  up to 7 GHz. In addition, the measured group delay until 7 GHz is 65±10 ps. The chip dissipates 18.5 mW from a single 1.8V supply.

FIGURE 3.5: A RGC TIA with gain reuse introduced in [12].

FIGURE 3.6: A current mode TIA with active feedback [26].

FIGURE 3.7: TIA in parallel configuration for bandwidth enhancement [31].

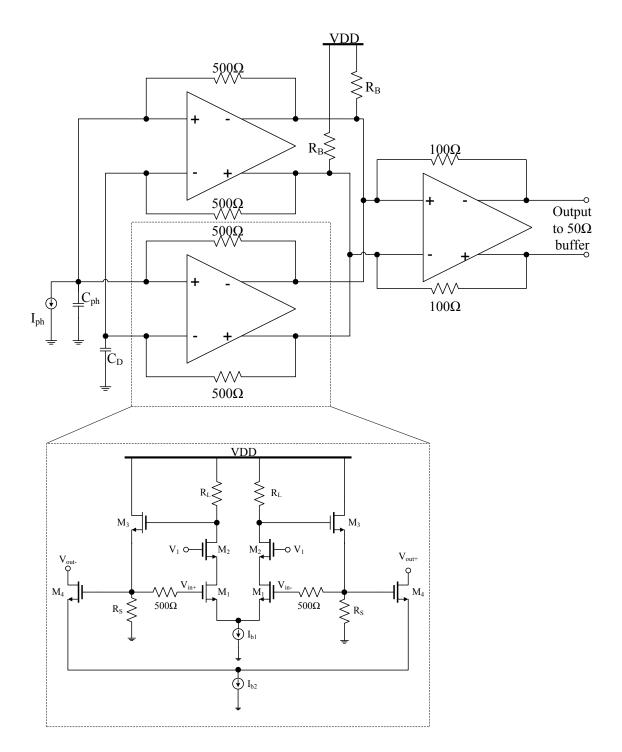

A different bandwidth enhancement techniques was proposed in [31]. The presented technique requires no inductors, it is based on the use of N (in this case it is 2) similar TIAs connected in parallel configuration, as shown in figure 3.7. In this technique, each single TIA experience smaller input capacitance  $(C_{ph}/N)$  resulting in bandwidth enhancement without changing the transimpedance gain of a single TIA. The circuit implementation of the feedback TIA is shown in figure 3.7, the input amplifier is a cascode differential amplifier  $(M_1, M_2 \text{ and } R_L)$  followed by a source follower  $(M_3 \text{ and } R_s)$  and the output of the two TIAs are summed by a common source buffer  $(M_4 \text{ and } R_B)$ . The parallel TIAs are followed by another TIA to convert the summed currents of the parallel TIAs. The chip is implemented in 130nm digital CMOS process. The measured transimpedance gain is 62 dB $\Omega$  and bandwidth of 6 GHz for an input parasitic capacitance of 250fF. The measured minimum detectable input current is 22.4  $\mu$ A and it dissipates 98mW (N = 2) from a 2V supply.

FIGURE 3.8: The low power RGC TIA present in [1].

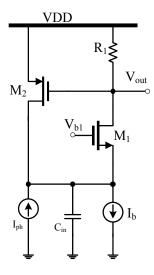

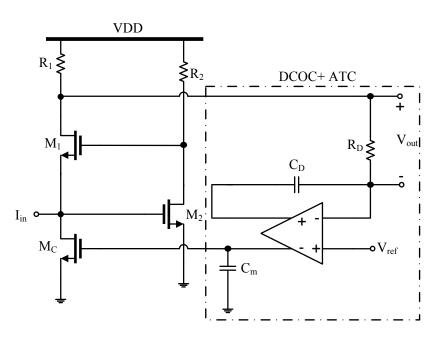

A RGC TIA with low power and area efficient method of single to differential signal conversion is proposed in [1]. The method is based on sharing the passive components for DC offset canceller (DCOC) and autothreshold controller (ATC) at the TIA as shown in figure 3.8. The DCOC is implemented with a non-inverting integrator connected between input and output forming a negative feedback as shown in figure 3.8.  $C_D$  and  $R_D$  of the integrator also act as ATC saving area and power. The TIA was fabricated in 65nm CMOS. The measured transimpedance gain of the TIA and the limiting amplifier is 75.6 dB $\Omega$  and the data rate achieved is 6Gb/s for 300fF input capacitance. The achieved sensitivity is -3.8dBm at a BER of  $10^{-11}$ . The chip dissipates 2.86mW from 1.1V supply.

### **3.2** Laser Diode Drivers

FIGURE 3.9: Laser diode driver (LDD) proposed in [47].

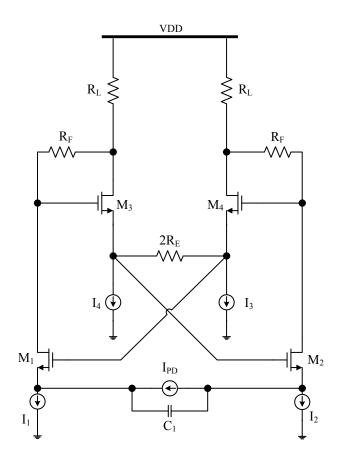

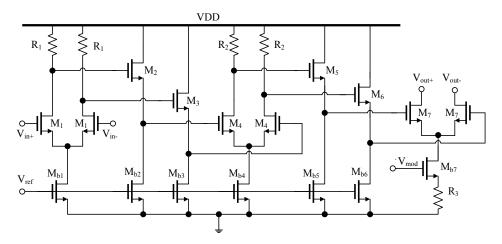

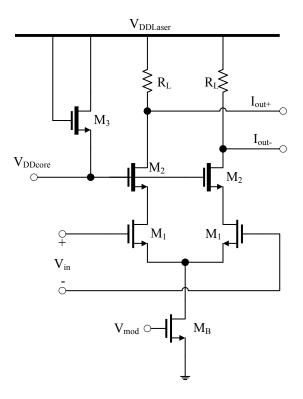

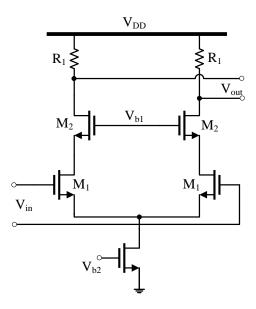

The laser diode driver (LDD) proposed in [47] consists of 3 stages as shown in figure 3.9. The output stage  $(M_7, M_{b7} \text{ and } R_3)$  is an open drain topology where the laser diode is connected externally to the drain of  $M_7$ .  $R_3$  and  $M_{b7}$  act as the tail current source which define the modulation current of the LDD. This stage offers the modulation current and enough voltage swing to the laser diode. The two differential pairs  $(M_1, M_{b1}, R_1, M_4, M_{b4} \text{ and } R_2)$  are voltage gain stages to provide enough voltage swing to the input of the output stage. The purpose of the source followers  $(M_2, M_{b2}, M_3, M_{b3}, M_5, M_{b5}, M_6$  and  $M_{b6}$ ) is to avoid the loading effect of the large gate width of the input transistor of the differential pairs. The presented LDD is realized in  $0.35\mu$ m CMOS technology achieving a data rate of 2.5 Gb/s. The maximum output current provided is 60mA with a 200mV voltage swing peak to peak. The power consumption is 500mW from a 5V supply. The amplifying stages including the source followers are consuming 45mA and dissipating 225mW from a 5V supply.

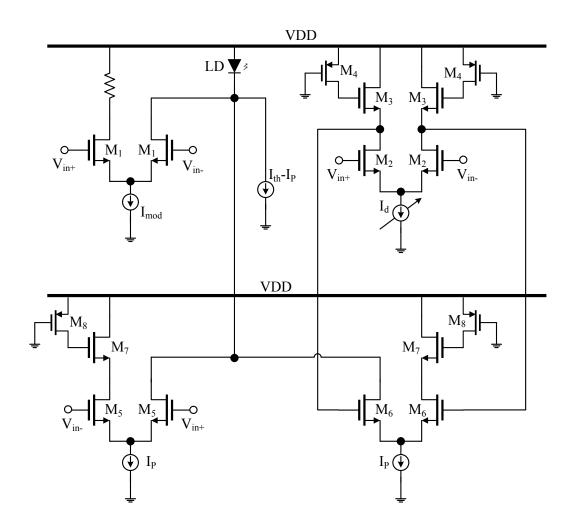

Figure 3.10 shows the output stage of LDD presented in [6]. The driver is a simple differential pair  $(M_1)$  with a tail current source defining the modulation current  $(I_{mod})$ . The laser diode (LD) and resistor are connected externally. The biasing current of the LD is defined by a DAC (not shown for simplicity). This paper enhances the switching speed of the LDD by using active inductive peaking and pre-emphasis techniques. The pre-emphasis circuit (PAC)  $(M_5, M_6, M_7 \text{ and } M_8)$  provides more current to the LD at every transition edge of the input data enhancing the switching speed of the LDD. The PAC needs a delay cell which is realized by a differential pair  $(M_2)$  with an active inductive load  $(M_3 \text{ and } M_4)$ . The proposed LDD is implemented in 0.35 $\mu$ m digital CMOS technology. It achieves a data rate of 2.5 Gb/s and modulation current of 20mA with power dissipation of 150mW from a 3V supply and area of 1200 $\mu$ m × 900  $\mu$ m.

FIGURE 3.10: LDD using active inductive peaking and pre-emphasis techniques in [6].

FIGURE 3.11: LDD with a push-pull source follower preamplifier proposed in [24].

The LDD introduced in [24] is shown in figure 3.11. The LDD consists of a pre-amplifier and output driver. The preamplifier is a differential pair  $(M_1, R_1)$  followed by a quasi push-pull source follower  $(M_2, M_3, M_4, M_5, M_6 \text{ and } M_7)$ . A quasi push-pull source follower is a classical source follower with two cross-coupled pairs This topology is used to avoid the asymmetric rise and fall edge of the signal caused by the classical source follower. The output driver is a simple differential pair  $(M_8)$  connected externally to an inductor and resistor to establish DC circuitry. The LDD was implemented in  $0.35\mu$ m CMOS process. The achieved data rate is 5Gb/s with maximum peak to peak voltage $(V_{p-p})$  of  $4.2V_{p-p}$  under 3.3V supply and  $6.2V_{p-p}$  under 5V supply. The chip dissipates 310mW and 945mW from 3.3V and 5V supply voltage, respectively. The chip area is  $0.57mm^2$ .

FIGURE 3.12: The proposed LDD architecture in [11].

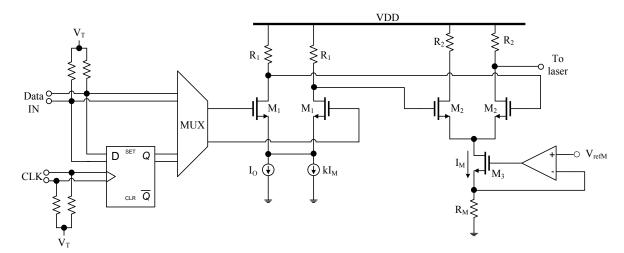

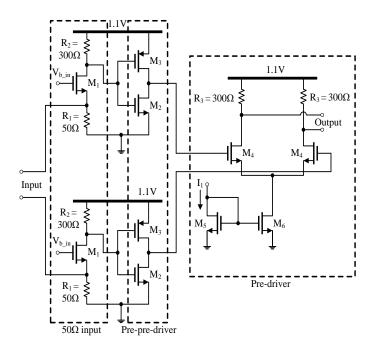

The LDD presented in [11] is shown in figure 3.12. The proposed LDD includes data retiming control, waveform shaping control and output driver. The LDD's input stage include a 50 $\Omega$  single to differential converter for both the clock (CLK) and the data inputs, a master slave flip flop for retiming control, a 2 to 1 multiplexer, a waveform shaping control with a tail current source proportional to the modulation current ( $I_M$ ) at the buffer stage and the output stage is a differential pair for providing  $I_M$  to the laser diode. The purpose of the offset current  $I_O$  is to increase the linearity of the buffer. The LDD is implemented in 0.25 $\mu$ m CMOS technology. It operates at a 3.8 Gb/s data rate and supports a maximum modulation current of 60mA. The chip consumes 37mA excluding the modulation and biasing current of the LD from 2/3.3V supply. The chip including pads is 1.2mm × 1mm.

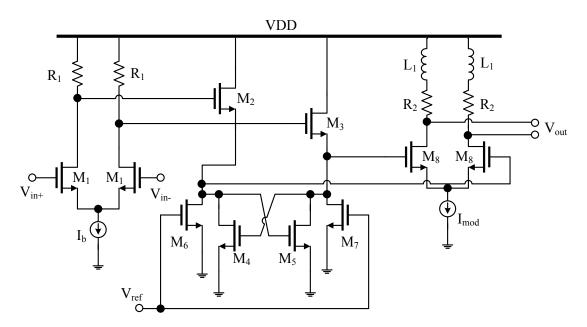

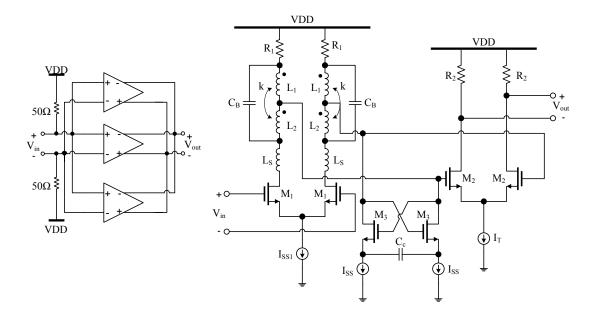

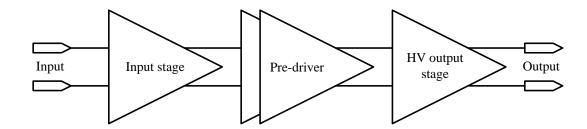

The LDD architecture proposed in [23] is shown in figure 3.13. The LDD as shown in the left hand side of the figure is formed of 3 identical slices connected in parallel. Each slice contains a pre-amplifier and output driver. The preamplifier  $(M_1, L_s, L_1, L_2 \text{ and } R_1)$  is a differential pair with three techniques to improve the bandwidth: Negative impedance

FIGURE 3.13: 10Gb/s LDD presented in [23].