# DIPLOMARBEIT

## VERGLEICH VON QUENCHERSCHALTUNGEN UND SPADs

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines

**Diplom-Ingenieurs**

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnologie

am

Institute of Electrodynamics, Microwave and Circuit Engineering

unter der Leitung von

Univ.Prof. Dr.ing. Horst Zimmermann Univ.Ass. Dipl.-Ing. Bernhard Steindl

durch

Samuel Gaspar

Mat. Nr.: 1428158

Wien, März 2018

Samuel Gaspar

# DIPLOMA THESIS

# COMPARISON OF QUENCHING CIRCUITS AND SPADs

| Institute:  | Institute of Electrodynamics, Microwave and Circuit Engineering            |

|-------------|----------------------------------------------------------------------------|

| Supervisor: | Univ.Prof. Dr.ing. Horst Zimmermann<br>Univ.Ass. DiplIng. Bernhard Steindl |

| Author:     | Samuel Gaspar<br>Mat. Nr. 1428158                                          |

Vienna, March 2018

### Abstract

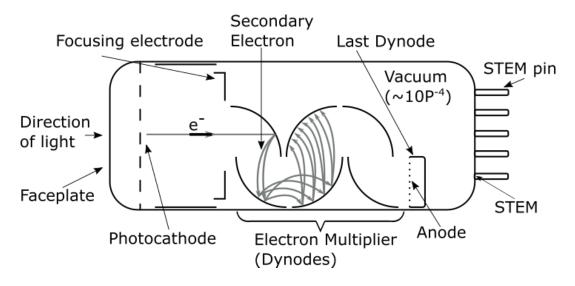

In the past years, there has been an increase of interest in the field of quantum information. Quantum objects, such as photons, are used to transfer or encode information in quantum information technologies. Single photon in the visible or near infrared range has extremely small energy, only around 10<sup>-19</sup> J. To detect such a small amount of energy, detectors with high sensitivity need to be deployed. Initially, photomultiplier tubes have been used for this purpose, but new detectors and technologies emerged in the recent years, such as superconducting nanowires, frequency upconversion, quantum-dot phototransistors and single photon avalanche diodes (SPADs). SPADs are probably the mostly used single photon detectors nowadays: they are reliable, offer great quantum efficiency, low dark count rate and high maximal counting rate. Si SPADs are used to detect photons in the visible or near infrared range and are more common, whereas SPADs fabricated from 3-5 semiconductors can be deployed for light detection in the telecommunication wavelength of 1.55 µm.

Detector device is, however, not the only component required for single photon light detection. These devices have to be connected to a quenching circuit that ceases the avalanche ignited by the photon and restores the bias voltage to ready the device for another detection. Some of the quenching circuit types are passive quenching circuits, passive quenching circuits with active reset and active quenching circuits, and these circuits can be integrated on a chip together with the SPAD, or produced from discrete components with discrete SPADs.

The choice of the detector type, circuit operating principle as well as the specific type of construction affect the performance of the device significantly. It is therefore of high importance to choose the right device and quenching circuit for the application to fulfil the required specifications.

In this work, two discrete Si SPADs from two different manufacturers will be compared together with 3 quenching circuits: two passive quenching circuits and one active. In the first chapter, most common detector types are introduced. Second chapter is dedicated to types of quenching circuits, both integrated and discrete. In the third chapter design and measurements of the SPADs and chosen circuits are presented and compared. Fourth chapter describes possible single photon detector applications.

### Kurzfassung

In den letzten Jahren hat das Interesse auf dem Gebiet der Quanteninformation zugenommen. Photonen werden Quantenobjekte, wie verwendet, um Informationen in Quanteninformationstechnologien zu übertragen oder zu kodieren. Ein einzelnes Photon im sichtbaren oder nahen Infrarotbereich hat eine extrem kleine Energie von nur etwa 10-19 J. Um solch eine kleine Menge an Energie zu detektieren, müssen Detektoren mit hoher Empfindlichkeit eingesetzt werden. Für diesen Zweck wurden zunächst Photomultiplierröhren verwendet, aber in den letzten Jahren sind neue Detektoren und Technologien entstanden, wie supraleitende Nanodrähte, Frequenz-Up-Conversion, Quantenpunktphototransistoren und Einzelphoton-Lawinen-Dioden (SPADs). SPADs sind heutzutage wahrscheinlich die am häufigsten verwendeten Einzelphotonendetektoren: Sie sind zuverlässig, bieten eine große Quanteneffizienz, eine niedrige Dunkelzählrate und eine hohe maximale Zählrate. Si SPADs werden verwendet, um Photonen im sichtbaren oder nahen Infrarotbereich zu detektieren, wohingegen SPADs, die aus 3-5 Halbleitern hergestellt sind, zur Lichtdetektion in der Telekommunikationswellenlänge von 1,55 µm eingesetzt werden können.

Die SPAD ist jedoch nicht die einzige Komponente, die für die Detektion von Einzelphotonenlicht benötigt wird. Der gesamte Detektor besteht aus einer SPAD in Kombination mit einer Quencherschaltung, die die durch das Photon gezündete Lawine stoppt und die Vorspannung wiederherstellt. Das ist notwendig um die Vorrichtung für eine weitere Detektion sensitiv zu sein. Einige der Quencherschaltungsarten sind passive Quencherschaltungen, passive Quencherschaltungen mit aktiver Rücksetz und aktive Quencherschaltung. Diese Schaltungen können zusammen mit der SPAD auf einem Chip integriert oder aus diskreten Komponenten mit diskreten SPADs hergestellt werden.

Die Wahl des Detektortyps, des Schaltungsprinzips sowie der spezifischen Bauart beeinflusst die Leistungsfähigkeit des Gerätes erheblich. Um die erforderlichen Spezifikationen zu erfüllen, ist daher von großer Wichtigkeit die richtige Kombination aus SPAD und Quencherschaltung für die gewünschte Anwendung zu wählen.

In dieser Arbeit werden zwei diskrete Si SPADs von zwei verschiedenen Herstellern mit drei Quencherschaltungen verglichen: zwei passive Löschkreise und ein aktiver. Im ersten Kapitel werden die gebräuchlichsten Detektortypen vorgestellt. Das zweite Kapitel widmet sich den integrierten und diskreten Arten von Quencherschaltungen. Im dritten Kapitel werden Design und Messungen der

ii

SPADs und ausgewählter Schaltungen vorgestellt und verglichen. Das vierte Kapitel beschreibt mögliche Anwendungen eines einzelnen Photonendetektors.

### Acknowledgement

I would like to express my thanks to Univ.Prof. Mag.rer.nat. Dr.techn.Horst Zimmermann for allowing me to write this Diploma thesis at the Institute of Electrodynamics, Microwave and Circuit Engineering. I would also like to thank my colleagues from the institute, mainly Univ.Ass. Dipl.-Ing. Bernhard Steindl and Univ.Ass. Dipl.-Ing. Dr.techn. Michael Hofbauer for their support and help with the measurement setup.

## Table of Contents

| Ab   | stract  |        |                                                 | i  |

|------|---------|--------|-------------------------------------------------|----|

| Ku   | rzfassu | ing    |                                                 | ii |

| Acl  | knowle  | edgen  | nenti                                           | v  |

| Ab   | brevia  | tions  | & Symbolsv                                      | ii |

| List | of Fig  | gures. | vi                                              | ii |

| List | of Ta   | bles   |                                                 | х  |

| 1.   | Sing    | le-ph  | oton detectors                                  | 1  |

|      | 1.1     | Dete   | ector characteristics                           | 1  |

|      | 1.2     | Dete   | ector technologies                              | 2  |

|      | 1.2.2   | 1      | Photomultiplier tubes                           | 2  |

|      | 1.2.2   | 2      | Superconducting nanowire single-photon detector | 4  |

|      | 1.2.3   | 3      | Frequency up-conversion                         | 5  |

|      | 1.2.4   | 4      | Quantum-dot phototransistor                     | 6  |

|      | 1.2.5   | 5      | Avalanche photodiodes                           | 6  |

|      | 1.2.6   | 5      | Single photon avalanche diodes                  | 7  |

|      | 1.2.7   | 7      | Comparison of single-photon detectors1          | 2  |

|      | 1.3     | Sing   | le-photon detector applications1                | 4  |

|      | 1.3.2   | 1      | Single-molecule fluorescence spectroscopy1      | 4  |

|      | 1.3.2   | 2      | Quantum random-number generator 1               | 7  |

| 2.   | Que     | nchin  | ng circuits                                     | 0  |

|      | 2.1     | Pass   | ive quenching circuits                          | 0  |

|      | 2.2     | Pass   | ive quenching circuit with active reset 2       | 5  |

|      | 2.3     | Activ  | ve quenching circuits                           | 6  |

|      | 2.4     | Mixe   | ed active-passive quenching circuits            | 1  |

|      | 2.5     | Spec   | ial quenching circuits                          | 5  |

|      | 2.6     | Circu  | uits with gated operation                       | 0  |

| 3.   | Com     | paris  | on of the quenching circuits4                   | 3  |

|      | 3.1     | Dete   | ector selection                                 | 3  |

|      | 3.2     | Circu  | uit simulations                                 | 6  |

|      | 3.2.2   | 1      | SPAD spice model 4                              | 7  |

|      | 3.2.2   | 2      | LTspice simulations                             | 0  |

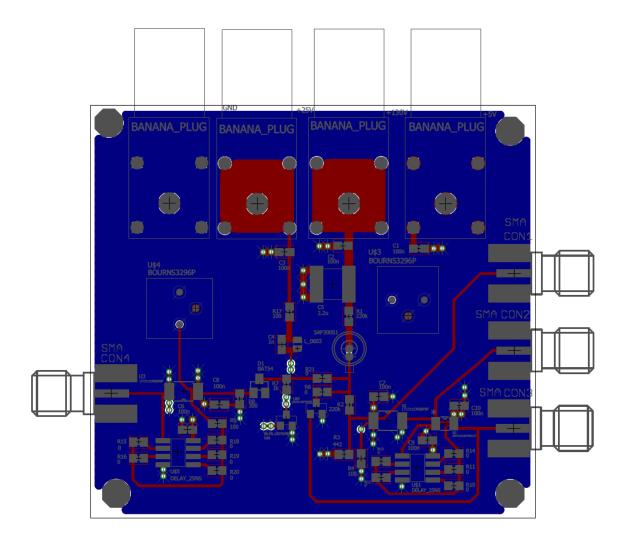

|      | 3.3     | PCB    | Design                                          | 6  |

|      | 3.4     | Mea    | surement setup                                  | 9  |

| 3    | 3.5     | Mea    | surement results                                | 0  |

| 3.5.1         | Passive quenching circuit with quenching resistor at the SPAD cathode | 60  |

|---------------|-----------------------------------------------------------------------|-----|

| 3.5.2         | Passive quenching circuit with quenching resistor at the SPAD anode   | 64  |

| 3.5.3         | Active quenching circuit                                              | 66  |

| Conclusion    |                                                                       | 70  |

| References    |                                                                       | 71  |

| Appendix A: P | CB layout                                                             | .76 |

# Abbreviations & Symbols

| APD             | avalanche photodiode                            |

|-----------------|-------------------------------------------------|

| FET             | Field effect transistor                         |

| Ge              | Germanium                                       |

| Не              | Helium                                          |

| К               | Kelvin                                          |

| PMT             | photomultiplier tube                            |

| PPLN            | Periodically poled lithium niobite              |

| QD              | quantum dot                                     |

| Si              | Silicium                                        |

| SNSPD           | superconducting nanowire single-photon detector |

| SPAD            | Single-photon Avalanche diode                   |

| V <sub>E</sub>  | Excess voltage                                  |

| WDW             | Wavelength-division multiplexer                 |

| η               | detection efficiency                            |

| λ               | wavelenght                                      |

| $	au_R$         | detector recovery time                          |

| In              | Indium                                          |

| Ga              | Galium                                          |

| As              | Arsenic                                         |

| Р               | Phosphorus                                      |

| h               | Planck's constant                               |

| υ               | photon frequency                                |

| τ <sub>D</sub>  | detector dead time                              |

| CD              | SPAD junction capacitance                       |

| Cs              | SPAD stray capacitance                          |

| QT              | Total charge                                    |

| T <sub>QD</sub> | delay of active quenching                       |

| QRND            | Quantum random number generator                 |

| Mb              | Megabit                                         |

| Kb              | Kilobit                                         |

| V <sub>BR</sub> | breakdown voltage                               |

| IC              | integrated circuit                              |

| MOS             | metal oxide semiconductor                       |

| N-MOS           | n-type metal oxide semiconductor                |

| P-MOS           | p-type metal oxide semiconductor                |

## List of Figures

| Figure 1-1 Schematic of a photomultiplier tube [9]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

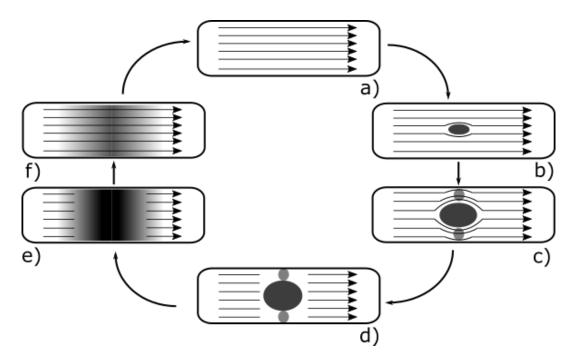

| Figure 1-2 Hotspot creation process in SNSPD [14]: a) SNSPD is biased below the specific current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nt for   |

| superconductivity loss and kept below the critical temperature. b) After photon absorption loc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | al       |

| resistive hotspot is created. c) hot electrons diffuse to the sides of the nanowire and the hotsp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ot       |

| grows. This forces the current density on the edges to increase, because the current flowing th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rough    |

| the nanowire is forced to the sides. d) If the current density at the edges exceeds critical current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | nt,      |

| barrier is formed across the whole device. e) Resistive barrier spreads across the nanowire three                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ough     |

| the Joule heating f) External electronic circuit is needed to reduce the bias current and the bar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | rier is  |

| fading. a) The device is fully superconductive again                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4        |

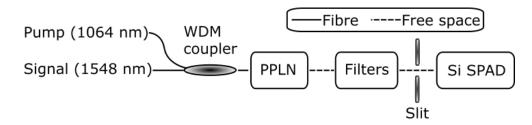

| Figure 1-3 Schematic picture of a frequency up-conversion detector [2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5        |

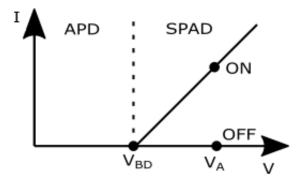

| Figure 1-4 APD vs SPAD region of operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7        |

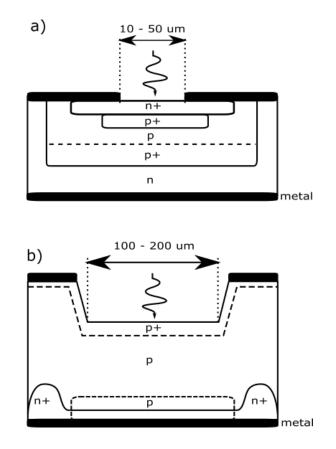

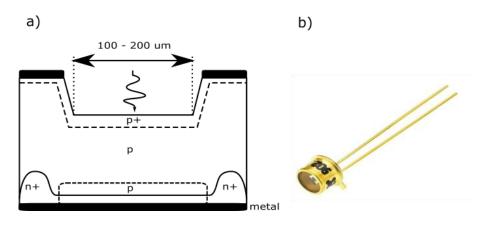

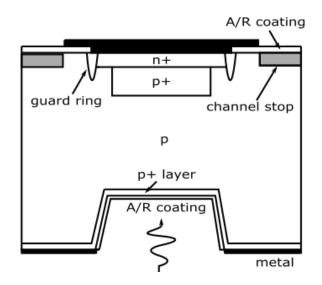

| Figure 1-5 Cross-section of SPAD device structures fabricated from silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

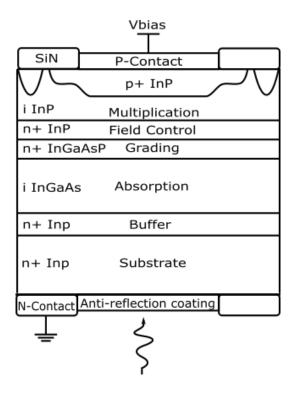

| Figure 1-6 Schematic of an InGaAs/ InP SPAD structure with a graduated InGaAsP layer is adde                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10       |

| Figure 1-7 Trap lifetime versus temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11       |

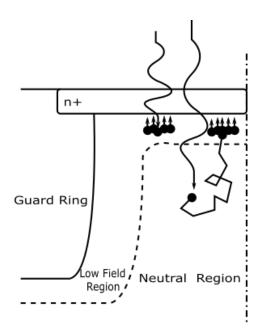

| Figure 1-8 Schematic of the avalanche effect caused by an electron generated in the neutral re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| the SPAD and an electron generated in the SPAD depletion layer nearby [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -        |

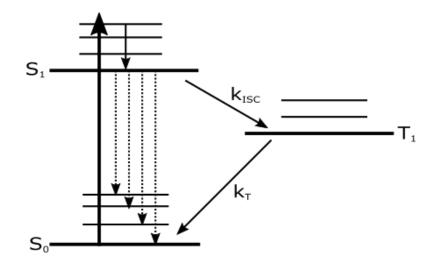

| Figure 4-1 Band scheme for single-molecule emission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

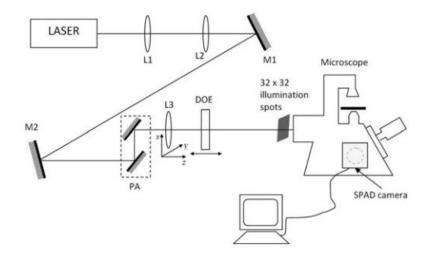

| Figure 4-2 Schematic of the optical setup for multifocal microscopy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

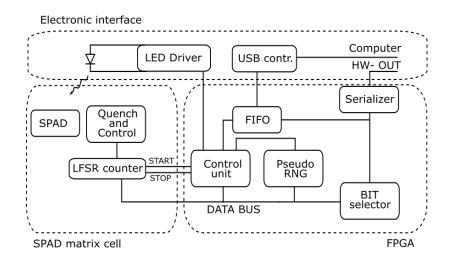

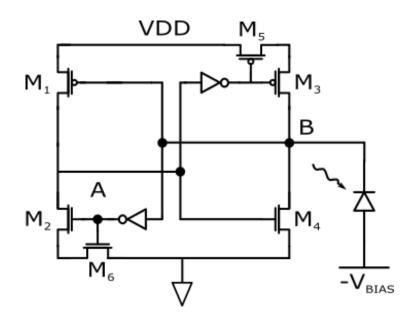

| Figure 4-3 Schematic of the QRNG module architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

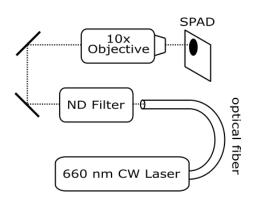

| Figure 4-4 Setup for QRNG chip optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

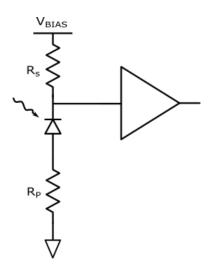

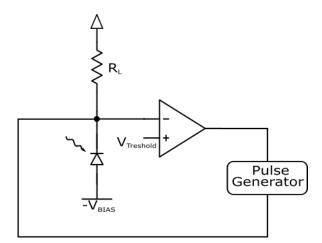

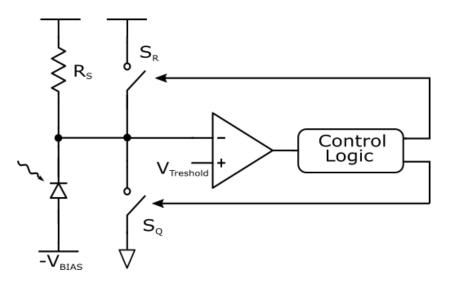

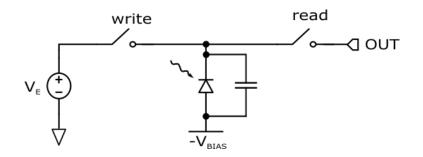

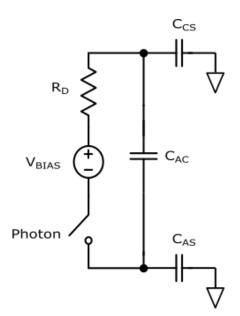

| Figure 2-1 Simple schematic of a passive quenching circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

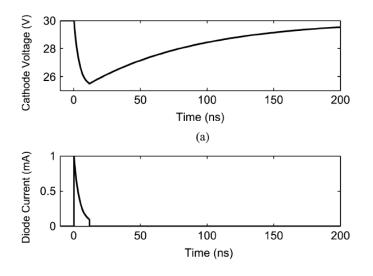

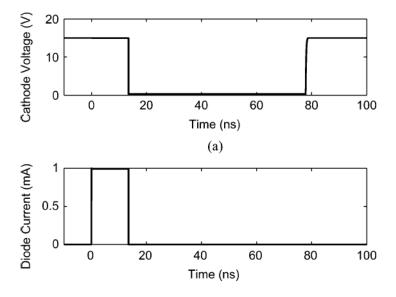

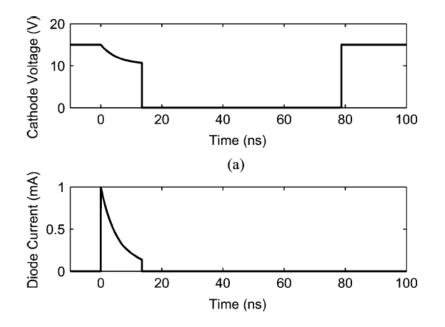

| Figure 2-2 Current and the voltage at the cathode of a SPAD [25]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

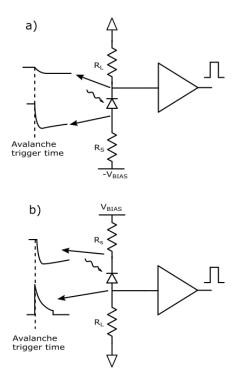

| Figure 2-3 Passive quenching circuit configuration a) in voltage-mode output; b) in current-mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

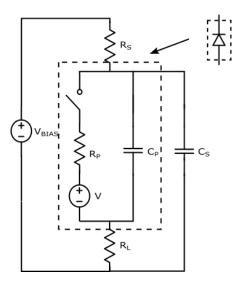

| Figure 2-4 Current output equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| Figure 2-5 Schematic of a passive quenching circuit with active reset [29]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

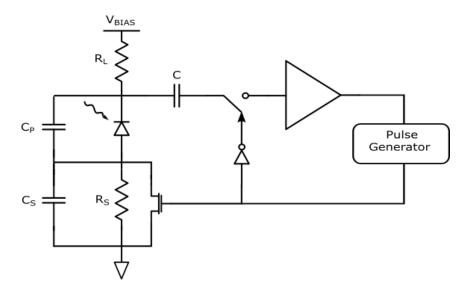

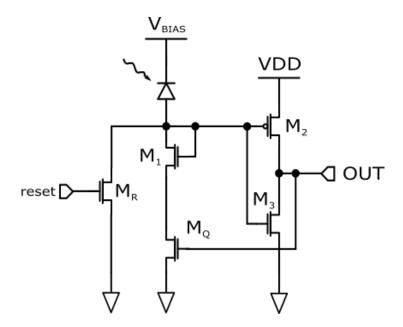

| Figure 2-6 Schematic of a basic active quenching circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| Figure 2-7 Voltage at the cathode and SPAD current waveforms [25]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

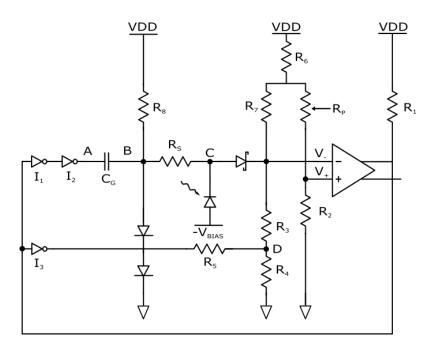

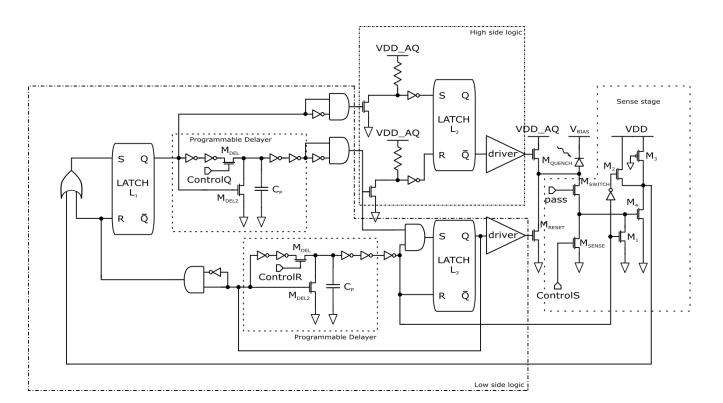

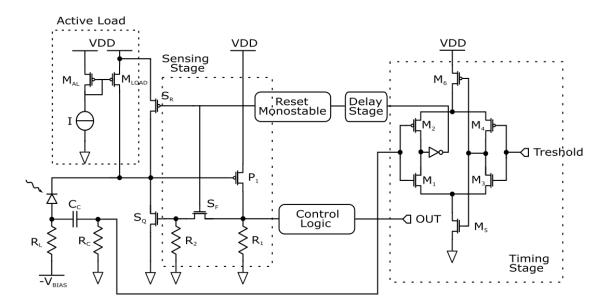

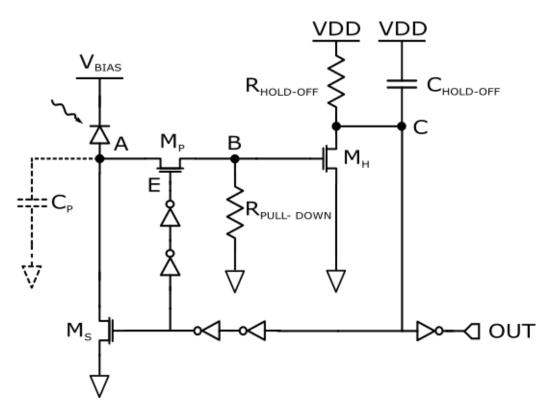

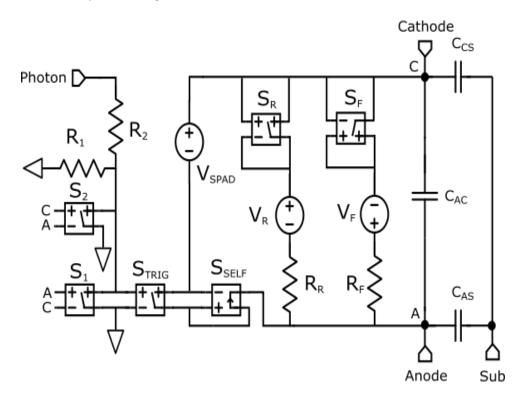

| Figure 2-8 An example of discrete active quenching circuit [31]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

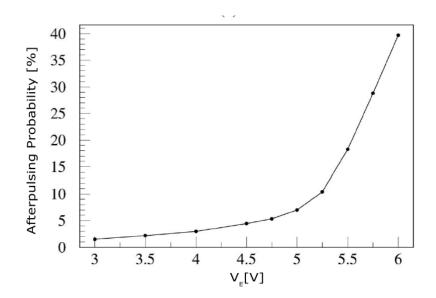

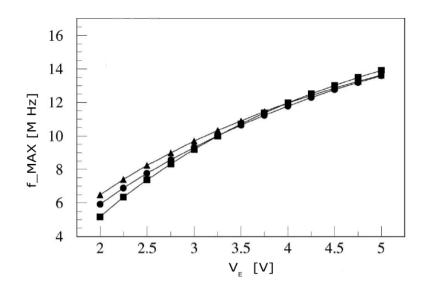

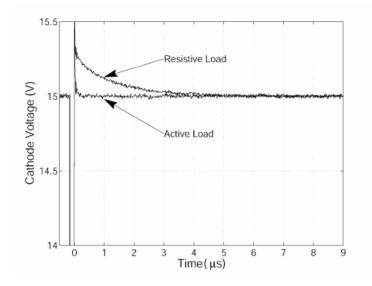

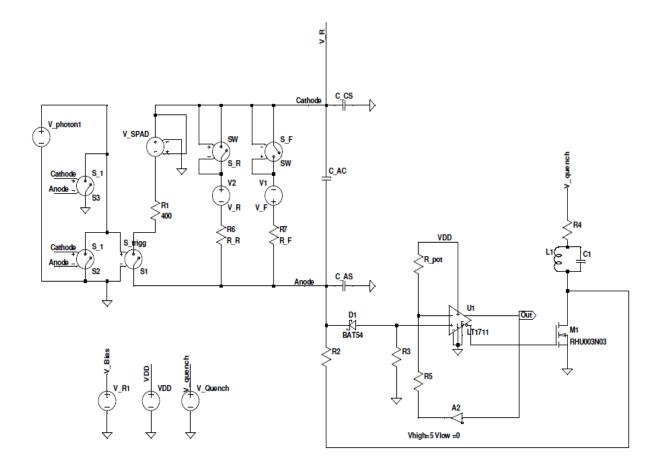

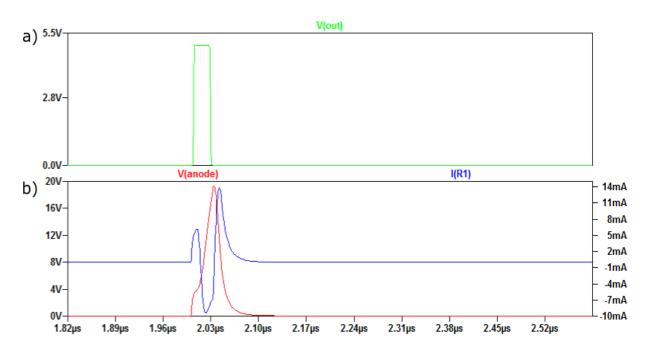

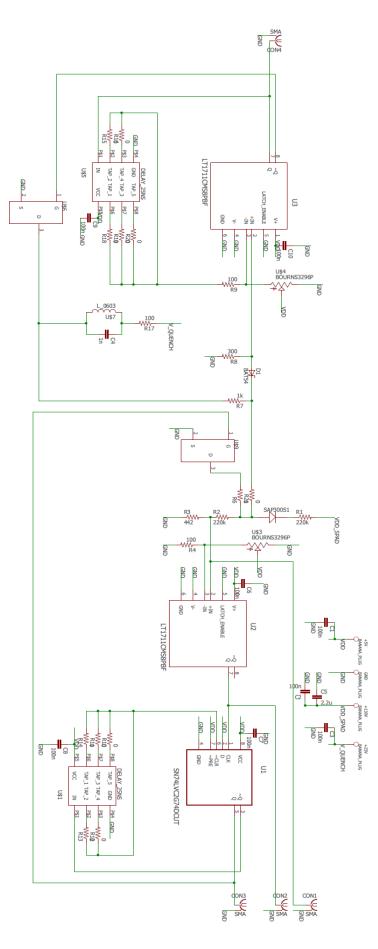

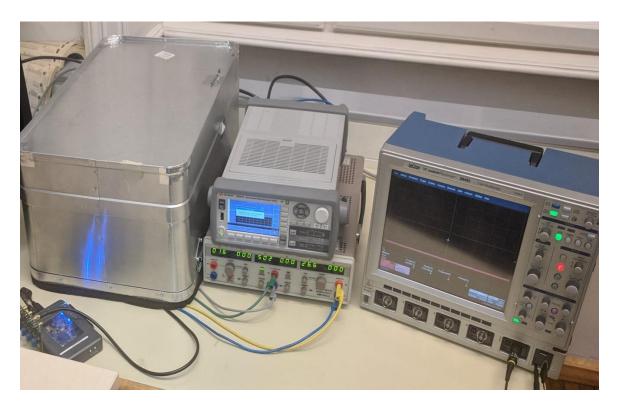

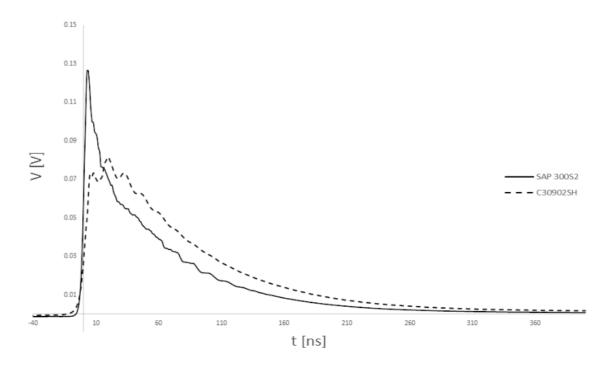

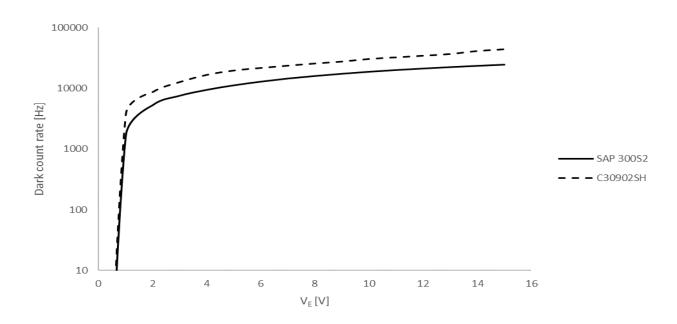

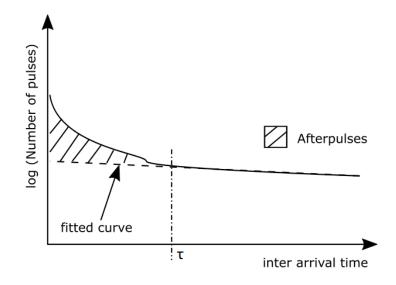

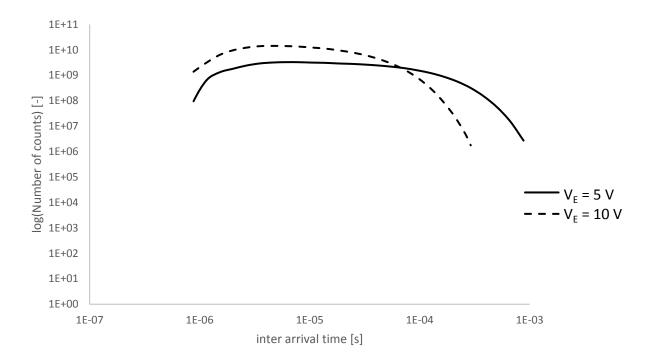

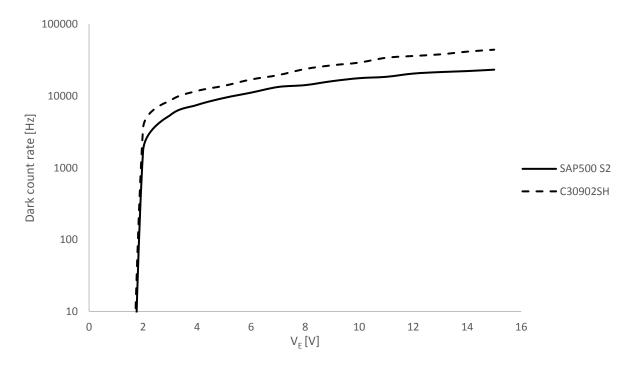

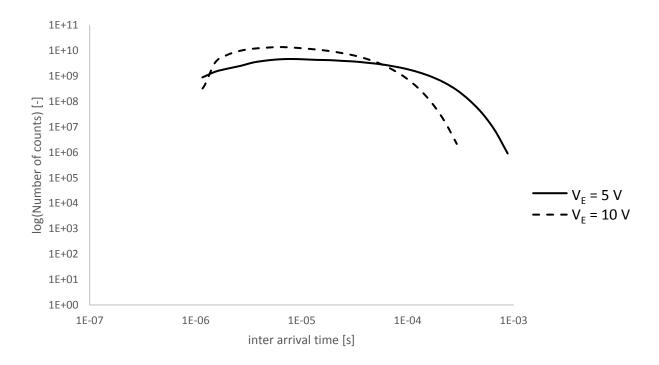

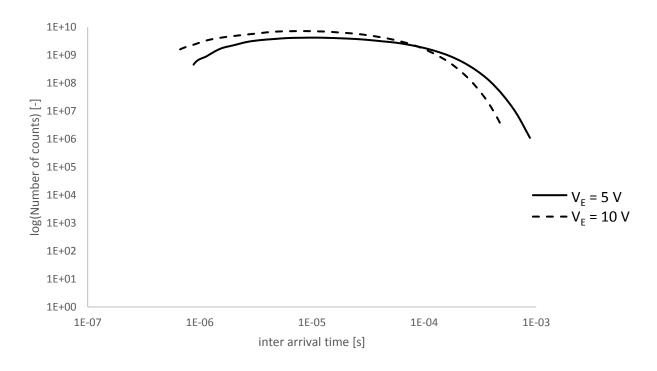

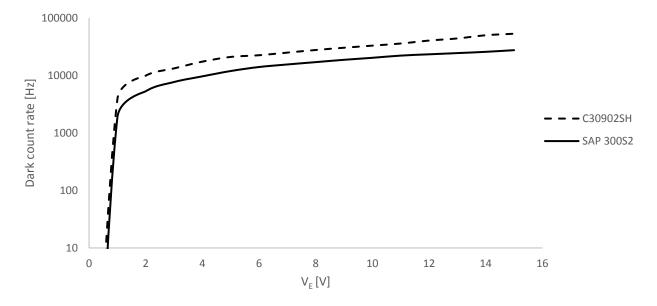

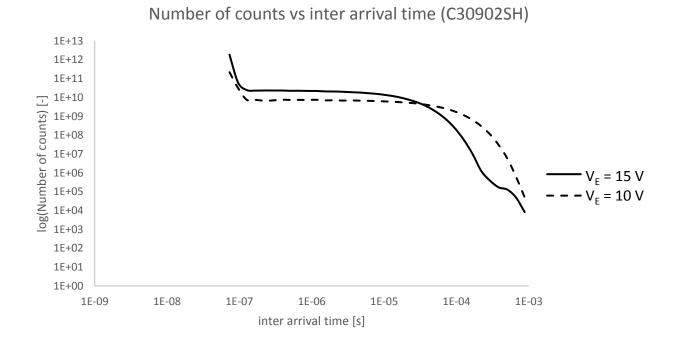

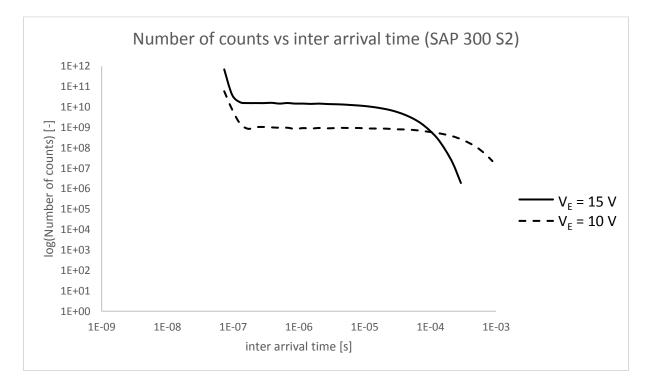

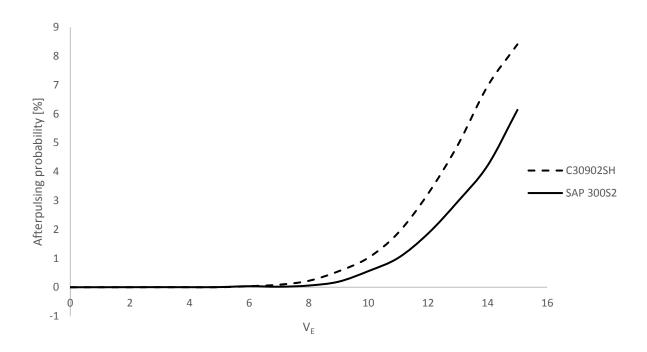

| Figure 2-9 Afterpulsing probability vs $V_{E}$ [31]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |