FAKULTÄT FÜR !NFORMATIK Faculty of Informatics

# Systematic Testing of Analog-Mixed Signal Systems

## DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

#### Technische Informatik

eingereicht von

### Mario Heindl, BSc.

Matrikelnummer 1125055

an der Fakultät für Informatik

Die approbierte Originalversion dieser Diplom-/ Masterarbeit ist in der Hauptbibliothek der Technischen Universität Wien aufgestellt und zugänglich.

The approved original version of this diploma o master thesis is available at the main library of the

ΤŪŪΒ

ttp://www.ub.tuwien.ac.at

Vienna University of Technology. http://www.ub.tuwien.ac.at/eng

der Technischen Universität Wien

Betreuung: Univ.Prof. Dipl.-Ing. Dr.rer.nat. Radu Grosu Mitwirkung: Univ.Lektor Dr. Dejan Nickovic

Wien, 15. Februar 2017

Mario Heindl

Radu Grosu

# Systematic Testing of Analog-Mixed Signal Systems

## DIPLOMA THESIS

submitted in partial fulfillment of the requirements for the degree of

## **Diplom-Ingenieur**

in

#### **Computer Engineering**

by

## Mario Heindl, BSc.

Registration Number 1125055

to the Faculty of Informatics

at the TU Wien

Advisor: Univ.Prof. Dipl.-Ing. Dr.rer.nat. Radu Grosu Assistance: Univ.Lektor Dr. Dejan Nickovic

Vienna, 15<sup>th</sup> February, 2017

Mario Heindl

Radu Grosu

## Erklärung zur Verfassung der Arbeit

Mario Heindl, BSc. Wiener Strasse 23, 2120 Wolkersdorf

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Wien, 15. Februar 2017

Mario Heindl

## Danksagung

An dieser Stelle möchte ich mich bei meinen Betreuern, Prof. Radu Grosu und Dr. Dejan Nickovic, für ihre Unterstützung bedanken. Sämtliche Diskussionen trugen dazu bei, diese Masterarbeit Schritt für Schritt zu verbessern. Dejans Rat zur Implementierung sowie seine Feedbacks hatten großen Anteil daran diese Arbeit zu vervollständigen. Ebenso war Radus Feedback ein wichtiger Teil, um die Arbeit in dieser Qualität fertigzustellen.

Ebenso danken möchte ich Dieter Haerle vom Kompetenzzentrum für Automobil- und Industrieelektronik für all die Zeit die er aufgebracht hat, um mich beim Erreichen der Ziele dieser Arbeit zu unterstützen. Ohne die gemeinsamen Diskussionen, Debugging Sessions und die Koordination wäre es nicht möglich gewesen die hier vorgestellten Lösungen zu implementieren. Weiters danke ich auch Stephen Sabanal von Infineon Technologies für seinen Support betreffend des ATE Tests, der mir beim Vertsändnis und der Modellierung sehr geholfen hat. Vielen Dank auch an Hermann Tauber von Infineon Technologies, ohne dessen Erweiterungen im bestehenden GPIF Fileformat es nicht möglich gewesen wäre diese Masterarbeit in der bestehenden Form fertigzustellen.

Mein Dank gilt auch meinen Eltern, Andrea Heindl und Wolfgang Loho, die mich bereits mein ganzes Leben lang unterstützen und die mir dieses Studium ermöglichten. Auch bin ich meiner Freundin Alexandra Leukauf dankbar, die mich all die Zeit unterstützt und motiviert hat.

## Acknowledgements

I would like to express my gratitude to Prof. Radu Grosu and Dr. Dejan Nickovic for supervising me throughout this thesis. Discussions with them improved this thesis step by step. The practical support from Dejan and his reviews helped me quite a lot to finish this thesis. Also Radu's feedbacks were important to finish this thesis with this quality.

Furthermore I want to thank Dieter Haerle from the Kompetenzzentrum für Automobilund Industrieelektronik (KAI) for all the discussions, debugging sessions and the coordination during the practical part of this thesis. He spent a lot of time in supervising me to achieve all the targets. I also want to thank Stephen Sabanal from Infineon Technologies for his support regarding the ATE Test which helped me quite a lot to understand and model the simulation environment. Many thanks also to Hermann Tauber from Infineon Technologies. Without his extensions in the existing GPIF file format, it would not have been possible to finish the practical part of this thesis in that kind of way.

Thanks also to my parents Andrea Heindl and Wolfgang Loho for supporting me my whole life. They enabled the possibility of studying for me. I am also grateful for the support of my girlfriend, Alexandra Leukauf, who supported and motivated me all the time.

## Kurzfassung

Ein wichtiger Schritt im Design-Flow von Analog Mixed-Signal Systemen ist die Post-Silicon Verifikation. Sie dient dazu, um Random Manufacturing Defects zu erkennen und kostenintensive Field Returns vom Kunden zu verhindern. Diese Art von Test wird durch das Automatic Test Equipment (ATE) unterstützt. Ein ATE dient dazu, um analoge sowie digitale Stimuli anzuwenden sowie Messungen durchzuführen anhand derer verifiziert wird, ob das System die Spezifikationsanforderungen erfüllt.

Die heute am meisten verbreitete Testmethode zum Verifizieren von Analog Mixed-Signal Systemen ist Parameter Oriented Testing (POT). Die größte Schwäche dieser Methode liegt darin, dass keinerlei Aussage über die Testcoverage bezüglich Random Manufacturing Defects getroffen werden kann. Eine Alternative, um eine höhere Coverage zu erreichen ist Defect Oriented Testing (DOT). Dazu ist es notwendig, die aktuelle Coverage der existierenden Tests zu analysieren und zu messen.

Im Rahmen dieser Arbeit wurde ein Framwork zur Unterstützung der Analyse der Testcoverage entwickelt. Dazu wird ein beliebiges ATE Testprogramm übersetzt und in einer Simulationsumgebung ausgeführt. In dieser Simulationsumgebung ist es möglich Random Manufacturing Defects zu injezieren und die Effektivität der aktuellen Tests zu messen.

In einem ersten Schritt werden die Teile des ATE und die verwendeten Testinstrumente vorgestellt, bevor die zu modellierenden Funktionalitäten identifiziert werden. Aufbauend auf diesen Informationen gibt diese Arbeit einen Überblick darüber wie diese modelliert werden können. Zusätzlich wird eine Methode vorgestellt, um ein existierendes, allgemeines ATE Testprogramm automatisch in ein Format zu übersetzen, das von der Simulationsumgebung importiert und ausgeführt werden kann. Diese Ergebnisse ermöglichen es, ein ATE Testprogramm mit minimaler manueller Interaktion und einem großen Anteil an Wiederverwendung von vorhandenen Informationen im Rahmen einer Simulation auszuführen. Um Aussagen über die Simulationszeit und die Funktionalität der vorgestellten Methode treffen zu können, wurde der gesamte Prozess anhand eines existierenden Chips, zur Verfügung gestellt von Infineon Technologies, verifiziert.

## Abstract

Post-silicon verification consists of testing and detecting random manufacturing defects just before its delivery to the customer. This is an important verification step that allows preventing costly field returns. This type of tests are executed by the *automatic test equipment* (ATE), which provides both ,analog and digital stimuli, and measurement units to check whether the design meets its specification requirements.

Nowadays, parameter oriented testing (POT) is the predominant testing method used by industry for the verification of analog and mixed-signal designs. The main drawback of POT is the relative lack of coverage information that it provides with respect to random manufacturing defects, e.g. opens and shorts caused by particles during the manufacturing process. More recently, *defect oriented testing* (DOT) has been proposed as an alternative testing method that can achieve higher test coverage than POT. In order to achieve this goal, it is essential to be able to analyze and measure the coverage of existing test suites.

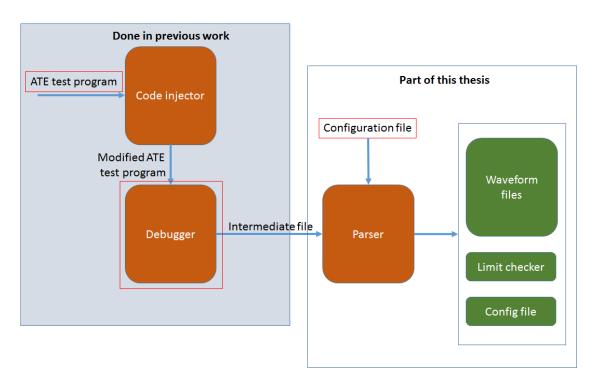

In this thesis, we develop a framework that enables and facilitates the coverage analysis of ATE tests by allowing translation of arbitrary ATE test programs into a given simulation environment. The simulation environment allows fault injection that mimics manufacturing defects and thus can be used to assess the effectiveness of the existing ATE test programs.

We first introduce the ATE environment and its instruments. We then identify the ATE functionality that needs to be supported in the simulation environment, and we propose a methodology for modelling it. Furthermore, we develop a procedure for automatically translating general ATE test programs into a format, which can be imported into and executed from a simulation environment. The resulting outcomes enable applying ATE test programs during the simulation runs with a minimal manual interaction, thus considerably increasing automation and reuse in the testing effort. We implement the results and evaluate them on a real industrial chip, provided by Infineon Technologies to ensure the correct functionality of the translation and simulation process as well as for getting an idea about the needed simulation time for a whole ATE test.

# Contents

| K        | Kurzfassung x                |                                      |                        |  |  |  |

|----------|------------------------------|--------------------------------------|------------------------|--|--|--|

| A        | Abstract                     |                                      | xiii                   |  |  |  |

| С        | Contents                     |                                      | $\mathbf{x}\mathbf{v}$ |  |  |  |

| 1        |                              |                                      | 1                      |  |  |  |

|          |                              |                                      |                        |  |  |  |

|          |                              |                                      |                        |  |  |  |

|          | 1.3 Contribution of this wo  | ork                                  | . 7                    |  |  |  |

| <b>2</b> | 2 Background to automatic    | c test equipment (ATE) test programs | 11                     |  |  |  |

|          | 2.1 Requirements for an AT   | TE test                              | . 12                   |  |  |  |

|          | 2.2 General setup $\ldots$ . |                                      | . 12                   |  |  |  |

|          | 2.3 Common test cases in i   | industry                             | . 16                   |  |  |  |

| 3        | 3 Setting up the simulation  | n environment                        | <b>21</b>              |  |  |  |

|          | 3.1 Modelling of an ATE te   | est                                  | . 22                   |  |  |  |

|          | 3.2 ATE instrument model     | l                                    | . 26                   |  |  |  |

| <b>4</b> | 4 Translation of an ATE te   | est program                          | 37                     |  |  |  |

|          | 4.1 Identification of needed | l functionalities                    | . 38                   |  |  |  |

|          | 4.2 General test program la  | anguage                              | . 46                   |  |  |  |

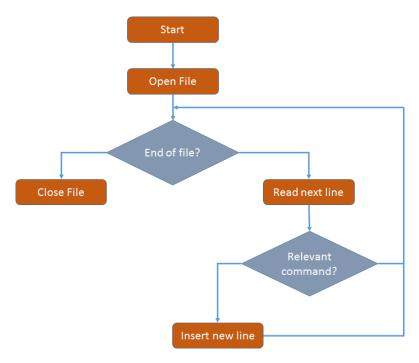

|          | 4.3 Translation process      |                                      | . 47                   |  |  |  |

|          | 4.4 Code injection $\ldots$  |                                      | . 48                   |  |  |  |

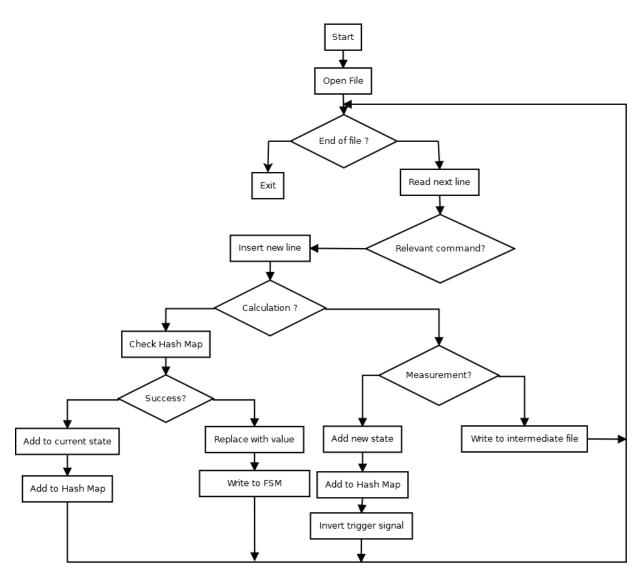

|          | 4.5 Parsing of the intermed  | liate file                           | . 50                   |  |  |  |

|          | 4.6 Creating the limit check | ker                                  | . 51                   |  |  |  |

|          | 4.7 Example translation for  | r the continuity test                | . 55                   |  |  |  |

| <b>5</b> | 5 Evaluation                 |                                      | 61                     |  |  |  |

|          | 5.1 Setup $\ldots$           |                                      | . 61                   |  |  |  |

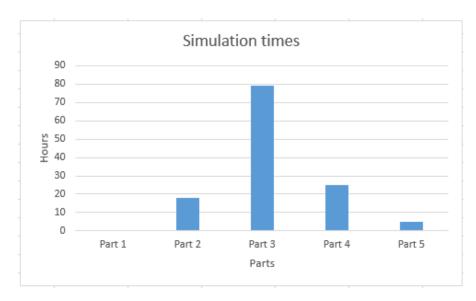

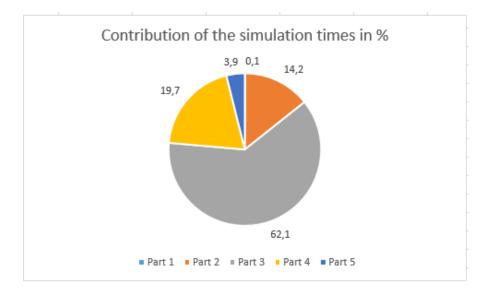

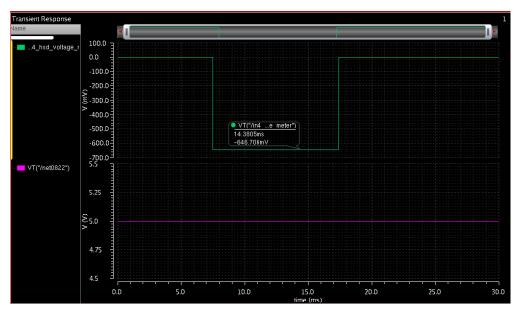

|          | 5.2 Simulation time $\ldots$ |                                      | . 63                   |  |  |  |

|          | 5.3 Fault detection $\ldots$ |                                      | . 65                   |  |  |  |

| 6  | Conclusion and future work | 69 |

|----|----------------------------|----|

| 7  | Appendix                   | 73 |

| Li | st of Figures              | 77 |

| Li | st of Tables               | 78 |

| Bi | bliography                 | 83 |

## CHAPTER

## Introduction

#### 1.1 Motivation

Nowadays, the importance of analog mixed-signal (AMS) designs in system on chips (SoC) is constantly increasing, resulting in elaborated interactions between heterogeneous components and consequently a higher complexity of the designs. Since reliability and robustness have become more and more important for the customers, especially in safety critical applications, testing AMS designs turns out to be a non trivial challenge for the industry. From the industry's point of view there are certain requirements regarding testing methodologies: since testing time contributes significantly to the manufacturing costs, a major target is to keep this time as low as possible while keeping a high test coverage. Whereas in the domain of digital design well-known ATE methodologies, like scan-chains, are used, there is no such systematic approach for AMS designs.

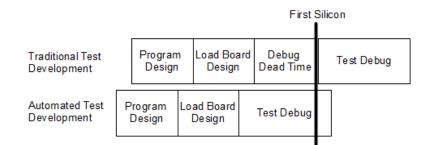

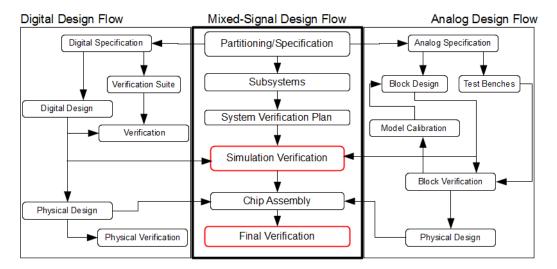

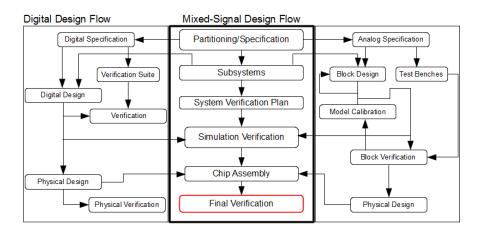

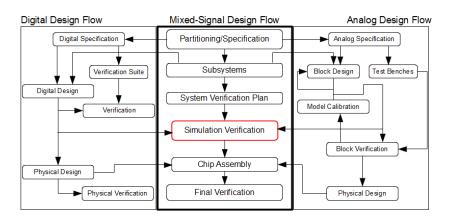

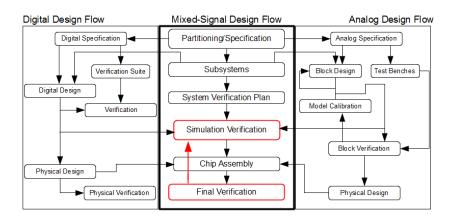

Figure 1.2 gives an overview of a simplified AMS design flow, based on [BSED07]. As one can see, the design is divided into an analog as well as a digital part, which are then combined in the *mixed-signal design flow*. First of all, the mixed-signal specification is divided into an analog and a digital specification, such that both parts can be developed independently from each other. In the analog design flow, shown on the right hand side, the design engineers have to define several blocks, which are then combined for the complete analog design. In parallel, the test engineers define the test benches, used for the verification of the analog part. After a verification step, the model is calibrated, such that a precise model of the device is available in a simulation environment. When the verification was successful and the model is complete, physical development of the analog part starts. The design of the digital parts of an AMS design is similar: the digital components are designed and tested based on a verification suite. When the design is complete, physical manufacturing can start. Both parts are combined in the mixed-signal design flow. Based on the specification, a verification plan is developed, describing all the scenarios and test cases, which need to be verified. The verification takes place at two different levels in this design flow which are highlighted in Figure 1.2. During the *Simulation Verification* the test benches are executed in a simulation run, for verifying that all functional requirements of the specification are met. Note, that in [RGA02] it is shown how simulation runs might influence time-to-market in a positive way (Figure 1.1). In contrast to the traditional approach, verification can be started earlier which yields in much lower time-to-market since the debugging time after the first silicon is reduced significantly.

Figure 1.1: Time-to-market improvement by ATE

Caused by high simulation times, this is a common bottleneck in the design flow for AMS systems. For this purpose often simplifications are used to speed up the simulation runs. After all the test benches have been executed in the simulation and the functional verification was successful, manufacturing of the chip starts.

Figure 1.2: Analog Mixed-Signal Design Flow [BSED07]

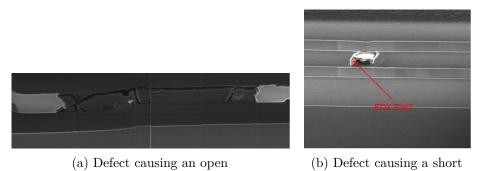

Although the functional behaviour has been verified well during the simulation phase, it cannot be guaranteed that no faults will occur during the manufacturing process. The reason are the so called *random manufacturing defects*. This kind of defects is caused

Figure 1.3: Random Manufacturing Defects

for instance by particles during the manufacturing process, yielding in an open or a short. Figure 1.3 visualizes these two kinds of defects. On the left hand side, one can see an open, where the wires are not connected any more, whereas on the right hand side, a short between the metal layers is shown - two layers, which are not supposed to be connected, are connected now.

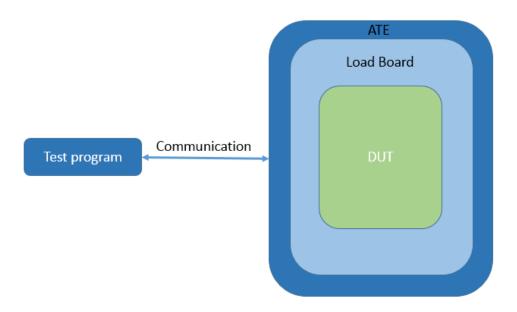

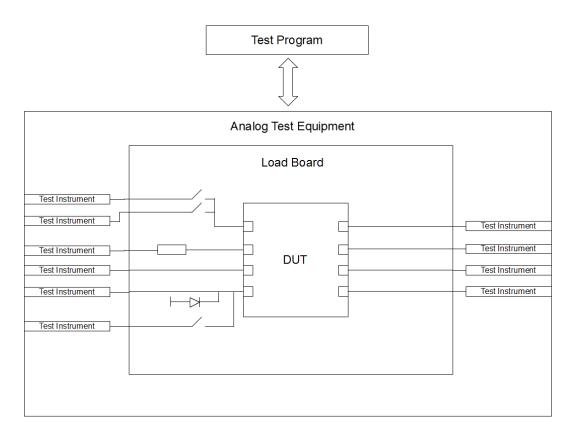

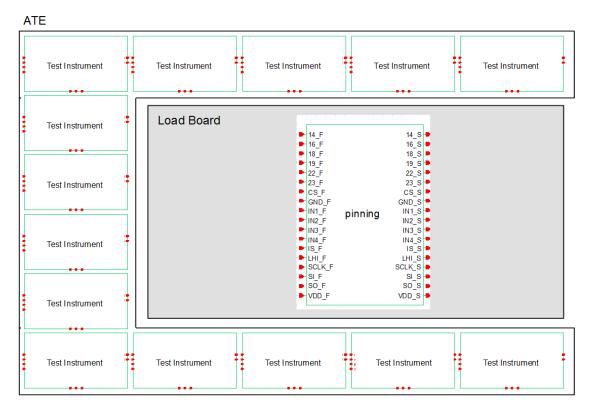

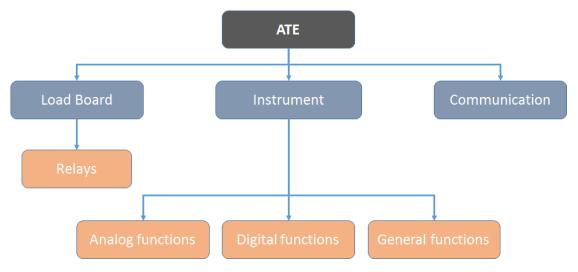

For this *final verification* an ATE is used, which provides different test instruments, which are able to force a specific voltage, current as well as wave forms as inputs to the device under test (DUT). Furthermore, these instruments have the possibility of measuring analog signals and verify if their value lies within the user-specified limits. In Figure 1.4 a schematic of the setup of an ATE test is shown. The DUT is connected to the instruments of the ATE via the *load board*, which has the purpose of realizing dynamic connections. For instance, relays on the load board are used for connecting various test instruments to a special pin of the DUT during different tests. Apart from the hardware, the ATE consists of a test program, describing the test run (e.g. when relays shall be opened/closed, actual pin levels, current or voltage to apply). Moreover, measurements performed by the ATE hardware can be read and post-processed to check if the recorded values lie within specified limits or not. This is referred to as *parameter oriented testing* (POT).

The main problem of a POT test is the unknown test coverage. It can never be ensured, that all possible defects of a device are detected by the test. Therefore, whenever a *random manufacturing defect* occurs that is not covered by the POT test, this yields in a field return by the customer which is very critical in semiconductor industry. Currently, companies have a big interest to get a quantitative number concerning their test coverage in order to improve it. Other drawbacks of a POT test are:

1. **Test time:** This unit is a significant factor regarding manufacturing costs. Therefore it is necessary to keep test time as low as possible. With the current approach of testing, single test cases might be redundant and could be dropped out - there is a high potential for improving test times.

Figure 1.4: Schematic of the test environment

- 2. **Complexity:** The quality of the test run mainly depends on the experience of the test engineer. Designing test cases is a complex task caused by the number of interactions in AMS designs and the lack of insight into the different tests.

- 3. Bottleneck in the design process: Designing the load board and implementing the test program are time consuming tasks. Since the test engineers have to work with prototypes, development of the test program starts in a late phase of the design process since there is no possibility for testing the ATE test program earlier.

Caused by the lack of insight into the ATE test because of limited measurement resources, these challenges cannot be addressed at the stage of *Final Verification* in the design flow. It is necessary to go back one step to the *Mixed-Mode System Verification*. At this level, a testing approach which has already been proposed in the 90's in [SGOT98] or [KTH<sup>+</sup>11] can be used: the defect oriented test (DOT). Some industrial experience of DOT is given in [Xin98]. It has been shown that this kind of test indeed comes up with higher test coverage.

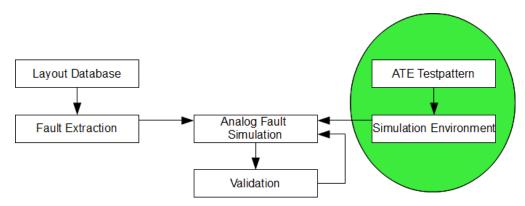

The idea of a DOT is to inject a specific fault into a model of the DUT and check with a simulation of the ATE test program, whether this fault would be detected or not. A schematic of the work flow for DOT is shown in Figure 1.5. On the left hand side the faults are identified and extracted such that they can be injected into the simulation model of the DUT while on the right hand side the ATE test patterns are executed within a simulation environment of the ATE. During the Analog Fault Simulation, it is checked whether an injected fault has been detected by the simulation or not. With the advantages of getting an optimized test run and having a quantitative number of the test coverage (as has been shown in [Xin98]) this testing method has high potential for being used in industry, but still there are different challenges like high simulation times and the translation from an ATE test into some kind of format which can be understood by the simulation environment.

Figure 1.5: Flow diagram of DOT

This thesis focusses on the second of these challenges. We show, how to set up a methodology for translating the ATE test program in such a way that it can be simulated in a pre-silicon simulation environment.

#### 1.2 Related Work

Since DOT testing is not a very new idea, there have already been several proposals of how to verify the correct behaviour of a device in the context of a simulation environment.

One of the big topics which is actually dealt with in research is *formal verification*. [ZT09] gives an overview about different approaches of *formal verification*, like *equivalence checking*, model checking or deductive verification methods.

Equivalence checking is based on two models, one of the specification and another one for the implementation of the AMS design. The question which has to be answered during the check is whether these models are equal with respect to some notion of equivalence or not. At this point, the approach of equivalence checking becomes challenging: how should equivalence between the models be defined? An example is given in [BHA95] where it is proposed to use the transfer function of the models to define their equality. Since the calculation of the transfer function in AMS designs is non trivial, this technique has been restricted to linear circuits in the content of their work. As one can see, equivalence checking is a complex approach, which needs a lot of computation time and effort, yielding in rare usage in industry.

Another approach which was dealt with is *deductive verification* [Fil11] based on inference rules. Tools were used to perform *equivalence checking* based on such rules for instance in

#### 1. INTRODUCTION

[GV99]. The problems occurring regarding *deductive verification* are quite similar to the challenges faced with *equivalence checking*: the models have to be linearized to reduce the complexity and the computation effort is much too high.

The third kind of *formal verification* method to be mentioned is *model checking* [CGP99]. Here, starting from a specific state, all possible signal sequences are checked whether they lead to a bad state or not. For this decision, the user first has to define the specification with a temporal logic formula. This translation is a common bottleneck during *model checking* since it cannot be done automatically yet. Secondly, the state explosion problem yields in high computational cost causing that *model checking* still needs an insufficient amount of time.

As one can see, all those verification methods have several challenges in common: computation time, complexity and strong restrictions to the class of circuits that can be addressed. Therefore, unfortunately, they are insufficient for industrial practice. Instead of such an exhaustive methodology, which is able to detect all possible faults, an incomplete approach is the common way for testing. Based on a set of test cases, derived from the specification at the beginning of the design flow, the correct functionality of the device is verified - with the disadvantage of not being able to detect every single fault.

Defect oriented testing techniques, presented in [KTH<sup>+</sup>11], [Xin98] and [BXvK<sup>+</sup>99] all have in common the usage of a DOTSS (defect oriented test simulation system) tool. This tool requires the manual definition of stimuli, the test bench and the limits and supports only the testing of shorts. This lack of an automatic translation yields in high costs.

An approach which can also be used for setting up a simulation environment for AMS tests is proposed in [Lan90]. In the content of this work, a *test pattern specification language* is proposed for translating stimuli in the other way round. The design engineer has to define the test run with this special language which can then be translated into a format supported by the tester. Although the translation could be also done in the other direction, the problem with this approach is the lack of the possibility of injecting and identifying faults in the simulation environment resulting in the problem of not being usable for DOT.

Anther methodology has already been proposed in [KRT02], where a *test setup simulation* was introduced which translates an ATE test program from a specific format into a general file format called GPIF. Furthermore the instruments were modelled to simulate the given test program out of this GPIF file. Also in [BK92], there was a focus on this approach. They introduced a tool called DANTES, which provides a simulation environment as well as a database to share information between the design and the test engineer. The problem of setting up a simulation environment and sharing information was already addressed in [Web89]. All these proposed solutions have one big drawback in common: a lot of manual interaction is needed for the test setup - there is no automatic translation between the design and the test stage in the design flow. Moreover, they neglect the automatic verification (check of certain limits) and are focussed on debugging

a test program with less accuracy which is not sufficient for a DOT test. In other works, e.g. [RKR03], there was just a view at modelling a specific part of the ATE test - the *load board*.

[DG04] for instance gives a more formal approach of defining an ATE test concept. This approach on the one hand shall solve the problem of the manual interaction in the solutions mentioned before. Anyway, the focus of this work also lies on the debugging of a test program instead of the fault injection, caused by the lack of accuracy.

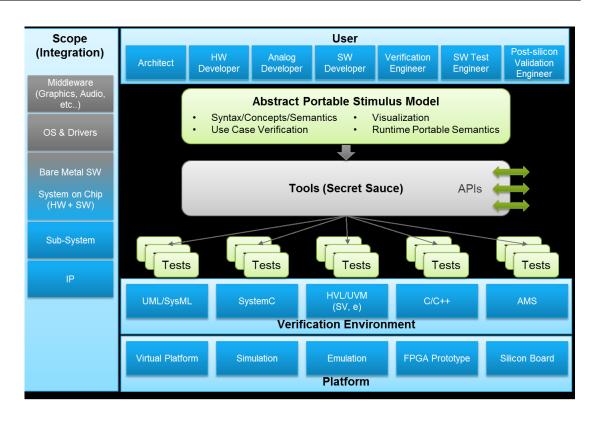

The challenge of defining a usable format through all the design stages has also been tackled by the recently formed Accellera Proposed Working Group with the aim of defining a standard for so called portable stimuli. A portable stimulus is defined once and can be reused through all stages in the design flow. Furthermore it should be not just reusable within the design process, but also between different tools of different vendors. Members of this working group are big companies regarding AMS designs, like Cadence, Mentor Graphics or Synopsis.

The abtsract language for defining the stimuli shall be independent of all the currently used languages. The existence of reusable stimuli would certainly enable a speed up of the verification time and increase the robustness of the whole design process [TSR<sup>+</sup>09]. In the last update of the working group, a presentation was given where in Figure 1.6 a rough overview of the usage of this abstract language is given. The target is to define an Abstract Portable Stimulus Model which can be parsed into different languages used for verification or testing with one single tool. Therefore this language can be used through the whole design process.

As one can see, the setup of the simulation environment and translation of a test program is not a trivial task. In today's solutions the user has to define test bench, limits and stimuli manually since there is no common format which can be used in all phases of the design process. Although defining standards for portable stimuli has already started, currently there is no possibility for automatically translating a general ATE test program into a format which can be executed in a simulation environment.

#### 1.3 Contribution of this work

Although, the challenge of setting up the simulation environment of an ATE and sharing test information has already been addressed, there is currently no approach that can be used in a fully automatic way. Together with the lack of accuracy, this approaches are insufficient for executing a DOT test. Therefore, we address exactly this problem in the context of this thesis.

We develop a methodology and implement a framework for setting up the simulation environment for ATE tests and translating generic ATE test programs into a format that can be simulated. Since during the design flow of AMS designs several languages (e.g. SystemVerilog, SystemC, Verilog-AMS or VHDL) are used, there is no possibility for reusing the information which was generated at a specific design level. So, there

#### 1. INTRODUCTION

Figure 1.6: Overview of an abstract language for portable stimuli [Gro16]

are completely different languages used for defining the ATE test program as well as defining a simulation run. Reimplementing test benches in different languages used during the design flow contributes significantly to the time-to-market as well as in the design costs. Therefore it is indispensable to support an automatic translation mechanism to support reusing information, which was defined at a specific state. In this thesis, we study the practical challenges of DOT and more specifically, we address the problem of systematically translating an ATE test environment into a simulation environment. The novel contributions of this thesis can be summarized as follows:

- 1. Modelling of arbitrary ATE environments: the thesis provides a general simulation environment that can be used independently from the chosen ATE. The proposed methodology can be used for extending the functionality of the models with minimal effort.

- 2. Automatic translation of ATE tests into simulation test runs: the translation of an ATE test is fully automated, therefore the information from the final verification is reused to configure the simulation environment.

- 3. **Translation of limit checkers:** we develop a methodology for manual translation of limit checkers from the ATE to the simulation environment and propose a sketch of a procedure that allows automation of this process.

- 4. Implementation and the evaluation of the framework: we implemented all the results presented in this thesis and applied them to a real industrial chip using a real ATE setup.

The main outcome of this thesis is a framework for systematic translation of ATE test programs in the simulation environment. This framework allows in particular the quality analysis of the existing ATE test programs in the context of DOT. We demonstrated its applicability on a real industrial example, making it possible to simulate an entire ATE test for the first time inside Infineon.

This thesis is organized as follows. In Chapter 2, the ATE test will be considered from a general point of view to get an idea what exactly has to be supported by a simulation environment and which constructs are used in such an ATE test program. Afterwards, in Chapter 3, a closer look at the different test instruments and their content shall be given to show how a simulation environment can be set up. Combined with the translation process given in Chapter 4, the simulation process can be executed, which will then be used for evaluating the results on a specific chip from the area of automotive applications in Chapter 5.

# $_{\rm CHAPTER} \, 2$

# Background to ATE test programs

In this chapter, we introduce ATE testing. It starts with a short overview of the requirements for an ATE test, before we continue with the general setup of such a test. In the third part of this chapter, a short overview about common test cases will be shown. As a conclusion, we introduce the test case, which will be used as leading example throughout this thesis. Please note that this chapter is based on [RGA02] and focusses on the part of *final verification* in the design flow as shown in Figure 2.1.

Figure 2.1: Analog Mixed-Signal Design Flow focussed on final verification [BSED07]

#### 2.1 Requirements for an ATE test

Caused by the *random manufacturing defects* it is indispensable to perform a last check of the devices during the *final verification*. Since high test times yield in higher manufacturing costs, it is desired by the industry to keep the duration of the testing activities as low as possible, while the quality of the product has to stay the same. To ensure that these basic requirements are met, test benches based on the specification are developed early in the design flow. There are several targets for them.

Of course, the main purpose of a test is to ensure the quality of the product, which is done by checking whether all the specification requirements are met or not. Faults need to be detected as early as possible to decrease testing costs. Furthermore, it is possible to give quantitative information about the device, like rise times for digital signals. Apart from the checks on the device itself, the test is able to verify the quality of the design process, such that it can be improved for later production.

As one can see, the test benches have an important role in the design process and their development becomes more and more important with the growing complexity of the circuit, especially in AMS designs. Therefore, also requirements for the single test benches should be kept in mind as given in [BSED07]:

- 1. Scalability: The input stimuli of different technologies are defined as parameter, such that they can be changed easily for other technologies.

- 2. Configurability: It has to be possible to define all the test bench variables through parameters in a main control file.

- 3. Automated Result Analysis: The verification of a correct test run has to be performed automatically, without manual interaction.

Nowadays, it is desired to test a high number of devices simultaneously such that the test is automatically executed and controlled by a computer. This is exactly what an ATE is used for: execute and evaluate the test benches at high speed without loss of accuracy of the test. For this purpose, the ATE has to provide several programmable instruments with desired accuracy such that they can be used in a dynamic way.

Furthermore, for verifying the correctness of analog and digital signals, checking waveforms and performing timing measurements, the ATE has to provide measurement units which are able to support these measurements. The general setup of an ATE test will be given in the next section.

#### 2.2 General setup

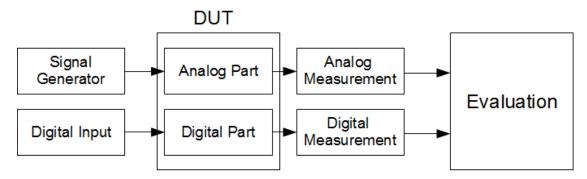

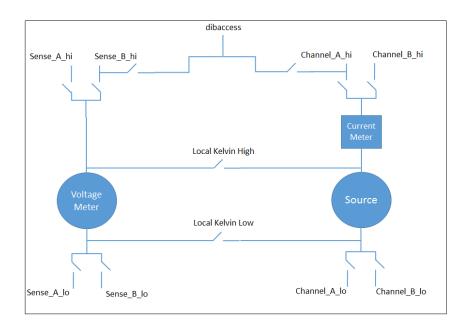

An ATE test consists of several parts, introduced in this section. The general setup of such a test is given in Figure 2.2. As shown, the DUT is the central element, a chip

consisting of analog as well as digital inputs/outputs. The inputs of the chip are shown on the left hand side of the figure, whereas its outputs can be found on the right hand side. It is the test engineer's task to setup different stimuli as inputs for this DUT and measuring the outputs for verifying its correct functionality. The ATE's objective is to provide the necessary test instruments for achieving these targets. In general, one can distinguish between digital and analog test instruments. Main tasks which have to be supported by the analog instruments are:

- 1. Provide voltage source with current-clamp

- 2. Provide current source with voltage-clamp

- 3. Source an arbitrary waveform

- 4. Measure voltage

- 5. Measure current

- 6. Measure timing information

- 7. Capture waveform

Whereas the digital instruments have to support:

- 1. Source digital waveform

- 2. Measure and verify digital signals

The connection between the instruments of the ATE and the DUT is done by the *load board*. Its purpose it to provide dynamic connections such that the test environment can be set up dynamically for different tests (e.g. open and close relays to switch between different test instruments as inputs for the DUT or provide higher current). Note that the design of the load board is a time consuming task, since a test program combines several tests and therefore different connections might be needed for them. During a simulation run, the correct functionality of the load board should be verified for performing debugging in an early phase of the design flow.

Additionally to the hardware part, the tester is able to understand a special programming language used for describing the test flow. It is possible for the test engineer to open/close relays, connect/disconnect instruments, configure the sourced signals etc. during the test. Furthermore, different test patterns are executed. A *test pattern* describes the sequence of the test vectors, consisting of analog and digital signals, which shall be applied to the DUT. Furthermore, the points in time when strobes should be performed are specified (they are similar to procedures used in imperative programming languages). A strobe

#### 2. Background to ATE test programs

Figure 2.2: Hardware setup of an ATE test

is simply a measurement of an analog or a digital signal within the execution of a test pattern.

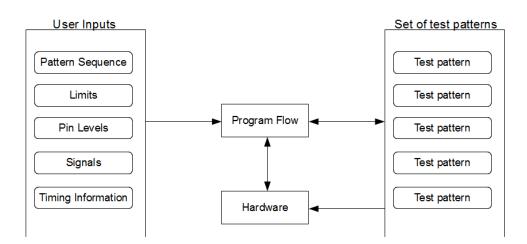

Figure 2.3 shows how the software interface of an ATE test is organized. The *program* flow exactly describes the actions performed during the test run and determines the sequence in which the test patterns have to be executed. Therefore, different inputs, defined by the test engineer, have to be set up. First of all, the user has to define in which sequence the patterns shall be executed and the limits which should be used for the test cases. Furthermore, for sourcing/measuring digital signals, the pin levels have to be specified. Moreover, the user has to create and store the arbitrary waveforms which shall be used during the execution. The program flow and the test patterns are normally executed in parallel and can be synchronized with several flags. For instance it is possible to close a relay before continuing with the pattern execution. To read the measurements performed during a test run and check them with the limits, the hardware supports an interface for communicating with the test program.

A typical test setup for AMS designs is shown in Figure 2.4. Analog signals are applied to the analog part of the device, whereas the specified digital signals are applied to the digital part. So, first the test engineers specify the setup of the *load board*, before

Figure 2.3: Software setup of an ATE test

executing the test pattern. During the execution, several strobes are performed and stored in the memory of the test instruments. After the test pattern has finished, the measurements can be read by the test program. When needed, the test engineer can also do post calculations in the context of the test program. Last but not least, the results are compared with the specified limits and automatically verified in the evaluation block.

Figure 2.4: ATE test flow

As one can see, setting up an ATE test is a complex task and combines a lot of information. Therefore it is necessary to start developing the test program early in the design flow such that it can already be tested in a simulation environment to ensure its functionality. The ability of automatically translating the specific test program into a format which can be imported into the simulation environment would be a big improvement in the development of an ATE test, which would save time and cost.

#### 2.3 Common test cases in industry

Since test time has a significant contribution to the time-to-market and manufacturing costs, it is strongly desired to keep test times as low as possible. Therefore ordering of the tests is a crucial point to ensure an early detection of a defect during the test. Note: with DOT this ordering can be optimized automatically based on the simulation results.

In general, an ATE test needs to cover a lot of possible faults. Therefore, different test categories have been developed which are quite common in industry. The first test case which is normally executed is the so called *continuity test* - it is responsible to verify whether the connection between the chip and the *load board* is done properly. Afterwards, the parameters given in the specification (like leakage current or power consumption) are verified. Other categories, which need to be covered are digital tests (testing the digital functionality based on truth tables from the specification) and timing tests. A timing test verifies the quality of the signals (e.g. rise times for digital signals). Last but not least, also the combination of digital and analog parts of the DUT needs to be verified - this is done during a mixed-signal test. A more detailed view at AMS testing is given in [Wan06].

During the test, several test cases chosen from these categories are executed (e.g. during the parametric test, the power supply is checked as well as the leakage current). In the remaining parts of this work, it shall be focussed on the *continuity test* as example.

#### 2.3.1 Example Continuity Test

Since the continuity test is one of the most common test cases used in industry, we use it as our illustrating example throughout this thesis. Therefore, a short introduction of this kind of test will be given here. As has already been mentioned, the purpose of this kind of test is to figure out if the connection between the chip and the *load board* is done properly.

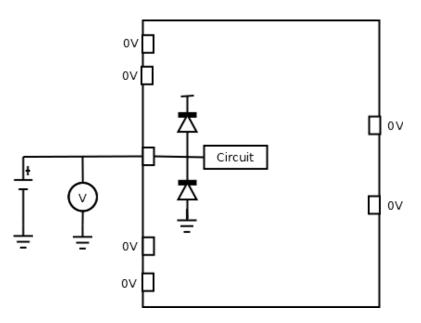

Figure 2.5 gives an overview of the functionality of a continuity test. First of all a single pin is selected which shall be tested for opens or shorts. Normally, a pin is used as input path to some circuit, which is protected by the *protection ESD diodes*. Exactly these diodes are used for the continuity test. The corresponding test instruments are connected to the pins of the DUT. Every instrument acts as a voltage source, sourcing 0V. The instrument connected to the pin which shall be checked is configured to sink current. The current flows through the protection diode to the test instrument - therefore the voltage measured by the instrument should be in a certain area around a diode voltage of 0.7V. Otherwise there exists an open/short between two pins.

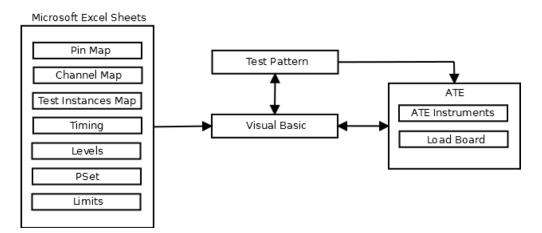

We use this simple kind of test throughout this thesis as leading example. What remains to show is the setup of the test program for running a continuity test. As ATE we used Teradyne's Flex Tester. Figure 2.6 depicts the parts a test program consists of. The communication between tester and software is done by some code, written in *Visual Basic*. This program is split up into several specific procedures, where every procedure

Figure 2.5: Continuity test

represents a single test. Within this code, the test engineer has the ability to fully control the different instruments of the ATE, read the measurements or run conventional program code like calculations or loops. Furthermore it is possible to define single test patterns. A test pattern is similar to a procedure - it contains a set of commands, which are executed in parallel to the Visual Basic code. Also in the content of the test pattern, program constructs like loops or other conditional statements are available. To ensure a deterministic test, the user can synchronize the pattern and the Visual Basic codes via specific statements (e.g. wait). Whereas the Visual Basic program has a bidirectional communication to the ATE (instruments can be configured and information like measurements can be read), a pattern can just configure the instruments, which makes sense because after reading a measurement the user might perform post calculations. We are having a closer look at the detailed configuration parameters in Chapter 4.

What remains is the configuration of such a test program. The test engineer might want to control the Visual Basic code and the patterns to be executed from a graphical user interface. This configuration is done via specific Microsoft Excel Sheets, where the essential ones are shown in Figure 2.6. For example, in the Test Instances Sheet, the test flow is specified - here the user can exactly define the test cases (procedures in the code) to run. The sheets describing the instruments of the ATE are the Pin Map (specifies the instrument and relay names, which will be used throughout the program) and the Channel Map, which maps the names of the Pin Map to the physical identification of the ATE instruments (they are normally identified by unique numbers). Whenever a function for configuring an instrument is called, the name specified in the Pin Map is used as identification. Note, that also a grouping of several instruments is possible.

Figure 2.6: Setup of the Teradyne Flex Tester

The *Timing Sheet* as well as the *Level Sheet* define the parameters, needed during a program run, like which voltage values indicates a logic 1, when we want to make a digital measurement or for how long a signal is active. A set of these parameters is available for every instrument - these sets are defined in these two sheets. As already mentioned, during a test run, different parameters are applied to single instruments. Instead of configuring one by one, Teradyne also supports configuring an instrument with a parameter set (PSet), containing a group of configuration parameters. They are defined in the *PSet Sheet*, but in contrast to the other sheets, this one is not mandatory.

Last but not least we have the *Limit Sheet*. Here the test engineer can define the limits, to verify the correct behaviour of the DUT. The limits are defined for every test separately in a list. Whenever a check is executed in the test program, the next values are taken from the list and checked with the desired value.

After this short introduction to Terdyne's Flex tester, we present now a small example of the continuity test how it is used for an Infineon chip as DUT. We neglect all the sheets, since they are very specific and not necessary for the next parts. Just keep in mind that the timings, levels and parameters are configured in the context of these sheets. Note that they can also be configured within the *Visual Basic* code.

```

Listing 2.1: Setup of a continuity test

```

```

Call Relay_On("OUTxF_k", 0.02) 'maintain 10ms

Call Alarm_On("Vs_dc30,Vdd_dc30,IS_dc30,all_dc90_hi_a", False)

TheHdw.DCVI.pins("Vs_dc30,IS_dc30").Connect (tlDCVIConnectDefault)

TheHdw.Wait (resource_relay_settling)

TheHdw.DCVI.pins("Vs_dc30").PSets("DC30v_0VR30V_100mAR200m_measV").Apply

TheHdw.DCVI.pins("Vs_dc30").Gate = True

TheHdw.DCVI.pins("Vs_dc30").Disconnect (tlDCVIConnectHighGuard)

TheHdw.Wait (0.001) 'maintain 1ms

TheHdw.DCVI.pins("all_dc90_lo_a").Connect (tlDCVIConnectLowForce)

```

```

TheHdw.Wait (0.006) 'maintain 6ms

If quad220_device = True Then

TheHdw.DCVI.pins("all_dc90_hi_a").Connect (tlDCVIConnectDefault)

TheHdw.Wait (0.006)

`maintain\ 6ms

Else

TheHdw.DCVI.pins("all_dc90_Quad").Connect (tlDCVIConnectDefault)

TheHdw. Wait (0.006) 'maintain 6ms

If quad040_device = True Then

Call Relay_On("SO_OUT5_k", 0.002)

TheHdw.DCVI.pins("OUT0_dc30,SO_OUT5_dc30"). Connect (tlDCVIConnectHighSense)

TheHdw.DCVI.pins("COUT0_dc30.SO_OUT5_dc30"). Connect (tlDCVIConnectHighSense)

TheHdw.DCVI.pins("OUT0_dc30,SO_OUT5_dc30").Connect (tlDCVIConnectHighForce)

TheHdw.Wait (resource_relay_settling)

TheHdw.DCVI.pins("OUT0_dc30,SO_OUT5_dc30").LocalKelvin = False

TheHdw.DCVI.pins("OUT0_dc30,SO_OUT5_dc30").Disconnect (tlDCVIConnectHighGuard)

End If

End If

TheHdw.PPMU.pins("all_hsd").Connect

TheHdw.DCVI.pins("Vs_dc30, IS_dc30, all_dc90_lo_a").LocalKelvin = False

TheHdw.Wait (resource_relay_settling)

TheHdw.PPMU.pins("all_hsd").ForceV 0, 200 * uA, 200 * uA, -200 * uA

TheHdw.Wait (0.001)

Call TheHdw. Digital. Patgen. Continue(0, cpuA) 'VBT_code

TheHdw.DCVI.pins("Vdd_dc30").PSets("DC30v_0VR30V_100mAR200m_measI").Apply

TheHdw.Wait (0.001)

TheHdw.DCVI.pins("Vdd_dc30").Gate = True

TheHdw.Wait (0.001)

TheHdw.DCVI.pins("Vdd_dc30").Connect (tlDCVIConnectDefault)

TheHdw.Wait (resource_relay_settling)

TheHdw.DCVI.pins("Vdd_dc30").LocalKelvin = False

TheHdw.Wait (resource_relay_settling)

If quad220_device = True Then

TheHdw. Digital. Patterns. Pat(Continuity.pat"). Start (("Continuity_Quad220_Initial")

End<sub>11</sub> I f

If \_quad040\_device \_\_True\_Then

TheHdw. Digital. Patterns. Pat(Continuity.pat"). Start ("Continuity_Quad040_Initial")

End If

I\,f \text{ penta\_device = True } Then

Then TheHdw. Digital. Patterns. Pat(Continuity.pat"). Start ("Continuity_Penta_Initial")

End \, {\scriptstyle \sqcup} \, I \, f

If \_hexa\_device \_=\_True\_Then

Then_TheHdw. Digital.Patterns.Pat(Continuity.pat").Start ("Continuity_Hexa_Initial")

End If

Note: from here the pattern {f and} the VBA code are executed in parallel */

/* We jump directly to the limit checks */

gnd_vs = TheHdw.DCVI.pins("VS_DC30").Meter.Read(tlNoStrobe, 5, -1, Average)

/* The voltage has to be less than -0.7V */

datalog(gnd_vs)

```

Listing 2.1 illustrates an example of the program code for the setup of a continuity test. This code snipped is used for configuring the relays of the load board, connect the needed instruments and set the voltage of all instruments to 0V as common for a continuity test. As we can see, with conditional statements several types of DUTs are distinguished (e.g. devices with different channels). In the end the program chooses the pattern to run depending on the device type.

Listing 2.2: Pattern for the continuity test

| :vec_nr | :patexe        | :ws :stimuli |    | :pset :ms                                     |

|---------|----------------|--------------|----|-----------------------------------------------|

| 1,      | ,              | 7,           | —, | $d137 \ d258 \ d142 \ d6 \ d6 \ d6 \ d6 \ . $ |

| 2,      | repeat = 100,  | 7,           | -, | -,                                            |

| 3,      | repeat = 3000, | 7,           | -, | —,                                            |

| 4,      | _,             | 8,           | -, | -, \$Enable_Alarm                             |

| 5,      | repeat = 5,    | 8,           | —, | -, \$Strobe                                   |

| 6,      | —,             | 8,           | —, | -, \$Disable_Alarm                            |

| 7,      | _,             | 7,           | —, | d140 ,                                        |

| 8,      | repeat = 3000, | 7,           | —, | -,                                            |

| 9,      | -,             | 8,           | —, | -, \$Enable_Alarm                             |

| 10,     | repeat = 5,    | 8,           | —, | -, \$Strobe                                   |

| 11,     | _,             | 8,           | —, | -, \$Disable_Alarm                            |

| 12,     | —,             | 7,           | —, | d137 ,                                        |

| 13,     | repeat = 500,  | 7,           | —, | —,                                            |

| 14,     | —,             | 7,           | —, | d139 d141 d155 d9 d9 d9 d9,                   |

| 15,     | repeat = 500,  | 7,           | —, | —,                                            |

In Listing 2.2 we see an extraction of the pattern in GPIF format [KRT02] as it is called in the context of the code. Here, every line describes a test vector, where every line consists of several columns. The first column just describes the line number (which can be used for jumps inside the pattern), whereas in the second column simple programming constructs can be used (e.g. repeat, call, jump). The code is followed by a timing information, represented by a number. This number identifies the timing defined in the *Timing Sheet*. This timing information determines the duration of such a line. After this duration the next line is executed. With this information it is possible to satisfy timing constraints like rise times. The next column describes a digital waveform - a list of digital instruments is defined at the beginning of a pattern. The digital waveform assigns a logical output or expected value to every of these instruments. Afterwards, the analog waveform is defined, just with the difference of applying a PSet instead of a logic value. A dot means "don't change". The last column can be used for executing so called microcodes for every instrument. Here for example, a filter can be enabled for an instruments or strobes can be made to be read afterwards in the Visual Basic code.

In Chapter 4 we show the parts and commands used in this program from a more abstract perspective and use it to clarify which steps have to be taken until we are able to run it in the simulation environment we propose in the next chapter.

# CHAPTER 3

### Setting up the simulation environment

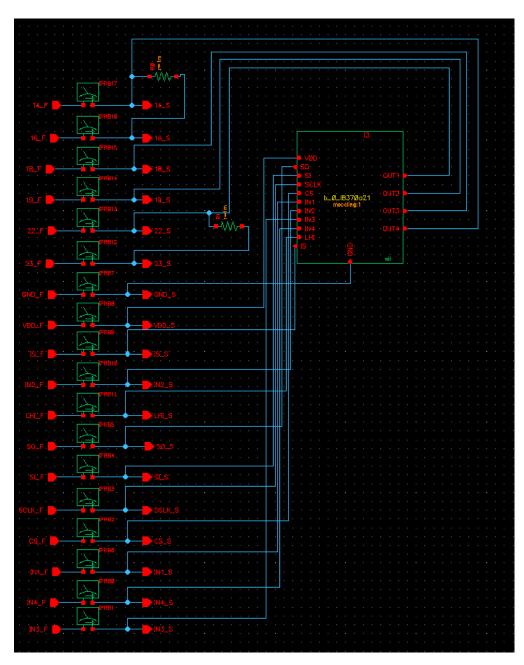

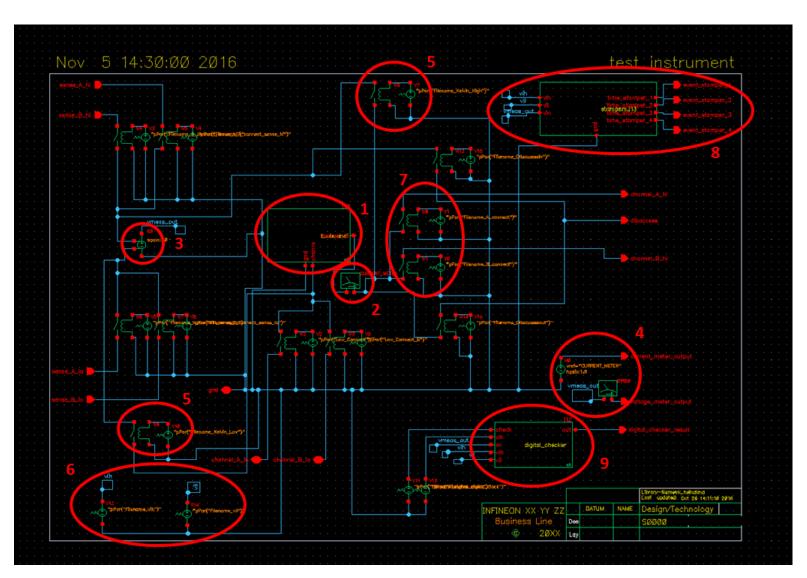

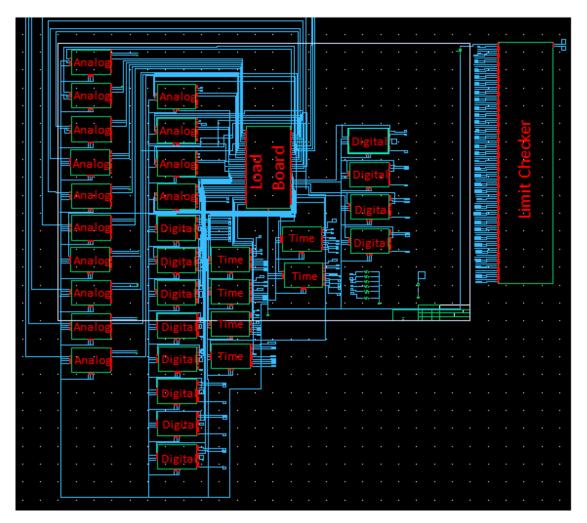

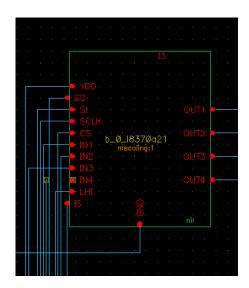

In this chapter, we develop a model of an ATE test for the simulation environment. Although there are already test benches available in the simulation environment, they are not useful as model for the ATE test, since they are not using the same instruments with the same properties and the load board might be neglected. Therefore it is necessary to model the different resources, available at an ATE to run the test in a simulation equivalent to the real test. We first present the overall description of a test environment model using a top-down approach. We then instantiate this model to a concrete example of an Infineon chip. We implement this concrete example, using the Cadence Virtuoso tool and simulate it with Spectre. The modelling activity presented in this chapter is part of the mixed-model verification part of the design flow, as illustrated in Figure 3.1.

Figure 3.1: Modelling part in the design flow [BSED07]

#### 3.1 Modelling of an ATE test

In this section, we present a step-by-step overview of the ATE test model that is not specific to concrete instrument types. Whereas in the ATE test several kinds of resources are available (e.g. high current/low current or analog/digital instruments), we model all of them with one single model. We illustrate the modelling steps and the use of the resulting model with an example from the automotive field, a chip provided by Infineon Technologies. This chip plays the role of the DUT in our presented scenario.

Figure 3.2 depicts the top level setup of the hardware of an ATE test. The ATE typically consists of several kinds of test instruments connected to the *load board* and provides different functionalities. As one can see, we are using the same model for every instrument, since a general schematic is used for all types of test instruments. They are connected to the DUT via the load board. Consider the pinning block in Figure 3.2. This block includes the detailed connection of the DUT to the load board. It is used to introduce force and sense lines for the design.

Figure 3.2: Top-Level setup of the simulation environment

We note that the *load board* is a very special part of an ATE test. Its configuration depends on the available resources (instruments) of the specific ATE and the tests to be executed on the DUT. Therefore, the load board is specific to the design and its test configuration. Due to this specificity, we do not detail the model of the load board in

this thesis. One should just keep in mind that this part has to be remodelled whenever a new load board is used in the test. Note that the problem of modelling the *load board* was also addressed in [RKR03].

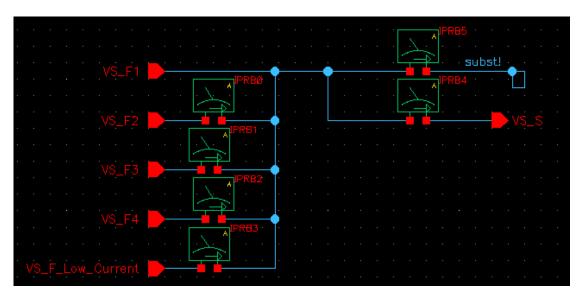

There is just one part of the load board, which can be modelled generally: the connections to the DUT. During the test, two kinds of connections are used - a force line and a sense line. The force line is responsible for sourcing a specified voltage, current or waveform, the signal is driven by the source of the instrument. In contrast to the force line, the sense line is used for measuring voltage. The distinction between these kind of connections is necessary, since we want to measure voltage directly at the DUT according to the *kelvin measurement principle*. We note that the sense line is shorted with the force line, in order to measure voltages inside the test instrument later on. This shorting is referred to as *kelvin connection*.

The wires used for connecting the power supply of the DUT to the load board are shown in Figure 3.3. On the left hand side, one can see the input pins to which several test instruments can be directly connected. Sometimes it is necessary to use an implicit wiring, where connections are realized via *ConnectionByName*. Moreover, Cadence supports global wires, available through all design hierarchies. They are identified by a "!" at the end of the wire name. Therefore, the input pins are connected to the global wire *vsub!*, which is the power supply of the model of the chip. Moreover, the output pin, VS\_S is shorted with *vsub!* for measuring the voltage. We can see that these two wires are not directly shorted, because of a specific tool feature. Cadence Virtuoso does not allow a direct connection between two or more input pins. One solution to overcome this issue is to use low ohmic resistors for these connection, with the disadvantage of introducing more complexity to the overall design, yielding in higher computational effort during the simulation. Therefore we used the IProbe, which is normally used for current measurements. In the circuit they act like a resistor of  $0\Omega$ , but do not increase the computational effort.

The force and the sense lines of the remaining input pins of the chip can be connected directly, since no global wires are used. Similarly to the previous case, we see on the left hand side of Figure 3.4 the input pins, also known as force lines, whereas on the right hand side, the sense lines have a direct connection to the output pins.

With these connections, we can both force current or voltage as input to the DUT pins and measure voltage directly from the sense lines, shorted with the force lines. We recall that in this thesis we ignore the load board - hence we directly connect the DUT pins to the instrument models. In reality, these connections are implemented via the manually modelled load board.

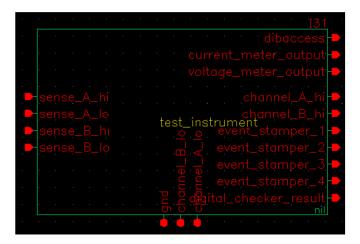

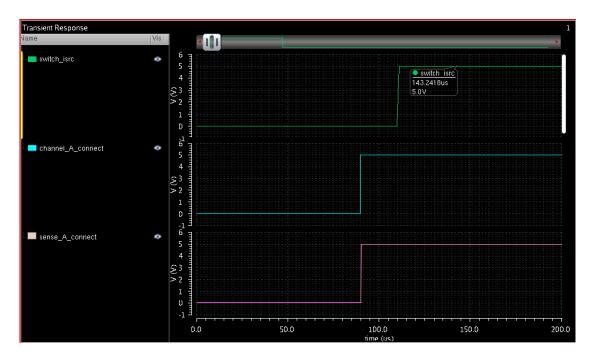

This concludes the presentation of the high level model of the ATE test environment. In the remainder of this chapter, we focus on the specific models of the test instruments. Figure 3.5 depicts a conceptional schematic of a test instrument, whereas Figure 3.6 shows the block diagram of a test instrument. We start with a description of the static interface (the pins) in a test instrument. Consider the right hand side of Figure 3.6.

Figure 3.3: Connection between DUT supply and load board

The pins *channel\_A\_hi* and *channel\_B\_hi* act as high side connections of the source included in the test instruments. With these channels, it is possible for the test engineer to realize two different connections for the high side and select the active one in the context of the test program. At most one of these channels is connected at any time, never both. A third output which might be used is the so called *dibaccess*. Via two switches this output pin can be either connected to the sense or the force line. The *dibaccess* can be used for implementing an additional connection, like a flow from the force line to ground.

On the bottom side of the block, we have the low force connections  $channel\_A\_lo$  and  $channel\_B\_lo$ . Similar to the high force line, one can multiplex between these low force connections. Moreover the channels of the high and the low interface can be mixed, e.g. on the high side  $channel\_B\_hi$  might be used, while on the low side  $channel\_A\_lo$  is connected. Furthermore, on the low side we have modelled a ground pin, which is used for voltage sources and the switches inside the block. In contrast to the other channels, ground is connected all the time.

Furthermore, we have the input pins for measuring voltage on the left hand side of the instrument -  $sense\_A\_hi$ ,  $sense\_A\_lo$ ,  $sense\_B\_hi$  and  $sense\_B\_lo$ . Similarly to the source, the voltmeter needs a high as well as a low side connection. Also here, the test engineer can switch between two channels for both sides. Again, it is possible to mix the channels of the high and the low sense interface. For our DUT, just one of the sense channels ( $sense\_A\_hi$ ) is used. It is either connected to ground or floating for the power supply.

Apart from the pins used for driving and measuring signals, a test instrument can perform two evaluations on the measured voltage: verify the logical value or performing a timing

Figure 3.4: Connection between DUT and load board

measurement. Since all these informations are needed for limit checking, we use additional output pins for the corresponding values. They source the measured value as voltage such that the limit checker can use them as input for post calculations and verification.

Figure 3.5: Schematic of a test instrument

Figure 3.6: Pinning of a test instrument

#### 3.2 ATE instrument model

We now present the actual models of the test instruments. Normally one can distinguish between different kinds of test instruments. In general there are analog and digital instruments, whereas one can further divide these categories. For instance, Teradyne's Flex tester distinguishes between grounded and floating analog instruments, high/low current/voltage instruments, instruments with timing measurement capabilities and so on. Since this is caused by the available resources of such a tester (increasing costs with increasing number of complex instruments), this is just an issue of the tester hardware. In the context of a simulation environment it is not necessary to take care of this hardware specialities - therefore we designed a general test instrument which combines all these features, to reduce the complexity of the modelling work and ensure that changes can be made easily (e.g. when a test instrument of a special type is replaced in the ATE test by another one).

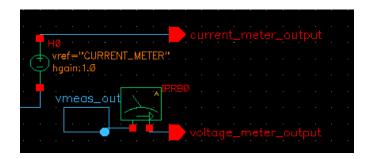

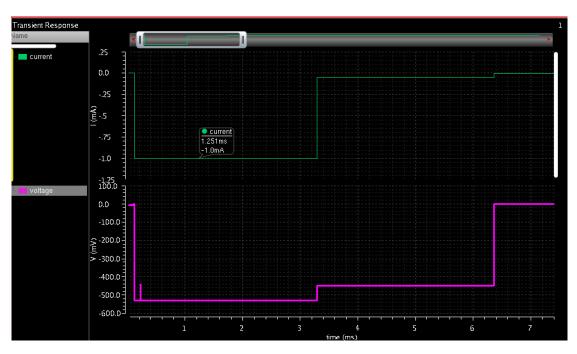

The overview of a generic test instrument model is shown in Figure 3.9. The central element is the block in the middle (1), containing the source which can dynamically switch between a current or a voltage source. The high pin is located at the right side of the block. It is connected through an ampere meter (an *iprobe* called CURRENT\_METER (2)) to two switches: one connected to *channel\_A\_hi* and another one connected to *channel\_B\_hi* (7). At every point in time, at most one of these switches is closed, the other one has to be open. They are controlled by a voltage piecewise linear source (VPWL) - 5V indicate a closed switch (low resistance), whereas 0V indicate an open switch (high resistance). Also on the low side, two switches act as a multiplexer for selecting the desired connection from the available ones.

Apart from this forcing part of the instrument, the sensing input is responsible for measuring voltage at a specific point in the hardware (current is measured directly at the force line with low resistance). A voltage controlled voltage source (VCVS) is used for acting as a voltmeter (3). The two switches between the high input of the voltmeter and sense A hi and sense B hi are acting as a multiplexer such that at every point in time just one of these lines is used as input. The low sense lines are connected in the same way. In our example, just channel A is used on the low sides (for the force as well as for the sense line). For most of the instruments, the low force lines are connected to ground. The test instruments connected to the power supply need to be floating - therefore their low force/sense lines are connected to the output ports of the DUT. The voltmeter measures the voltage between the high and the low sense input and sources the measured voltage to the net *vmeas* out, such that it can be used for timing measurements or the verification of a logical value. Current metering works in a similar way: a current controlled voltage source (CCVS) (4) uses the measurement of CURRENT\_METER as input and sources the corresponding value. How the voltages representing the actual voltage/current are sourced throughout the output ports is shown in Figure 3.7, such that they can act as input for the limit checker.

We can see, that there are two additional switches - one for directly connecting the high force line with the high input of the voltmeter and another one for connecting the low force line with the low input of the voltmeter. These are so called *local kelvin connections*(5). These connections are useful to have a reference even when no sense line connection is active. The main intention of the *local kelvin* is to have a reference for the control loop used in the test instrument. Moreover it is also possible to force voltage or current over these sense lines - one has to connect the *local kelvin connection*, disconnect both force lines and connect the desired sense line. This might be useful in some cases (e.g. providing higher current in that way because of a limited number of available resources).

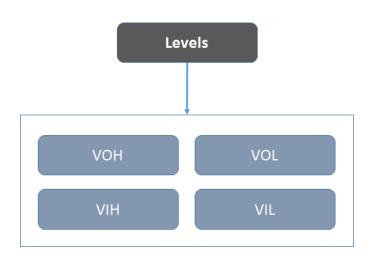

Figure 3.7: Meter outputs

On the right hand side of the model, we have two additional blocks - one is responsible for performing timing measurements (8), whereas the other one verifies a desired logical value (9). Both use the measured voltage from *vmeas\_out* as input. Additionally for both evaluations the information of the pin levels (voltage in high (VIH) and voltage in low (VIL)) is needed. Since the levels can also change dynamically during the execution, they are controlled externally. Therefore one VPWL is used for sourcing the actual value of VIH and another one for VIL (6) - the outputs are sourced to the nets called *VIL* and *VIH*.

In the following sections, we have a closer look at the blocks used inside a test instrument to get a better understanding of their functionality and configuration.

Figure 3.8: ATE test instrument channel

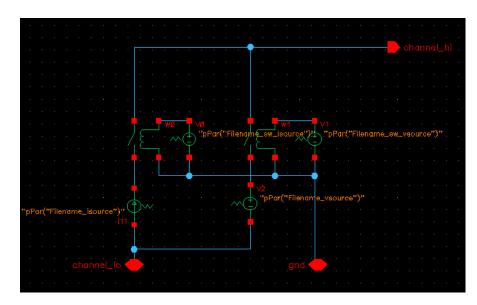

#### 3.2.1 The source

This section provides a closer look at the used source within an instrument. It has already been mentioned, that an instrument can either act as a voltage or current source. The mode of the source might change dynamically during the execution of the ATE test. As shown in Figure 3.8, this block contains a VPWL as well as an current piecewise linear source (IPWL). Two switches are used for the dynamic mode change - at every point in time, exactly one of the switches is closed. One needs to take special care of the current source: whenever the current source is used, it needs to be ensured that the switch is closed, otherwise this behaviour would result in high voltage and undesired behaviour. The signal is sourced at the output pin *channel\_hi*, while the pin *channel\_lo* is used as reference (it can either be grounded or floating). The *gnd* pin is just used for the controlling voltage sources and the switches. We use this configuration also for digital signals - here just the voltage source is active with the voltage corresponding to the desired logical value.

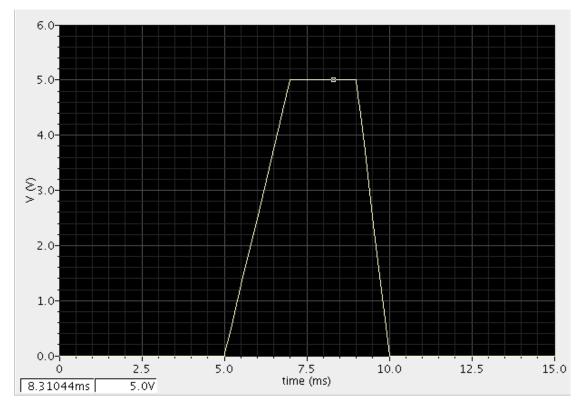

The central element in the whole model is the VPWL. Such a source is configured by a pair consisting of a point in time (in seconds) and a voltage value (in Volts). The source linearly interpolates the voltage values between these two points in time. Since the classical VPWL has an upper bound on the number of points which can be defined and cannot be controlled from external, an extension of this kind of source must be used: the voltage piecewise linear source - file controlled (VPWLF). In general the VPWLF supports the same features as the classical VPWL with the difference that it reads the pairs from an external file with a much higher upper limit.

An example input file for an VPWLF is shown below. While the output of the source is shown in Figure 3.10. As one can see, the voltage is configured to stay at 0V until 5ms, then it starts rising linearly to 5V for 2ms, before it is linearly decreasing to 0V again from 9ms until 10ms. The configuration for the current source (current piecewise linear source - file controlled (IPWLF)) works the same.

$\begin{array}{cccc} 0 & 0 \\ 0.005 & 0 \\ 0.007 & 5 \\ 0.009 & 5 \\ 0.010 & 0 \end{array}$

Figure 3.10: Example definition of a waveform

At the end of this chapter we would like to mention an additional feature supported by ATE testers: the voltage/current clamp. For example, the test engineer has the possibility to define a current clamp for a voltage source. When the current reaches this clamping value, the voltage source takes the role of a current source, forcing the clamping value as current. For a current source with a voltage clamp it works symmetrically. Modelling this feature together with dynamic clamps usually yields in convergence problems during the simulation and at the moment there is no known solution to this issue in spectre. Therefore we neglect this feature and assume that an excess of the clamp just occurs in the case of a fault.

In the next sections we have a closer look at two evaluation blocks used during simulation.

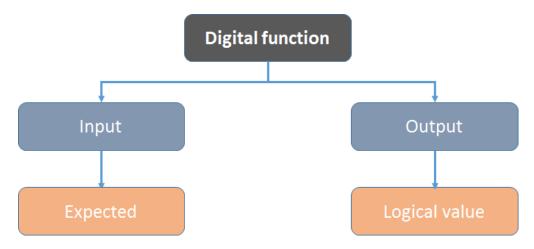

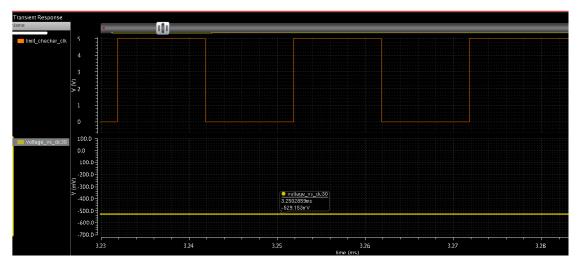

#### 3.2.2 Digital checker

In AMS designs, we need to verify both, analog and digital behaviours. Whereas the sampled value of voltage or current is sourced directly out of the pins *current\_meter\_output* and *voltage\_meter\_output*, the digital value is checked first inside the digital checker which is shown in 3.11 as it is used in the test instrument. Within the ATE test program, the test engineer can specify the expected logic value at some point in time. This expected logic value is sourced by a VPWLF - 5V correspond to an expected logic high value,

whereas 0V mean that a logic zero is expected. The nets *VIH* and *VIL* are used as input for the actual pin levels. For the information whenever a check shall be performed, an additional signal is used: at every (rising or falling) edge, the digital checker verifies the input voltage (*vmeas\_out*) with the expected value according to the pin levels. As long as no fault occurred, the output *out* is set to 5V. In case the expected and measured value differ it is set to 0V. This output is written to *digital\_checker\_result* such that it can be verified in the limit checker later on.

Figure 3.11: Digital checker block

Figure 3.12 depicts an example of the usage of a digital checker during the simulation. The first signal *clk* is used for triggering the measurements, whereas *check* denotes the expected value. In the third line, one can see the signals *vmeas\_out*, *VIH* and *VIL*, whereas in the last line we have the output *digital\_checker\_result*. We note, that at every event (edge) of the clock, the signal *vmeas\_out* corresponds to the expected logic value, therefore the output remains at 5V.

Figure 3.12: Example for the functionality of the digital checker

In our environment we implemented the digital checker in Verilog-A - the corresponding code an be found in the appendix.

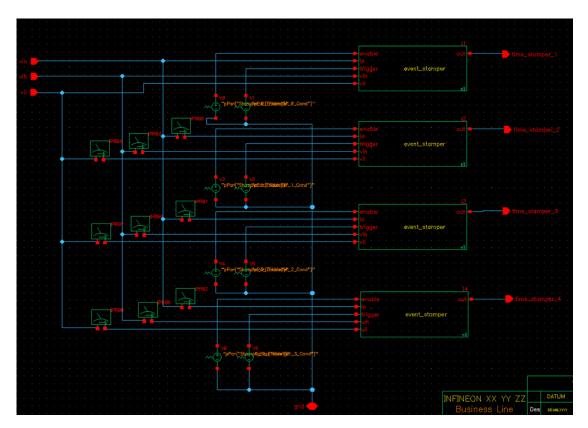

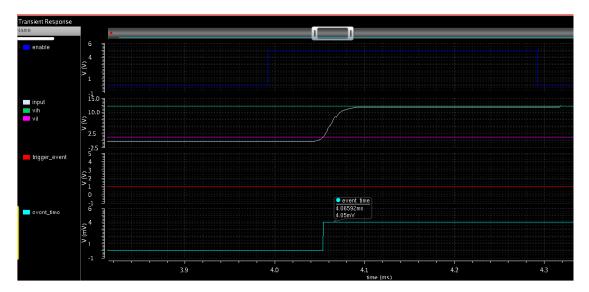

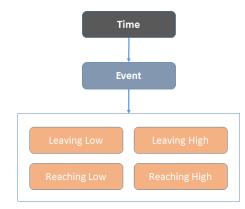

#### 3.2.3 Event stampers

Another measurement used during a test is the timing measurement. It is necessary to ensure that rise/fall times meet specification requirements of the device. Every test instrument consists of four event stampers, combined in the block *event\_stampers* shown in Figure 3.13. It takes the actual levels *VIL* and *VIH* as well as the measured voltage *vmeas\_out* as input. An event stamper is triggered by an event (e.g. leaving the low value). Whenever this event occurs, the time is measured and written to the output port. The outputs of the block are the times measured by every event stamper.

Figure 3.13: Event stamper block of the instrument

Figure 3.14 shows how the four event stampers are connected to the input/output pins. Every event stamper uses the levels and the measured voltage as input. Additionally we need to specify which event shall trigger a measurement. Here we distinguish between *leaving low, leaving high, reaching low* and *reaching high* events. These events are discussed in more detail in the next chapter. Furthermore, an event stamper block needs to be enabled - otherwise no measurements are done. The events of interest are configured via the voltage of a VPWLF where every voltage level indicates an event. Every stamper can be triggered on a different event. To enable the desired block, the VPWLF of the enable signal needs to be set to 5V. When this source is set to 6V a measurement is performed immediately without waiting for an event. In the case an event happens more often, always the last time is sourced at the output.

An example of such a timing measurement is shown in Figure 3.15. As can be seen, the digital voltages VIH and VIL are set to 2.3V and 13V. The voltage indicating the trigger event is about 1V which means we are waiting for a *leaving low event*. When the enable signal is set to high, these values are stored and the stamper waits for the corresponding event. When the input signal reaches the value of VIL, event\_time is set to the actual time - in this example the event occurs at approximately 4.05ms, therefore the output voltage of the stamper is set to 4.05mV.

We implemented the event stamper in in Verilog-A, the corresponding code can be found in the appendix.

Figure 3.14: Connections of the four event stampers

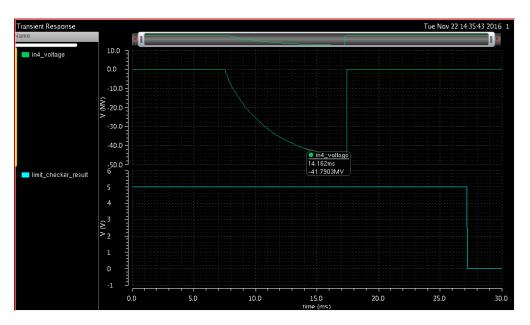

#### 3.2.4 Limit checker

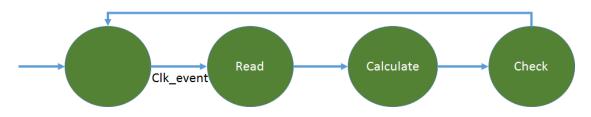

Now that we are able to measure voltage, current, time and verify the correctness of logical values, we need to combine all those information for evaluating the correct functionality of the DUT. Since the limit checker is generated during the translation of an ATE test program, we just discuss its connections and high-level functionality here.

The limit checker takes all the measurement signals as inputs. Similar to the digital checker, it is triggered by a clock where every edge indicates an event. Whenever such an event occurs, either the value of a signal is measured and stored within an array or post calculations/checks are performed. Its output is 5V as long as no fault occurred and all checks were successful, in the case of an error the output voltage is set to 0V. The digital checks are not event driven, at the moment one digital checker falls down to 0V, the limit checker immediately triggers an error.

In this kind of way, the limit checker knows about every signal from every instrument, therefore also dependencies of measurements can be checked. When there are no dependencies between test instruments one might also implement the limit checker within the test instrument.

Figure 3.15: Example of an event stamper

With this discussion, we conclude the modelling part of the ATE environment. In the next chapter we show how to translate an ATE test program such that we can simulate it in this environment and verify the results automatically.

## CHAPTER 4

## Translation of an ATE test program

In the previous chapters, we presented the functionality of ATE tests and we showed how to model it in a simulation environment. Next, we develop a procedure for translating ATE test programs into test descriptions that can be executed in the simulation environment in the content of this chapter. We first identify the functionality that is needed in order to successfully port ATE test programs into the simulation environment. We then propose a general language in which we can express such functionality and propose the concrete translation from ATE to simulation test programs.

Figure 4.1: Translaton process in the design flow [BSED07]

#### 4.1 Identification of needed functionalities

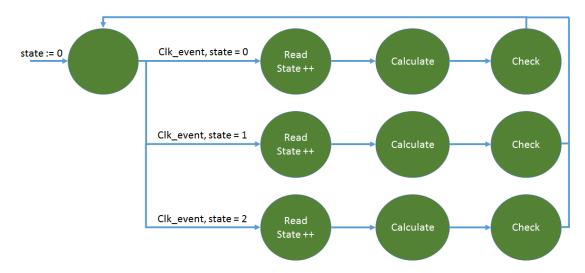

In this section, we identify the core functionality of ATE test programs that is independent from a specific ATE and is needed for their accurate translation into a simulation environment.

Figure 4.2 depicts the abstract view of the main components in an ATE test. The ATE hardware consists of a load board and the test instruments. The test program must be able to control different functionalities of these hardware components. A load board contains relays that are dynamically configured at runtime. They are responsible for dynamically setting up the DUT connections. Note that the remaining components of the load board are passive (e.g. resistors or capacities with static values), therefore they will not be discussed in this section.

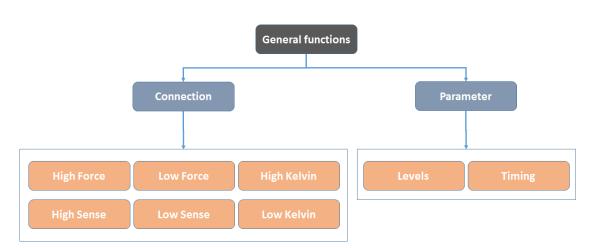

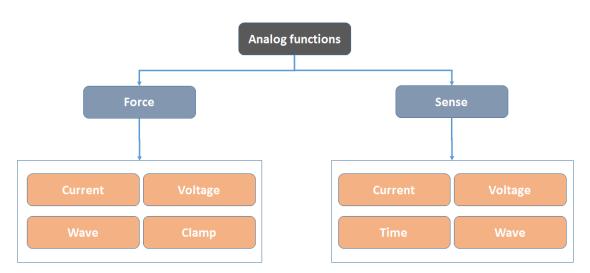

The ATE test instruments are configurable by test engineers. We distinguish between analog, digital and general ATE functionality in the context of AMS design. In the previous section we showed how to model test instruments with such heterogeneous functionality.

Furthermore, communication between the ATE hardware and the test program plays an important role and must be considered. This communication typically has the following form: the test program provides a sequence of input values to the ATE hardware, one by one. In every step, the test program sends an input value, waits for the ATE to process the data and acknowledge with a special event before it moves to the next step. This functionality is represented by the Communication block in Figure 4.2.

Figure 4.2: Abstract schematic of ATE

We now present specific aspects of the elements identified in Figure 4.2 and have a closer look at their provided functionalities in the sense of an abstract language.

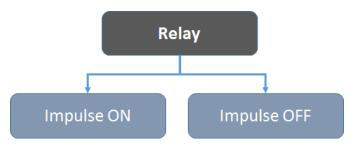

The load board relays are controlled by an impulse (input voltage), which can have two states: on (5V) or off (0V). Note that by default, the impulse of every relay is in the off state, whereas the relay is either open or closed in this state, depending on the design of the load board. Whenever the impulse changes, the state of the relay is updated accordingly.

Figure 4.3: Relay functionalities

It follows that a test program can control a relay by switching the impulse on and off. This action is done by the two commands Relay\_On and Relay\_Off as shown in Table 4.1.

| Description                                    | Command   |

|------------------------------------------------|-----------|

| Turn on the impulse, which controls the relay  | Relay_On  |

| Turn off the impulse, which controls the relay | Relay_Off |

Table 4.1: Relay functionalities and commands