# DISSERTATION

# Behavior of Silicon and Gallium Nitride devices under electrical overstress conditions

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

unter der Leitung von

Ao. Univ. Prof. Dr. Dionyz Pogany Institut für Festkörperelektronik

eingereicht an der

Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

# Dipl.-Ing. Clément Fleury

Mat.Nr. 1228707

Wien, Dezember 2017

####

zugänglich.

http://www.ub.tuwien.ac.at

University of Technology.

http://www.ub.tuwien.ac.at/eng

Die approbierte Originalversion dieser Dissertation ist in der Hauptbibliothek der Technischen Universität Wien aufgestellt und

The approved original version of this thesis is

available at the main library of the Vienna

TUUB

Dissertation Betreuer und Prüfer: Ao.Univ.-Prof. Dr. Dionyz Pogany Begutachter und Prüfer: Prof. Dr. Gaudenzio Meneghesso Begutachterin und Prüferin: Dr. Marise Bafleur

Tag der mündlichen Prüfung: Donnerstag, 25. Jänner 2018, 13:30 Uhr

"There is no need to ask the question "Is the model true?". If "truth" is to be the "whole truth" the answer must be "No". The only question of interest is "Is the model illuminating and useful?".", George Box, 1978.

# Abstract

The miniaturization of integrated circuits has made microelectronics devices better and better whether in terms of integrability, speed or cost. One of the drawbacks of this trend is that the devices are more and more prone to failure caused by unwanted electrical stresses, as power density increases. This has gone to the point where half of the available area is sometimes used for protecting the active device. In general, the protection also hinder the performance of the device.

The first type of unwanted stress whose effects have been studied in this thesis is electrostatic discharge (ESD).

ESD effects on Silicon-Germanium hetero-junction bipolar transistors (SiGe HBT) used in low noise amplifiers have been studied. Two different types of athermal failure behaviors have been identified and explained in terms of silicon breakdown for long rise time and transistor parasitic action for short rise time and/or substrate coupling.

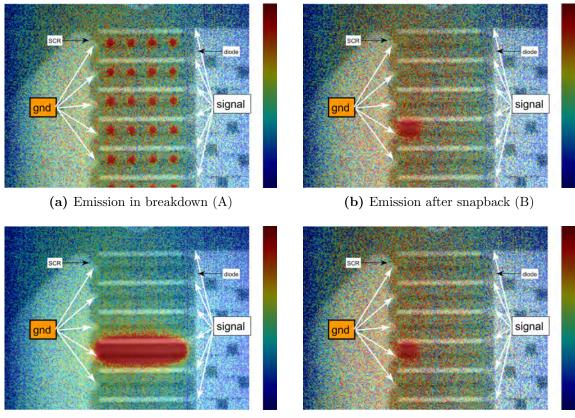

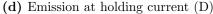

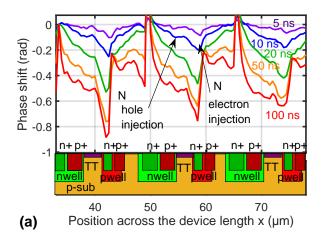

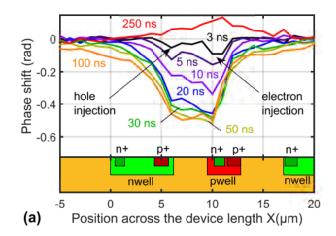

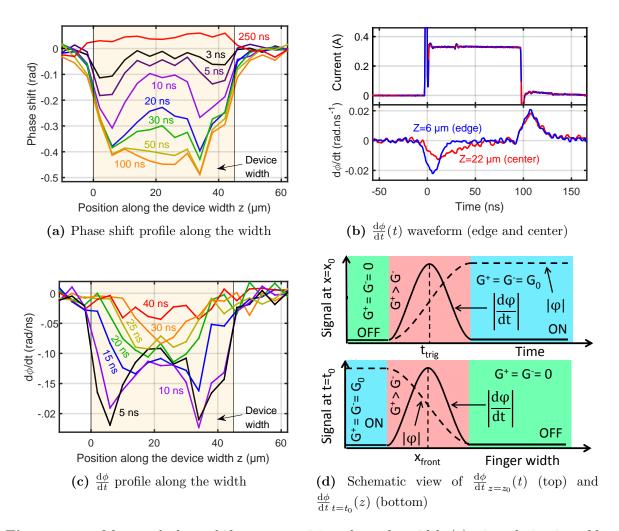

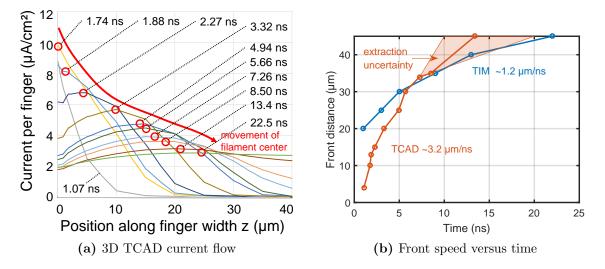

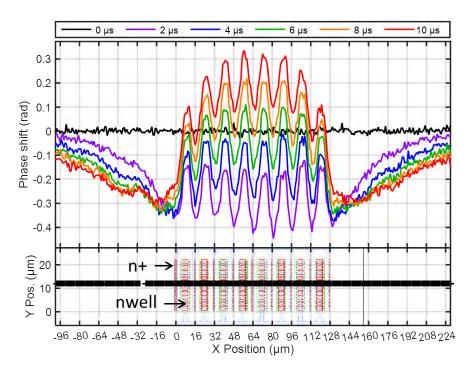

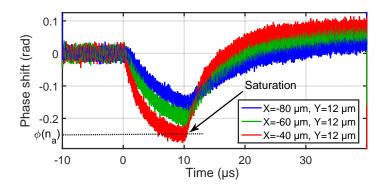

Two types of Silicon controlled rectifiers (SCR) used as ESD protection were studied. The SCR action was studied in terms of initial triggering, on-state spreading (OSS) in one finger, and sequential finger triggering was studied using Transient Interferometric Mapping (TIM). The role of trigger taps was investigated in breakdown with Emission Microscopy (EMMI) and during triggering using TIM.

The reliability of Gallium Nitride High Electron Mobility Transistors (GaN HEMTs) has been investigated in terms of vertical breakdown, degradation of the conducting and blocking performance at high temperature and short circuit load conditions. The behavior of HEMT devices under pulsed stress conditions (ESD and short circuit load) was studied with the TIM technique, which allows to probe the heat dissipation and the free carrier concentration through their effect on the refractive index of the material. New methods to analyze of the phase shift were developed, also enabling to work with distorted signal, or indirect probing outside the active region.

# Kurzfassung

Durch die Miniaturisierung von integrierten Schaltkreisen sind mikroelektronische Vorrichtungen hinsichtlich deren Integrierbarkeit als auch deren Leistung und Preisverhältnis immer besser geworden. Ein Nachteil bei diesem Trend stellt jedoch die Tatsache dar, dass diese Geräte auf Grund von unvorhergesehenen, von steigender Energiedichte verursachten Spannungsdurchschlägen immer mehr zum Durchbruch neigen.

So wird manchmal bis zu der Hälfte der verfügbaren Fläche als Schutz für die aktiven Vorrichtungen eingesetzt. Somit wird übrigens die Leistungsfähigkeit der Vorrichtungen beeinträchtigt.

Diese Arbeit befasst sich zuerst mit elektrostatischer Entladung (ESD) als erste Ursache eines unvorhergesehenen Spannungsdurchschlags.

Dabei wurden die Effekte der ESD auf Silizium-Germanium-Heterobipolartransistoren (SiGe HBT) in rauscharmen Verstärkern erforscht. Es konnten zwei verschiedene Arten athermalen Spannungsdurchschlags bemerkt und analysiert werden, d.h. der Durchbruch von Silizium für lange Anstiegszeiten und die parasitäre Transistorwirkung für kurze Anstiegszeiten und/oder Substratkopplungen.

Es wurden zwei Typen von gesteuerten Silizium-Gleichtrichtern (SCR) mittels transienten interferometrischen Abbildungverfahren beobachtet, welche als ESD-Schutz benutzt wurden. Besondere Aufmerksamkeit wurde auf deren Wirkung bei der Auslösung der Triggerspannung sowie bei der Ausbreitung in einem und in den darauffolgenden Fingern während der Durchlassphase geschenkt. Die Rolle von Abgriffen wurde in Durchbruchsituationen durch Emissionsmikroskopie, bei der Auslösung durch TIM analysiert.

Darüber hinaus wurde die Beständigkeit von Galliumnitrid-Transistoren mit hoher Elektronenbeweglichkeit gegen vertikalen Durchbruch, Funktionsbeeinträchtigung im Sperrund Durchlasszustand bei höheren Temperaturen und Kurzschluss getestet. Das Verhalten von HEMTs unter gepulster Belastung (ESD und Kurzschluss) wurde mit der TIM-Technik untersucht, welche es ermöglicht, die Wärmeabfuhr und die freie Ladungsträgerkonzentration durch deren Wirkung auf den Brechungsindex vom Material zu beweisen. Dabei wurden neue Techniken zur Analyse der Phasenverschiebung – etwa Datengewinnung aus dem verzerrten Signal oder der indirekten Beobachtung außerhalb des aktiven Bereichs – entwickelt.

# Acknowledgement

I would like to thank all the people that have made this thesis a pleasant and fruitful period, which is both the end of my student life and the start of my professional carrier.

The first person I would be like to thank personally is Prof. Dr. Dionyz Pogany for supervising the thesis. His advice has been very valuable to making right choices for experiment design, and less wrong interpretation.

A special thank is owed to Dr. Sergey Bychikhin and Dr. Michael Heer for sharing their knowledge and experience.

I thank the head of the institute, Prof. Dr. Emerich Bertagnolli, Prof. Dr. Gottfried Strasser, and Dr. Mattia Capriotti and (soon to be Dr.) Matteo Rigato with whom I had fruitful cooperation.

I thank Dr. Benedikt Schwarz, Dr. Max Andrews and Dr. Roman Gansch for providing their expertise on various topics.

I thank all the partners of the HiPoSwitch project, and in particular Prof. Gaudenzio Meneghesso, Dr. Jan Kuzmík, Dr. Oliver Hilt, Dr. Joachim Würfl, Dr. Eldad Bahat-Treidel and Dr. Rimma Zhytnytska.

I deeply thank Infineon and Nexperia for trusting me with the analysis of the devices that were investigated, and particularly Werner Simbürger, Hans Tadikken, Markus Sauter, Guido Notermans, Hans-Martin Ritter and Steffen Holland for sharing their deep understanding of their respective fields of knowledge and competence.

Finally I would like to thank my family and friends for their support and patience.

# Contents

| 1 | Introduction                                                                                |            |                 |                                                      |    |  |  |

|---|---------------------------------------------------------------------------------------------|------------|-----------------|------------------------------------------------------|----|--|--|

|   | 1.1                                                                                         | Motivation |                 |                                                      |    |  |  |

|   | 1.2                                                                                         | ESD        |                 |                                                      | 2  |  |  |

|   |                                                                                             | 1.2.1      | Silicon §       | germanium HBT reliability                            | 2  |  |  |

|   |                                                                                             |            | 1.2.1.1         | Silicon germanium HBT concept and use as a low-noise |    |  |  |

|   |                                                                                             |            |                 | amplifier                                            | 2  |  |  |

|   |                                                                                             | 1.2.2      | SCR as          | ESD protection                                       | 4  |  |  |

|   |                                                                                             |            | 1.2.2.1         | A general presentation of ESD protections            | 4  |  |  |

|   |                                                                                             |            | 1.2.2.2         | Silicon Controlled Rectifiers (SCR)                  | 6  |  |  |

|   |                                                                                             |            | 1.2.2.3         | State of the art                                     | 7  |  |  |

|   |                                                                                             |            | 1.2.2.4         | Outline of the section                               | 7  |  |  |

|   | 1.3                                                                                         | GaN I      | HEMTs r         | eliability                                           | 8  |  |  |

|   | 1.4                                                                                         | Metho      | ods             |                                                      | 11 |  |  |

|   |                                                                                             | 1.4.1      | Electric        | al stressing                                         | 11 |  |  |

|   |                                                                                             |            | 1.4.1.1         | Transmission Line Pulser (TLP)                       | 11 |  |  |

|   |                                                                                             |            | 1.4.1.2         | Solid State Pulser (SSP)                             | 12 |  |  |

|   |                                                                                             | 1.4.2      | Optical methods |                                                      |    |  |  |

|   |                                                                                             |            | 1.4.2.1         | Transient Interferometric Mapping (TIM)              | 12 |  |  |

|   |                                                                                             |            | 1.4.2.2         | Backside Infrared Microscopy                         | 16 |  |  |

|   |                                                                                             |            | 1.4.2.3         | Emission microscopy (EMMI)                           | 16 |  |  |

|   |                                                                                             |            | 1.4.2.4         | Optical Beam Induced Current (OBIC)                  | 17 |  |  |

| 2 | ESD self-protected HBT devices and discrete SCR protection 1                                |            |                 |                                                      |    |  |  |

|   | 2.1ESD self protected Silicon-Germanium base HBT as low noise ampli2.1.1Devices under study |            |                 |                                                      |    |  |  |

|   |                                                                                             |            |                 |                                                      |    |  |  |

|   |                                                                                             |            | 2.1.2.1         | Base-emitter characterization                        | 22 |  |  |

|   |                                                                                             |            | 2.1.2.2         | Base-collector characterization                      | 24 |  |  |

|   |                                                                                             |            | 2.1.2.3         | Emitter-collector characterization                   | 24 |  |  |

|   |                                                                                             |            | 2.1.2.4         | Summary of the multifinger device ESD robustness and |    |  |  |

|   |                                                                                             |            |                 | choice of study                                      | 25 |  |  |

|     |       | 2.1.3 Intrinsic and extrinsic Base-Collector failure modes                            | . 26      |

|-----|-------|---------------------------------------------------------------------------------------|-----------|

|     |       | 2.1.3.1 Intrinsic mode $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | . 26      |

|     |       | 2.1.3.2 Extrinsic mode $\ldots$                                                       | . 37      |

|     | 2.2   | SCRs as external ESD protections                                                      | . 43      |

|     |       | 2.2.1 Devices under study                                                             | . 43      |

|     |       | 2.2.2 Study of the trigger taps behavior in breakdown and triggered                   |           |

|     |       | modes in SCRs                                                                         | . 44      |

|     |       | 2.2.2.1 DC EMMI analysis of the SCR                                                   |           |

|     |       | 2.2.2.2 TIM analysis of the SCR with trigger taps                                     |           |

|     |       | 2.2.3 On-state spreading in SCR devices                                               | . 48      |

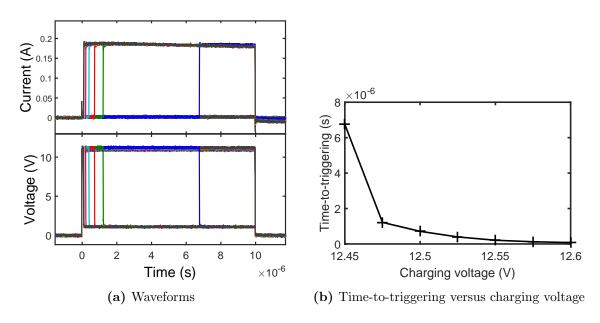

|     |       | 2.2.4 Time-to-triggering in open base SCRs                                            | . 52      |

|     |       | 2.2.5 Rise time effect and sequential finger triggering in SOI open base              |           |

|     |       | SCR                                                                                   | . 55      |

|     |       | 2.2.6 High current regime in open base SCR                                            |           |

|     |       | 2.2.6.1 High current regime in bulk open base SCR $\ldots$                            |           |

|     |       | 2.2.6.2 High current regime in SOI open base SCR $\ldots$                             | . 67      |

| 5   | Gal   | llium nitride HEMTs                                                                   | <b>73</b> |

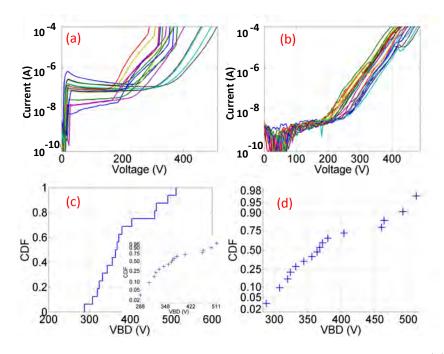

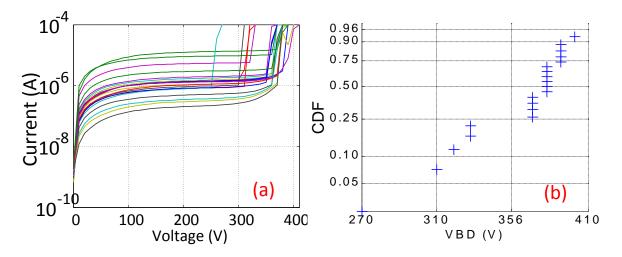

|     | 3.1   | Study of the vertical breakdown                                                       | . 73      |

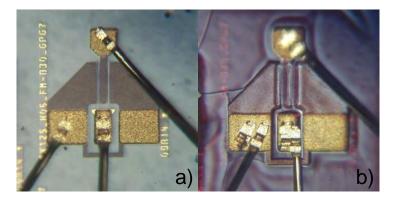

|     |       | 3.1.1 Devices under study                                                             | . 73      |

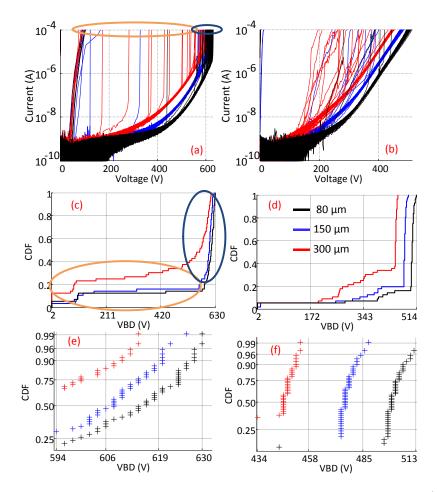

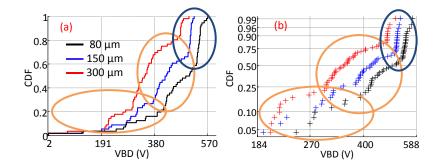

|     |       | 3.1.2 Statistical IV analysis                                                         | . 74      |

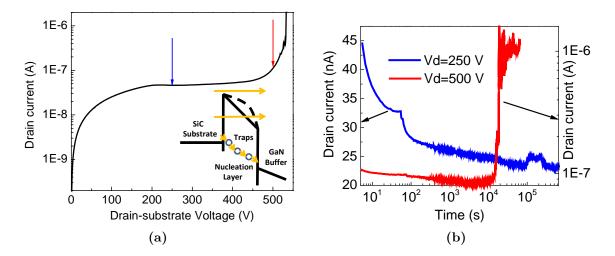

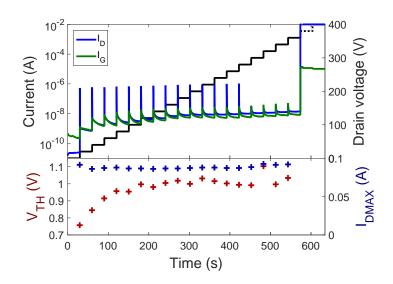

|     |       | 3.1.3 Time dependent vertical breakdown                                               | . 78      |

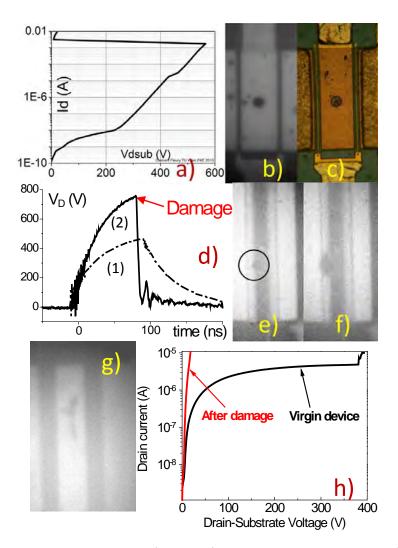

|     |       | 3.1.4 Failure analysis using backside infrared microscopy                             | . 79      |

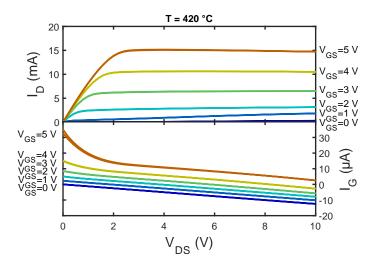

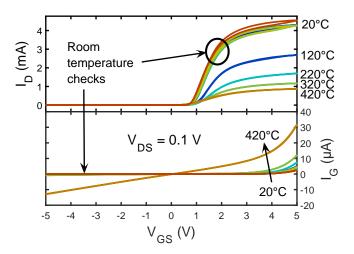

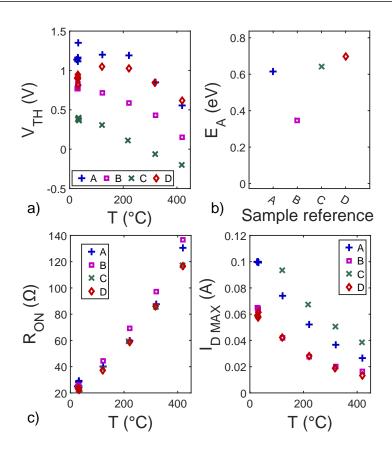

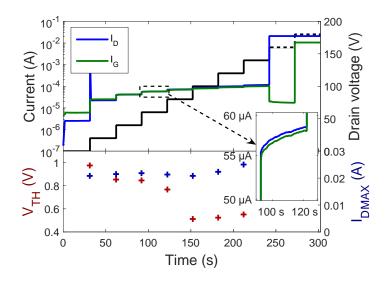

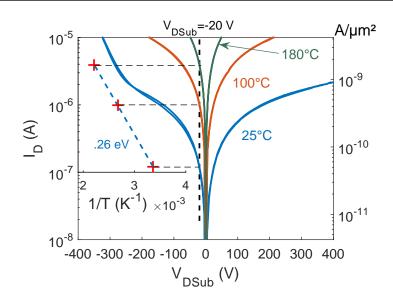

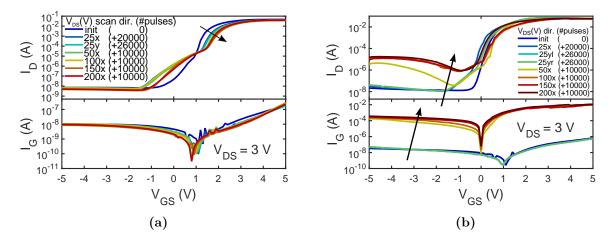

|     | 3.2   | Degradation of GaN HEMTs in high temperature conditions $\ . \ . \ . \ .$             | . 82      |

|     |       | 3.2.1 Devices under study                                                             | . 82      |

|     |       | 3.2.2 High temperature DC performance                                                 | . 83      |

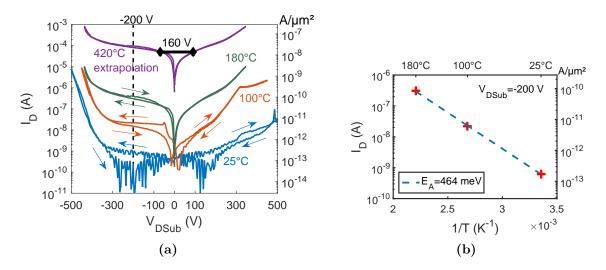

|     |       | 3.2.3 High temperature blocking capabilities                                          | . 86      |

|     |       | 3.2.4 Vertical leakage current dependence on temperature                              |           |

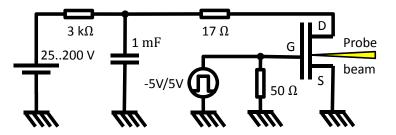

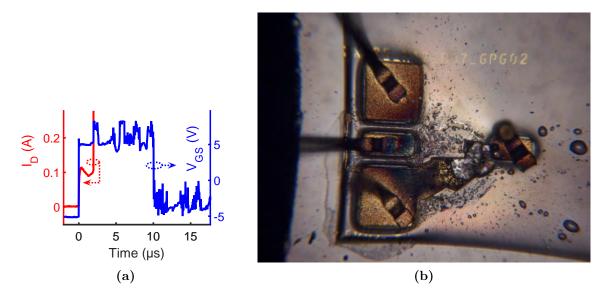

|     | 3.3   | Short circuit conditions                                                              | . 90      |

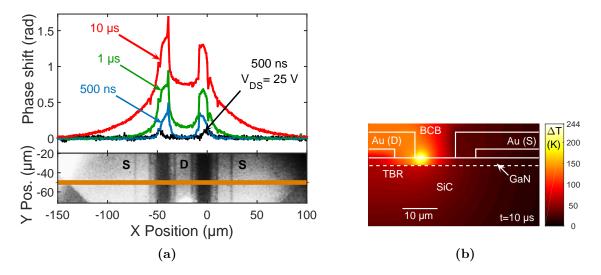

|     |       | 3.3.1 Power dissipation and reliability                                               | . 90      |

|     |       | 3.3.2 A new method for power dissipation and temperature extraction                   |           |

|     |       | from TIM data                                                                         | . 93      |

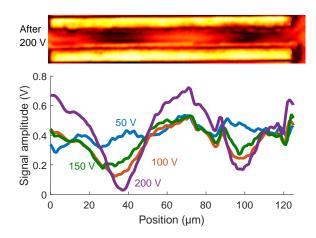

|     |       | 3.3.2.1 Optical artifacts in the access region                                        | . 94      |

|     |       | 3.3.2.2 Use of optical and thermal simulation for data analysis .                     | . 95      |

| Ł   | Cor   | nclusion and prospects                                                                | 99        |

| Re  | efere | ences                                                                                 | 101       |

| ۸ ۱ | bbro  | viations                                                                              | 117       |

| A   | nnte  | v1a010115                                                                             | тт (      |

# Chapter 1

# Introduction

# 1.1 Motivation

From smart phones to autonomous cars, microelectronics devices are more and more central to modern society. Since its beginning, microelectronics industry has been in a continuous process of diversification and improvement. The strength of microelectronics lies in the lithographic processes, that have allowed a mass production. The progress of the lithography has allowed to reach smaller and smaller feature size, thus improving the density of the devices on the wafer, which reduces their fabrication cost. In parallel, the fabrication on larger and larger silicon wafers has allowed to produce more and more devices on one wafer.

The miniaturization has not only been interesting for questions of cost, but also for the performances of the devices. The miniaturization of field effect transistors has enabled processors to reach higher speeds by reducing the switching time, and has allowed multicore designs with billions of transistors. The reduction of the size of bipolar junction transistors allows to decrease the base transit time, and therefore improve their cut-off frequency.

Nowadays, the reduction has reached critical points for some of the silicon devices. The blocking capabilities of the devices are constrained by the breakdown electric field of silicon. The use of other materials having higher breakdown electric fields while still having other interesting properties has been developed in the last decades, such as silicon carbide, or ultimately gallium nitride. These materials are more expensive than silicon, and growing them on silicon substrates to reduce the costs has been a very active field of research.

Independently of the material, the miniaturization of the active region leads to an increase of the power density. This leads in turn to self heating, which can in the best cases be a source of performance degradation, and in the worst case lead to catastrophic failure due to thermal instability. This makes the devices very sensitive to certain types of stress that their bulky ancestors would have sustained without difficulty, and other new

types of stress that they would never have encountered in their use - even by accident.

# 1.2 ESD

Electrostatic discharges are produced when an object who has gathered charges by triboelectric or electrostatic induction effect discharges to another object due to a contact or a dielectric breakdown [1]. The energy of the discharge is low, but as the microelectronic circuit are small, the dissipated power density might be high enough to damage the components. Difference in objects capacitance and resistivity result in different density and duration of the current flow. As the microelectronic circuit should encounter various type of object in their production and their use, the industry has defined standardized models that define several types of ESD. The Human Body Model (HBM) of ESD aims to capture the ESD that is produced when a human being touches a pin and discharges in it. The model is essentially a capacitive discharge. The standardized test is made with an ESD gun, whose charging voltage is chosen according to the requirements of the situation in which the device will be placed. The device will then be called "robust" to a precise charging voltage if it sustains an ESD discharge at this charging voltage.

# 1.2.1 Silicon germanium HBT reliability

## 1.2.1.1 Silicon germanium HBT concept and use as a low-noise amplifier

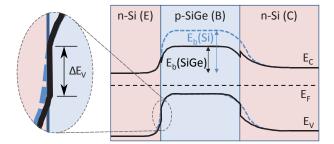

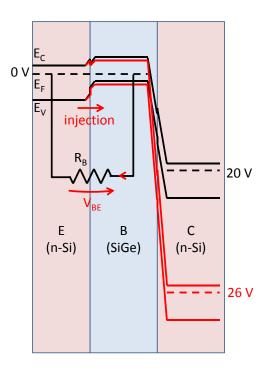

Figure 1.1: Schematics band diagram of a SiGe HBT, with silicon BJT in dashed line for comparison.[2]

Silicon germanium (SiGe) base hetero-junction bipolar transistor (HBT) are widely used in RF circuits due to several interesting properties, that we will shortly detail before discussing reliability issues. SiGe HBTs are made on silicon wafers. The silicon serves as collector, and is generally accessed by a burried layer. Then a p-doped noncrystalline SiGe layer that will be used as the base is grown, and a growth of silicon on top of the SiGe, or poly-silicon in some cases, makes the emitter on top of the base. The use of a silicon wafer enable SiGe HBT technology to inherit some of the advantages of silicon, for example in terms of thermal conduction, but also in terms of technological developments for large

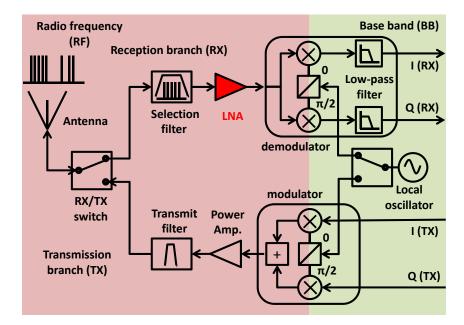

**Figure 1.2:** Position of the HBT as a low noise amplifier (LNA) in a reception branch of a mobile phone

crystal growth and doping, which makes them an affordable solution. Another advantage of using a silicon wafer is that a silicon CMOS circuitry can be included on the same chip to be used in BCMOS technology, or for a separate logic circuitry. The added value of the SiGe compared to pure silicon is the possibility of band gap engineering. The band gap of SiGe ranges between the band gap of silicon (1.14 eV at 273K) and germanium (0.67 eV at 273K). The alloy stoichiometry is typically in the range of 12 % germanium in the base of the HBT, which provides a band gap shrinkage of 50 meV [3]. The device that will be studied here have a Si<sub>.85</sub>Ge<sub>.15</sub> base. Figure 1.1 shows the comparison between a SiGe HBT and a Si BJT band diagram at equilibrium. One can see that the valence bandgap discontinuity  $\Delta E_V$  allows to keep a barrier for holes from base to emitter that is very similar as for the Si BJT, as seen in the zoom. This helps maintaining a low base leakage current. The main effect of the band gap engineering is seen in at the conduction band where the built-in potential of the base-emitter junction is lower in the case of the SiGe HBT compared to its silicon counterpart.

This allows to increase the doping in the base and reduce the base width to minimize the transit time of electrons to increase the speed of the device, while still avoiding punchthrough and gain loss. The cut-off frequency is roughly five times higher than with Si BJT [2, 4, 5]. Another key aspect is the lattice constant that varies according to the stoichiometry of the alloy. At 300 K, the lattice constant of  $Si_{.85}Ge_{.15}$  (5.47 Å[6]) is larger than the lattice constant of pure Si (5.43 Å[6]), and the SiGe is therefore compressively strained. This opens the possibility of strain engineering but also gives constraints to the largest achievable mono-crystal that can be grown on a silicon substrate at a given thickness. The devices under study will have a maximum emitter window length of 10  $\mu$ m and 2  $\mu$ m width, or will have several fingers in parallel to achieve the desired collector current.

The HBT that has been studied here is used as a low noise amplifier. Figure 1.2 shows a possible architecture for the hardware of a general RF communication device, such as a mobile phone. For transmission, the RX/TX switch is set to connect the transmission branch to the antenna. The signal is mixed with the signal of a local oscillator to reach the desired RF frequency. For reception purposes, the RX/TX switch is set to connect the reception branch to the antenna (as in the schematics). The signal is filtered by the selection filter, amplified by the low noise amplifier and the IQ frequency demodulator brings the signal to the base band. As its name suggests, the LNA device amplifies with minimal increase of the signal to noise ratio from the input (filtered signal from the antenna) to the output (mixer). More than noise, the major concern of nowadays' design is linearity. The generation of harmonics that could cause intermodulation distortion in the mixing, as well as a noise for other reception channel (e.g GPS), should be minimized.

The devices under study are derived from the base technology presented in [4, 5] but with modified collector and base for higher breakdown voltage. Nevertheless, this modification also results in a lower cut-off frequency. The goal of this study is therefore to find how to get an improved ESD robustness of the device without giving up on the performance.

Part 2.1.2 will present the robustness of all junctions of the device. Section 2.1.3.1 will show the study of a high current, long rise time failure of the base-collector, whereas section 2.1.3.2 will show the causes of a low current/short rise time failure of the base-collector.

# 1.2.2 SCR as ESD protection

## 1.2.2.1 A general presentation of ESD protections

Many devices are nowadays equipped with USB ports, one function of whose is to transmit data through wire with a high rate - in 2017, 10 Gb/s has already been achieved. The devices that are directly on the interface between the system and the external world are subject to electrostatic discharges (ESD), that have become more and more dangerous for them as the miniaturization has concentrated the same electrical currents into a smaller and smaller area. These devices therefore need to be protected against ESD with protection devices that cannot be scaled down with the same factor, as they are bounded by the hard constraint of the electrical current value of the discharge. Although technological progress has been achieved with ESD protection, the protection takes more and more space on the die, which limits the yield, and sometimes the performance. Protection devices can be quite complex structures on the inside, but from the outside they are mere

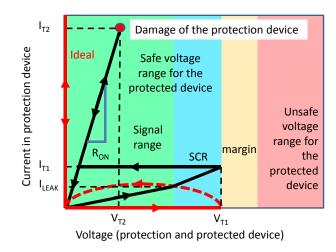

Figure 1.3: IV characteristics of an ideal ESD protection and a realistic SCR

two port devices that need to be connected in parallel to the protected USB port. This simplicity of the connections allows them to be placed in the third dimension as discrete components, which make their market one of the few microelectronics areas where the discrete component approach is still preferred to the integration. Several technologies of ESD protection are available on the market against different kinds of ESD and for different kinds of protected devices. Here we will focus on the Silicon Controlled Rectifier (SCR) for the protection of USB ports.

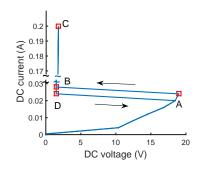

Ideally the protection is invisible to the rest of the system until it is needed to protect it. Figure 1.3 shows with red lines the current intensity-voltage characteristics (IV) of an ideal protection. Note that the protection device is in parallel with the protected device, so they share the same voltage. The ideal device is an open circuit when the voltage is safe (green and blue voltage range), and turns instantaneously into a short circuit if - and only if - the voltage ever goes beyond a given triggering voltage that is chosen from the designer at a margin of the unsafe voltage range for the protected device (the red area). The triggering voltage is noted  $V_{T1}$ .

The protection should also be able to go back to its dormant state once the ESD is over. Since the current is the only variable when the protection device is triggered, the protection has to be designed to turn off when the current value corresponds to a safe voltage in the characteristics of the protected device. This current is called the holding current  $I_{\rm H}$ .

In practice, the device is not a perfect open circuit in its dormant state, because it has a leakage current (marked  $I_{LEAK}$  on figure 1.3), but also a capacitance, which is a source of attenuation and distortion for the useful signal. For high data rate USB purpose, the capacitance has to be less than 0.25 pF in the useful voltage range according to the IEC 61000-4-2 standard [7].

In its active state a real device does not feature a zero voltage, but is clamped below a voltage that should be safe for the protected device (green and blue area in figure 1.3). As

the device should stay in the safe zone independently of the current value in the protection, the slope of the IV curve in the triggered state should be as vertical as possible. The device should therefore have a large ON-conductance, or a small ON-resistance  $R_{ON}$ . A large  $R_{ON}$  also generates a power dissipation which can be a source of failure for the protection device itself at high current. The destruction current and voltage are called  $I_{T2}$  and  $V_{T2}$ , respectively. Last but not least, a real device takes a non zero time to react to the high voltage at its ports. This is referred as triggering time.

Shunting high currents is demanding in terms of space as the current needs to be spread to a large width so that the protection itself stays safe. Devices are therefore usually composed of several fingers in parallel, which divide the R<sub>ON</sub> by as many folds.

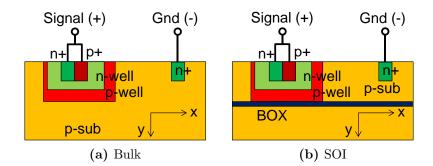

## 1.2.2.2 Silicon Controlled Rectifiers (SCR)

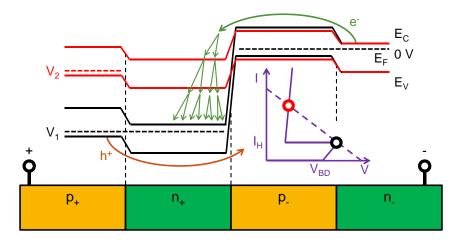

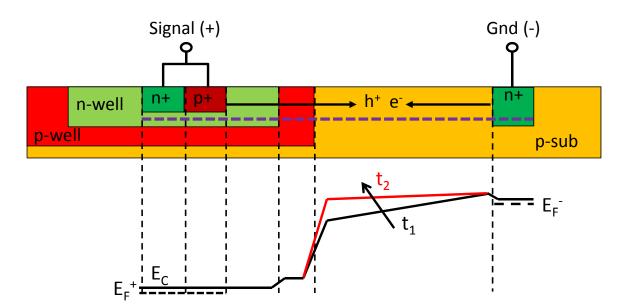

Figure 1.4: SCR structure and band diagram in blocking and triggered configurations

SCRs are PNPN structures [8] such as described in figure 1.4, which also shows the band diagram of the structure under blocking condition at voltage V1 (black) and triggered conditions at voltage V2 (red). The IV characteristics of the SCR in inset show the IV points in corresponding colors. SCR are used as ESD protection due to their S-shaped characteristics. For voltage V1 below the triggering voltage, the SCR presents a band structure such as presented in black in figure 1.4. At such voltage levels, both  $p^+/n^+$  and  $p^-/n^-$  junctions are forward biased, and the  $n^+/p^-$  junction is reverse biased, which is the cause of the blocking state. This allows an SCR in parallel of a protected device to have a low leakage. The breakdown voltage V<sub>BD</sub> corresponds to the voltage at which the  $n^+/p^-$  junction starts its avalanche breakdown represented by the arrows above the conduction band. The avalanche multiplication factor is voltage dependent, and is represented schematically by the 8 arrows that reach conduction band for V=V1 (against 2 for V=V2). At higher and higher voltage, the current flow increases, and the injections of electrons from the  $n^-$  through the  $p^-$  and holes from the  $p^+$  through the  $n^+$  provide more and more carriers to feed the avalanche process. Provided enough current, the device will "trigger". This means that the voltage that is needed to maintain the current level by means of carrier multiplication drops, as the avalanche current is fed by the injection. This state is represented by the red band diagram, where the multiplication is schematically represented as 2 arrows reaching the conduction band for V=V2. In practice, the device has to follow a load line, so the current increases as the voltage drops. From the triggered condition, the device can only be brought back to a breakdown condition by having a current flowing that is smaller than the holding current I<sub>H</sub>.

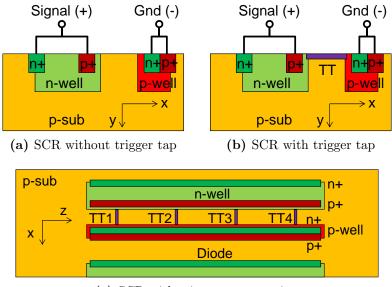

#### 1.2.2.3 State of the art

The SCR scheme that has been presented in the previous part can be applied in several ways to achieve the desired parameters for  $V_{T1}$ ,  $I_H$ , Capacitance,  $R_{ON}$ , and leakage current, although there are tradeoffs to be made. First of all, in some applications, another connection can be made to the p<sup>-</sup> to be used as a gate. A pulsed current can serve as triggering current instead of the breakdown current. This is not used for ESD protection, where the p<sup>-</sup> is connected to the n<sup>-</sup>.

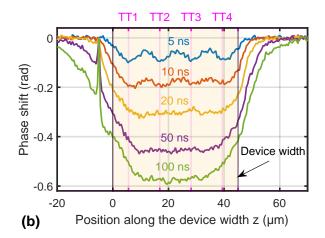

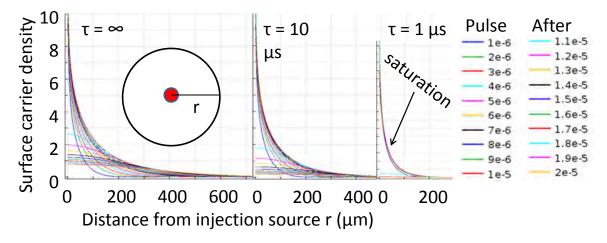

The  $n^+$  and  $p^-$  can be widened, and less doped to lower the leakage current and diminish the capacitance by spreading the depletion width. In the SCR that will be presented in this part, the p<sup>-</sup> length is largely composed of the low p-doped substrate itself. In turn this approach gives a much larger triggering voltage (up to 80 V), that can be unsuitable to the use of the SCR as an ESD protection. The way around this problem is to insert trigger taps [9]. The trigger taps are narrow regions of p implants in the p<sup>-</sup> region in the device width to achieve the desired low triggering voltage. Their role is to start the injection that can trigger the rest of the device. On the one hand, the trigger taps have a high contribution to the overall capacitance and to the leakage, and their number should therefore be minimized. On the other hand, the process of propagation of the ON-state (On-state spreading) has a finite speed along the width, which imposes a large enough number of these trigger taps to start the mechanism at several places. The  $R_{ON}$  of the device depends on the resistance of the structure, which is dominated by the low p-doped p<sup>-</sup> region, and the total width of the device. This width can be the combined width of several fingers that are independent SCRs. If the fingers are isolated, one should not expect that they all trigger, as the first finger to trigger will make the voltage drop and prevent the current to flow in the other ones. Making all fingers of the device trigger simultaneously requires either that the voltage goes temporarily higher than the triggering voltage, or that a parasitic current (e.g to the substrate [10] or a displacement current [11]) initiates the triggering in all fingers, in a similar way as when the gate is used.

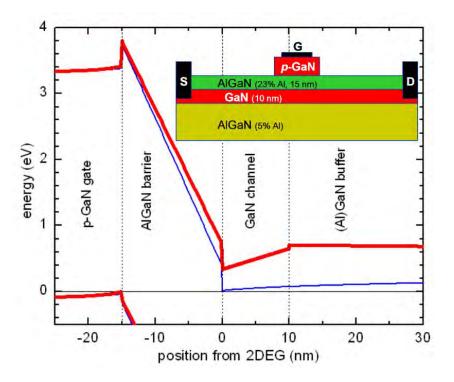

Figure 1.5: Simulated band structure at the gate position for a device with GaN buffer (thin, blue) and a device with Al 0.05 Ga 0.95 N buffer (bold, red). Inset: schematic cross section of the p-GaN gate GaN transistor. [12]

## 1.2.2.4 Outline of the section

Section 2.2.2 will show the behavior of the trigger taps in blocking and triggered state using EMMI and TIM. In the next part (2.2.3) the ON-state spreading will be measured with TIM and compared to simulations. The time-to-triggering at low voltage will be analyzed in part 2.2.4. In part 2.2.5, the focus will be made on how the fingers of the open base SCR share the power during the pulse depending on the pulse rise time, also using TIM at different current levels. Finally in part 2.2.6 the power dissipation at very high current will be analyzed to see the origin of the high current failure of the device.

# 1.3 GaN HEMTs reliability

**Gallium nitride (GaN)** is a III-V semiconductor with a 3.4 eV direct band gap. Although the 2014 Nobel prize for Physics has been awarded to Isamu Akasaki, Hiroshi Amano and Shuji Nakamura for their research on GaN to produce blue and white light by making a electroluminescent diode out of it [14, 15], large band gap semiconductors are also suitable for other purposes, in particular for the design of high voltage devices, thanks to their high blocking capability. GaN features a relatively high thermal conductivity of 250 W/mK at room temperature [16], which can be used to evacuate the dissipated heat

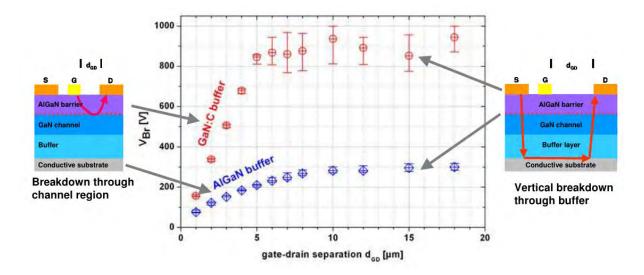

Figure 1.6: Median value of device breakdown in dependence on gate-to-drain distance ( $d_{GD}$ ) for different buffer designs. The insets on the left and right side are highlighting the proposed breakdown mechanisms in the respective regions of the IV-characteristic. [13]

in a device. It also features a spontaneous polarization [17], that provides additional possibilities for the design of devices. The material capabilities of GaN also give hope that these devices be able to operate at high temperatures whether due to self- or external heating conditions [18, 19].

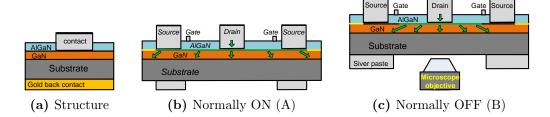

Numerous designs of GaN power devices have been demonstrated, such as vertical power transistors [20] or MOSFETs [21]. In this part, the focus will be made on Al-GaN/GaN high electron mobility transistors (HEMTs) [22].

**High electron mobility transistors** Figure 1.5 shows the schematics cross-section of a transistor made with a GaN channel [12] and the associated simulated band diagram under the gate. The channel presents a triangular well that is created by polarization charges at the barrier/channel interface [23] (hence the electrical field discontinuity). In absence of a p-GaN gate, as in the access region, the triangular well is partially under the Fermi level, which allows conduction. The confinement of the electrons in a 2-dimensional electron gas (2DEG) gives them a high mobility [24]. The additional growth of a p-GaN gate on top of a part of the 2DEG is used to lift the triangular well above the Fermi level as in figure 1.5, which depletes it. This area is called the channel of the transistor, and the area between the channel and the drain/source contacts where the 2DEG is present is called the access region. To operate the transistor, the triangular well can be brought down under the Fermi level by applying a positive voltage on the p-GaN gate. This brings the transistor in ON state. For safety reasons, the transistor should have a high enough threshold voltage. In OFF state, when a high voltage is set on the drain and the gate is grounded, the access region gets depleted as well and the whole access

region sustains the electric field. The use of an AlGaN buffer allows to have an insulated buffer to limit the punch-through under the gate. This is made at the expense of the thermal conductivity [25]. Carbon or iron doping of a GaN buffer can also be used to the same purpose. As bulk GaN is expensive, the buffer is grown on a SiC substrate, with a final goal to have GaN on silicon devices [26]. Gallium nitride HEMTs face several reliability issues, such as charge trapping [27], or dynamic ON-resistance due to virtual gate effect [28].

**Vertical breakdown** The first part of this study will focus on the high voltage breakdown. The breakdown voltage  $V_{BD}$  of HEMTs has been proved to linearly increase with the gate to drain distance  $L_{GD}$ , as a critical electric field needs to be reached in the gate-to-drain area, see figure 1.6 on the left. Beyond a critical voltage,  $V_{BD}$  becomes independent of  $L_{GD}$  [13, 29]. The explanation involves a parasitic current path through the substrate as depicted in figure 1.6 on the right. To enable this path, the voltage should be high enough to breakdown the vertical stack in one direction and the other [13, 29]. The high spreading in the  $V_{BD}$  data in vertical mode might indicate that the vertical current conduction is related to extended defects. Trap-mediated transport [30, 31] was hypothesized by several groups, and the failure was located by conventional microscopy [31]. These studies have led to the optimization of the contact areas. [32]. However, more understanding of the vertical breakdown is necessary to produce devices that can be reliable at high voltage. In section 3.1, a statistical analysis that can extract useful information from vertical DC-IV measurements at the wafer level will be shown. The time dependence of the vertical breakdown will be demonstrated and explained in section 3.1.4. The vertical breakdown will also be analyzed by the failure analysis of purposely damaged device using infrared microscopy in section 3.1.4.

**High temperature behavior** As a strong point of GaN devices should be their high temperature operation, reliability of GaN HEMTs under high temperature conditions need to be studied. The variations of the threshold voltage, and the decrease of the transconductance and the maximum drain current will be shown in section 3.2.2 in DC operation. The blocking capabilities of the GaN HEMT at high temperature will be shown in section 3.2.3 and the hypothesis that the lowering of the breakdown is due to vertical breakdown will be discussed using high temperature vertical breakdown measurement in section 3.2.4.

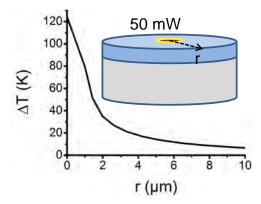

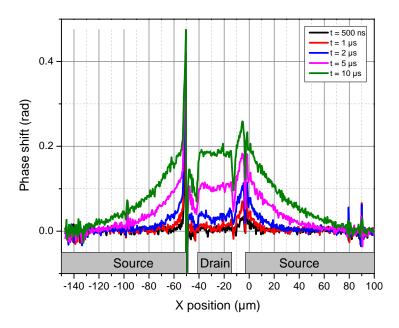

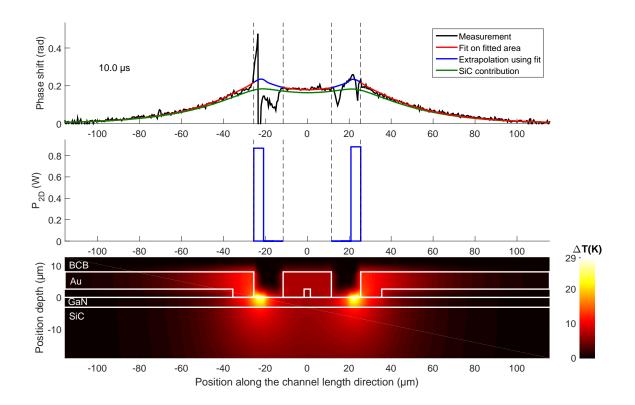

**Short circuit load operation** The self-heating effect is one of the main limiting factors for the performance and reliability of these devices. Liquid crystal thermography [33], micro-Raman thermography [34] or scanning thermal microscopy [35], have been used to map the temperature distribution in GaN-based devices. Section 3.3 will show the thermal analysis and the reliability of HEMT devices by the TIM technique (see section 1.4.2.1)

under short circuit load operation, where the drain voltage is nearly fixed due to the short circuit like load line and the gate is open during 10  $\mu$ s. By nowadays' standards, The HEMTs should be robust to this conditions during few microseconds [36, 37].

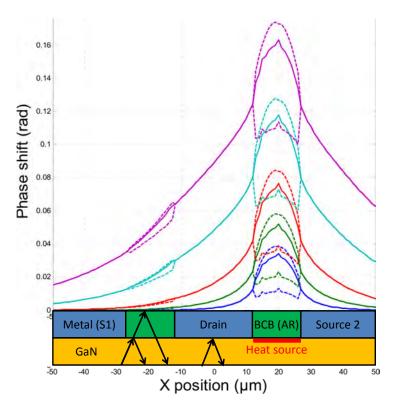

**TIM on GaN HEMTs** Section 3.3.2 will present a new post-processing method for TIM data evaluation, enabling temperature extraction in the whole heated region from the limited TIM data outside the active region utilizing the 2-dimensional nature of the power dissipation source located in the two-dimensional electron gas (2DEG).

# 1.4 Methods

# 1.4.1 Electrical stressing

#### 1.4.1.1 Transmission Line Pulser (TLP)

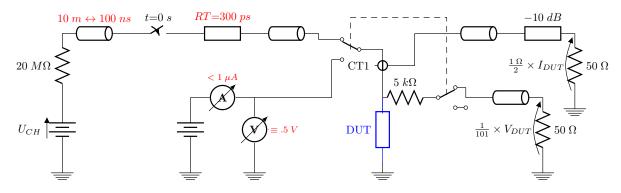

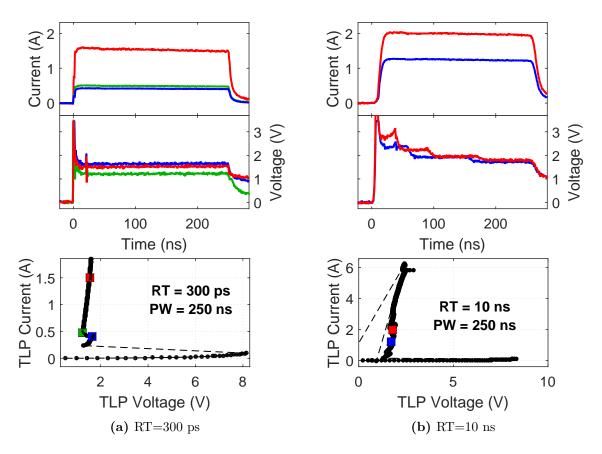

Figure 1.7: Schematics of a 4-point-probe TLP system, adjustable parameters are shown in red.

The Transmission Line Pulser (TLP) is an instrument that allows to provide a wide range of electrical pulses. As figure 1.7 shows, a coaxial cable is charged at a defined charging voltage (between -1.5 kV and +1.5 kV for this HPPI model). The opening of a relay (REED, or mercury relay) then discharges the line into the device under test [38, 39]. The width of the pulse (PW) is equal to the time that the pulse needs to travel twice the length of the charged line, which makes 10 ns/m. In the following study, we used line lengths that provide pulses from 10 ns up to 450 ns. Rise Time (RT) filters can be connected between the end of the charged transmission line and the output of the relay that low-pass filter the pulse, hence smoothing the edges, so that the pulse RT is fixed at a specified value. The user can choose between values of 100 ps (no filter), 300 ps, 1 ns, 5 ns, 10 ns, and 50 ns. The main inconvenient of the TLP for some purposes is its large jitter, i.e the precision on the time at which the pulse starts. This means that the TLP has to be the trigger source for all other instruments in the measurement. This for

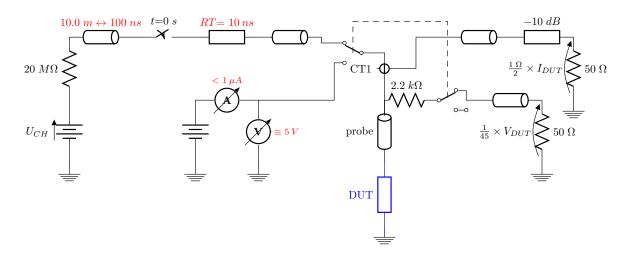

Figure 1.8: Schematics of a 2-point-probe TLP system, adjustable parameters are shown in red.

example excludes the TLP as a stress for the 2D-TIM setup, where a pulsed laser has to be synchronized to the electrical stress.

The pulse parameters that correspond best to the HBM model are PW = 100 ns and RT = 10 ns [1]. This approximation is valid mostly from the energy point of view and not necessarily for all the transient voltage or current, to which a device can also be sensitive, as it will be shown with the HBT devices in part 2.1 and with the SCR in part 2.2.

Two ways have been used to probe the voltage at the device. The 4-point-probe configuration is shown in figure 1.7, where the voltage is probed at the device with a  $5k\Omega$  probe needle. This configuration allows to cancel the contact resistance due to the force probe. The setup shown in figure 1.8 is a two point probe setup. The measured voltage should be corrected for the contact resistance, but its compactness makes it a more convenient tool for stressing during TIM.

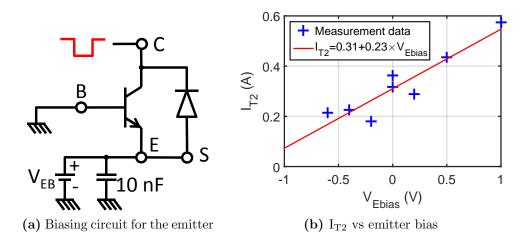

## 1.4.1.2 Solid State Pulser (SSP)

The solid state pulser uses a solid state switch. The interest of the SSP is a low jitter in the ns range that allows synchronization with other instruments, pulses of arbitrary lengths, and the possibility of using a repetitive mode, which can be useful for techniques such as EMMI where a single pulse does not produce a detectable response. A baseline can also be used. The limitations of the SSP are the minimum rise time of 5 ns, and the maximum charging voltage of 100 V, which provides 2 A under 50  $\Omega$  load line.

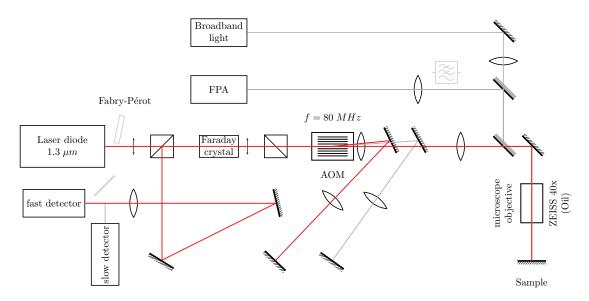

Figure 1.9: Schematics of the TIM setup in fast heterodyne configuration

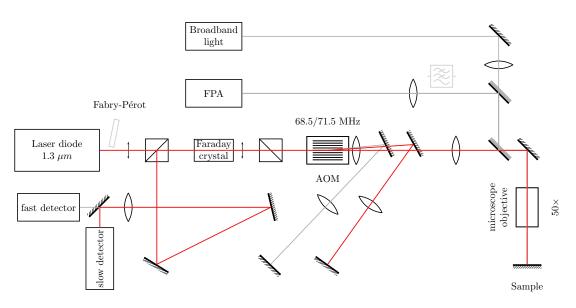

Figure 1.10: Schematics of the TIM setup in slow heterodyne configuration

# 1.4.2 Optical methods

## 1.4.2.1 Transient Interferometric Mapping (TIM)

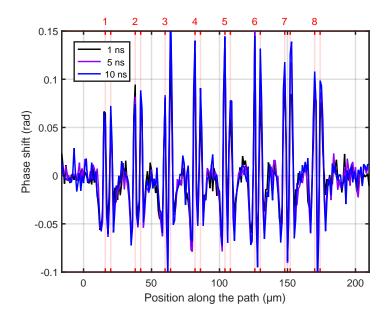

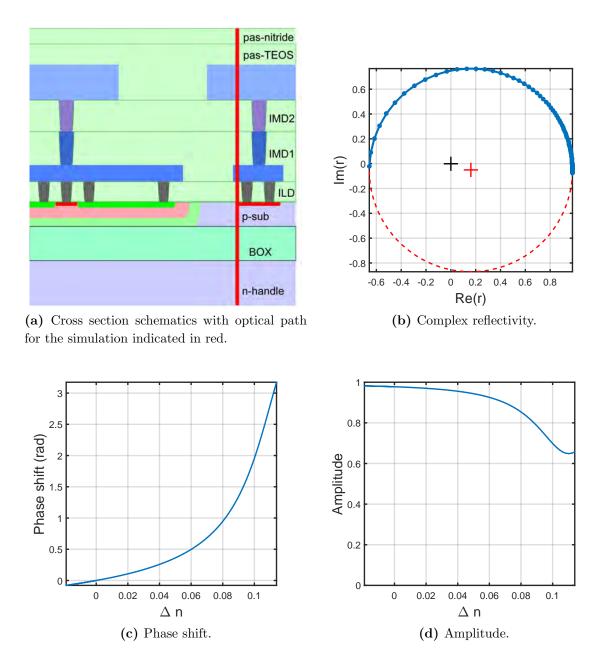

The TIM technique is based on the measurement of the change of refractive index due to temperature or free carrier concentration (FC) change during an electrical stress (e.g under TLP stress). The measurement is performed with an interferometer shown schematically in figure 1.9 and 1.10, where the probe beam probes the device from the polished backside. The wavelength of the laser is  $\lambda=1.3 \ \mu m$ , so semiconductors with a band gap larger than 0.95 eV (including silicon with 1.1 eV and GaN with 3.4 eV) are transparent to the probe

beam, provided they are low-doped.

The change of the index of refraction with the density of the free carrier plasma can be explained in terms of the Drude model for the photons going through the medium, where they can scatter with the free carriers, hence decreasing their group velocity. [40]

The change of the index of refraction with temperature has been measured for several materials by [41]. In general the change of the refractive index with temperature or FC will be described with a linear model around a fixed condition, where the coefficient will only be material dependent.

**The effect of the refractive index change** on the phase of the probe beam depends on the behavior of the light in the device. The light can be scattered, in which case the effect is unpredictable without accurate 3D optical modeling, so this case will be left apart.

The simplest case is the single reflection, where the phase shift is due to the lengthening or shortening of the optical distance. As the beam is reflected on the metal or on the top interface with air, it goes twice through the device. We note z the direction of the beam in the device and  $\lambda$  the wavelength of the light in vacuum (here 1.3  $\mu$ m). Provided a field of refractive index change  $\Delta n(x, y, z, t)$ , the phase shift  $\Delta \phi(x, y, t)$  of the probed beam will therefore be given by:

$$\Delta\varphi(x, y, t) = 2 \times \frac{2\pi}{\lambda} \int_{bottom}^{top} \Delta n(x, y, z, t) dz$$

(1.1)

In this case the reflectivity of the device will change very little during the pulse.

If there are reflections at other interfaces, as in the case of a SOI substrate or a GaN heterostructure, the dependence on the phase shift is more complicated and the reflectivity is likely to change due to constructive and destructive interferences. One way to compute the phase shift response to a given refractive index change at a given vertical position is to use the transfer matrix method [42], where a complex valued transfer matrix is computed for each layer using its thickness and refractive index (plus the refractive index variation for the active layer). After the multiplication of all matrices corresponding to each layer, the complex reflection coefficient of the whole stack is extracted. The complex argument of the reflection coefficient is the phase of the beam, and its squared modulus is the reflectivity.

This computation can give the phase associated to any field of refractive index, but it suffers some issues when applied to practical cases. The computation requires a level of precision on the thicknesses of the layers that is small compared to  $\lambda/2n$ , i.e tens of nanometers. As the process is not always able to reach this precision in all layers (particularly for the passivation layer), the best course of action is to FIB-cut the device along the scan path after the TIM scan and measure the layer, which is still quite an investment to make.

#### 1.4. METHODS

Note that these simulation techniques compute the response from a given refractive index change, whereas we are actually much more interested by the inverse problem. This will be discussed in a few paragraphs.

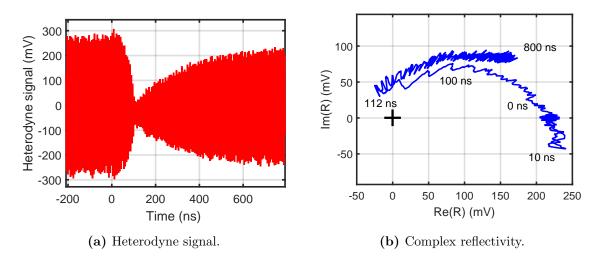

**The measurement of the phase shift** is performed with a heterodyne interferometer. The word "heterodyne" indicates that there is a mixing to an intermediate frequency. The fast heterodyne configuration shown in figure 1.9 is suitable for short stress in the order of 100 ns. The mixing is made through a Acoustical-Optical Modulator (AOM) fed with a 80 MHz signal, that shifts the frequency of the probe beam by 160 MHz compared to the reference beam. The interference of these two beams at the detector creates a 160MHz beating signal with a phase that is equal to the phase of the probe beam.

The slow heterodyne configuration shown in figure 1.10 uses a frequency for the probe beam and a second frequency for the reference beam. The beating frequency is then half the difference between both. The heterodyne signal will typically be at 71.5-68.5=3 MHz. This allows using a slower, more precise detector and record the response to longer stress.

The device positioning is performed by a stage with 100 nm step. The device is contacted on the stage with the appropriate circuitry. Every step of the scan consists in displacing the device to a new position, enabling the stress a chosen number of time while recording the electrical waveforms and the signal from the detector (the oscilloscope is triggered on the current or the voltage), and performing a leakage check to control whether the device suffers cumulative damage. The leakage check uses relays to switch the connection of the device to a SMU.

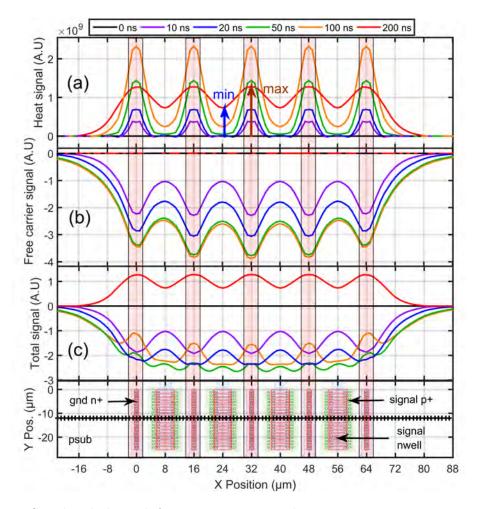

**The post-processing** of the TIM signal is done numerically by phase demodulation of the recorded signal for the phase shift [43]. The amplitude can be extracted as well, for example using Hilbert transform. The averaging is done after the extraction on individual waveforms. Filtering of the signal can be needed in some cases, at the expense of the high frequency features of the signal.

The interpretation of the phase shift should be made using different approaches, depending on the optical response discussed earlier and the nature of the optical phenomenon (FC or temperature). In the case of a single reflection and when only one material is heated, a purely thermal signal is proportional to the integral of the heat along the z axis. As long as the diffusion length of the heat is smaller than the resolution of the scan, the time derivative of phase shift corresponds to the integral of the power dissipation. As the phase shift starts at zero by definition, the derivative is proportional to the phase shift itself at low time, provided that the power dissipation be constant during this interval, which provides yet another simplification of the phase shift interpretation,

at the cost of one more hypothesis. This hypothesis will be unsafe to use in the case of filaments that move faster than the diffusion allows, for example, and the derivative needs to be used even for time below the diffusion time corresponding to the scan step or the required precision [44]. As time goes, the diffusion spreads the heat and the phase shift distribution is no longer representative of the instantaneous power dissipation. Furthermore, additional heat is dissipated during the pulse. To compute the power dissipation, or rather its horizontal projection  $P_{2D}$ , one should integrate the heat diffusion equation including the diffusion term along the z direction [43]. The resulting equation (1.2) shows the relation between the 2D power dissipation  $P_{2D}$  and the phase shift  $\Delta\varphi$ , where  $\mu$  is the thermo-optical coefficient,  $C_V$  is the thermal capacitance of the material of the active layer, and  $\gamma$  its thermal conductivity.

$$P_{2D} = \mu^{-1} \times \left[ C_V \frac{\partial}{\partial t} - \gamma \left( \frac{\partial^2}{\partial x^2} + \frac{\partial^2}{\partial y^2} \right) \right] \Delta \varphi + J_z^{th}$$

(1.2)

This method only requires a local measurement of the device (at least 5 points to be able to compute second derivatives in both direction) to extract the local power dissipation. However, there are a few difficulties to overcome when applying it to experimental data. One remarks that the z-component of the thermal current density  $J_z^{th}$  cannot be solved. This is due to the projection that the TIM operates on the z-axis. The vertical heat flow cannot be sensed and the numerical extraction method is best when this component can be neglected. This is not always an issue, as microelectronic devices mostly have their active region in the first few micrometer of the top side. The equation also features a first derivative with time and two second derivatives with space. The numerical derivation is in general very sensitive to noise, and this can be a major issue in some cases. The phase shift distortion due to multiple reflection can also be problematic.

This method will also suffer some issues when dealing with a device using several materials that do not feature the same thermo-optical response, such as GaN on SiC. The heat flow from one to the other material will increase or decrease the phase shift without needing any heat input, and yet this effect will be interpreted as power dissipation.

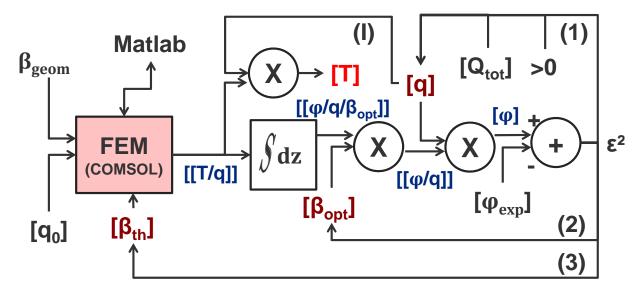

In part 3.3.2 a new method will be presented that can avoid the problem of multiple materials by making a linear thermo-optical model of the whole device. This approach will also enable to deal with the uncertainty of the optical response by using indirect probing.

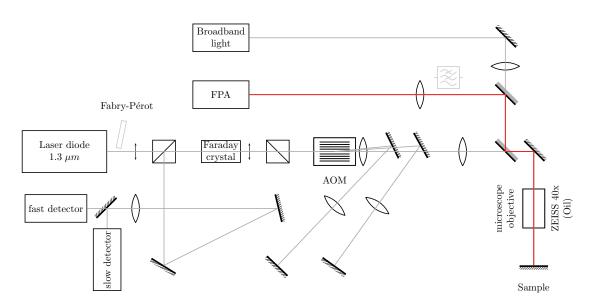

## 1.4.2.2 Backside Infrared Microscopy

The backside infrared microscopy uses partly the TIM setup, as shown in figure 1.11. The device is lit from the backside and an infrared camera looks at it. This allows to align the device with the laser beam for TIM, and can also be used to identify damage signatures on a damaged device, in particular when metal hides the active region from the top. The camera that is used for this purpose is either a Vidicon camera, or a InGaAs

Figure 1.11: Schematics of the TIM setup used for imaging devices from the backside.

Focal Plane Array (FPA). Several objectives have been used, depending on the device, including oil-immersion objectives.

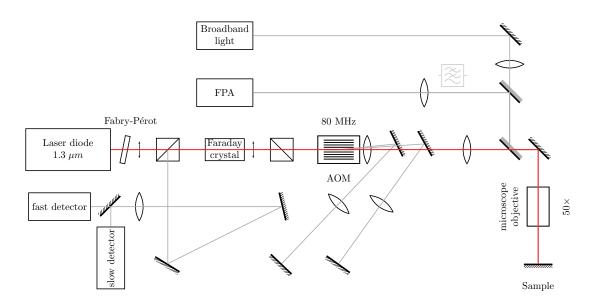

## 1.4.2.3 Emission microscopy (EMMI)

Figure 1.12: Schematics of the TIM setup used to perform EMMI

EMMI consists in stressing a device electrically and simultaneously looking at the device with a camera, as shown in figure 1.12. The stress that have been used are DC and repetitive pulses. In our case, as the TIM setup is used, the device is imaged from the

back side. The microscope objective is a 50x oil-immersion and the camera is a InGaAs Focal plane array. Filters can be used to identify the emitted wavelength.

# 1.4.2.4 Optical Beam Induced Current (OBIC)

Figure 1.13: Schematics of the TIM setup used to perform OBIC

The OBIC technique is the only technique that has been used in this thesis that uses the laser beam in an invasive way. As figure 1.13 shows, the device is biased at a fixed DC voltage or current and the probe beam scans the device. The leakage level for each position of the beam is recorded and a map of the leakage current under light is drawn. The high current position are parts of the device that are light sensitive, as forward pn junctions. The damage signature of a damaged device might respond to light in some case, depending on the nature of the damage and the wavelength of the laser beam, which makes it an interesting tool for failure analysis. The setup that is used for OBIC is the TIM setup where an additional Fabry-Pérot is set at the output of the laser to shape the laser spot.

# Chapter 2

# ESD self-protected HBT devices and discrete SCR protection

- 2.1 ESD self protected Silicon-Germanium base HBT as low noise amplifiers

- 2.1.1 Devices under study

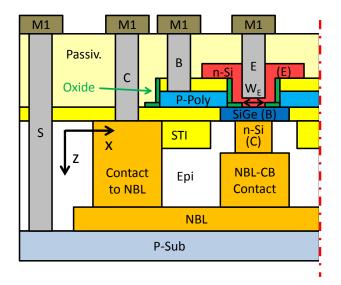

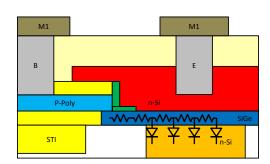

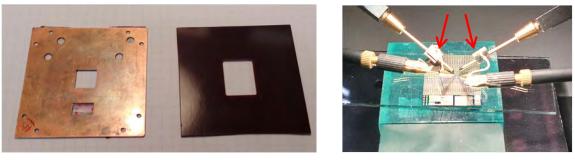

**Figure 2.1:** Schematic cross-section of a single finger device. The dashed line on the right shows the symmetry for the double finger device.

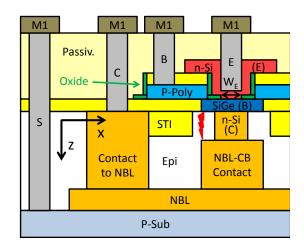

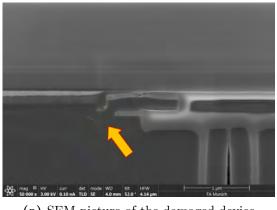

The devices under study are npn HBTs with a  $Si_{.85}Ge_{.15}$  base. The devices structure is shown in figure 2.1 for a single finger HBT, and should be mirrored with respect to the dashed line to obtain the structure of a double finger device. The collector is brought from the n-doped buried layer (NBL) through n-implantation. The NBL is connected to the collector metal by the n-implantation contact marked as "contact to NBL" and

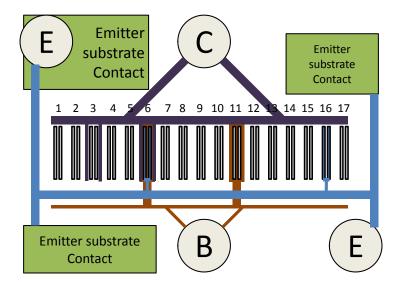

Figure 2.2: Schematic layout of the multifinger HBT device

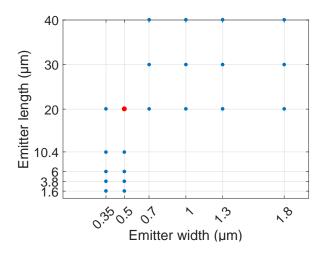

Figure 2.3: Available width and length combinations for the emitter window of test structures. The red dot at (W<sub>E</sub>=0.5  $\mu$ m, L<sub>E</sub>= 20  $\mu$ m) indicates the dimensions of one finger of the multifinger device

the collector of the device is connected to the NBL by the n-implant contact marked as "NBL-CB contact". The SiGe base is contacted with a p-poly-silicon layer that accesses the finger from all around the emitter window. The emitter n-Si is separated from the p-poly by a SiO<sub>2</sub> deposited layer marked with the arrow and the "oxide" label. The size of the base emitter junction, or emitter window, in the x (resp. y) dimension will be referred as emitter width (resp. length) and noted  $W_E$  (resp.  $L_E$ ). The two types of devices that were studied are:

• Multifinger devices, that consist of 16 blocks of double finger HBTs, where the width of each finger is 0.50  $\mu$ m and the 20  $\mu$ m length is divided into two 10  $\mu$ m SiGe islands. In these devices, the substrate is connected to the emitter with a via and a

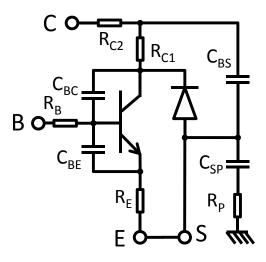

Figure 2.4: Device with its main parasitic elements. The ground symbol shows the shield of the probe needle, wherever the ground contact is placed.

metal. This connection scheme is used because the amplifier is operated in common emitter mode, and the substrate is chosen to be the ground of the circuit. Figure 2.2 shows the layout of the multifinger device that was analyzed in this study. The collector and base pads and the two emitter-substrate pads are shown. All fingers are shown as gray rectangles in the center, corresponding to their emitter contour. The collector, base and emitter-substrate metals are shown in dark purple, brown and blue, respectively. Finger 9 is not connected. On finger 3, the collector metal M2 is shown, which is connected to the collector M1 that is shown in figure 2.1. In finger 11, the base connections are shown in brown: the M1 is used to go underneath the M2 of the emitter metal in blue. Inside the transistor block the base contact is made with poly-silicon, as shown in figure 2.1. On finger 16 are shown the emitter contacts with the M2 metal. The M1 shown in figure 2.1 is connected by vias to the emitter M2. In finger 6, all connections are shown at once.

The layout in figure 2.2 also shows the location of the main substrate contact to the emitter.

Test structures (TS), which consists of a double-finger and single-finger HBTs with independent substrate contacts. They have emitter width values W<sub>E</sub>=0.35, 0.5, 0.7, 1, 1.3 and 1.8 μm and emitter length L<sub>E</sub>=1.6, 3.8, 6, 10.4, 20, 30, and 40 μm. All available combinations are shown in figure 2.3. Notably, all the emitter width values are available for L<sub>E</sub>=20 μm, as double finger structures with W=0.50 μm, and L=20 μm are the building blocks from which the multifinger devices are made.

The parasitic elements of the device are shown in figure 2.4. The diode between the p-substrate and the n-collector is due to the pn junction.  $C_{BC}$  and  $C_{BE}$  and  $C_{CS}$  are the three junction capacitance.  $C_{BE}$  is large as it also includes the thin oxide capacitance.

$R_B$  and  $R_E$  are respectively the base and emitter series resistance.  $R_{C1}$  is the resistance to the substrate/NBL junction and  $R_{C2}$  is the contact from the NBL to the collector pad. To explain the substrate coupling,  $C_{SP}$  and  $R_P$  are introduced. The reduced form of the HBT schematics (whether test structure or multifinger) will keep the substrate diode as a convenient notation to explicit the substrate connection.

# 2.1.2 ESD robustness of the HBT in different combinations

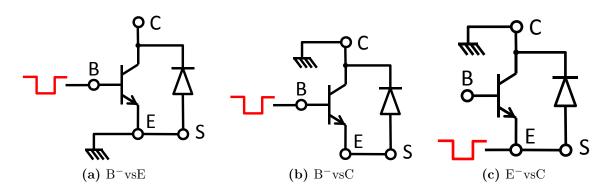

Figure 2.5: Stressing conditions for HBT multifinger device

The robustness of the multifinger device was studied by making the TLP-IV of all possible pairs of pads. In the following we show the reverse base-emitter ( $B^-vsE$ ), the emitter-collector ( $E^-vsC$ ) and the reverse base-collector stressing ( $B^-vsC$ ) that are represented in figure 2.5.

## 2.1.2.1 Base-emitter characterization

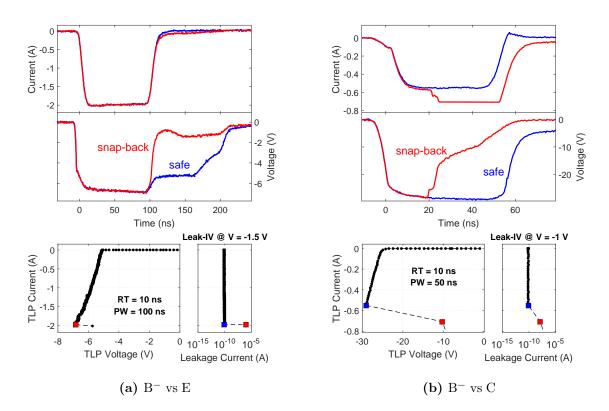

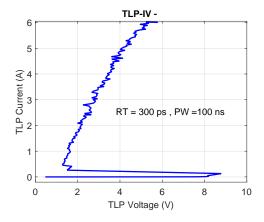

The reverse base-emitter TLP-IV for a rise time of 10 ns and a pulse width of 100 ns is shown in figure 2.6a (bottom). As long as the voltage is below the breakdown voltage of 5 V, the current is negligible and the voltage is equal to the charging voltage of the pulser (see part 1.4.1.2). Beyond the breakdown voltage, the device shows a breakdown, which is a rise of the reverse current. The ON-resistance, i.e the differential resistance of the device in breakdown is roughly 1  $\Omega$ . This corresponds to the intrinsic base and emitter resistance, plus the access resistance to the base emitter junction from the pads, most of which should be due to the base resistance, as it includes the poly-silicon, and narrower metal lines. The contact resistance of the probe is not affecting the voltage measurement, as the measurement is done in 4 point mode (see part 1.4.1.2). In the blue waveform, where the device is safe, one can see that the voltage is rising during the pulse. This is typical of avalanche breakdown, which is caused by the impact ionization of the lattice that leads to carrier multiplication. The temperature increase due to self heating during the pulse shortens the mean free path of the electrons, thus diminishing

Figure 2.6: TLP IV of the multifinger device under B<sup>-</sup>vsE and B<sup>-</sup>vsC conditions (described in figure 2.5) and post stress leakage. Waveforms corresponding to the cursors in the TLP-IV and leakage are shown in corresponding colors. The TLP-IV values correspond to a 70-90 ns averaging window.

their impact energy, and therefore the multiplication that drives the current. As the value of the current/voltage follow the load line, where the load resistance is the characteristic impedance of the transmission line (50  $\Omega$ ), the decrease in the current is accompanied by an increase of the voltage. The "safe" waveform also shows that the device voltage stays at the breakdown voltage after the end of the pulse during about 60 ns and then decreases. This is probably due to a reflected pulse that that is attenuated in the pulser so that its effective charging voltage is hardly above 5 V.

When the charging voltage is set to 100 V, the device is damaged, which can first be seen in the increase of the leakage current in figure 2.6a. There is no visible snapback during the pulse (see red waveform in figure 2.6a), but the low value of the voltage for the reflected pulse (at 150 ns) and the slightly higher current show that the device now features low impedance. The voltage drops as fast as the incident pulse, and the current is slightly higher than for the safe pulse, which corresponds to the increase of the conductance of the discharge path. After the pulse it can be seen that the DC leakage value at  $V_{BE} = -1.5V$  has rose to 1  $\mu$ A, which is also the sign of a damage of the transistor. The snap-back at the end of the pulse for a small charging voltage increase is evidence for a thermal damage.

The  $I_{T2}$  value of the base-emitter stressing under 100 ns and 10 ns is 2 A. This shows that the device should be robust to 3 kV HBM testing.

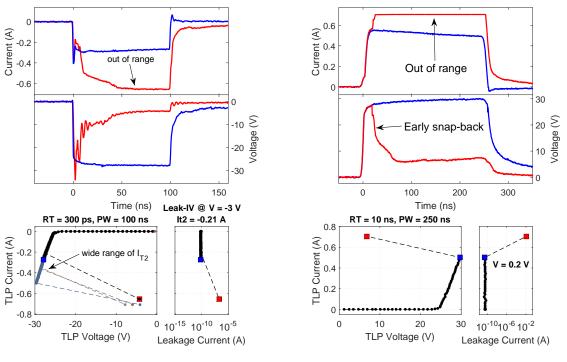

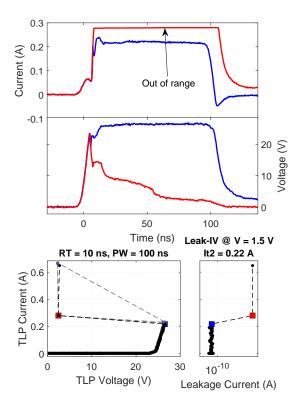

## 2.1.2.2 Base-collector characterization

The stressing of the base-collector junction is shown in figure 2.6b for a pulse width of 50 ns and rise time of 10 ns. The shape of the IV (bottom) is similar to the base emitter IV for low charging voltage up to the breakdown voltage. The breakdown voltage is -24 V which is much higher than for the base emitter due to the much lower doping of the collector. The ON-resistance is 7  $\Omega$ , which is due to the high resistance of the electrical path corresponding to the contact to the buried layer and to the collector pad (see figure 2.1). Figure 2.6b shows a safe waveform in blue and a destructive waveform featuring a snap-back in red. Despite a larger resistance, the safe waveform does not show a clamping of the voltage at the end of the pulse as in the BE case, which probably means that the parasitic capacitance is much smaller. In these measurement conditions, the  $I_{T2}$  of this device is 550 mA, which is low. Furthermore, looking at the red snap-back waveform in figure 2.6b, one can see that the device enters in snap-back in the middle of the pulse. The dissipated energy up to the snap-back is therefore less than the dissipated energy during the whole safe pulse. This rules out the hypothesis of a thermal damage. The snap-back is likely due to a purely electrical phenomenon, such as a parasitic BJT triggering or damage due to concentration of the current into one finger of the transistor.

## 2.1.2.3 Emitter-collector characterization

To complete the characterization of the transistor as concerns HBM type ESD between pairs of pins, a device was stressed in negative emitter versus collector. In the TLP-IV presented in figure 2.7, one sees a breakdown voltage of 7 V. This breakdown is smaller than the base-collector breakdown. This means that a transistor action takes place. The breakdown could be due to open base breakdown where the emitter triggers the BC breakdown by providing carriers [45, 46]. Alternatively the breakdown might be due to a punch-through phenomenon, in particular the base depletion region at the BC junction extends across the whole base to the emitter. This hypothesis is supported by the observation of an Early effect in DC. With further increase of the charging voltage, a non destructive snap-back is visible at V=11 V. It can be that the increased current makes a stronger injection from the emitter that provide the electrons for initiating the avalanche in the base collector junction. This is a feature of open-base breakdown.

With increasing current, the device builds a voltage until the second snap-back at V=11 V and I=1.63 A. Beyond the second snap-back the device degrades. As it can be seen in the green waveforms, the snap-back happens at the end of the pulse and has no visible effect on the leakage measurement. At slightly higher charging voltage, the device

Figure 2.7: TLP IV of device A13 under E-vsC (negative stressing of the emitter versus grounded collector)

has an earlier snap-back and gets damaged. This is probably due to a thermal instability similarly as in [47] that concentrates the whole power into one finger, thus starting the thermal runaway in this finger. Given enough time in this inhomogenous configuration, this finger gets damaged. In any case the  $I_{T2}$  value for this device is more than 1.5 A.

#### 2.1.2.4 Summary of the multifinger device ESD robustness and choice of study

| Stress conditions | $I_{T2}$ | type of breakdown          | type of failure      |

|-------------------|----------|----------------------------|----------------------|

| $B^- vs E$        | 2 A      | avalanche                  | thermal runaway      |

| $B^- vs C$        | 600  mA  | avalanche                  | electrical - unknown |

| $E^- vs C$        | 1.6 A    | punch-through/open-base BD | thermal instability  |

| Table 2.1: | Summary | table of the | different | junctions |

|------------|---------|--------------|-----------|-----------|

|------------|---------|--------------|-----------|-----------|

Table 2.1 summarizes the TLP measurements of the HBT for all three configurations and the conclusions that were drawn from the analysis of the TLP-IV, the waveforms and the leakage measurements. The base collector stressing shows that this configuration is the least robust one for this transistor, and might be considered too low for some applications. This problem needs to be solved and will be investigated in details in the following.

## 2.1.3 Intrinsic and extrinsic Base-Collector failure modes

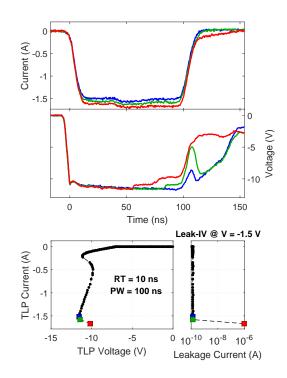

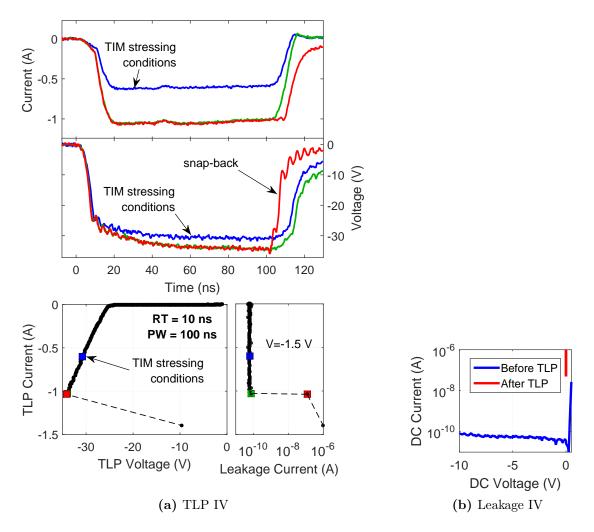

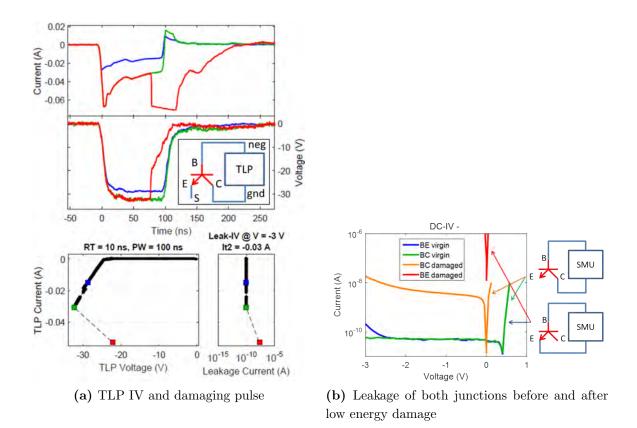

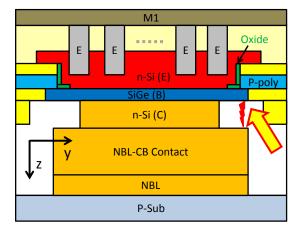

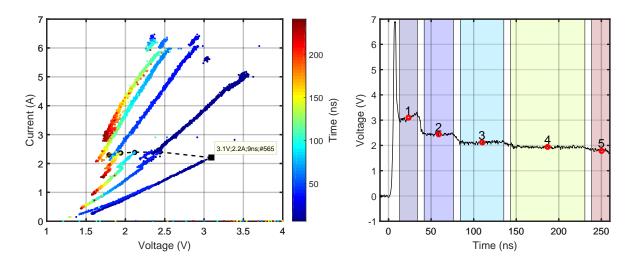

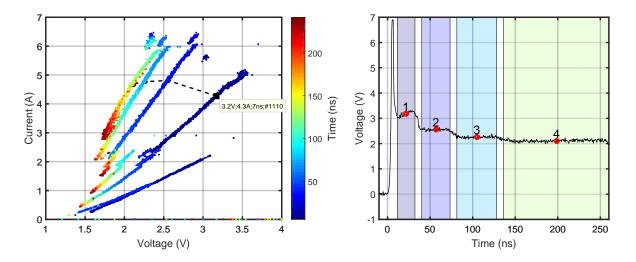

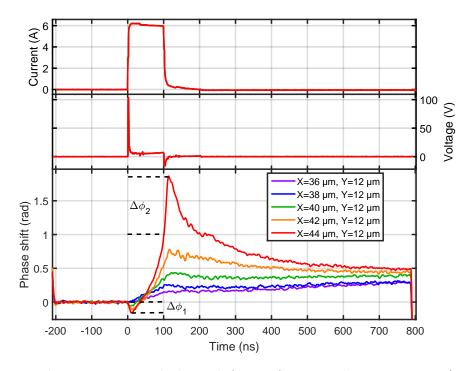

The first measurements of the base-collector junction in reverse by means of the TLP depending on pulse width, rise time, and substrate capacitive coupling to the probe station (or TIM setup), reveal a clear separation of two failure modes in the multifinger devices.

- One of these modes has a high value for  $I_{T2}$  ( $\approx 1$  A). This mode will be called "intrinsic". It takes place for long rise times ( $\geq 10$  ns).

- The other presents low  $I_{T2}$  failures that can be problematic for the use of the device, as it has been shown in the previous part. This mode will be called "extrinsic". It takes place for low rise times ( $\leq 10$  ns) or substrate coupling with the probe shield or a metallic sample holder. The failure example given in figure 2.6b is due to substrate coupling.

| Stress conditions         | RT < 10 ns                 | $RT \ge 10 ns$ |

|---------------------------|----------------------------|----------------|

| Weak substrate coupling   | extrinsic                  | intrinsic      |

| Strong substrate coupling | $\operatorname{extrinsic}$ | extrinsic      |

Table 2.2: BC failure observed modes

The differences between the intrinsic and extrinsic failure modes and the stressing conditions that are required to achieve each of them are summarized in table 2.2. The experimental conditions for each mode will be detailed in their dedicated part. For simplicity, the conditions themselves will sometimes be called "intrinsic" or "extrinsic", depending on the failure mode that is observed in this conditions, given high enough charging voltage of the TLP for the failure to occur.

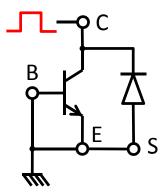

## 2.1.3.1 Intrinsic mode

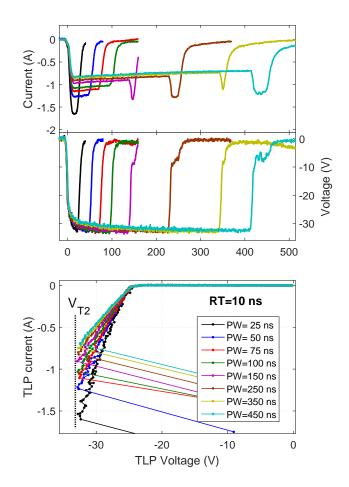

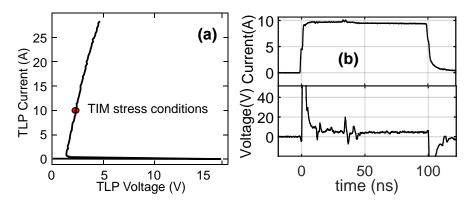

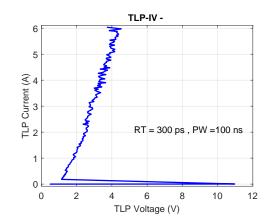

Figure 2.8a shows a negative base versus collector ( $B^-vsC$ ) TLP-IV of the multifinger device for 10 ns rise time and 100 ns pulse width measured on an insulating holder. The I<sub>T2</sub> value is 1 A. As the red waveforms in figure 2.8a show, the snap-back occurs at the end of the pulse, which is typically the sign of a thermal failure. The leakage IV characteristics of the base-collector has been measured before and after the TLP stress, and is shown in figure 2.8b. Figure 2.8b shows that where the virgin base collector junction shows little leakage current in reverse, the measurement after the stress shows a very low ohmic characteristics.

**Pulse width scaling in intrinsic conditions** The goal of the pulse width scaling is to determine whether the snap-back is thermal by using a Wunsch-Bell methodology [48].

Figure 2.8: TLP IV and leakage IV of device A13 under reverse base collector conditions for RT=10 ns, PW=100 ns. The averaging window is 70-90 ns.

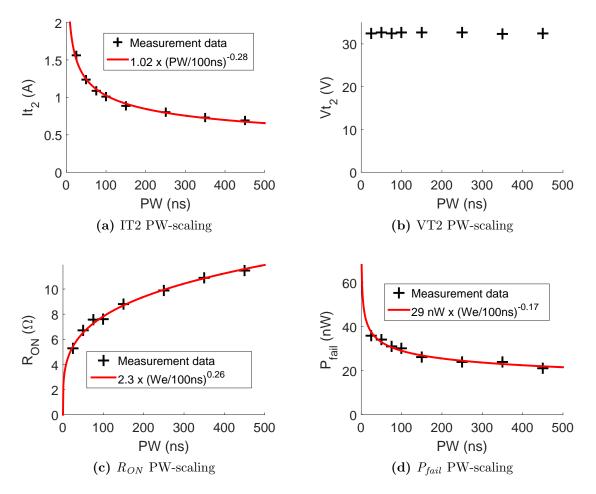

Figure 2.9 shows in the same picture the TLP-IV and the destructive waveforms for the multifinger device in floating substrate configuration under 10 ns rise time and various pulse widths and figure 2.10 presents the extracted parameters of these TLP-IVs. In the waveforms, one can see that the devices fail at the end of the pulse for all pulse widths. The relevant parameter to describe this failure is  $V_{T2}$ , as its value of 33 V seems independent of the pulse width, as it is shown in the TLP-IVs and in the summary figure 2.10b. The variation in  $I_{T2}$  with pulse width (figure 2.10a) is due to the breakdown current power dissipation that heats the junction, decreasing the efficiency of the avalanche breakdown, and thus leading to an increase of the on-resistance, which is shown in figure 2.10c. The  $I_{T2}$  value is therefore the consequence of the fixed  $V_{T2}$  value and the  $R_{ON}$  increase with time. This is seen in the power fit of the  $R_{ON}$  and the  $I_{T2}$  values versus pulse width that show opposite values (±0.26). The breakdown voltage does not seem to be affected

**Figure 2.9:** TLP IV and destructive waveforms for multifinger devices under  $B^+vsC$  conditions for 10 ns rise time and different pulse widths. The averaging window is 70-90% of the pulse width for all TLP-IVs.

significantly by the self heating.

Figure 2.10d shows the average dissipated power versus the time-to-failure, i.e the pulse width in this case. As the pulse width is increased, the decrease of the power is too weak to support the hypothesis of a thermal process in the time domain that is relevant to the HBM type of ESD. This means that identifying and solving the problem that causes the intrinsic failure could lead to a much robust device.

To summarize, the intrinsic mode is a purely electrically-caused snap-back which leads to a failure of the device as the voltage reaches a critical value. As the voltage increases during the pulse for thermal reasons, the snap-back always happens at the very end of the pulse (as showed for example in figure 2.8a), but it is not thermally driven.

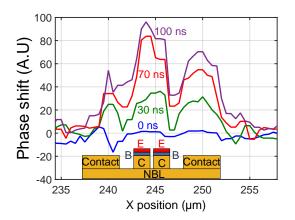

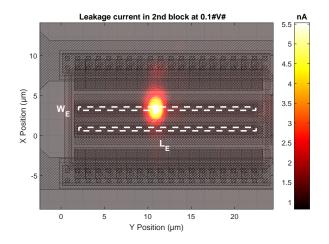

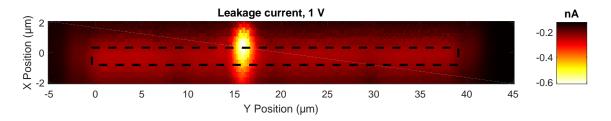

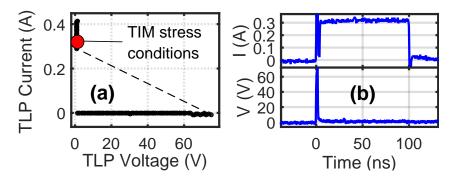

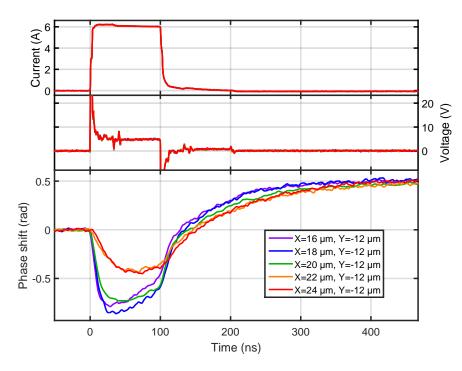

TIM characterization of multifinger devices in intrinsic conditions The multifinger devices were submitted to the TIM experiments under the conditions that correspond to the intrinsic mode (10 ns rise time performed on insulating holder). The chosen current was 600 mA which is at a safe margin from the intrinsic  $I_{T2} \approx 1 A$ . The point on the

Figure 2.10: PW-scaling of TLP extracted parameters on multifinger devices

TLPIV and the waveforms are presented in blue in figure 2.8a.

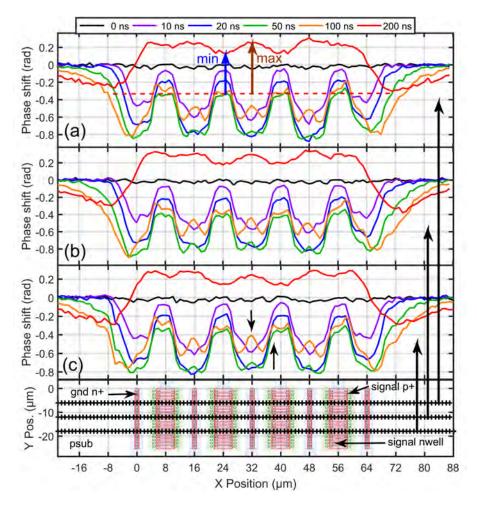

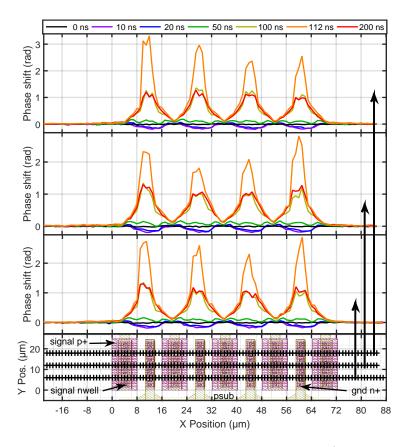

The TIM data that is presented in figure 2.11a is the result of a scan that has been performed across the width of a double finger block of the multifinger device. At all time instants, there are 3 peaks in along the width direction of the device, at positions 240, 245 and 250  $\mu$ m. The two external peaks are at the position of the connection to the NBL, whereas the central peak is at the position of both base collector junctions. The positive phase shift indicates that the change of the index of refraction is due to heat dissipation.

The phase shift is proportional to the integrated heat over the beam path (see part 1.4.2.1 for more details). The drawing at the bottom of figure 2.11a schematically shows the parts of the device where the current flows (more details in figure 2.1). As the contacts (n-doped silicon) are vertical, the beam probes a heated region for a longer part of its path, thus making one peak for each contact. Indeed, two peaks are counted for the external contacts (marked as "contacts to NBL" in figure 2.1), and two peaks that are merged into a larger one for the contacts to the active region (marked as C in the drawing at the bottom of figure 2.11a and as "NBL-CB contacts" in figure 2.1). The merging of the peaks corres-

Phase shift (A.U) 200 0 300 0 100 200 400 X Position (µm)

35 ns

70 ns

100 ns

+ 0 n

600

400

(a) Detailed scan on one of the 16 double finger blocks of the multifinger device

(b) Scan featuring three points for each block

Figure 2.11: TIM scans in device A13 for PW=100 ns and RT=10 ns (intrinsic conditions), I=600 mA

ponding to the active regions is due to the small separation between the two fingers of about 3  $\mu$ m, which is the thermal diffusion length value at 100 ns in silicon [49]. Between the peaks (at positions 243 and 247  $\mu$ m), the phase shift signal is weaker because the part of the optical path that is dissipating heat is only the NBL itself.

From this analysis it can be deduced that the heat dissipation is roughly homogeneous in all the collector and sub-collector regions, i.e the NBL and the n+ contacts, and the collector n-silicon itself.

Figure 2.11b shows the TIM phase shift in few points in every double finger block of the multifinger device, namely the three peaks positions from figure 2.11a. Except for the central block, which is not contacted, the height of the peaks of the blocks are roughly similar, so it is deduced that all blocks share the power dissipation equally. This is expected, as the heat dissipation has a negative feedback on the current inhomogeneity under avalanche breakdown conditions [50].

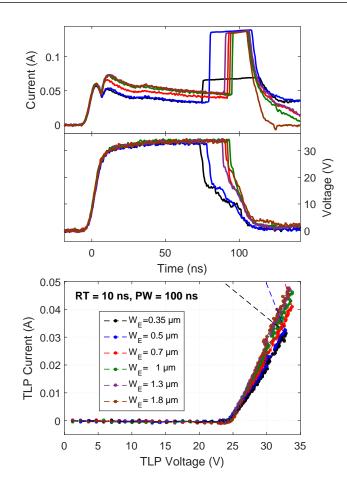

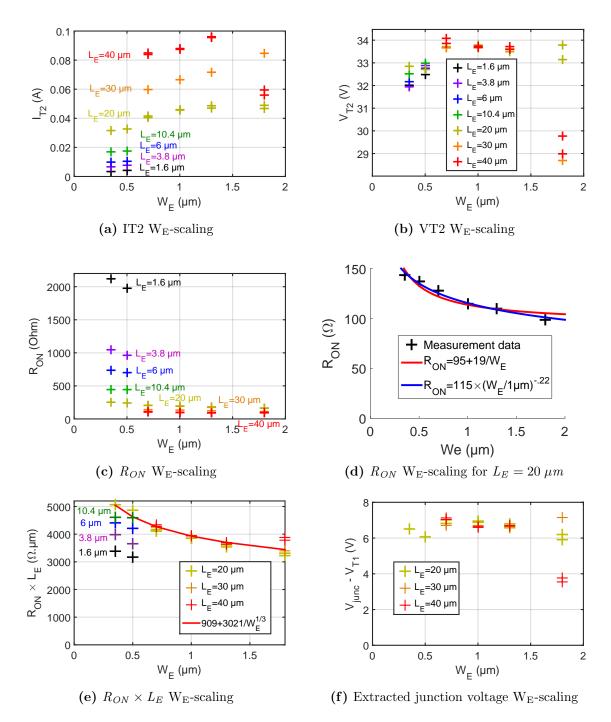

**Emitter width scaling in intrinsic conditions** To further collect evidence on the intrinsic failure mode, it was chosen to perform TLP stressing of single-fingered test structures with different emitter widths. The device substrate was externally connected to the emitter with a flexible pitch set to mimic the connection scheme of the multifinger devices. The results are presented in figure 2.12. It can be seen on the TLP-IV that the breakdown voltage has a very low dependence on the emitter width. The waveforms show that the snap-back happens at the end of the pulse, although for the narrower width devices the snap-back occurs around 80 ns. This is compatible with the hypothesis of the critical voltage, considering that the voltage at the end of the waveform is quite flat with time. The charging voltage step that was used for the pulser is therefore larger than the increase

## 2.1. ESD SELF PROTECTED SILICON-GERMANIUM BASE HBT AS LOW NOISE AMPLIFIERS

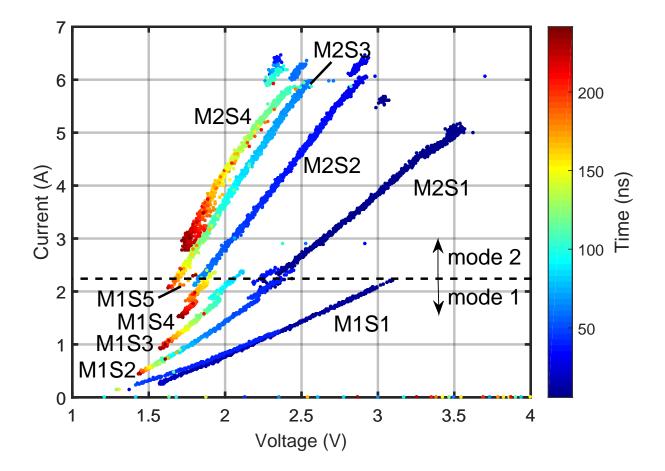

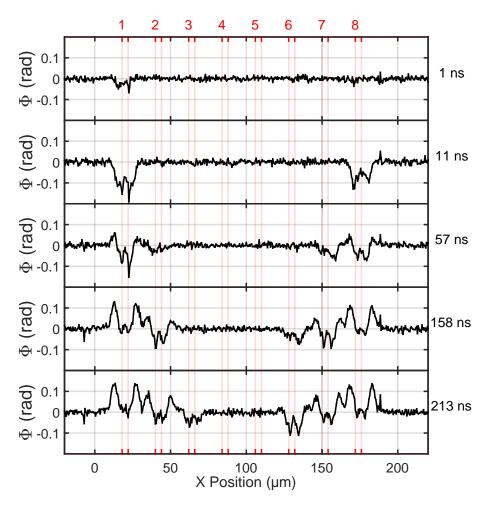

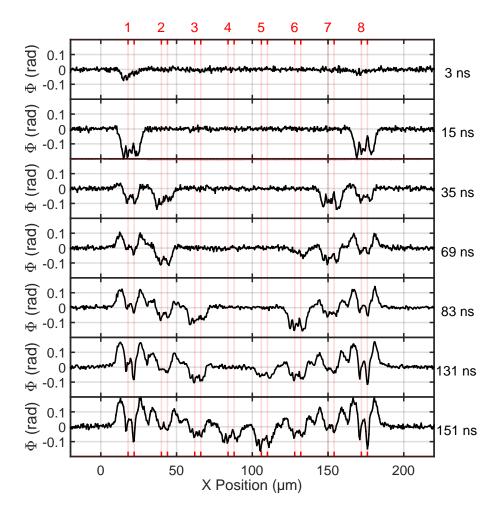

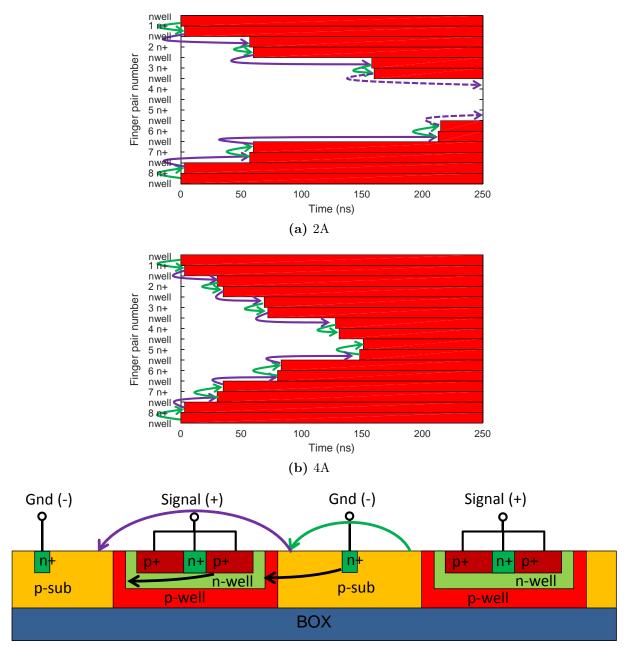

Figure 2.12: TLP IV and destructive waveforms for test structure devices with 20-µm-long emitter and various emitter widths under C<sup>+</sup>vsB conditions for 10 ns rise time and 100 ns pulse width. The averaging window is 70-90 ns.