TU UB

Die approbierte Originalversion dieser Diplom-/ Masterarbeit ist in der Hauptbibliothek der Technischen Universität Wien aufgestellt und zugänglich.

> TU UB WIEN Universitätsb

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology. http://www.ub.tuwien.ac.at/eng

## DIPLOMARBEIT

# Investigation of charge up effects on silicon test structures

Ausgeführt am Atominstitut der Technischen Universität Wien und am Institut für Hochenergiephysik der österreichischen Akademie der Wissenschaften

unter der Anleitung von Univ.Doz. Dipl.-Ing. Dr. Manfred Krammer und Dipl.-Ing. Dr. Thomas Bergauer

> durch Paul Jagenteufel Haydnstraße 5/5 2103 Langenzersdorf

Wien, im Oktober 2015

## Abstract

The CMS-experiment is one of the large LHC experiments at CERN. As it is continuously running, the detector degrades with time because of the radiation damage of the colliding particles. So the detector has to be renewed around 2023 in the so-called phase II upgrade. For this upgrade, new sensors have to be developed with new technology or materials that exhibit higher radiation hardness, because after the upgrade the luminosity of the LHC shall be increased. The scope of this diploma thesis is the comparison of the process quality of the sensors of different vendors based on the characterisation of test structures. Special emphasis was laid on charge up effects that were examined and also tried to provoke on MOS structures in particular.

## Contents

| 1 | СМ                                       | S-Experiment                                              | 4  |  |  |

|---|------------------------------------------|-----------------------------------------------------------|----|--|--|

|   | 1.1                                      | Phase II upgrade                                          | 7  |  |  |

| 2 | Semiconductor detectors                  |                                                           |    |  |  |

|   | 2.1                                      | Semiconductor theory                                      | 7  |  |  |

|   | 2.2                                      | Silicon sensors as particle detectors                     | 10 |  |  |

|   |                                          | 2.2.1 Silicon strip sensors                               | 10 |  |  |

|   |                                          | 2.2.2 Signal generation                                   | 11 |  |  |

|   |                                          | 2.2.3 Radiation damage                                    | 13 |  |  |

|   |                                          | 2.2.4 Manufacturers                                       | 13 |  |  |

| 3 | Test                                     | t structures                                              | 13 |  |  |

|   | 3.1                                      | Diode                                                     | 14 |  |  |

|   | 3.2                                      | MOS                                                       | 16 |  |  |

|   | 3.3                                      | Gate Controlled Diode                                     | 19 |  |  |

|   | 3.4                                      | Interstrip capacitance $C_{\rm int}$                      | 23 |  |  |

|   | 3.5                                      | Interstrip resistance $R_{\text{int}}$                    |    |  |  |

|   | 3.6                                      | Sheet resistances                                         | 23 |  |  |

| 4 | Standard measurements on test structures |                                                           |    |  |  |

|   | 4.1                                      | IV-characteristic of diodes                               | 26 |  |  |

|   | 4.2                                      | CV-characteristic of diodes                               | 26 |  |  |

|   | 4.3                                      | CV-characteristic of MOS                                  | 33 |  |  |

|   | 4.4                                      | IV-characteristics of GCDs                                | 35 |  |  |

|   | 4.5                                      | Interstrip capacitance $C_{\text{int}}$                   | 40 |  |  |

|   | 4.6                                      | Interstrip resistance $R_{\text{int}}$                    | 40 |  |  |

|   | 4.7                                      | Sheet resistances                                         | 43 |  |  |

| 5 | Det                                      | ailed investigation of MOS structures                     | 48 |  |  |

|   | 5.1                                      | MOS with nitride-layer and several different passivations | 48 |  |  |

|   | 5.2                                      | N-type MOS with n-spray layer                             | 53 |  |  |

|   | 5.3                                      | MOS long term charge up measurements                      |    |  |  |

| 6 | Con                                      | clusions for new designs and further measurements         | 71 |  |  |

## 1 CMS-Experiment

The CMS-experiment is one of the four big experiments at the Large Hardron Collider (LHC) at CERN<sup>1</sup>. The LHC is a circular particle accelerator with a circumference of 26.7 km, located about 100 m below the earth's surface. It was built to accelerate two proton beams in opposite direction, each with an energy of 7 TeV. When brought to collision, this results in a center-of-mass energy of 14 TeV, which is released and thus available for the creation of (new) particles [2].

The four big experiments<sup>2</sup> at the LHC are ALICE, LHCb, ATLAS and CMS. ALICE is designed to investigate heavy ion collisions (i.e. Pb-nuclei) to search for quark-gluon plasma, a special state of matter that is believed to have dominated the universe in the first fractions of seconds after the Big Bang. It only exists at very high densities, because else quarks and gluons only occur in bound states due to the so-called quark confinement. The LHCb experiment is intended to study the CP-violation<sup>3</sup> observing the decay modes of B-mesons (i.e. the  $B^0 - \overline{B^0}$ -system consisting of  $d\overline{b}$  and  $\overline{d}b$  quarks, respectively) and to precisely measure the elements of the quark mixing matrix, which describes the mixing angles between the down-type (d, s, b) and up-type (u, c, t) quarks and is also referred to as CKM-matrix<sup>4</sup> [3].

The two experiments ATLAS and CMS have the same goals, but are designed differently and completely independent of each other, so that they can confirm the results of each other and, thus, rule out systematic errors [4]. They are built as general purpose detectors to investigate a wide field of physics, e.g. supersymmetry<sup>5</sup> [2]. A major task of these two experiments was fulfilled on 4 July 2012, when ATLAS and CMS announced that they had each observed a new particle in the mass region around 126 GeV that is consistent with the Higgs boson predicted by the Standard Model<sup>6</sup> [1].

The acronym CMS stands for *Compact Muon Solenoid*, as it lays emphasis on the detection of muons created by the proton-proton-interactions, since they reveal much information about the decay modes. The term *compact* has to be understood in comparison to other detectors of similar weight<sup>7</sup>, as it still has a length of 21 m and a diameter of 15 m. The solenoid is superconducting, induces a magnetic field of 4 Tesla and, thus, makes possible the compact design. The functional principle of CMS is the

<sup>&</sup>lt;sup>1</sup>CERN is the European Organisation for Nuclear Research, located near Geneva, Switzerland. The acronym stands for the former French name *Conseil Européen pour la Recherche Nucléaire* [1].

<sup>&</sup>lt;sup>2</sup>There are also two smaller experiments called TOTEM and LHCf that shall measure the cross-section of the proton and the number and energies of  $\pi^0$ -mesons produced in the collisions [3].

<sup>&</sup>lt;sup>3</sup>CP-violation is the violation of the so-called CP-symmetry, a theory, according to which the laws of physics should be the same when a particle is interchanged with its antiparticle (charge conjugation) and its spatial coordinates are inverted (parity).

$<sup>^4\</sup>mathrm{The}$  three letters are standing for the discoverers Cabibbo, Kobayashi and Maskawa.

<sup>&</sup>lt;sup>5</sup>Supersymmetry (SUSY) is a theory that postulates a supersymmetric bosonic partner to each fermion and vice versa. Though, these supersymmetric particles are so heavy that they haven't been found yet.

<sup>&</sup>lt;sup>6</sup>The Higgs boson was proposed by Robert Brout, François Englert and Peter Higgs in 1964, the latter two were awarded with the Nobel prize in physics in 2013 [1].

<sup>&</sup>lt;sup>7</sup>CMS weights around 12,000 t, while ATLAS, for example, only weights about half of it, but has almost eight times the volume of CMS [2, 3].

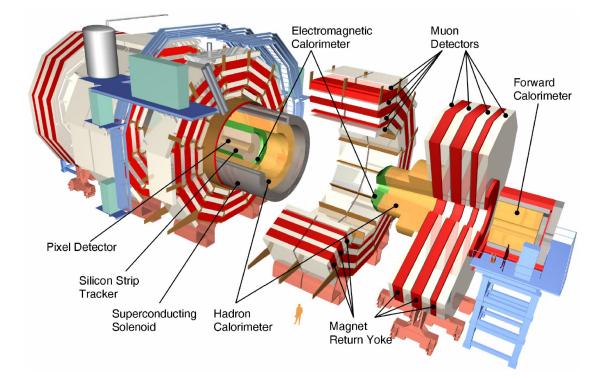

Figure 1: A schematic view of the CMS detector, for comparison the size of a person is shown in front. [2]

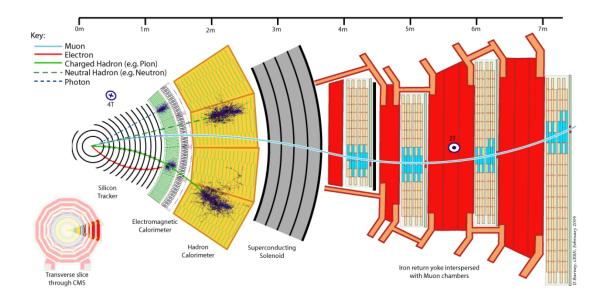

Figure 2: A slice of the CMS detector with the trajectories of different traversing particles and the sections where they are detected. [4]

following: In the magnetic field of the solenoid, charged particles follow spiraling paths and the curvature of this paths reveals the momenta of the particles. The energy of the particles is measured in the calorimeters. The electrons and photons are absorbed by the so-called *electromagnetic calorimeter* (ECAL), as they interact electromagnetically, while hadrons, which are interacting by the strong force, are measured in the *hadronic calorimeter* (HCAL). The muons are detected in the *muon chambers* and only weakly interacting particles, as the neutrinos, are escaping all detectors. Nevertheless, they can be determined by adding up the momenta of all the detected particles and evaluate the missing momentum [5].

The CMS detector is composed of different layers that are arranged onion-like around the interaction point. The innermost part is the so-called *tracker* that utilises silicon pixel (two-dimensional) and silicon strip (one-dimensional) sensors to reconstruct the trajectories of the particles and their interaction point, and thus locate secondary vertices<sup>8</sup>. The next layers are filled with the calorimeters described above, first the ECAL, then the HCAL. Thereafter the solenoid is situated, and outside of it, the muon chambers are located, since muons are likely to traverse the whole detector. In figure 1 a schematic view of the whole CMS detector is displayed. Figure 2 shows a slice of the detector with different traversing particles and in which part of it they are detected [3].

In the LHC, every 25 ns two bunches of protons collide. This corresponds to an interaction frequency of f = 40 MHz and results in a luminosity of  $10^{34} \text{ cm}^{-2} \text{s}^{-1}$ . The luminosity  $\mathcal{L}$  describes the probability of an interaction of two colliding particle bunches

<sup>&</sup>lt;sup>8</sup>Secondary vertices occur when very short-lived particles decay into other (lighter) particles before they reach the detector.

and can be calculated by

$$\mathcal{L} = f \frac{n^2}{4\pi\sigma_x \sigma_y} \tag{1}$$

where n is the number of particles of each bunch and  $\sigma_x$  and  $\sigma_y$  characterise the beam spreads in horizontal and vertical directions. This value is, beside the center-of-mass energy, the most important parameter characterising a collider and shall be increased by a factor of 5 after the so-called *phase II upgrade* in 2025 [2].

### 1.1 Phase II upgrade

The increased luminosity of the so-called *high luminosity LHC* (HL-LHC) corresponds to more interactions and leads to a higher track density. This can be measured with the so-called *pile-up*, the number of events produced at one beam crossing. The pile-up shall be increased to 140 interactions per beam crossing after the phase II upgrade.

To deal with this increase, the tracker will grow in granularity. This will be realised by more implemented silicon sensors, shorter strips in the outer tracker and more layers of pixel sensors in the inner tracker.

Another advantage is the reduction of material in the tracker volume, what improves the particle detection.

However, a higher luminosity also means higher radiation, which primary affects the tracker, as this is the innermost detector. Therefore, a more radiation-hard material is needed and so the new tracker shall be built of silicon sensors in p-type bulk and n-type implant [6].

The functional principle of silicon sensors is explained in the following section.

## 2 Semiconductor detectors

Initially, it was planned to use Micro-Strip Gas Chambers for the CMS tracker, however, silicon detectors are more practical due to their advantages like a higher radiation tolerance, a low mean ionisation energy and a fast signal response [7].

## 2.1 Semiconductor theory

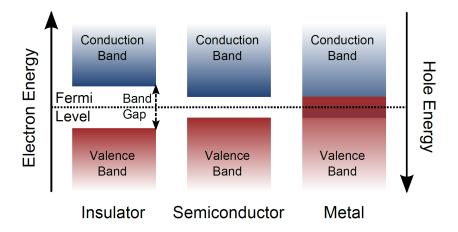

In a crystal lattice, there are so many atoms that the energy states form almost continuous energy bands. Nevertheless, there are empty energy intervals that can not be occupied by electrons and, thus, are called *energy band gaps*  $E_{\rm g}$ . The uppermost entirely filled energy band is called *valence band* and the lowermost empty or partly filled band is called *conduction band*. Solids can be classified by these energy band gaps into conductors, where conduction and valence band are overlapping and electrons can be exited to higher energy levels with only small amounts of energy, semiconductors, where the band gap is large ( $E_{\rm g} \gtrsim 5 \, {\rm eV}$ ), so that it is unlikely that electrons are excited from the valence band to the conduction band (see fig. 3) [4, 2].

Figure 3: Energy band structure of solids classified by the energy band gap  $E_{\rm g}$  into insulators, semiconductors and conductors (metals) [4].

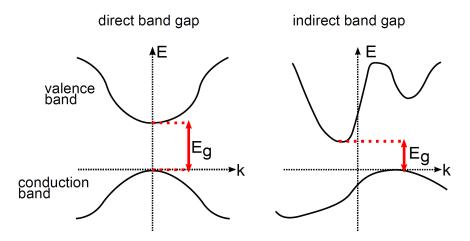

There are semiconductors like silicon that have an *indirect band gap*, which means that the minimum energy in the conduction band is shifted to the maximum in the valence band by a  $\vec{k}$ -vector in momentum space (see fig. 4). Thus, to conserve the momentum, an electron needs some source of momentum to fall from the conduction band into the valence band. However, in a semiconductor with *direct band gap* like germanium or gallium arsenide, electrons at the conduction band edge can combine directly with holes at the valence band edge. As the energy from this recombination process will be emitted as light, this is called spontaneous emission [2].

Figure 4: Energy diagram in momentum space for a semiconductor with direct (left) and indirect (right) band gap [4].

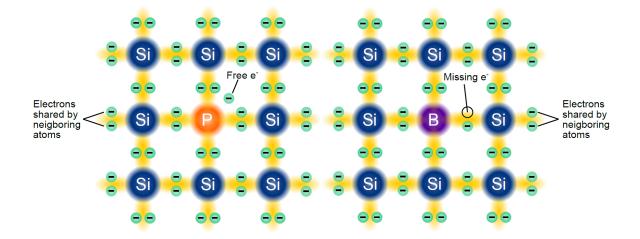

Figure 5: Silicon lattice doped with phosphorus (P) forming an n-type material (left) and with boron (B) forming a p-type material (right side) [4].

By introducing a small amount<sup>9</sup> of impurity atoms into an intrinsic semiconductor, one can modify its energy band configuration and affect its electrical properties. This process is called doping and there are two types, affecting the electrical properties differently, depending on the doping material and its position in the periodic table of the elements. Donors are elements from the fifth main group of the periodic table that add some energy states below, but very close to the conduction band, when incorporated into the crystal lattice of the semiconductor crystal. They provide weakly-bound valence electrons to the material, creating excessive negative charge carriers and, thus, this material is called *n-type*. A typical element used for n-type doping is phosphorus (P), seen on the left side of fig. 5. Acceptors are elements with three valence electrons that introduce energy states closely above the valence band, when incorporated into the crystal lattice. The missing negative electron in the lattice, called *hole*, acts like a positive charge and, thus, this material is called *p-type*. A typical element used for p-type doping is boron (B), seen on the right side of fig. 5. For silicon with boron doping, the energy gap between the introduced energy states and the conduction band edge is reduced to only 0.045 eV [2].

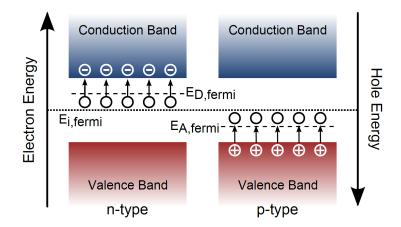

The doping of a semiconductor shifts the Fermi energy  $E_{\rm F}$  towards the corresponding band edge, for donors to the conduction band and for acceptors to the valence band (see fig. 6). So, when two differently doped materials are brought into contact with each other (e.g. a *pn-junction*), the energy bands are bending, because the Fermi level must remain constant in a system in thermodynamic equilibrium. This leads to many useful electrical properties, also described in section 3 in more detail (e.g. sec. 3.2, fig. 11) [2].

<sup>&</sup>lt;sup>9</sup>1 atom per  $10^6$  atoms of silicon [4].

Figure 6: Energy band structure for semiconductors doped with donors (left) and acceptors (right side) and the shift of the corresponding Fermi levels  $E_{D,\text{fermi}}$  and  $E_{A,\text{fermi}}$  towards the conduction band (n-type) and the valence band (p-type), respectively [4].

## 2.2 Silicon sensors as particle detectors

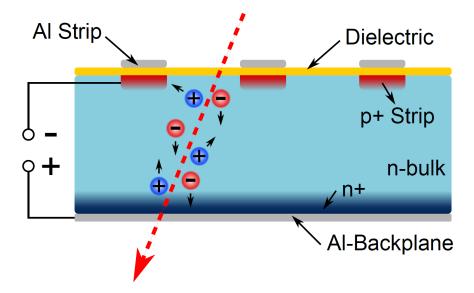

For a silicon sensor, as it is used in the current tracker of the CMS experiment, a very lowly doped silicon *n*-bulk is used as substrate. A thin, highly doped  $p^+$ -region ( $p^+$ implant) on this *n*-substrate forms a large-area pn-junction. (This holds for so-called p-in-n sensors, though, in the phase II upgrade of the tracker, there shall be used psubstrate and  $n^+$ -implant. However, this is more complex since it needs additional implantations<sup>10</sup> and goes beyond the scope of this thesis, as it is not yet fully developed.) A detector is utilised like a diode operated in reverse direction. Therefore, a reverse bias voltage is applied between the  $p^+$ -implant and the back side of the substrate which is highly doped  $n^+$  to ensure good ohmic contact to the aluminium backplane. This bias voltage depletes the bulk from free charge carriers and a so-called space charge region (SCR) forms, starting from the  $p^+$ -implant. When a particle is traversing the sensor now, it creates electron-hole-pairs along its track, similar to the ionisation of gas, while loosing energy. Due to the applied voltage, the electron-hole-pairs are separated, the electrons move to the  $p^+$ -implant and the holes to the  $n^+$ -backplane. This drift is detected as electrical signal.

### 2.2.1 Silicon strip sensors

To achieve a spatial resolution, the  $p^+$ -implant is segmented into strips or pixels. So by differentiating the implant-segment where a signal is detected, one obtains a one-(strips) or two-dimensional (pixels) spatial resolution of the particles track. In figure 7 a schematic cross section of an n-bulk silicon strip detector is shown. Here one can also see that the readout of the signal is coupled capacitively from the implant-strips via a

$<sup>^{10}</sup>$ So-called *p-stop* implantations or *p-spray* to ensure strip separation.

Figure 7: Schematic cross section of an n-bulk silicon strip detector with a traversing particle (red dashed arrow) producing electron-hole-pairs [4].

dielectric to the aluminium readout strips to prevent the readout electronics from the leakage current of the detector.

### 2.2.2 Signal generation

The number of created electron-hole-pairs per particle n is given as the quotient of the total energy loss  $E_{\text{loss}}$  and the energy required for the creation of an electron-hole-pair  $E_{\text{eh}}$ :

$$n = \frac{E_{\rm loss}}{E_{\rm eh}}.$$

(2)

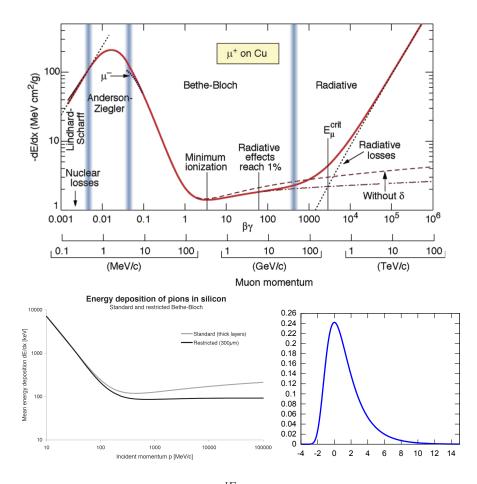

For silicon  $E_{\rm eh} \approx 3.6 \,{\rm eV}$ .  $E_{\rm loss}$  comes from the Bethe-Bloch formula (see fig. 8 top) considering a minimum ionising particle (minimal turning point of the curve). However, corrections are necessary for thin layers  $(300 \,\mu{\rm m})$ , due to high energetic  $\delta$ -electrons (knock-on-electrons). This is known as restricted Bethe-Bloch formula (seen in fig. 8 bottom left) and not only lowers the mean energy deposition  $\frac{dE}{dx}$ , but also deviates the minimum of the curve. Moreover, the statistical fluctuations of the energy loss in thin layers is described by the *Landau distribution* (seen in fig. 8 bottom right), which is not symmetric but has a long upper tail (also called *Landau tail*) due to the high energetic  $\delta$ -electrons. Therefore, the mean value of the energy deposition is higher than the most probable value (peak of the Landau distribution) by a factor of 1.22. So the most probable energy loss is  $E_{\rm loss} \approx 80 \,{\rm keV}$ , resulting in a most probable charge of about n = 22,000 electron-hole-pairs created by a minimum ionising particle traversing a silicon sensor of 300  $\mu{\rm m}$  thickness. (More detailed information to this calculation can be found in [8].)

Figure 8: Top: Mean energy deposition  $\frac{dE}{dx}$  according to the Bethe-Bloch formula, minimum ionisation at the minimal turning point of the curve. Bottom left: Comparison of standard (thick layers, grey) and restricted Bethe-Bloch formula (300  $\mu$ m silicon, black). Bottom right: Landau distribution resulting in a ratio of 1.22 between mean value and most probable (peak) value [3, 8].

Compared to the intrinsic charge carrier density of silicon of about  $10^{10}$  cm<sup>-3</sup>, this is a relatively small number and, therefore, it is crucial to deplete the sensor of free charge carriers to achieve a suitable signal-to-noise ratio (SNR). Only the depleted region of the detector acts as sensitive area for detection, and so, the detector should be operated with a bias voltage sufficiently high for the space charge region to extend across the whole sensor. This threshold bias voltage is called *full depletion voltage*  $V_{depl}$  [3].

As this thesis only deals with test structures (described in sec. 3), more information about silicon sensors can be found in any of the references [9], [10], [11] or [2], a detailed explanation of the manufacturing process of silicon microstrip detectors gives [4].

#### 2.2.3 Radiation damage

The irradiation induces changes in the semiconductor that degrade the performance of the detector and are thus called *radiation damage*. A few examples for this are an effective doping change of the bulk material (including type inversion of n-type silicon to p-type), an increase of resistivity of undepleted bulk material, a change of oxide charge or charge trapping and thus the reduction of the signal [2].

#### 2.2.4 Manufacturers

There are two commercial vendors for the sensor production that are considered in this thesis: The Japanese company *Hamamatsu Photonics K. K.* (HPK) and the Austrian company *Infineon Technologies Austria AG* (Infineon).

## 3 Test structures

As the mostly rectangular sensors are produced on round wafers, there are free areas in the rim regions of the wafer, where additional devices are placed. These devices are called *test structures* (TS) and allow to extract a lot of electrical properties of a wafer that cannot be measured directly on the sensor (or only with much more difficulties). Also destructive measurements can be performed on test structures. Since they are produced on the same wafer as the sensor, one can assume that the test structures and the sensors perform identical or exhibit the same weaknesses and, therefore, they are also used to monitor the stability of the production process. The test structures are placed on semicircle-shaped wafer fragments and, thus, also called *half-moons* (HM).

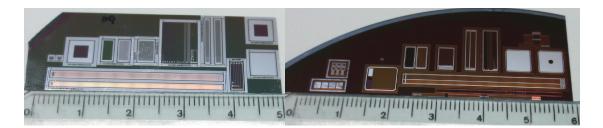

A so-called standard half-moon was designed by the tracker collaboration, a test structure with identical layout for all involved vendors, so that they could be compared to each other.

These standard half-moons were also implemented in all subsequent designs to make a comparison possible. In some cases, some improvements were done or some structures were added, but all standard half-moons contain the six standard test structures that are described in the following subsections of this chapter. In figure 9, a photo of a standard half-moon of HPK and Infineon is shown.

Figure 9: Standard half-moon of HPK (left) and Infineon (right).

## 3.1 Diode

A diode is a simple pn-junction where a space charge region (SCR) forms between the implant and the bulk material, where the two different doped semiconductors come into contact with each other. The diode is very similar to the sensor, as a sensor is basically also a simple pn-junction just like diode. The main difference is that the implant of the test structure is not segmented. Naturally, it is smaller in size and it also has no poly silicon resistors and bias ring, but is directly connected to the metal pad, where the bias voltage is applied.

So on a diode, the same quantities as on a sensor can be measured and the main parameters characterising the sensor can be extracted.

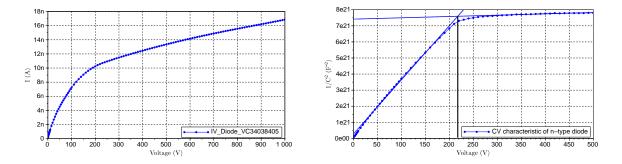

When a reverse bias voltage ( $V_{\text{bias}}$ ) is applied to the *pn*-junction, the space charge region grows with increasing voltage, until the whole bulk is depleted of free charge carriers. The reverse bias voltage, at which the whole bulk is depleted, is called *full depletion voltage*  $V_{\text{depl}}$ . The current flowing through the SCR, called *reverse dark current*, is measured for the current versus voltage (IV) characteristic of the diode. A typical IV-curve of an n-type diode is shown in figure 10. The slope is higher for  $V_{\text{bias}} < V_{\text{depl}}$ and becomes lower for  $V_{\text{bias}} > V_{\text{depl}}$ . The measured reverse dark current should be as low as possible to minimize the power needed for biasing the detector and it can also serve as an indicator for defects in the bulk material [13].

When a sufficiently large reverse bias voltage is applied to the diode, the junction breaks down and conducts a very large current. This breakthrough is not inherently destructive, but the maximum current must be limited to avoid an excessive heating [10].

Between the implant and the backside of the diode, the capacitance versus voltage (CV) characteristic can be measured as well. The measured capacitance is dependent on the thickness of the depletion region W, which can be estimated with [2]

$$W \approx \sqrt{2\varepsilon_0 \varepsilon_r \mu \rho |V_{\text{bias}}|} \tag{3}$$

where  $\varepsilon_0$  is the vacuum permittivity,  $\varepsilon_r$  is the relative permittivity, and  $\rho$  and  $\mu$  are resistivity and the the mobility of the majority charge carriers of the lower doped region, respectively. According to the formula of the parallel-plate capacitor

$$C = \varepsilon_0 \varepsilon_r \frac{A}{W} \tag{4}$$

Figure 10: IV-curve of an n-type diode (left) and CV-curve with two linear fits for extracting the full depletion voltage  $V_{\text{depl}} = 218 \text{ V}$  (right).

with the active area A of the diode, the capacitance decreases with  $V_{\text{bias}}$  in accordance with the following dependency:

$$C \approx A \sqrt{\frac{\varepsilon_0 \varepsilon_{\rm r}}{2\mu \rho |V_{\rm bias}|}} \propto |V_{\rm bias}|^{-\frac{1}{2}}.$$

(5)

This formula, of course, is only valid for  $V_{\text{bias}} < V_{\text{depl}}$ , because at  $V_{\text{depl}}$  the depletion zone reaches its maximum extension and the capacitance stays constant when  $V_{\text{bias}}$  exceeds  $V_{\text{depl}}$ :

$$C = \varepsilon_0 \varepsilon_r \frac{A}{d} \tag{6}$$

with d the thickness of the detector that is an active region for the detection.

Due to the dependency of C on  $V_{\text{bias}}$  of eq. (5), one usually plots  $1/C^2$  vs.  $V_{\text{bias}}$ , so that one can see ideally an curve that increases linearly until  $V_{\text{depl}}$  and is constant for all  $V_{\text{bias}} > V_{\text{depl}}$ . From that curve,  $V_{\text{depl}}$  can easily be extracted by two linear fits, as shown in figure 10, where a measured CV-curve of an n-type diode is plotted.

At the sensor, however, the implant is segmented into strips and, therefore, the electrical field is not linear and the depletion zone does not grow homogeneously. For that reason, a correction factor between the full depletion voltage of a segmented sensor and a planar diode has to be taken into account [14]:

$$\frac{V_{\text{depl sensor}}}{V_{\text{depl diode}}} = \left(1 + \frac{2p}{d}f\left(\frac{w}{p}\right)\right). \tag{7}$$

In this equation w is the strip width, p the strip pitch, d the thickness of the device and the function  $f\left(\frac{w}{p}\right)$  is a numerical approximation of the Poisson equation for the non-linear field [2]:

$$f(x) = -0.00111x^{-2} + 0.0586x^{-1} + 0.24 - 0.651x + 0.355x^{2}.$$

(8)

A further quantity can be measured with the CV-characteristic: the *total capaci*tance  $C_{\text{tot}}$  of the device, which is those capacitance that is measured for  $V_{\text{bias}} > V_{\text{depl}}$  and should ideally be constant. (In practice, the mean value of the horizontal fit over the fitted region is taken for  $C_{\text{tot}}$ ; normally the CV-curve is measured up to twice the expected  $V_{\text{depl}}$ , so that one has roughly the same number of measured points for the fit of the linearly increasing part of the curve and the fit of the horizontal one.) With  $C_{\text{tot}}$  one can determine the active thickness d of the device, which is the fully depleted region that is an active region for the detection of the sensor, by using the equation of the parallel plate capacitor of eq. (6):

$$d = \varepsilon_0 \varepsilon_r \frac{A}{C_{\text{tot}}}.$$

(9)

With  $V_{\text{depl}}$  and  $C_{\text{tot}}$  one can furthermore determine the resistivity of the bulk material  $\rho_{\text{bulk}}$  with the equation [2]:

$$\rho_{\rm bulk} = \frac{d^2}{2\varepsilon_0\varepsilon_{\rm r}\mu V_{\rm depl}} \tag{10}$$

respectively with eq. (9) inserted:

$$\rho_{\text{bulk}} = \frac{\varepsilon_0 \varepsilon_{\text{r}} A^2}{2\mu C_{\text{tot}} V_{\text{depl}}}.$$

(11)

At last, a remark to the determination of the active area A, occurring in many formulas in this section: This is the area of the depletion zone forming under the implant, but the depletion zone does not only grow in depth, but also laterally, according to formula (3). So A is not identical with the area of the implant region, but is measured from half the way between the implant and the *edge ring*. The edge ring is encircling every device and shielding it electrically from the other devices on the wafer because it is doped the same way as the backplane and, therefore, practically lies on backplane potential. So we can assume that the potential applied on the metal pad falls to backplane potential to the guard ring.

## 3.2 MOS

A Metal Oxide Semiconductor (MOS) structure consists, as the name says, of a metal layer, an oxide layer and a semiconductor. More general, this structure is referred to as a MIS (metal-insulator-semiconductor) structure, but as for silicon devices the common insulator is SiO<sub>2</sub>, the more commonly used expression is MOS.

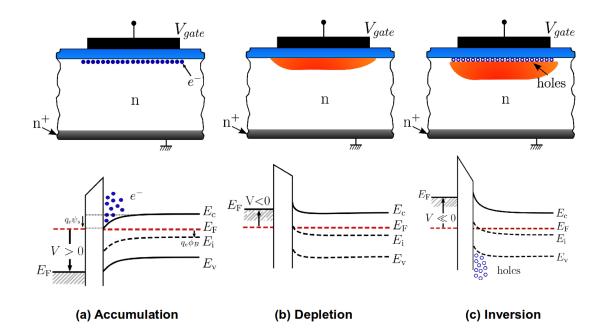

The metal layer of the MOS is called *gate*, here the *gate voltage*  $V_{\text{gate}}$  is applied to vary the band structure of the energy band diagram beneath the semiconductor-oxide interface. When no voltage is applied, the semiconductor bands bend down to the dielectric layer for n-doped silicon (and up for p-doped silicon) to accommodate the work function difference between the metal and the semiconductor, because at thermal equilibrium the Fermi level must be constant. The work function  $q\Phi$  is the energy necessary to move an electron from the Fermi level to the vacuum level. To achieve the so-called *flat-band* condition, when all bands are flat, the work function difference

Figure 11: A schematic cross section (top) and the energy band diagram (bottom) of an n-type MOS in (a) accumulation, (b) depletion and (c) inversion. In the energy band diagrams one can see from left to right the metal with the Fermi level  $E_{\rm F}$ , the oxide and the semiconductor with the conduction band  $E_{\rm c}$ , the quasi Fermi level  $E_{\rm F}$ , the intrinsic Fermi level  $E_{\rm i}$  and the valence band  $E_{\rm v}$  [15, 16].

between the metal and the semiconductor  $q\Phi_{\rm m} - q\Phi_{\rm s}$  has to be compensated by applying an external voltage, the so-called *flat-band voltage*  $V_{\rm fb}^{11}$ :

$$V_{\rm fb} = \Phi_{\rm m} - \Phi_{\rm s}.\tag{12}$$

This equation is, however, only valid in the ideal case of the absence of oxide charges. Hence, the value of  $V_{\rm fb}$  can be used as an indicator of the oxide charges, as we will see later. But first, we discuss further states an external gate voltage  $V_{\rm gate}$  can induce (In figure 11 the schematic cross section (top) and the energy band diagram (bottom) of an n-type MOS is shown, and so we will discuss the following cases for an n-type semiconductor):

**Accumulation:** When  $V_{\text{gate}} > V_{\text{fb}}$ , the energy bands bend downwards in the boundary region and the Fermi level gets closer to the conduction band edge and so free electrons are accumulated at the semiconductor-oxide interface (fig. 11 (a)).

<sup>&</sup>lt;sup>11</sup>Theoretically  $V_{\rm fb}$  should be close to zero, because the work function difference  $\Phi_{\rm m} - \Phi_{\rm s} \coloneqq \Phi_{\rm ms}$  is very small and typically lies in a range of  $-0.1 \,\rm V$  and  $-1 \,\rm V$ , but it is dependent on the doping concentration and the temperature [15].

**Depletion:** For  $V_{\text{gate}} \leq V_{\text{fb}}$ , the energy bands bend upwards at the semiconductor-oxide interface and the electrons are repelled from the interface region and a depletion layer forms beneath the interface (fig. 11 (b)).

**Inversion:** If the voltage is further decreased ( $V_{\text{gate}} \ll V_{\text{fb}}$ ), the intrinsic Fermi level ( $E_{\text{i}}$ ) at the interface will reach and cross the quasi Fermi level ( $E_{\text{F}}$ ) and the concentration of holes will increase, so that a layer filled with minority charge carriers forms, called *inversion layer* (fig. 11 (c)). When the Fermi level and the intrinsic level at the interface coincide, the concentrations of electrons and holes are the same (and equal to the intrinsic carrier concentration) and the inversion layer starts to form. This happens, when the surface potential  $\Psi_{\text{s}}$  equals the potential difference of the Fermi level and the intrinsic level  $\phi_{\text{B}}$  (both drawn in fig. 11 (a)). When  $\phi_{\text{B}} < |\Psi_{\text{s}}| < 2\phi_{\text{B}}$ , the concentration of holes at the interface is higher than that of the electrons, but lower than the doping concentration, what is referred to as *weak inversion*. For  $|\Psi_{\text{s}}| \ge 2\phi_{\text{B}}$ , the concentration of the silicon bulk, and that state is called *strong inversion* [15, 11].

Although the behaviour above was described for n-type MOS, for p-type it is very analogue, only all polarities have to be reversed, the bands bend up instead of down and vice versa and, instead of electrons, the holes are the majority charge carriers and the electrons the minority charge carriers.

Now to the practical purpose of a MOS as a test structure: For a real MOS structure, the flat-band voltage does not only depend on the work function difference  $\Phi_{\rm m} - \Phi_{\rm s} := \Phi_{\rm ms}$ , but also on charges present in the oxide or at the oxide-semiconductor interface. There are oxide trapped charges, mobile ionic charges, fixed oxide charges (near the interface) and interface trapped charges. The flat-band voltage change doesn't only depend on the amount of charge, but also on the distribution inside the oxide (in particular on the distance x from the metal gate). Thus, the flat-band voltage, with the combined effect of a surface charge density  $\sigma$  at the interface (with a distance from the metal gate of  $d_{\rm ox}$ , the oxide thickness) and a volume charge density  $\rho(x)$  inside the oxide, can be written as [11]:

$$V_{\rm fb} = \Phi_{\rm ms} - \frac{\sigma d_{\rm ox}}{\varepsilon_{\rm ox} \varepsilon_0} - \frac{1}{\varepsilon_{\rm ox} \varepsilon_0} \int_0^{d_{\rm ox}} \rho(x) x dx.$$

(13)

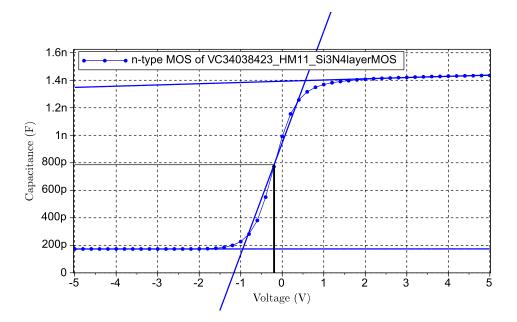

From a MOS device, the capacitance is measured and plotted over the gate voltage, since this curve shows a typical characteristic for the regions of accumulation, depletion and inversion explained above. In the case of accumulation, one measures the constant capacitance of the oxide layer  $C_{\text{ox}}$ . When  $V_{\text{gate}}$  reaches the region of depletion, the capacitance drops down rapidly as the depletion layer grows (because  $C \propto \frac{1}{d}$ , see eq. (6)). The measured capacitance is the series of the oxide capacitance  $C_{\text{ox}}$  and the capacitance of the depletion layer forming in the semiconductor  $C_{\text{s}}$ :  $C = \frac{C_{\text{ox}}C_{\text{s}}}{C_{\text{ox}}+C_{\text{s}}}$ . The capacitance measured in inversion depends on the frequency of the AC signal applied to the MOS for measuring the capacitance. If the AC signal is of a sufficiently low frequency for the minority charge carriers to be able to respond to the signal, they can move into the depletion layer and short the capacitance and the low-frequency (lf) MOS-curve is obtained, where one measures the oxide capacitance  $C_{\text{ox}}$  only. If the AC signal frequency is too high for the minority charge carriers to be able to respond to the signal, the more commonly measured high-frequency (hf) MOS-curve is obtained, where one measures the series of the oxide capacitance and the capacitance of the depletion layer at its maximum extent, and so this capacitance stays constant. However, when the DC sweep rate is too high, so that no inversion charge can form during the sweep, the capacitance doesn't stay constant, but drops further down and one obtains the deep-depletion curve [9, 15].

To obtain the true hf-curve, one has to ensure that the time between setting the gate voltage and measuring the capacitance is long enough for the device to come to equilibrium, because otherwise, at a sweep direction from accumulation to inversion, the CV-curve tends to go into partial deep depletion and the resulting curve will be below the true one, and, for a sweep direction from inversion to accumulation, inversion charge can be injected into the substrate and the measured curve will be above the true curve in the inversion region [9].

With the oxide capacitance  $C_{\text{ox}}$  measured in the accumulation region, one can easily compute the thickness of the oxide  $d_{\text{ox}}$  by inserting it in equation (9) with the area of the metal gate for A.

The main interest in this measurement, however, is the change of the CV-curve due to oxide charges and interface traps. While the oxide trapped charges, the mobile ionic charges and the fixed oxide charges cause a parallel shift of the CV-curve, the shift due to large amounts of interface trapped charges varies with the surface potential and, therefore, this contribution doesn't only shift but also distort the CV-curve [10].

To measure the shift of the CV-curve, one can lay three linear fits into the hf-curve of the MOS, one in each region of accumulation, depletion and inversion, as seen in figure 12, and extract  $V_{\rm fb}$  as the voltage where the capacitance dropped to half the value between accumulation and inversion, to compare it to the ideal value of  $V_{\rm fb} \approx 0$  or a reference sample.  $C_{\rm ox}$  is taken as the mean value of the accumulation fit over the fitted region.

## 3.3 Gate Controlled Diode

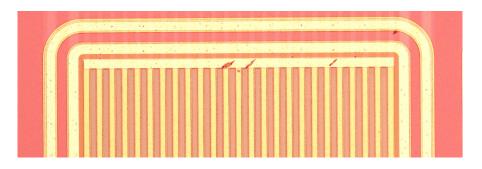

A gate controlled diode (GCD) is a combination of a diode and a MOS structure. It consists of a segmented implant that is comb-shaped and intertwined with a comb-shaped MOS structure, which consists of a gate coupled over a dielectric layer to the bulk between the implant strips<sup>12</sup>. In figure 13, one can see an image detail of the comb-shaped gate of a GCD under the microscope. The gate can be made not only out of metal (e.g. aluminium), but also out of polysilicon and it should overlap the implant region slightly to prevent potential barriers [9].

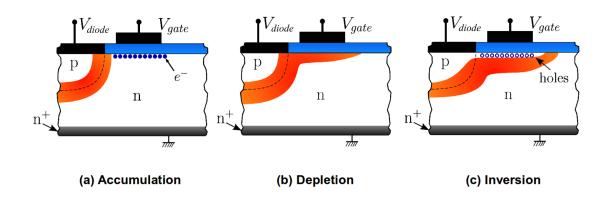

Similar to a MOS device, a GCD is operated in three different states: Accumulation, depletion and inversion. However, from a GCD, the current that flows between the implant and the backplane is measured as a function of the gate voltage  $V_{\text{gate}}$ , keeping

<sup>&</sup>lt;sup>12</sup>There are also produced round GCDs with a circular implant that is encircled by one or more gate rings.

Figure 12: Example for a fit of a hf-MOS-curve with a resulting  $V_{\rm fb} = -0.2$  V and  $C_{\rm ox} = 1.42$  nF.

Figure 13: A picture detail of a GCD under the microscope of the comb-shaped gate (yellowish) and the implant stripes in between (reddish).

Figure 14: A schematic cross section of an n-type GCD in (a) accumulation, (b) depletion and (c) inversion [16].

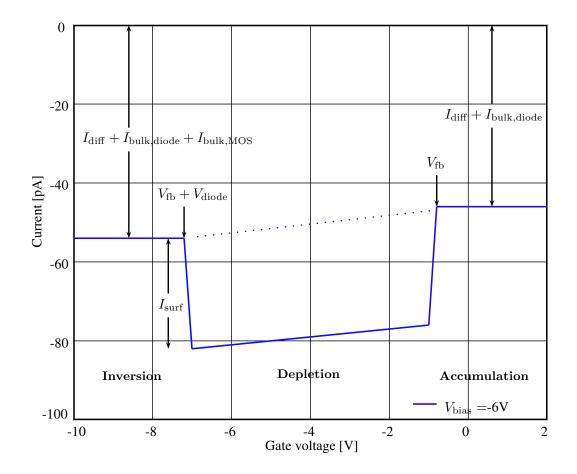

the bias voltage  $V_{\text{bias}}$  constant. Figure 14 shows a schematic cross section and the working principle of an n-type GCD and figure 15 an ideal IV (current vs. gate voltage) curve with all current contributions in the different regions that are explained below:

**Accumulation:** When  $V_{\text{gate}} > V_{\text{fb}}$ , electrons accumulate beneath the oxide layer under the gate and separate the implant strips (see fig. 14 (a)). The measured current in this situation is only the diffusion current  $I_{\text{diff}}$  and the bulk-generation current due to defects in the depleted region of the diode  $I_{\text{bulk, diode}}$  (as seen in fig. 15).

**Depletion:** When  $V_{\text{gate}}$  reaches  $V_{\text{fb}}$ , the region under the gate starts to deplete and the current increases rapidly, due to the surface generation current  $I_{\text{surf}}$  arising from the interface traps (see fig. 14 (b) and fig. 15). The total current measured in depletion is the sum of the surface generation current  $I_{\text{surf}}$ , the diffusion current  $I_{\text{diff}}$  and the bulkgeneration current due to defects in the depleted region of the diode  $I_{\text{bulk, diode}}$  and the MOS  $I_{\text{bulk, MOS}}$ . The state of depletion holds for  $V_{\text{fb}} > V_{\text{gate}} > V_{\text{fb}} + V_{\text{bias}}$  and the depletion zone under the gate widens with increasing  $V_{\text{gate}}$  and connects the depletion zones from the adjacent implant strips. The current increases slightly, as the bulkgeneration current due to defects in the depleted region of the MOS  $I_{\text{bulk, MOS}}$  increases with the widening of the depletion zone under the gate (see fig. 15).

**Inversion:** If the voltage is further decreased, for  $V_{\text{gate}} < V_{\text{fb}} + V_{\text{bias}}$ , holes accumulate beneath the oxide-semiconductor interface under the gate and shield the interface traps and, thus, suppress the surface current. Therefore, the current rapidly drops at  $V_{\text{fb}} + V_{\text{bias}}$  and then stays constant at the level of  $I_{\text{diff}}$  plus  $I_{\text{bulk, diode}}$  plus  $I_{\text{bulk, MOS}}$ .

The I vs  $V_{\text{gate}}$  characteristic of a GCD can be easily used to extract the surface current due to the interface traps, as  $I_{\text{surf}}$  is the height of the step of the depletion region [15].

Figure 15: Ideal IV (current vs. gate voltage) curve of a GCD with all current contributions in the different regions at a bias voltage of -6 V [15].

## 3.4 Interstrip capacitance $C_{int}$

The interstrip capacitance  $C_{int}$  is measured on the CAP-TS-AC test structure. This test structure consists of 9 strips that are processed the same way and, naturally, have the same geometry as the sensor. However, the outermost sets of 3 strips on either side are connected among themselves to lie on the same potential and are intended to reproduce the sensor conditions. Between the middlemost strip and its two adjacent strips, the interstrip capacitance is measured, while the structure is biased with different bias voltages over the bias ring.

The so obtained CV characteristic shows variable values within the first voltage steps, when the strips are not perfectly isolated from each other, but stays constant when the area beneath the implant strips is fully depleted [17].

The value of  $C_{\text{int}}$  is an important parameter for achieving a low signal-to-noise ratio (SNR) of the sensor [13].

#### **3.5** Interstrip resistance $R_{int}$

The interstrip resistance  $R_{int}$  is measured on the CAP-TS-DC test structure, which is very similar to the CAP-TS-AC test structure. Though, the polysilicon resistors are lacking and, thus, the strips are not connected to the bias ring and therewith to each other. This is necessary, because otherwise, essentially the polysilicon resistors would be measured, since they are much smaller than the interstrip resistance. In addition, the implant strips are connected directly to the metal layer above through contact holes and, thus, can be contacted also by the AC pads.

The interstrip resistance is measured between the middlemost strip and its two adjacent strips at different bias voltages. At each bias voltage step (which is applied at the backplane while the bias ring is kept on ground), a small voltage ramp is applied between the middlemost strip and its two grounded adjacent strips and the current flowing between the strips is measured. From the resulting IV curves, the resistance values are obtained by linear fits. This increases the measurement accuracy and suppresses the contribution of a constant leakage current. However, the voltage ramp must be kept small in respect to the bias voltage to avoid a perturbation of the depletion field. Besides, the measured current is expected to be very small, as the interstrip resistance should be high to ensure a good spatial resolution of the sensor [7, 13].

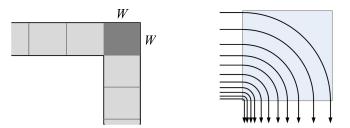

#### 3.6 Sheet resistances

The test structure called *sheet* is designed to measure the resistance values of all conductive layers. These are metal, polysilicon, strip implant, edge implant, and for n-in-p type also p-stop or p-spray. For each material, there are some meander shaped structures with different widths and lengths, where the resistance value is extracted with a linear fit from an IV curve measured on each structure. The measured resistance scales with the length and the inverse of the width. So, for the specific resistivity  $\rho/sq$ . in  $\Omega/sq$ . (which is called *sheet resistance*), it is divided by the length and multiplied by the width, or directly multiplied by the square number, as the ratio of width to length w/l is called and which is normally known for each sheet structure.

While for the metal and the polysilicon measurement a depletion zone has no significant influence, for the resistance measurement of the implants, a sufficient bias voltage is essential to ensure that there is no short between the meander of the structure and the resistance over the whole length of the implant is measured.

## 4 Standard measurements on test structures

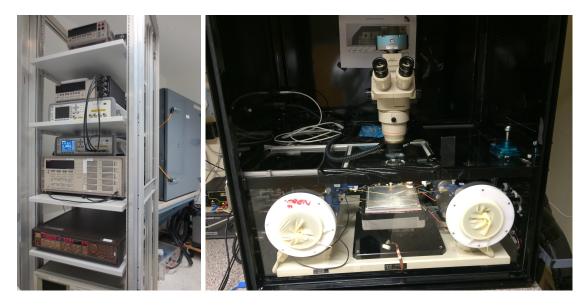

All the measurements were performed on the *Process Qualification Center* (PQC) setup in the clean room of HEPHY (fig. 16). This setup consists of a probe table where the device under test can be fixed with a vacuum jig. This table is made of aluminium and connected to a cable, so that the backplane of the device is contacted. Furthermore, there are several needles attached to positioners with micrometer screws to contact the various pads on the surface of the devices. Above the probe table is installed a microscope, which is needed to see the fine structures of the devices and to contact the pads with the needles. All this is set in a light-tight box that is made from aluminium to serve as a Faraday cage and prevent the devices from light-induced currents. Moreover, the environmental conditions in the box (temperature and relative humidity) are monitored and nitrogen gas can be injected to reduce the relative humidity inside the box. In addition, the probe table is equipped with Peltier elements that are joined to a secondary cooling circuit with a liquid coolant, so that the device can be set to a fixed temperature<sup>13</sup>.

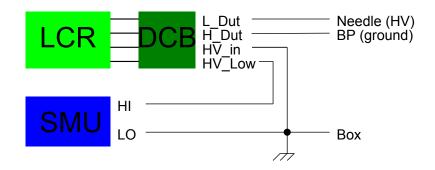

The measurement devices are located outside the box and connected with the needles and the probe table with plugs through the box. In addition, they are connected via  $GPIB^{14}$  to a computer where  $Labview^{15}$  programs are controlling all the devices and retrieving the data. For this setup the following measurement instruments were available:

**Source measure unit (SMU): Keithley 237:** For applying and measuring a voltage or current with high accuracy (pA-range).

**Secondary source measure unit (SMU2): Keithley 2410:** An additional SMU, required for some of the measurements for applying a gate voltage.

**Capacitance meter (LCR): Agilent E4980A:** A high-frequency capacitance measure device using frequencies between 20 Hz and 2 MHz. A decoupling box separates the LCR meter from the high bias voltages and thus allows DC voltages beyond the instruments limit of 42 V.

All the standard test structures were measured on an n-type half moon of HPK, a p-type half moon with p-stop implantation and a p-type half moon with p-spray layer,

<sup>&</sup>lt;sup>13</sup>In the range of -20 to +200 °C [3].

<sup>&</sup>lt;sup>14</sup>General Purpose Interface Bus.

<sup>&</sup>lt;sup>15</sup>National Instruments, Labview – Graphical Development Environment for Data Acquisition, Analysis, and Presentation (http://www.ni.com/labview/).

Figure 16: Pictures of the PQC setup.

also from HPK, and for comparison on two half moons of Infineon, one from run 1 and one from run 4, which were, however, only in n-type available. The used wafers are listed in table 1 with their descriptions. The n-type and p-type half moons are identical in design, only the structures CAP-TS-AC, CAP-TS-DC and sheet of the p-type wafer with p-stop have additional p-stop implantations. The wafer with p-spray naturally has a p-spray layer over the whole wafer and, therefore, over all structures. Though, this shouldn't influence the devices, since the doping concentration of the p-spray layer is much less than that of the implant.

<sup>16</sup>Technique used for ingot production; in contrast to Czochralski process which is more often used in chip production but obtains lesser purity [18].

| structure          | description                                          | producer |

|--------------------|------------------------------------------------------|----------|

| FZ320N_W4_TS-2     | float-zone <sup>16</sup> , 320 nm thickness, n-type, | HPK      |

|                    | wafer 4, TS $2$                                      |          |

| FZ320P_W6_TS-2     | float-zone, 320 nm thickness, p-type                 | HPK      |

|                    | with p-stop, wafer 6, TS $2$                         |          |

| FZ320Y_W4_TS-2     | float-zone, 320 nm thickness, p-type                 | HPK      |

|                    | with p-spray, wafer 4, TS 2                          |          |

| VC14095619_ExtHM   | n-type, run 1, wafer 19, extended half               | Infineon |

|                    | moon                                                 |          |

| VC34038405_ExtHM_8 | n-type, run 4, wafer 5, extended half                | Infineon |

|                    | moon 8                                               |          |

Table 1: Measured structures and their description.

| V <sub>max</sub> | $\pm 1000 \mathrm{V}$ |

|------------------|-----------------------|

| Stepsize         | 10 V                  |

| Compliance       | $10\mu\mathrm{A}$     |

| Wait             | 1000 ms               |

Table 2: Parameters for the IV-measurements of the diodes.

| SMU                    |                      |  |

|------------------------|----------------------|--|

| $V_{ m max}$           | $\pm 500 \mathrm{V}$ |  |

| Stepsize               | $10\mathrm{V}$       |  |

| Compliance             | $20\mu\mathrm{A}$    |  |

| Wait                   | $1000\mathrm{ms}$    |  |

| LCR initialisation     |                      |  |

| Voltage level          | $100\mathrm{mV}$     |  |

| Current level          | 0                    |  |

| Frequency of AC signal | 1 kHz                |  |

Table 3: Parameters for the CV-measurement of the diodes.

## 4.1 IV-characteristic of diodes

For the IV-characteristic of a diode, the SMU is connected to the aluminium layer of the diode with its grounded LO-terminal and to the backplane its HI-terminal. Then, the reverse dark current through the diode is measured while the bias voltage is ramped up. The measurement was controlled by the Labview program 'Diode\_IV\_ntype.vi' for n-type and 'Diode\_IV\_ptype.vi' for p-type, respectively. The chosen parameters are listed in table 2. For n-type, a positive bias voltage, and for p-type, a negative one has to be applied to operate the diode in reverse direction.

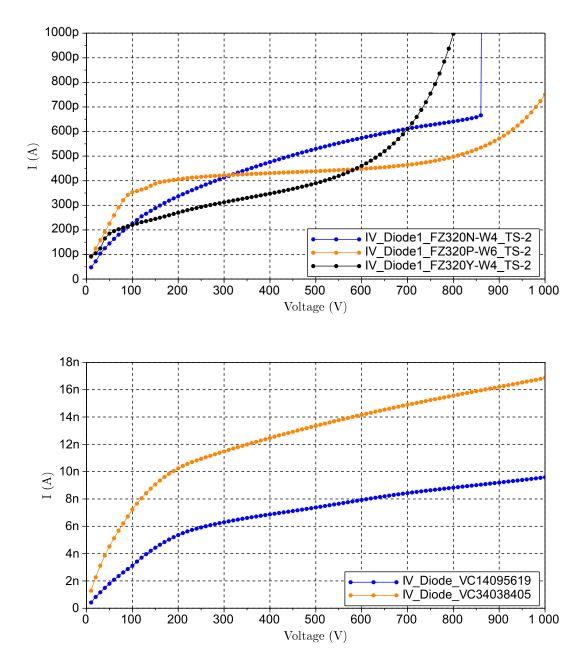

The results of the reverse dark current measurements are plotted in fig. 17, on the abscissa the modulus of the bias voltage is displayed. Only the two diodes from the Infineon wafers are absolutely stable until 1000 V, the n-type diode from HPK exhibited a breakthrough at 860 V, the p-type with p-spray showed a soft breakthrough at about 900 V and the p-type with p-stop was stable until 1000 V, but showed the beginning of a soft breakthrough.

## 4.2 CV-characteristic of diodes

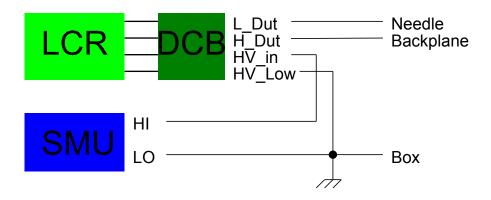

For the CV-characteristic of a diode, the LCR meter is connected via the decoupling box (DCB) parallel to the SMU, to the backplane with the HI-terminal and to the aluminium pad of the diode with the LO-terminal, as can be seen in the circuit diagram in fig. 18. The capacitance of the depleted area is measured while the bias voltage is ramped up. The measurement was controlled by the Labview programs 'Diode\_CV\_ntype.vi' and 'Diode\_CV\_ptype.vi', respectively. All the parameters listed in table 3, the bias voltage is again positive for n-type and negative for p-type.

Figure 17: IV curves of the diodes (top: HPK, bottom: Infineon). The bias voltage was ramped up to  $\pm 1000$  V in steps of 10 V. On each step the reverse dark current was measured after a delay time of 1 s.

Figure 18: Circuit diagram for the CV-measurements of the diodes and MOS.

| structure          | $V_{\rm depl}$   | $C_{ m tot}$      | d              |

|--------------------|------------------|-------------------|----------------|

| FZ320N_W4_TS-2     | 188 V            | $10.3\mathrm{pF}$ | $281\mu{ m m}$ |

| FZ320P_W6_TS-2     | $-221\mathrm{V}$ | $10.1\mathrm{pF}$ | $286\mu{ m m}$ |

| FZ320Y_W4_TS-2     | $-218\mathrm{V}$ | $10.4\mathrm{pF}$ | $278\mu{ m m}$ |

| VC14095619_ExtHM   | $232\mathrm{V}$  | $11.3\mathrm{pF}$ | $309\mu{ m m}$ |

| VC34038405_ExtHM_8 | $218\mathrm{V}$  | $11.5\mathrm{pF}$ | $304\mu{ m m}$ |

Table 4: Results of the CV-measurements of the diodes for the full depletion voltages  $V_{\text{depl}}$ , the total capacitances  $C_{\text{tot}}$  and the active thicknesses d.

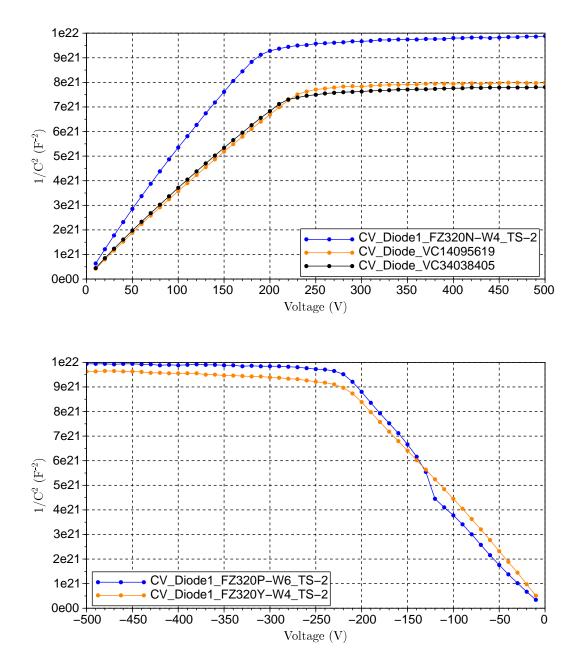

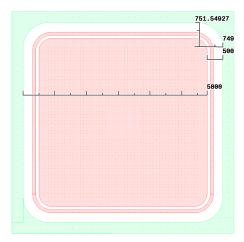

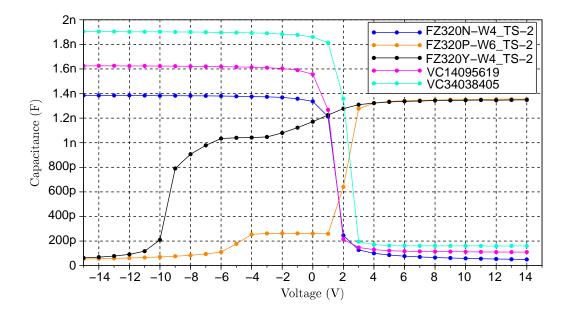

The results of the capacitance measurements are plotted in fig. 19. The full depletion voltages  $V_{\text{depl}}$ , extracted with fits as described in section 3.1, are listed in table 4 together with the total capacitances  $C_{\text{tot}}$  of the diodes and the active thicknesses d. The latter ones were calculated with equation (9), therefore the active areas A were needed. They were determined as described at the end of section 3.1 and also the rounded corners were considered. In figure 20 the layout file from an Infineon diode is shown with the measured distances. A was then calculated with the formula:

$$A = a^{2} - \left(c - \frac{b}{2}\right)^{2} \cdot (4 - \pi)$$

(14)

with a the side length of the square from half the way between the implant and the edge ring, b the distance from implant to edge ring and c the radius of the rounded corners of the edge ring (see fig. 20). For the Infineon diodes these values are:  $a = 5800 \,\mu\text{m}$ ,  $b = 500 \,\mu\text{m}$  and  $c = 750 \,\mu\text{m}$ , and for the HPK diodes:  $a = 5267.5 \,\mu\text{m}$ ,  $b = 374.5 \,\mu\text{m}$  and  $c = 453.5 \,\mu\text{m}$ . So one obtains  $A_{\text{Infineon}} = 33.4 \,\text{mm}^2$  and  $A_{\text{HPK}} = 27.7 \,\text{mm}^2$  for the active areas.

The results for the active thicknesses d were a bit surprising, as the wafers from HPK are  $20 \,\mu\text{m}$  thicker than that from Infineon, actually. Though, HPK made a deeper backside implantation to reduce the active thickness to  $300 \,\mu\text{m}$ . Obviously, this reduces d more than  $20 \,\mu\text{m}$ , presumably because the implantation gradient is less sharp for deeper

Figure 19: CV curves for n-type (top) and p-type (bottom) diodes. The bias voltage was ramped up to  $\pm 500$  V in steps of 10 V. On each step the capacitance of the depleted area was measured after a delay time of 1 s.

Figure 20: Layout file from an Infineon diode with the implant, the guard ring (not used) and the edge ring (green). The side length from half the way between the implant and the edge ring is  $a = 5800 \,\mu\text{m}$ , the distance from implant to edge ring is  $b = 500 \,\mu\text{m}$  and the radius of the rounded corners of the edge ring is  $c = 750 \,\mu\text{m}$  (for the Infineon diodes).

implantation. The difference in the active thickness also explains the difference of the CV-curves between Infineon and HPK in figure 19 (top).

Furthermore, there was investigated whether one can measure the IV-characteristic and the CV-characteristic in one measurement to achieve more time and work efficiency. In the CV-measurement, the current is also measured and recorded in the file. However, it is measured via the decoupling box and, therefore, depends on the delay time between applying the voltage and measuring the current, as the decoupling box consists of big capacitors that are charged and need some time to discharge.

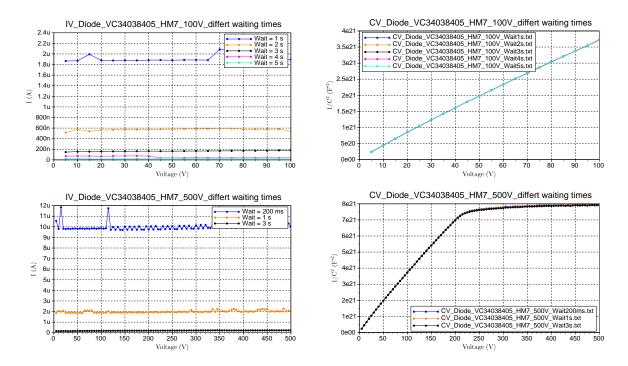

Hence, capacitance and current versus bias voltage measurements were performed with different delay times and the effect on the IV- and the CV-characteristics was examined. This was done on the structure VC34038405\_ExtHM\_7, with the same settings as in table 3, but 5V stepsize and delay times (*Wait*) of 200 ms, 1 s, 2 s, 3 s, 4 s and 5 s, and the curves were measured only up to  $V_{\text{max}} = 100 \text{ V}$ , except for the curves with Wait = 200 ms, 1 s and 3 s, they were measured up to  $V_{\text{max}} = 500 \text{ V}$ .

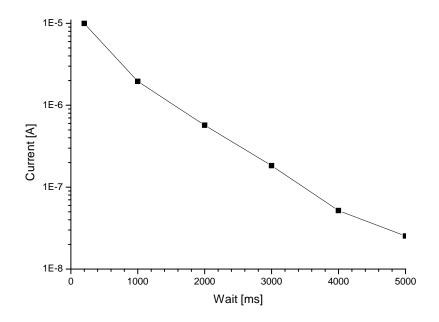

The resulting IV- and CV-curves can be seen in fig. 21, the IV- on the left side and the CV-curves on the right side. One can see that the current values are some orders of magnitude higher than that in fig. 17 in the previous subsection (4.1) and are decreasing with the delay time exponentially, as plotted in fig. 22 with logarithmic ordinate. Even for a delay time of Wait = 5 s, the current is still at approximately 25 nA and, therewith, about one order of magnitude too high. Furthermore, the current is constant over the bias voltage and doesn't show the characteristic shape described in section 3.1. Therefore, the IV-characteristic is measured separately without LCR-meter and decoupling box.

The CV-curve, however, doesn't change with the delay time and the full depletion

Figure 21: IV-curves (left side) and CV-curves (right side) measured at the same time (both via DCB) and with different waiting times (top: 1, 2, 3, 4 and 5s; bottom: 0.2, 1 and 3s).

Figure 22: The current measured via LCR-meter and decoupling box is exponentially decreasing with the delay time.

| SMU                    |                   |  |

|------------------------|-------------------|--|

| $V_{\min}$             | $-15\mathrm{V}$   |  |

| $V_{ m max}$           | $+15\mathrm{V}$   |  |

| Stepsize               | 1 V               |  |

| Compliance             | $10\mu\mathrm{A}$ |  |

| Wait                   | $1000\mathrm{ms}$ |  |

| LCR initialisation     |                   |  |

| Voltage level          | $5\mathrm{mV}$    |  |

| Current level          | 0                 |  |

| Frequency of AC signal | 1 kHz             |  |

Table 5: Parameters for the CV-MOS-measurements of fig. 23.

voltage, that can be fitted from the lower right plot in fig. 21, is also identical for all curves ( $V_{\text{depl}} = 216 \text{ V}$ ). Thus, the CV-characteristic is measured with a delay time of Wait = 1 s, because this doesn't retard the measurement time too much and with only 200 ms of delay time, one can see in the lower left plot of fig. 21 that the current is more noisy and, with values of  $10 \,\mu\text{A}$ , rather high, as this is normally set for the compliance value.

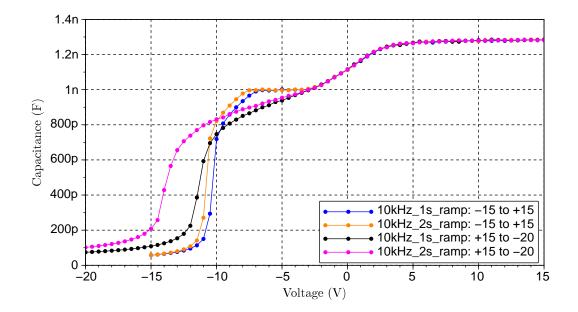

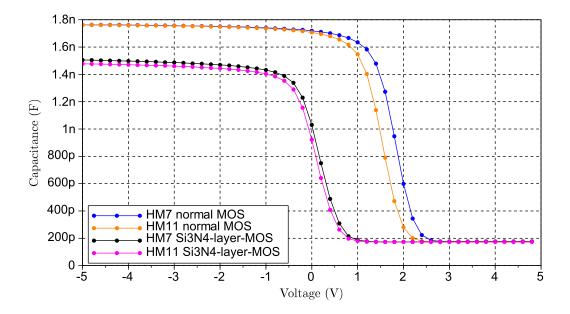

#### 4.3 CV-characteristic of MOS

For the CV-characteristic of the MOS, the device is connected to the LCR-meter and the SMU the same way as the diode for the CV-measurement (explained in the previous subsection and seen in fig. 18). On the MOS, the capacitance between the gate and the backplane is measured while the voltage applied to the gate is varied between -15 and +15 V. All measurements were controlled by the program 'MOS\_CV\_nptype.vi' with the parameters listed in table 5. Here, the gate voltage was varied from minus to plus for all wafer types.

The results of the MOS-measurements are shown in fig. 23. For the n-type MOS, the region of accumulation is on the left side of the plot, where the gate voltage is negative, and the region of inversion where  $V_{\text{gate}}$  is positive, though, for p-type it is the other way around. Hence, the p-type MOS were measured here in the direction from inversion to accumulation. According to this, the step in the curve of the MOS of the p-type wafer with p-stop (the orange curve in fig. 23) presumably represents the phenomenon described in section 3.2 that inversion charge is injected into the substrate and, thus, the obtained curve is above the true curve in the inversion region.

Therefore, this device was then also measured with twice the delay time and with reversed ramp direction of the gate voltage. Further, the frequency was increased and tested for different values and the stepsize was reduced, which not only yields a better resolution of the curve, but also a smaller current flowing at each step of the voltage ramp.

The so measured curves are shown in fig. 24 and the therefore used parameters are

Figure 23: CV-characteristics for the n-type MOS (blue, pink and turquoise) and the p-type MOS with p-stop (yellow) and p-spray (black). Here, the gate voltage was varied from minus to plus for all wafer types.

| SMU                    |                           |  |

|------------------------|---------------------------|--|

| $V_{\min}$             | $+15\mathrm{V}$           |  |

| $V_{ m max}$           | $-15\mathrm{V}$           |  |

| Stepsize               | $-0.5\mathrm{V}$          |  |

| Compliance             | $10\mu\mathrm{A}$         |  |

| Wait                   | $1000{ m ms}/2000{ m ms}$ |  |

| LCR init               | ialisation                |  |

| Voltage level          | $5\mathrm{mV}$            |  |

| Current level          | 0                         |  |

| Frequency of AC signal | 10 kHz                    |  |

Table 6: Parameters for the CV-MOS-measurement of the p-type wafers with reversed ramp direction of the gate voltage.

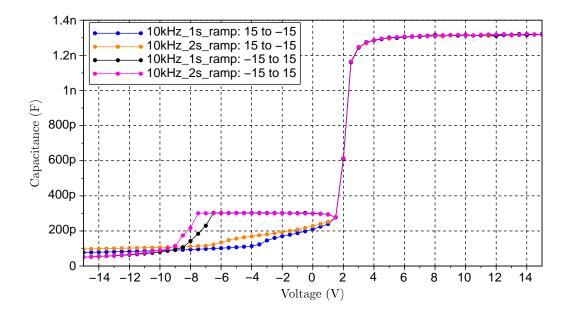

listed in table 6. One can see, that the grater *Wait*-value only widens the step, but the ramp direction is crucial for the shape of the curve. The true value is somewhere in between the curves of the two ramp directions. However, the capacitance drop of depletion is exactly the same and so, for the flatband voltage or its shift between the different samples, the ramp direction is insignificant.

For the MOS of the p-type wafer with p-spray, the same remeasurements were done as for that with p-stop, and they can be seen in fig. 25. In this case, however, it is not clear whether it is the same effect or some other strange behaviour of the p-spray layer. It may be that the junction of the differently doped p-spray layer and the bulk material causes the second step noticeable in the CV-characteristic (and it is also not clear where to take  $V_{\rm fb}$ ).

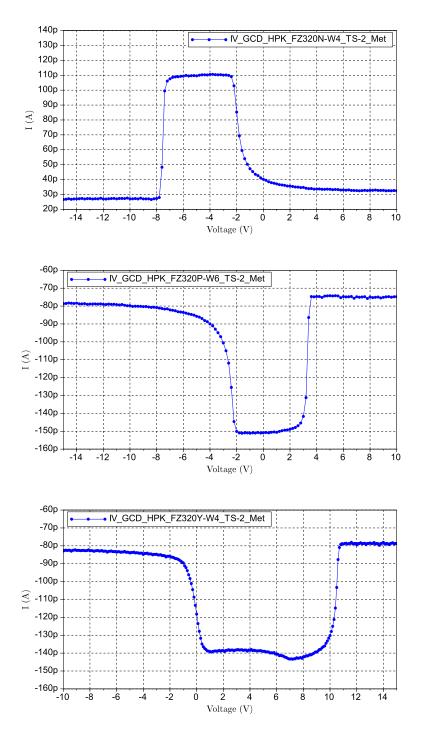

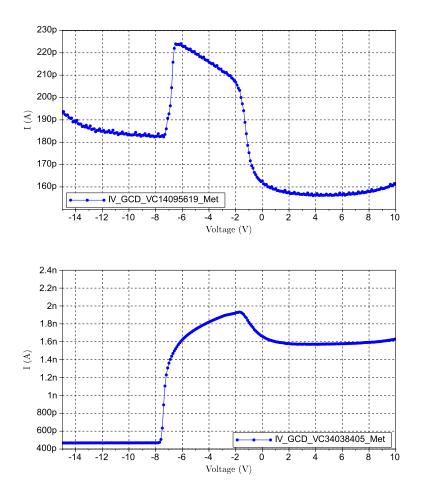

## 4.4 IV-characteristics of GCDs

The gate controlled diodes have to be connected to two SMUs, the first SMU (K237) provides the constant bias voltage  $V_{\text{bias}}$ , and the SMU2 (K2410) provides the gate voltage  $V_{\text{gate}}$  that is varied during the measurement. According to their purpose of use, the SMUs are also called *Bias-SMU* and *Gate-SMU*, respectively. The Bias-SMU also measures the current that flows between the implant and the backplane (BP). For the following measurements, it was connected with its HI-terminal to the implant strips and with its LO-terminal to the backplane, which was grounded. The Gate-SMU was connected with its HI-terminal also to the grounded backplane.

$V_{\text{gate}}$  was varied between -15 V and +10 V for n-type and -10 V and +15 V for p-type and the constant  $V_{\text{bias}}$  was set to -5 V for n-type and +5 V for p-type GCDs, respectively. The measurements were controlled with the program 'GCD\_IV\_nptype\_changed.vi' and all the parameters are listed in table 7.

The results of the IV-characteristics can be seen in fig. 26 and 27. The characteristic of the GCD of the n-type half moon of HPK is in good agreement with the ideal curve

Figure 24: CV-curves of the p-type MOS with p-stop with different ramp directions and waiting times of 1 s and 2 s, respectively.

Figure 25: CV-curves of the p-type MOS with p-spray with different ramp directions and waiting times of 1 s and 2 s, respectively.

| SMU (K237)     |                                     |  |  |  |  |  |

|----------------|-------------------------------------|--|--|--|--|--|

| $V_{ m bias}$  | $\pm 5\mathrm{V}$                   |  |  |  |  |  |

| Compliance     | $10\mu\mathrm{A}$                   |  |  |  |  |  |

| Wait           | 1000 ms                             |  |  |  |  |  |

| SMU2           | (K2410)                             |  |  |  |  |  |

| $V_{ m start}$ | $-15{ m V}$ / $-10{ m V}$           |  |  |  |  |  |

| $V_{ m max}$   | $+10 \mathrm{V}$ / $+15 \mathrm{V}$ |  |  |  |  |  |

| Stepsize       | $0.2{ m V}$ / $0.1{ m V}$           |  |  |  |  |  |

| Compliance     | $10\mu\mathrm{A}$                   |  |  |  |  |  |

Table 7: Parameters for the IV-GCD-measurement.

of fig. 15 (in sec. 3.3). It shows a distinctive step-shape and a surface current  $I_{\rm surf}$  of ~ 80 pA. The characteristic of the GCD of the p-type HM with p-stop is mirrored at both axes, but has the same shape and the absolute value of the surface current is nearly identical with  $I_{\rm surf} \approx -70$  pA. The resulting curve of the GCD of the p-type HM with p-spray is similar to that with p-stop and the current levels have the same height ( $I_{\rm surf} \approx -60$  pA), however, the width of the step is much broader. This may again be some strange effect of the p-spray layer, because here, also the estimation, that the width of the step should approximately equal the bias voltage, is not valid.

The curves of the GCDs of the Infineon wafers (fig. 27) are rather odd. That of run 1 seems to have a very high bulk-generation current  $I_{\text{bulk, MOS}}$  (compare fig. 15 in sec. 3.3), but even more strange is the fact that the current level on the left side of the step is higher than that on the right. Nevertheless, one can extract a surface current  $I_{\text{surf}}$  of  $\sim 45 \text{ pA}$ . That of run 4, however, doesn't look like an usual GCD-characteristic. The current levels on either side of the step are very unequal and the curve in the depletion-region is curved in such a way that one can not identify a step on the left side. Moreover, the current is one order of magnitude higher than that of the reference wafers. This also causes a much higher  $I_{\text{surf}}$ . However, at the right side the step is  $\sim 300 \text{ pA}$  high and at the left the height is at least 1 nA, while at all the other wafers the steps at the left and right side have approximately the same height.

Therefore, more measurements were done, with reversed direction of the gate voltage ramp and with different ramp rates (up to a stepsize of 50 mV and a waiting time of 10 s), but neither of it had any effect on the curve. Also other wafers from that run were measured, but although the curves were slightly different, the shape was the same. A variation of the bias voltage only affected the width of the region of depletion, as expected, but not the shape of the curve. Even a change of the measurement circuit was tried out, but this only shifted the curve, due to changed reference potentials, and didn't change its shape. Thus, more detailed studies will be necessary to explain this curious behaviour.

Figure 26: IV-characteristics of GCDs of HPK n-type (top), p-type with p-stop (middle) and p-type with p-spray (bottom) at bias voltages of  $V_{\text{bias}} = -5 \text{ V}$  for n-type and  $V_{\text{bias}} = +5 \text{ V}$  for p-type.

Figure 27: IV-characteristics of GCDs of Infine ons run 1 (top) and 4 (bottom) at bias voltages of  $V_{\rm bias}=-5\,{\rm V}.$

| SI                     | ЛU                                                                                           |  |  |

|------------------------|----------------------------------------------------------------------------------------------|--|--|

| $V_{ m start}$         | 0 V                                                                                          |  |  |

| $V_{ m end}$           | $\pm 100\mathrm{V}$                                                                          |  |  |

| Voltage ramp style     | 'CEC voltage ramp'                                                                           |  |  |

| Stepsize               | $1 \mathrm{V} (\mathrm{for} \ 0 - 20 \mathrm{V}) \mathrm{and} \ 5 \mathrm{V} (\mathrm{for})$ |  |  |

|                        | $20 - 100 \mathrm{V})$ / p-type with p-stop: $0.2 \mathrm{V}$                                |  |  |

|                        | $(for \ 0 - 5 V)$                                                                            |  |  |

| Compliance             | $10\mu\mathrm{A}$                                                                            |  |  |

| Wait                   | $1000\mathrm{ms}$                                                                            |  |  |

| LCR init               | ialisation                                                                                   |  |  |

| Voltage level          | $250\mathrm{mV}$                                                                             |  |  |

| Current level          | 0                                                                                            |  |  |

| Frequency of AC signal | 1 MHz                                                                                        |  |  |

Table 8: Parameters for the  $C_{\text{int}}$ -measurement.

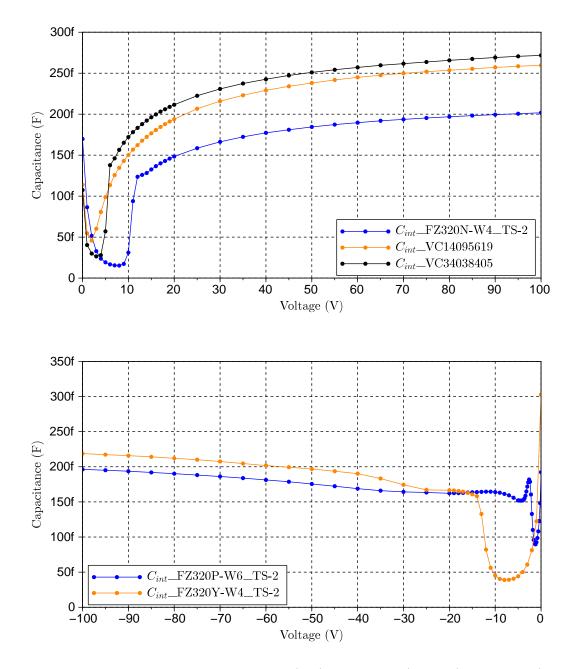

#### 4.5 Interstrip capacitance C<sub>int</sub>

For the measurement of the interstrip capacitance, the CAP-TS-AC structure was connected to the LCR-meter via the decoupling box, with the H-Dut-exit to the middlemost strip and the L-Dut-exit to its two adjacent strips. The SMU was connected with the HI-terminal to the backplane and with the grounded LO-terminal to the bias ring. The capacitance was then measured while the bias voltage was ramped from 0 to  $100 \,\mathrm{V}$ (+100 V for n-type and -100 V for p-type). In the programs used for these measurements, the 'CEC voltage ramp' was selected and modified, so that, up to  $|V_{\text{bias}}| = 20 \text{ V}$ , there was measured in steps of 1V, to ensure that the deviations in the small voltage range are not due to inaccuracies in the measurement resolution. For  $|V_{\text{bias}}| >$ 20 V the stepsize was 5 V. The used programs were 'CINT\_ntype\_rampslow.vi' and 'CINT\_ptype\_rampslow.vi' for n- and p-type, respectively. For the p-type with p-stop 'CINT\_ptype\_rampveryslow.vi' was used, where the stepsize between  $0 < |V_{\text{bias}}| < 5 \text{ V}$ was reduced to  $0.2 \,\mathrm{V}$ . All parameters are listed in table 8. The results were divided by the strip length, which was 3.475 cm for HPK and 3.521 cm for Infineon, and plotted in fig. 28. As mentioned in section 3.4, the values in the range of small bias voltages are variable, but the capacitance stays more or less constant for  $|V_{\text{bias}}| \ge 20 \text{ V}$ .

### 4.6 Interstrip resistance $R_{int}$

For the interstrip resistance measurement, the SMU was connected to the middlemost strip of the CAP-TS-DC structure with the HI-terminal and with the LO-terminal to its two adjacent strips, which were grounded. The SMU2 (K2410) was used to apply the bias voltage between the backplane (HI) and the bias ring (ground). The bias voltage was then ramped from 0 to 200 V (+200 V for n-type and -200 V for p-type) in steps of 10 V. At each bias voltage step, a small voltage ramp was applied with the SMU (from -2 to 2 V in steps of 0.5 V) and the current was measured. From these IV curves,

Figure 28: Interstrip capacitances for n-type (top) and p-type (bottom) structures (per cm strip length).

| SMU (K237)     |                      |  |  |  |  |

|----------------|----------------------|--|--|--|--|

| $U_{\min}$     | -2 V                 |  |  |  |  |

| $U_{ m max}$   | +2 V                 |  |  |  |  |

| Compliance     | $10\mu\mathrm{A}$    |  |  |  |  |

| Stepsize       | $0.5\mathrm{V}$      |  |  |  |  |

| SMU2 (         | (K2410)              |  |  |  |  |

| $V_{ m start}$ | 0 V                  |  |  |  |  |

| $V_{ m max}$   | $\pm 200 \mathrm{V}$ |  |  |  |  |

| Stepsize       | 10 V                 |  |  |  |  |

| Compliance     | $10\mu\mathrm{A}$    |  |  |  |  |

| Wait           | $1000\mathrm{ms}$    |  |  |  |  |

Table 9: Parameters for the  $R_{\rm int}$ -measurement.

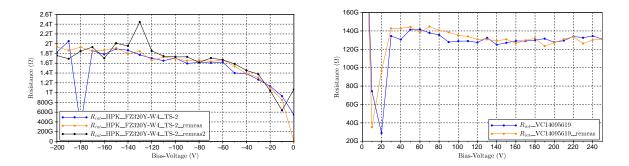

Figure 29: Interstrip resistances of the p-type wafer with p-spray (left) and the n-type wafer from Infineons run 1 (right side).

the resistance values were determined as the slopes of linear fits to these curves. This was done with the programs 'RINT\_ntype.vi' and 'RINT\_ptype.vi' for n- and p-type, respectively, and the parameters listed in table 9.

The problem with these measurements was, however, that in most cases the fits were not linear, and so the resistance values were very erratic and did not yield an useful curve. Only the IV ramps at the p-type wafer with p-spray and the wafer from Infineons run 1 were sufficiently linear that some useful resistance values were obtained, which are plotted in fig. 28. Apart from the first few bias voltage steps, where the voltage ramp probably influences the depletion field (as mentioned in section 3.5), the resistance value stays tolerably constant. However, one can see that the several remeasurements are not wholly identical and show many outliers. Nevertheless, one finds out that the resistance value of the Infineon wafer is more than one order of magnitude lower than that of the HPK wafer, but still it is more than two orders of magnitude higher than the specification of  $R_{\rm int} > 1 \,\mathrm{G}\Omega$  [7].

Though, to ensure reliable results of this measurement, there should be checked the

| SMU                                  | (K237)                                                                  |  |  |  |

|--------------------------------------|-------------------------------------------------------------------------|--|--|--|

| $V_{ m start}$                       | 0 V                                                                     |  |  |  |

| Wait                                 | $500\mathrm{ms}$                                                        |  |  |  |

| Compliance                           | 10 / 20 / 30 / 50 / 100 $\mu { m A}$                                    |  |  |  |

| $V_{ m stop}$ (Poly-Si)              | 10 V                                                                    |  |  |  |

| Stepsize (Poly-Si)                   | 1 V                                                                     |  |  |  |

| $V_{\rm stop}$ (Metal)               | 0.01 V                                                                  |  |  |  |

| Stepsize (Metal)                     | $0.001\mathrm{V}$                                                       |  |  |  |

| $V_{\rm stop}$ (Implant n- / p-type) | $10 \mathrm{V}  /  5 \mathrm{V}$                                        |  |  |  |

| Stepsize (Implant n- / p-type)       | 1 V / 0.5 V                                                             |  |  |  |

| SMU2                                 | (K2410)                                                                 |  |  |  |

| $V_{ m bias}$                        | $180\mathrm{V}$ / $-175\mathrm{V}$ / $-150\mathrm{V}$ / $300\mathrm{V}$ |  |  |  |

| Compliance                           | $10\mu\mathrm{A}$                                                       |  |  |  |

Table 10: Parameters for the sheet-measurements.

quality of the fits in the Labview program and the measurement should be enhanced to yield more linear IV curves.

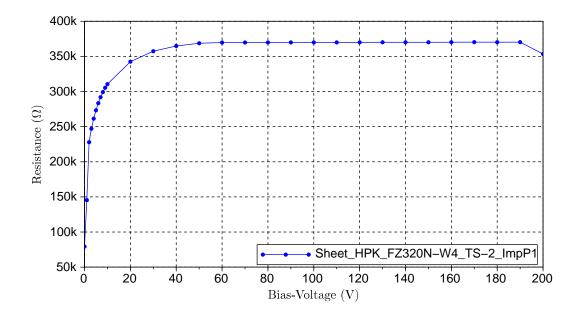

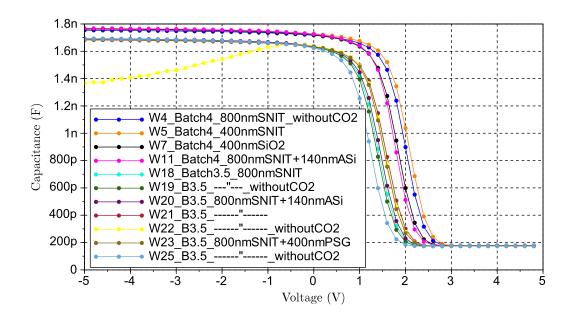

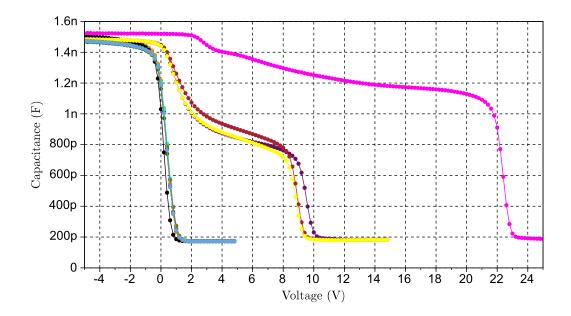

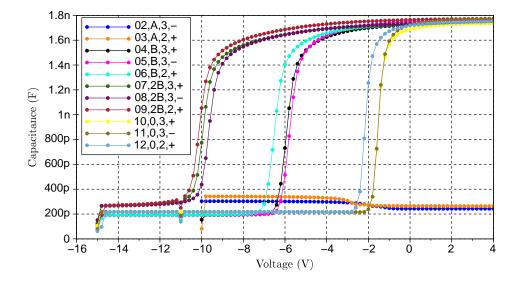

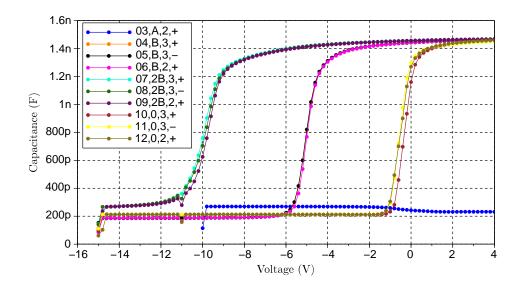

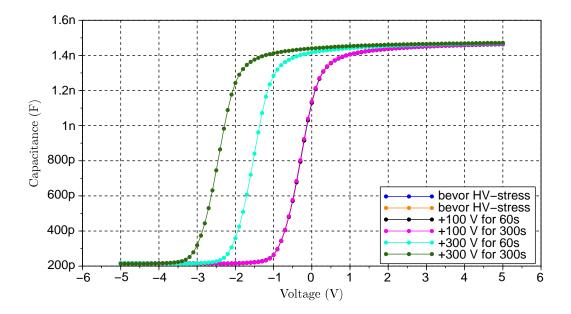

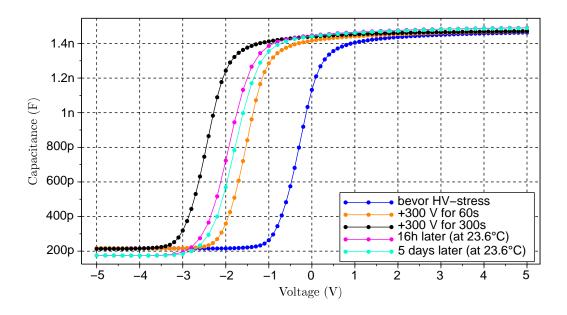

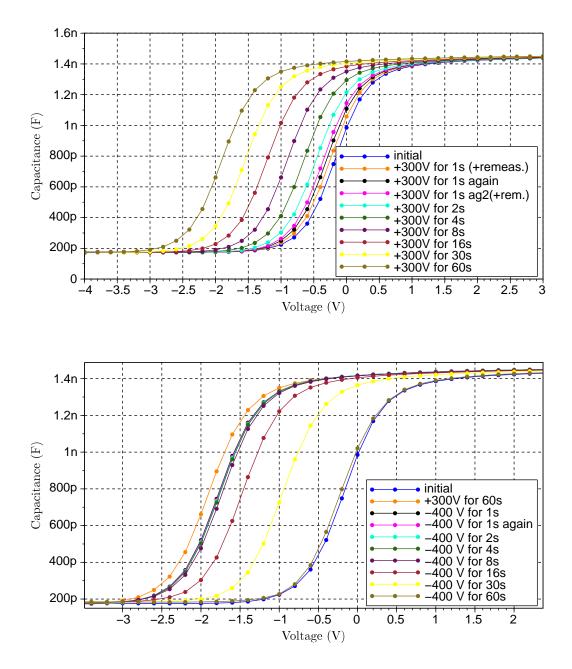

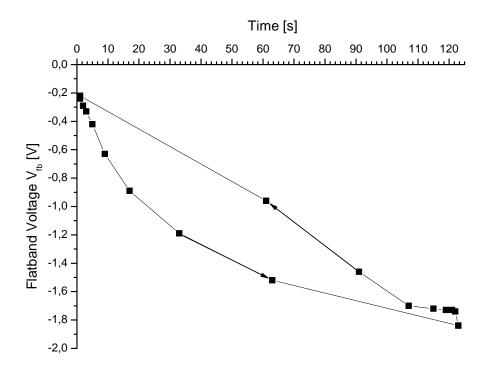

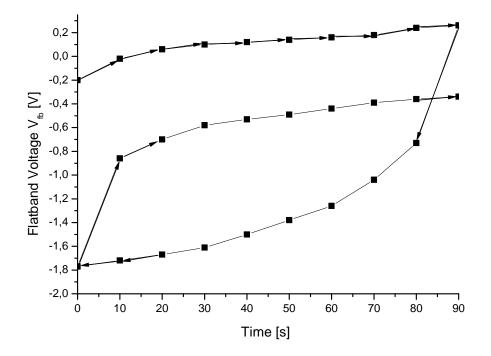

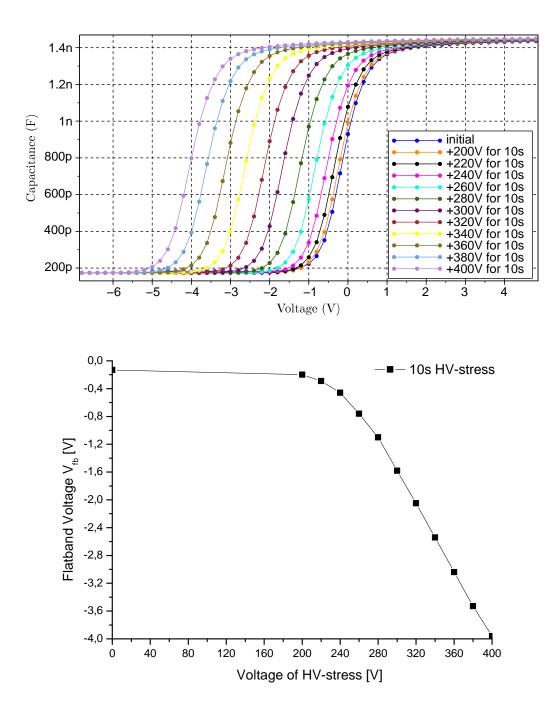

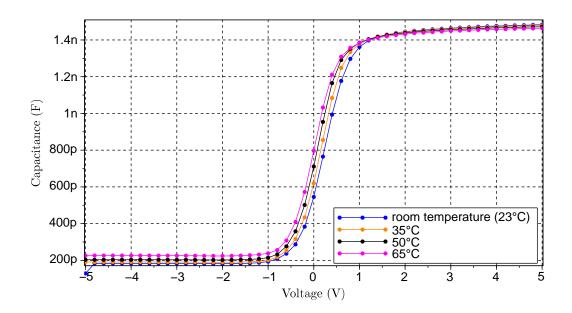

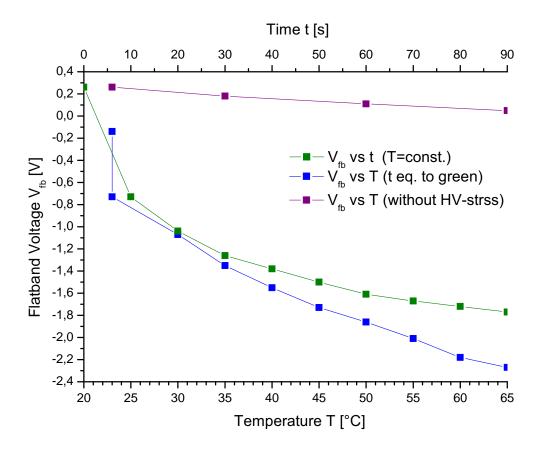

### 4.7 Sheet resistances