The approved original version of this thesis is available at the main library of the Vienna University of Technology.

FAKULTÄT FÜR !NFORMATIK Faculty of Informatics

# Neural Models For Monitoring and Control

## with Applications in Automotive Domain

## PhD THESIS

submitted in partial fulfillment of the requirements for the degree of

## **Doctor of Technical Sciences**

within the

## Vienna PhD School of Informatics

by

Dipl.Ing. Konstantin Selyunin

Registration Number 01228206

to the Faculty of Informatics

at the TU Wien

Advisor: Univ.Prof. Dipl.-Ing. Dr.rer.nat. Radu Grosu Second advisor: Asst.-Prof. Dr. Ezio Bartocci Industrial Co-advisor: Dr. Thang Nguyen

External reviewers: Prof. Dr. Martin Leucker. Universität zu Lübeck, Germany. Assc. Prof. Ph.D. Yliés Falcone. Univ. Grenoble Alpes, France.

Vienna, 9<sup>th</sup> October, 2017

Konstantin Selyunin

Radu Grosu

## **Declaration of Authorship**

Dipl.Ing. Konstantin Selyunin 1040 Wien, Treitlstr. 3, CPS Group

I hereby declare that I have written this Doctoral Thesis independently, that I have completely specified the utilized sources and resources and that I have definitely marked all parts of the work - including tables, maps and figures - which belong to other works or to the internet, literally or extracted, by referencing the source as borrowed.

Vienna, 9<sup>th</sup> October, 2017

Konstantin Selyunin

## Acknowledgements

This thesis represents the accomplishments of my academic-research career at the Cyber-Physical-Systems Group of the TU Wien. Looking back to the past five years of my PhD Study with the Vienna PhD School of Informatics and the CPS Group, I see this time as a fantastic experience which broadened and deepened my expertise in cyber-physical systems, robotics, neural models, runtime monitoring, and in computer science in general.

I would like to thank Prof. Hannes Werthner, Prof. Hans Tompits, Prof. Andreas Steininger and Ms. Clarissa Schmid for organizing and smoothly running the "Vienna PhD School of Informatics", a program that gave me the opportunity to conduct the research at the Faculty of Informatics of the TU Wien. During my studies Ms. Clarissa Schmid and Ms. Gerda Belkhofer helped me in organizational and administrative issues. I would like to equally express my gratitude to Prof. Radu Grosu and Dr. Ezio Bartocci that agreed to work with me, accepted me at the Cyber-Physical Systems Group, and guided me through my research and studies. I am also thankful to Dr. Thang Nguyen who became my industrial co-advisor, and gave his valuable advice and guidance to shape my work in a way to be applicable in automotive electronic industry.

Furthermore, I thank all my colleagues from the Cyber-Physical-Systems Group and the PhD School for the fruitful discussions, support and collaboration. Notably, I appreciate Denise Ratasich, Alena Rodionova, Stefan Jaksic, Anna Lukina, Haris Isakovich, Bernhard Frömel, Christian Hirsch, and Aysylu Gabdulkhakova for their help in shaping my research and inspiring discussions that contributed to the results presented in this thesis.

I am also grateful for the financial support from the Vienna PhD School of Informatics and the project HARMONIA (845631), funded by a national Austrian grant from FFG (Österreichische Forschungsförderungsgesellschaft) under the program IKT der Zukunft.

My special thanks are devoted to my family and friends, in particular to Lyudmila Selyunina, Ekaterina Lashmanova, Rostislav Zabolotnyi, Maryna Kostikova, Ivan Zykov, and Roland Mayr who helped me to overcome difficulties and supported me emotionally, shared with me adventures, organized vacations, and helped to recharge.

## Abstract

Cyber-physical systems (CPS), which incorporate physical as well as computational components, are a grand challenge of academia and industry in terms of their development, verification, and maintenance. In order for CPS to serve their purpose and ultimately make human lives safer, easier, more enjoyable, and convenient, both academia and industry needs to develop new methods for control and monitoring of such systems. Neural models are a very promising and far looking direction for the design of CPS controllers and monitors. In this thesis we first show how neural models can be applied in CPS control to quantify the uncertainty of the system. We then present how digital spiking neural model, called TrueNorth, can be used in the runtime monitoring of temporal-logic specifications for mission-critical systems. In order to be able to deliver not only a qualitative verdict, but also to reason in a quantitative way, we propose an approach for modeling arithmetic-functions with spiking neurones, and implement neural monitors for (signal) temporal logic specifications based on circular convolution.

In the applied part of the thesis we demonstrate how runtime monitoring can speed up the verification and validation phases in automotive electronic development. We identify phases where runtime monitoring can facilitate both pre- and post-silicon verification and testing. To build runtime monitors that are capable of keeping up with the speed of the physical sensors, we developed an approach to convert formalized requirements to hardware monitors, which are then synthesized in an FPGA. The results of this work enable long-term requirements evaluation and foster reuse of the monitors from pre- to post-silicon verification phases using high-level synthesis. We illustrate our approach by formalizing, creating hardware monitors, and evaluating the results in the lab environment for electrical and timing requirements of the industrial SENT and SPC protocols.

## Contents

| A        | bstra | $\mathbf{ct}$                                      | vii            |

|----------|-------|----------------------------------------------------|----------------|

| Co       | onter | nts                                                | ix             |

| Li       | st of | Figures                                            | xi             |

| Li       | st of | Tables                                             | $\mathbf{xiv}$ |

| Tł       | nesis | Publications                                       | xvi            |

| 1        | Intr  | oduction                                           | 1              |

|          | 1.1   | Motivation                                         | 2              |

|          | 1.2   | Problem Statement                                  | 3              |

|          | 1.3   | Research Questions                                 | 4              |

|          | 1.4   | Scientific Contributions                           | 5              |

|          | 1.5   | Structure of the Work                              | 7              |

| <b>2</b> | Bac   | kground                                            | 11             |

|          | 2.1   | Neural Models                                      | 11             |

|          | 2.2   | Runtime Verification                               | 15             |

|          | 2.3   | Automotive Electronic Development                  | 18             |

| 3        | Stat  | te of the Art Analysis                             | <b>21</b>      |

|          | 3.1   | Related Work on CPS Control with Neural Models     | 21             |

|          | 3.2   | Related Work on Neural Models in Monitoring        | 23             |

|          | 3.3   | Related Work on Runtime Verification in Automotive | 25             |

|          | 3.4   | Related Work on Protocol Verification              | 27             |

| 4        | Neu   | ral Models for Control & Quantifying Uncertainty   | <b>31</b>      |

|          | 4.1   | Preliminaries                                      | 33             |

|          | 4.2   | Key Components of Neural Programs                  | 34             |

|          | 4.3   | Bayesian-Network Learning                          | 38             |

|          | 4.4   | Case studies                                       | 41             |

|          | 4.5   | Summary                                            | 49             |

| <b>5</b>     | Net          | ral Models for Qualitative Monitoring                 | 51       |

|--------------|--------------|-------------------------------------------------------|----------|

|              | 5.1          | Qualitative Monitoring with the TrueNorth model       | 52       |

|              | 5.2          | Neural Temporal Testers                               | 55       |

|              | 5.3          | Case Study and Experimental Results                   | 59       |

|              | 5.4          | Summary                                               | 61       |

|              |              | v                                                     |          |

| 6            | Net          | ral Models for Quantitative Monitoring                | 63       |

|              | 6.1          | Neuron and Synapse Modeling                           | 64       |

|              | 6.2          | Computations with Neural Models                       | 66       |

|              | 6.3          | Neural filters as temporal logic monitors             | 70       |

|              | 6.4          | Summary                                               | 73       |

| 7            | Bur          | ntime Monitoring in Automotive Electronic Development | 75       |

| •            | 7.1          | Use Case 1: Runtime Monitors in Simulation            | 78       |

|              | $7.1 \\ 7.2$ | Use Case 2: Runtime Monitors for Lab Evaluation       | 78<br>78 |

|              |              |                                                       |          |

|              | 7.3          | Case Study: Automotive Sensor Interface               | 79       |

|              | 7.4          | Summary                                               | 80       |

| 8            | Ind          | ustrial Case studies and Evaluation                   | 83       |

|              | 8.1          | Timed Regular Expressions                             | 84       |

|              | 8.2          | Formalization of the SENT and SPC Protocols           | 85       |

|              | 8.3          | Runtime Monitoring with Recovery                      | 92       |

|              | 8.4          | Runtime Monitoring of SENT and SPC protocols          | 95       |

|              | 8.5          | Summary                                               | 99       |

| 9            | Cor          | clusions and Future Work                              | 101      |

| 0            | 9.1          | Summary of Contributions                              | 101      |

|              | 9.2          | Critical Reflections                                  | 102      |

|              | 9.3          | Research Questions Revisited                          | 102      |

|              | 9.4          | Future Work                                           | 100      |

|              | 5.4          |                                                       | 104      |

| G            | lossa        | ry                                                    | 105      |

| A            | crony        | vms                                                   | 107      |

| Bi           | bliog        | graphy                                                | 111      |

| $\mathbf{A}$ | open         | dix: SENT/SPC Monitoring                              | 131      |

|              |              | allation Instructions                                 | 131      |

|              |              | $\operatorname{prial}$                                | 134      |

|              |              | T/SPC Monitoring: Details                             | 142      |

|              |              | avioral Code and Test data                            | 147      |

|              |              | Study                                                 | 149      |

| C,           | irria        | ulum vitæ                                             | 151      |

| $\mathbf{U}$ | 1110         | urum viva                                             | TOT      |

## List of Figures

| 1.1          | Thesis contributions                                                                                                                                | 6               |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1.2          | Outline of the thesis                                                                                                                               | 9               |

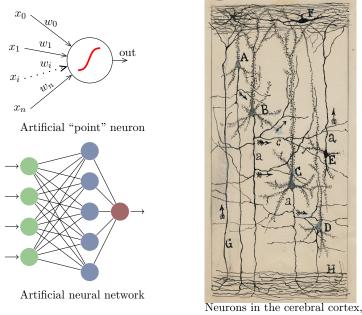

| 2.1          | Biophysical and Artificial neurons: a Bird's Eye View                                                                                               | 13              |

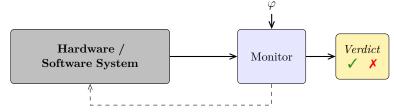

| 2.2          | Runtime Monitoring: System's overview                                                                                                               | 16              |

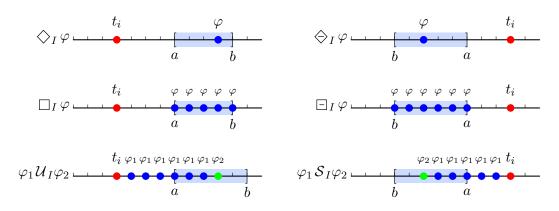

| 2.3          | STL past and future temporal operators                                                                                                              | 18              |

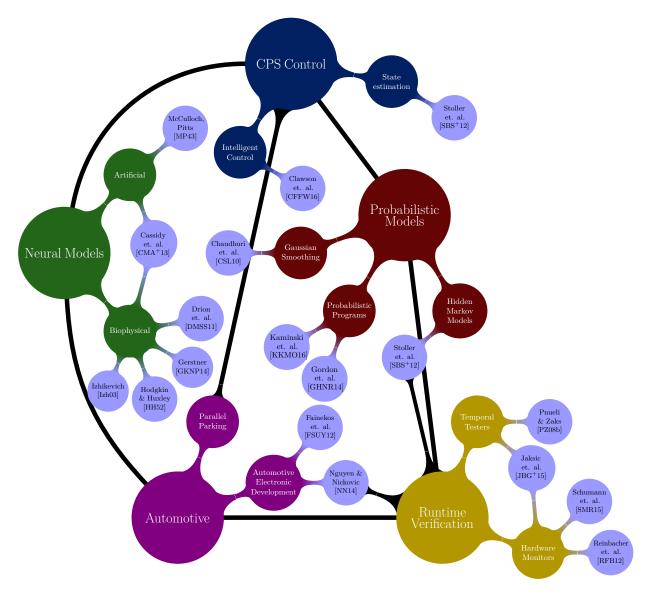

| 3.1          | High-level overview of the related work                                                                                                             | 29              |

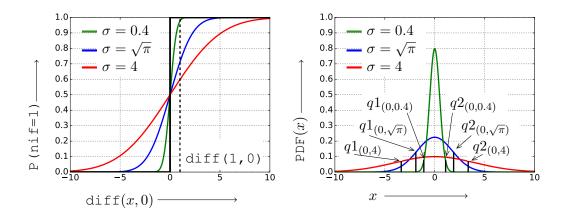

| 4.1          | Left plot: "Soft" (colored lines) and "hard" (bold black line) thresholds; Right                                                                    | 26              |

| 4.2          | plot: PDFs and the quantiles for $x = 1$ and $a = 0$                                                                                                | $\frac{36}{37}$ |

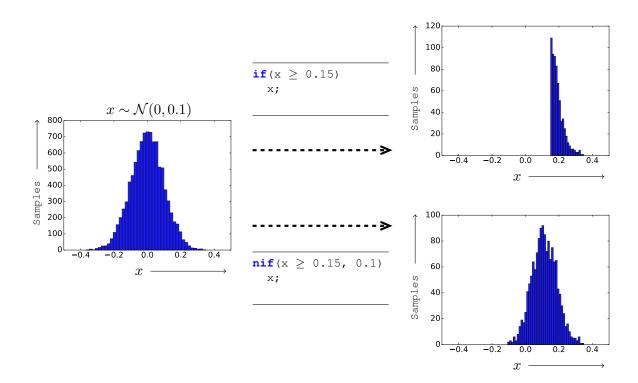

|              | Passing RVs through conditions                                                                                                                      | 37<br>39        |

| 4.3          | Gaussian Bayesian Network for parking                                                                                                               |                 |

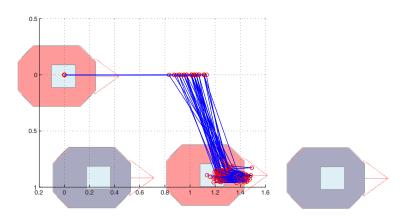

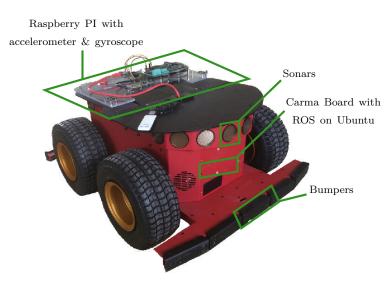

| $4.4 \\ 4.5$ | Example trajectories for the parking task                                                                                                           | $39 \\ 42$      |

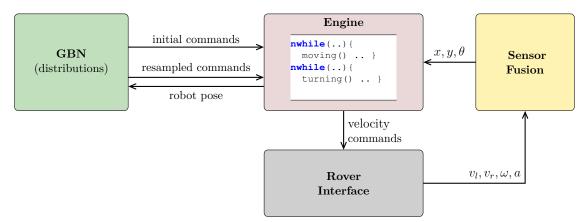

| 4.5<br>4.6   | Experimental platform: Pioneer RoverParking system architecture                                                                                     | 42<br>43        |

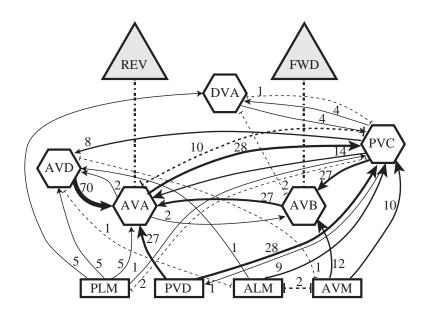

| 4.0<br>4.7   | Tap withdrawal circuit of C. Elegans                                                                                                                | 45<br>45        |

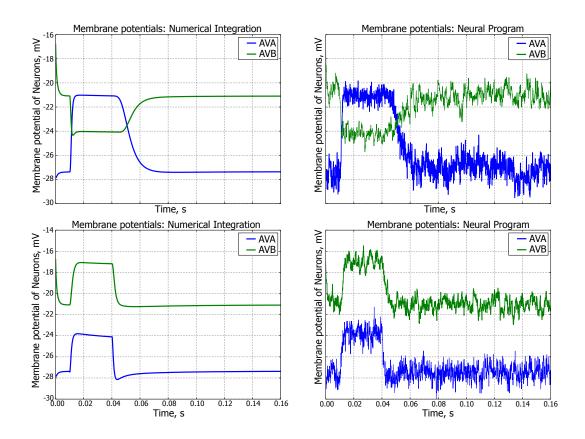

| 4.8          | Deterministic simulations of potentials of AVA and AVB neurons (left); stochas-                                                                     | 40              |

| 4.0          | tic simulations using nif condition (right)                                                                                                         | 47              |

| 4.9          | Controller for parallel parking as a neural circuit                                                                                                 | 48              |

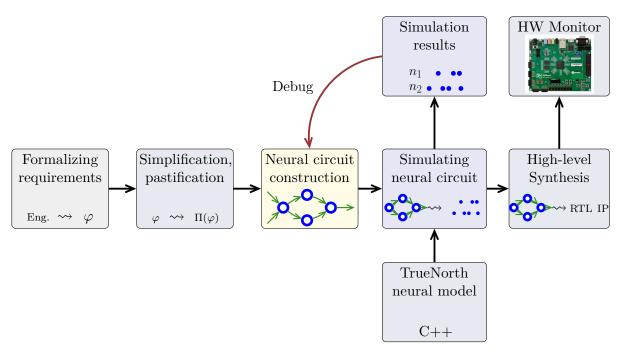

| 5.1          | Neural Monitor Generation Flow                                                                                                                      | 53              |

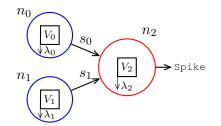

| 5.2          | Two input TrueNorth circuit                                                                                                                         | 56              |

| 5.3          | Neural Temporal Testers                                                                                                                             | 58              |

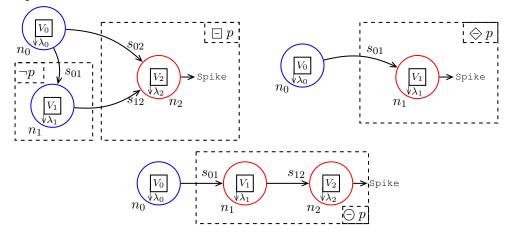

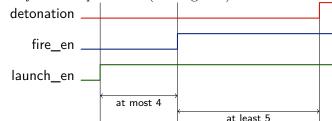

| 5.4          | Missile timing property specification                                                                                                               | 60              |

| 5.5          | Missile monitor: simulation results                                                                                                                 | 60              |

| 5.6          | Experimental setup (see [osc] for oscillograms)                                                                                                     | 61              |

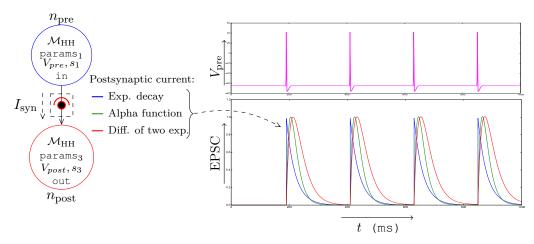

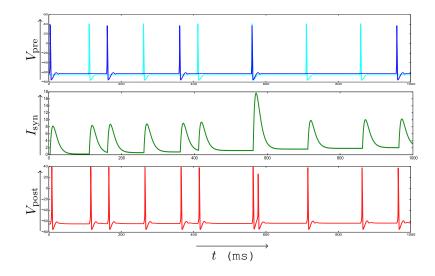

| 6.1          | Normalized EPSC in response to pre-synaptic action potentials $(V_{\rm pre})$ .                                                                     | 65              |

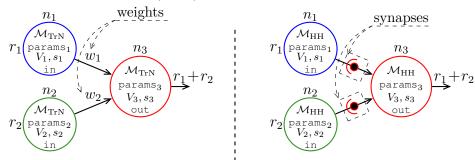

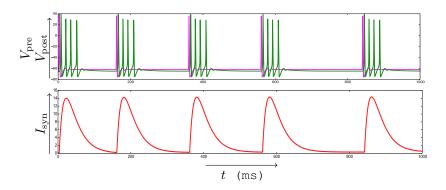

| 6.2          | Neural models for computations on spike rates                                                                                                       | 66              |

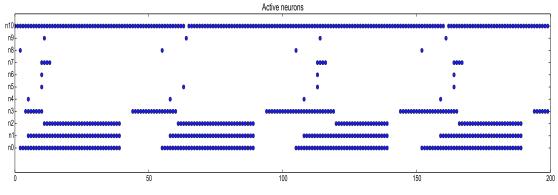

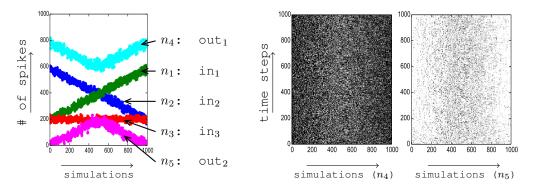

| 6.3          | Addition in the spike rates using the TrueNorth model                                                                                               | 67              |

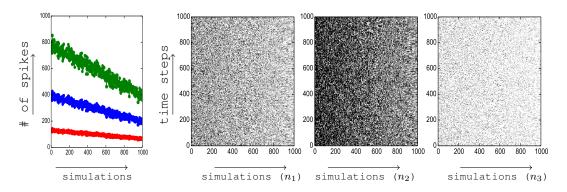

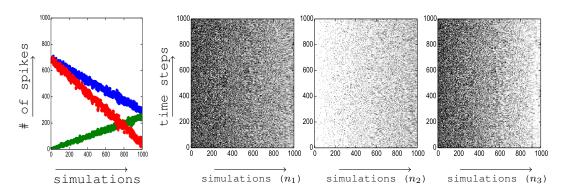

| 6.4          | Addition of spike rates with the Hodgkin-Huxley model                                                                                               | 68              |

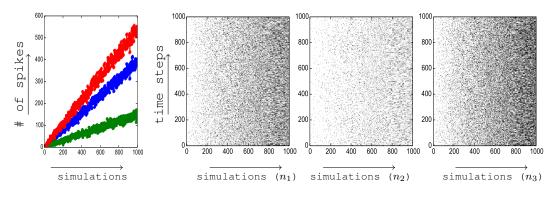

| 6.5          | Constant multiplication and division of the spike rates with the TrueNorth                                                                          |                 |

|              | model: $2 \cdot \text{blue} = \text{green}, \frac{1}{3} \cdot \text{blue} = \text{red} (n_1 - \text{blue}; n_2 - \text{green}; n_3 - \text{red})$ . | 69              |

|              |                                                                                                                                                     |                 |

| $\begin{array}{c} 6.6 \\ 6.7 \end{array}$ | Constant multiplication of the spike rates with the Hodgkin-Huxley model<br>Subtraction in the spike rates with the TrueNorth model: blue – green = red                                                                      | 69       |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                           | $(n_1 - \text{blue}; n_2 - \text{green}; n_3 - \text{red}). \ldots \ldots$                                                                                    | 70       |

| 6.8                                       | Computing $min/max$ using the TrueNorth model: $r_4 = max(r_1, r_2) + r_3$ , and $r_5 = min(r_1, r_2) - r_3$                                                                                                                 | 70       |

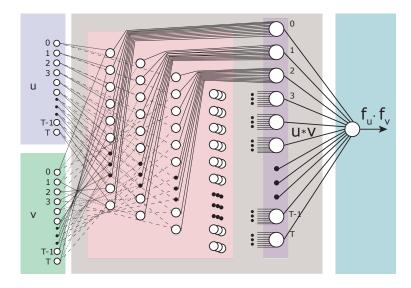

| 6.9                                       | Circular Convolution using TrueNorth: the Circuit                                                                                                                                                                            | 71       |

| 6.10                                      |                                                                                                                                                                                                                              | 72       |

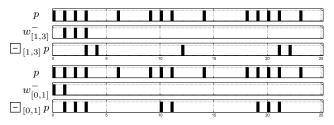

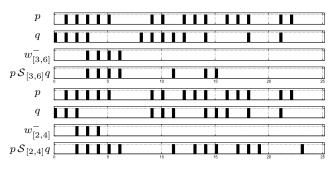

| 6.11                                      |                                                                                                                                                                                                                              | 73       |

|                                           | Computing $\mathcal{D}_{[a,b]}$ using TrueNorth                                                                                                                                                                              | 74       |

|                                           |                                                                                                                                                                                                                              | 70       |

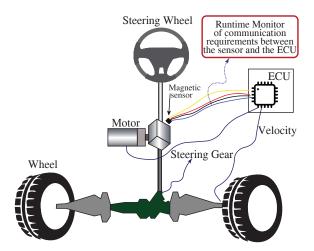

| 7.1                                       | Electronic power steering application                                                                                                                                                                                        | 76       |

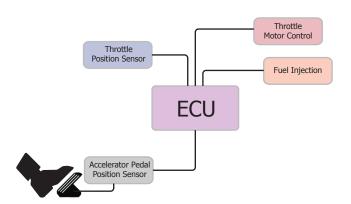

| 7.2                                       | Electronic Throttle Control for Engine Management                                                                                                                                                                            | 77       |

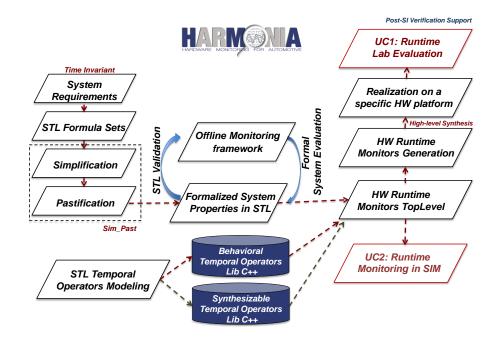

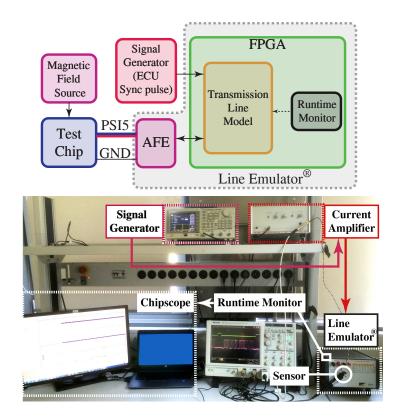

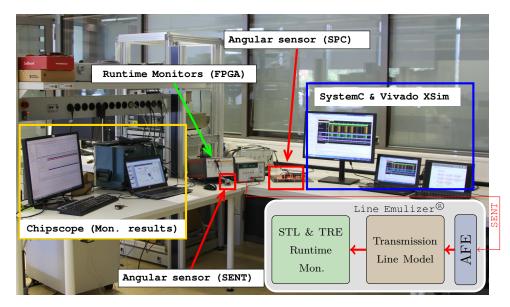

| $7.3 \\ 7.4$                              | Runtime Monitoring Generation Flow                                                                                                                                                                                           | 78<br>80 |

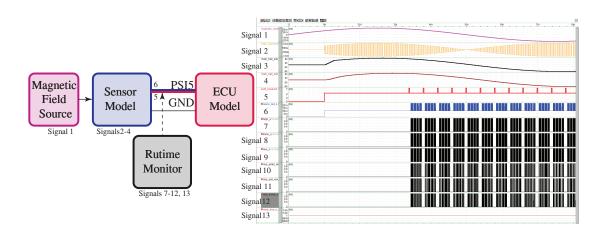

| $7.4 \\ 7.5$                              | Runtime Monitor in Hardware: Lab Setup                                                                                                                                                                                       | 80<br>81 |

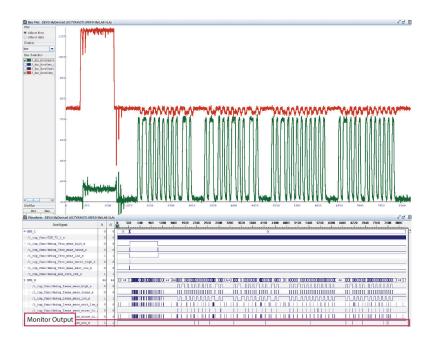

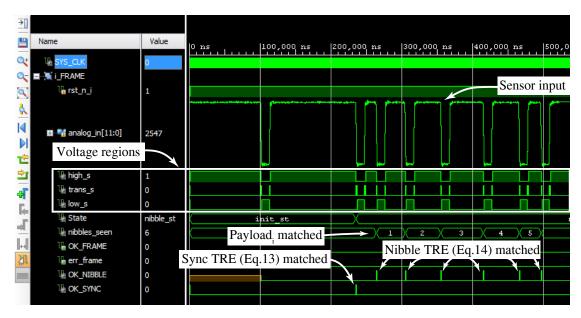

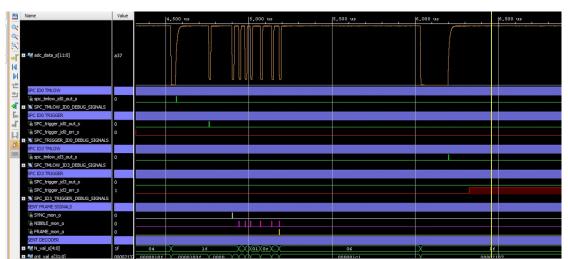

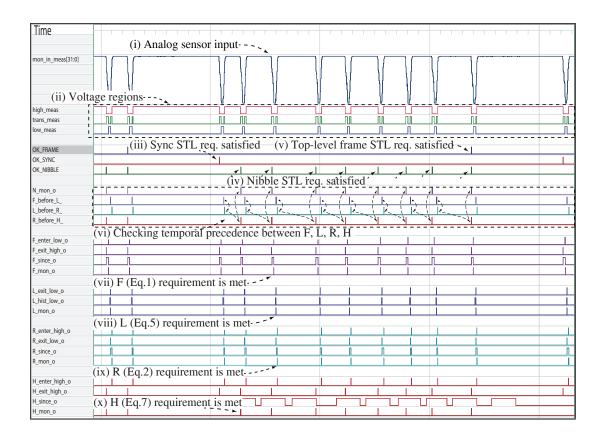

| 7.0 $7.6$                                 | Runtime Monitor in Hardware: Lab Setup                                                                                                                                                                                       | 82       |

| 1.0                                       | Runtime Momitor in Hardware. Chip Scope Results                                                                                                                                                                              | 02       |

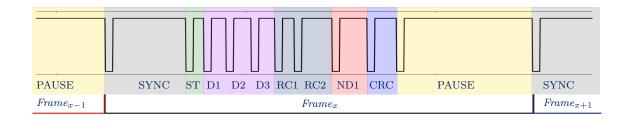

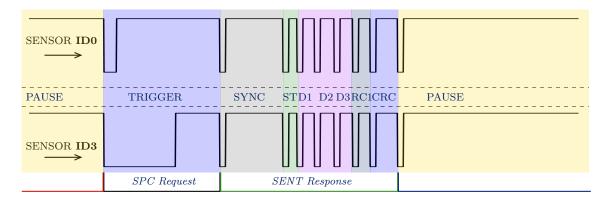

| 8.1                                       | A SENT frame starts with a synchronisation pulse (SYNC), followed by a status nibble (ST), data nibbles (D1, D2, D3), rolling counters (RC1, RC2), bit inverse of D1 (ND1), cyclic redundancy check (CRC), and finishes with |          |

|                                           | an optional pause.                                                                                                                                                                                                           | 86       |

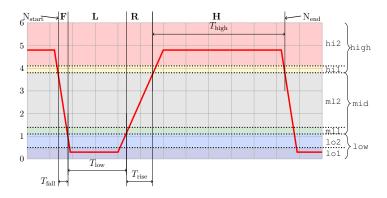

| 8.2                                       | SENT nibble pulse: A pulse starts $(N_{\text{start}})$ with a falling edge F, followed by                                                                                                                                    |          |

| 8.3                                       | a low region L, followed by a rising edge R, followed by a high region H<br>SPC bus mode: Specification signal for two sensors: ID0 and ID3 – communi-                                                                       | 86       |

|                                           | cation starts with the trigger pulse, which is followed by a response from a                                                                                                                                                 | 07       |

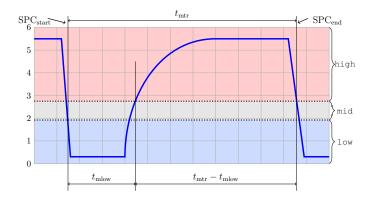

| 8.4                                       | sensor                                                                                                                                                                                                                       | 87       |

| 0.4                                       | which encodes the sensor id, followed by a high region $\ldots$                                                                                                                                                              | 88       |

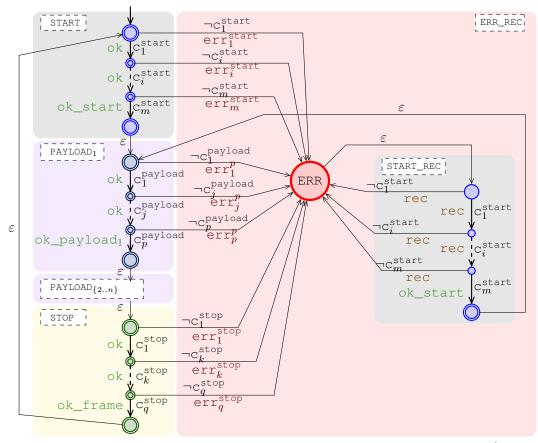

| 8.5                                       | Monitoring an asynchronous serial protocol with recovery <sup>1</sup>                                                                                                                                                        | 93       |

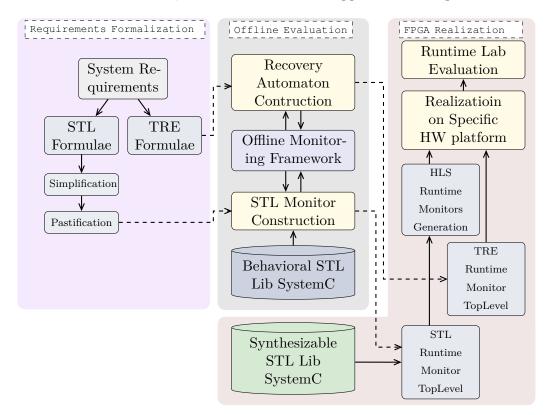

| 8.6                                       | Monitor Generation                                                                                                                                                                                                           | 95       |

| 8.7                                       | Runtime Monitoring of the SENT: Hardware Setup                                                                                                                                                                               | 97       |

| 8.8                                       | Runtime TRE monitoring: Vivado functional simulation                                                                                                                                                                         | 98       |

| 8.9                                       | Runtime monitoring of SPC protocol                                                                                                                                                                                           | 99       |

|                                           | Runtime monitoring of the STL requirements                                                                                                                                                                                   | 100      |

| 0.20                                      |                                                                                                                                                                                                                              |          |

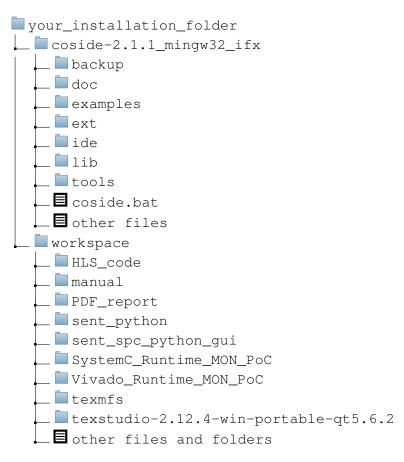

| 1                                         | Installation Directory Structure                                                                                                                                                                                             | 132      |

| 2                                         | Workspace launcher                                                                                                                                                                                                           | 133      |

| 3                                         |                                                                                                                                                                                                                              | 133      |

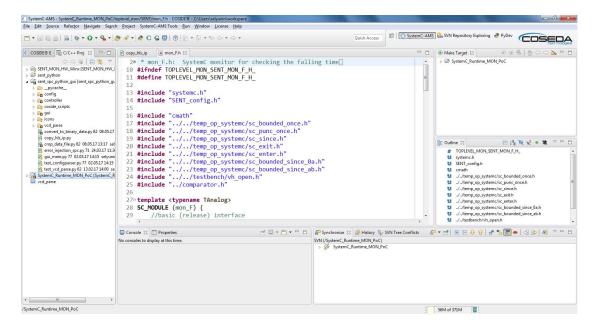

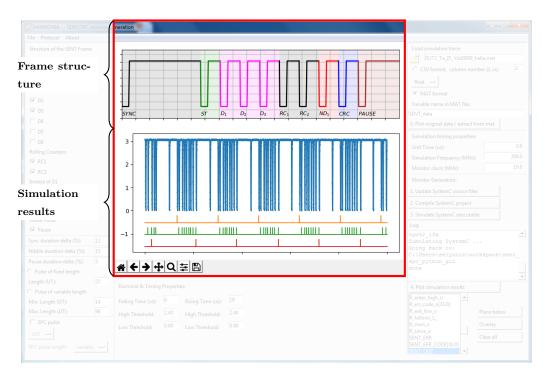

| 4                                         | COSIDE GUI                                                                                                                                                                                                                   | 135      |

| 5                                         | Expanded `sent_spc_python_gui' project                                                                                                                                                                                       | 135      |

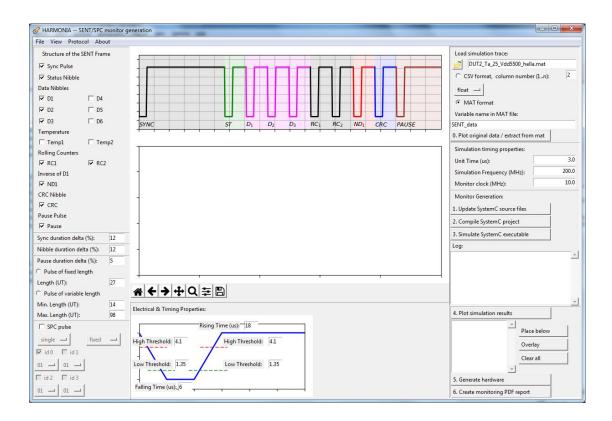

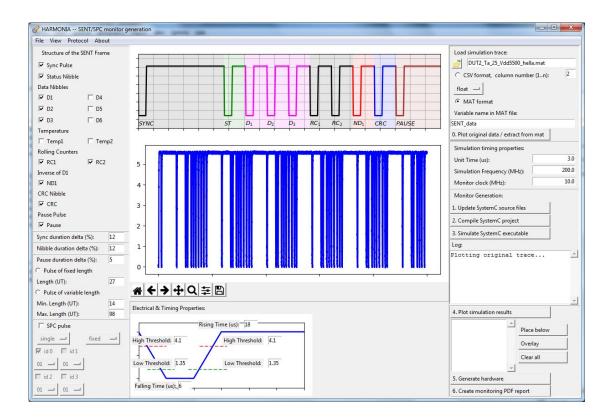

| 6                                         | Launching the SENT/SPC Monitor GUI                                                                                                                                                                                           | 136      |

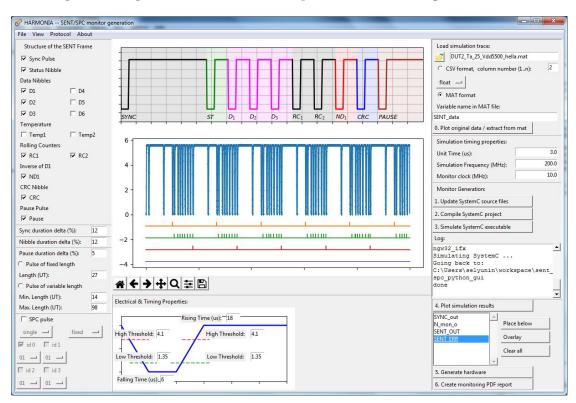

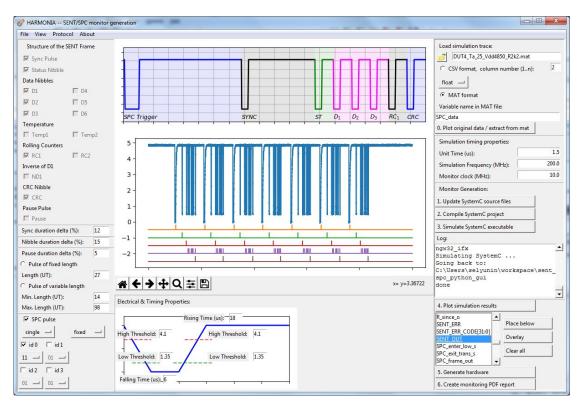

| 7                                         | SENT/SPC Monitor GUI                                                                                                                                                                                                         | 136      |

| 8                                         | Applying `sent_config_Vdd5500_DUT2.ini' configuration                                                                                                                                                                        | 137      |

| 9                                         | Plotting original sensor data                                                                                                                                                                                                | 138      |

| 10 | Plotting signals from the monitor_dump.vcd                                 | 139 |

|----|----------------------------------------------------------------------------|-----|

| 11 | Loading the SPC configuration                                              | 141 |

| 12 | SPC Monitoring Results                                                     | 142 |

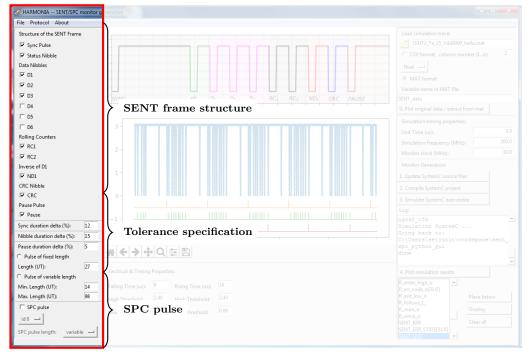

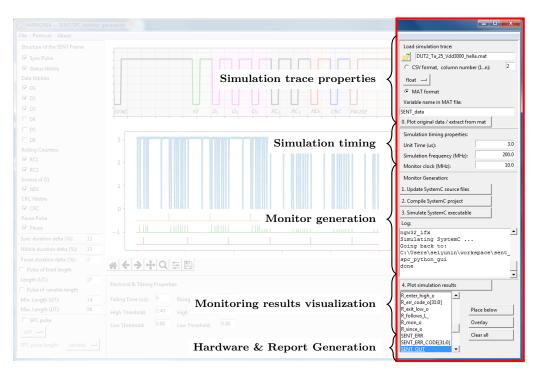

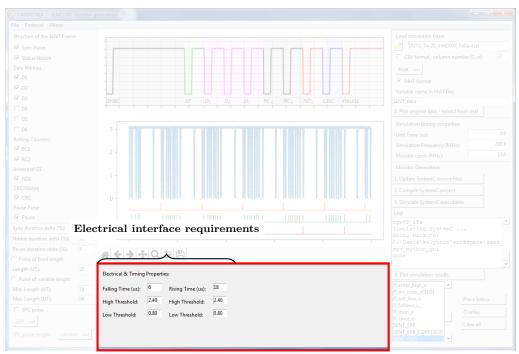

| 13 | Specifying the parameters of the protocol and defining the frame structure | 144 |

| 14 | Right panel: elements for the monitor generation                           | 145 |

| 15 | Plot panel                                                                 | 146 |

| 16 | Bottom panel                                                               | 146 |

| 17 | Excerpt from the monitoring report                                         | 147 |

| 18 | Example configuration file                                                 | 148 |

| 19 | Behavioral code structure                                                  | 149 |

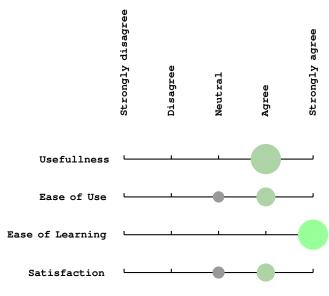

| 20 | Summary of user study results                                              | 150 |

## List of Tables

| 4.1 | BN variances and coefficient dependences      | 45 |

|-----|-----------------------------------------------|----|

| 4.2 | Comparison of simulation results              | 48 |

| 5.1 | Neural Parameters of Logical Operators        | 57 |

| 5.2 | Neural Temporal Testers                       | 59 |

| 5.3 | Missile monitor: implementation results       | 61 |

| 6.1 | Parameters of neuron and synapse model        | 65 |

| 6.2 | Parameters of the TrueNorth Model             | 71 |

| 8.1 | SENT Requirements in natural language         | 87 |

| 8.2 | SPC Requirements in natural language          | 89 |

| 8.3 | STL Monitors Generation: FPGA & HLS resources | 99 |

## **Thesis Publications**

The thesis is based on the author's work published in scientific conferences and workshops. For quick-reference and brevity reasons, these core papers, which build the foundation of the thesis, are listed here once and for all, and will not generally be explicitly referenced again. Parts of these papers are contained in the thesis in verbatim.

- Konstantin Selyunin, Denise Ratasich, Ezio Bartocci, Md. Ariful Islam, Scott A. Smolka, Radu Grosu: "Neural Programming: Towards Adaptive Control in Cyber-Physical Systems." In Proceedings of the 54th IEEE Conference on Decision and Control (CDC 2015), Osaka, Japan. pp.6978-6985, December 15-18, 2015.

- Konstantin Selyunin, Thang Nguyen, Ezio Bartocci, Dejan Nickovic, and Radu Grosu: "Monitoring of MTL Specifications With IBM's Spiking-Neuron Model." In Proceedings of the 19th Design, Automation and Test in Europe Conference and Exhibition (DATE 2016), Dresden, Germany. pp.924–929, March 14-18, 2016.

- Konstantin Selyunin, Thang Nguyen, Ezio Bartocci, Radu Grosu: "Applying Runtime Monitoring for Automotive Electronic Development." In Proceedings of the 16th International Conference on Runtime Verification (RV 2016), Madrid, Spain. pp.462-469, September 23-30, 2016.

- Thang Nguyen, Ezio Bartocci, Dejan Nickovic, Radu Grosu, Stefan Jaksic, Konstantin Selyunin: "The HARMONIA Project: Hardware Monitoring for Automotive Systems-of-Systems." In Proceedings of the 7th International Symposium on Leveraging Applications of Formal Methods, Verification and Validation: Discussion, Dissemination, Applications (ISoLA 2016) Corfu, Greece. pp.371-379, October 10-14, 2016.

- Konstantin Selyunin, Thang Nguyen, Andrei Daniel Basa, Ezio Bartocci, Dejan Nickovic, Radu Grosu: "Applying High-Level Synthesis for Synthesizing Hardware Runtime STL Monitors of Mission-Critical Properties." In Proceedings of the 13th Design and Verification Conference and Exhibition (DVCon 2016), San Jose, CA, USA. pp.1-8, February 28-March 3, 2016.

- Konstantin Selyunin, Ramin M, Hasani, Ezio Bartocci, Radu Grosu: "Computing with Biophysical and Hardware-efficient Neural Models." In Proceedings of the 14th International Work-Conference on Artificial Neural Networks (IWANN 2017), Cadiz, Spain. pp.535-547, June 14-16, 2017.

- Konstantin Selyunin, Stefan Jaksic, Thang Nguyen, Christian Reidl, Udo Hafner, Ezio Bartocci, Dejan Nickovic, Radu Grosu: "Runtime Monitoring with Recovery of the SENT Communication Protocol." In Proceedings of the 29th International Conference on Computer Aided Verification, (CAV 2017), Heidelberg, Germany. pp.336-355, July 24-28, 2017.

## CHAPTER

## Introduction

Herbert A. Simon [Sim96] outlined the fundamental difference between the natural sciences and the "sciences of the artificial" as follows: While a natural scientist starts from *the physical world* and tries to build a model of the phenomenon under study, possibly by revising the model, an engineer starts with the *model* and tries to realize the model in the physical world, possibly revising realizations.

Despite of this fundamental difference, and dating back to Leonardo da Vinci's flying machine in the "*Codex on the Flight of Birds*" (c.a. 1505, itself very much inspired by the bat's wings), inspiration from nature greatly affected technological development. Unlike market economy, nature is not under strict time-to-market pressure, and crafts its solutions by millions of years of evolution. This makes its results optimal with respect to energy usage, environmental adaptation, perception, and robustness to failure.

Employing solutions from nature resulted in scientific disciplines such as biomimicry[Ben02] and bionics[NW15]. Their goal is to study the application of ideas from biological systems in the engineering context, with prominent examples such as hair sensors for flow control [GS12], running-dog robots from Boston Dynamics [RBNP08], or self-cleaning nano-materials [GT11] (inspired by the lotus flower). These successes encourage the application of principles mastered by nature in Cyber-Physical Systems (CPS), too.

CPS [BG12] pose grand challenges in terms of managing system complexity, ensuring safety, and developing optimal solutions. The large number of interconnected devices, and the huge amount of data generated by their components, result in considerable obstacles for processing and reasoning about CPS. In this thesis, we are primarily concerned with the *cyber* component of CPS. This has to be reliable, fault tolerant, and satisfy strict safety requirements. Although formal verification [BK08] and model-based design [BKKS12], are in principle capable of providing a formal-correctness proof for a software component of the cyber part, these methods have limitations when applied to real-world industrial problems, due to the sheer complexity of the associated systems.

#### 1.1 Motivation

From the "sciences of the artificial" perspective, it is vital to understand how the principles adopted by nature can be applied in the context of the "design sciences".

An animal's brain, which is a very prominent area of investigation [GKNP14, DA05], is an excellent example of the astonishing progress of research: From the early beliefs (e.g. when nerve cells were considered to be pipes transferring the "spirituous liquor", William Croone, 1667, [Ros32]), to the birth of the neuroscience in 1888 by Ramón y Cajal [She15], and to state-of-the-art methods like the connectomics [Per14], optogenetics [HQB+09] and brain-machine interfaces [CLC+03], we are witnessing nowadays a much deeper understanding of the brain's function: From the micro scale perspective (e.g. release of neuro-transmitters and change of ionic concentrations during generation of an action potential), to the macro-scale perspective (e.g. modelling the cortical activity of a macaque's brain [PWD<sup>+</sup>12]). This is all possible due to the incredible research progress in neuroscience.

These advancements have important implications: Neurons are now seen as plastic devices [Doi07], constantly adapting and changing their function, according to the external stimuli. Starting from the paper of McCulloch & Pitts [MP43], the advances in brain research provide a source of inspiration for different fields of computer science. The concept of a neuron, as a universal computing device that is capable to dynamically adapt to the external changes, is particularly promising for designing solutions for CPS.

As CPS operate in dynamic uncertain environments, where computational components are tightly coupled with the physical world, it is important to develop controllers for CPS that are capable of taking into account the uncertainty of the environment, together with the prior knowledge about the system. From the computational perspective, CPS are regarded as reactive systems [AILS07]. For them, it is vital not only to provide control inputs, but also to provide mechanisms for monitoring properties of interest at runtime, in order to capture and report violations, and to trigger recovery mechanisms.

To leverage neuronal functional/structural plasticity, it is essential to understand how models of neurons (the universal information processing elements in biological systems), can be used from the "sciences of the artificial" perspective, in the context of CPS.

From a practical point of view, it is necessary to cope with the complexity and the sheer amount of data generated by the CPS. For example, in the automotive electronic-development domain, which is responsible for producing the CPS components (consider the angular sensors based on the Hall effect and their associated controllers) it is of utter importance to develop methods that speed up the testing process, and eliminate errors at the early stages of the development cycle. Manufacturers strive for additional safety barriers to capturing violations during product verification phases, aim for automated solutions and reduced workload for an engineer, during the design and testing process.

### 1.2 Problem Statement

The aforementioned research/applications challenges uncover a broad range of questions that have to be solved. To narrow down the scope of the thesis, we outline the main research problems in this section, and specify a list of research questions in Section 1.3.

From a control perspective, we need to address the decisions that have to be made under uncertainty in CPS. We aim to use neural models that are capable quantify the uncertainty, and give on average "smooth" control decisions.

From a monitoring perspective, it is necessary to develop methods allowing the use of neural circuits as monitors, to check the properties of CPS at runtime. In recent years, we have seen the emergence of new, brain-inspired computer-hardware architectures [SMN11, WHTvS14, CMA<sup>+</sup>13]. We target the application of state-of-the-art spiking neural-architecture models, for monitoring temporal properties of CPS. We do this for both qualitative and quantitative properties, with the same neural model, by reconfiguring its parameters. This approach leverages the functional plasticity of the neural models.

To cope with the system's complexity, and to provide an additional safety mechanism, it is important in many practical scenarios, to show at runtime, that the system has not violated its safety requirements. Runtime verification [Leu12], a light-weight state-ofthe-art verification technique, treats the system under investigation as a black-box, and reports system's conformance to formal requirements in a current run. In the automotive electronic-development domain, it is necessary to speedup the testing process for sensing products. In particular, runtime verification solutions are of great interest, since they are non-intrusive, and in principle, capable to check in real-time, the specification conformance of sensing blocks at various abstraction layers, or collect and report violations.

The main theoretical goal of this thesis, is to study neural models for the control and monitoring of CPS. The main practical goal of this thesis is to build efficient runtime monitors in hardware and software, that are applicable to the state-of-the-art components of CPS, in particular, of the automotive electronic-development domain CPS.

These research-statement goals imply that the solutions to be developed within the scope of this thesis, should possess the attributes of:

- 1. *Simplifying controller design in CPS* while taking into account both, the uncertainty about the environment, and prior knowledge about the system;

- 2. Unifying qualitative- and quantitative-monitoring techniques for checking temporal system-properties, by exploiting plasticity of neural models;

- 3. *Speeding up product testing* by allowing the runtime monitoring of the CPS under investigation, in both hardware and software.

Solutions with the aforementioned attributes are attractive from two perspectives. First, they facilitate the design of CPS controllers as well as CPS monitors by using neural

models as a common basis. Second, they allow to introduce additional safety mechanisms, which are not only capable to catch errors (during several phases of product development), but also speed up the testing process of CPS (e.g. angular sensing product).

#### 1.3 Research Questions

The research work that is conducted within the scope of this thesis is mainly aligned around the following research questions:

#### **RQ 1:** How does one design controllers for CPS using neural models?

The ability of neurons to adapt to an uncertain and dynamically changing environment through structural and functional plasticity [DPM<sup>+</sup>11], renders their models as a very natural candidate for CPS controller design. CPS controllers also operate in an uncertain and dynamically changing environment, and they also need to adapt.

Efficient designs should consider controllers that are capable to adapt through plasticity (i.e. learning), while taking into account uncertainty and prior experience. It is therefore very important to understand how nature's principles, discovered by neuroscience, can be mapped to CPS controller design. One of them is for example, the availability of a measure, quantifying controller's uncertainty. This can be used whenever deciding which action to take. From a practical point of view, the measure has to be representable through programming constructs, that are familiar to software engineers.

Summarizing, the aim of this work is to develop adaptive CPS controllers inspired by neural models. These should quantify their uncertainty when taking decisions. Moreover, they should aim towards smooth average decisions, thus increasing their robustness.

## **RQ 2:** How does one perform qualitative and quantitative monitoring of temporal CPS properties, at runtime, when using neural models?

The evolution of CPS observable outputs as well as the one of CPS inferred states, must satisfy the CPS requirements specification (RS). Deviations from these RS might manifest errors in the system, which could lead to failures with possibly catastrophic consequences (e.g. if the CPS is safety-critical [Kop11]). Monitoring the evolution of the CPS in real-time, allows to catch important deviations from the RS early on, and opens the possibility to bringing the CPS back to a safe state. Temporal logics [Lon89] allow to formally define an RS, as the set of all permissible CPS evolutions in time. Thus, they provide a formal notation for RS compliance.

CPS with mixed-critical properties [BD13] require not only a qualitative "pass-fail" verdict, but also a quantitative verdict, measuring the amount of satisfaction/violation of the RS. This could signify, for instance, a level of service degradation, for non-safety-critical requirements. Quantitative interpretations of the RS assess the distance from satisfaction/violation. This can be viewed as an additional robustness metric.

The use of neural models for monitoring CPS allows to unify the qualitative and quantitative measurement of temporal logic properties. Moreover, neurons as universal atomic components for building monitors, allow to apply both functional and structural changes, in order to configure the best circuit producing the monitoring verdict.

#### **RQ 3:** How does one speed up testing within automotive electronic development?

From the industrial point of view, e.g. for Infineon [Inf17], which is an automotive Tier 2 supplier, it is important to reduce CPS testing time and engineering effort. Developing solutions that meet such needs, by introducing safety mechanisms capable of capturing errors in different phases of the design process, is of utmost importance. They allow CPS suppliers to meet strict safety standards (e.g. ISO 26262 [iso11]).

Although testing is an accepted industrial practice, it involves substantial manual work. Moreover, it is by no means complete, as it is mainly performed over short fragments of recorded data. Together with post-silicon verification, testing accounts up to 60-70% of total development time [NN16]. Shortening this while also increasing coverage is crucial.

Since monitors are capable to check the requirements at the system's runtime, they bring substantial potential for reducing the amount of data stored. They help identifying the relevant portions of data to be saved (as opposed to post-processing of the recorded data). Runtime monitoring also provides a way for checking classes of requirements at different abstraction layers. Hence, it is necessary to identify how runtime monitoring can be incorporated in the existing design practice in the automotive electronic industry.

## **RQ 4:** What are the necessary steps to building efficient runtime monitors in hardware that are applicable in the industrial state-of-the-art practice?

For runtime monitoring to be accepted in the existing industrial practice, it needs to be expressive enough, in order to formalize the RS of real products, provide sufficient performance to keep up with the speed of monitoring systems (enable real-time data processing), facilitate easy reconfiguration, and present monitoring results in a comprehensive way.

Current industrial practice relies on RSs that are written using natural language and graphics. An engineer has to interpret these requirements, and develop the corresponding tests. In order to eliminate ambiguities in RS interpretation, it is possible to specify the temporal evolution of a system in a suitable variant of temporal logic, which as an added benefit, allows the automatic translation of the RS to the monitoring code.

It is very important to develop a methodology enabling the translation of formal RSs to hardware-monitor implementations, capable of giving their verdicts in real time.

#### **1.4** Scientific Contributions

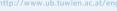

This section gives more details about the scientific contributions of this thesis. Figure 1.1 is a "birds-eye-view" of the work, which is then elaborated in more detail.

#### Contribution 1: We develoed a design method for adaptive CPS control, which is based on either artificial or biological neural models. We show the

Figure 1.1: Thesis contributions

utility of (neural) programs which contain branching statements that are capable to incorporating and quantifying uncertainty. The method consists of two steps. In the first step, one writes a program (a controller) skeleton, whose sigmoidal stochastic branching statements leave their mean and variance unspecified. In the second step, one learns the proper means and their associated variances in a supervised fashion, from (good) teacher's traces.

This adaptive-controller design method has been validated, by developing and testing a parallel-parking controller for a Pinoneer 3-AT rover, which is available in our CPS laboratory. We used artificial neural-networks models for the learning purpose, as well as biological neural-networks models based on the C.elegans nematode's neurons.

Details on applying neural models in the design of adaptive CPS controllers are discussed in Chapter 4. Contribution 1 has been published in [SRB<sup>+</sup>15].

Contribution 2: We developed both qualitative and quantitative techniques for CPS monitoring, based on spiking-neurons networks models. Spiking neural networks [Vre03], which were pioneered by the analysis of the action potential of the giant squid by Hodgkin and Huxley [HH52], have now became the classical biophysical model of a neuron. A digital spiking neural model, as proposed by [CMA<sup>+</sup>13], allows efficient realizations of neural circuits in the digital state-of-the-art hardware.

We developed a method that allows to create a neural circuit and configure its neurons to perform runtime monitoring of temporal logic properties of analog signals. The circuit receives the input signal and outputs the monitoring verdict for a temporal logic specification. For quantitative evaluation we show how to perform fundamental arithmetic operations over spike rates using neural models. These operations are the necessary components for computing quantitative semantics of a temporal logic specification at runtime. If the entire (or sufficiently large portions of the) signals are given in advance, we show how a temporal logic semantics, defined using convolution, can be utilized for constructing neural circuits that are capable to compute the monitoring verdict.

Details on qualitative monitoring using spiking neurons are discussed in Chapter 5. Quantitative monitoring with spiking neurons are presented in Chapter 6. The results of Contribution 2 have been published in [SNB<sup>+</sup>16a, SHR<sup>+</sup>17].

**Contribution 3:** We applied and validated our runtime verification techniques in the automotive electronic-development domain. As discussed in Section 1.3, it is very important to develop methods that are capable to speed up CPS testing. We analyzed the design and production phases of an automotive sensing component, showed how runtime verification can be applied, and what benefits and limitations it brings. Our results show that during the testing process, runtime monitoring can be applied in the pre-silicon concept-design phase, as well as in the post-silicon verification phase, to check the requirements conformance of the manufactured sensing component.

The non-intrusive nature of runtime monitoring allows one to use it as an additional safety mechanism and integrate it into existing design practice. Details on applying runtime monitoring for automotive electronic development are discussed in Chapter 7. The results of Contribution 3 have been presented in [SNBG16, NBN<sup>+</sup>16].

Contribution 4: We formalized the industrial-strength protocols Single Edge Nibble Transmission (SENT) and Short PWM Code (SPC), automatically generated monitors out of this formalization, and checked the conformance with these protocols of an Infineon's angular-sensing component at runtime. To show the applicability of the results on the industry-relevant case study, we illustrate the process of runtime monitoring requirements for the SENT and SPC protocols.

For these protocols we implemented the full flow from the analysis of existing documentation, formalization of requirements classes, creating simulation environment and violation scenarios, software/hardware implementation of runtime monitors and testing monitors on the real test data in industrial environment. For a subclass of asynchronous serial protocols we also defined a procedure to construct runtime monitors that are capable (i) to recover after violations, (ii) collect and report error types to the user.

Electrical and timing requirements of SENT and SPC protocols were formalized using two formalisms and compared in terms of resources, speed and conciseness of the formalized specifications. Details on runtime monitoring of the SENT and SPC protocols are discussed in Chapter 8. Contribution 4 was published in [SJN<sup>+</sup>17, SNB<sup>+</sup>16b].

#### 1.5 Structure of the Work

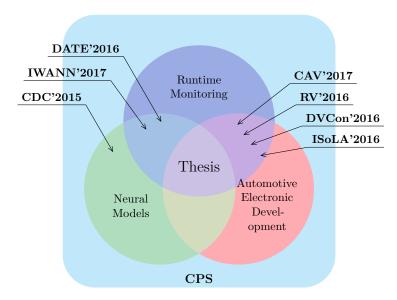

The remainder of the thesis is organized as follows (see also Figure 1.2):

- Chapter 2 provides background information, and introduces the terminology and concepts used throughout the thesis. In particular, it reviews types of neural models, runtime monitoring, and testing processes in automotive electronic development.

- Chapter 3 gives an overview of the existing scientific and industrial work, that is related in some way to the contributions of this thesis.

- Chapter 4 describes neural programs, how to define their skeleton, and how to learn means and variances of their branching statements. It also shows the use of stochastic branching in quantifying the uncertainty of adaptive CPS controllers.

- Chapter 5 focuses on performing qualitative monitoring of CPS using a digital spiking neural model, and presents a method for constructing a monitoring circuit, which computes a verdict of the temporal-logic properties.

- Chapter 6 discusses quantitative monitoring using digital spiking neural models, and the method for configuring neurons to perform computations over spike rates.

- Chapter 7 elaborates on the applications of runtime monitoring in the very rich and important domain of automotive electronic development.

- Chapter 8 discusses the formalization of the SENT and SPC protocols as industrial case studies, and the use of this formalization in runtime verification. It also provides details on recovery after detecting violations in asynchronous serial protocols.

- Chapter 9 concludes the thesis, offers a critical summary of the work, and discusses future research directions that emerged as a consequence of this work.

Figure 1.2: Outline of the thesis

# CHAPTER 2

## Background

This chapter summarizes information about well-established concepts and methodologies that form the basis of the thesis and are essential for understanding the remaining part of the work. In Section 2.1 we elaborate on neural models, emphasizing similarities and fundamental differences between artificial and biological neurons. The aforementioned neuronal models will then be used in Chapters 4, 5, and 6 for designing controllers and monitors for the *cyber* part of CPS. We then recap basic notions of the runtime monitoring in Section 2.2, discuss the specification languages for defining properties and online monitoring approaches. We will then use neural models for performing runtime monitoring in Chapters 5 and 6. In Section 2.3 we provide the details about the testing process in automotive electronic development, and then build up on this information in Chapters 7 and 8 when talking about industry-relevant parts of the work.

#### 2.1 Neural Models

Although the history of the scientific development of neuron theory can be reconstructed since the XIX century with the fundamental breakthroughs of Camillo Golgi [She15], Ramón y Cajal [LMBA06], Hodgkin & Huxley [HH52], and many other scientists [She15] who contributed both theoretically and experimentally to the development of the neuroscience, in the field of informatics neurons start attracted significant attention from the 1943 paper of McCulloch & Pitts [MP43], where neuronal "all-or-none" activity was discussed as as a property for building logical calculus. Since then, advances in artificial neural networks are showcased by their successful applications in different types of tasks, e.g., classification (handwritten digits recognition [LBD+90]), speech [GrMH13] and image recognition [SZ14], artistic style transfer [GEB15] and many others [DY14]. The main conceptual differences of the models and architectures of biophysical and artificial neurons and networks are discussed in subsequent section.

#### 2.1.1 Biophysical and Artificial Neurons Models and Networks

As already mentioned in Chapter 1, from biophysical point of view the primary concern is to discover "how things are", while to solve practical problems in the field of computer science it is necessary to understand "how things ought to be". Both perspectives see neurons as non-linear information processing elements and the interaction of these elements allows to solve complex tasks. In this section we refer to a neuron with a radial-basis activation function as an "artificial neuron"; we also refer to a generalization of Hodgkin & Huxley [HH52] model (which is not limited to sodium and potassium ionic channels, e.g. [DMSS11]) as a "biophysical model". Formally, the artificial neuron can be described as a tuple:  $(\mathbf{x}, \mathbf{w}, f, \text{out})$ , where  $\mathbf{x} = \{x_0, x_1, \ldots, x_n\}$  and  $\mathbf{w} = \{w_0, w_1, \ldots, w_n\}$ are respectively *n*-dimensional vectors of inputs and weights; an activation function  $f : \mathbb{D}_1 \to \mathbb{D}_2$  defines neural computation and maps inputs to an output,  $\mathbb{D}_2$  is usually normalized to [0, 1]; out  $\in \mathbb{D}_2$  is a variable that holds the computation result:

$$out = f(\mathbf{w}^T \mathbf{x}). \tag{2.1}$$

The biophysical neural model is a tuple  $(V, s, I_{in}, \mathbf{g}, \mathbf{params}, \mathbf{f}_g, \mathbf{E}_i, C_m)$ , where V is the membrane potential of the cell; s is the spike output;  $I_{in}$  represents input stimulus current;  $\mathbf{g} = \{g_1, g_2, \ldots, g_m\}$  is a vector of conductances for each ionic channel  $g_i$ , (also leak channel); a tuple  $\mathbf{params} = (\mathbf{params}_1, \ldots, \mathbf{params}_m)$  holds auxiliary parameters for describing temporal evolution of the conductances  $g_i$ ; a vector  $\mathbf{f}^{(g)} = \{f_1^{(g)}, \ldots, f_m^{(g)}\}$  defines functions  $f_i^{(g)}$  :  $\mathbf{params}_i \to \mathbb{R}$  that capture specific time dependence of each ionic channel,  $\mathbf{E}_i = \{E_1, \ldots, E_m\}$  represents potentials of each ionic channel;  $C_m$  is a membrane capacitance. Membrane potential of a neuron is then described by the ordinary differential equation (ODE):

$$C_m \frac{dV}{dt} = I_{in} - \sum_{i=1}^m g_i f_i^{(g)} \left( \mathbf{params}_i \right) \left[ V - E_i \right].$$

(2.2)

The output of an artificial neuron (see Figure 2.1 and Equation 2.1) is a value of the activation function, computed over a weighted sum of inputs, while the output of a neuron in a biological simulation is a rapid depolarization of the membrane potential called *action potential* (or *spike*), which can be seen as an "all-or-none" event. The neuron outputs a spike when the following two conditions are met: (i) the membrane potential from the Equation 2.2 is above the pre-defined threshold (usually in the range 40-60 mV), (ii) the membrane potential reaches the local maximum.

The artificial model introduces two simplifications: (i) the model is untimed and memoryless (i.e., no time dependence in Equation 2.1), while for the biophysical model (Equation 2.2) the temporal evolution of the membrane potential is an essential property; (ii) each artificial neuron has access to the state of the parent's neuron (i.e., the "out" variable), while in the biophysical model the state ( the membrane potential) and output (spike) are decoupled: communication between neurons happens via spikes, which lead to neuro-transmitter release and opening of ionic channels that, in turn, cause the flux of currents in the membrane. The synaptic transmission in the artificial neuron is modelled as excitatory (or inhibitory) weights, values of which are obtained during training phase, while in the biophysical model the synapses have much more intricate structure [DA05]. In the aforementioned biophysical model the synaptic transmission can be represented via introducing additional ionic channels (e.g. Ca [Lli99]) or as an external stimulus current  $I_{in}$ .

Neurons in the cerebral cortex, Ramon y Cajal Image credit: Instituto Cajal del Consjo Superior de Investigaciones Científicas, Madrid/CSIC

Figure 2.1: Biophysical and Artificial neurons: a Bird's Eye View

#### The Hodgkin-Huxley Neuron Model

A seminal model presented by Hodgkin and Huxley in [HH52] can be seen as a refinement of the biophysical model described in Section 2.1.1. The model qualitatively describes the dynamics of the membrane potential as a function of activation and deactivation of sodium and potassium ionic channels. Membrane potential is defined as an ODE, which relates ionic currents of the neuron of giant squid axon (for the detailed description the reader is referred to [HH52]). The membrane potential is computed as follows [HH52]:

$$C_m \frac{dV_m}{dt} = I_{in} - (\bar{g}_K n^4 (V_m - E_K) + \bar{g}_{Na} m^3 h (V_m - E_{Na}) + \bar{g}_L (V_m - E_L)), \qquad (2.3)$$

where the vector of conductances (see Section 2.1.1)  $\mathbf{g} = \{g_{Na}, g_K, g_L\}$  comprises of sodium, potassium and leak conductances;  $\mathbf{E} = \{E_{Na}, E_K, E_L\}$  represents reversal

potentials of the sodium, potassium and the leak channels respectively; **params** =  $(\{m, h\}_{Na}, \{n\}_K, \{1\}_L)$  are auxiliary voltage-gated variables to describe channels activation and deactivation; the temporal dependence of the parameters is guided by the functions  $\mathbf{f}^{(g)} = \{\{m, h\} \xrightarrow[Na]{} m^3h, \{n\} \xrightarrow[K]{} n^4, 1 \xrightarrow[L]{} 1\}.$

The model possesses the following important properties: (i) the internal state (membrane potential) and output are decoupled; (ii) at each time step neuron integrates its membrane potential together with the inputs; (iii) the membrane potential stabilizes at the resting value in absence of external stimuli; (iv) the frequency of outputting spikes is governed by the refractory period, during which no spike can be initiated.

To make the model computationally efficient for large-scale simulations and applicable in the context of "design sciences" various simplifications and abstractions has been proposed. For instance, the programmable reset of the integration after emitting action potential is described by nonlinear integrate-and-fire models [Izh04, GKNP14]. To be able to run this type of model on the *cyber* components of CPS, careful complexity reduction is required: avoiding computationally-expensive operations in digital hardware (e.g., floating point operations). In the subsequent section we describe the spiking neural model that is suited for implementation on the digital hardware, while still possessing the necessary properties of the biophysical model.

#### The TrueNorth Neuron Model

The TrueNorth model is proposed by IBM [CMA<sup>+</sup>13] and describes a digital spiking neuron, which follows the properties of the biophysical model introduced in previous section. All the parameters of the model are either integer or boolean values, which facilitates the implementation of the model in digital hardware (e.g., in Field-Programmable Gate Array (FPGA)). The model performs three computational steps: (i) the synaptic integration of the current membrane potential and the incoming inputs from the pre-synaptic neurons; (ii) the leak integration to model the dissipation of energy in absence of input; (iii) the "threshold-fire-reset" defines the reset behavior of the model upon reaching the thresholds. The model has deterministic and stochastic modes; we review the deterministic part of the TrueNorth model below. For an extended explanation, the reader is referred to [CMA<sup>+</sup>13].

**Synaptic Integration** is the first computational step where every neuron sums up the products of its inputs  $A_i(t)$  and weights  $s_{ij}$ . Every input is enabled by a flag  $w_{ij}$ . The result is added to its previous membrane potential  $V_j(t-1)$ . Although in the original model the maximum number of inputs bounded by 255, we drop this restriction and assume that every neuron has a configurable  $N \in \mathbb{N}$  number of inputs (the original assumption comes from the chip restrictions):

$$V_j(t) = V_j(t-1) + \sum_{i=0}^N A_i(t) w_{ij} s_{ij}$$

(2.4)

14

**Leak Integration** accounts for energy dissipation, self-stimulation, and convergence to an equilibrium in the absence of input. A TrueNorth neuron  $n_j$  can exhibit negative, zero or positive leak  $\lambda_j$ . To express divergent and convergent leak behaviors the leak reverse flag  $\epsilon_j$  can be set: in this case the leak changes its sign with the membrane potential's sign (i.e., when the signs are different, the leak forces  $V_j$  converge to zero) [CMA<sup>+</sup>13]:

$$\Omega_j = (1 - \epsilon_j) + \epsilon_j \operatorname{sgn}(V_j(t))$$

(2.5)

$$V_j(t) = V_j(t) + \Omega_j \lambda_j \tag{2.6}$$

Threshold, Fire, Reset is computed at each time step to generate the binary "allor-none" output (spike or no spike). A neuron  $n_j$  possesses a positive threshold  $\alpha_j$ and a negative threshold  $\beta_j$ . When the membrane potential  $V_j$  exceeds  $\alpha_j$ , the spike is generated, and the membrane potential is reset. The TrueNorth model is extended with three reset modes  $\gamma_j$ : (0) normal, (1) linear, or (2) non-reset. When  $V_j$  falls below the negative threshold  $\beta_j$ , no spike is generated, although the membrane potential is updated depending on the reset mode  $\gamma_j$  and the saturation flag  $\kappa_j$ .

$$if \qquad V_j(t) \ge \alpha_j \tag{2.7}$$

$$\begin{array}{l} \text{SPIKE} \\ \text{(2.8)} \\ \text{(2.8)} \end{array}$$

$$\gamma_{j} = 0 \cdot V_{j}(t) = R_{j}$$

$$\gamma_{j} = 1 : V_{j}(t) = V_{j}(t) - \alpha_{j}$$

$$\gamma_{i} = 2 \cdot V_{i}(t) - V_{i}(t)$$

(2.9)

$$V_j = 2 \cdot V_j(t) = V_j(t)$$

elseif  $V_j(t) < -\beta_j$

(2.10)

if

$$\kappa_j = 1$$

$V_j(t) = -\beta_j$

else

$\gamma_j = 0: V_j(t) = -R_j$

$\gamma_j = 1: V_j(t) = V_j(t) + \beta_j$

$\gamma_j = 2: V_j(t) = V_j(t)$

(2.11)

#### 2.2 Runtime Verification

Runtime verification<sup>1</sup> [Leu12, FZ12, Mal16, BLS11] is a *lightweight* verification technique, which is concerned with a derivation of a verdict for a formally-expressed correctness property  $\varphi$ . To derive a verdict, a monitor is attached to the observable outputs of the system under scrutiny. Figure 2.2 shows a general way of integrating runtime monitoring with an existing system: based on the observations from the Hardware/Software System, a monitor delivers a verdict if a predefined specification is satisfied/violated. Runtime

<sup>&</sup>lt;sup>1</sup>The terms "runtime verification" and "runtime monitoring" are used interchangeably in the thesis

monitoring is non-intrusive and outputs whether the system satisfies its formal requirements. If, on the other hand, violation of the specification triggers control actions from the observer to the system (i.e. the dashed line in Figure 2.2) the observer is seen as a runtime *enforcer* [FMFR11, PFJ<sup>+</sup>13] of the property. The questions about enforcement of formal properties are beyond the scope of the thesis.

Apart from the model checking, which, in general, tries to answer the question whether all possible runs of a hardware or software system adhere to given correctness properties, runtime monitoring [Leu12] tackles a more modest problem: "Does the current execution meet a correctness property ?". Stating the problem that way allows one to ensure that actual implementation (apart from the model) satisfies the correctness properties and employ runtime monitoring as a redundancy mechanism in safety-critical systems.

Figure 2.2: Runtime Monitoring: System's overview

Runtime monitoring usually deals with finite traces, and in online case the traces increase in size with the progress of time [BLS11]. In Section 2.2.2 we review the differences of monitoring hardware and software systems. As the monitor checks the formally defined property  $\varphi$ , in the Section 2.2.1 we discuss formal specification of system's properties.

#### 2.2.1 Specifications of Temporal Properties

Although in state-of-the-art engineering practice still significant fraction of requirements are expressed using combination of natural language and pictures (e.g. the requirements for the SENT and SPC protocols), this way of specifying requirements is subject to ambiguities and mis-interpretations between different communicating parties, and can be a source of potential errors. Languages with formal semantics enable an unambiguous interpretation of the properties in question and facilitate automatic monitor generation.

The relation of predicates over progression of time can be formulated using temporal logics [Lon89]. Linear Temporal Logic (LTL) [MP92] is a well-established formalism that allows to reason about temporal relations of events over infinite traces: (i) the notion of time in LTL is rather logical then physical, (ii) temporal operators are unbounded and in general only a subset of formulae can be evaluated over a finite prefixes – these main motivations fostered extensions of the logic to be applicable in the domain of real-time systems. Metric Temporal Logic (MTL) [OW08] is a real-time extension of LTL, which introduced bounded temporal operators. For analog-mixed signal components (which usually interface *physical* and *cyber* components of CPS) not only the time, but also the input variables are usually in domain of reals. We now consider the extension of MTL that is used in the thesis for specifying temporal behavior of analog-mixed signal systems.

**Signal Temporal Logic (STL)** [DMB<sup>+</sup>12] allows to specify mixed-signal properties of analog/digital components. The syntax of an STL formula  $\varphi$  with past and future operators over a set of boolean variables  $P = \{p_1, \dots, p_m\}$  and real-valued variables  $X = \{x_1, \dots, x_n\}$  is defined by the following grammar [NN14]:

$$\varphi := p | x \sim c | \neg \varphi | \varphi_1 \lor \varphi_2 | \varphi_1 \mathcal{U}_I \varphi_2 | \varphi_1 \mathcal{S}_I \varphi_2, \qquad (2.12)$$

where  $p \in P$ ,  $x \in X$ ;  $c \in \mathbb{Q}$  is a constant;  $\sim$  is a binary relation of the form:  $\{\leq, <, =, >, \geq\}$ ; interval I is of the form [a, b], where  $a, b \in \mathbb{N}$  and  $0 \leq a \leq b$ . An STL specification  $\varphi$  is interpreted over a mixed signal w which is a partial function:  $w : \mathcal{T} \to \mathbb{B}^m \times \mathbb{R}^n$ , where  $\mathcal{T}$  is an interval [0, T) with arbitrary finite value T i.e. a signal is a combination of boolean and real-valued variables that are at most T in length.

The semantics of an STL formula w.r.t. to a signal w at a time point i is defined as follows (where  $w_x[i]$  we denote  $x^{\text{th}}$  component of w):

$$(w,i) \models p \qquad \iff \qquad p[i] = \top$$

(2.13)

$$(w,i) \models x \sim c \qquad \Longleftrightarrow \qquad w_x[i] \sim c \tag{2.14}$$

$$(w,i) \models \neg \varphi \qquad \iff \qquad (w,i) \not\models \varphi \tag{2.15}$$

$$(w,i) \models \varphi_1 \lor \varphi_2 \quad \iff \quad (w,i) \models \varphi_1 \text{ or } (w,i) \models \varphi_2$$

$$(w,i) \models \varphi_1 \mathcal{U}_I \varphi_2 \quad \iff \quad \exists j \in (i+I) \cap \mathbb{T} : (w,j) \models \varphi_2$$

$$(2.16)$$

$$a, i) \models \varphi_1 u_1 \varphi_2 \qquad \longleftrightarrow \qquad \exists j \in (i+1) + 1 : (w, j) \models \varphi_2 \\ and \forall i < k < j, (w, k) \models \varphi_1 \qquad (2.17)$$

$$(w,i) \models \varphi_1 \mathcal{S}_I \varphi_2 \quad \Longleftrightarrow \quad \exists j \in (i-I) \cap \mathbb{T} : (w,j) \models \varphi_2$$

and

$$\forall j < k < i, (w, k) \models \varphi_1.$$

(2.18)

Other STL operators are derived from the definition in a standard way:  $\top = \varphi \vee \neg \varphi$ ;  $\bot = \neg \top$ ; eventually  $\diamondsuit_I \varphi = \top \mathcal{U}_I \varphi$ ; once  $\diamondsuit_I \varphi = \top \mathcal{S}_I \varphi$ ; always  $\Box_I \varphi = \neg \diamondsuit_I \neg \varphi$ ; historically  $\Box_I \varphi = \neg \diamondsuit_I \neg \varphi$ . Temporal operators: eventually, always, once and historically also admit a natural direct definition of their semantics:

$$(w,i) \models \diamondsuit_I \varphi \qquad \Longleftrightarrow \qquad \exists j \in (i+I) \cap \mathbb{T} : (w,j) \models \varphi \tag{2.19}$$

$$(w,i) \models \Box_I \varphi \qquad \Longleftrightarrow \qquad \forall j \in (i+I) \cap \mathbb{T} : (w,j) \models \varphi \tag{2.20}$$

$$(w,i) \models \bigotimes_{I} \varphi \qquad \Longleftrightarrow \qquad \exists j \in (i-I) \cap \mathbb{T} : (w,j) \models \varphi \tag{2.21}$$

$$(w,i) \models \Box_I \varphi \quad \iff \quad \forall j \in (i-I) \cap \mathbb{T} : (w,j) \models \varphi.$$

(2.22)

From now on we consider all STL specifications of the form  $\Box \varphi$ , for brevity of notation we omit the implicit globally operator from the specification if it is clear from the context. Figure 2.3 shows examples of STL future and past temporal operators: at the time instant  $t_i$ , we look either forward (future) or backward (past) over the time axis to evaluate the corresponding operator. Monitoring of the future STL formulae is *acausal*, i.e. the evaluation of the formula at a time instant  $t_i$  might depend on time interval  $t_i + I$ .

Figure 2.3: STL past and future temporal operators

#### 2.2.2 Runtime Monitoring in Software and Hardware

Programming a software application and designing a hardware component involve various technology stacks, and base on different abstraction layers. A view of a program as an abstract entity, which maps inputs to outputs with a termination as a desired property differs from a view of reactive systems, where hardware and software components are tightly coupled with ongoing interaction with the environment. It is usually the case that the speed of processing events is significantly larger in hardware systems, e.g. in Chapter 8 runtime monitor of the sensor interface evaluates the specification at the rate of  $\approx 10^6$  times per second, which cannot be achieved in a software system.

#### 2.3 Automotive Electronic Development

In order to comply with strict safety standards (e.g. ISO 26262 [iso11]) manufacturers in the automotive electronic industry often follow a variant of the V-model [RSB<sup>+</sup>14], where the development process starts with identifying requirements from the Original Equipment Manufacturer (OEM) or Tier 1 partner, designing a concept or a prototype, followed by the implementation and evaluation activities, testing, and possibly iterating back to the design phases.

The Verification and Validation (V & V) phase in this type of design cycle accounts up to 60% of the total development [NN16], and it is necessary to plan V & V activities early on, alongside with first iterations of the concept development. Main activities include [NN14] (i) *pre-silicon* verification, where the proposed solution is simulated, both at component and system level; (ii) *emulation* of the developed hardware on the existing hardware platform to assess implementation bottlenecks before manufacturing; (iii) *post-silicon* verification, where the manufactured component is evaluated – as seen from these activities, the V & V phase in the state-of-the-art industrial environment comprises extensive product testing under different scenarios, including stress conditions – which is different from verification in a sense of model checking where an formal evidence (e.g. a proof) is obtained that the investigated system will not violate safety properties. Although model-based design (e.g. SCADE [MSH<sup>+</sup>13]) can be used to generate C-code alongside with the proof, this approach is not directly applicable in the context of integrated circuit development.

To reduce the V & V time without sacrificing coverage it is important to automate the testing phase for the engineer, and to reuse verification scenarios and tools across validation and verification phases.

# CHAPTER 3

# State of the Art Analysis

This chapter provides an overview and analysis of existing approaches related to the topic of the thesis. Since the presented contributions are closely connected with several research fields, state of the art analysis has the following structure: (i) we first discuss related work concerning adaptive software control of CPS and neural programs in particular; (ii) we then elaborate on applications of neural models for performing qualitative and quantitative runtime monitoring. For the industry-relevant parts of the work we analyze existing approaches for protocol verification, formalization, and hardware runtime monitoring related to the SENT and SPC communication protocols.

# 3.1 Related Work on CPS Control with Neural Models

In order to apply key concepts of neural models in the context of CPS control (Chapter 4) we elaborate on state-of-the-art methods for creating controller software for CPS. Adaptive and intelligent control are established fields in control theory [AW94, AP93], which aim respectively to adjust the parameters of the controller during system's runtime and use methods from Artificial Intelligence (AI) for achieving control objectives. Components of CPS operate in dynamic and uncertain environments, which should be reflected in design of controller software. From the computer science perspective, we aim to incorporate properties of neurons as functional plasticity and learning in the controller design.