http://www.ub.tuwien.ac.at/eng

# Design of Custom ASIC for Radiation Experiments to Study Single Event Effects

### PhD THESIS

zur Erlangung des akademischen Grades

### Doktor/in der technischen Wissenschaften

eingereicht von

### Varadan Savulimedu Veeravalli

Matrikelnummer 1127877

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Ao.Univ.Prof. Dr.techn. Andreas STEININGER

Diese Dissertation haben begutachtet:

(Prof. Dr. Cecilia Metra)

(Prof. Dr. Milos Krstic)

Wien, 12.10.2017

(Varadan Savulimedu Veeravalli)

# Design of Custom ASIC for Radiation Experiments to Study Single Event Effects

### PhD THESIS

submitted in partial fulfillment of the requirements for the degree of

### Doktor/in der technischen Wissenschaften

by

Varadan Savulimedu Veeravalli

Registration Number 1127877

to the Faculty of Informatics at the Vienna University of Technology

Advisor: Ao.Univ.Prof. Dr.techn. Andreas STEININGER

The dissertation has been reviewed by:

(Prof. Dr. Cecilia Metra)

(Prof. Dr. Milos Krstic)

Wien, 12.10.2017

(Varadan Savulimedu Veeravalli)

# Erklärung zur Verfassung der Arbeit

Varadan Savulimedu Veeravalli Treitlstrasse, 3, 2nd Floor, E182/2

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit - einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

## Acknowledgements

First and foremost I would like to express my deepest appreciation to Prof. Andreas Steininger and Prof. Ulrich Schmid for presenting me the opportunity to work in the FATAL project that laid the foundation for this thesis.

Without Prof. Andreas Steininger's guidance, patience and encouragement this dissertation would not have been possible. He provided me the opportunity to work with different international groups to have a deeper understanding about radiation effects in digital circuits. I am grateful for his relentless support in overcoming numerous obstacles that I have been facing through my research.

I would like to thank my colleagues from the Embedded Computing Systems group, Jakob, Alexander, Rameez, Thomas, Robert, and Martin who took part in my activities from long research discussions to spicy luncheons. A special thanks goes to Florian for helping me translate my abstract from English to German. I would like to pay my gratitude to technical staff Karl Malle and Heinz Deinhart for their support. I would especially like to thank the department secretary Traude Sommer for her support and efforts in teaching me German.

I would also like to thank Dr. Cecilia Metra and Dr. Milos Kristic for taking their valuable time to be on my committee.

Last but not the least I would like to acknowledge my wife Nityaa for her continuous support throughout this thesis. She stood by me through thick and thin and I would have never achieved this milestone in my life without her persisting motivation and hard work.

I will never be able to thank everyone enough for making my life at the institute very comfortable and at the same time keeping me sane. I will always cherish the memories I made with you all.

# Dedication

To my wife Nityaa and my children Vaishali and Vishwa without whom this thesis would have been complete three years earlier

## Abstract

Technology scaling has made the transistors increasingly susceptible to radiation particle strikes. As a consequence, particles with lower energy – which are substantially more frequent – can already cause non-destructive single event effects in CMOS circuits. Understanding them is not very straightforward, as there are so many parameters involved along with these effects, like radiation particle strikes' strength, target circuit, path of propagation, and surrounding environment. Our goal in this thesis is to study these effects in digital CMOS circuits and aid construction of efficient radiation tolerant circuits. Firstly, the effectiveness of the existing radiation hardening techniques to particle hits in digital CMOS circuits has been mainly studied in this thesis (under a given set of environmental conditions). We explicitly analyze how the performance of two selected radiation hardening techniques, namely transistor sizing and stack separation, when exposed to particle hits varies with temperature and supply voltage.

We present design aims and concepts as well as implementation results of a digital ASIC that is dedicated as a target for long-term irradiation experiments. Its sole purpose is to study susceptibility to radiation as well as propagation of radiation effects, and aid in understanding the same. The infrastructure should be able to record the SETs, in spite of the need of being tolerant to particle strikes in itself that cannot be avoided in some types of radiation experiments. The problem of devising a suitable infrastructure lies in the partly contradictory requirements, like constrained area, radiation tolerance and good resolution of the location and propagation path of particle hits. This was a major challenge in our thesis.

To analyze *single-event-transient* (SET) sensitivity in digital CMOS circuits we propose an on-chip measurement architecture for various target circuit blocks. We also propose an architecture that allows tracing, generation and propagation of SETs in the Sklansky adder and inverter tree. Our measurement architectures are based on non-rad-hard counters namely, linear feedback shift registers and Muller pipeline based up/down counters. The design evaluation is done by means of comprehensive fault injection experiments, which are based on detailed Spice models of the target circuits in conjunction with a standard double-exponential current injection model for single-event transients (SET). We show that the infrastructure is resilient against double faults, as well as many triple and even higher-multiplicity faults. Together with a probabilistic analysis and fault dictionary we can conclude that the proposed architectures will indeed sustain significant target hit rates, without exceeding the resilience bound of the measurement infrastructure.

Finally to measure SET pulsewidths in any digital circuit a unique on-chip measurement infrastructure is proposed. Unlike the known oscilloscope-based methods, our approach is all-digital: SET durations are measured by the SET-gated counting of pulses generated by a high-frequency ring oscillator, and stored in an up/downcounter array organized in a ring. We carefully elaborate a comprehensive concept for making our infrastructure SEU tolerant, again with the main challenge being to attain a sufficiently high probability of recording useful hits in the target before exhausting the SEU tolerance of the infrastructure. Our key contribution here concerns the protection of the counter array: Rather than resorting to radiation hardening or explicit triple modular redundancy (TMR), we save area by using a novel redundant duplex counter architecture: For a small number of recorded SETs, our architecture implicitly implements TMR, albeit in a way that degrades gracefully for larger numbers of recorded SETs.

We have presented the measurement infrastructure and a detailed pre-fabrication analysis of the circuits hosted in the digital ASIC. We sketch our respective solutions for the on-chip transmission architecture and present the resulting area distribution of the final ASIC layout which has been performed for an industrial 65nm bulk CMOS process. We also show how we optimized the layout for the purpose of our experiments and present all relevant implementation details. The datasheet of the ASIC that is of paramount importance is presented in great detail. Moreover, an overview of the experimental setup is presented and some specific details are highlighted.

# Kurzfassung

Die ständig voranschreitende Verkleinerung der Strukturbreiten integrierter digitaler Schaltungen macht die verwendeten Transistoren zunehmend anfällig für Strahlungseffekte. Das führt dazu, dass bereits Partikel mit geringer Energie, die wesentlich häufiger auftreten, transiente Fehler (engl. Single-Event-Transient - SET) in CMOS Schaltungen verursachen können. Da dabei der Einfluss vieler verschiedener Parameter, wie die Stärke des auftreffenden Partikels, der betroffene Schaltungsteil sowie der Ausbreitungspfad und die unmittelbare Umgebung des Einschlagortes, eine Rolle spielt, sind diese Effekte schwierig zu analysieren und charakterisieren. Das Ziel dieser Arbeit ist es, diese Strahlungseffekte in der CMOS Technologie zu untersuchen, um so die Entwicklung von effizienten strahlungsresistenten Schaltungen zu ermöglichen. Zunächst wird die Effektivität existierender Methoden zur Strahlungshärtung (unter gegebenen Umweltbedingungen) evaluiert. Hierbei konzentrieren wir uns auf die Analyse der Fragestellung, in welchem Ausmaß die Temperatur bzw. die Versorungspannung Einfluss auf die Wirksamkeit zweier bestimmter Methoden hat, nämlich "Transistor Sizing" und "Stack Separation".

Weiters präsentieren wir Designziele und Konzepte, sowie Resultate aus der Implementierung eines digitalen ASICs, der für Langzeitstrahlungsmessungen entwickelt wurde. Dieser Chip soll dazu dienen, die Empfindlichkeit für, und die Ausbreitung von Strahlungseffekten zu untersuchen und besser zu verstehen. Die Messinfrastruktur muss in der Lage sein, SETs aufzuzeichnen und dabei aber selbst ein gewisses Maß an SET-Toleranz aufweisen, was bei Messungen dieser Art grundsätzlich nicht vermeidbar ist. Eine der größten Herausforderung dieser Arbeit war die Konzipierung dieser Infrastruktur. Dabei sind nämlich teilweise gegensätzliche Anforderungen, wie die eingeschränkte Chipfläche, gute Strahlungstoleranz, sowie eine möglichst gute Auflösung für die Erfassung des Einschlagortes und des Ausbreitungspfads eines auftreffenden Partikels, zu berücksichtigen.

Um die Empfindlichkeit von CMOS Schaltungen für SETs zu analysieren, schlagen wir eine auf den Chip integrierte Messeinrichtung vor, die es ermöglicht verschiedene Zielschaltungen zu untersuchen. Darüberhinaus stellen wir eine Architektur vor, die in der Lage ist die Erzeugung und Ausbreitung von SETs in Sklansky Addieren und Invertiererbäumen zu verfolgen. Den Kern unserer Messarchitekturen stellen nicht-strahlungsharte Zähler dar. Im speziellen kommen Linear Feedback Shift Register und auf Muller-Pipelines basierende Vor-/Rückwärtszähler zum Einsatz. Die Evaluierung des Designs erfolgt durch umfassende Fehlerinjektionsexperiemente, basierend auf detaillierten Spice Modellen der untersuchten Schaltung sowie des Standard doppelt exponentiellen Strompulsmodells für SETs. Mit diesen Untersuchungen können wir zeigen, dass unsere Messinfrastruktur robust gegen sämtliche Doppelfehler sowie etliche Dreifach- und Mehrfachfehler ist. Zusammen mit einer ergänzenden statischen Analyse kommen wir zu dem Schluss, dass die vorgestellte Architektur tatsächlich mit beträchtlichen Partikeleinschlagsraten umgehen kann, ohne dabei das Leistungsvermögen der Messinfrastruktur zu überschreiten.

Für die Messung der Pulsbreite von SETs in beliebigen digitalen Schaltungen stellen wir ebenfalls eine entsprechende Messeinrichtung vor. Im Gegensatz zu Methoden die auf Oszilloskopmessungen beruhen, ist unser Ansatz vollständig digital: Die SET-Dauer wird dabei durch SET-maskiertes Zählen von Pulsen, die von einem hochfrequenten Ringoszillator generiert werden, ermittelt. Die Ergebnisse werden in einem, als Ring organisierten, Array von Vor-/Rückwärtszählern gespeichert. Wir erarbeiten ein umfassendes Konzept um unsere Infrastruktur gegen SETs zu schützen, die sich in Speicherelementen manifestieren, wobei auch hier der Fokus darauf liegt, eine ausreichend hohe Wahrscheinlichkeit für das Auftreten eines SETs zu erreichen, ohne dabei die Toleranz der Messinfrastruktur zu überschreiten. Unser Hauptbeitrag konzentriert sich dabei auf den Schutz des Zählerarrays: Anstatt auf Strahlungshärtung oder explizite Dreifachredundanz (engl. Triple Modular Redundancy - TMR) zurückgreifen zu müssen, sparen wir Chipfläche durch eine neuartige Duplexzählerarchitektur. Für eine niedrige Anzahl an SETs implementiert unser Ansatz implizit ein TMR System, wobei dieses bei steigender Anzahl von SETs sogenanntes "graceful degradation" Verhalten aufweist.

In der Arbeit präsentieren wir die komplette Messinfrastruktur, sowie detaillierte Vorproduktionsanalysen der enthaltenen Schaltungen. Weiter skizzieren wir unsere Lösungen für die auf dem Chip integrierte Übertragungsarchitektur und zeigen die resultierende Chipflächenverteilung des finalen ASIC-Layouts für einen industriellen 65nm Fertigungsprozess. Wir diskutieren ebenfalls die vorgenommenen Optimierungen, die angewendet wurden, um das Chiplayout auf die Anforderungen der Experimente anzupassen und dokumentieren alle relevanten Implementierungsdetails. Das Datenblatt des ASICs ist dabei von besonderer Wichtigkeit. Abschließend präsentieren wir einen Überblick über den Aufbau des Experiments, wobei einige wichtige Details besonders hervorgehoben werden.

# Contents

| Li | st of I            | Figures x                                                    | vii |  |  |

|----|--------------------|--------------------------------------------------------------|-----|--|--|

| Li | List of Tables xxi |                                                              |     |  |  |

| 1  | Intro              | oduction                                                     | 1   |  |  |

|    | 1.1                | Motivation                                                   | 2   |  |  |

|    |                    | 1.1.1 SET Model                                              | 3   |  |  |

|    |                    | 1.1.2 Soft Error Rate                                        | 3   |  |  |

|    |                    | 1.1.2.1 SET Generation                                       | 4   |  |  |

|    |                    | 1.1.2.2 SET Propagation                                      | 5   |  |  |

|    |                    | 1.1.2.3 SET Masking                                          | 6   |  |  |

|    |                    | 1.1.3 Radiation Hardening Mechanisms                         | 7   |  |  |

|    | 1.2                | Scope                                                        | 8   |  |  |

|    | 1.3                | List of Key Contributions                                    | 9   |  |  |

|    |                    |                                                              | 10  |  |  |

|    |                    | 1.3.2 Innovative Measurement Infrastructure SET Sensitivity  | 10  |  |  |

|    |                    | 1.3.3 Novel Measurement Infrastructure for SET Propagation   | 11  |  |  |

|    |                    | 1.3.4 Unique Measurement Infrastructure for SET Pulse widths | 11  |  |  |

|    |                    | 1.3.5 Design of Radiation Target ASIC                        | 12  |  |  |

|    | 1.4                | Outline and Methodology                                      | 12  |  |  |

| 2  | SET                | Injection Mechanisms                                         | 15  |  |  |

|    | 2.1                | Background                                                   | 16  |  |  |

|    |                    | -                                                            | 17  |  |  |

|    |                    | 2.1.2 Spice model                                            | 18  |  |  |

|    |                    | 2.1.2.1 Double Exponential Current Model                     | 20  |  |  |

|    |                    | 2.1.2.2 Improved Current Model                               | 22  |  |  |

|    | 2.2                | SET Simulation Model                                         | 23  |  |  |

|    |                    | 2.2.1 3D TCAD model                                          | 24  |  |  |

|    |                    |                                                              | 26  |  |  |

|    | 2.3                | Spice Model Study - C-element Example                        | 29  |  |  |

|    |                    | · · ·                                                        | 29  |  |  |

|    |                    | 2.3.2 Variation Analysis                                     | 32  |  |  |

|    |                    | •                                                            | 33  |  |  |

|    | 2.4                |                                                              | 33  |  |  |

| 3 | Rad | iation H | Hardening   | g Mechanisms                                     | 35 |

|---|-----|----------|-------------|--------------------------------------------------|----|

|   | 3.1 | Backg    | round       |                                                  | 35 |

|   |     | 3.1.1    |             | evel Hardening                                   | 36 |

|   |     | 3.1.2    | Circuit-l   | evel Hardening                                   | 37 |

|   |     | 3.1.3    | System-     | evel Hardening                                   | 38 |

|   | 3.2 | Propos   |             | ion Hardening Mechanisms for Muller C-Element .  |    |

|   |     | 3.2.1    | Radiatio    | n Hardening by Sizing                            | 39 |

|   |     | 3.2.2    | Dual Inte   | erlocked Storage Cell Mechanism                  | 40 |

|   |     | 3.2.3    | Radiatio    | n Hardening by Separation Mechanism              | 41 |

|   |     | 3.2.4    | Summar      | y                                                | 41 |

|   | 3.3 | Combi    | inational C | Circuits                                         | 42 |

|   |     | 3.3.1    |             | alysis – XOR gate                                | 43 |

|   |     | 3.3.2    | Radiatio    | n Hardening Mechanisms                           | 44 |

|   |     |          | 3.3.2.1     | Radiation-Hardening by Gate Sizing               | 44 |

|   |     |          | 3.3.2.2     | Defect-Tolerant Logic                            | 46 |

|   |     |          | 3.3.2.3     | Analog Voter                                     | 48 |

|   |     |          | 3.3.2.4     | Radiation Hardening by Separation Mechanism      | 48 |

|   |     |          | 3.3.2.5     | Code Word State Preserving (CWSP) Element        | 50 |

|   |     | 3.3.3    | Summar      | y                                                | 52 |

|   | 3.4 | Perfor   | mance und   | ler VT Variations                                | 53 |

|   |     | 3.4.1    | Target C    | ircuits                                          | 53 |

|   |     |          | 3.4.1.1     | Sizing Requirements for Rad-Hard Sizing Mech-    |    |

|   |     |          |             | anism                                            | 54 |

|   |     | 3.4.2    | Setup for   | r VT Variation Experiments                       | 55 |

|   |     | 3.4.3    | SET Exp     | periments with VT variations                     | 57 |

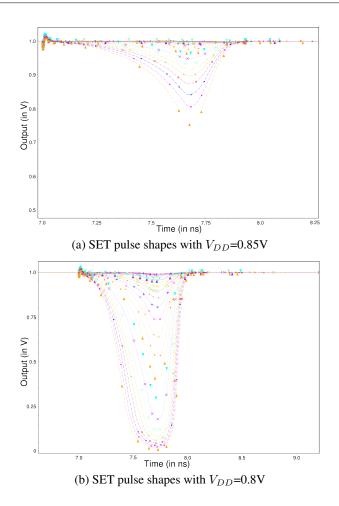

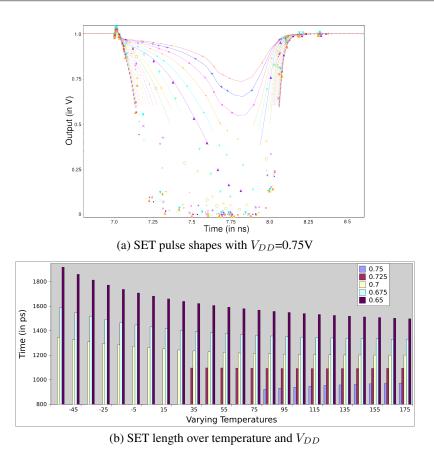

|   |     |          | 3.4.3.1     | Transistor Sizing Mechanism                      | 57 |

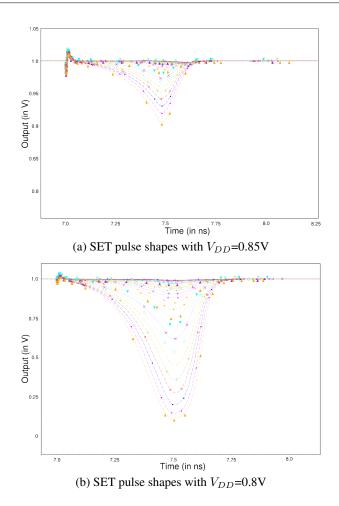

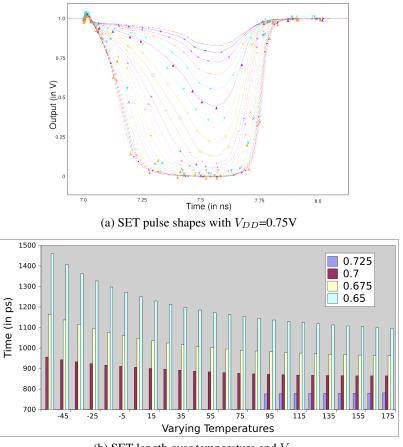

|   |     |          | 3.4.3.2     | Stack-Separation Mechanism                       | 60 |

|   |     | 3.4.4    | Summar      | y                                                | 67 |

|   | 3.5 | Seque    | ntial Circu | its                                              | 69 |

|   |     | 3.5.1    | Backgro     | und                                              | 70 |

|   |     |          | 3.5.1.1     | Linear Feedback Shift Register                   | 70 |

|   |     |          | 3.5.1.2     | Parallel-In Serial-Out                           | 71 |

|   |     | 3.5.2    | Proposed    | l Rad-hard Mechanisms                            | 72 |

|   |     |          | 3.5.2.1     | Radiation Hardening by Sizing for the LFSR       | 73 |

|   |     |          | 3.5.2.2     | Hardware Redundancy for the LFSR                 | 73 |

|   |     |          | 3.5.2.3     | Time Redundancy for the LFSR                     | 75 |

|   |     |          | 3.5.2.4     | Radiation Tolerance by Separation for the LFSR . | 75 |

|   |     |          | 3.5.2.5     | Radiation Tolerance using DICE for the LFSR      | 76 |

|   |     |          | 3.5.2.6     | Hardening by Sizing for the PISO                 | 77 |

|   |     |          | 3.5.2.7     | Radiation Tolerance by Separation for the PISO . | 77 |

|   |     |          | 3.5.2.8     | Radiation Tolerance using DICE for the PISO      | 77 |

|   |     |          | 3.5.2.9     | Time Redundancy for the PISO                     | 77 |

|   |     | 3.5.3    | Summar      | у                                                | 77 |

| 4 | Sens | sitivity a | and Spatial Distribution of SETs       | 81  |

|---|------|------------|----------------------------------------|-----|

|   | 4.1  | Target     | Architecture                           | 83  |

|   |      | 4.1.1      | Inverter                               | 83  |

|   |      |            | 4.1.1.1 Inverter Chain                 | 83  |

|   |      | 4.1.2      | NAND-NOR Logic                         | 84  |

|   |      |            | 4.1.2.1 NAND gate                      | 84  |

|   |      |            | 4.1.2.2 NOR gate                       | 85  |

|   |      |            | 4.1.2.3 NAND NOR Tree                  | 86  |

|   |      | 4.1.3      | Sequential Circuits                    | 87  |

|   |      |            | 4.1.3.1 Flip-Flop                      | 87  |

|   |      |            | 4.1.3.2 Flip-Flop Chain                | 88  |

|   |      | 4.1.4      | Asynchronous Circuits                  | 89  |

|   |      |            | 4.1.4.1 Muller C-element               | 89  |

|   |      |            | 4.1.4.2 Muller Pipeline                | 90  |

|   |      | 4.1.5      | XOR gate                               | 91  |

|   |      |            | 4.1.5.1 XNOR Tree                      | 92  |

|   |      | 4.1.6      | Summary                                | 93  |

|   | 4.2  | Measu      | rement Architecture – Semi-Static Mode | 94  |

|   |      | 4.2.1      | Architecture A                         | 95  |

|   |      | 4.2.2      | Architecture B                         | 96  |

|   |      | 4.2.3      | Architecture C                         | 96  |

|   |      |            | 4.2.3.1 Up/Down Counter                | 96  |

|   |      | 4.2.4      | Architecture D                         | 98  |

|   |      | 4.2.5      | Architecture E                         | 98  |

|   |      | 4.2.6      | Architecture F                         | 100 |

|   |      | 4.2.7      | Architecture G                         | 101 |

|   | 4.3  | Evalua     | ation and Analysis - Semi-Static Mode  | 101 |

|   |      | 4.3.1      | Overhead Analysis                      | 102 |

|   |      | 4.3.2      | Analysis Setup                         | 103 |

|   |      | 4.3.3      | LFSR Counter Evaluation                | 103 |

|   |      | 4.3.4      | Up/Down Counter Evaluation             | 105 |

|   |      | 4.3.5      | Fault Dictionary                       | 106 |

|   |      | 4.3.6      | SET Simulations                        | 109 |

|   | 4.4  | Probał     | bilistic Analysis                      | 110 |

|   | 4.5  | High S     | Speed Measurement Architecture         | 115 |

|   |      | 4.5.1      | SET Analysis                           | 117 |

|   |      | 4.5.2      | Hardware-Overhead Analysis             | 118 |

|   | 4.6  | Summ       | ary                                    | 120 |

| 5 | Pro  | nagatio    | n of SETs                              | 121 |

| J | 5.1  |            | sky Adder                              |     |

|   | 5.1  | 5.1.1      | Background                             |     |

|   |      | 5.1.2      | Architecture Description               |     |

|   |      | 5.1.2      | Measurement Architecture               |     |

|   |      | 5.1.5      |                                        | 144 |

|   |      |        | 5.1.3.1 Data Collection in the Carry Propagation Path            |     |

|---|------|--------|------------------------------------------------------------------|-----|

|   |      |        | 5.1.3.2 Overall Measurement Infrastructure                       | 125 |

|   | 5.2  |        | Tree                                                             |     |

|   |      | 5.2.1  | Measurement Architecture                                         |     |

|   |      | :      | 5.2.1.1 Static Mode                                              |     |

|   |      |        | 5.2.1.2 Dynamic Mode                                             |     |

|   | 5.3  | SET An | alysis – Sklansky Adder                                          | 131 |

|   |      |        | dentification of the most sensitive adder state                  |     |

|   |      | 5.3.2  | SET Injection Experiments in the 16-bit Adder                    | 132 |

|   |      | 5.3.3  | Fault Dictionary                                                 | 135 |

|   |      | 5.3.4  | SETs in the Counters                                             | 139 |

|   | 5.4  | SET An | alysis – Inverter Tree                                           | 140 |

|   |      | 5.4.1  | Static Mode                                                      | 140 |

|   |      | 5.4.2  | Dynamic Mode                                                     | 144 |

|   | 5.5  | Summar | у                                                                | 146 |

|   |      |        |                                                                  |     |

| 6 |      |        | leasurement of SETs                                              | 151 |

|   | 6.1  |        | und                                                              |     |

|   | 6.2  |        | ment Infrastructure Requirements                                 |     |

|   | 6.3  |        | SET Pulse-width Measurement Architecture                         |     |

|   |      |        | Principle                                                        |     |

|   |      |        | Design space                                                     |     |

|   |      |        | Switch placement                                                 |     |

|   |      |        | Radiation tolerance                                              |     |

|   |      |        | SET Analysis                                                     |     |

|   |      |        | 5.3.5.1 Verification for other target circuits                   |     |

|   | 6.4  |        | ment Infrastructure for Multiple SETs                            |     |

|   | 6.5  | -      | SET Architecture – Improvement of Counter Array                  |     |

|   |      |        | Counter array implementation                                     |     |

|   |      |        | Attaining Fault Tolerance                                        |     |

|   |      |        | 5.5.2.1 Guiding principles                                       |     |

|   |      |        | 5.5.2.2 Protecting the address counter                           |     |

|   |      |        | 5.5.2.3 Protecting the counter array                             |     |

|   |      |        | 5.5.2.4 Initialization and read-out                              |     |

|   |      |        | Resulting architecture                                           |     |

|   |      |        | Multiple Event Transients Analysis                               |     |

|   | 6.6  | -      | m for pulse width extraction from the read-outs                  |     |

|   | 6.7  |        | ctionary                                                         |     |

|   | 6.8  |        | istic Analysis                                                   |     |

|   |      |        | Computing $P_{fail}$ for at most 3 target SETs                   |     |

|   |      |        | Computing $P_{fail}$ for more than 3 target SETs $\ldots \ldots$ |     |

|   | 6.9  |        | on of our Analysis Results                                       |     |

|   | 6.10 | Summar | у                                                                | 189 |

|   |      |        |                                                                  |     |

### 7 Target FRad ASIC

|   | 7.1 | On-Ch   | nip Data Transmission Architecture                       | . 192 |

|---|-----|---------|----------------------------------------------------------|-------|

|   |     | 7.1.1   | Application Requirements                                 | . 192 |

|   |     | 7.1.2   | Operation of PISO                                        | . 193 |

|   |     | 7.1.3   | Architecture Options                                     |       |

|   |     |         | 7.1.3.1 Single PISO – Measurement Infrastructure         |       |

|   |     |         | 7.1.3.2 Single PISO – Multiple Measurement Infrastructur |       |

|   |     | 7.1.4   | Summary                                                  |       |

|   | 7.2 | ASIC    | Architecture                                             |       |

|   |     | 7.2.1   | FRad Overview                                            | . 199 |

|   |     | 7.2.2   | Requirements                                             | . 199 |

|   |     | 7.2.3   | Specifications                                           |       |

|   |     |         | 7.2.3.1 SET Sensitivity                                  | . 201 |

|   |     |         | 7.2.3.2 SET Propagation                                  |       |

|   |     |         | 7.2.3.3 PISO                                             |       |

|   | 7.3 | ASIC    | Layout and Implementation details                        |       |

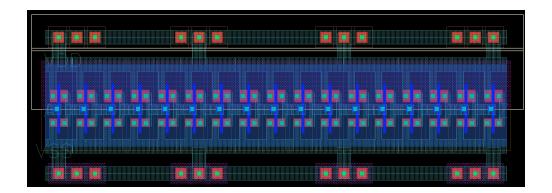

|   |     | 7.3.1   | ASIC Floorplan                                           |       |

|   |     | 7.3.2   | Layout and Placement                                     | . 205 |

|   | 7.4 | ASIC    | Functional Behavior                                      |       |

|   |     | 7.4.1   | Reset                                                    | . 213 |

|   |     |         | 7.4.1.1 Verification of Reset                            |       |

|   |     | 7.4.2   | Programming                                              | . 215 |

|   |     |         | 7.4.2.1 Verification                                     |       |

|   | 7.5 | ASIC    | – SET Experiments                                        | . 217 |

|   |     | 7.5.1   | 30-bit PISO                                              |       |

|   |     | 7.5.2   | 84-bit PISO                                              |       |

|   |     | 7.5.3   | 110-bit PISO                                             | . 221 |

|   |     | 7.5.4   | 75-bit PISO                                              |       |

|   | 7.6 | Data T  | Fransmission from ASIC to PC                             |       |

|   |     | 7.6.1   | Gateway                                                  |       |

|   |     | 7.6.2   | Operation of Gateway                                     |       |

|   |     | 7.6.3   | Requirements                                             |       |

|   |     | 7.6.4   | Concept                                                  |       |

|   |     |         | 1                                                        |       |

| 8 | Con | clusion | s and Future Work                                        | 227   |

|   | 8.1 | Summ    | ary of Key Contributions                                 | . 227 |

|   |     | 8.1.1   | SET Modeling                                             | . 227 |

|   |     | 8.1.2   | Design of Novel Radiation Hardening Mechanisms           | . 228 |

|   |     | 8.1.3   | Innovative Measurement Infrastructure SET Sensitivity    | . 229 |

|   |     | 8.1.4   | Novel Measurement Infrastructure for SET Propagation     | . 230 |

|   |     | 8.1.5   | Novel Measurement Infrastructure for SET Pulsewidths     | . 231 |

|   |     | 8.1.6   | Design of FRad Chip                                      | . 231 |

|   | 8.2 | Outloo  | ok                                                       | . 232 |

|   |     | 8.2.1   | Fabrication of the ASIC                                  | . 233 |

|   |     | 8.2.2   | Gateway FPGA Setup                                       | . 233 |

| . 234 |

|-------|

| . 234 |

| . 234 |

| . 235 |

| 237   |

| 253   |

| . 253 |

| . 257 |

| . 257 |

| . 258 |

| . 259 |

| 200   |

| . 260 |

| •     |

# **List of Figures**

| 2.1  | Inverter with Double Exponential Current Source                                    | 21 |

|------|------------------------------------------------------------------------------------|----|

| 2.2  | Simulation of an Inverter with Double Exponential Current Model                    | 21 |

| 2.3  | Improved Current Model                                                             | 22 |

| 2.4  | Simulation of an Inverter with Improved Current Model                              | 23 |

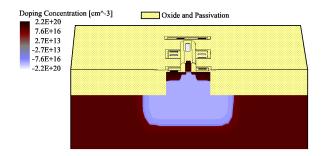

| 2.5  | TCAD 3D Structure of an Inverter (Cutting Plane through NMOS)                      | 24 |

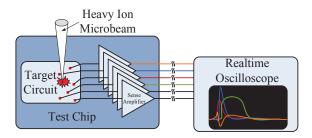

| 2.6  | Test Chip Schematics for Calibration and Validation of the 3D Model                |    |

|      | and the Spice Model                                                                | 25 |

| 2.7  | Measured SET Voltage Pulses (Inverter) under Heavy-Ion ( <sup>197</sup> Au, 946MeV | )  |

|      | Irradiation [129]: SETs for a) Low (0), b) High (1) Inputs                         | 26 |

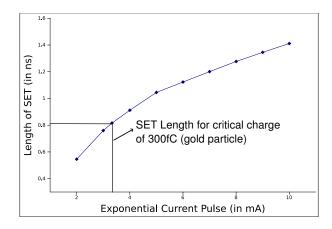

| 2.8  | Length of SET vs. Exponential Peak Current $I_0$                                   | 28 |

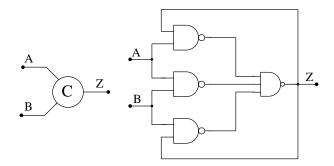

| 2.9  | Muller C-element (a) Symbol, (b) Logical equivalent                                | 29 |

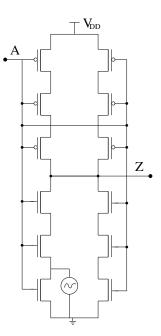

| 2.10 | Conventional Pull-up Pull-down Muller C-element                                    | 30 |

| 2.11 | Van Berkel Muller C-element                                                        | 30 |

|      | Weak Feedback Muller C-element                                                     | 31 |

| 2.13 | Inverter based Muller C-element                                                    | 31 |

| 2.14 | Simulation results                                                                 | 32 |

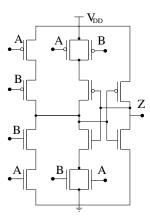

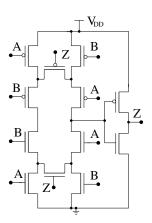

| 3.1  | DICE Cell Based Muller C-element                                                   | 40 |

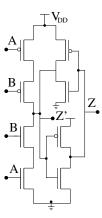

| 3.2  | Radiation Hardened Muller C-element using Separation Mechanism                     | 41 |

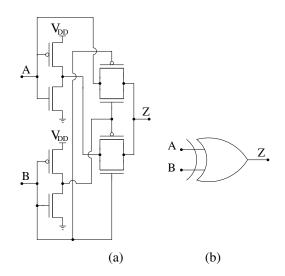

| 3.3  | Transistor level Schematic of Cross Coupled XOR gate                               | 43 |

| 3.4  | Gate Level Schematic of IAO XOR gate                                               | 43 |

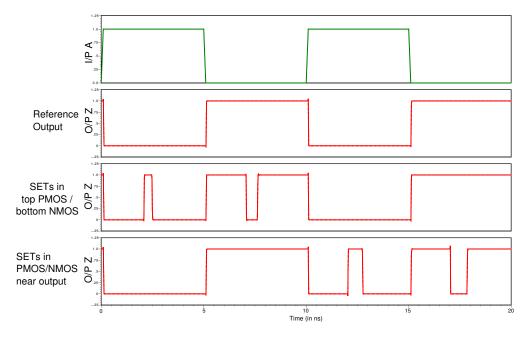

| 3.5  | Simulation of SET hits in CC XOR gate                                              | 44 |

| 3.6  | Simulation of SET hits in IAO XOR gate                                             | 45 |

| 3.7  | SET Simulations of Rad-Hard CC XOR Gate                                            | 45 |

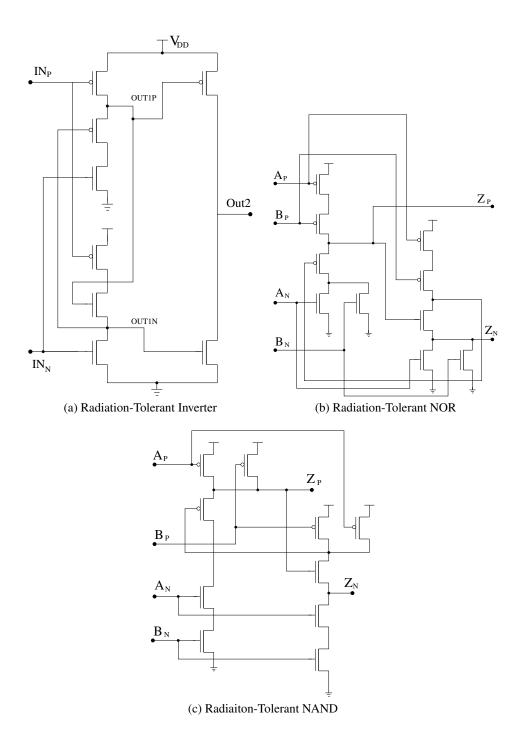

| 3.8  | Defect-Tolerant Inverter                                                           | 46 |

| 3.9  | Simulation of SETs in Defect-tolerant Inverter                                     | 47 |

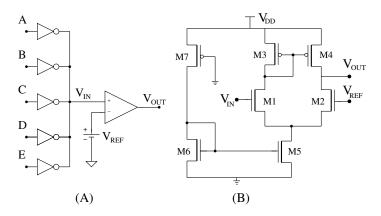

| 3.10 | Analog Voter with Comparator                                                       | 47 |

| 3.11 | SET Simulation of XOR gate with Analog Voter1                                      | 48 |

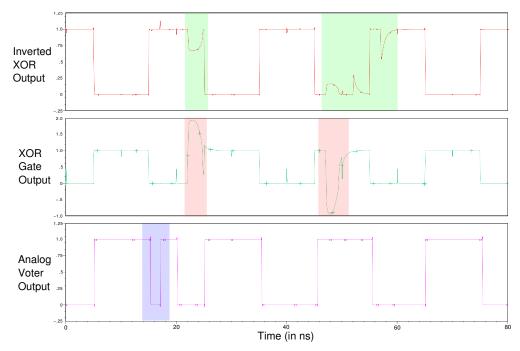

| 3.12 | Radiation Hardening by Separation Mechanism                                        | 49 |

| 3.13 | Simulation of SETs for Radiation Tolerant XOR gate                                 | 51 |

|      | CWSP CC XOR gate                                                                   | 51 |

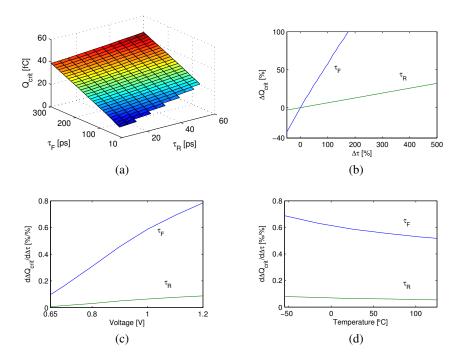

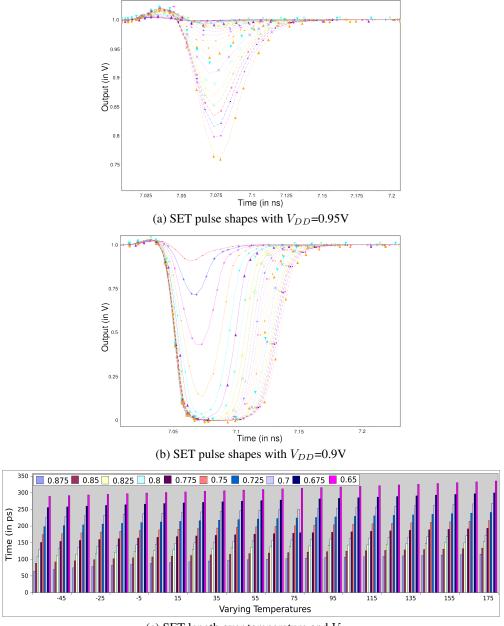

|      | Results of voltage and temperature variation experiments for Rad-Hard              |    |

|      | Sizing with Q=450fC, Tr=10ps, Tf=110ps, I=4.5mA                                    | 58 |

| 3.17 | Results of voltage and temperature variation experiments for Rad-Hard              |    |

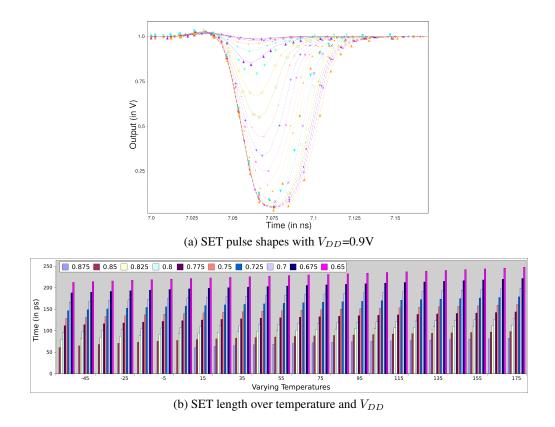

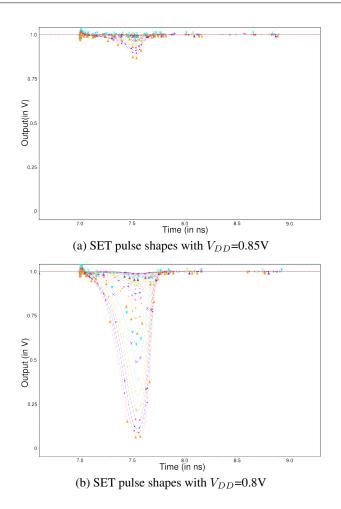

|      | Sizing with Q=450fC, Tr=10ps, Tf=160ps, I=3mA                                      | 59 |

| 3.18                                                                                                                                                                               | Results of voltage and temperature variation experiments for Rad-Hard                                                          |                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                    | Sizing with Q=300fC, Tr=10ps, Tf=110ps, I=3mA                                                                                  | 61                                                                                                                                                         |

| 3.19                                                                                                                                                                               | Results of voltage and temperature variation experiments for Stack Sep-                                                        |                                                                                                                                                            |

|                                                                                                                                                                                    | aration with Q=450fC, Tr=10ps, Tf=110ps, I=4.5mA                                                                               | 62                                                                                                                                                         |

| 3.20                                                                                                                                                                               | Results of voltage and temperature variation experiments for Stack Sep-                                                        |                                                                                                                                                            |

|                                                                                                                                                                                    | aration with Q=450fC, Tr=10ps, Tf=110ps, I=4.5mA                                                                               | 63                                                                                                                                                         |

| 3.21                                                                                                                                                                               | Results of voltage and temperature variation experiments for Stack Sep-                                                        |                                                                                                                                                            |

|                                                                                                                                                                                    | aration with Q=450fC, Tr=10ps, Tf=160ps, I=3mA                                                                                 | 64                                                                                                                                                         |

| 3.22                                                                                                                                                                               | Results of voltage and temperature variation experiments for Stack Sep-                                                        |                                                                                                                                                            |

|                                                                                                                                                                                    | aration with Q=450fC, Tr=10ps, Tf=160ps, I=3mA                                                                                 | 65                                                                                                                                                         |

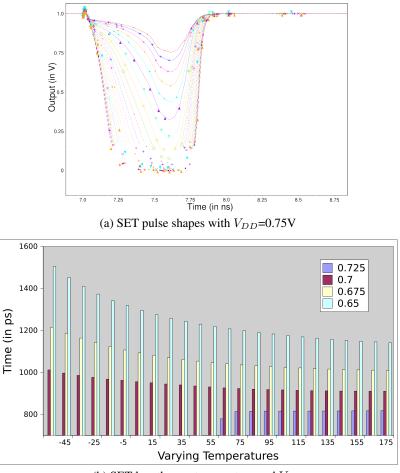

| 3.23                                                                                                                                                                               | Results of voltage and temperature variation experiments for Stack Sep-                                                        |                                                                                                                                                            |

|                                                                                                                                                                                    | aration with Q=300fC, Tr=10ps, Tf=110ps, I=3mA                                                                                 | 66                                                                                                                                                         |

| 3.24                                                                                                                                                                               | Results of voltage and temperature variation experiments for Stack Sep-                                                        |                                                                                                                                                            |

|                                                                                                                                                                                    | aration with Q=300fC, Tr=10ps, Tf=110ps, I=3mA                                                                                 | 67                                                                                                                                                         |

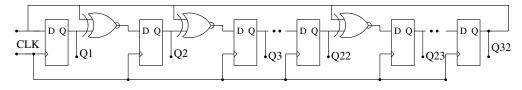

| 3.25                                                                                                                                                                               | 32-bit LFSR                                                                                                                    | 70                                                                                                                                                         |

|                                                                                                                                                                                    | 4-bit Parallel-in, Serial-out Shift Register                                                                                   | 71                                                                                                                                                         |

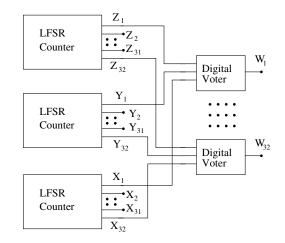

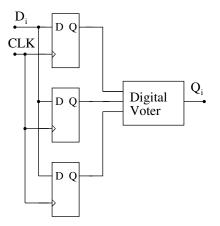

| 3.27                                                                                                                                                                               | Schematics of TMR LFSR Counter                                                                                                 | 73                                                                                                                                                         |

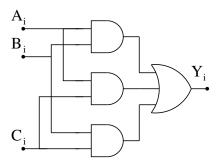

|                                                                                                                                                                                    | Schematics of the Digital Voter                                                                                                | 74                                                                                                                                                         |

| 3.29                                                                                                                                                                               | Schematics of TMR Flip-Flops                                                                                                   | 74                                                                                                                                                         |

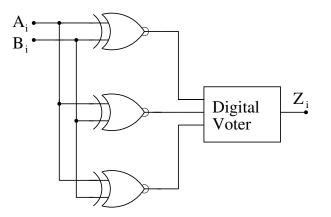

|                                                                                                                                                                                    | Schematics of TMR XNOR Gate                                                                                                    | 75                                                                                                                                                         |

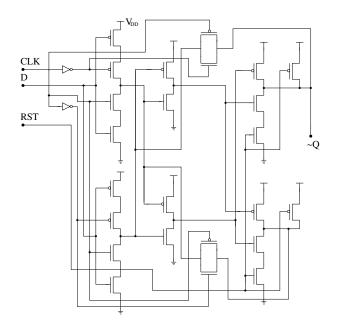

|                                                                                                                                                                                    | Transistor level Schematics of DICE Latch                                                                                      | 76                                                                                                                                                         |

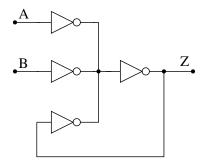

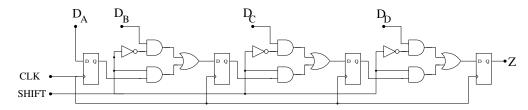

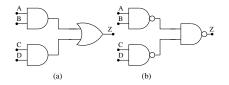

|                                                                                                                                                                                    | Control Logic of the PISO                                                                                                      | 77                                                                                                                                                         |

| 0.01                                                                                                                                                                               |                                                                                                                                |                                                                                                                                                            |

|                                                                                                                                                                                    |                                                                                                                                |                                                                                                                                                            |

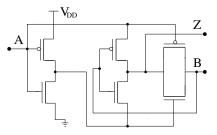

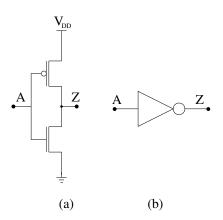

| 4.1                                                                                                                                                                                | (a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter                                                             | 83                                                                                                                                                         |

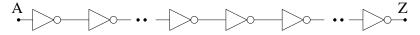

| 4.1<br>4.2                                                                                                                                                                         | (a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain                             | 84                                                                                                                                                         |

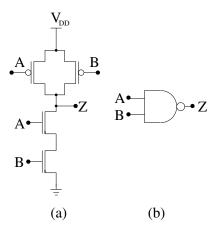

| 4.1<br>4.2<br>4.3                                                                                                                                                                  | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter</li> <li>Logic Diagram of Inverter Chain</li></ul> | 84<br>85                                                                                                                                                   |

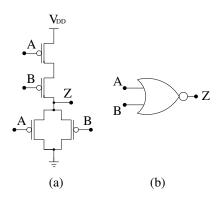

| 4.1<br>4.2<br>4.3<br>4.4                                                                                                                                                           | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter</li> <li>Logic Diagram of Inverter Chain</li></ul> | 84<br>85<br>85                                                                                                                                             |

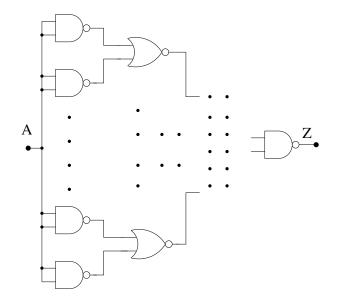

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5                                                                                                                                                    | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter</li> <li>Logic Diagram of Inverter Chain</li></ul> | 84<br>85<br>85<br>87                                                                                                                                       |

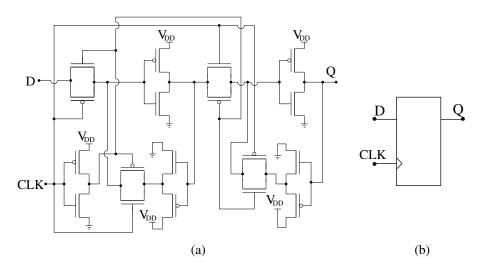

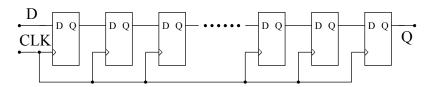

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                                                                                                                                             | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | 84<br>85<br>85<br>87<br>88                                                                                                                                 |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7                                                                                                                                      | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | 84<br>85<br>85<br>87<br>88<br>89                                                                                                                           |

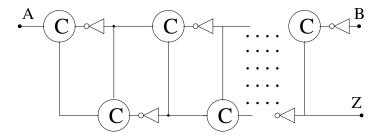

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8                                                                                                                               | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter</li> <li>Logic Diagram of Inverter Chain</li></ul> | 84<br>85<br>85<br>87<br>88<br>89<br>90                                                                                                                     |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9                                                                                                                        | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | 84<br>85<br>87<br>88<br>89<br>90<br>91                                                                                                                     |

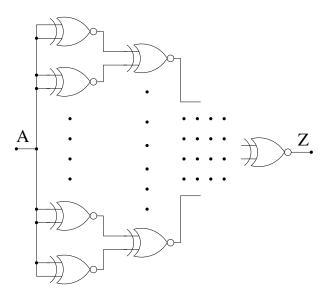

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10                                                                                                                | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | 84<br>85<br>87<br>88<br>89<br>90<br>91<br>92                                                                                                               |

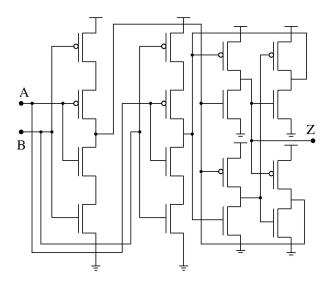

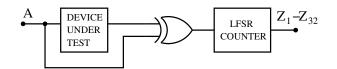

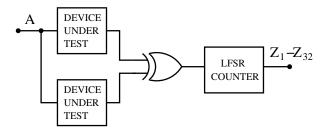

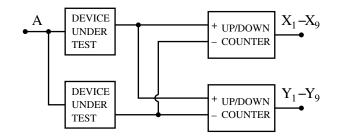

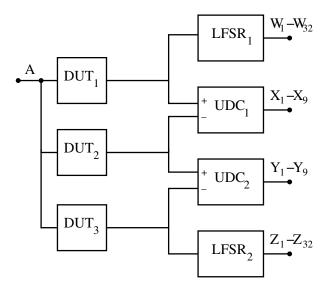

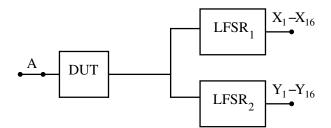

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11                                                                                                        | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | <ul> <li>84</li> <li>85</li> <li>87</li> <li>88</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>96</li> </ul>                                     |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12                                                                                                | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | <ul> <li>84</li> <li>85</li> <li>87</li> <li>88</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>96</li> <li>96</li> </ul>                         |

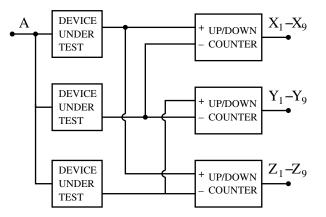

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13                                                                                        | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | <ul> <li>84</li> <li>85</li> <li>87</li> <li>88</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>96</li> </ul>                                     |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13                                                                                        | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | <ul> <li>84</li> <li>85</li> <li>87</li> <li>88</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>96</li> <li>96</li> <li>97</li> </ul>             |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13<br>4.14                                                                                | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | <ul> <li>84</li> <li>85</li> <li>87</li> <li>88</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>96</li> <li>97</li> <li>97</li> </ul>             |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13<br>4.14<br>4.15                                                                        | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | <ul> <li>84</li> <li>85</li> <li>87</li> <li>88</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>96</li> <li>97</li> <li>97</li> <li>98</li> </ul> |

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \\ 4.13 \\ 4.14 \\ 4.15 \\ 4.16 \end{array}$                                 | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | <ul> <li>84</li> <li>85</li> <li>87</li> <li>88</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>96</li> <li>97</li> <li>98</li> <li>99</li> </ul> |

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \\ 4.13 \\ 4.14 \\ 4.15 \\ 4.16 \\ 4.17 \end{array}$                         | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | <ul> <li>84</li> <li>85</li> <li>87</li> <li>88</li> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>96</li> <li>97</li> <li>97</li> <li>98</li> </ul> |

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \\ 4.13 \\ 4.14 \\ 4.15 \\ 4.16 \\ 4.17 \\ 4.18 \end{array}$                 | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | 84<br>85<br>87<br>88<br>89<br>90<br>91<br>92<br>96<br>97<br>96<br>97<br>97<br>98<br>99<br>100                                                              |

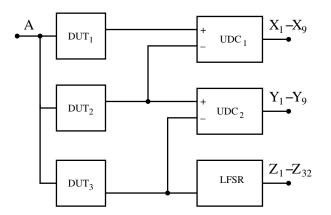

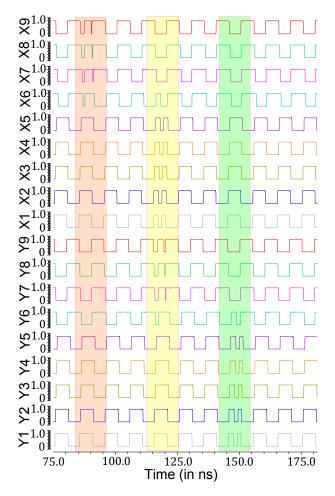

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \\ 4.13 \\ 4.14 \\ 4.15 \\ 4.16 \\ 4.17 \\ 4.18 \\ 4.19 \end{array}$         | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | 84<br>85<br>87<br>88<br>89<br>90<br>91<br>92<br>96<br>96<br>97<br>97<br>98<br>99<br>100<br>101                                                             |

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ 4.10 \\ 4.11 \\ 4.12 \\ 4.13 \\ 4.14 \\ 4.15 \\ 4.16 \\ 4.17 \\ 4.18 \\ 4.19 \\ 4.20 \end{array}$ | <ul> <li>(a) Transistor Level Schematic of Inverter, (b) Symbol of Inverter Logic Diagram of Inverter Chain</li></ul>          | 84<br>85<br>87<br>88<br>90<br>91<br>92<br>96<br>96<br>97<br>97<br>98<br>99<br>100<br>101<br>110                                                            |

| 4.22 | Simulation of the LFSR Counter 2                                            | 113  |

|------|-----------------------------------------------------------------------------|------|

| 4.23 | Measurement Setup for Dynamic Mode                                          | 116  |

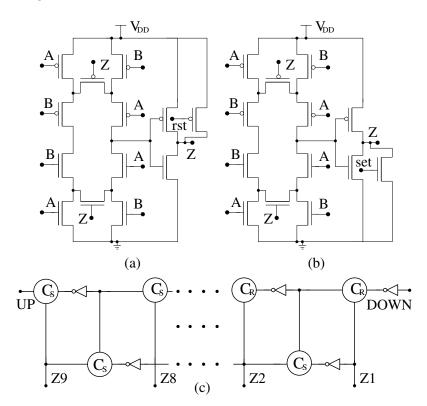

| 4.24 | Schematic of Weak-Feedback (a) Muller C-element with Reset (rst), (b)       |      |

|      | Muller C-element with Set (set) and (c) Up/Down Counter                     | 116  |

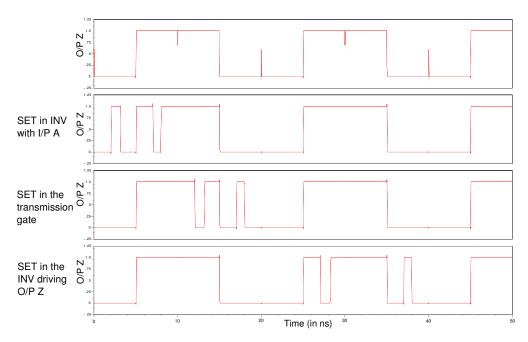

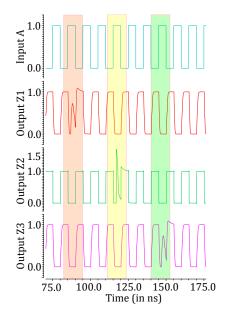

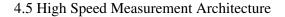

| 4.25 | Simulation of the pipeline with target circuit under exposure               | 118  |

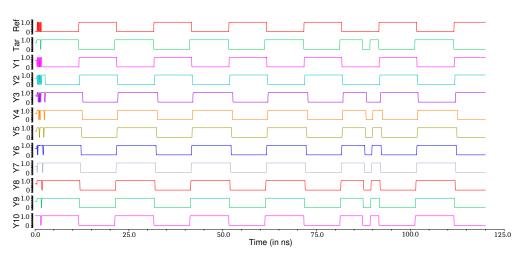

| 4.26 | Simulation of the pipeline with reference circuit under exposure            | 118  |

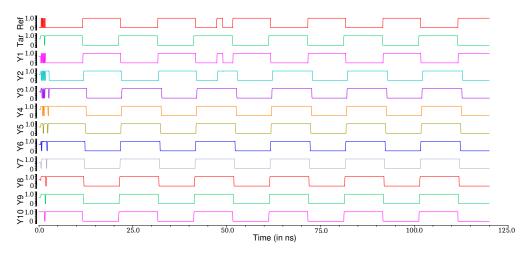

| 4.27 | Simulation of the pipeline with target and reference circuit under exposure | e119 |

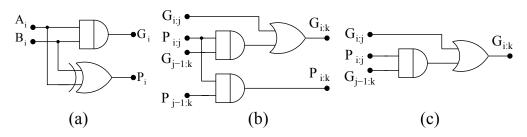

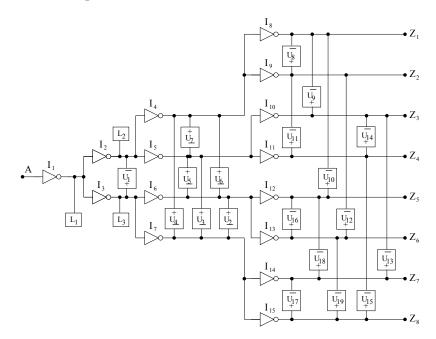

| 5.1  | Gate Level Schematic of Sklansky Adder Cells                                | 123  |

| 5.2  | Architecture of 16-bit Sklansky Adder                                       |      |

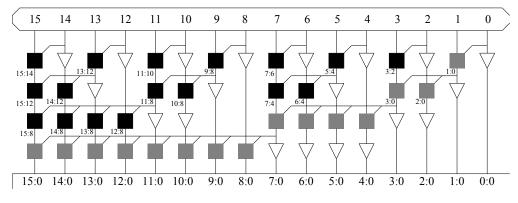

| 5.3  | Measurement Architecture for SET Propagation in the 16-bit Sklansky         |      |

|      | Tree Adder                                                                  | 126  |

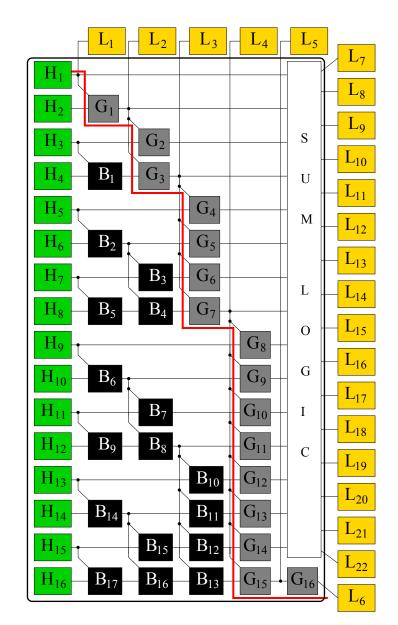

| 5.4  | Measurement Architecture for the Static Inverter Tree                       |      |

| 5.5  | Measurement Architecture for the Inverter Tree – Dynamic Mode               |      |

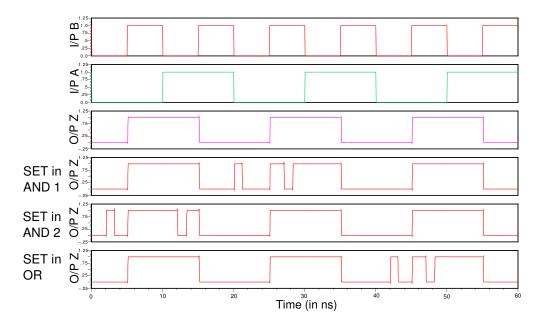

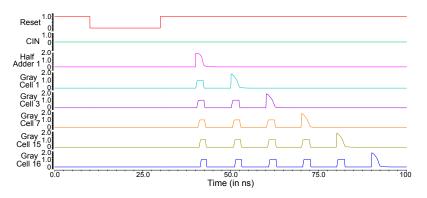

| 5.6  | SET Analysis of Sklansky Adder                                              |      |

| 5.7  | SET Analysis of Sklansky Adder                                              |      |

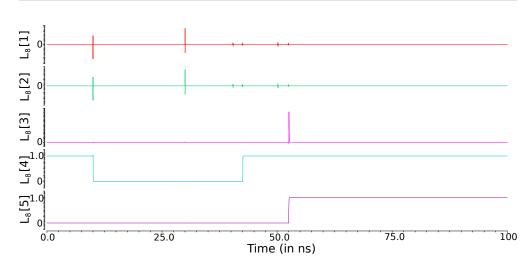

| 5.8  | Counter $L_8$ - SET Analysis of Sklansky Adder                              |      |

| 5.9  | Counter $L_{14}$ - SET Analysis of Sklansky Adder                           |      |

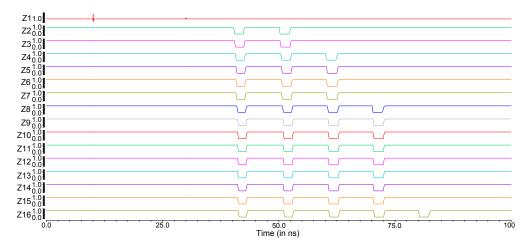

| 5.10 |                                                                             |      |

|      |                                                                             |      |

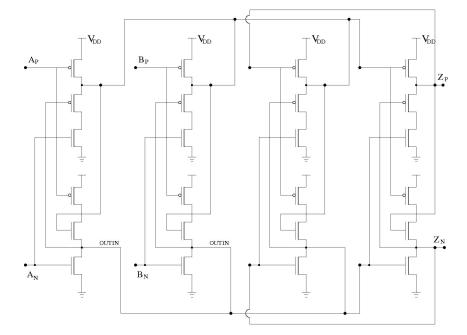

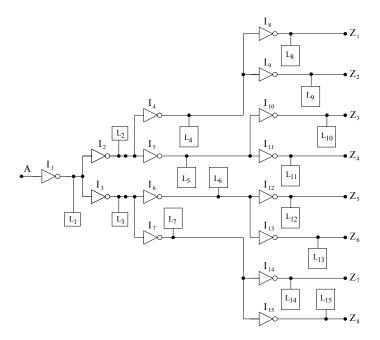

| 6.1  | Baseline Architecture to Measure SET Lengths                                |      |

| 6.2  | Length of SETs in a D Flip-Flop                                             |      |

| 6.3  | Architecture to Measure Multiple SET Lengths                                |      |

| 6.4  | Pulse width Measurement Architecture for Multiple SETs                      |      |

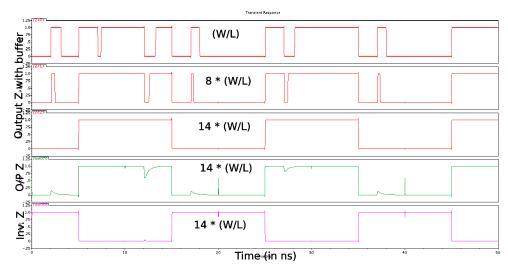

| 6.5  | Simulation results for the SETs injected in the target circuit              | 173  |

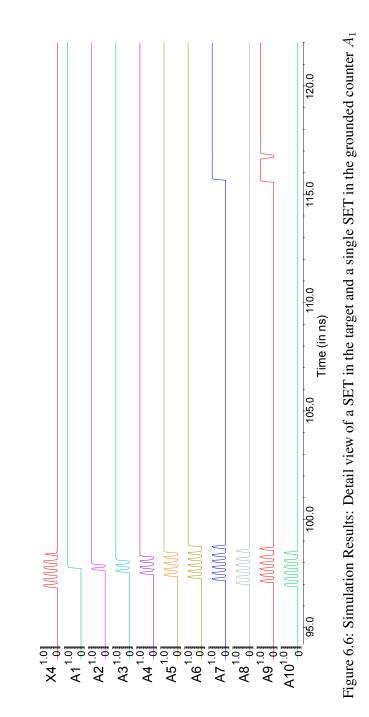

| 6.6  | Simulation Results: Detail view of a SET in the target and a single SET     |      |

|      | in the grounded counter $A_1$                                               | 175  |

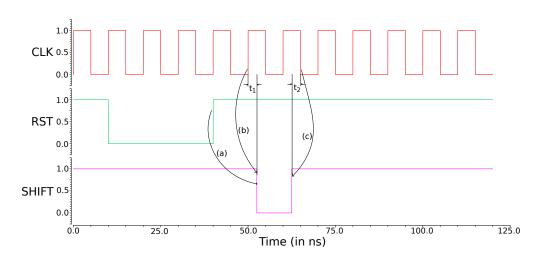

| 7.1  | Simulation of 4-bit PISO                                                    | 194  |

| 7.2  | 4-bit PISO Timing diagram                                                   | 195  |

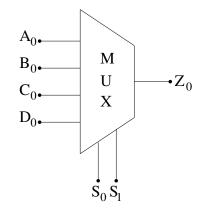

| 7.3  | Block diagram of 4:1 MUX                                                    |      |

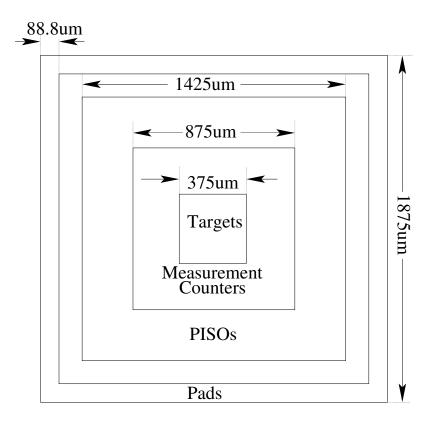

| 7.4  | ASIC Floorplan                                                              |      |

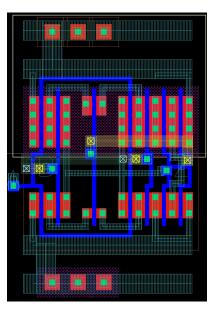

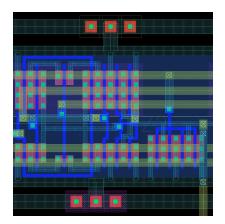

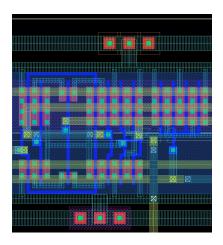

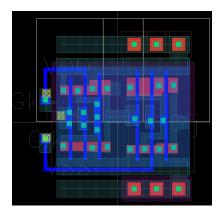

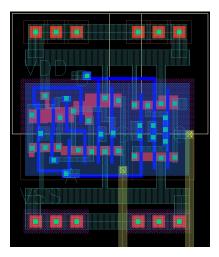

| 7.5  | Muller C-element Layout                                                     | 206  |

| 7.6  | Muller C-element with "set" Layout                                          | 206  |

| 7.7  | Muller C-element with "reset" Layout                                        | 207  |

| 7.8  | Inverter Chain Layout                                                       | 207  |

| 7.9  | Nand Nor Tree Layout                                                        | 207  |

| 7.10 | Inverter Tree Layout                                                        | 208  |

| 7.11 | Black Cell Layout                                                           | 208  |

| 7.12 | Gray Cell Layout                                                            | 209  |

| 7.13 | Half Adder Layout                                                           | 209  |

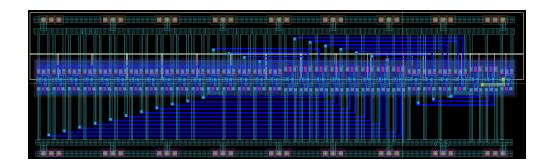

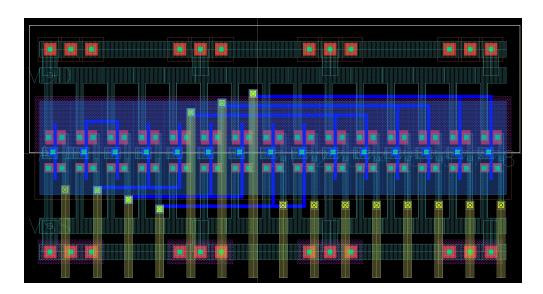

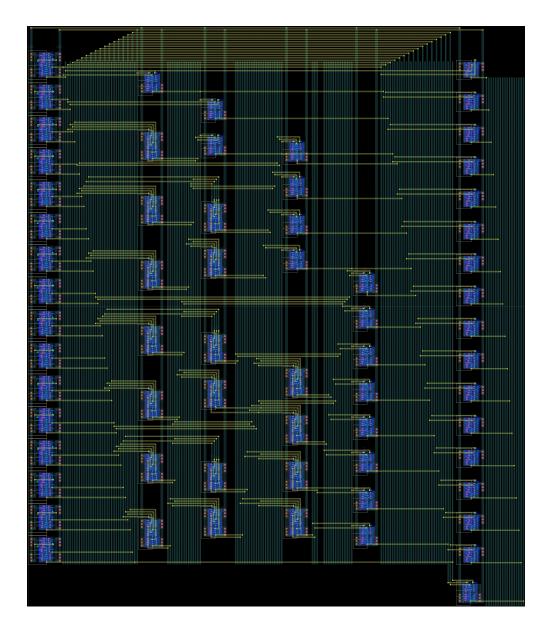

|      | Sklansky Adder Layout                                                       |      |

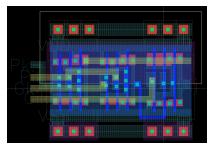

|      | Up/Down Counter Layout                                                      |      |

|      | 32-bit LFSR Layout                                                          |      |

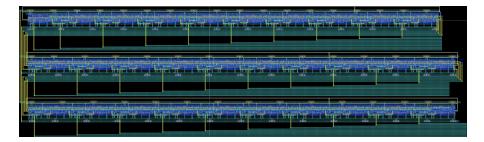

| 7.17 | 30-bit PISO Layout                                                          | 211  |

| 7.18 | 84-bit PISO Layout                                                   |

|------|----------------------------------------------------------------------|

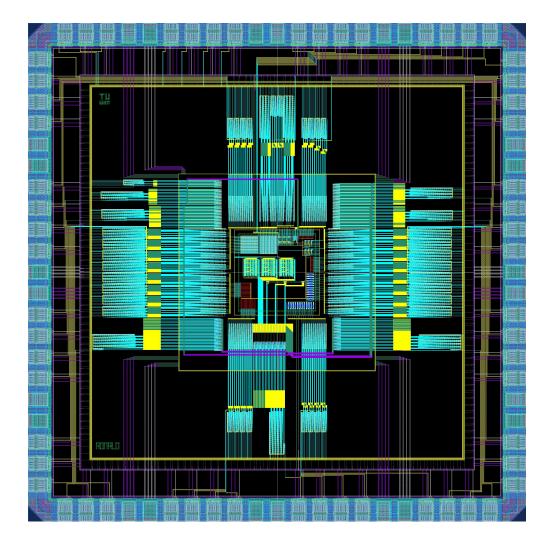

| 7.19 | ASIC layout with Targets, Measurements and PISO circuits 212         |

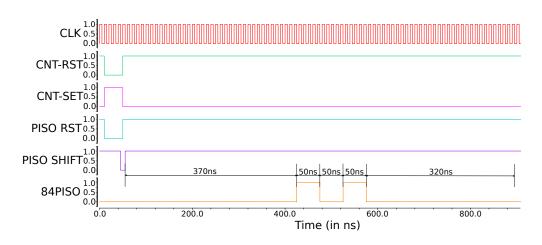

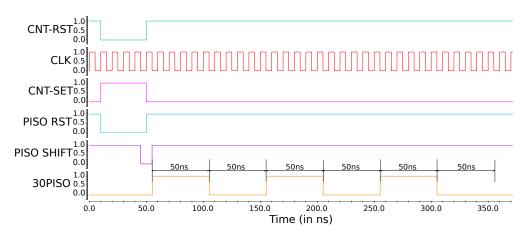

| 7.20 | Behavior of the Counters (read out from 84-bit PISO) after Reset 214 |

| 7.21 | Behavior of the Counters (read out from 30-bit PISO) after Reset 214 |

| 7.22 | Behavior of the Counters (read out from 84-bit PISO) after Program-  |

|      | ming 10 Transitions                                                  |

| 7.23 | Behavior of the Counters (read out from 30-bit PISO) after Program-  |

|      | ming 10 Transitions                                                  |

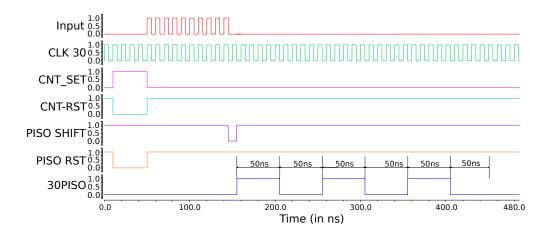

| 7.24 | SETs in the Target Circuit read out by the 30-bit PISO               |

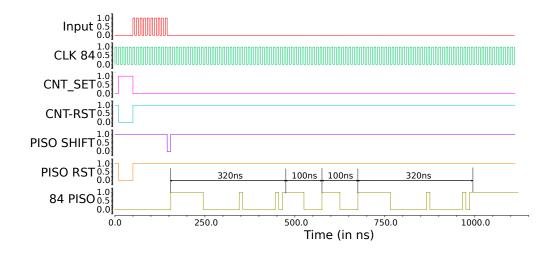

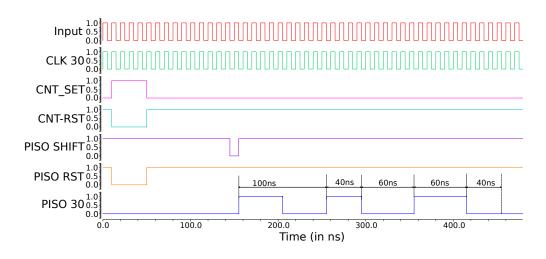

| 7.25 | SETs in the Target Circuit read out by the 84-bit PISO               |

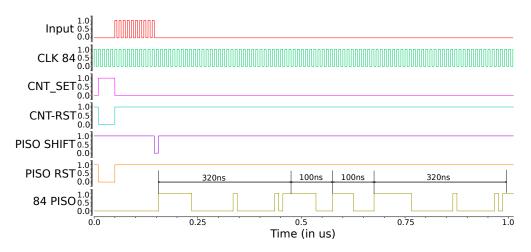

| 7.26 | SETs in the Sklansky Adder read out by the 110-bit PISO              |

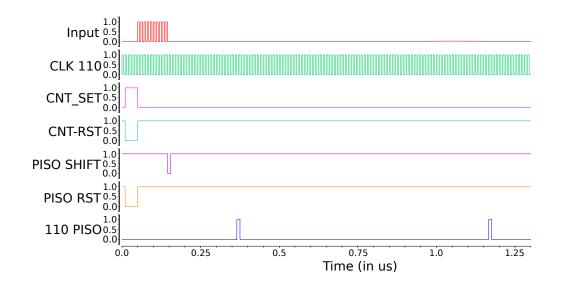

| 7.27 | SET in the Inverter Tree read out by the 75-bit PISO                 |

| 7.28 | Interface Architecture                                               |

| 7.29 | Timeline of our Architecture Setup                                   |

|      |                                                                      |

# **List of Tables**

| 2.1        | Truth Table of Muller C-Element                                                                                           | 0 |

|------------|---------------------------------------------------------------------------------------------------------------------------|---|

| 3.1<br>3.2 | Comparison of Radiation Hardening Mechanisms for Muller C-element 42<br>Comparison of Different Fault-Tolerant Mechanisms |   |

| 3.3        | Required sizing for different choices of current pulse parameters, all with a charge of 450fC                             | 4 |

| 3.4        | Required sizing for different choices of current pulse parameters, all with a charge of 300fC                             | 5 |

| 3.5        | Comparison of Different Radiation-Tolerance Mechanisms                                                                    |   |

| 3.6        | Comparison of Different Fault-Tolerant Mechanisms                                                                         | 9 |

| 4.1        | Truth Table of Inverter                                                                                                   |   |

| 4.2        | Truth Table of NAND gate 84                                                                                               |   |

| 4.3        | Truth Table of NOR gate                                                                                                   |   |

| 4.4        | Truth Table of D-Flip-Flop                                                                                                |   |

| 4.5        | Truth Table of XOR gate                                                                                                   |   |

| 4.6        | Number of Transistors for Different Architectures                                                                         | 2 |

| 4.7        | Hardware Overhead Analysis for Measurement Setup                                                                          | 3 |

| 4.8        | Operation of the LFSR Counter in No-Fault Scenario                                                                        | 4 |

| 4.9        | LFSR Counter – SETs in XNOR Gates & Flip-Flops                                                                            | 5 |

| 4.10       | Fault Analysis of the Up/Down Counter                                                                                     | 7 |

| 4.11       | Fault Dictionary                                                                                                          | 8 |

|            | Hardware Overhead Analysis                                                                                                |   |

| 5.1        | Fault Coverage of the Static Inverter Tree Architecture                                                                   | 8 |

| 5.2        | Fault coverage of the proposed architecture (symmetric cases for which                                                    |   |

|            | identical arguments apply are shown in parentheses)                                                                       |   |

| 5.3        | Fault Dictionary for Sklansky Adder                                                                                       | 6 |

| 5.4        | Fault Dictionary for Sklansky Adder                                                                                       | 7 |

| 5.5        | Fault Dictionary for Sklansky Adder                                                                                       | 8 |

| 5.6        | Fault Dictionary                                                                                                          | 2 |

| 5.7        | Fault Dictionary                                                                                                          | 3 |

| 5.8        | Fault Dictionary for Inverter Tree                                                                                        |   |

| 5.9        | Fault Dictionary for Inverter Tree                                                                                        |   |

| 5.10       | Fault Dictionary for Inverter Tree                                                                                        |   |

|            |                                                                                                                           |   |

| 6.1 | Recording capabilities (vs. reference count) of Architectures I-IV for           |

|-----|----------------------------------------------------------------------------------|

|     | different charges injected in an inverter                                        |

| 6.2 | Architecture (II) & (IV) – Measurement Statistics – $Q_{SET}$ =1.06pC 161        |

| 6.3 | Sequence of addressing in the counter array                                      |

| 6.4 | Fault Dictionary for SETs in the Target Circuit                                  |

| 6.5 | Fault Dictionary (excerpt): SEUs in the Up/Down Counters 179                     |

| 6.6 | Values for $P_{fail}(k)$ for $N = 14$ and different values of $C, k. \ldots 185$ |

| 7.1 | SET Sensitivity Architectures                                                    |

| 7.2 | SET Propagation Architecture                                                     |

| 7.3 | Leaf Cells with die area                                                         |

| A.1 | FRad Pin List                                                                    |

| A.2 | FRad Pin List                                                                    |

| A.3 | FRad Pin List                                                                    |

| A.4 | MUX and CUT combination                                                          |

# CHAPTER 1

### Introduction

Economic progress and technical advancement of the commercial semiconductor industry in the 1960s completely changed the way electronic components were purviewed [127]. This technology advent created a resilient components market for design against radiation. Since then, radiation tolerant components are widely used only in areas such as satellites, spacecrafts (abundance of radiation particles in space), nuclear power stations (sensors), military aircraft's (against atmospheric particles) and nuclear weapons. Typically to harden the circuits against radiation insulating substrates, redundancy, hardened latches, etc. are employed. The aggressive expansion of the consumer and business markets in the 90s has dramatically affected the development of radiation resilient hardware, which was only a tiny fraction of the commercial market [127].

Currently in the nano age shrinking feature sizes are the key to the progress in VLSI technology with respect to clock speed, dynamic power, integration density etc. However, this increases the susceptibility to faults (due to their smaller geometries and critical charge [133, 63, 75]), ultimately making radiation effects very relevant for commercial circuits. It is also argued in the literature [16, 133, 50, 34, 15] that, while with older technologies (130nm and above) radiation-induced transient errors used to be relevant for aerospace applications only, now with recent technologies, they are becoming an issue even for earth-bound applications, making the need for efficient radiation hardening mechanisms a pertinent problem that is not only restricted to specific safety-relevant functions but may also apply to future commodity circuits. Previously, the type of faults being dealt with in commercial semiconductor components were aging [30, 88, 91], electric wear-out [79, 31], stuck-at faults [116, 22, 115], stuck-open faults [96, 67, 99, 121] and manufacturing defects [118, 139, 83]. There is a huge body of work to rely upon when it comes to these "classic" sources of errors, but, for radiation-induced errors, which are increasingly dominating the failure rate of deep sub-micron VLSI circuits [75, 16], there is comparatively very little available.

Our main concern in the thesis are radiation-induced errors, collectively termed *single-event effects* (SEEs) in literature. Technology scaling has increased the im-

portance of these errors in digital circuits, furthermore, it has increased the requirement for SEE studies. SEEs occur when the active area of a VLSI circuit is hit by ionizing particles (or even by neutrons, which typically result from heavy ion interactions with nitrogen or oxygen atoms in the atmosphere). There are two types of SEEs namely destructive and non-destructive ones. As opposed to permanent (destructive) SEEs such as latch-up, threshold voltage shifts and burn-outs in power semiconductors [113, 40, 128], the primary concern in modern VLSI circuits are non-destructive SEEs. The errors resulting from non-destructive SEEs are not permanent but rather transient (i.e., can be corrected).

Consequently a systematic study of radiation effects on a given VLSI circuit is no more an exotic task of some space engineer, but a necessity even for everyday products, and novel, cost-effective radiation tolerance methods need to be developed. In order to be able to build efficient radiation tolerant hardware, one must have a good understanding of SEEs. The hardware that needs to be hardened should be exposed to radiation and the effects must be observed. This would provide us an insight on the vulnerabilities of the hardware. Performing the same process for standard logic gates would help us build any hardware that can be protected against radiation. Our thesis aids in building a solid knowledge on SEEs in digital circuits, that would enable anyone with basic knowledge of semiconductor physics to build efficient radiation hardened circuits.

### **1.1** Motivation

There are three types of non-destructive SEEs in digital circuits:

- ★ Single Event Transients (SETs)

- ★ Single Event Upsets (SEUs)

- \* Single Event Functional Interrupts (SEFIs)

When an energized particle strikes the silicon, it transfers its energy by creating free electron-hole pairs, resulting in a dense ionized layer in the region of impact. This ionization in turn generates a transient current pulse that can cause an upset when interpreted as a signal in the circuit [156]. If the current induced by the particle strike is high enough the ON-transistor cannot balance it and a voltage change at the node will occur causing a SET. If the SET manifested in the combinational circuit propagates to a sequential circuit or a storage cell then it could lead to an SEU (also called "soft error"). Unfortunately, SEUs may also occur if a transistor within the storage element is affected by a particle strike. A soft error which would cause a temporary loss of device functionality in a detectable way, but would not require power cycling of the device to restore operability is called as SEFI. If the voltage on the struck node is recovered by the current feed through the ON-transistor no SET will be observed. In this thesis we focus only on SETs and SEUs in digital circuits.

### 1.1.1 SET Model

In order to trigger these effects in a digital circuit we need to either build an elaborate device level model, or a simple model that only considers the circuit architecture (transistor placement). Previously SET models were built only for space applications, mainly to construct radiation mitigating components. Recent trends in electronics such as technology scaling require us to build SET models not only to construct rad-hard components but to understand charge distribution, SET generation, SET propagation, etc, in digital circuits. A device level model typically consumes a lot of time in executing a simple simulation on a larger circuit to describe the SEEs (as it takes into account technology parameters, parasitic load, etc.,), hence is impractical to use. In contrast, the simple model (that does not take into consideration the technology parameters or parasitic load) completes a simulation of million gates in hours, but does not model the SEEs accurately. This raises the need for a model that accurately describes the SEEs in digital circuits.

Robust circuit design – in particular, for critical applications in space and aerospace, needs models that accurately describe SET/SEU generation and propagation in modern VLSI technology, yet are easy and efficient to use at early design stages: Such models both allow to assess the radiation tolerance of different architectural designs and hardening techniques and to estimate the final soft-error rate of a circuit. Moreover, to elaborate more efficient, cheaper solutions for radiation mitigation, the propagation and masking of SETs must be precisely understood.

Modeling radiation effects both on the analog and on the digital level have their own challenges, like:

- How does a circuit's susceptibility to radiation depend on its own activity (rate of ongoing transitions during exposure)?

- How to precisely represent the charge deposition caused by the particle impact in an analog simulation?

### **1.1.2 Soft Error Rate**

*Soft error rate* (SER) is the rate at which SEUs occur in a digital circuit. The three primary reasons for the increase in SERs in digital circuits over the years are:

- · increased circuit complexity results in more hit targets

- decreasing feature sizes and supply voltages decrease the electrical charge used for representing information, which makes it more likely for a particle hit to create an SEE

- increasing clock frequencies increase the probability that an SET generated in combinational logic gates gets latched and hence causes an SEU.

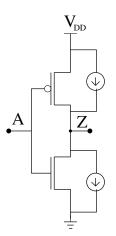

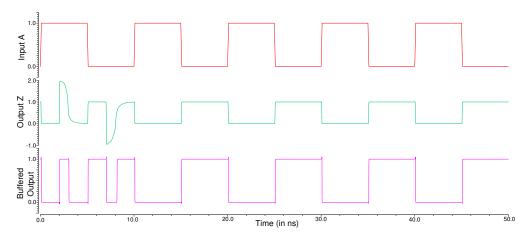

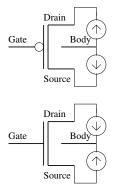

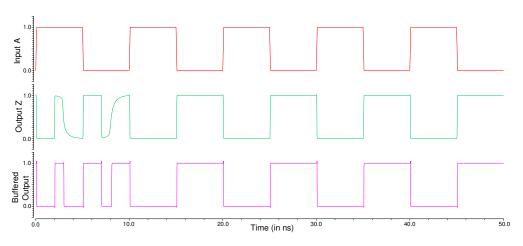

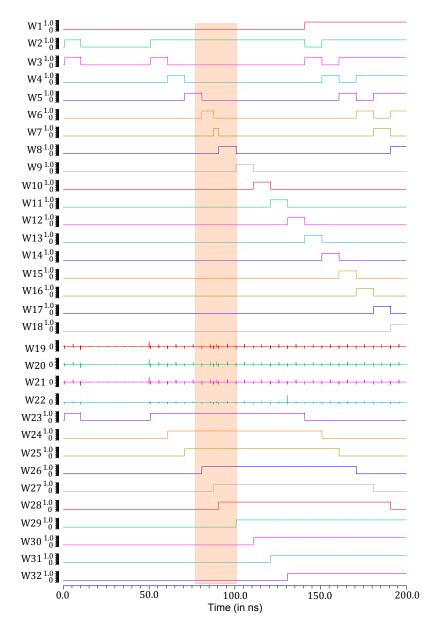

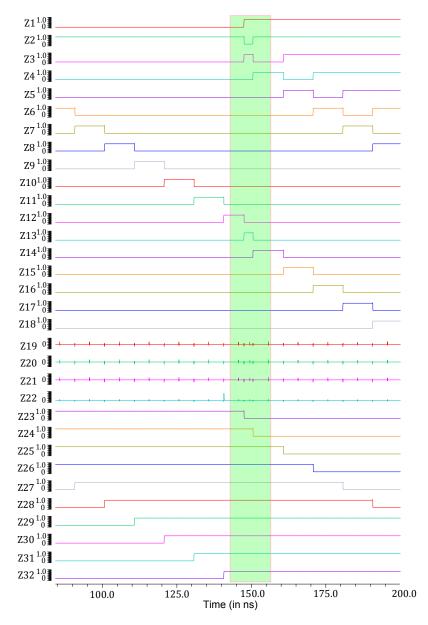

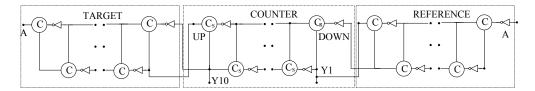

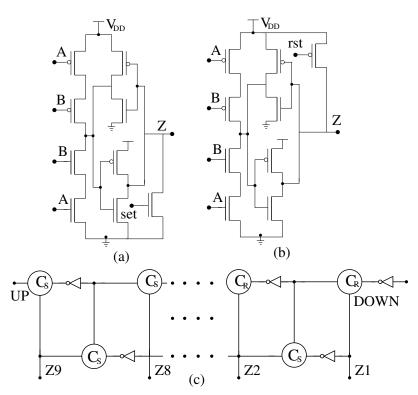

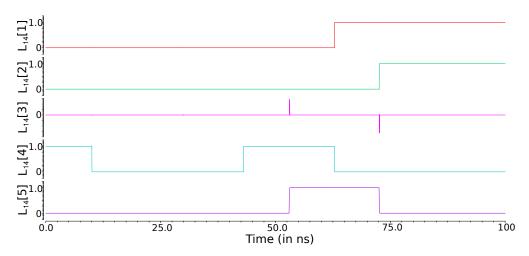

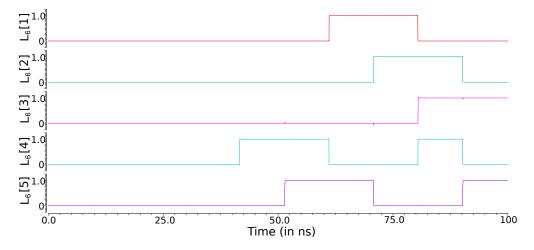

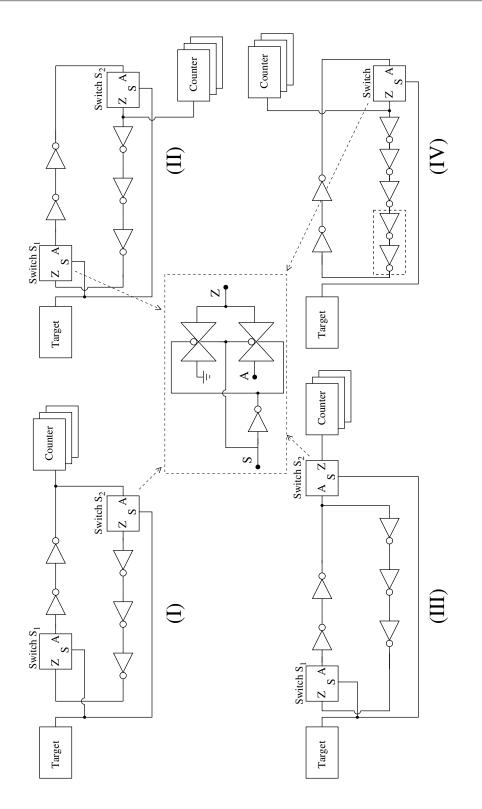

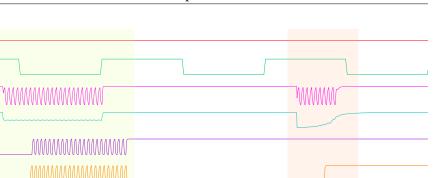

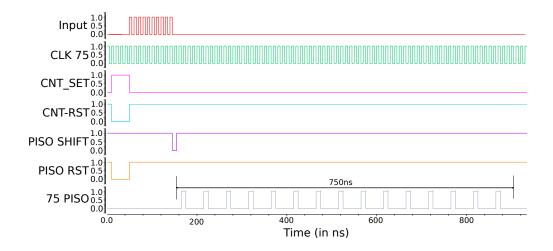

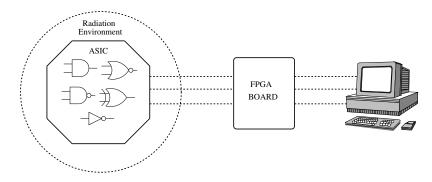

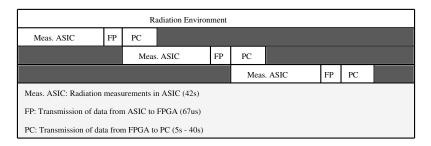

To compute the SER of a given chip, simulation [50, 90, 136, 16], probabilistic analysis [32, 90, 110, 119, 133, 130] as well as validating measurements[142, 61,