an der

# Programmanalyse und Verifikation von SPS-Programmen

## **DISSERTATION**

zur Erlangung des akademischen Grades

### Doktor der technischen Wissenschaften

eingereicht von

#### Gernot Kucera

Matrikelnummer 6026191

| Fakultat für Informatik der Technischen Universität Wien              |

|-----------------------------------------------------------------------|

| Betreuung: Ao.UnivProf. DiplIng. Dr. techn. Gernot Salzer             |

| Diese Dissertation haben begutachtet:                                 |

|                                                                       |

| Em. O.UnivProf. DiplIng. u. Ing. (grad.) DrIng. Gerhard-Helge Schildt |

|                                                                       |

| UnivProf. DrIng. Prof. h.c. Stefan Böhm                               |

| Wien, 30.06.2017                                                      |

| Gernot Kucera                                                         |

# Erklärung zur Verfassung der Arbeit

Gernot Kucera Hermesstraße 145, 1130 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit - einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Wien, 30.06.2017

Gernot Kucera

# **Danksagung**

Speicherprogrammierbare Steuerungen und Steuerungstechnik begleiten nahezu meinen gesamten beruflichen Werdegang. Besonderer Dank gilt meinen Betreuern, die meine Interessen für diese Arbeit geteilt und gefördert haben.

Herrn Prof. Salzer danke ich, dass er meine Arbeit durch seine Anregungen und Diskussionsbeiträge aktiv begleitet hat. Insbesondere sein kritischer Blick auf die Auswahl der von mir verwendeten Quellen hat meinen Blick geschärft und damit meine Arbeit verbessert.

Herrn Prof. Schild danke ich für seine kritischen Fragestellungen, die wesentlich zur Verbesserung und zur Verständlichkeit des Textes beigetragen haben. Auch Beispiele aus seiner langjährigen Berufserfahrung haben mir weitergeholfen, den Blick auf das Wesentliche nicht aus den Augen zu verlieren. Seine Anregungen zu Erklärungen und Detaillierungen von Sachverhalten, die ich als selbstverständlich und damit als gegeben betrachtet hatte, unterstützen die Verbreitung der Erkenntnisse in praktische Umsetzungen.

Herrn Prof. Böhm danke ich für seine Bereitschaft meine Arbeit aus der Sicht seiner Expertise zu begutachten.

Meinem Freund Herbert Paulis danke ich für sein Lektorat und den gezeigten besonderen Spürsinn, versteckte Fehler und Ungenauigkeiten in der Ausdrucksweise aufzudecken.

Meiner Familie danke ich für die mir entgegengebrachte Geduld und das Verständnis für meine Arbeit, welche neben einer beruflichen Vollauslastung nicht gezählte Wochenenden und Nachtstunden in Anspruch genommen hat.

Wien, im Juni 2017

Gernot Kucera

# Kurzfassung

Speicherprogrammierbare Steuerungen (SPS) werden zur Lösung von Automatisierungsaufgaben technischer Systeme und Anlagen genutzt. Die Herausforderung an die moderne Automatisierungstechnik ist die Beherrschung der Komplexität von Prozessen. Innerhalb dieser Prozesse ist dies durch die steigende Anzahl der Signale und damit verbunden durch immer größere Datenmengen gekennzeichnet. In den dazu verwendeten Rechnersystemen nehmen SPS eine wichtige Rolle ein. Nicht nur Steuerungsaufgaben, sondern auch Betrachtungen zur Zuverlässigkeit und zur Sicherheit und die Umsetzung geeigneter Maßnahmen dazu werden immer stärker in den Mittelpunkt der Automatisierung gerückt.

Als programmgesteuerte Automatisierungscomputer werden SPS in nahezu allen Bereichen der Anlagentechnik beginnend bei chemisch technologischen Anlagen bis hin zu Maschinensteuerungen eingesetzt. SPS werden darin als sichere Rechensysteme für hoch verlässliche Steuerung und Regelung technischer Prozesse genutzt. Der ständig steigende Automatisierungsgrad neuer technischer Systeme und der Wunsch nach immer mehr Funktionalität und Flexibilität in Automatisierungseinrichtungen führen zwangsläufig zu höherer Komplexität der sie bereitstellenden Hard- und Softwaresysteme. Damit wird die Frage der Zuverlässigkeit und Sicherheit zum zentralen Problem des Entwurfs und der Realisierung neuartiger Automatisierungssysteme.

Nicht nur für in sicherheitsrelevanten Anwendungen eingesetzte SPS Systeme muss für das betrachtete System das ausfallsicherheitsgerichtete Verhalten nachgewiesen werden. Dazu sind oft zeitaufwändige Tests während der Phase der Inbetriebsetzung notwendig. Anlagefunktionen werden dabei verifiziert und validiert. Eine wesentliche Rolle spielen dabei die SPS-Programme. Weil die Leistungsfähigkeit von SPS-Systemen im Zuge der technischen Weiterentwicklung zusammen mit den Anforderungen an solche Systeme Schritt gehalten hat, sind Systeme mit mehreren Tausend Signalzuständen die Regel und nicht die Ausnahme. Das exponentielle Anwachsen der möglichen Systemzustände ist bekannt als das "state explosion problem", die Beherrschung des Problems Gegenstand der Forschung.

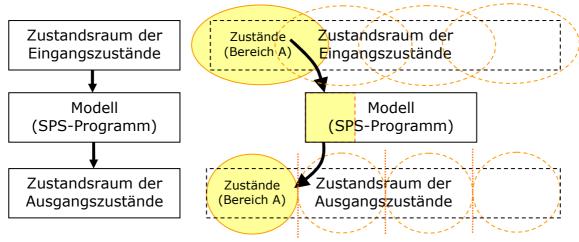

Als Beitrag zur Beherrschung der Komplexität zeigt diese Arbeit, wie durch die Zerlegung der Systemfunktionalität eines umfangreichen durch eine SPS gesteuerten Systems die Gesamtaufgabe einer Verifikation automatisiert unterstützt wird, in dem durch Segmentierung SPS-Programmbereiche definiert werden, die im Sinne der Gesamtfunktion von Programmteilen überblickbar und damit handhabbar werden. Diese SPS-Programmbereiche werden einzeln einer Verifikation zugänglich gemacht. Die Zerlegung selbst erfolgt durch automatisierte Analyse des vom Anwender einer SPS erstellten Anwender-Programms.

Die Analyse von Anwender-Programmen speicherprogrammierbarer Steuerungen ist ein Teilschritt für die automatisierte Verifikation. Zweck der Analyse ist es, einerseits mögliche Probleme im Programm einer SPS aufzudecken und andererseits ein SPS-Programm einer weitgehend automatisierten Verifikation zugänglich zu machen.

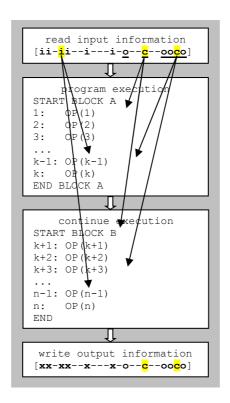

In der Folge werden Programmkonstrukte einer SPS als Segmente bezeichnet, die gleichzeitig einzeln verifizierbare Einheiten sind. Frei nach dem Ausspruch "divide et impera" kann mit Hilfe von Analysetechniken ein SPS-Programm geeignet zerlegt werden. Bezogen auf einzelne Segmente wird dadurch der Untersuchungsraum stark verkleinert. Die zulässige Größe eines Segments kann durch das Verändern seiner Grenzen an die Rechenleistung des Untersuchungssystems angepasst werden. Einzige Voraussetzung für die Verifikation ist, dass ein SPS-Programm vollständig untersucht wird. Deshalb werden bei Mehrfachverwendung von Informationen die Segmentgrenzen im Untersuchungsraum derart angepasst, dass auch Überschneidungen durch Mehrfachverwendung von Programmelementen vollständig bei der Bearbeitung berücksichtigt werden. Zweckmäßigerweise werden hierzu Minima für die Überschneidungen bestimmt.

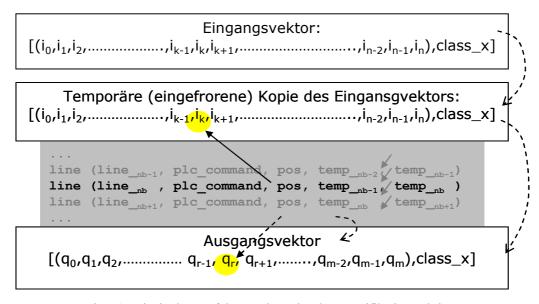

Die Tatsache, dass bei einem SPS-Programm von "Linearität" bei der Programmbearbeitung ausgegangen werden kann, weil speziell bei sicherheitsrelevanten Steuerungen Programmkonstrukte mit Rückwärtssprüngen oder Programmschleifen unzulässig sind, erleichtert die Aufgabe. Untersucht wird der vollständige Lösungsraum innerhalb jedes Segments. Genügen daher alle Kombinationen der als Startbedingung vorausgesetzten Eingangsabbilder (Eingangsvektoren) den Anforderungen an die Ausgangsabbilder (Ausgangsvektoren), ist die Verifikation erfolgreich. Durch Rückwärtsanalyse werden für jeden SPS-Ausgang die bestimmenden Elemente zugeordnet. Damit wird der Lösungsraum vollständig in Bezug auf die Ausgangsabbilder abgebildet.

Das zugehörige Konzept für die Verifikation folgt den Regeln klassischer Verifikationstechniken: Eingangsabbilder werden als Vorbedingungen behandelt und mathematisch untersucht, ob zugehörige Ausgangsabbilder als Ergebnis erreicht werden. Anstatt den gesamten Verifikationsschritt auf einmal durchzuführen, wird ein mehrfach gestuftes Verfahren vorgeschlagen. Grob gesehen können Schritte identifiziert werden: die Voruntersuchungen zur Syntax mit semantischen Anteilen, die Zerlegung mit Verifikation von Teilbereichen und die Untersuchung auf Vollständigkeit.

Das Ende einer Untersuchung, die erfolgreiche Verifikation, ist nicht von der Reihenfolge der Festlegung der Prämissen für die Verifikation abhängig. Im konventionellen Ansatz zur Verifikation werden zuerst die Bedingungen definiert zusammen mit zu erzielenden Ergebnissen, um in Relation mit dem Quellcode in möglichst wenigen Schritten eine Entscheidung herbei-

zuführen. Prinzipiell ist dies beim hier verfolgten Ansatz genauso. Im Unterschied dazu erlaubt jedoch die hier verfolgte Methode die Nutzung auch so genannter "offener" Referenzen, die erst in einem weiteren Zwischenschritt zu Prämissen werden. Zuletzt werden Verifikationsergebnisse von Teilbereichen zu einer Verifikation des gesamten SPS-Programms rekombiniert.

Schlüsselwörter: Programmanalyse, Verifikation, SPS-Programm

#### **Abstract**

Programmable Logic Controllers (PLC) are used in automation of technical systems and machines. The challenge for modern automation is in the handling of the complexity of the processes. These processes are characterized by an increasing number of signals and linked to this is an increasing amount of data. PLC used in the processing systems play an important role. Not only controlling tasks but also reliability and safety issues and their realisation come more and more into the focus of automation.

PLC are used as programmable automation controllers in almost all areas of plant engineering all the way from chemical plants to production machinery controls. In these fields PLC are used as safe computing systems for safety relevant controls and feedback control of technical processes. The increasing level of automation in new technical systems and the demand for more and more functionality and flexibility in automation systems inevitably lead towards higher complexity of supporting hardware and software systems. This makes problems of reliability and safety a central problem in design and realisation of new automation systems.

Safeguarding against failure for systems in question must be verified not only for safety relevant applications. This often calls for time-consuming testing during installation of systems. System functionalities get verified and validated in the process. PLC software plays a critical role in this. As the performance of PLC systems has increased with modern technical enhancements together with the requirements for such systems, nowadays systems with several thousands of signal conditions are no exceptions any more but rather state of the art. The exponential growth of possible system states is known as "state explosion problem" and research currently focuses on dealing with this problem.

This thesis contributes to handling the complexity by showing how automated verification of a large PLC controlled system can be supported by breaking down the functionality of the system. This is achieved by segmenting PLC program components to make them straightforward and therefore manageable in the sense of the full functionality. These PLC program segments will now be put to verification part by part. The segmentation itself is done by means of automatic analysis of the user-generated PLC program.

Analysing user programs for programmable logic controllers (PLC) is a step towards automatic verification. Purpose of the analysis is on one hand to find possible problems in the PLC program and on the other hand to make the PLC program available for an in most parts automated program verification.

Subsequently, program constructs for PLC will be called segments, which will at the same time be stand-alone verifiable components. According to the saying "divide et impera" analysis techniques can be used to fittingly decompose a PLC program. Regarding single segments, the scope for examination will be made significantly smaller by this. The size of one segment can be adapted to the performance capabilities of the analysing system by reducing its size. The only requirement for verification is that the PLC program must be analysed completely. Therefore, if information is used repeatedly, segment borders will be adapted in such a way that overlapping of code parts is fully considered during processing. Overlapping minima will be defined appropriately for this purpose.

The task is made easier by the fact that linearity can be assumed with PLC programs as in safety relevant programs loops and backward jumps are not allowed. For each segment the full solution space will be analysed. So if all possible combinations of input images (input vectors) satisfy the requirements of the output images (output vectors) the verification is successful. By backward analysis every PLC output has its determining elements assigned. By this the solution space will be fully mapped with regard to the output images.

The associated verification concept for the verification clings to the common verification rules. Input images will be considered as preconditions and mathematically analysed if they lead towards corresponding output images as results. Instead of performing a complete verification in one single step, a multiple step approach is suggested. In a bigger picture, the following steps can be identified: syntactic pre-examinations with semantic parts, breaking the system down and verifying portions, and a test for completeness

An examination finish, the successful verification, does not depend on the order of defining the assumptions for verification. In the conventional approach first all conditions together with the expected results are defined to provide a result together with the source code in as little steps as possible. The approach discussed here basically works the same but the method described allows for so called open references which will become assumptions only at later steps. Finally, all verification results for the various parts will be recombined into a verification of the complete PLC program.

Key words: program analysis, verification, PLC program

#### Vorwort

Obwohl SPS bereits eine hohe Verbreitung haben, gibt es nur wenige Ansätze, Steuerungsprogramme zu verifizieren. Ein Grund dafür ist das als "state explosion problem" bekannte Phänomen, dass mit jeder neu eingeführten binären Variablen sich die Anzahl der Untersuchungen verdoppelt.

Die bekannten Arbeiten nutzen Methoden, die entweder sehr komplex und damit aufwendig umzusetzen sind oder man beschränkt die Funktionalität und damit die Möglichkeiten zur Verifikation so stark, dass sie in der Praxis nur geringen Nutzen haben. Die Durchführung einer Verifikation ist ein sehr aufwendiger Vorgang. In dieser Arbeit wird eine Vorgehensweise vorgeschlagen, die weitgehend automatisiert ablaufen und darüber hinaus parallel zur Erstellung des SPS-Programms erfolgen kann.

Auch hier wurden Einschränkungen in der Funktionalität durch Beschränkung der möglichen SPS-Befehle auf die in Steuerungen am häufigsten verwendeten gemacht. Auf Grund des modularen Aufbaus der einzelnen Programme sind weitere Funktionen jedoch vergleichsweise einfach nachrüstbar.

Die vorliegende Arbeit bereitet SPS-Programme auf, um diese mit dem in "Schritte zur Verifikation von SPS-Programmen – Ist Prädikatenlogik eine Lösung?" [KP12] vorgestellen Verifikator der Verifikation zugänglich zu machen. In [KP12] wurde ein in "first order logic" (FOL) geschriebenes Programm als so genannter Verifikator eingeführt und für die Verifikation von SPS-Programmen genutzt. Die ersten Ideen zu diesem Buch stammen aus zwei Diplomarbeiten des Autors. Die Arbeiten "Entwicklung einer speicherprogrammierbaren Steuerung" (2000) und "Ertüchtigung einer Mikrocontroller Plattform zum Einsatz in sicherheitsgerichteten Anwendungen" (2001) führten zu Mikrocontrollersystemen, die mit einem Befehlsinterpreter das Sprachkonzept Anweisungslisten für die Anwenderprogramme genutzt hat.

Als Co-Autor von [KP12] hat Herbert Paulis das Verifikationsmodell beruhend auf dem von Loeckx und Sieber in "The Foundations of Program Verification" entwickelten formalen Modell beschrieben [KP12, Kapitel 6]. Auch die Die PROLOG-Verifikationsmaschine und die Hilfsprogramme [KP12, Kapitel 7, Anhang] stammen im Wesentlichen von Herbert Paulis, wobei Tests der Programme zur Überprüfung der Funktionalität gemeinsam durchgeführt worden sind.

Wien, im Juni 2017

Gernot Kucera

# Inhaltsverzeichnis

| Ku  | URZFASSUNG                                                              | I    |

|-----|-------------------------------------------------------------------------|------|

| AB  | STRACT                                                                  | V    |

| Vo  | PRWORT                                                                  | VII  |

| AB  | BILDUNGEN                                                               | XIII |

|     | BELLEN                                                                  |      |

|     |                                                                         |      |

| AB  | KÜRZUNGEN                                                               | XVII |

| 1   | EINFÜHRUNG                                                              | 1    |

| 1.1 | Motivation                                                              | 1    |

| 1.2 | Definition des Problems                                                 |      |

|     | 1.2.1 Funktionalität von SPS-Programmen                                 | 5    |

|     | 1.2.2 Spezifikation                                                     | 6    |

|     | 1.2.3 Verfikationstechnik, Begriffsabgrenzung und Verifikationsmethoden | 8    |

|     | 1.2.4 Formalisierung einer Spezifikation                                | 10   |

|     | 1.2.5 SPS-Programmiersprachen und Eigenschaften                         | 11   |

|     | 1.2.6 Lösungsansätze verwandter Arbeiten                                |      |

|     | 1.2.7 Zusammenfassung                                                   |      |

|     | 1.2.8 Abstraktion                                                       |      |

| 1.3 | Aufbau der Arbeit                                                       |      |

| 1.4 | Begriffe                                                                | 29   |

| 2   | SPS GRUNDLAGEN                                                          | 33   |

| 2.1 | Aufbau                                                                  | 33   |

| 2.2 | Arbeitsweise                                                            |      |

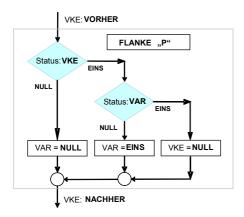

| 2.3 | Programmierung                                                          | 37   |

| 2.4 | Anweisungen und Speicherbereiche                                        | 38   |

| 3   | GLIEDERUNGSSTRUKTUREN VON SPS-PROGRAMMEN                                | 39   |

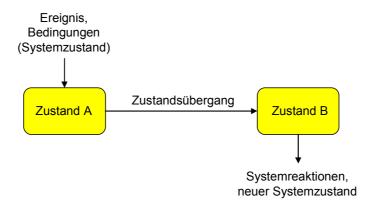

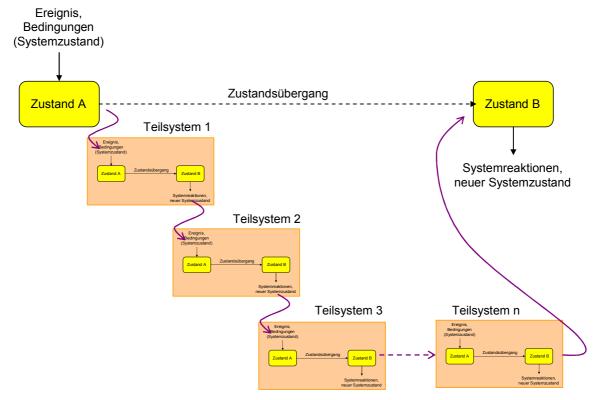

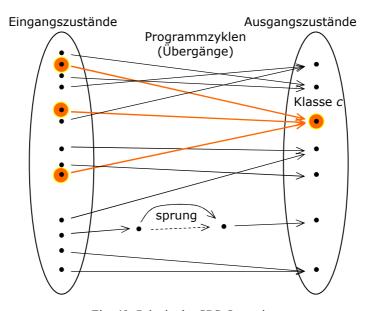

| 3.1 | Zustandsübergänge                                                       | 39   |

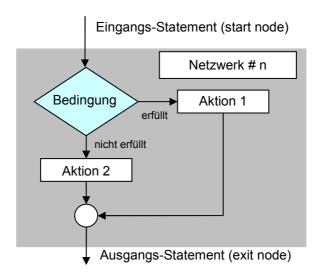

| 3.2 | Programmverzweigungen                                                   |      |

| 3.3 | Stufenmodell für die Programmüberprüfung                                |      |

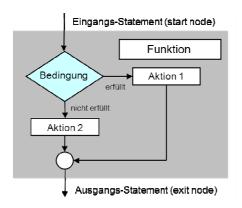

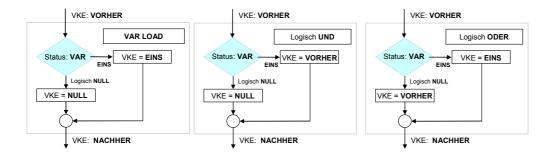

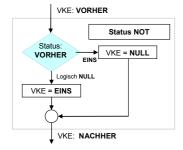

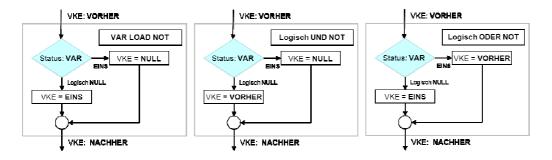

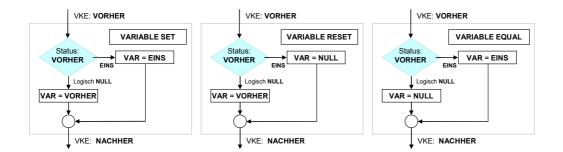

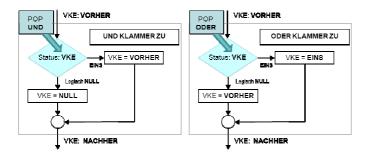

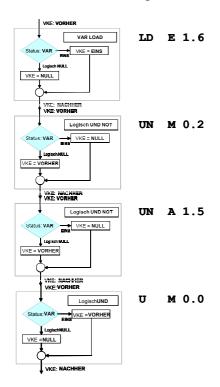

| 3.4 | Kommandos als Flussdiagramme                                            |      |

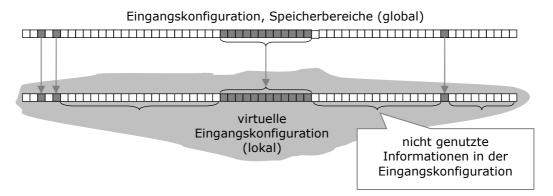

| 3.5 | Speicherbereiche für Zustandsabbilder                                   | 60   |

| 3.6 | Gruppierung von Kommandofolgen                                          | 62   |

| 4   | ANALYSE BEI UNBEKANNTER PROGRAMMSTRUKTUR                                | 67   |

| 4.1 | Programmierumgebungen                                                   | 69   |

| 4.2 | Analysetechniken                                                        |      |

| 4.3 | Programm-Module                                                         |      |

| 4.4                                                                                   | Semantische Programmanalyse                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77                              |

|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 4.5                                                                                   | Sonderfunktionen                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |

| 4.6                                                                                   | Weitere Überprüfung                                                                                                                                                                                                                                                                                                                                                                                                                                           | 84                              |

|                                                                                       | 4.6.1 Kombination von Programmdurchläufen (Zyklen)                                                                                                                                                                                                                                                                                                                                                                                                            | 84                              |

|                                                                                       | 4.6.2 Kreuz-Korrelation                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |

| 4.7                                                                                   | Zusammenfassung                                                                                                                                                                                                                                                                                                                                                                                                                                               | 86                              |

| 4.8                                                                                   | Rückwärtsanalyse                                                                                                                                                                                                                                                                                                                                                                                                                                              | 87                              |

| 4.9                                                                                   | Rückwärtsanalyse als Verifikationswerkzeug                                                                                                                                                                                                                                                                                                                                                                                                                    | 89                              |

| 4.10                                                                                  | Schlussbemerkungen                                                                                                                                                                                                                                                                                                                                                                                                                                            | 90                              |

| 5                                                                                     | ERWEITERTE PROGRAMMANALYSE                                                                                                                                                                                                                                                                                                                                                                                                                                    | 91                              |

| 5.1                                                                                   | Voranalyse                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 91                              |

| 5.2                                                                                   | Aufgaben                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 92                              |

| 5.3                                                                                   | Rückwärtsanalyse                                                                                                                                                                                                                                                                                                                                                                                                                                              | 94                              |

|                                                                                       | 5.3.1 Fall 1: Untersuchung bestimmter Ausgänge                                                                                                                                                                                                                                                                                                                                                                                                                | 95                              |

|                                                                                       | 5.3.2 Fall 2: Vollständige Einzelanalyse                                                                                                                                                                                                                                                                                                                                                                                                                      | 96                              |

|                                                                                       | 5.3.3 Fall 3: Untersuchung mehrerer Ausgänge                                                                                                                                                                                                                                                                                                                                                                                                                  | 97                              |

|                                                                                       | 5.3.4 Fall 4: Verträglichkeit                                                                                                                                                                                                                                                                                                                                                                                                                                 | 97                              |

|                                                                                       | 5.3.5 Fall 5: Kombinationen                                                                                                                                                                                                                                                                                                                                                                                                                                   | 97                              |

|                                                                                       | 5.3.6 Fall 6: Folgeuntersuchung                                                                                                                                                                                                                                                                                                                                                                                                                               | 97                              |

|                                                                                       | 5.3.7 Fall 7: Innere Struktur von Netzwerken                                                                                                                                                                                                                                                                                                                                                                                                                  | 98                              |

|                                                                                       | 5.3.8 Fall 8: Zusammenhänge in Programmstrukturen                                                                                                                                                                                                                                                                                                                                                                                                             | 98                              |

| 5.4                                                                                   | Ausschluss von Zuständen                                                                                                                                                                                                                                                                                                                                                                                                                                      | 99                              |

| 5.5                                                                                   | Zusammenfassung                                                                                                                                                                                                                                                                                                                                                                                                                                               | 100                             |

|                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                 |

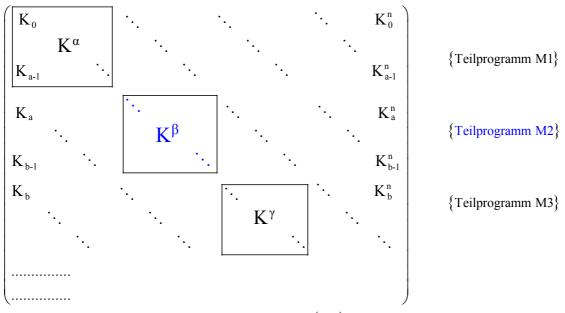

| 6                                                                                     | FORMALE DARSTELLUNG DER SPS                                                                                                                                                                                                                                                                                                                                                                                                                                   | 101                             |

| <b>6</b> 6.1                                                                          | FORMALE DARSTELLUNG DER SPS                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |

|                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 101                             |

| 6.1                                                                                   | Mathematisches Modell Formale Beschreibung Konzept zur Teilverifikation                                                                                                                                                                                                                                                                                                                                                                                       | 101<br>101<br>108               |

| 6.1<br>6.2                                                                            | Mathematisches Modell                                                                                                                                                                                                                                                                                                                                                                                                                                         | 101<br>101<br>108               |

| 6.1<br>6.2<br>6.3                                                                     | Mathematisches Modell Formale Beschreibung Konzept zur Teilverifikation                                                                                                                                                                                                                                                                                                                                                                                       | 101<br>101<br>108               |

| 6.1<br>6.2<br>6.3<br>6.4                                                              | Mathematisches Modell Formale Beschreibung Konzept zur Teilverifikation Eigenschaften von Konfigurationen  VORBEREITENDE ARBEITEN                                                                                                                                                                                                                                                                                                                             |                                 |

| 6.1<br>6.2<br>6.3<br>6.4                                                              | Mathematisches Modell  Formale Beschreibung  Konzept zur Teilverifikation  Eigenschaften von Konfigurationen                                                                                                                                                                                                                                                                                                                                                  | 101<br>108<br>111<br>115        |

| 6.1<br>6.2<br>6.3<br>6.4                                                              | Mathematisches Modell Formale Beschreibung Konzept zur Teilverifikation Eigenschaften von Konfigurationen  VORBEREITENDE ARBEITEN Programmsegmentierung                                                                                                                                                                                                                                                                                                       |                                 |

| 6.1<br>6.2<br>6.3<br>6.4                                                              | Mathematisches Modell Formale Beschreibung Konzept zur Teilverifikation Eigenschaften von Konfigurationen.  VORBEREITENDE ARBEITEN  Programmsegmentierung 7.1.1 Ablesen aus der Aufgabenstellung                                                                                                                                                                                                                                                              | 101<br>108<br>111<br>115<br>115 |

| 6.1<br>6.2<br>6.3<br>6.4                                                              | Mathematisches Modell Formale Beschreibung Konzept zur Teilverifikation Eigenschaften von Konfigurationen  VORBEREITENDE ARBEITEN  Programmsegmentierung 7.1.1 Ablesen aus der Aufgabenstellung 7.1.2 Nachträgliche Bestimmung                                                                                                                                                                                                                                |                                 |

| 6.1<br>6.2<br>6.3<br>6.4<br><b>7</b><br>7.1                                           | Mathematisches Modell Formale Beschreibung Konzept zur Teilverifikation Eigenschaften von Konfigurationen  VORBEREITENDE ARBEITEN  Programmsegmentierung 7.1.1 Ablesen aus der Aufgabenstellung 7.1.2 Nachträgliche Bestimmung 7.1.3 Anwendung Methoden zur Bestimmung von Vor- und Nachbedingungen Vordefinierte Funktionen                                                                                                                                  |                                 |

| 6.1<br>6.2<br>6.3<br>6.4<br><b>7</b><br>7.1                                           | Mathematisches Modell Formale Beschreibung Konzept zur Teilverifikation Eigenschaften von Konfigurationen  VORBEREITENDE ARBEITEN  Programmsegmentierung 7.1.1 Ablesen aus der Aufgabenstellung 7.1.2 Nachträgliche Bestimmung 7.1.3 Anwendung  Methoden zur Bestimmung von Vor- und Nachbedingungen Vordefinierte Funktionen Einordnung von Funktionen in die Verifikation                                                                                   |                                 |

| 6.1<br>6.2<br>6.3<br>6.4<br><b>7</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5               | Mathematisches Modell Formale Beschreibung Konzept zur Teilverifikation Eigenschaften von Konfigurationen.  VORBEREITENDE ARBEITEN  Programmsegmentierung 7.1.1 Ablesen aus der Aufgabenstellung 7.1.2 Nachträgliche Bestimmung 7.1.3 Anwendung  Methoden zur Bestimmung von Vor- und Nachbedingungen Vordefinierte Funktionen Einordnung von Funktionen in die Verifikation Zusammenfassung                                                                  |                                 |

| 6.1<br>6.2<br>6.3<br>6.4<br><b>7</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6        | Mathematisches Modell Formale Beschreibung Konzept zur Teilverifikation Eigenschaften von Konfigurationen  VORBEREITENDE ARBEITEN  Programmsegmentierung 7.1.1 Ablesen aus der Aufgabenstellung. 7.1.2 Nachträgliche Bestimmung 7.1.3 Anwendung Methoden zur Bestimmung von Vor- und Nachbedingungen Vordefinierte Funktionen Einordnung von Funktionen in die Verifikation Zusammenfassung SPS-Programmbeschreibung für sequentielle Abläufe                 |                                 |

| 6.1<br>6.2<br>6.3<br>6.4<br><b>7</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5               | Mathematisches Modell Formale Beschreibung Konzept zur Teilverifikation Eigenschaften von Konfigurationen.  VORBEREITENDE ARBEITEN  Programmsegmentierung 7.1.1 Ablesen aus der Aufgabenstellung 7.1.2 Nachträgliche Bestimmung 7.1.3 Anwendung  Methoden zur Bestimmung von Vor- und Nachbedingungen Vordefinierte Funktionen Einordnung von Funktionen in die Verifikation Zusammenfassung                                                                  |                                 |

| 6.1<br>6.2<br>6.3<br>6.4<br><b>7</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6        | Mathematisches Modell Formale Beschreibung Konzept zur Teilverifikation Eigenschaften von Konfigurationen  VORBEREITENDE ARBEITEN  Programmsegmentierung 7.1.1 Ablesen aus der Aufgabenstellung. 7.1.2 Nachträgliche Bestimmung 7.1.3 Anwendung Methoden zur Bestimmung von Vor- und Nachbedingungen Vordefinierte Funktionen Einordnung von Funktionen in die Verifikation Zusammenfassung SPS-Programmbeschreibung für sequentielle Abläufe                 |                                 |

| 6.1<br>6.2<br>6.3<br>6.4<br><b>7</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7 | Mathematisches Modell Formale Beschreibung Konzept zur Teilverifikation Eigenschaften von Konfigurationen  VORBEREITENDE ARBEITEN  Programmsegmentierung 7.1.1 Ablesen aus der Aufgabenstellung 7.1.2 Nachträgliche Bestimmung 7.1.3 Anwendung  Methoden zur Bestimmung von Vor- und Nachbedingungen Vordefinierte Funktionen Einordnung von Funktionen in die Verifikation Zusammenfassung SPS-Programmbeschreibung für sequentielle Abläufe Zusammenfassung |                                 |

| 6.1<br>6.2<br>6.3<br>6.4<br><b>7</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7 | Mathematisches Modell Formale Beschreibung Konzept zur Teilverifikation Eigenschaften von Konfigurationen  VORBEREITENDE ÅRBEITEN  Programmsegmentierung 7.1.1 Ablesen aus der Aufgabenstellung 7.1.2 Nachträgliche Bestimmung 7.1.3 Anwendung  Methoden zur Bestimmung von Vor- und Nachbedingungen Vordefinierte Funktionen Einordnung von Funktionen in die Verifikation Zusammenfassung SPS-Programmbeschreibung für sequentielle Abläufe Zusammenfassung |                                 |

| 8.4  | Überlegungen zur Vollständigkeit des Untersuchungsraums | 146 |

|------|---------------------------------------------------------|-----|

| 8.5  | Arbeitsschritte                                         |     |

| 8.6  | Beitrag der Programmanalyse                             | 147 |

| 9    | ERGEBNISSE                                              | 153 |

| 9.1  | Beitrag der Analyse                                     | 153 |

| 9.2  | Teilverifikation                                        |     |

| 9.3  | Testen                                                  |     |

| 9.4  | Erweiterungen                                           |     |

| 9.5  | Kombination der Teilergebissen                          |     |

| 9.6  | Verifikation                                            |     |

| 10   | SCHLUSSBETRACHTUNGEN                                    | 169 |

| Lit  | ERATUR                                                  | 175 |

| Ani  | HANG A: ALGORITHMEN FÜR SPS-BEFEHLE                     | 179 |

|      | ische Verknüpfungen                                     |     |

| _    | eiterungen im Wertebereich                              |     |

|      | HANG B: SPS-PROGRAMME                                   |     |

|      |                                                         |     |

|      | igungsautomat für Kohlebürsten                          |     |

|      | steine für Bohrstationen                                |     |

|      | stein für Wenden                                        |     |

| Baus | stein für Stampfen                                      | 204 |

| Ani  | HANG C: ANALYSE DURCH HILFSPROGRAMME                    | 213 |

| Beis | piele von SPS Programmbausteinen                        | 213 |

| Baus | stein FC21 Bohren                                       | 213 |

| Baus | stein FC34 Wenden                                       | 215 |

| Baus | stein FC38 Stampfen                                     | 218 |

| Zusa | ammenfassung                                            |     |

|      | vendung der Rückwärtsanalyse                            |     |

| Anw  | vendungsbeispiel: Bestimmen von Zusammenhängen          | 223 |

| Ani  | HANG D: VERIFIKATION MIT DEM VERIFIKATOR                | 227 |

| Allg | emeines                                                 | 227 |

| Veri | fikation mittels PROLOG                                 | 229 |

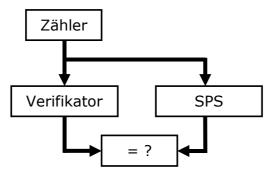

| SPS  | und Verifikator                                         | 234 |

| Anp  | assungen                                                | 235 |

| Vorg | gehensweise                                             | 236 |

|      | ulation als Teilverifikationsschritt                    |     |

|      | le Arbeit Verifikator - SPS                             |     |

|      | grammanalyse und Verifikation                           |     |

| _    | en mit dem Verifikator                                  |     |

|      | egoriesierung "bad states in result"                    |     |

|      | inzungen im Verifikator                                 |     |

| Schlussbemerkungen              | 254 |

|---------------------------------|-----|

| ANHANG E: LEBENSLAUF            | 255 |

| Universitätsstudien, Abschlüsse | 255 |

| Berufliche Tätigkeit            | 256 |

| Publikationen                   | 257 |

# Abbildungen

| Fig. 1: Zustandsraum und Zuordnung                            |     |

|---------------------------------------------------------------|-----|

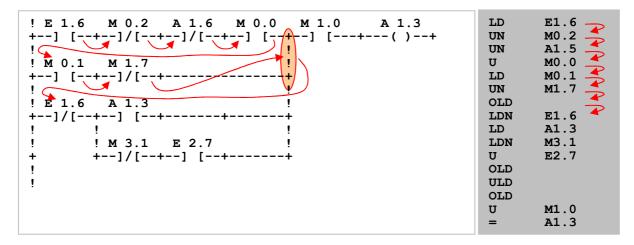

| Fig. 2: SPS-Programm, links KOP, rechts AWL (STEP 7)          | 34  |

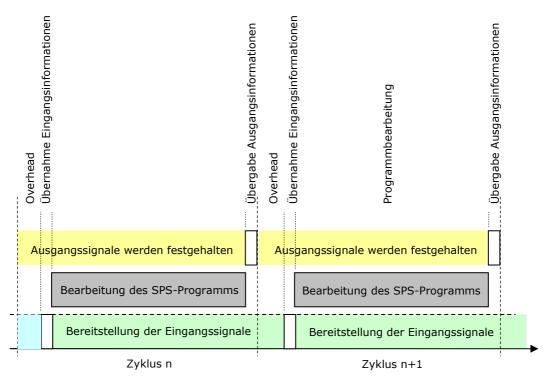

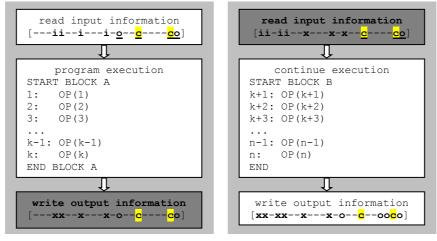

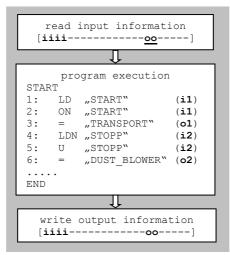

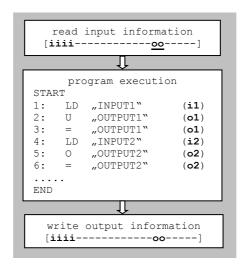

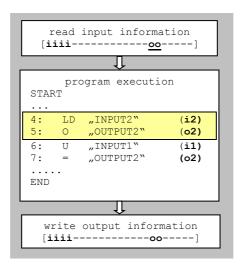

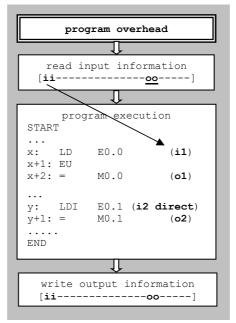

| Fig. 3: Zyklische SPS-Programmbearbeitung                     | 35  |

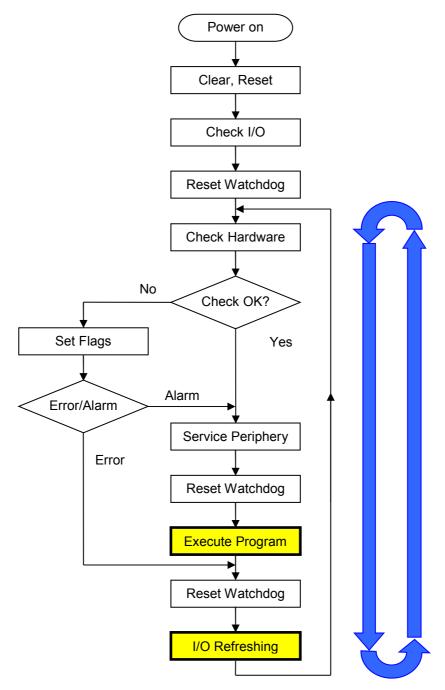

| Fig. 4: SPS-Zyklus mit Überwachungsfunktionen                 | 36  |

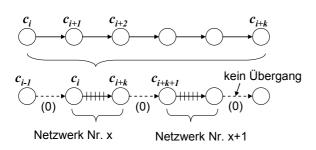

| Fig. 5: Übergang 1                                            | 39  |

| Fig. 6: Kommandofolge                                         | 39  |

| Fig. 7: Übergang 2                                            | 39  |

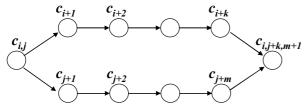

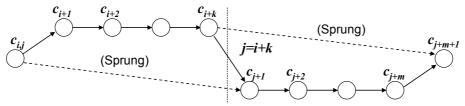

| Fig. 8: Nebenläufige Abläufe                                  | 41  |

| Fig. 9: Nebenläufige Abläufe sequenziert                      | 41  |

| Fig. 10: Beispiel Netzwerk 1 (KOP)                            |     |

| Fig. 11: Beispiel Netzwerk 1 (FUP)                            | 46  |

| Fig. 12: Beispiel Netzwerk 1 – Kommandofolge (Ausschnitt)     | 51  |

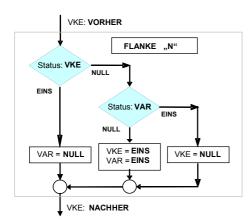

| Fig. 13: Flanke AWL                                           | 57  |

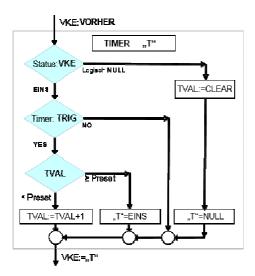

| Fig. 14: Zeitglied (AWL)                                      | 58  |

| Fig. 15: Speicherbelegung                                     | 61  |

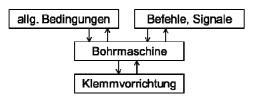

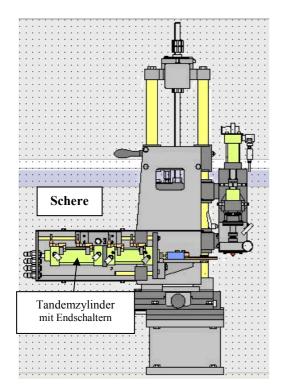

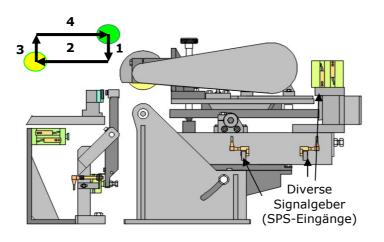

| Fig. 16: Bohrmaschine Übersicht                               | 63  |

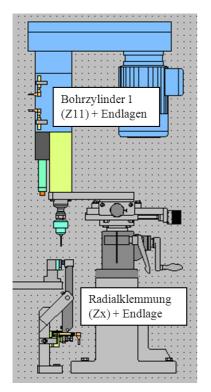

| Fig. 17: Bohrstation (schematisch)                            | 63  |

| Fig. 18: Stampfstation (schematisch)                          | 65  |

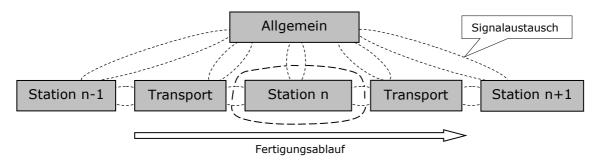

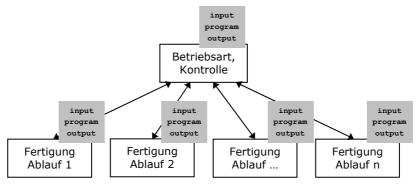

| Fig. 19: Programmstruktur Fertigungsablauf                    | 68  |

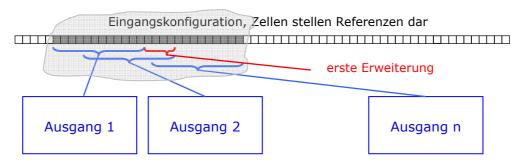

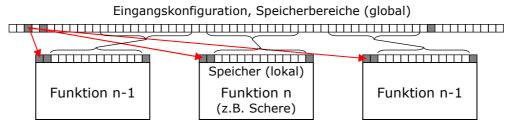

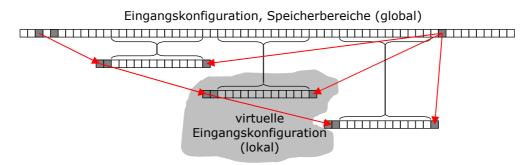

| Fig. 20: Speichernutzung 1                                    |     |

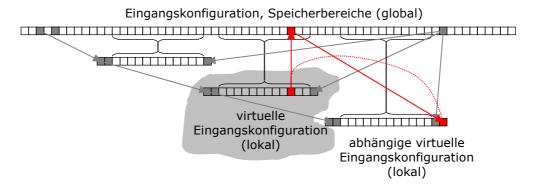

| Fig. 21: Speichernutzung 2                                    | 73  |

| Fig. 22: Speichernutzung 3, Programm in Abschnitte geteilt    | 73  |

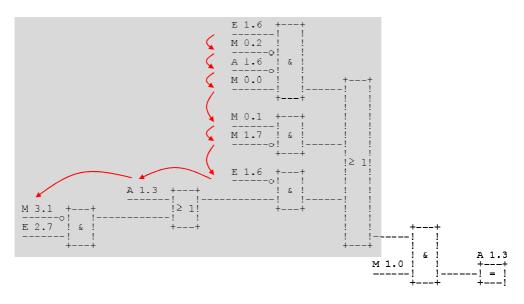

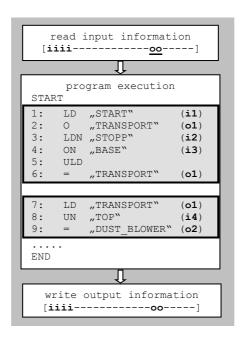

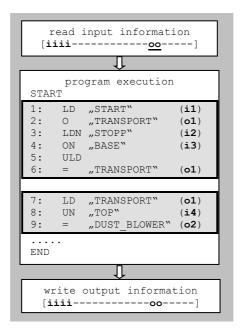

| Fig. 23: Testprogramm Bohrmaschine (ähnlich STEP 7)           | 76  |

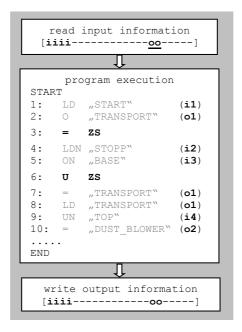

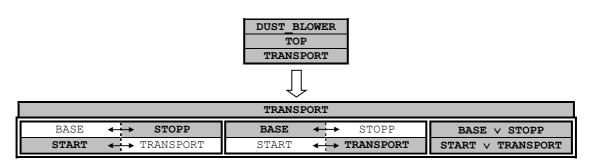

| Fig. 24: Programmstruktur                                     | 77  |

| Fig. 25: Testprogramm (Zwischenspeicher)                      | 78  |

| Fig. 26: Testprogramm (direkte Tautologie oder Kontradiktion) |     |

| Fig. 27: Testprogramm (Quasi-Tautologie oder Kontradiktion)   |     |

| Fig. 28: Testprogramm (Selbsthaltung)                         |     |

| Fig. 29: Testprogramm (Zeiten, Zähler, ähnlich STEP 7)        |     |

| Fig. 30: Testprogramm (Flanke, immediate, ähnlich STEP 7)     |     |

| Fig. 31: Adressierung (ähnlich STEP 7)                        |     |

| Fig. 32: Analyse der Funktion Bohrmaschine (ähnlich STEP 7)   |     |

| Fig. 33: Analyseschritte                                      |     |

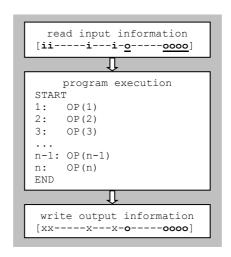

| Fig. 34: Struktur eines SPS-Programms in AWL                  |     |

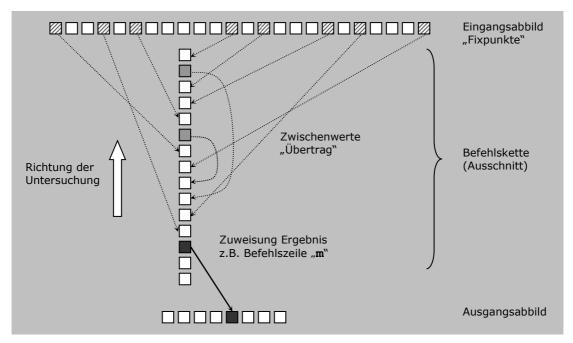

| Fig. 35: Prinzip der Rückwärtsanalyse                         |     |

| Fig. 36: Modell eines Programmsegments (Funktion)             |     |

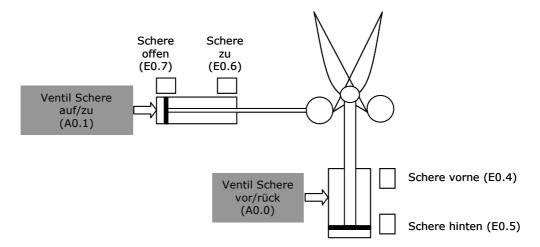

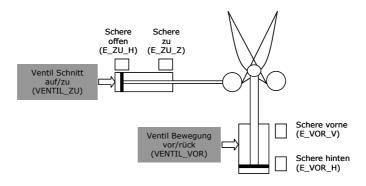

| Fig. 37: Prinzip Steuerung der Schere                         |     |

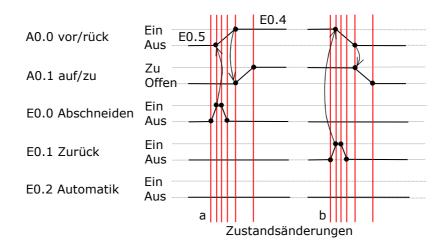

| Fig. 38: Steuerung der Schere, Ablaufdiagramm (Ausschnitt)    |     |

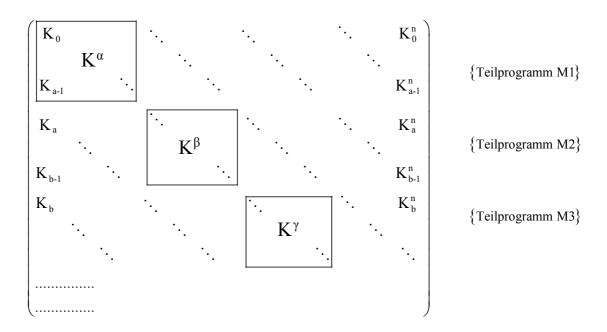

| Fig. 39: Modell der Konfiguration mit Bereichszuordnung       |     |

| Fig. 40: Lokale Konfigurationen                               |     |

| Fig. 41: Verbindung lokaler Konfigurationen                   | 122 |

| Fig. 42: Skizze "Schere"                                      |     |

| Fig. 43: Befehlsbearbeitung (vgl. [NF92])                     |     |

| Fig. 44: SPS als Zustandsübergangsmaschine                    |     |

|                                                               |     |

| Fig. 45: Zustandsübergangsmaschine aus Teilübergängen                  | 149 |

|------------------------------------------------------------------------|-----|

| Fig. 46: Virtuelle Eingangskonfigurationen                             | 160 |

| Fig. 47: Schleifmaschine mit Klemmvorrichtung                          | 167 |

| Fig. 48: Anordnung, Prinzip                                            | 240 |

| Fig. 49: Prinzip der SPS-Operation                                     | 243 |

| Fig. 50: Prinzip der Ausführung eines einzelnen Verifikationsschrittes |     |

# **Tabellen**

| Tab. 1: Zuordnung Befehl/Funktion                        | 103 |

|----------------------------------------------------------|-----|

| Tab. 2: Zuordnung Kommando/Wirkung                       | 104 |

| Tab. 3: Signale für das Programm "Schere"                | 119 |

| Tab. 4: Programm Schere                                  | 128 |

| Tab. 5: Zustandsübergänge Schere                         | 137 |

| Tab. 6: Zustandsübergänge Schere für Verifikation        | 139 |

| Tab. 7: Zustandsübergänge Schere ohne Schrittmerker      |     |

| Tab. 8: Abfragen und Verknüpfungen                       | 179 |

| Tab. 9: Klammerbefehle                                   |     |

| Tab. 10: Zuweisungsoperationen                           | 181 |

| Tab. 11: Funktionalität (dont_care) 1                    | 181 |

| Tab. 12: Funktionalität (dont_care) 2                    |     |

| Tab. 13: Funktionalität (dont_care) 3                    | 183 |

| Tab. 14: Funktionalität (dont_care) 4                    | 184 |

| Tab. 15: Funktionalität (dont_care) 5                    | 185 |

| Tab. 16: Funktionalität (dont_care) 6                    |     |

| Tab. 17: Funktionalität (dont_care & Calculate)          | 187 |

| Tab. 18: FC21 Umwandlung (Analyseschritt 1)              | 214 |

| Tab. 19: FC21 Ergebnis (Analyseschritt 2)                | 214 |

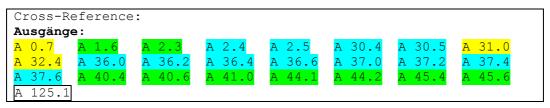

| Tab. 20: FC21 Querverweise (kompletter Baustein)         | 215 |

| Tab. 21: FC34 Netzwek 3                                  | 216 |

| Tab. 22: FC34 Netzwek 33                                 |     |

| Tab. 23: FC34 Querverweise (kompletter Baustein)         |     |

| Tab. 24: FC34 Querverweise Programmteil Wenden 1         | 217 |

| Tab. 25: FC34 Querverweise Programmteil Wenden 2         |     |

| Tab. 26: FC34 Querverweise Programmteil Wenden allgemein | 218 |

| Tab. 27: FC38 Netzwek 24                                 |     |

| Tab. 28: FC38 Querverweise Programmteil Stampfen         | 219 |

| Tab. 29: Querverweise Ausgänge untersuchte Programmteile | 220 |

| Tab. 30: Querverweise Beispiel                           | 223 |

| Tab. 31: Querverweise Ausgangslage (Schritt 1)           | 224 |

| Tab. 32: Querverweise Schritt 2                          |     |

| Tab. 33: Querverweise Schritt 3                          | 225 |

| Tab. 34: Querverweise Schritt 4                          | 225 |

| Tab. 35: Querverweise Schritt 5                          |     |

| Tab. 36: Wahrheitswerte des Ausdrucks a ∧ ¬b ∨ c = d     | 248 |

| Tab. 37: Quelle und Testprogramm für PROLOG.             | 250 |

| Tab. 38: Ausschnitt der PROLOG Ausgabe                   |     |

# Abkürzungen

Abkürzung Anmerkung

APLC Abstract Programmable Logical Controller, Abstraktion einer von Susta

[RS02] vorgeschlagenen SPS

AWL Anweisungsliste, Sprachkonzept für SPS nach IEC 61131 Teil 3

BBD Binary Decision Diagram

CTL Computation Tree Logic

FD Function Diagram, Sprachkonzept für SPS nach IEC 61131 Teil 3

FOL First Order Logic

FUP Funktionsplan, Sprachkonzept für SPS nach IEC 61131 Teil 3

IL Instruction List, Sprachkonzept für SPS nach IEC 61131 Teil 3

KOP Kontaktplan, Sprachkonzept für SPS nach IEC 61131 Teil 3

LTL Linear Temporal Logic

NuSMV A new Sybolic Model Checker

OBBD Ordered Binary Decision Diagram

PLC Programmable Logical Controller

RLL Relay Ladder Logic, Sprachkonzept für SPS nach IEC 61131 Teil 3

SMV Symbolic Model Verifier

SPS Speicherprogrammierbare Steuerung

# 1 Einführung

Die Verifikation von Programmen allgemein und die Verifikation von Steuerungsprogrammen sind aufwendig und erfordert umfangreiche Kenntnisse, so dass dafür in der Regel nur Experten mit derartigen Aufgabenstellungen betraut werden können. In dieser Arbeit werden Möglichkeiten untersucht, die bereits dem Programmierer von speicherprogrammierbaren Steuerungen (SPS) Werkzeuge zur Verfügung stellen, mit dem SPS-Programme automatisiert überprüft und verifiziert werden können.

#### 1.1 Motivation

Speicherprogrammierbare Steuerungen und formallogische Verifikation sind Bereichen der Informationstechnologie zuzuordnen, die in der Regel nur wenig miteinander zu tun haben. Je kleiner und leistungsfähiger Steuerungssysteme werden, etwas, das heutzutage schon fast alltäglich passiert, umso stärker durchdringen sie alle Bereiche der modernen Fertigungstechnologie. Nahezu alle Aufgabenstellungen beinhalten auch sicherheitskritische Elemente und damit wächst der Bedarf an verifizierter und im Weiteren auch an validierter Software für derartige Systeme, die bereits vor ihrem Einsatz auf ihre Korrektheit überprüft wird.

Bis dato hat sich die Verifikation von Steuerungsprogrammen immer als extrem zeit- und kostenaufwändige Angelegenheit gezeigt und daher wurde sie auch nur sehr sparsam angewendet, wenn es sich aus technischen oder rechtlichen Gründen absolut nicht vermeiden ließ. Ebenso hat sich in der Informatik die formale Verifikation ausschließlich auf höhere Programmiersprachen konzentriert. Vielfach wurden die vergleichsweise einfacheren Strukturen von Steuerungssprachen für eine Analyse als zu simpel empfunden. Stellt man sich dieser Herausforderung trifft man dabei auf eine Vielzahl von alles andere als trivialen Problemen. Ziel ist es, einen theoretischen Oberbau zu entwickeln und zusätzlich die Verwendbarkeit in der Praxis zu ermöglichen.

#### 1.2 Definition des Problems

Allgemein gilt, dass wenn ein Computerprogramm - im speziellen ein SPS-Programm - einer Spezifikation genügt, dieses als korrekt bezeichnet wird. Allerdings deckt dabei der Begriff Korrektheit nicht ab, ob die Spezifikation die vom Programm zu lösende Aufgabe in allen Einzelheiten vollständig beschreibt.

Die grundlegende Technik für die Verifikation geht auf Hoare zurück. Hoare führte in seinem Aufsatz "An axiomatic basis for computer programming" [HO69] aus, dass ein Programm-

code bezüglich einer Vorbedingung  $\mathcal{P}$  und der Nachbedingung  $\mathcal{Q}$  dann partiell korrekt genannt wird, wenn bei einer Eingabe die erfüllende Vorbedingung  $\mathcal{P}$  jedes Ergebnis der Berechnung auch die Nachbedingung  $\mathcal{Q}$  erfüllt. Dabei können Programmeingaben existieren, bei denen das Programm kein Ergebnis liefert. In diesem Fall heißt das, dass das Programm nicht terminiert. Ein Programmcode wird total korrekt genannt, wenn er partiell korrekt ist und zusätzlich für jede Eingabe terminiert, die auch die Vorbedingung  $\mathcal{P}$  erfüllt.

Im Wesentlichen fokussiert diese Arbeit Wirkungsabläufe in Folgesteuerungen. Solche Abläufe werden in der Steuerungstechnik von Anlagen, Maschinen bzw. Fertigungseinrichtungen als Kommandofolgen in SPS-Systemen realisiert.<sup>1</sup> Als Aufgabenstellung wird in dieser Arbeit die Verhaltensanalyse von gesteuerten Einheiten, wie diese z.B. in Fertigungseinrichtungen anzutreffen sind, untersucht und der Verifikation zugänglich gemacht. Das Merkmal dieses Verhaltens ist, dass während des Ablaufs des Prozesses von der SPS Stellsignale ausgegeben werden, die als Schaltsignale wie Sprungfunktionen wirken. Dieses Verhalten ist typisch für die Ausgänge. Sich daraus ergebende Sprungantworten erfolgen entsprechend des jeweiligen Zeitverhaltens in der Regel zeitlich versetzt und sind von Ereignissen abhängig. Solche Ereignisse sind z.B. das Erreichen eines bestimmten Zustands, der seinerseits Folgezustände initialisieren kann oder Eingriffe im Rahmen der Bedienung. Signalzustände werden als Eingänge in der SPS verwaltet.

Das Hauptproblem der Verifikation allgemein liegt in der Anzahl von zu berücksichtigen Zuständen, bekannt als das "state explosion problem". Auch in SPS-Steuerungsprogrammen von automatisierten Fertigungseinrichtungen wächst die Anzahl der zu überwachenden Funktionen und damit die damit verbundenen Zustände stark an. Einhundert Variable bedeutet, dass  $2^{100}$  oder  $1,27\cdot10^{30}$  unterschiedliche Zustandskombinationen untersucht werden müssen, um sichere Aussagen zur Korrektheit eines SPS-Logikprogramms zu machen. Dabei werden bereits für mittlere Steuerungsaufgaben einige hundert verschiedene Signale zur Steuerung und Überwachung einer Fertigungseinrichtung notwendig. SPS-Programme können Verifikationsmethoden wie dem Model-Checking in der Regel nicht zugänglich gemacht werden, weil anstelle formaler Programmspezifikationen für die Aufgabenstellung nur informelle Beschreibungen üblich sind.

Nicht zu unterschätzen ist der Umstand, dass SPS-Programmierer in den seltensten Fällen Informatiker sind. Typische SPS-Programmierer sind die Konstrukteure von Fertigungsmaschinen, Techniker, die sich auf Steuerungsprogrammierung spezialisiert haben oder Automa-

In der DIN-IEC 60050-351[1] ist zum Begriff Steuern wenig hilfreich definiert, dass das "Kennzeichen für das Steuern [...] der offene Wirkungsweg oder ein geschlossener Wirkungsweg [ist], bei dem die durch Eingangsgrößen beeinflussten Ausgangsgrößen nicht fortlaufend und nicht wieder über dieselben Eingangsgrößen auf sich selbst wirken".

tisierungstechniker. Vielfach ist das Servicepersonal programmierend tätig, das Eingriffe in die Programme vornehmen muss um den Betrieb aufrecht zu erhalten. Dieser Personenkreis besitzt nur eine geringe Bereitschaft, Methoden der Verifikation als Werkzeug zu nutzen. Grund dafür ist unter anderen, dass ab einer Anzahl von verschiedenen Zuständen oder Zustandskombinationen die Überblickbarkeit nicht mehr gegeben ist. Darüber hinaus sind die erforderlichen Kenntnisse der Zielgruppe SPS-Programmierer üblicherweise nicht groß genug, um die Verifikation anwenden zu können. Das Spezialwissen der typischen SPS-Programmierer reicht für die Programmerstellung gut aus, für das Verstehen der Konzepte für die Verifikation jedoch nicht.

Wird eine Verifikation notwendig, muss sich der mit Verifikation von SPS-Programmen betraute Personenkreis mit der Aufgabenstellung intensiv beschäftigen, um den Gedankengängen der Programmierer und deren Umsetzung in ein SPS-Programm zu folgen und, um auf Grund ihrer Untersuchung zur Korrektheit der Programme, diese gegebenenfalls zu verifizieren. Demgegenüber haben SPS-Programmierer den unmittelbaren Vorteil, dass sie ihre Aufgabenstellungen und deren Besonderheiten bereits sehr gut kennen. Sie mussten sich intensiv mit den für das Programm festgelegten Vorgaben bis ins Detail beschäftigen und haben damit bei korrekten SPS-Programmen alle Aspekte eines Steuerungsablaufs behandelt. Aus diesem Grund scheint es naheliegend zu sein, den SPS-Programmieren ein Werkzeug bereitzustellen, mit dem sie bereits im Zuge der Programmierung SPS-Programme verifizieren können.<sup>2</sup> Als wichtige Eigenschaft solcher Werkzeuge sind für deren Akzeptanz notwendig, dass Spezialkenntnisse nur in geringem Umfang erforderlich werden. Idealer Weise sollten die Kenntnisse zur SPS-Programmierung und der Wirkungsweise von SPS-Systemen ausreichen.

Bei technischen Systemen wird Sicherheit<sup>3</sup> als Zustand einer störungsfreien und gefahrenfreien Funktion verstanden. Dabei ist der Begriff "Sicherheit" von seiner Definition abhängig bzw. welcher Grad von verbleibender Restunsicherheit für die Nutzung von technischen Funktionen akzeptiert wird. Die Norm IEC 61508 [1] definierte Sicherheit als "Freiheit von unvertretbaren Risiken" und beschreibt funktionale Sicherheit als Teilaspekt eines technischen Systems.

Bei der Programmerstellung werden die Übergänge von einem Status der Maschine in den folgenden Status definiert. Diese Definition basiert auf Zuständen von Ein- bzw. Ausgängen z.B. eine Ausgangsstellung der Maschine und der Umsetzung durch das Programm, was als nächstes auf Grund einer Aufgabenstellung passieren soll. Aus einer folgerichtigen Programmierung muss sich daher die Folgestellung der Maschine ergeben, wodurch die Zielzustände implizit gegeben sind. In "Schritte zur Verifikation von SPS-Programmen" [KP12] wird ein Ansatz diskutiert, wo das Prinzip einer reaktionsschnellen Steuerung skizziert ist, deren Programm ausschließlich aus Übergangsfunktionen gebildet wird.

Synonym wird der Begriff "Betriebssicherheit" in diesem Zusammenhang genutzt.

Eine besondere Bedeutung für Sicherheit von technischen Systemen liegt bei der genutzten Software. Zur Entwicklung wird ein hoher Aufwand für die Sicherstellung der Fehlerarmut der Software betrieben. Dieser Aufwand ist umso mehr gerechtfertigt, wenn sicherheitskritische Prozesse überprüft werden, die in technischen Systemen ablaufen.

Stark verkürzt liegen die grundlegenden Probleme in der wachsenden Komplexität von SPS-Programmen, die auf die Steigerung von Möglichkeiten für SPS-Anwendungen zurückzuführen ist und der fehlende Zugang für typische SPS-Progammierer zu Verifikationstechniken.

#### Kompexität von SPS Programmen

SPS wurden ursprünglich als Ersatz für herkömmliche Steuerungssysteme konzipiert und eingeführt. Eines der Hauptziele war auch, die Konzeption und Programmierung von SPS derart einfach zu gestallten, um den für den Betrieb solcher Systeme zuständigen Personenkreis einen einfachen Zugang zu bieten. Dieses Ziel wurde so gut erreicht, so dass für Programmierung oder Wartung von Programmen bzw. für Inbetriebnahme von Steuerungen und Anlagen vielfach Praktiker eingesetzt werden können, die mit vergleichsweise geringen theoretischen Kenntnissen auskommen.

Die technische Weiterentwicklung der SPS-Systeme ist bereits derart fortgeschritten, dass solche Systeme in hochkomplexen Anwendungen einsetzbar sind, die früher Rechnersystemen vorbehalten waren. SPS-Systeme werden auch zur Kontrolle sicherheitskritischer Aufgabenstellungen genutzt. Auch aus diesem Grund rückt die Verifikation von Steuerungssystemen mehr und mehr in den Mittelpunkt des Interesses.

#### Zugang von SPS-Programmieren zu Verifikationtechniken

Ganz allgemein gesehen erfordert die Anwendung von Methoden für die Verifikation von Programmen besondere Kenntnisse, die auf Grund von Herkunft und Vorbildung der Programmierer von SPS-Systemen nur in Ausnahmefällen gegeben sind.

Das Hauptproblem liegt in der Diskrepanz der Denkweise von theoretischen Informatikern im Gegensatz zu Praktikern, die eine Steuerung oder Anlage und deren Erfordernisse aus der Sichtweise der Anwendung so gut kennen, dass vertiefende Kenntnisse zu den zugrundeliegenden Theorien für die Programmumsetzung nicht benötigt werden. Im Gegenzug ist die Ausdruckweise bzw. die Beschreibungssprache der Praktiker üblicherweise nicht formal genug, dass die theoretische Informatik damit etwas anfangen kann.

Formale Spezifikationen für SPS-Programme sind sehr selten anzutreffen. Beschreibungen von SPS-Programmen sind üblicherweise verbal und zum Teil nicht vollständigen Beschreibungen zugrunde gelegt, die erst durch ergänzende Informationen in Steuerungsprogramme umgesetzt werden können. Typisch ist auch, dass Informationsketten gebildet werden, beginnend bei der Konzeption durch den Maschinenbau, Transfer der Information an die Steuerungstechnik mit Abgleich zu technischen oder technologischen Gegebenheiten, die in der Folge zu Variationen in der Programmentwicklung führen. Die SPS-Programmierung wird dadurch zu einem iterativen Prozess mit Anpassungen und Veränderungen, der erst bei der Abnahme einer Maschine oder Anlage als abgeschlossen betrachtet werden kann.

SPS-Programme folgen den Regeln ihrer Programmiersprachen, sind also per se formal. Sie dienen in dieser Arbeit als das Bindeglied zwischen einer praktischen Anwendung und ihrer formalen Verifikation. Die Programmierer, die eine Aufgabenstellung umsetzen, können jedenfalls Ausgangssignalzustände beschreiben und die zugehörigen Zielzustände definieren. Mit Hilfe solcher Zuordnungen soll die Überprüfung der erstellten SPS-Programme in der Form einer Verifikation durchgeführt werden. Anders ausgedrückt: die Zielvorstellung ist, eine Methode zu definieren, mit der SPS-Programmierer ohne besondere Zusatzkenntnisse ihre Programme selbst bereits im Zuge der Programmerstellung und bei den allfälligen Programmanpassungen wiederholt automatisiert verifizieren können.

Erschwerend ist dabei die Komplexität, weil SPS-Programme auch auf Grund der immer größer werdenden Leistungsfähigkeit solcher Systeme eine große Anzahl von Zuständen einnehmen können. Das exponentielle Anwachsen von zu betrachtenden Zuständen, die Verdoppelung der Anzahl von Zuständen für jeden weiteren, ist als das state explosion problem bekannt und bildet Schranken für die Übersichtlichkeit und in Folge für die Verifikation.

#### 1.2.1 Funktionalität von SPS-Programmen

Als Beispiel wird die typische Vorgehensweise einer Funktionsüberprüfung von SPS-Programmen herangezogen. Historisch gesehen waren die ersten SPS-Programme auf Grund der noch geringen Leistungsfähigikeit dieser Geräte vergleichsweise einfach, sowohl was die Programmierung als auch die Inbetriebsetzung betroffen hat. Die typische Überprüfung auf Korrektheit einer Anlage erfolgte durch schrittweises Testen der programmierten Funktionen. Eines der Hauptargumente für die Einführung von SPS war, dass einerseits auf Grund der Einfachheit der Verdrahtung und andererseits der zugehörigen Programme solche Steuerungssysteme mit geringem Aufwand in Betrieb genommen werden konnten.

Dem Grunde nach hat sich diese Argumentation bis heute nicht verändert. Auch die Vorgehensweise für Inbetriebsetzung ist im Wesentlichen gleichgeblieben: ausgehend von Ein-

gangsbedingungen - den Zuständen einer Maschine oder Fertigungseinrichtung - resultieren bei korrekter Funktion Ausgangsbedingungen. Die Vorgehensweise beim schrittweisen Testen ist vergleichbar mit der Verifikationstechnik von Hoare.

Dieses Schema wird auch heute noch angewendet. Als problematisch gilt dabei nur die gesteigerte Komplexität der Aufgabenstellungen. Umgangen wird das in der Praxis dadurch, dass geeignete Teilbereiche gesucht und diese dann entsprechend behandelt werden.

#### Untersuchungen und Ziele

In dieser Arbeit wird untersucht und gezeigt, dass durch geeignete Segmentierung von SPS-Programmen auch komplexere SPS-Programme in Teilbereiche derart zerlegt werden können, dass damit bereits bei der Erstellung solcher Programme Verifikationsschritte durchführbar sind. Im Gegensatz zur realen Inbetriebnahme muss in diesen Arbeitsschritten die zu überprüfende Anlage oder Fertigungseinrichtung noch nicht zur Verfügung stehen.

Gezeigt wird auch, dass die Untersuchung vollständig durchgeführt werden kann, dass also der Untersuchungsraum der Zustände vollständig abbildbar ist. Die für die Verifikation definierten Teilbereiche sind zusammensetzbar. Gefolgt wird bei der Prüfung von Teilbereichen dem bei der Inbetriebsetzung von Maschinen oder Anlagen üblichen Prinzipien. Zu jedem Segment des zu untersuchenden Programms werden Zustandskombinationen gebildet, die den Testszenarien einer typischen Inbetriebnahme entsprechen. Im Unterschied zur realen Inbetriebnahme können mit der vorgeschlagenen Methode aber auch Zustandskombinationen überprüft werden, die bei einer fertig gestellten Maschine oder Anlage z.B. wegen einer speziellen mechanischen Anordnung von Maschinenteilen nie erreichbar sind.

#### 1.2.2 Spezifikation

Vielfach erfolgt die Konzeption eines SPS-Programms nach dem Schema, dass auf Grund einer informellen Spezifikation zu einer Aufgabenstellung das Programm direkt implementiert wird.

Nach der Erstellung des Programms wird in der Testphase die Funktionalität mit der informellen Spezifikation in Bezug gebracht und so die Abläufe validiert. Validieren bedeutet in diesem Zusammenhang, dass nicht nur die vorgegebene Funktionalität durch das Programm erfüllt wird, sondern auch die gesamte Anlage einschließlich der an die SPS angeschlossenen Sensoren und Aktuatoren mit einbezogen werden.

Eine weitere Möglichkeit besteht darin, dass ausgehend von der informellen Spezifikation durch Formalisieren eine formale Spezifikation gebildet wird. Diese kann verifiziert werden. Das grundsätzliche Ziel dabei ist, Ein- und Ausgangzustände der SPS in Relation mit dem SPS-Programm zu untersuchen. Zusätzlich kann gefordert werden, dass als Ergebnis dieser Untersuchung ausschließlich Zustandsübergänge erfolgen, die im Sinne der Aufgabenstellung als erwünscht zu bewerten sind. Existieren nur erwünschte Ergebnisse und umfasst die Verifikation alle Zustandsübergänge, kann von einer Vorstufe zur Validation gesprochen werden. Während beim Validieren das gesamte System betrachtet werden muss, beschränkt sich die Verifikation auf das SPS-Programm.

Typisch für informelle Spezifikationen sind "wenn – dann" Zusammenhänge. Derartige Zusammenhänge beschreiben gewünschte Abläufe sowie Ereignisse, die verhindert werden müssen. Während die gewünschten Abläufe in der Regel vollständig dargestellt werden, ist die Vollständigkeit in einer informellen Spezifikation für mögliches Fehlverhalten nicht immer der Fall. In Testfällen wird daher bei der Inbetriebsetzung das SPS-Programm auf Fehlerfreiheit im Sinne der Funktionalität überprüft. Nachteilig bei einer Inbetriebsetzung ist, dass eine 100%ige Testabdeckung in der Regel nicht erfolgen kann, insbesondere auch deshalb, weil nicht alle Zustände erreichbar sind.

Ein SPS-Programm besteht grundsätzlich aus Vorgaben, die für einen bestimmten Ablauf definiert werden. Derartige Vorgaben können als Algorithmen einer Steuerungsaufgabe oder einer Teilfunktion daraus gesehen werden. Ein rein formales Modell ist die Summe aller Algorithmen, die eine Aufgabenstellung vollständig beschreiben.

#### **Modellierung**

Das in dieser Arbeit verfolgte Konzept formalisiert bestehende SPS-Programme bzw. Teile davon. Dazu wird unterstellt, dass ein zu untersuchendes SPS-Programm bereits in einer Form vorliegt, die auch einer rein formalen Spezifikation genügt, also, dass darin nicht nur die funktionalen, sondern auch nicht-funktionale Anforderungen an ein System bereits programmtechnisch berücksichtigt worden sind. Damit kann ein Modell des SPS-Programms gebildet werden.

Die Modellbildung erfolgt durch das Aufstellen einer Wissensbasis, die auf Fakten, Regeln und Formeln beruht. Aufbauend auf der Wissensbasis, ist das Modell die Kette aller Instruktionen in geordneter Reihenfolge, die durch die Programmierung vorgegeben ist. Ein Weg zur Formalisierung wurde in "Schritte zur Verifikation von SPS-Programmen" [KP12] vorgezeichnet. Theoretisch sind derartige Modelle in ihrer Größe nicht beschränkt. Der typische Verifikationsschritt ist die Überprüfung, ob ein untersuchtes Programm alle Übergänge von

Ein- zu Ausgangsbedingungen erfüllt. Notwendig werdende Begrenzungen sind aus diesem Grund nur auf das exponentielle Anwachsen mit steigender Anzahl der zu betrachtenden Zustände in Bezug auf die zu untersuchenden Testfälle zurückzuführen. Um diese Grenzen zu überwinden wird das SPS-Programm in Teilbereiche segmentiert.

#### 1.2.3 Verfikationstechnik, Begriffsabgrenzung und Verifikationsmethoden

Model-Checking ganz allgemein gesehen wurde als formales Verfahren zur automatisierten Verifizierung nebenläufiger Systeme mit einem endlichen Zustandsraum eingeführt.<sup>4</sup> Mit diesem Verfahren können große Zustandsräume automatisch untersucht werden. Dazu wird ein System modelliert und dieses Modell auf seine Systemspezifikation überprüft, wobei in erster Linie die Sicherheits- und Lebendigkeitseigenschaften untersucht werden. In diesem Zusammenhang zielt die Untersuchung von Sicherheitseigenschaften auf Zustände ab, die im Modell nicht auftreten dürfen, die Lebendigkeitseigenschaften darauf, dass irgendwann ein erwünschter Zustand eintritt.

Dazu wird das zu verifizierende System in Form eines Zustandübergangsgraphen bzw. Berechnungsbaums auf Fehler untersucht. Jeder Befehl eines Prozesses bewirkt eine Veränderung des Zustandsraums. Unterschieden werden dabei das on-the-fly Model-Checking und das symbolische Model-Checking. Beim Verfahren on-the-fly Model-Checking wird der komplette Zustandsgraph mit allen Übergängen aufgebaut und jeder Zustand untersucht. Zur Überprüfung eines Modells müssen alle relevanten Zustände eines Systems gespeichert werden. Es werden entsprechende Datenstrukturen benötigt, um Zustände zu speichern. Beim symbolische Model-Checking werden Zustandsübergangsgraphen nicht explizit aufgebaut, sondern der Zustandsraum mit Entscheidungsdiagrammen (Binary Decision Diagrams, BBD) abgebildet, mit denen die Übergänge zwischen den Zuständen berechnet werden (vgl. [Cl et al.09], [Bc et.al.08]).

Mathematische Modelle von Programmabläufen, insbesondere jene für Zustandsübergänge, werden als Automaten bezeichnet. Dabei wird z.B. beim so genannten ω-Automat<sup>5</sup> ausgehend

\_

Als Zustandsraum wird hier die Menge jener Zustände verstanden, die Modelle beeinflussen. Unterscheidungen werden in Laufe der Arbeit zusätzlich getroffen. Bezogen auf das SPS-Programm existieren Eingangszustände oder initiale Zustände. Diese treten am Anfang eines SPS Zyklus in Erscheinung. Während der zyklischen Programmbearbeitung existieren temporäre Zwischenzustände, die Ausgangszustände am Ende eines Zyklus stellen Berechnungsergebnisse dar. In der Sprechweise werden später auch die Begriffe Eingangsvektor bzw. Eingangskonfiguration (von Zuständen) eingeführt, Konfiguration (von Zuständen) für temporäre Zwischenergebnisse und Ausgangsvektoren bzw. Ausgangskonfigurationen (von Zuständen).

<sup>&</sup>lt;sup>5</sup> Eine spezielle Form des ω-Automaten ist der nach dem Schweizer Mathematiker Julius Richard Büchi benannte Büchi-Automat. Dieser Automatentyp ist eine spezielle Form des ω-Automaten.