Die approbierte Originalversion dieser Dissertation ist in der Hauptbibliothek der Technischen Universität Wien aufgestellt und zugänglich. http://www.ub.tuwien.ac.at

WIEN Universitätsbibliothek The approved original version of this thesis is available at the main library of the Vienna University of Technology.

http://www.ub.tuwien.ac.at/eng

TU UB

### PhD Thesis

## **On Memory Induced, Nonlinear Behavior of All-Digital Radio Frequency Transmitters**

unter der Leitung von em. O. Univ.-Prof. Dipl.-Ing. Dr. Gottfried Magerl Ass. Prof. Dipl.-Ing. Dr. Holger Arthaber Institute of Electrodymamics, Microwave and Circuit Engineering

> eingereicht an der Technischen Universität Wien, Fakultät für Elektrotechnik und Informationstechnik

> > von

DI Norbert LEDER Matr.Nr. 0525421 Bahnstraße 45 2285 Leopoldsdorf i.M. geb. 26.3.1985

Wien, im August 2017

#### Abstract

This work discusses the design and modeling of all-digital radio frequency transmitters (DRFTx). Transmitters based on nonlinear radio frequency (RF) modulators can be energy efficient and universal with respect to center frequencies and modulation formats. This ability is highly desirable for the steadily increasing pace and multitude at which RF-modulation standards are developed and deployed.

However, despite its potential, the DRFTx hasn't been adopted for today's mainstream applications, mainly for three reasons. Firstly, the RF-circuitry requires low loss filters with high quality factors which are inherently bulky and expensive. Secondly, the modulator introduces undesired signal components that need to be sustained throughout the signal chain in order to preserve certain properties of that signal. However, this renders many design paradigms for high efficiency power amplifiers (PA) useless. Dealing with the many issues of a completely novel design methodology is a hurdle in itself. Thirdly, due to its entanglement between the software based modulator and the attached RF circuitry the modulator and PA cannot be developed separately. Both of these entities are highly nonlinear and show memory affected behavior. In order to get the best overall system performance a co-design approach is required, which again is not established yet.

This work demonstrates some of these dependencies and shows that a system approach is required in order to gain an optimized DRFTx design. An important stepping stone is the availability of a circuit-centric model. This allows linking circuit measures like energy efficiency, effective memory depth or nonlinear distortion to properties of the excitation signal generated by the modulator. By using a model that captures these dependencies, a joint optimization between modulator settings and circuit variants can be conducted. Ultimately, this allows to balance nonlinear distortion, circuit complexity, and power efficiency in order to gain an overall viable system.

There are different model types that can serve for this purpose which are presented as an overview in this work. However, the auto regressive exogenous (ARX) and a type of look up table model (LUT) have been investigated and compared in detail. The latter one has been found to be the more suitable option and it was possible to improve it by introducing a hierarchical data structuring technique.

All the results presented in this work are based upon or verified by measurements of a purpose built DRFTx setup. It is based on a laboratory test bench which was built to produce a 20 MHz LTE signal at a center frequency of 2.5 GHz utilizing a 10 W GaN HEMT.

### Kurzfassung

Diese Arbeit beschäftigt sich mit dem Entwurf und der Modellierung von volldigitalen Hochfrequenz-Sendern (DRFTx). Der Einsatz nichtlinearer Hochfrequenz-Modulatoren ermöglicht es Sender zu realisieren, die gleichsam hoch effizient und software-konfigurierbar sind. Damit würde man den lang ersehnten Brückenschlag zwischen der rasanten Entwicklung und der im Vergleich dazu schleppenden Verbreitung neuer Funkstandards ermöglichen.

Obwohl der DRFTx theoretisch großartiges Potential verspricht, wird er bis dato nicht großflächig eingesetzt. Das lässt sich vor allem durch gewisse Eigenheiten des Konzepts und mehrere inhärente Eigenschaften erklären. Erstens müssen verlustarme Filter mit hohen Gütefaktoren eingesetzt werden, um die gewünschte Funktionalität zu erreichen. Diese sind aber schwer zu integrieren, groß und teuer. Zweitens erzeugt der Modulator aufgrund seiner Funktionsweise eine Vielzahl an Signalkomponenten, die nicht dem eigentlichen Ausgangssignal zuzurechnen sind. Diese müssen, um die Funktionsweise des Gesamtsystems zu ermöglichen, bis zum Leistungsverstärker (PA) durch die Signalkette aufrechterhalten werden. Das steht allerdings im Widerspruch zu den meisten Entwurfsparadigmen für hocheffiziente Leistungsverstärker. Um solche Sender zu realisieren, wäre daher ein komplett neues Entwicklungskonzept notwendig, was eine große Hürde darstellt. Drittens, die Abhängigkeiten zwischen dem Modulator, der ausschließlich aus Software besteht, und jenen der Schaltungstechnik verhindert eine separate Entwicklung dieser Einheiten. Um das Gesamtsystem zu optimieren, ist hier ein übergreifender Entwurf notwendig, der momentan sehr unüblich ist.

Diese Arbeit zeigt, dass für die Optimierung des Gesamtsystems die Abhängigkeiten zwischen Modulator und Schaltung berücksichtigt werden müssen. Ein Schaltungsmodell welches das leistet, ist ein erster und wichtiger Schritt dazu. Das Modell muss dazu auf Basis der digitalen Ausgangssignale des Modulators das Verhalten der Schaltung prädizieren können. Das erlaubt schaltungsspezifische Kennwerte, wie Leistungseffizient oder Speichertiefe, mit den Eigenschaften und Einstellungen des Modulators zu verknüpfen. Nur wenn das Modell diese Abhängigkeiten korrekt abbildet, ist es möglich, das Gesamtsystem zu optimieren. Als übergeordnetes Ziel kann dadurch eine Realisierung gefunden werden, die eine optimale Balance zwischen Schaltungskomplexität, Leistungseffizienz und nichtlinearer Verzerrung aufweist.

Es gibt eine Fülle von Modelltypen, die für diese Anwendung in Frage kommen. Diese Arbeit handelt die wichtigsten überblicksmäßig ab und vergleicht zwei davon detailliert. Dabei handelt es sich um die Klasse der äuto regressive exogenous"(ARX) Modelle und eine Tabellen basierterte Lösung (LUT). Der Tabellen Ansatz hat sich im Rahmen der Analyse als die handhabbarere herausgestellt. Außerdem konnte diese durch den Einsatz einer hierarchischen Daten-Strukturierung für diese Anwendung optimiert werden.

Alle Ergebnisse, die in dieser Arbeit präsentiert werden, basieren auf Messungen an einem DRFTx Test-Aufbau. Dieser ist Teil eines Laboraufbaus zur Untersuchung dieser Sendertopologie, welcher ein 20 MHz LTE Signal bei einer Mittenfrequenz von 2,5 GHz erzeugt. Die Leistungsendstufe verwendet einen weit verbreiteten 10 W GaN HEMT von *CREE*.

### Acknowledgements

During the five years while I was working on the overarching project this work is based on, it consumed a lot of my time and attention. I want to thank my family and friends for their continuous support during this time, without it, this work would have not been possible.

As most of this project was carried in the workplace I also want to thank all my colleges for their help, hints and pats on the back. However, some of them stand out as supporters, companions and/or drinking buddies.

Firstly, the microwave group, a team of self-proclaimed nerds with an impressive skill-set that runs on freshly prepared meals and humor, helped me out countless times and I want to thank them for all the time, effort and wit. It was a pleasure to work side by side with Bernhard Pichler on many of the experiments leading up to this thesis and the corresponding papers. He is a true optimist and an excellent scientist. Holger Arthaber managed this project and provided dangling carrots, as well as, the creative deadline management, which is sometimes required for an efficient paper writing process. Thomas Faseth spent many hours, often on short notice, proofreading paper drafts and giving highly valued feedback. Gottfried Magerl provided many brilliant hints, funny anecdotes, and know-how for almost every situation. Last but not least, I want to thank Margit Maritzen, as one of the good souls behind the scenes. She eased many administrative obstacles and paved the way for a better work environment.

# Contents

| 1 | Mot                                    | ivation and Thesis Outline                          | 2  |

|---|----------------------------------------|-----------------------------------------------------|----|

|   | 1.1                                    | The DRFTx from a Technological Perspective          | 3  |

|   | 1.2                                    | Circuit Design Considerations                       | 5  |

|   | 1.3                                    | Modeling Considerations for DRFTx Systems           | 7  |

| 2 | Test Bench for Digital RF Transmitters |                                                     |    |

|   | 2.1                                    | Signal Source                                       | 12 |

|   | 2.2                                    | Booster Amplifier                                   | 14 |

|   | 2.3                                    | Power Amplification Stage                           | 17 |

|   | 2.4                                    | Output Filter                                       | 21 |

|   | 2.5                                    | Output Coupler                                      | 23 |

|   | 2.6                                    | Measurement Setup                                   | 24 |

| 3 | Design of DRFTx Circuit Modules        |                                                     |    |

|   | 3.1                                    | Bias Module for Experimental RF-Amplifiers          | 27 |

|   | 3.2                                    | Load Pull Measurements and Setup                    | 29 |

|   | 3.3                                    | Matching Network Design                             | 37 |

|   | 3.4                                    | Circuit Synthesis Based on SRFT                     | 41 |

|   | 3.5                                    | Measured Matching Networks                          | 48 |

|   | 3.6                                    | Design of the Output Coupler Section                | 50 |

| 4 | Non                                    | linear System Characterization and Modeling         | 55 |

|   | 4.1                                    | Characterizing Nonlinear Memory Affected Distortion | 57 |

|   | 4.2                                    | Modeling Requirements for DRFTx                     | 61 |

|   | 4.3                                    | Model Estimation and Verification                   | 64 |

| 5 | The ARX Model                          |                                                     |    |

|   | 5.1                                    | Formal Definition of an ARX Model                   | 68 |

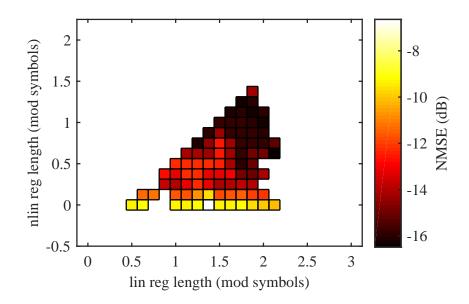

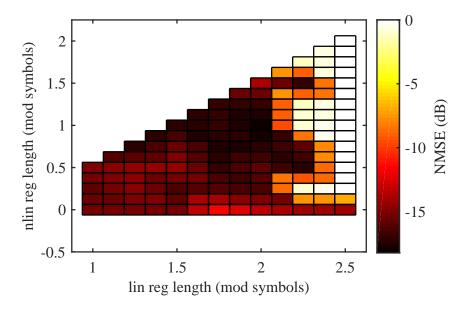

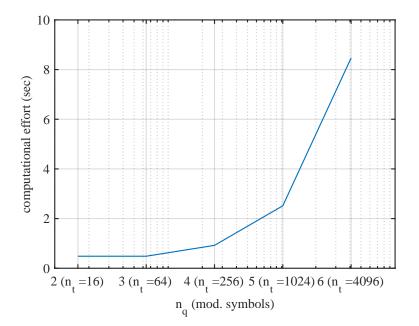

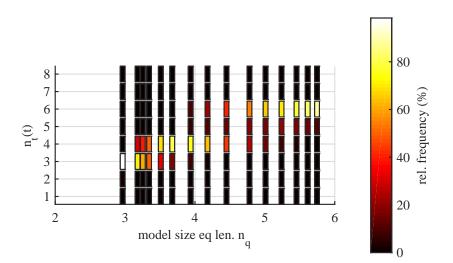

|   | 5.2                                    | Determining the Required ARX Model Complexity       | 70 |

|   | 5.3                                    | ARX Modeling Results                                | 72 |

#### CONTENTS

| 6 | LUT              | Models                                    | 76  |  |  |

|---|------------------|-------------------------------------------|-----|--|--|

|   | 6.1              | Formal Definition of LUT Model Parameters | 77  |  |  |

|   | 6.2              | Generation of LUT Model Entries           | 79  |  |  |

|   | 6.3              | Gauging LUT Models                        | 82  |  |  |

|   | 6.4              | Hierarchical LUT Models                   | 84  |  |  |

|   | 6.5              | Verification of LUT Models                | 88  |  |  |

| 7 | Model Comparison |                                           |     |  |  |

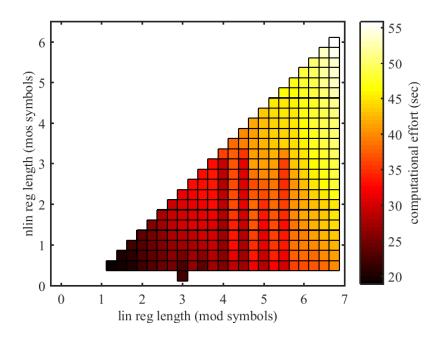

|   | 7.1              | Model Estimation and Model Complexity     | 93  |  |  |

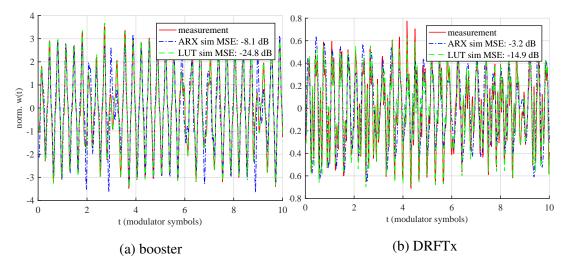

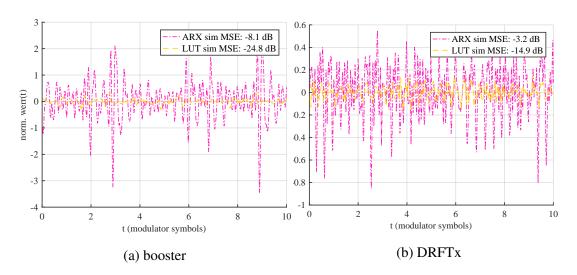

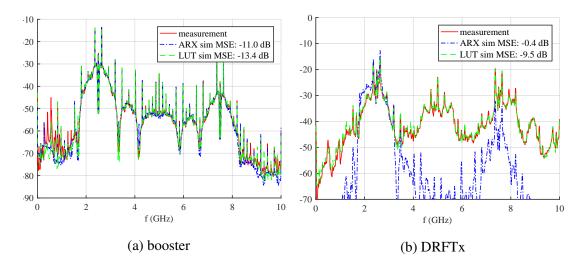

|   | 7.2              | Simulation and Prediction-Error           | 96  |  |  |

|   | 7.3              | Conclusion and Outlook                    | 105 |  |  |

|   |                  |                                           |     |  |  |

### Appendices

### 114

# **CHAPTER 1**

# **MOTIVATION AND THESIS OUTLINE**

Transmitters based on nonlinear radio frequency (RF) modulators are subject of ongoing research. Pursuing this technology is largely driven by the need for transmitters that are energy efficient and universal with respect to center frequencies and modulation formats. At least in theory, these requirements can be addressed by employing RF pulse width modulation (PWM) in RF transmitter circuits. However, this class of digital RF transmitters (DRFTx) hasn't yet arrived in today's circuit mainstream and that for good reasons. Despite, or maybe just because of that DRFTx are an interesting system which is influenced by the findings of many research fields, ranging from analog RF-circuit design over nonlinear signal processing to memory affected circuit modeling.

This work is based on a laboratory test bench for a DRFTx which was built to produce a 20 MHz LTE signal at a center frequency of 2.5 GHz utilizing a 10 W GaN HEMT. Since the DRFTx in this setup was designed entirely within the time the work on this thesis was conducted, it allowed for a very experimental approach. In contrast to the following chapters which explain the setup and methods involved in detail, this chapter introduces the basic principles behind the DRFTx and the theoretical aspects that need to be considered in order to build and constructively analyze a DRFTx setup.

### **1.1** The DRFTx from a Technological Perspective

Designing and building highly efficient, flexible yet broadband RF signal generators is the subject of research spanning decades. Although, all approaches that overcome the stringent efficiency limits dictated by linear power amplifiers[1] do that by employing nonlinear phenomena in their power amplification stage.

Basically there are two ways to do so: Firstly, using amplifiers that behave dominantly linear are driven into saturation. This boosts their efficiency, although, causes some unintentional nonlinear distortion, like compression for example. These effects are combated by countermeasures restoring the intended signal. Typical examples are amplifiers in conjunction with predistortion, Doherthy amplifiers, and many more.

Secondly, it is also possible to intentionally operate the amplifier permanently in saturation resulting in the family of switched mode power amplifiers (SMPA). Of course, these amplifiers behave inherently nonlinear. However, harmonic components that originate from these nonlinear effects, in conjunction with harmonic controlled matching networks, can be utilized to reach even higher efficiencies. For narrow-band excitation, SMPA concepts are reasonably complex to implement and well understood [2]. In general, the nonlinear behavior of the amplifier also generates signal components within its baseband. These components are usually undesirable and their relative power grows with higher relative signal bandwidth of the amplifier [3]. It is important to note, that building a SMPA always requires to include some kind of filter. The terminology varies for different approaches. In some cases a harmonic controlled matching network, which also performs a filter functionality, is sufficient to remove the unwanted signal components. Other designs may require a dedicated reconstruction filter to reach sufficient suppression.

While this work is inclined to the SMPA category, there is one key difference to it. Harmonic controlled amplifiers are driving an SPMA with an analog RF-signal, very similar to the desired output signal with respect to waveform and spectral content. This is equivalent to the assumption that the signal present at the active element of the amplifier is similar to the desired output signal. All additional signal components at the active component do not account for the dominant share of the overall power. For the system presented in this work, things are very different.

The signal exciting the power amplification stage of the system is generated us-

ing a pulse width modulator which generates the baseband signal using pulse width modulation (PWM) and performs the up conversion to the desired center frequency [4]. However, it has a rather low coding efficiency which expresses the ratio if the energy of desired signal components and the overall energy of the signal. For the presented system the coding efficiency is on the order of 1-10% [5], depending on specific modulator settings, which results in wide-ranging implications regarding circuit design and modeling of the circuit. Ultimately, this is equivalent to envelope elimination and restoration approach with only a single bit encoding of the envelope and a binary drive signal.

The concept of employing a PWM modulator with noise shaping techniques together with switched mode power amplifiers, is well established [6], and found nowadays primarily in base-band applications of moderate bandwidth. The combinations of switched mode amplifier and noise shaping modulator have substantial benefits, namely superb linearity, broad band operation, and high efficiency [7]. However, that comes at the expense of operating the whole circuit, including the power amplifier, at frequencies orders of magnitude higher than the bandwidth of the system and the need for low-loss yet very selective filters to eliminate unwanted modulator noise. While this is not a big issue, when dealing for example with audio signals, expanding this concept to radio frequency (RF) systems in a straight forward manner is not possible. One key idea to get around this problem is to further incorporate the up-converter into the system. Works like [8] [9] [10] [11] have demonstrated concepts that are based on this idea and are more suitable for typical RF modulation schemes. Furthermore, they are realizable with readily available components. However, designing a setup capable of delivering significant output power at center-frequencies in the GHz domain is a challenging task.

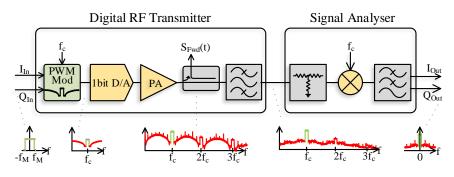

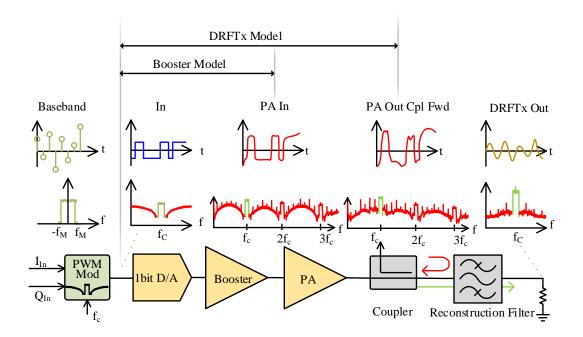

Additionally, there is an ongoing trend of incorporating as much as possible into the digital signal processing chain of the RF system which led to the concept of digital-SMPAs [9]. Here, an SMPA is directly excited by the binary output of a PWM modulator operating the power stage permanently in a saturated regime. Determining the overall energy efficiency of such a system is not a trivial task and is discussed in works like [12]. However, the resulting excitation signals are very broadband what makes dealing with nonlinear effects a challenging task. Figure 1.1 provides an overview of a DRFTx system including the spectrum of the signals in question at relevant sections

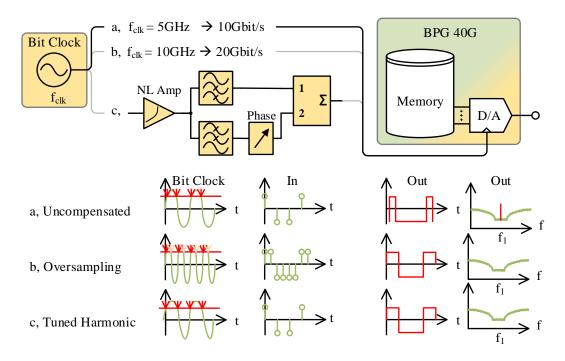

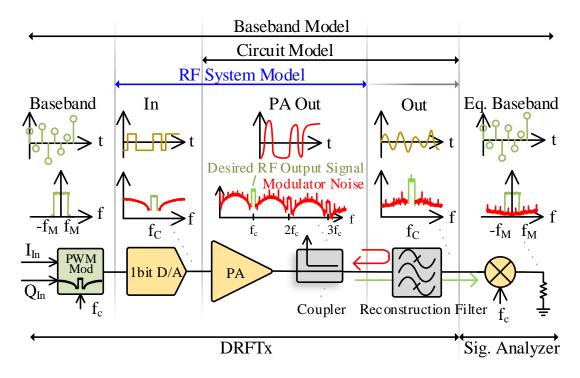

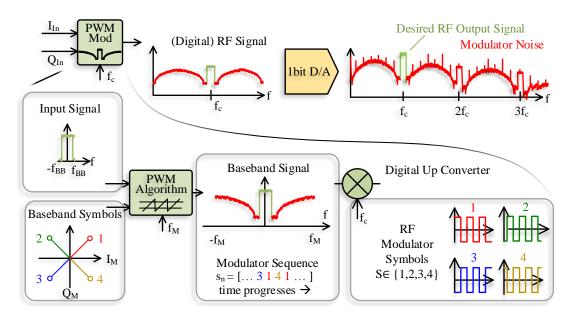

Figure 1.1: Operation principle of a DRFTx.

in the circuit.

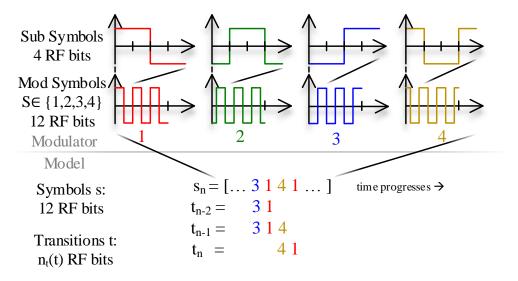

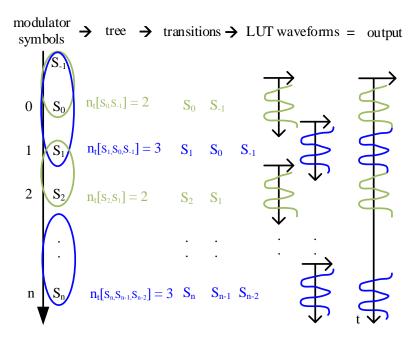

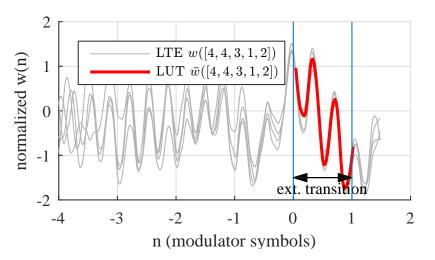

The inner workings of the PWM modulator discussed within this thesis were published in [5] [13], and, [14]. Figure 1.1 illustrates the most important interrelations and signals related to the PWM modulator. Basically, it generates its binary output signal reassembling the desired output signal from a digital input signal and a predetermined set of baseband symbols. In a first step, a baseband version of the output signal is formed by the PWM algorithm employed in the PWM modulator. The algorithm is operating at a higher sampling rate than the input sequence which allows to utilize noise shaping. Although the sequence already reassembles the desired output signal, it is still located in the baseband of the modulator. The digital up converter shifts this frequency band to the RF domain by remapping the baseband symbols to RF symbols. These RF symbols need be chosen appropriately according to the different sampling rate of input sequence, modulator sampling frequency, as well as the center frequency. A single bit digital to analog converter (DAC) is required in order to gain a time continuous version of the signal used to drive the following stages of the DRFTx circuit.

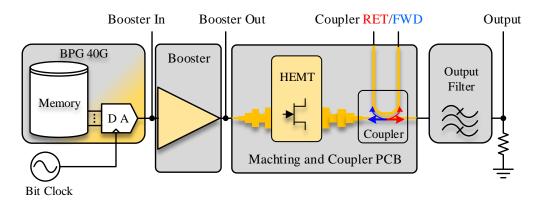

### **1.2** Circuit Design Considerations

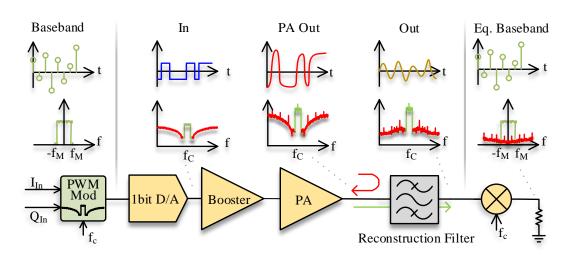

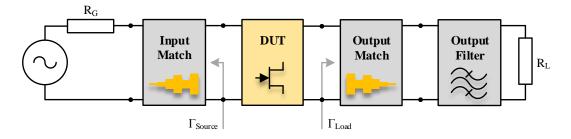

Figure 1.2 provides an overview on the circuit modules of a DRFTx and typical signals at important interfaces. A DRFTx system uses a digital PWM modulator to generate the desired RF-signal within its modulation bandwidth. Therefore, the input signal of the analog section is binary and requires a high bit rate in the range of 10 Gbit/s to

Figure 1.2: Circuit modules and typical signals within of a DRFTx.

be feasible for the task at hand. Practically all digital sources capable of delivering such a data rate use low voltage differential signaling (LVDS). From a circuit design perspective, such a signal is very weak compared to the drive levels required in order to reach saturation within the PA stage. This calls for a booster amplifier in between the LVDS output of the modulator and the PA stage. However, broadband high gain limiting-amplifiers are notoriously nonlinear. Although not all nonlinear effects degrade the overall linearity of the system due to the special nature of the signal, any nonlinear contribution that produces signal components within the modulation band reduces the overall linearity. This is discussed throughout chapter 4, where different methods are discussed that allow to test a given circuit for memory affected nonlinear behavior.

Since the majority of the energy of the signal is located outside the modulation band, the PA's mode of operation is dominantly defined by the side products of the PWM modulator, instead of the intended output signal. Thus, the design of the PA stage in this setup is strongly dependent on the output signal of the modulator. This is at odds with classical PA design approaches and the utilized approach is documented in section 2.3. Furthermore, the PA design strategy is also very closely related to the design of the reconstruction filter that also makes up a significant part of the PA's output matching network. Designing this filter is a balancing act. On one hand, high suppression of modulator noise at the output and the requirement for highly reflective terminations in harmonic controlled amplifiers is in favor of a very narrow band reconstruction filter that requires high quality factors. On the other hand, by having highly reflective terminations, load-modulation effects at the output of the active device are poorly dampened. If these effects exhibit time constants, that are not negligibly short compared to the sequence length of the PWM-modulator, quasi static design considerations will fail. So to reduce distortion introduced by nonlinear memory effects an absorptive, low quality factor filter would be beneficial. This kind of memory induced, nonlinear behavior was in fact observed in the lab setup, so the corresponding interpretation and analysis of these effects is one of the major parts in this work. Thirdly, the need for a higher order filter that is required to handle multiple times the output power of the system, features a tuneable center frequency, and behaves highly linear is disastrous at best. In fact, herein lies the most problematic design aspect of this concept. While piezo electric tuneable cavity filters [15] have the potential to make this problem approachable, no solution that utilizes current technology will be neither economically feasible, nor will it be a physically compact one. Nevertheless, this problem is very interesting from an academic point of view.

### **1.3 Modeling Considerations for DRFTx Systems**

Finding a balance between the complexity of the modulator, the circuit design, and nonlinear distortion is essential to build an overall efficient DRFTx setup. Doing so in an experimental manner is possible, however, time consuming and requires new hardware iterations for any new circuit to be tested. It was demonstrated [16] that the observed memory induced nonlinear effects can be measured and modeled effectively in time domain, which makes it possible to efficiently perform circuit-modulator codesign.

Modeling complex systems is nearly as much about describing specific dependencies, as it is about splitting a complicated system into more manageable parts that can be analyzed separately. As indicated in Figure 1.2, a DRFTx consists of numerous parts that need to be considered in order to capture the behavior of such a system. The first step towards partitioning this system is to have a separate model for the PWMmodulator. This is straight forward, since the modulator is implemented in software and has clear defined interfaces. It is excited by the desired output signal provided in the equivalent base-band and requires some parameters that define its resulting center frequency, noise shaping, and its resulting bandwidth. While these parameters may affect the circuit with regards to in-band linearity or overall energy efficiency, the functionality of the modulator is not influenced by any effects in the circuit. Therefore, the modulator is considered a black-box in this work and its inner workings are not investigated, however, it is extensively described in [14].

In contrast to the modulator, the circuit cannot be segmented as extensively as it is done in many more traditional design approaches. A partitioning of the circuit is hindered due to two main differences in the way this circuit operates:

Firstly, traditional design approaches usually consider the amplifier of a TX-system as quasi-stationary nonlinear. In the presented case, however, the load modulation of the active device causes an entanglement between the nonlinear circuitry and the statistics of the input signal. Measurements [16] show that the memory depth of the circuit is in the same range as typical burst lengths of the the modulator, which clearly violates the assumed quasi-stationary behavior. Therefore, methods like passive tunerbased load-pull cannot be applied directly for such circuits since they require quasistatic load conditions for the DUT. Chapter 2 elaborates this issue in greater detail. For the same reasons, assigning a class of operation to a DRFTx is not meaningful. Dependent on the excitation sequence, the active device's mode of operation changes drastically as demonstrated in chapter 4.

Secondly, a DRFTx produces the desired RF waveform by means of a binary modulator. The spectrum of the binary signal resembles the desired spectrum around a chosen center frequency [17], however, the modulator also introduces modulator noise [5]. The output signal of the modulator is composed of many components. Its power spectral density is illustrated in Figure 1.2, which also indicates the frequency-band occupied by the desired RF-signal. The cumulative power of the modulator noise usually supersedes the overall power of the intentional signal. The corresponding power ratio of intended RF signal and the overall signal power is denoted as coding efficiency [12], which is 2-5 % for the described system. Therefore, in order to achieve a certain behavior of the active device, like power efficient operation, the entirety of signals present at the active device need to be known. Even though, around 95 % of these signals do not contribute to the desired output signal.

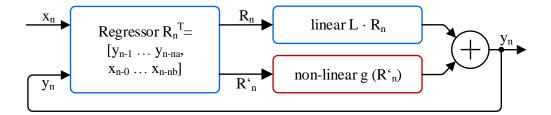

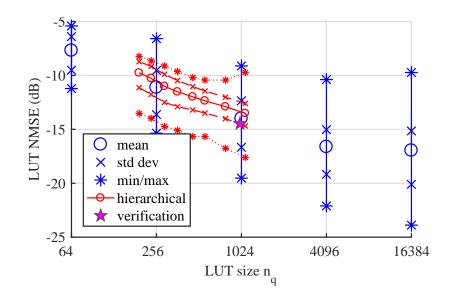

Out of this set of possibilities a lookup table (LUT) model has been found to be the

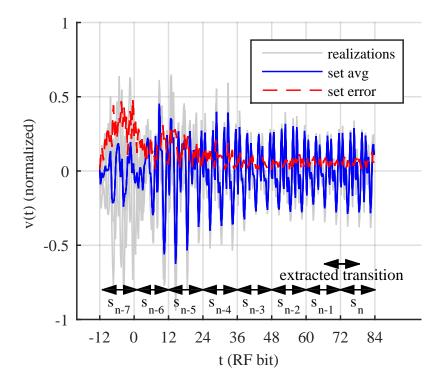

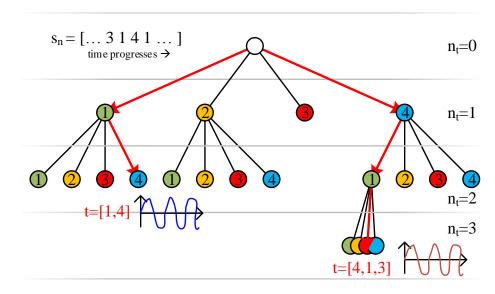

most practical choice, because it provides a compact nonlinear model which allows to adaptively capture the memory depth of the circuit. It is based on a LUT, consisting of the output waveforms of the system for all possible input symbol combinations up to a certain memory depth. In order to predict the output of the system, it combines LUT entries according to the input sequence in question. In a general case such an approach is impractical since it would require a huge LUT to capture the multitude of possible input signals. However, this model exploits the fact that any excitation signal, as provided by the PWM-modulator, is composed of a limited set of binary symbols. This greatly simplifies the structure of the LUT and allows to cover all possible input signals with a discrete set of input symbol combinations. Since this model takes advantage from the limited signal space used by the modulator, it is a less general approach than a filter model. However, while this limits the model to a specific set of PWM parameters it does not anticipate a specific baseband encoder/modulation algorithm. The PWM parameters are strongly linked to the target application and technology used. Hence, this limitation doesn't limit the universality of the model in practice.

Chapter 2 elaborates what capabilities are required from a test bench in order to characterize a DRFTx. The following chapter 3 explains the design of the DRFTx, that served as the DUT in the test bench. The modeling issues specific to the DRFTx, as well as its ramifications, are explained in chapter 4. Since there are many possibilities how to describe memory induced, nonlinear behavior chapters 5 and 6 show how to obtain practical relevant models based on auto-regressive- and LUT-model approaches. The results and noteworthy aspects of each of these are discussed in chapter 7 which also concludes this work and provides an outlook on potential expansions of that concept.

## CHAPTER 2

# TEST BENCH FOR DIGITAL RF Transmitters

In contrast to Software Defined Radios (SDR), which are the functional siblings of DRFTxs, there are no standardized hardware platforms to conduct research, mostly due to the fact that DRFTx setups need to be built purposely for a given frequency and power range. As explained in chapter 1, building a DRFTx is about building a transmitter that operates power efficiently across different modulation formats and power levels and not about finding a universal transmitter architecture like a SDR. This ambitious goal requires to co-develop RF-modulator algorithms and DRFTx circuitry. A DRFTx is a complex piece of circuitry and its modules are strongly depending on each other. Therefore, it requires some dedicated design methods which utilize data gained from different functional units to optimize the overall functionality which is impossible to illustrate for the individual unit. The focus of this chapter is to illustrate these dependencies and how they can be addressed. This is complemented by chapter 3 which explains the more cohesive design methods and measurements that have been used.

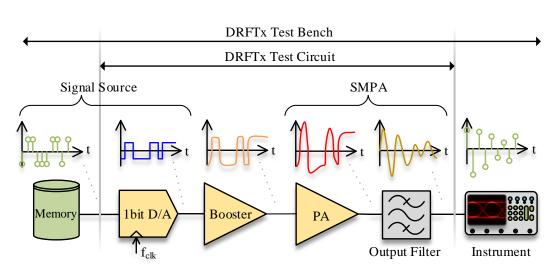

This chapter describes the DRFTx that served as DUT as well as the setup of the test bench itself. The test bench must allow testing different DRFTx algorithms and circuitry against each other. Therefore, modularity and flexibility have been given top priority over available yet rigid solutions. It also explains why nonlinear modeling is a necessary step to develop nonlinear memory affected circuits that operate efficiently

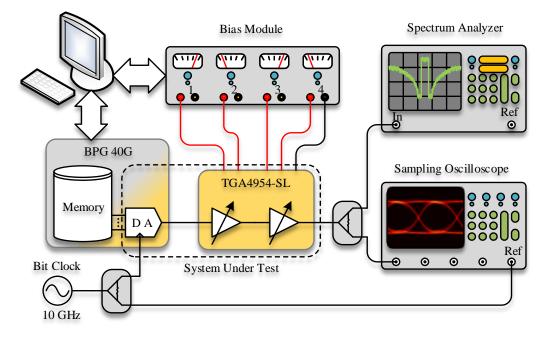

Figure 2.1: Test bench overview

under modulated excitation. While this chapter has a focus on the interaction between the different functional modules, chapter 3 complements this by elaborating the inner workings of these models and the design choices that went into them. Chapter 4 explains how the nonlinear memory affected behavior can be gauged, even though modulators are not available or their performance is insufficient. Modeling the circuit is in many ways superior over just characterizing it. Different modeling approaches suitable for this type of circuits are described and compared in chapters 5 to 7.

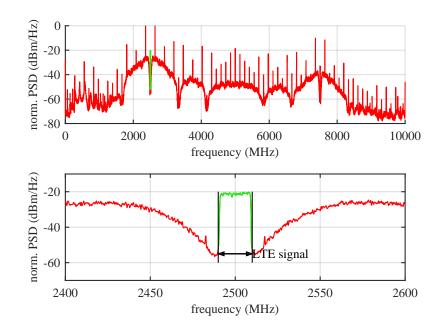

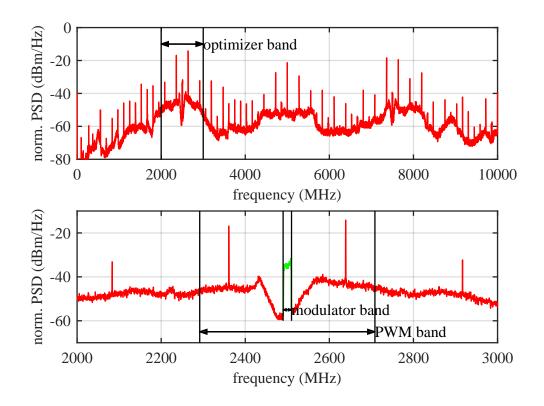

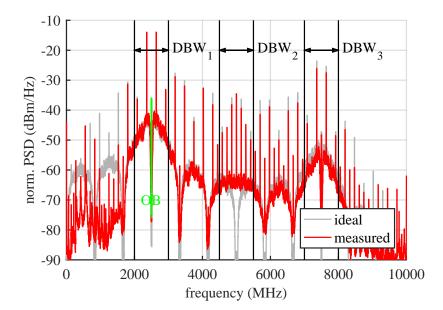

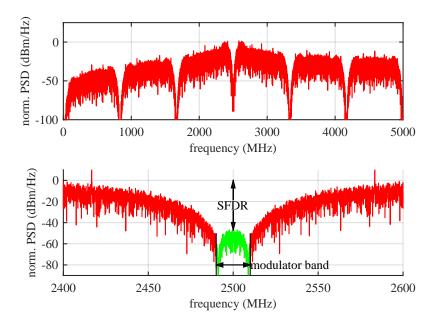

The experimental nature of this work is reflected in not having stringent circuit parameters to be met. However, there are some overarching design goals and parameters that are derived from the potential target application, namely an LTE transmitter: The DRFTx was designed to work as an LTE transmitter for a channel bandwidth of  $f_{Mod} = 20$  MHz around a center frequency about  $f_c = 2.5$  GHz. The exact center frequency can be adjusted by means of the employed modulator [14]. The utilized modulator symbol length is  $n_s = 4$  bit, resulting in a bit rate of  $f_{bit} = 10$  Gbit/s for the excitation signal. This in return defines the modulator's fundamental frequency to be  $f_1 = f_{bit}/n_s = 2.5$  GHz. A measured spectrum of such an excitation signal is depicted in Figure 2.2.

In order to provide comparability to other works, the very popular *CGH40010F* HEMT from *Cree* was chosen as the active device in the PA stage rated for about 10 W of saturated output power. Other stages like the booster amplifier or the output

Figure 2.2: Power spectral density of the PWM modulated excitation signal

filter where designed to fit in with the requirements defined by the application as LTE transmitter.

### 2.1 Signal Source

A binary signal source, capable of operating at 10 Gbit/s with sufficient memory to store a modulated LTE frame is required to excite the attached circuitry. A *BPG 40G* from *Sympuls Aachen* was used throughout this work. However, since the unit does not provide an internal bit clock signal an RF source (*Agilent E8244A*) acts as a configurable bit clock. It is used to drive the bit pattern generator and to synchronize the attached measurement equipment with the bit pattern generator. To generate a specific excitation sequence, the bit-pattern-generator can be loaded with an arbitrary bit sequence which is played back repetitively.

As the bit-pattern generator is designed to test digital communication equipment, it operates on a double data rate principle. This, however, is problematic with respect to the task at hand since it causes asymmetric bit durations. Any offset error in the

Figure 2.3: The digital signal source and used bit length balancing

bit-pattern generator's clock input or any asymmetry of the circuitry that goes with it affects the bit duration. Therefore, the duration of a bit triggered by the falling edge will be slightly different to one triggered by a rising edge. The distortion due to this effect is most noticeable in the frequency domain since it causes additional spurs. In contrast to a random clock jitter, which causes an evenly raised noise floor in the DAC's output signal, a deterministic variation in bit duration gives rise to undesired spectral lines [18].

Since the bit clock is an integer multiple  $n_s$  of the modulator's base frequency  $f_1$ , it causes significant distortion around the system's center frequency. Strictly speaking this effect is one example for memory induced, nonlinear distortion since two adjacent bits affect their individual bit length depending on their values. Although, as this effect only shows a memory depth of two RF-bits, it is rather short in comparison to others discussed in this work. Section 4.1 discusses how this effect can be quantified. In any case this effect reduces the dynamic range of the overall system. Therefore, it needs to be compensated. Two methods have been investigated to tackle this issue:

The first approach simply oversamples the input sequence by a factor of two and

increases the clock rate to twice the bit rate. While this method eliminates the effect perfectly without the need for tuning and for any possible clock rate, it effectively halves the bit-pattern generator's memory. Since some of the excitation sequences require memory on the order of  $10^6$  bits, this method is not optimal in every sense.

Secondly, a nonlinear amplifier is used to generate a distorted version of the clock signal. A diplexer then separates the fundamental frequency from the predominant first harmonic while a phase shifter allows varying the phase relation of these two components. Doing so, allows the waveform to be modified in order to compensate the observed uneven bit's length. However, it requires the phase shifter to be tuned according to measurements. On top of that, this approach also suffers from a significant drift and temperature dependence. Therefore, the oversampling method was used when ever possible. Figure 2.3 depicts this issue and the two methods that have been used to mitigate this behavior.

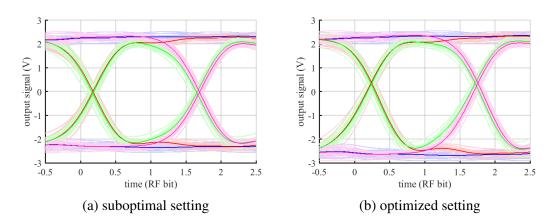

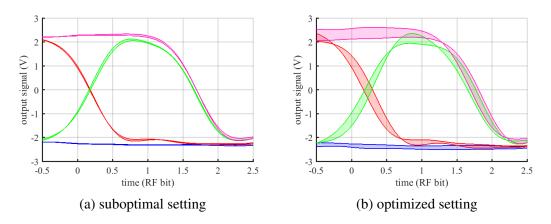

### 2.2 Booster Amplifier

The booster amplifier stage is necessary to amplify the small voltage swing provided by the signal source to levels suitable for driving an RF transistor into saturation. It consists of an integrated limiting amplifier namely the *TGA4954-SL* from *TriQuint*. This device is intended for driving Mach-Zehnder modulators up to about 12.5 GBit/s with +30 dBm output power. Its properties make it suitable as gate driver as well. Furthermore, the TGA4954-SL's output waveform can be continuously tuned by its bias voltages. This basically affects both, the output voltage swing, and the pulse symmetry, which are both critical parameters for controlling the overall nonlinear behavior. Setting the bias for this unit in a consistent manner is a nontrivial task that is discussed in section 3.1.

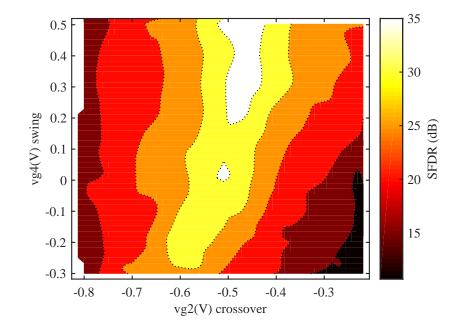

From a design perspective it is important to find an optimal bias setting with respect to nonlinear distortion. As explained in section 4.1, static nonlinear distortion does not affect the linearity of a binary system. However, memory afflicted nonlinear behavior limits the maximum dynamic range of the system. Therefore, the bias settings of the booster amplifier were optimized to reduce these effects in a setup as depicted in Figure 2.4. Works like [19] and [20] have demonstrated that this is vital for the quality of the overall setup.

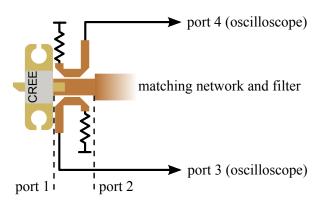

Figure 2.4: Setup used to investigate the booster's nonlinear distortion.

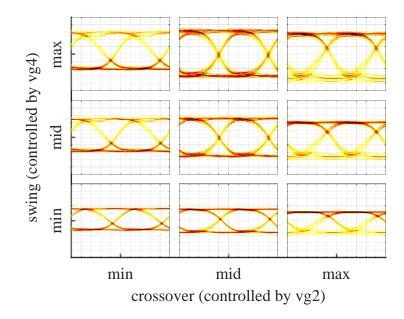

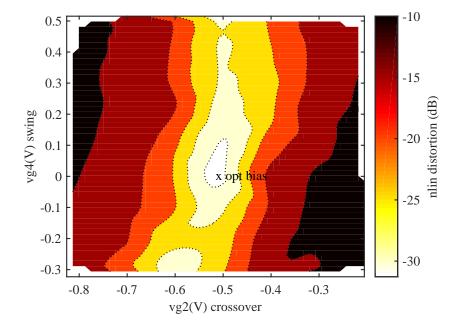

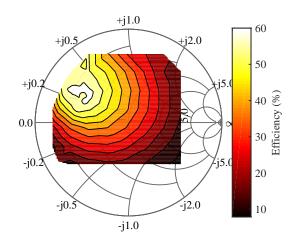

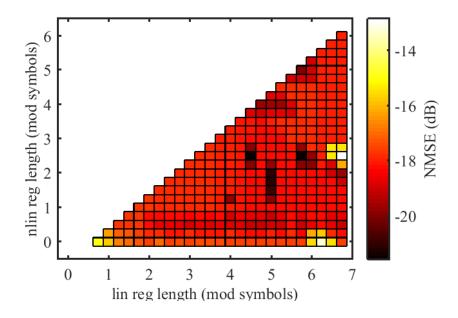

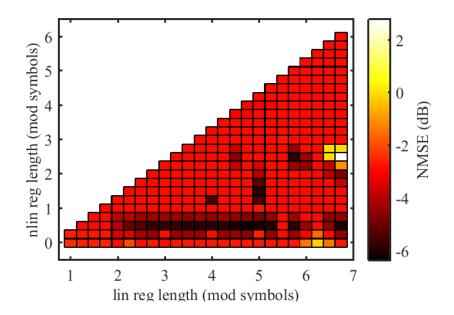

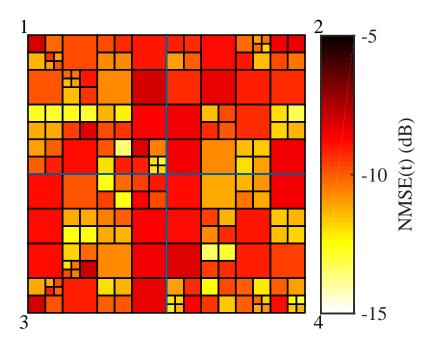

Figure 2.5 illustrates this effect by visualizing the achieved dynamic range depending on the bias setting. The measurement method is described in section 4.1. In the following, only bias points in the favorable region that form the central ridge in this graph have been used to bias this stage.

In the ideal case the resulting dynamic range is solely limited by the employed modulator. Therefore, deriving measurements based on the modulator's output signals can be sub-optimal. This can be avoided by utilizing test methods that use very generic excitation signals that don't require a modulator. For this work a characterization method based on eye-diagrams was investigated (section 4.1) as well as an auto regressive behavioral model (chapter 5).

The eye diagram is a convenient way to visualize the amplifier's variable performance depending on its bias. Figure 2.6, provides an overview. Some settings produce very symmetric eye diagrams, while in other cases they result in less regular patterns. Nonetheless, how this affects the resulting RF-signals' quality is not easy to predict. Although, the effect can be quantified by using the method described in section 4.1.

Figure 2.5: Memory induced, nonlinear distortion as function of the booster stage's bias settings measured in frequency domain.

Figure 2.6: Eye diagram of the booster amplifier's output depending in the applied bias settings.

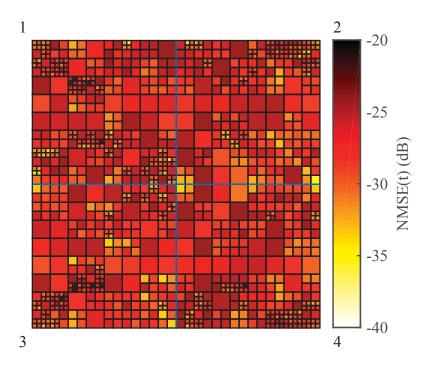

The results are depicted in Figure 2.7 and verify that the beneficial bias settings, as identified using frequency domain measurements, are correct.

Figure 2.7: Memory induced, nonlinear distortion as function of the booster stage's bias estimated based on its eye diagram.

One drawback of these methods is that they allow characterizing only the memory induced, nonlinear distortion, however, they provide no information about the memory depth of this effect. By finding a model for the circuit it is possible to gain more insight by evaluating the resulting modeling error over the model's complexity. This is explained in greater details in chapter 5.

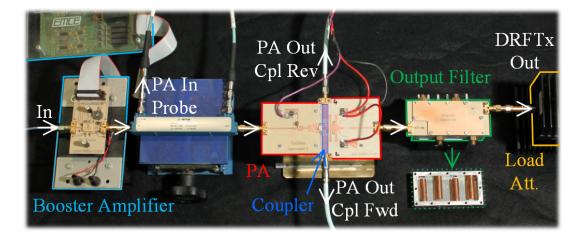

To provide a more tangible illustration of the hardware making up this section, the booster amplifier and its peripherals can be found in Figure 2.14. The booster amplifier in this pictured is attached to the bias controller using a ribbon cable and are marked with the same blue color frame.

### 2.3 **Power Amplification Stage**

Switch-mode power amplifiers (SMPAs) are promising candidates for the power amplification stage in DRFTx systems. Their potential high power efficiency, which is gained by exploiting the nonlinear nature of the transistor, makes them attractive for this kind of application. By using a matching network and output filter combination that is highly reflective at the signal's harmonics, the current and voltage waveform at the transistor's output can be adjusted. Depending on the configuration, a specific class of operation can be achieved [2]. In its basic variation this only holds true for the design frequency. However, continuous modes have been proposed [21] that allow to gain additional design space and realize highly efficient operation over a wider frequency range. SMPAs in continuous mode have demonstrated operational frequency ranges up to one octave [22]. Although, it is important to note that the efficiency achieved in these works is measured using continuous wave (CW) excitation of varying frequency, not for modulated excitation. If modulated signals are used to drive the circuit, the power efficiency significantly reduces [23] [12]. Therefore, having a SMPA that is delivering good performance over a wide frequency range is not equivalent with achieving high efficiency under broadband modulated excitation.

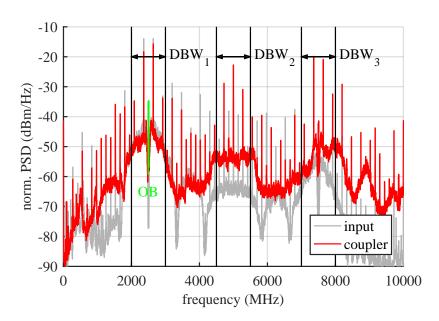

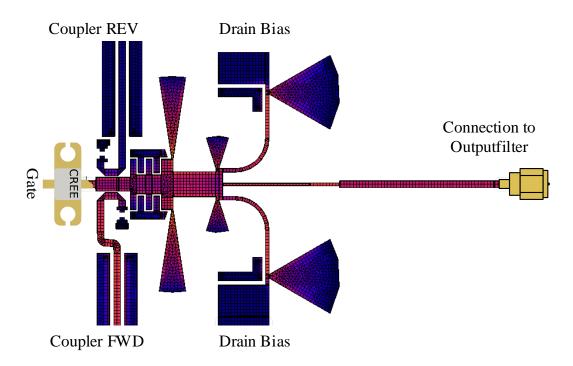

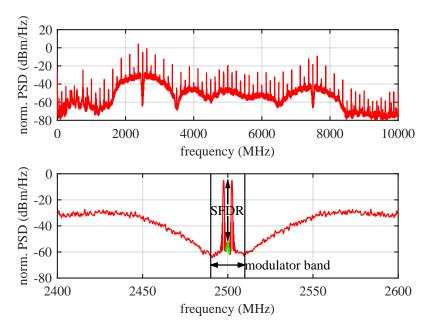

Figure 2.8: Circuit elements of the power amplifier stage

The signal's components provided by the PWM modulator can be separated into two categories. Firstly, there is the intended RF signal located around the desired center frequency, secondly, there is the modulator noise. This is depicted in Figure 2.2 and 2.9 which depict the spectrum of the excitation-signal and at the PA's transistor respectively. The red signal components indicate the modulator noise and the green components correspond to the desired signal. The ratio of the powers of these two components is usually referred to as coding efficiency [13] and is determined by the PWM modulator's parameters. For the utilized modulator and a 20 MHz LTE signal the coding efficiency is typically ranging from 2-5 %.

In both cases, about 90 % of the signal's power is distributed over a bandwidth of

310 MHz around the center frequency, which underlines the wide bandwidth of the system. The desired LTE signal is located in the center and occupies only 20 MHz of bandwidth. The frequency bands denoted in Figure 2.9 indicate which parts of the spectrum are relevant for individual functional units. While the modulator-band contains the desired RF-signal, the PWM-band is the part of the spectrum that is considered within the equivalent baseband of the modulator. The optimizer-band is the sum of all fundamental frequencies that are used to design the power amplification stage. A more formal definition of those frequency bands can be found in subsection 3.3.

Figure 2.9: Power spectral density of DRFTx's output signal measured at its coupler for LTE excitation.

This calls for a specialized design approach since straightforward amplifying all signal components in the excitation, even if accomplished in energy efficient manner, is not suitable. Since the modulator noise is accounting for 95-98% of the overall power, using an absorptive output filter would limit the overall power efficiency to

#### 2-5 % and render the system to be inefficient per definition [11].

Filtering the modulator noise signal in between the booster and the PA stage would eliminate the need for a specialized design approach of the PA. However, this would also destroy the binary nature of the signal at this point. Binary signals represent a special case when dealing with nonlinear systems because their potential dynamic range does not degrade when applied to a static nonlinear system [18]. This makes binary excitation signals very attractive for nonlinear power amplifier designs and interesting from a scientific perspective. Therefore, it was decided to investigate solely the option of driving the PA with a binary signal.

Broadly speaking, typical continuous mode SMPAs utilize matching networks that optimize a single figure of merit over a given design frequency range implicitly assuming narrow-band excitation. In the case of continuous mode Class-F amplifiers for example, the power added efficiency (PAE) is optimized over their design frequency range [21] including their harmonics, however, without addressing any other signal components outside this frequency range.

The starting point for designing the PA was to adapt an existing continuous mode PA design [24] to the specification of this project. This was described in [25], although, this work expands the method by employing a banded approach. The idea behind it is to distinguish between modulator noise and intended RF signal already in the design phase and adapt the matching network and filter components accordingly, as described in chapter 3, section 3.3. By distinguishing these signal components, the target is to minimize the power consumption attributed to sustain the modulator noise while achieving efficient amplification for the desired output signal.

This is a paradigm shift with respect to many other RF-design approaches as the design evolves as much around the modulator noise as with respect to desired output signal. The very frequency selective transition between these bands is dictated by the design of the output filter. However, in order to achieve certain operational properties of the PA specific source- and load-trajectories have to be realized at the PA's transistor. The filter alone does not offer enough design space to accomplish this. However, by introducing a matching network between the active device and the output filter it is possible to overcome these issues.

From a design perspective this leaves two issues to be solved: Firstly, favorable source- and load-conditions need to be identified in order to optimize a design for such

a banded approach. Section 3.2 explains the relevant issues regarding this method and explain how this method was used in this project.

Secondly, a realizable matching network needs to be found that maximizes a figure of merit based on the load-pull contours. The theory behind this step is discussed in section 3.4 alongside the realization of the matching network for this work.

Practical designs are hindered mostly due to the huge bandwidth required for the load pull measurements. However, it has been demonstrated that designs based on load-pull measurements that cannot utilize modulated excitation [26] improve the DRFTx efficiency over standalone SMPA designs.

### 2.4 Output Filter

In a DRFTx the output filter serves a double purpose. On one hand, it is intended to suppress the modulator noise at the overall system's output. As depicted in Figure 2.9, the majority of the PA's output signal energy is located outside the modulation band. Therefore, the need for high suppression and the requirement for highly reflective terminations in harmonic controlled amplifiers is in favor of a very narrow band, high quality factor (Hi-Q) reconstruction filter.

On the other hand designing a matching network incorporating a high-Q factor filter is much more challenging and less stable with respect to manufacturing tolerances. It also introduces a potentially nonlinear feedback between active device and filter which gives rise to the generation of additional unwanted signal components [27] and causes prolonged load-modulation driven by the energy stored in the filter. If these effects exhibit time constants in the range of the PWM-modulator's sequence length or longer, this effect will significantly contribute to overall memory of the system. To ease the matching network design and to reduce nonlinear memory effects, theoretically, an absorptive or low quality factor filter would be beneficial.

Finally, the filter needs to be able to handle the system's output power, which is in the ballpark of the transistor's saturated output power of about 10 W.

This ultimately results in a trade off between potential energy efficient operation, memory depth and design complexity. Since this work aims at energy efficient operation, a highly reflective termination of the active device was chosen [11]. To ensure low insertion loss at a relatively low bandwidth of 1.6 % a fourth order interdigital filter

Figure 2.10: The output filter used in the DRFTx test bench.

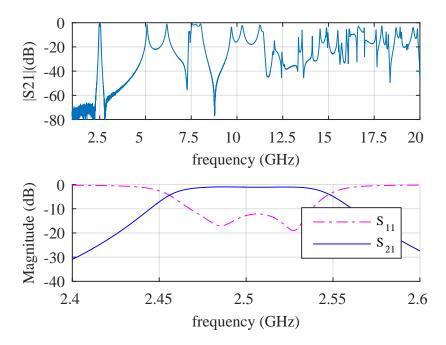

with a bandwidth of 40 MHz was chosen. The filter was based on a computer aided design, carried out in *HFSS*, and custom built to provide best control over its properties. A photograph of the filter can be found in Figure 2.10.

Measured results of the filter's S-parameters are depicted in figure 2.11. Around the center-frequency of 2.5 GHz this unit provides the frequency selectivity needed to separate the desired RF-signal from other signal components. However, at the harmonics of this frequency the filter also couples to its output as well as at some other higher modes occurring above 5 GHz. If only the filter would be used to set the load condition to the transistor this would be an issue due to leaking harmonic content. Although, the matching network has a low pass characteristic which rejects this components before reaching the output filter. To get a more holistic result of this circuit section, see section 3.5.

Settling on a specific filter, PA and modulator combination is the most important design decision for this class of circuits. It is important to note that the nonlinear contributions of all of these parts are well researched as isolated phenomenons. However, only their interaction gives rise to memory induced, nonlinear behavior. Since this type of distortion is very interesting from an academic standpoint and not very well researched, it was decided to use a filter that will contribute to a deeper nonlinear memory instead of building just another nonlinear amplifier with short memory. Inherently this causes potentially bad distortion performance that goes with it, how-

Figure 2.11: Measured characteristics of the filter utilized as the output filter in the DRFTx test bench.

ever, this is a more radical approach towards efficiency and also allows to study more pronounced memory induced, nonlinear behavior.

### 2.5 Output Coupler

The output filter is a necessary component within a DRFTx, however, when it comes to characterizing the circuitry it causes some issues. The output filter's narrow relative bandwidth makes many frequency components unobservable through the system's output. Especially when using very broad band instruments which have inherently lower dynamic range. Conducting circuit characterization solely based on the signal components present within the modulator band can be sufficient for distortion analysis, however, lacks most of the modulator noise which is mostly defining the PA's efficiency.

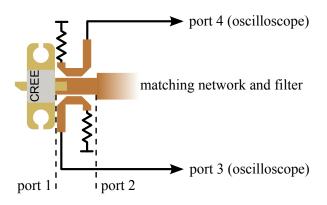

To overcome this issue, a coupler is integrated into the matching network between the transistor and the filter. This allows, in combination with a calibration step, to gain access to almost the entirety of signals present at this stage. On top of this common deembedding techniques can be applied to directly measure current- and voltagewaveforms at the intrinsic transistor. The design and calibration of a coupler designed for this application was already published in [28], however, the most important aspects are summarized in this section.

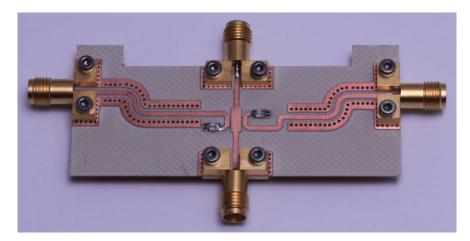

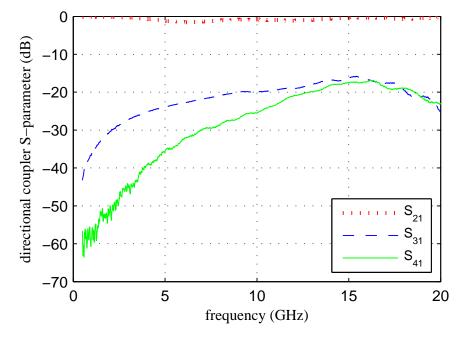

Figure 2.12: Dual directional coupler

For the design of the directional coupler several design issues have to be considered. Firstly, a microstrip line based topology is required to allow an integration into the transistor's matching network as described in section 3.3. Secondly, a high bandwidth is a major design goal to be able to cover a bandwidth of about 500 MHz up to 20 GHz.

To achieve a reasonable high bandwidth, the coupled length has been chosen such that the quarter wave resonance is out of the desired frequency band. Hence, the coupled length becomes small which lowers both coupling factor and directivity. While the low coupling factor is beneficial for the intended application, its other characteristics are suboptimum. However, due to the calibration presented in [28] the error of the directional coupler can be mathematically corrected to allow for exact measurement results.

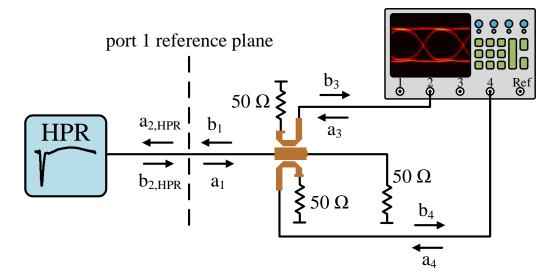

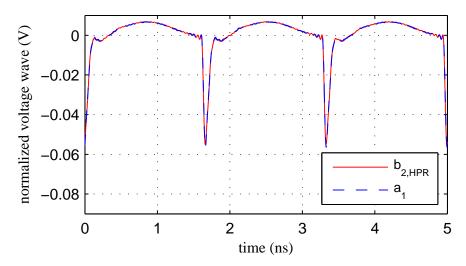

### 2.6 Measurement Setup

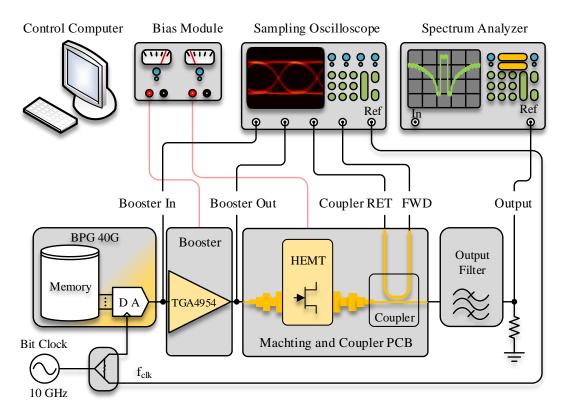

The sum of all these components including some measurement instruments makes up the resulting DRFTx test bench. A conceptual diagram of it is depicted in Figure 2.13.

It allows to gain a multitude of different time- and frequency-domain measurements at important interfaces of the DRFTx. The individual interfaces are also named within Figure 2.13 to clarify from which signal specific measurements are derived.

Figure 2.13: Test bench setup used for modeling

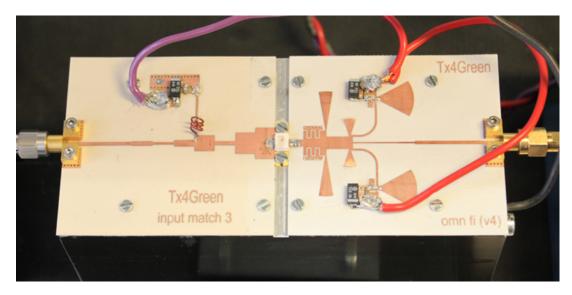

To put that into perspective, Figure 2.14 provides a photograph of the test bench. The picture also indicates some important signals, indicated by red lines with arrows. However, one has to keep in mind that several different measurements were conducted using this setup and only a typical configuration is depicted here. When discussing individual measurement results and the corresponding modeling in chapter 4, any deviation from this setup is explicitly stated.

Figure 2.14: Photograph of the DRFTx used in the test bench.

# **CHAPTER 3**

# DESIGN OF DRFTX CIRCUIT MODULES

This chapter discusses the RF-circuit design specific issues evolving around the DRFTx setup that is explained in chapter 2. Some circuit components are vital for the practical use and functionality of the testbench, however, they are not directly related to the functionality as a signal source. As a result they are discussed in this chapter which is built around implementation. This is especially true for sections 3.1, 3.3 and 3.6.

As described in chapter 2, a DRFTx is a complex piece of circuitry and on top of that its modules are strongly interdependent. Chapter 2 illustrates how some design methods, which utilizes data gained from different functional units, optimize the overall functionality which is impossible to demonstrate for the individual unit. This chapter explains the more cohesive methods and the manufacturing challenges used in this work. Most prominent, the simplified real frequency technique (SRFT) is explained in section 3.4.

### 3.1 Bias Module for Experimental RF-Amplifiers

RF-amplifiers that operate close to their physical limits are inherently problematic in a test setup. They can fail due to many different reasons, however, thermal or electrical breakdown being the most common. In most cases it destroys the active device and, even more problematic, potentially also destroys the attached stages. This not only

results in financial inconvenience because simply replacing the active device is not enough to repair the setup. As active devices show significant component variations a redesign and re-manufacturing of the damaged circuits within the system as well may be required.

Sadly when designing highly efficient power amplifiers there is little to no space for safety margins in circuit design. Firstly, amplifiers need to operate in compression to function as SMPAs. This can be achieved by operating a device close to its electrical breakdown or utilizing a transistor designed for higher powers and restricting it artificially by lowering its bias. But, larger devices always suffer from lower gain and poorer frequency response which makes them ill suited for highly power efficient designs. Secondly, the waveform at the intrinsic amplifier cannot be measured in most cases. Therefore, under varying load conditions it is hard to predict if an active device is operated outside its specifications. If so, the device may spontaneously malfunction. Finally, the overall gain of cascaded amplifiers can be high enough that RF-leakage, for example through the bias circuits, can cause oscillations. Since this is a parasitic effect, that can occur not only at design frequencies, it is hard to predict. If it occurs it will likely lock up and destroy something by overheating it.

Since these problems cannot be addressed by overbuilding the circuit, they can be encountered by having failure protocols in place. If something fails, it is important to detect it and immediately power down the setup to a safe state. This is especially important since the test-setup is used to conduct many measurement runs in an automated but unattended fashion. In this work a purpose built bias unit was used to perform this functionality. It is a dedicated PCB with its own micro controller unit to decouple this functionality from the overall measurement setup. It allows biasing a circuit that requires up to four control voltages and two bias rails using a state machine. During measurements it monitors these voltages as well as currents and temperatures to ensure stable conditions.

This unit has been used extensively during this project to bias and monitor the booster amplifier, as well as the PA's transistor in some cases. Having a dedicated module to control the booster amplifier's bias in an automated manner is necessary since the integrated limiting amplifier, namely the *TGA4954-SL*, requires a specific biasing sequence. Its four control voltages and two supply rails that need to be turned on and off in a specific sequence and some of the bias parameters depend on each other.

For example, two control voltages are found by measuring the idle current consumption of the overall circuit and adjusting the control voltages iteratively until a certain quiescent current ratio is achieved. Whenever it is required to alter the bias parameters for different measurements, it is necessary to power down the signal source and the booster module in a controlled manner and to start over with the adaptive bias routine.

#### **3.2** Load Pull Measurements and Setup

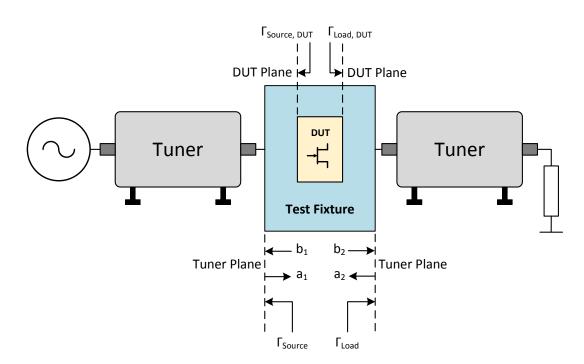

Biasing a transistor consistently is the first step to ensure RF-measurements are reproducible. The measurements gained from monitoring the bias can help to determine if the device is still functioning and well, however, these results carry little information about the RF-properties of the device. In recent years sophisticated computer-models and nonlinear measurement techniques have made an effort to replace lab experiments as the design method of choice to build RF-PAs. Although, especially when operating in a strongly nonlinear regime some measurement based characterization techniques have stood the test of time up to this day. Load pull setups for example are common place in today's RF-PA design [29]. While being around for decades, the need to deal with non-unilateral and nonlinear devices still poses design challenges that are hard to tackle using solely simulations.

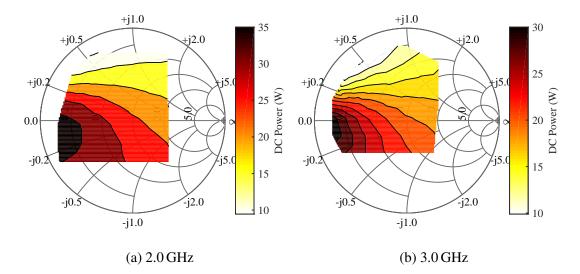

Load pull setups allow to measure the performance of transistors directly by exciting the active device using an RF signal source while manipulating the source- and load-impedance using so called tuners. It allows to record different performance measures as a function of the impedance imposed by the tuner. Typically, signal power levels and DC power consumption would be used to identify favorable input- and output-reflection coefficients for the given device. What is ultimately chosen to be used as the figure of merit and how to turn this information into a circuit defines the design of the PA.

A very basic load pull setup is depicted in Figure 3.1. There are many alternatives to this kind of setup that expand the capabilities with respect to bandwidth, harmonic tuning, modulated excitation, and so on. Choosing a specific setup strongly depends on the requirements imposed by the overarching project. In fact there are so many that discussing all possibilities is out of the scope of this work, however, suitable literature

Figure 3.1: Basic Load Pull Setup

is available [29]. Since a passive tuning setup was available, it was decided to utilize it for this project. Although, this still leaves room for many implementation options. While the basic idea is always the same, each approach has some intrinsic limitations or benefits. The relevant alternatives are briefly discussed in the following:

Passive tuner setups suffer from a tuning range that is bounded by having smaller than unity reflection coefficients. Additionally, passive tuners, which are usually based on a double slug tuner approach, are intrinsically narrow band and, therefore, can only be utilized with a CW or narrow band excitation.

Harmonic tuning concepts allow to control impendances at the fundamental and the harmonics of the excitation signal. If realized with a passive system they require multiple tuners, and therefore, have higher insertion losses. Depending on the implementation, they require sophisticated signal combiners to separate and combine the individual harmonic components, that intrinsically limit the available frequency range of the setup. Alternatively, multiple tuners can be cascaded to gain the desired additional design space. In the latter case, the dependencies between the individual tuners are captured by a more sophisticated calibration, although, achieving less precise results.

Active concepts can deal with modulated excitation and have no intrinsic limitation with respect to the synthesized reflection coefficients. However, since the wave traveling towards the active device  $(a_x)$  is artificially generated, these setups require some sophisticated active circuitry. The active tuner needs to handle the power required without distorting the signal, which is in the ballpark of the active device's saturated power. They need to synthesize given impedance trajectories for the design bandwidth, which directly translates to bandwidth demands of all the circuits involved. When harmonic concepts are employed, the individual signal bands around the harmonics need to be handled separately requiring additional active hardware. The overall bandwidth is further limited due to the fact that the signal's bandwidth at the harmonics grows with its order.

Finally, there are many kinds of hybrid approaches that combine some of these concepts, like using a passive tuner for the fundamental frequency and active branches at the harmonics for example.

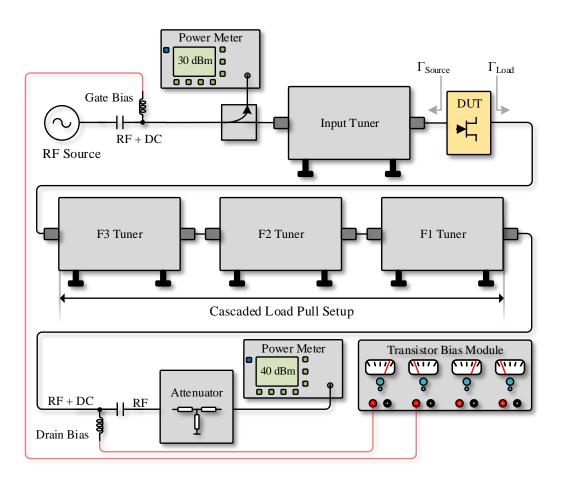

So choosing the most suitable load pull setup out of this variety is not a trivial task. The design of the PA for the DRFTx in this work would require a baseband bandwidth in the range of hundreds of MHz due to the employed modulator. That would require an extraordinarily expensive active load pull setup. Out of the passive options, cascaded tuning has been found to be the best compromise between setup complexity, measurement control ability, and, most important, bandwidth. Such a setup is depicted in Figure 3.2 and was used extensively throughout this project.

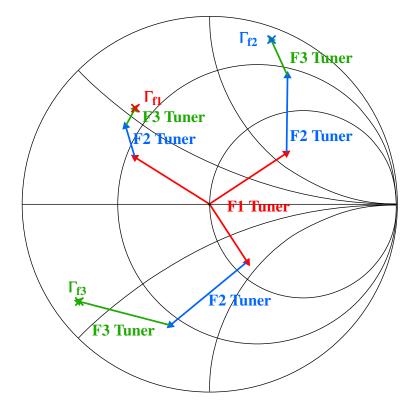

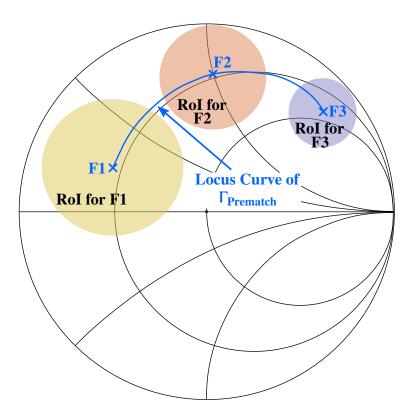

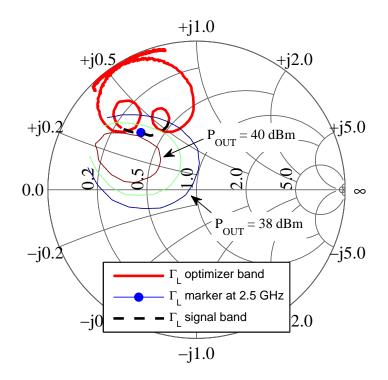

The setup uses only one tuner at the input, allowing to control solely the fundamental impedance at the active device's input, however, three tuners at the output to jointly control the impedances at the fundamental, first, and second harmonic at this interface. Circuit simulations have shown that this tuner combination yield sufficient control over the circuit's behavior to optimize gain and power efficiency. Figure 3.3 depicts the composition of three different reflection coefficients, realized at the fundamental- $f_1$ , the second- $f_2$  and third- harmonic  $f_3$  frequency. The contribution of the individual output tuners (F1, F2, and F3) are color coded correspondingly.

Since the resulting impedance at the individual frequencies is dependent on the mutual state of all load tuners, the mutual state of the tuners that result in the desired reflection coefficients needs to be found by pre-characterization measurements. This

Figure 3.2: Basic harmonic load pull setup

is based on a software package by *Maury Microwave* called *ATS5*. While the cascaded setup provides the opportunity to expand the capabilities to harmonic tuning, the mutual dependency also causes higher uncertainties when synthesizing specific impedance values. This design is based on [30] which explains these issues in greater detail.

The setup covers a broad frequency range  $f_{design}$  around the chosen fundamental  $f_1$  and is, therefore, often considered broadband. This is a problematic nomenclature since the load pull setup uses a swept CW source while the DRFTx target system (see Figure 2.2) uses a constant envelope, yet heavily modulated source to drive the amplifier. So while the setup is capable of covering the whole bandwidth, that is occupied by the PWM-modulator's excitation signal, it is important to note that the RF-excitation used in both setups is significantly different. However, works like [12] allow to pro-

Figure 3.3: Tuner dependencies in cascaded tuning setups

vide an estimated power efficiency based on load pull results. Therefore, it is possible to derive constructive system design measures for broad band modulated systems even though the measurements are derived from a narrow band load pull setup.

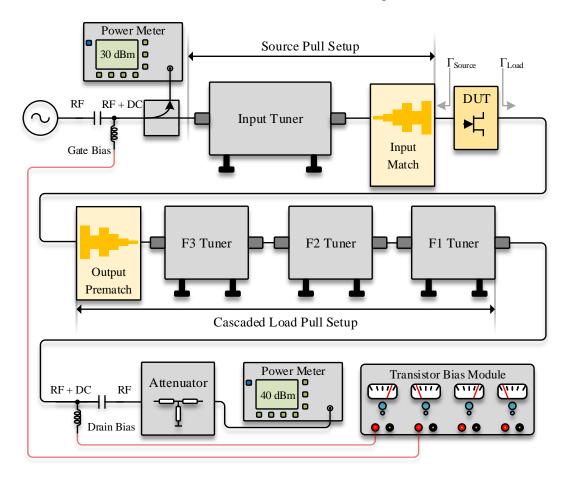

Measurements and simulations indicate that the basic setup depicted in Figure 3.2 lacks tuning range with respect to the maximum reflection coefficients imposed by the system's losses. Especially for the harmonic signal components at the transistor's output, highly reflective terminations are required to achieve beneficial load trajectories, which are identified in section 3.3. So cascading tuners alone is very useful to cover a very large proportion of the design space governed by the passive reflection coefficients. This way allows to narrow down the design space to dedicated regions of interest (RoI). However, after a specific range of reflection coefficients have been identified as RoI, additional circuitry is required to improve the maximum reflectivity

and resolution in this region. So called pre-matching circuits are introduced between tuner and DUT to accomplish this.

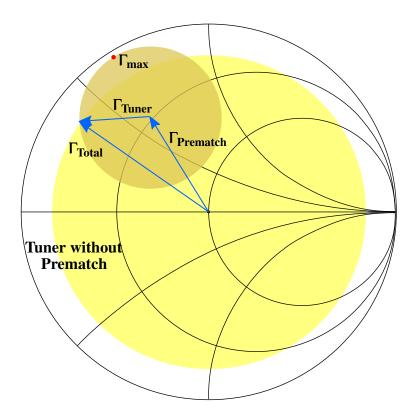

A setup including this extension is depicted in Figure 3.4. It is basically a passive structure that provides a controlled static reflection close to the active device. Since this is another lossy device, it also reduces the overall tuning range, however, it shifts it towards a RoI within the Smith-chart as illustrated in Figure 3.5.

Figure 3.4: Prematched harmonic load pull setup

The calculation of the resulting reflection coefficient  $\Gamma_{\text{Total}}$  is shown in eq. (3.1), where  $S_{12}$ ,  $S_{21}$ , and  $S_{22}$  are the S-parameters of the pre-match. As a result, the maximum achievable reflection coefficient  $\Gamma_{\text{max}}$  is greater than the maximum reflection coefficient of the tuner alone.

$$\Gamma_{Total} = \Gamma_{Prematch} + \frac{S_{12}S_{21}\Gamma_{Tuner}}{1 - S_{22}\Gamma_{Tuner}}$$

(3.1)

Figure 3.5: Tuning range with and without pre-match

Pre-matching is very useful to improve the coverage of a load pull setup for a limited RoI. However, in order to complement a cascaded tuning setup the pre-match circuit needs to take on a specific value for all harmonics that are considered in the given setup. In this work the number of harmonic considered is denoted by  $N_{PA} = 2$ . As aforementioned, by using cascaded harmonic tuning it is possible to cover a wide measurement bandwidth. However, in order to make use of this flexibility the RoI dictated by the pre-match circuit needs to encompass the optimum within the I design space for all considered design frequencies which are denoted as  $DBW_i$  at the individual harmonics  $i = 1..N_{PA}$ . Therefore, prior knowledge of the DUT's behaviour is required in order to tailor the pre-match circuits according to these requirements. By using

the cascaded tuning measurement setup without pre-match, RoIs for the individual frequencies can be estimated through interpolation. The measured results were in good agreement with circuit simulations. The synthesis of circuits based on this data is described in section 3.4.

Since this design procedure is based on having multiple frequency bands and some also corresponding harmonics, the individual frequency bands are also summed up in eq. (3.2).

Figure 3.6: Tuning range with prematching for three harmonics

The optimum reflection coefficient  $\Gamma_{ideal}(f)$  for the given circuit can be located using the pre-match design based on the framework as denoted in eq. (3.1). Figures 3.5 and 3.6 illustrate the transformation of the tuning ranges to a certain area of interest for the design bandwidth *DBW<sub>i</sub>* at each considered harmonic.

# **3.3 Matching Network Design**

The spectrum of a typical PWM modulated signal for a 20 MHz LTE signal, is illustrated in Figure 3.7. It shows that the spectrum is segmented into the intended output signal  $f_{Mod} = 20$  MHz centered around  $f_1 = 2.5 GHz$ , resulting in the occupied bandwidth *OB* and the modulator noise covering almost the rest of the spectrum.

However, the majority of the power is concentrated around the harmonics  $f_i$ . This is the reason why the design band *DB* was chosen to cover most of the overall signal power, resulting in a design bandwidth of  $f_{design} = 1000$  MHz. If the signal source's DAC would have a perfectly flat frequency response the excitation spectrum would by cyclic in  $2 \cdot f_0$ . Therefore, also the higher order design bands *DBW<sub>i</sub>* need to be considered. It was found that considering the first two harmonics is sufficient for the design since the gain of the active device is very low beyond this band. Therefore, the the design bands *DBW<sub>i</sub>* have been specified according to  $n_{PA}$ .

Figure 3.7: Normalized power spectral density of the LTE excitation signal.

$$f_{i} = 2.5GH_{Z} \cdot i$$

$$f_{Mod} = 20 \text{ MHz}$$

$$n_{PA} = \{1..N_{PA}\} = \{1,2,3\}$$

$$OB = f_{0} + \left[\frac{-f_{Mod}}{2}, \frac{f_{Mod}}{2}\right]$$

$$f_{design} = 1000 \text{ MHz}$$

$$DBW_{i} = f_{i} + \left[\frac{-f_{design}}{2}, \frac{f_{design}}{2}\right]$$

$$NLBW_{i} = f_{i} + \left[\frac{-f_{BW}}{2}, \frac{f_{BW}}{2}\right] \cdot i$$

$$DB = \bigcup_{i=0}^{N_{PA}} DBW_{i}$$

$$NB = \bigcup_{i=0}^{N_{PA}} DBW_{i} \cap OB$$

The signal components in these bands stem from the amplified excitation as well as from nonlinear signal components produced in the transistor. This distinction marks another important difference to more mainstream SMPA designs, in which case the bands occupied by the nonlinear mixing products require a bandwidth that is proportional to its order as in  $NLBW_i$ . This is depicted in Figure 3.8 where the output signal of the active device as observed through the coupler, is compared to the measured input signal. The design band *DB* consists of all frequencies considered for designing the matching network, while the noise band *NB* is a subsection of it. All these frequency ranges are defined in equation eq. (3.2) and are used to distinguish them for the banded matching network design approach described in this subsection.

By using a load pull setup it is possible to gain many load-pull contours that measure a load pull parameter as function of the realized input- and output-reflectioncoefficients. For a broad band problem also the frequency is a variable, since the contour will change significantly with frequency f. So every load-pull parameter results in a function of form  $LP(\Gamma_{in}, \Gamma_{out}, f)$ .

Figure 3.8: Normalized power spectral density of the PWM-modulated LTE signal at the in- and output of the PA.

$$FG(\Gamma) = |Gain(\Gamma)|$$

$$FPAE(\Gamma) = |PAE(\Gamma)|$$

$$FPD(\Gamma) = -|P_{Bias}(\Gamma)|$$

$$FOUT(\Gamma) = \begin{cases} FOM_{PAE} \cdot cPAE, f \in OB \\ FOM_{PD} \cdot cPD, f \in NB \end{cases}$$

(3.3)

While this is the most general description, it somewhat problematic since it requires many points to be measured in order to analyze a single parameter. Since the data gathering is based on mechanical tuners this translates to long measurement times. However, this can be avoided by first starting with an optimization step. For every considered frequency point, the load-pull setup conducts a joint optimization of the inputand output- load condition for every analyzed system parameter. When the ideal load combination is found, two extensive measurement runs are conducted at the load- and source- side while the respective other is fixed to a specific value. Early in the design this is the before found optimum value, as the design progresses, the most likely value will be used. This allows to analyze the impact of a reflection coefficient deviating from its optimum, however, it requires an optimum to be defined for each parameter. The resulting contours are called load pull contours and Figure 3.9 provides an example. As a result a load pull contour is a simpler function that only depends on one reflection coefficient as in  $LPC(\Gamma_{test}, f)$ . These contours allow to indicate favorable source and load conditions depending on a given application. However, in order to gain a single parameter that can be optimized figures of merit need to be defined. They use a source or load trajectory  $\Gamma(f)$  in order to gauge how well a circuit parameter is optimized for this trajectory. Some examples are denoted in eq. (3.3). Usually harmonic controlled amplifiers rely on two static FOMs for in- and output- to gauge the optimality of a matching network.

Figure 3.9: Measured DC power consumption load pull contour.

For the presented solution banded FOMs are employed at the output to differentiate between the parts of the spectrum that are occupied by the intended output signal present in *OB* and the modulator noise occupying *NB*. Within the signal band the same FOM is used as in many popular class F amplifier designs. It is a FOM that tries to optimize the power added efficiency for all the components in this bandwidth (*FPAE*( $\Gamma$ )). Outside this band and within regions where a significant amount of modulator noise is present (*NB*) a minimum power consumption (*FPD*( $\Gamma$ )) is important for this design. Therefore, this FOM is used in these sections of the spectrum. Figure 3.9 illustrates the results of these load pull measurements related to the power consump-

Figure 3.10: Measured PAE load pull contour at 2.5 GHz.

tion. The location of the optimum with respect to the output power maximum is depicted in Figure 3.10. They are contradictory, however, by using a banded approach as described by  $(FOM_{out put})$  a compromising load trajectory can be found based on this FOM. The coefficients *cPAE* and *cPD* are used to adjust the weight of the FOMs with respect to each other. Deriving a circuit from these results asks for an optimizer based circuit design which is described in section 3.4.

For the PA's input a single FOM is employed that is used throughout the overall design bandwidth *DB*. In this the gain of the transistor is maximized via  $FG(\Gamma)$  in order to have plenty of output signal available.

# **3.4** Circuit Synthesis Based on SRFT

As described in section 3.3, the source- and load-contours for optimum operation of the transistor were determined with the help of load pull measurements. Especially the load-contours are affected by the banded approach since the figure of merit changes frequency dependent from power consumption to PAE.

In a next step, a realizable matching network for the transistor's input and output needs to be found based on these load pull measurements. The so-called Simplified Real Frequency Technique (SRFT) method was used for this task. Because of the problem's broadband nature analytical approaches, based on the classical gain-bandwidth theory, cannot be applied in order to gain a realizable circuit.

The SRFT is a semi-analytical approach which is superior in many ways. It allows to find a lossless circuit that maximizes an arbitrary figure of merit instead of only optimizing power transfer. This method was proposed in [31] and has been refined continuously [32]. It was used in many other works [33] [34], as well as in the works [25] [30] related to the overarching project. A modified version was used in [26] which already employs a banded approach and forms the basis of this section.

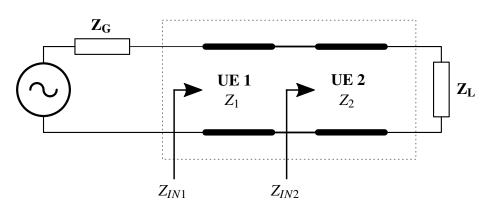

As illustrated in Figure 2.8, matching networks connect a DUT to other circuit sections which realize a certain impedance trajectory. The method's goal is to design two lossless two-ports that match the generator- and the load-side of the network where both can take on complex impedances. Matching is here used in a broader sense since it not necessarily means to optimize solely the power transfer, but to optimize some FOM for this section. Finding a circuit that fulfills this condition is often referred to as a double matching problem, since both sides of the matching networks can take on complex impedances.

The SRFT allows to do so by, firstly, finding an analytic description for all realizable two ports using polynomials. Secondly, it allows to compute S-parameters describing the matching networks from these polynomials. In conjunction with measured S-parameters of source- and load-impedances the reflection coefficients at the transistor's interface can be computed. The figure of merit 3.3 is now used to compute an error function. Thirdly this error function is minimized by a nonlinear optimizer. Since the polynomial description ensures a valid result, the final optimized polynomial also represents a realizable circuit.

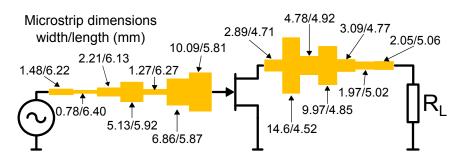

In the next step the optimized polynomial is used to compute circuit parameters. In this case a transmission line implementation was chosen. Characteristic impedances and electrical lengths are used to describe the circuit to be manufactured.

While the SRFT ensures that the results are meaningful in a physical sense they can very well be impossible to manufacture, due to the for example ridiculously small characteristic impedances or so on. Finally, computer aided circuit design and EMsimulations are utilized to design a manufacturable circuit with parameters as close to the theoretical ones as possible. The individual steps of this process are described in the upcoming subsections.

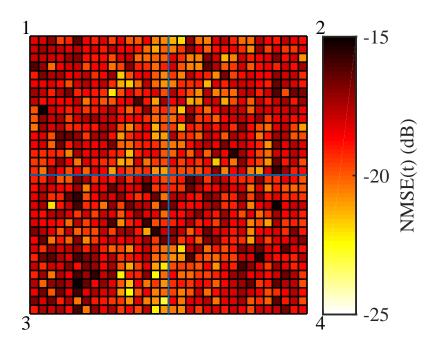

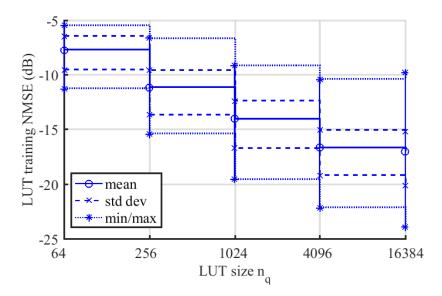

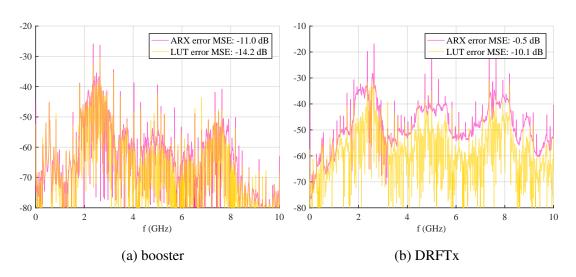

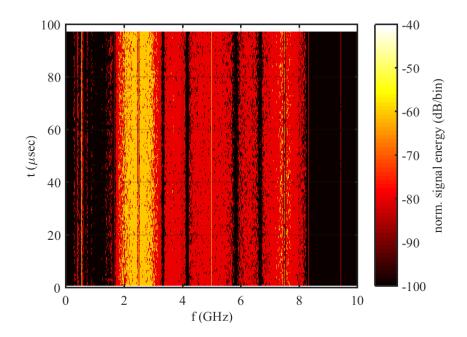

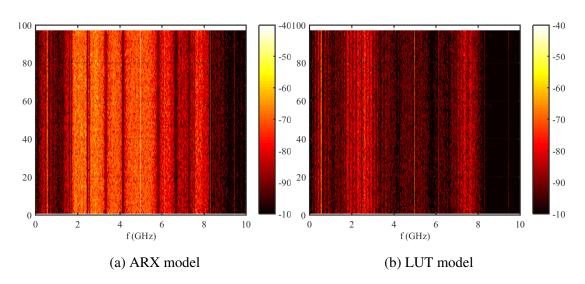

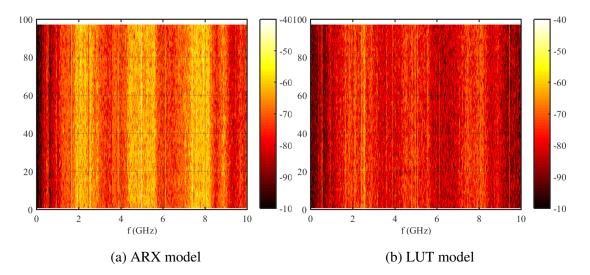

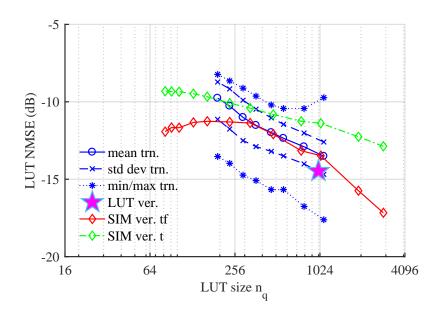

The SRFT algorithm is independent of the chosen type of circuit elements used