Die approbierte Originalversion dieser Diplom-/ Masterarbeit ist in der Hauptbibliothek der Technischen Universität Wien aufgestellt und zugänglich.

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology. http://www.ub.tuwien.ac.at/eng

DIPLOMA THESIS

## Hardware Acceleration of Cryptographic Procedures for Secure Distributed Storage Systems

Submitted at the Faculty of Electrical Engineering and Information Technology, Vienna University of Technology in partial fulfillment of the requirements for the degree of Diplom-Ingenieur (equals Master of Sciences)

under supervision of

Univ.Prof. Dipl.-Ing. Dr.techn.Axel Jantsch Univ.Ass. Dr. Sai Manoj Pudukotai Dinakarrao

Institute of Computertechnik Technology (E384) Vienna University of Technology

by

Jakob Stangl Matr.Nr. 0925320 Schellenseegasse 11/5, 1230 Wien

25.04.2017

#### Abstract

Cloud computing gives new opportunities to many applications. The advantages of reducing the cost and complexity of up-front infrastructure are accompanied with various security issues.

A cloud storage provider has to be trusted to handle ones data confidentially and ensure its availability. In order to guarantee the secrecy and availability of sensitive data, it is unavoidable for the end-user to encrypt and replicate the data in any way. An approach for these issues is to store the data in a virtual cloud formed of multiple cloud providers.

With a scheme called secret sharing a free selectable amount of redundancy is added. The data to be protected is split into multiple pieces and distributed to several servers. To restore the original data a certain amount of arbitrary pieces is required. In this way, the failure of a single server in the cloud does not influence the availability. Moreover, this schemes enables high secrecy as only a certain amount of pieces reveal the original information. Any party holding less pieces are not capable of obtaining any information of the original data.

It is of high computational effort to split the data in such a manner. While various software solutions exist, there are only few investigations in hardware. However, the implantation in dedicated hardware allows the possibility of high performance increase and has the potential to expand its applicability.

This work firstly handles the implementation of an information theoretical secure secret sharing scheme, proposed by Adi Shamir. Subsequently, it discusses and presents the implementation of a more efficient scheme in terms of storage space, the Computational Secret Sharing. All these investigations are targeted for a Field Programmable Gate Array (FPGA). A final implementation of a complete secret sharing system operating in a network environment and the capability of managing, sharing and distributing complete files as well as successfully restoring them completes this work.

#### Kurzfassung

Viele Anwendungen wurden durch das Zusammenschließen von Computern zu einer *Cloud* erst möglich oder bedeutsam verbessert. Allerdings ergeben sich durch die Auslagerung von Daten auch neue Bedenken. Speichert man etwa Daten in der *Cloud*, so muss man dem Anbieter vollkommen vertrauen, die Daten zu schützen, sowie auch ihre Verfügbarkeit sicherzustellen. Letztendlich liegt es jedoch in der Verantwortung des Nutzers vertrauliche Daten entsprechend zu schützen und sich gegen den Ausfall der *Cloud* oder Datenverlust abzusichern. Dies führt unweigerlich zu Verschlüsselung und Replikation.

Eine Lösung dies zu erreichen besteht darin, eine virtuelle *Cloud* aufzubauen, die aus mehreren physischen *Clouds* besteht. Mittels eines Verfahrens namens *SecretSharing* wird zu den Daten eine beliebige Menge an Redundanz hinzugefügt. Dabei werden die Originaldaten in mehrere Teile zerlegt und in der virtuellen *Cloud* auf unterschiedliche Server verteilt. Um die Originaldaten wiederherzustellen, wird eine vordefinierte Anzahl dieser Teile rekombiniert. Dabei ist es gleichwertig, welche dieser Teile für die Rekombination verwendet werden. Dank dieser Methode wird der Ausfall einer definierbaren Anzahl von Servern kompensiert. Zusätzlich wird mit diesem Verfahren Vertraulichkeit sichergestellt. Mit weniger als für die Wiederherstellung benötigten Teile lässt sich keine Information über den Inhalt der Daten ableiten.

Für dieses Konzept existiert eine Vielzahl an Softwarelösungen, jedoch nur eine sehr limitierte Auswahl an Hardwarerealisierungen. Eine eigens dafür konzipierte Hardware in dieser Arbeit bringt erhebliche Durchsatzsteigerungen und erweitert somit den Anwendungsbereich bei gesenkten Kosten.

Zunächst wird in dieser Arbeit ein informations-theoretisch sicheres Verfahren, erstmals vorgestellt von Adi Shamir, in Hardware implementiert. Darauf aufbauend wird das *Computational Secret Sharing*, welches eine bessere Speichereffizienz besitzt, untersucht. Für beide Ansätze werden generische Hardwarearchitekturen für die Realisierung in einem FPGA entworfen. Abschluss dieser Arbeit ist die Implementierung eines kompletten Systems in einer Netzwerkumgebung, die in der Lage ist mehrere Dateien zu verwalten, zu teilen und wiederherzustellen.

#### Danksagung

An erster Stelle möchte ich meinen Eltern Renate und Gerhard Stangl danken, ohne die ich heute diese Arbeit nicht hätte schreiben können. Ich möchte mich bedanken, dass sie mir nicht nur ein sorgenfreies Studieren ermöglicht haben, sondern mich überdies dazu ermutigt haben ein universitäres Studium abzuschließen.

Für die intensive und kompetente Betreuung von Thomas Lorünser von seitens des Austrian Institute of Technology (AIT) möchte ich mich bedanken. Seine fachlichen Anregungen und Analysen waren von großer Hilfe für diese Arbeit.

Für die Betreuung meiner Arbeit seitens der TU Wien, möchte ich mich bei Axel Jantsch bedanken, der es mir ermöglicht hat die Diplomarbeit mit hoher fachlicher Unterstützung in einem angenehmen Umfeld zu schreiben.

Bei Sai Manoj Pudukotai Dinakarrao möchte ich mich ebenfalls für die kompetente und unkomplizierte Betreuung seitens der TU Wien bedanken. Seine flexible und spontane Art waren mir bei vielen Problemen von großer Hilfe.

Mein ganz besonderer Dank in Bezug auf diese Arbeit gilt Jasmin Pajenda. Ohne ihre unermüdliche Bereitschaft neue Ideen zu diskutieren und den langen konstruktiven Gesprächen wäre diese Arbeit nicht in diesem Ausmaß gelungen.

# **Table of Contents**

| 1 | Intr | roduction                                | 1  |

|---|------|------------------------------------------|----|

|   | 1.1  | Secret Sharing In The Cloud              | 1  |

|   | 1.2  | Motivation For A Hardware Implementation | 2  |

|   | 1.3  | Objectives                               | 3  |

|   | 1.4  | About This Work                          | 3  |

|   | 1.5  | Organisation Of Thesis                   | 3  |

| 2 | Pre  | liminaries And Related Work              | 4  |

|   | 2.1  | Finite Fields                            | 4  |

|   | 2.2  | Secret Sharing Principles                | 5  |

|   | 2.3  | Shamirs Secret Sharing                   | 5  |

|   | 2.4  | Computational Secret Sharing             | 7  |

|   | 2.5  | Robust And Verifiable Secret Sharing     | 7  |

|   | 2.6  | Hardware Implementations                 | 9  |

|   | 2.7  | Software implementations                 | 9  |

| 3 | Sha  | mir's Secret Sharing                     | 11 |

|   | 3.1  | Introduction                             | 11 |

|   | 3.2  | Share Generation                         | 11 |

|   | 3.3  | Secret Reconstruction                    | 18 |

|   | 3.4  | Evaluation                               | 20 |

| 4 | Adv  | vanced Multipliers                       | 25 |

|   | 4.1  | Introduction                             | 25 |

|   | 4.2  | Applying Karatsuba's Algorithm           | 25 |

|   | 4.3  | A Better Overall Resource Utilization    | 28 |

|   | 4.4  | Conclusion                               | 32 |

| 5 | Cor  | nputational Secret Sharing               | 34 |

|   | 5.1  | Introduction                             | 34 |

|   | 5.2  | Advanced Encryption Standard             | 35 |

|   | 5.3  | Share Generation                         | 39 |

|   | 5.4  | Secret Reconstruction                    | 39 |

|   | 5.5  | A Full Computational Secret Sharing Core | 41 |

|   | 5.6  | Evaluation                               | 43 |

| 6  | A F   | ull Computational Secret Sharing System   | <b>47</b> |

|----|-------|-------------------------------------------|-----------|

|    | 6.1   | Introduction                              | 47        |

|    | 6.2   | True Random Number Generator              | 48        |

|    | 6.3   | Protocol                                  | 50        |

|    | 6.4   | External Communication                    | 51        |

|    | 6.5   | Computational Secret Sharing Core Wrapper | 52        |

|    | 6.6   | Client And Server                         | 53        |

|    | 6.7   | Full Setup And Evaluation                 | 54        |

| 7  | Con   | iclusion                                  | 57        |

|    | 7.1   | Summary And Discussion                    | 57        |

|    | 7.2   | Applications                              | 58        |

|    | 7.3   | Further Work                              | 58        |

| A  | ppen  | dix                                       | 59        |

| Li | terat | ure                                       | 86        |

# Abbreviations

| ARP                 | Address Resolution Protocol                    |

|---------------------|------------------------------------------------|

| AES                 | Advanced Encryption Standard                   |

| ADC                 | Analog to Digital Converter                    |

| AIT                 | Austrian Institute of Technology               |

| AXI                 | Advanced Expandable Interface                  |

| BRAM                | Block Random Access Memory                     |

| CBC                 | Cipher Block Chaining                          |

| CFB                 | Cipher Feedback                                |

| clk                 | Clock                                          |

| CSP                 | Cloud Service Provider                         |

| $\mathbf{CSS}$      | Computational Secret Sharing                   |

| CTR                 | Counter                                        |

| CRC                 | Cyclic Redundancy Check                        |

| D-FF                | D-Flip-Flop                                    |

| DSP                 | Digital Signal Processor                       |

| ENC                 | Encryption Function                            |

| ECB                 | Electronic Code Block                          |

| ESS                 | Extended (Shamir) Secret Sharing               |

| $\mathbf{FFT}$      | Fast Fourier Transformation                    |

| FPGA                | Field Programmable Gate Array                  |

| FSM                 | Finite State Machine                           |

| FIFO                | First In- First Out                            |

| $\operatorname{GF}$ | Galois Field                                   |

| GUI                 | Graphical User Interface                       |

| RGMII               | Gigabit Media Independent Interface            |

| GPU                 | Graphics Processing Unit                       |

| HW                  | Hardware                                       |

| $IP_1$              | Intellectual Property                          |

| $IP_2$              | Internet Protocol                              |

| ISO                 | International Organisation for Standardisation |

| LFSR                | Linear Feedback Shift Register                 |

| LUT                 | Look-Up-Table                                  |

| MAC                 | Media Access                                   |

| NIST                | National Institute of Standards and Technology |

| NSA                 | National Security Agency                       |

| OLED                | Organic Light-Emitting Diode                   |

| OFB                 | Output Feedback                                |

| PEU                 | Polynomial Evaluation Unit                     |

| PLL                 | Phase Locked Loop                              |

| PL                  | Programmable Logic                             |

|                     | 5 0                                            |

| $\mathbf{PS}$        | Processing System                                                |

|----------------------|------------------------------------------------------------------|

| PEU                  | Polynomial Evaluation Unit                                       |

| RAID                 | Redundant Array of Independent Disk                              |

| RO                   | Ring Oscillator                                                  |

| SRU                  | Secret Reconstruction Unit                                       |

| SHA                  | Secure Hash Algorithm                                            |

| SLA                  | Service-Level Agreement                                          |

| SSS                  | Shamir Secret Sharing                                            |

| $\operatorname{SGU}$ | Share Generation Unit                                            |

| SW                   | Software                                                         |

| TDP                  | Thermal Design Power                                             |

| TRNG                 | True Random Number Generator                                     |

| VHDL                 | Very High Speed Integrated Circuit Hardware Description Language |

| WPA2                 | Wi-Fi Protected Access 2                                         |

|                      |                                                                  |

## 1 Introduction

This work starts with an outline of computational clouds and the application fields within the cloud setup. While various software (SW) solutions exist, a special motivation for a hardware (HW) acceleration is given. The general conditions for implementations is listed as well as the outline and notations of this work at the end of the chapter.

## 1.1 Secret Sharing In The Cloud

In the field of information technology the purpose of a cloud is outsourcing resources and reducing the complexity and cost of up-front infrastructure, rapidly realizable with minimal management effort. While cloud computing has a wide field of application, the focus of this work is on data storage. However, handing the data to a Cloud Service Provider (CSP) of a cloud leads to various issues. The costumer has to trust the service provider to handle the data confidentially. This is of special interest for companies or individuals, if the data contains sensitive information. Moreover, the data should be available at any time when requested.

(A a minimum uptime for cloud services is specified in the service-level agreement (SLA), which is ...) In the service-level agreement (SLA), a minimum uptime is specified for cloud services. For example the popular Amazon Cloud Service the SLA value is 99.9% uptime per month [?]. Anyway, as shown by recent incidents in [15] a downtime greater than the specified value is still possible, but only allows to receive redress. It is still in the responsibility of the user to ensure compliance of the final security and confidentiality [8].

Various different approaches to overcome those problems include replicating the data and encryption. Another attempt is the cloud-of-cloud approach. In this scenario a virtual cloud consisting of more than one physical cloud provider is in charge and realized by a process called secret sharing. Various systems exist and some of them are summarized in [67].

In the secret sharing approach, a file is split into pieces (shares) and stored on multiple servers within different clouds. In order to obtain the original file, an arbitrary subset of these shares are required. In this way, the reliability of a single cloud or server is avoided, if sufficient shares are generated. For example, if 10 servers are in use with an uptime of 99.9 % with 4 required shares, the failure probability is brought from  $10^{-3}$  to  $1.1 \times 10^{-16}$  [49].

Moreover, it is of special advantage, that a certain amount of shares, k, is required to obtain the original file. With less shares than this boundary, no information is obtained and of no use for a malicious cloud provider, or attacker. It ensures confidentiality if less than k share holders collaborate.

Compared to the straight forward approach of encryption and duplication of files, the scheme of this work allows two advantages. Firstly, no key management is required as no key exists in the scheme and secondly, the data overhead is adjustable. Due to possible malicious attacks, there are still credentials required to authenticate the shares and guarantee a consistent and secure secretfile. However, such an authentication mechanism is required anyway in an encrypted scheme.

## **1.2** Motivation For A Hardware Implementation

To realize the concept of secret sharing a mathematical algorithm is applied subsequently. Performing the algorithm on a file, it is first split into blocks of a certain bit-width. The block can be seen as numbers on which the algorithm is applied. On one hand, blocks of higher bitwidths lead to a mathematical higher complexity due to multiplications in the algorithm. On the other hand, a higher bit-width comes with benefits. Even in a computational secure scheme, it is possible to guess a right secret, but every possibility is same likely. Using higher bit-widths makes it significantly more unlikely to guess a right word. Moreover, the performance of higher protocols in a cloud-of-cloud approach is increased. The protocol [21] for auditing [9] and [39], a process to verify the consistency of shares without retrieving the original file benefits of bigger blocks. Furthermore, the scheme of secret sharing is homomorph. Consider two subsecrets and each split into multiple shares. Multiplying shares from both subsecrets lead to a new topsecret. This topsecret is the same as both subsecrets multiplied. In this case, a topsecret is generated, without revealing any subsecrets. However, this homomorphic attribute is only applicable within a block.

Because of the performance penalties in the storage domain software implementations usually perform the calculations on blocks of one byte, as the calculations are able to be performed efficiently in look-up-tables. For processing 16 bits at once, other look-up-table based approaches exit, but the calculation becomes significantly slower for higher bit-widths and inefficient in terms of possible throughput. Therefore current software implementations of secret sharing, such as proposed in Archistar [49] work with a block size of 8 bit and can achieve a share generation rate of about 32 Mbit/s. Another implementation of Nubisave in [68] reach a throughput of about 5 Mbit/s in a real world environment. In chapter 2.7 more software implementations of secret sharing algorithms are discussed.

For the improvement of the performances in terms of their throughput and bit-widths, a hardware implementation is of interest. Especially when we want to apply the technology within a larger data centre which also requires low latency. According to the block size, the calculations are performed on a hardware designed for a certain bit-width.

To the best of my knowledge, only two hardware implementations of secret sharing are published, [77] and [50]. Gaining a high throughput in both works, the sharing and reconstruction process as well as the evaluation of the architecture for different bit-widths was not the intention in these works.

Therefore, this work discusses the feasibility of a hardware implementation and evaluates the performances of different bit-widths. It is focused on different secret sharing algorithms and word widths, specifically optimized for storage configuration motivated by the use cases covered by the ARCHISTAR system [49].

## 1.3 Objectives

The aim of this thesis is to evaluate the feasibility to realize a secret sharing mechanism in a FPGA for different bit-widths specifically targeted for efficient distributed storage solutions. Hardware units are designed and bit-widths are discussed, which are generically selectable. In the following, the bit-widths 8, 16, 32, 64 and 128 were investigated and implications for practical realizations have been elaborated.

The work firstly deals with a secret sharing scheme of information theoretical secrecy, the Shamir Secret Sharing (SSS) scheme [65]. It forms the foundation for a more complex secret sharing scheme with better storage efficiency, the Computational Secret Sharing (CSS) scheme [46], investigated subsequently.

After evaluation of the performance in different bit-widths, a prototype is built. It is capable of sharing and restoring files with a high throughput in a real network environment.

## 1.4 About This Work

#### **Evaluation Platform**

The Zedboard [82] was selected as FPGA platform. The hardware description code was developed in Very High Speed Integrated Circuit Hardware Description Language (VHDL). The synthesis and implementations of this work were performed with Vivado<sup>®</sup> 2015.3 [79] and targeted for the Zedboard. The Zedboard consists of a Xilinx Zynq-7000 AP SoC XC7Z020-CLG484 [80] FPGA. It is partitioned into a Programmable System (PS) and a Programmable Logic (PL), connected via an Advanced Expandable Interface (AXI). The PS contains a dual-core ARM Cortex<sup>TM</sup>-A9 processor. The PL consists of 6-input look-up-tables (LUTs), D-Flip-Flops (D-FFs), 36 kbit Block Random Access Memories (BRAMs) and Digital Signal Processors (DSPs) as well as several interfaces.

#### Notations

In figures presenting architectures of hardware designs, bold lines symbolize buses (usually data paths), while thin lines represent single signals (usually control signals). The abbreviation LUT refers to the logic element within a FPGA, while written out refers to a look-up-table in general terms.

### **1.5** Organisation Of Thesis

The chapter 2 describes fundamental basics, important for the understanding of this work as well as related work. Then, the implementation of Shamir's Secret Sharing scheme, an information theoretical secure secret sharing scheme is investigated in 3. The next chapter 4 contains strategies for more efficient implementations of a polynomial multiplier. In chapter 5 the development from the implementation of Shamir's scheme to a Computational Secret Sharing scheme is presented. A complete prototype capable of sharing files in a network environment is presented in chapter 6. Finally, a conclusion and outlook of this work is in 7. All chapters with implementations and findings include a dedicated evaluation and summary subsection.

## 2 Preliminaries And Related Work

In this chapter an introduction of the main elements and important topics, such as the detailed description of Shamir's Scheme and finite fields, is given. Starting with finite fields, new concepts in each section are introduced in order to get a complete understanding of a robust computational secret sharing scheme. The following sections provide an overview of related work, which will be the content of the rest of this chapter.

## 2.1 Finite Fields

In a secret sharing algorithm a lot of additions and multiplications have to be performed sequentially on an initial value. If the operands are represented by natural numbers, it leads to a rapid increase of the original value. A large number of bits would be needed to represent the highest possible value in a digital system to avoid overflows. However, most of the bits are often not used which is very inefficient. For an efficient use of these bits all calculations are performed in finite fields, or more specific, in binary extension fields.

For detailed information of finite fields and related mathematical basics it is referred to [48] while a brief introduction is given in the following.

Finite fields, denoted as  $\mathbb{F}_p$ , consist of a finite number p of elements and satisfy all rules of fields. They are often denoted as a Galois field, GF(p), in honour of Évariste Galois. The simplest construction of finite fields uses prime numbers for p. Operations of arithmetic, such as addition and multiplication of any operand within this field, lead to a result in the same field. This is necessary to satisfy the axioms of fields and is only possible if p is a prime. To obtain such a result, a reduction step (modulo p) is performed after each operation. While the numbers don't grow larger, each operation can still be unambiguously reversed. In order to gain a better understanding a simple example for  $\mathbb{F}_7$  is given in (2.1).

$$3 + 5 = 8 \mod 7 = 1$$

1 - 5 = -4 mod 7 = 3 (2.1)

Extension fields, denoted as  $GF(p^n)$ , are used for constructing fields with a number of elements different to prime numbers. These fields consist of  $p^n$  elements, where p stands for a prime and n any natural number. In order to construct such a field, the elements are represented by polynomials with a degree less than n and coefficients are described by elements of the field  $\mathbb{F}_p$ . Similar to the first example with finite fields of p elements, a reduction is performed after each operation to stay in the field. Instead of the prime number an irreducible polynomial is used, which is chosen arbitrary but unique for a specific binary extension field. The reduced polynomial is the remainder of a division by the irreducible polynomial. A simple example of a multiplication in  $GF(2^2)$  with the irreducible polynomial  $x^2 + x$  is given in 2.2.

$$(x+1)(x+0) = (x^2+x) \mod (x^2+x+1) = 1$$

(2.2)

If p is chosen as 2, the coefficients can only be 0 or 1. Such fields are named binary extension fields and often denoted as  $GF(2^n)$ , where n signifies the bit-widths. They can be applied easily and efficiently in digital systems.

### 2.2 Secret Sharing Principles

Secret sharing is an algorithm for distributing one secret into several share parts among different parties. The secret is divided into shares, where a specific number of shares is needed to restore the secret. In a n/k threshold scheme n shares are produced, while a minimum of freely chosen k shares are needed to reconstruct the secret. Any number of shares less than k does not reveal any information about the secret.

An algorithm to meet this criteria was first independently introduced by Adi Shamir [65] and George Blakley [10]. Shamir's Secret Sharing algorithm is based on two-dimensional polynomials, while Blakley's algorithm works with planes and their intersection in a n-dimensional space. Shamir's algorithm is more efficient in a storage setting, because it produces smaller overheads. A share of Blakley's algorithm is the size of n times the secret, whereas one share in Shamir's model has exactly the size of the secret. Shamir size is optimal for information theoretical security, however, for practical reasons it can be more efficient with slightly weaker security assumptions. Therefore the basic algorithm was adapted to a more advanced secret sharing mechanism to meet more requirements such as smaller overheads, robustness and verification.

## 2.3 Shamirs Secret Sharing

Shamir's Secret Sharing is based on the evaluation and interpolation of polynomials. For a n/k threshold scheme a polynomial with a degree of k-1 is used (2.3). The first coefficient m at  $x^0$  represents the secret, while all other coefficients,  $c_x...c_1$ , are filled with random numbers. To construct a share the polynomial is evaluated at a point x, where x can be chosen arbitraryily except  $x \neq 0$ , which is the secret itself.

$$y = c_{k-1} \times x^{k-1} + \dots + c_2 \times x^2 + c_1 \times x^1 + c_0$$

where:  $y = \text{share}$

$c_0 = \text{secret}$

$c_1 \dots c_{k-1} = \text{random values}$  (2.3)

A polynomial interpolation is performed to reconstruct the secret. Any share represents a point of the polynomial, where the x-position is publicly known and the y-position is the share itself. The y-value at x = 0, or equally the coefficient at  $x^0$  from the interpolated polynomial, is the secret. For an exact interpolation of a polynomial with a degree of k-1, a minimum of k points is required. If only k-1 points are available it is obvious, that the polynomial can't be reconstructed as the secret could still take any value depending on the last share-point.

In this scheme the size of the shares are exactly the size of the secret. Therefore an overhead of n-times the secret is produced. An advantage of this scheme is its information-theoretic secrecy, which means it can not be broken with any computing effort.

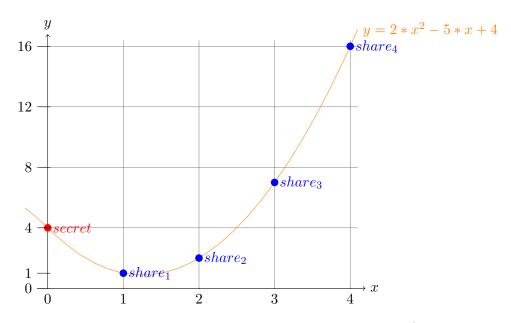

For a deeper understanding of Shamir's Secret Sharing an illustration is given in figure 2.1.

We choose a polynomial with a degree of  $2 - c_2 * x^2 + c_1 * x^1 + c_0$ .  $c_0$  represents the secret, which we assume is 4. The coefficients  $c_1$  and  $c_2$  are randomly chosen with 2 and -5. Next, we calculate 4 shares  $s_1...s_4$  on the points 1...4, which gives us  $s_1 = 1, s_2 = 2, s_3 = 7, s_4 = 16$ .

We select the shares  $s_1, s_2, s_4$  and use the Lagrange Interpolation at the point x = 0 (2.4). There are many other interpolation schemes which could be used equally.

$$\sum_{i=0}^{n} \left( f(i) * \prod_{j=0, j \neq i}^{n} \frac{0 - x_j}{x_i - x_j} \right)$$

(2.4)

The Lagrange Interpolation leads to the following equation (2.5) with the result of the original secret we selected.

$$y = \left(1 * \frac{-2}{1-2} * \frac{-4}{1-4}\right) + \left(2 * \frac{-1}{2-1} * \frac{-4}{2-4}\right) + \left(16 * \frac{-1}{4-1} * \frac{-2}{4-2}\right) = 4$$

(2.5)

Figure 2.1: An illustration of a polynomial for Shamir's Secret Sharing of a 4/3 threshold scheme, using 4 as the secret and 1, 2, 7, 16 as random coefficients.

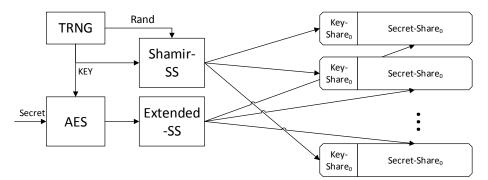

## 2.4 Computational Secret Sharing

The information-theoretic secrecy comes with the cost of shares with sizes of the secret itself. Although in practical implementations it is often sufficient if the secret is computational secure. The secret can not be revealed with a limited computational effort. Hugo Krawczyk published such a scheme called Computational Secret Sharing [46].

Computational Secret Sharing is described with an abstract secure secret sharing scheme. For a better understanding a brief explanation is given based on Shamir's scheme. Instead of random numbers it uses secrets in higher coefficients of the polynomial and a secure encryption function.

First the secret is encrypted with a secure encryption function (ENC) using a key A. The shares  $s_1, ..., s_i$  are generated by evaluating a polynomial at any point  $x_i \neq 0$  and each coefficient is part of the secret. This is the fundamental difference to Shamirs's scheme, where all coefficients except  $c_0$  are filled with random numbers. The key is then shared with a perfect secure secret sharing scheme into key-shares  $K_i$ . Each pair, consisting of a secret-share  $s_i$  and a key-share  $K_i$ , is distributed to one shareholder.

In the process of reconstructing the secret, first the key is restored followed by the encrypted secret. In comparison to Shamir's scheme all coefficients of the polynomial are needed to be restored. The result is then decrypted by using the restored key and the reversed encryption function  $ENC^{-1}$  to reveal the original secret.

## 2.5 Robust And Verifiable Secret Sharing

Computational Secret Sharing makes the scheme efficient and computational secure, but the scheme is still vulnerable for attacks. If a shareholder distributes a modified share, it is not feasible for the system to detect the faulty share and a wrong secret would be the result. The error can not be detected nor can the faulty share be identified.

#### **Robust Secret Sharing**

A secret sharing system is called robust, if such a malicious share is detected and the original secret can still be recovered. To be more specific, it is  $(t, \delta)$ -robust, where t is the maximal number of corrupted shares.

Shamir's scheme is robust for the case of t < n/3, t < k and if all shares are available. In this case all possible combinations of shares could be reconstructed and a majority vote would show the correct secret. However, this scheme works to an upper bound of n/3 and is not efficient in term of computational effort, because a lot of reconstructions would be needed.

R.J McEliece and D.V. Sarwate first published a solution for this problem [53] by using error correcting codes. This scheme is also bounded by t < n/3. Another solution was presented by Tompa and Woll [70], where they use a much larger space than the secret itself. Therefore the probability for a recovered secret to be outside the original possible space is high, if at least one of its shares were corrupted. However, there is still a probability greater zero that the fault might not be detected and the scheme is inefficient in terms of space usage.

Rabin and Ben-Or used message authentication codes [57]. Their scheme is often referred to as information checking. Every share  $s_i$  gets extended by an authentication tag  $\tau_{i,j}$  for every shareholder  $P_j$  and the key is then send to the corresponding  $P_j$ . At the secret reconstruction it is checked if the share is accepted my sufficient many authentication tags.

In [56] Rabin introduced a scheme based on digital signatures. This was extended by H. Krawczyk in [46] to overcome the problem of key-management and increase the space efficiency. It is based on distributed fingerprints [45] and published by Krawczyk. The fingerprints are generated with hash-functions and divided into shares, for example with schemes described above. These shares are now distributed to the shareholders. Using hashes as here is only suitable for computational secret sharing, because the hashes leak information. Contrary, the information checking above is information theoretical secure. In the following the share construction applying distributed fingerprints is outlined.

- 1. Calculate n shares  $s_i$  out of the secret

- 2. Calculate fingerprint of each share  $f_i$  with a Hash function

- 3. Calculate shares of all fingerprints  $s_{fj}$

- 4. Every shareholder gets one share of the secret  $s_i$  and one share from each fingerprint  $s_{fj}$  $(s_i + s_{f0} + ... + s_{fj})$

#### Verifiable Secret Sharing

In the scenarios of robust secret sharing we assume that the dealer, who distributes the shares to the shareholders, is honest. If the dealer is corrupt he can distribute modified shares, the restored secret would depend on the shareholders selected for reconstruction. A scheme to detect such a behavior is called Verifiable Secret Sharing.

The first scheme to fulfil this requirement was published by Chor et. al [14]. There are a couple more solutions which are working for a limited amount of corrupted nodes (e.g. t < n/3) and unconditionally private, e.g. [34], [35] or with the assumption of a limited computational power of the attacker. Such computational secure schemes schemes can work with a higher boundary of corrupted nodes.

#### Auditing

The process where shares are verified if they are still valid is called Auditing. It is of benefit if this can be done without downloading all information and without reconstructing the secret itself. This gives convenience and the possibility to outsource this task to a third party which may be untrusted. Such schemes for the proof of retrieve-ability have been first introduced by Ateniese et al. [9] and Jules and Kalinski [39].

In the meantime a lot of schemes for single server setups e.g. [64] [63] [12] as well as for cloud of cloud setups, e.g. [21], have been proposed.

However, specifically for secret shared data a new protocol has been proposed recently [21] which leverages the redundancy in systems with k < n and can be very efficiently applied to large sets of stored data, e.g., they introduce almost no overhead for practical configurations.

## 2.6 Hardware Implementations

There are only few hardware implementations of secret sharing algorithms known from the literature and no extensive treatment of such has been done so far. The focus in these works is different from the one in this thesis and to the best of knowledge there is no speed optimized FPGA implementation of the full Computational Secret Sharing scheme. Moreover, no work deals with the evaluation of different bit-widths of the secret to be processed at once.

In [77] secret sharing is used in a network monitoring application. The monitored data is encrypted and the key is shared using Shamir's algorithm. Only if enough evidence is collected the specific key is available to a monitoring entity. Therefore the encryption and share generation must be able to work for Gigabit-networks. To meet this criteria a dedicated hardware implementation in a FPGA was developed. Because the share generation is time critical, only the implementation of this part is described, while improvements were given also on the reconstruction algorithm.

The key is derived using an Advanced Encryption Standard (AES) function, a master key and the packet flow identifier. This key is used for the coefficient  $c_0$  in the Shamir polynomial which is to be shared. All other coefficients in the Shamir polynomial are also generated over the same AES method. The generated key is then used to encrypt the payload of the package with an other AES unit, while the coefficients are used in a Shamir core. Beside the coefficients, the core also gets a x-value as input, which is supplied by a True Random Number Generator (TRNG).

For the evaluation of the Shamir polynomial, the Horner-Scheme is applied. This gives the possibility to break m - 1 squarings and multiplications down to m - 1 multiplications, where m - 1 is the degree of the polynomial. These multiplications are then processed sequentially using the same multiplier. After each multiplication an addition and a reduction step follows. The reduction step is necessary because the algorithm works in a binary extension field. Since a fixed irreducible polynomial was used, the reduction can be done in one step with static XOR-connection. The x-coordinate was restricted to a 32 bit value in order to reduce the size of the multiplier. A 191 × 16 bit multiplier was used, which processes the 191 × 32 bit multiplication in two cycles.

The work was implemented on a Network FPGA card using a Virtex-II Pro 50 FPGA. The isolated examination of the share generation reveals a throughput of 2359Mbit/s with the usage of 1633 slices in this design. This are roughly 3266 4-Input look-up-tables. The full keyshare units reach a throughput of 343 Mbit/s with 3687 slices and 18 instances of BRAMs.

Another implementation from [50] focuses on secure secret sharing. In comparison to the implementation above, it's target architecture are ASICs and therefore it was synthesized with Cadence Encounter RTL Compiler with the Nangate 45nm Opencell library. While the Secret Sharing is an effective way to divide a secret, it is vulnerable to attackers and cheaters as mentioned in section 2.5. In their work they apply robust codes and algebraic manipulation detection to resist strong cheating attacks. Besides the size of the implementation the results are focusing on the efficiency of cheating detection and correction and the causing size-overhead.

## 2.7 Software implementations

There are various software implementations on secret sharing. The crucial parts of software implementation are the time-consuming polynomial multiplications limiting the performance.

Multiplications of small word-widths can be processed efficiently with look-up-tables, but the sizes growth exponentially with the used Galois field and respectively the bit-widths. For example, an  $8 \times 8$  bit multiplication for a GF(2<sup>8</sup>) would require  $2^{8+8}/2 = 32768$  entries of 1 Byte. The size of the look-up-table would be about 32kByte and easily realizable in a common computer system. However, a look-up-table in GF(2<sup>16</sup>) would need 4.3TB which is currently not feasible in an efficient manner.

The implementation of  $GF(2^{16})$  can be efficiently done with logarithms and logarithm look-uptables. Therefore the problem is transformed according to equation (2.6), where a and b are the factors and c the result of the multiplication.

$$a * b = c = \log^{-1}(\log(a * b)) = \log^{-1}(\log(a) + \log(b))$$

(2.6)

The logarithm and inverse logarithm can be stored in a look-up-table with  $2^{16}$  entries and only the addition has to be performed.

However, after a certain size of the Galois field the method can not be applied anymore and the plain multiplication has to be performed by shift, AND and XOR operations.

In [42] a collection of libraries supporting secret sharing where gathered. The GFShare library [24] operates in a  $GF(2^8)$  field and was analyzed in detail on an Intel i5-2500K, 3.3 GHz, 8 Gbit RAM, computer system. The achieved throughput for sharing large files for an applied 5/3 threshold scheme was 7.4 Mbit/s. This value is relatively small compared to Gigabit networks and small extension fields.

In [7] secret sharing schemes were analyzed in terms of their performance. The focus of their work is the comparison of different schemes according to the threshold parameters n and k. There was no information about the used specific computer system. However, with Shamir's Secret Sharing scheme a throughput of about 9 Mbit/s could be achieved for generating 10 shares. The Computational Secret Sharing achieved a throughput of about 18 Mbit/s for the same amount of shares.

To increase the throughput, efforts were made to use the Graphics Processing Unit (GPU) for better performance. In [13] it was shown that the benefit of a GPU increases with higher thresholds. A threshold of 4 achieves a throughput of 48 Mbit/s for the calculation of one share. Another implementation of secret sharing based on cellular automata on a GPU [38] reveals a speed of 40-160 Mbit/s in a 5/5 threshold scheme.

## 3 Shamir's Secret Sharing

In this section the implementation of Shamir's Secret Sharing scheme in a FPGA is presented. Its resource utilization is discussed as its performance is evaluated against a software implementation as well.

## **3.1** Introduction

The concept of Shamir's Secret Sharing scheme was introduced in chapter 2.3. The aim of this chapter was to find an efficient FPGA implementation of Shamir's scheme in terms of throughput.

In the use-case of this work the secrets to be shared are files. In order to apply Shamir's algorithm, first the secret has to be divided into words of a certain bit-width depending on the selected binary extension field. The binary extension field is generic and can be freely selected from  $GF(2^n), n \in \{8, 16, 32, 64, 128\}$  to compare their efficiency.

The tasks are divided into the share generation, the share reconstruction and finally the creation of a whole system which manages the dataflows. Different implementation strategies and optimization methods are presented and evaluated as is the efficiency of the algorithm, applied in different Galois fields. The results are fully parametrizable cores for the parameters (n, k) of a threshold secret sharing scheme and the bit-widths of secret-words.

## 3.2 Share Generation

The generation of a share according to Shamir's scheme requires the definition of an unique Shamir polynomial for each secret (-word) and the evaluation at a specific point x with the condition  $x \neq 0$ . The information required to build the Shamir polynomial includes the secret itself, the x-point and various random data for the coefficients  $c^n, n > 0$ .

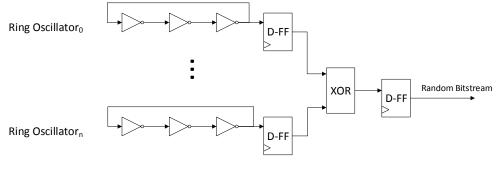

While the randomness of the coefficients is of crucial importance to the secrecy of the scheme, the generation of random numbers is not covered in this chapter. Moreover, they are considered as given from an interface from an outer party. However, it is theoretical possible to include the random number generation within the FPGA even if it contradicts the FPGA's purpose, as it should be a fully determined system. Various works have identified sources of randomness on a FPGA and showed the possibility to build a TRNG within it, e.g. [51], [72], [66], [32]. In chapter 6.2 the generation of random numbers on a FPGA will be discussed.

The evaluation of a polynomial with a degree of n in a straight forward approach (3.1), processing the coefficients in an ascending manner, consists of  $\sum_{i=0}^{n} (i)$  multiplications and n additions. The usage of the Horner scheme, where the coefficients are processed in an opposite way from  $c_n$  to  $c_0$ , allows a significant reduction to n multiplications and n additions. It is illustrated in equation (3.2). Additionally, it allows efficient implementations in hardware.

$$y = c_0 + c_1 \times x + c_2 \times x^2 + \dots + c_{n-1} \times x^{(n-1)} + c_n \times x^n$$

(3.1)

$$y = (((c_n \times x + c_{n-1}) \times x + \dots + c_2) \times x + c_1) \times x + c_0$$

(3.2)

If the result of an operation exceed the bit-widths of its field, a reduction is required. Therefore three different operation types can be identified for the computation of the equation (3.2). They consist of an addition, a multiplication and a reduction.

#### Addition

The addition in a binary extension field is implemented efficiently with little effort. Due to the fact that only two symbols are used for one digit in the polynomial, no carry bits are needed. The truth table for a bitwise addition is shown in table 3.1b and is the exact equivalent to a XOR-operation. The implementation on the FPGA could be realized with linear complexity in dependence of the bit-width of the operands.

**Table 3.1:** Truth table for bitwise addition and multiplication in  $GF(2^n)$ .

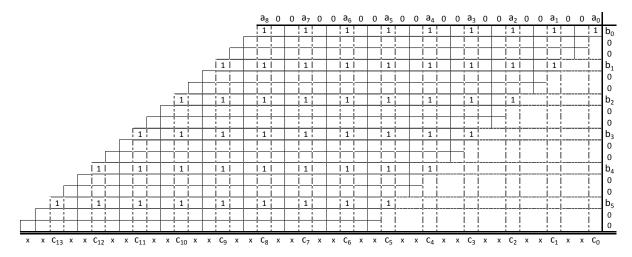

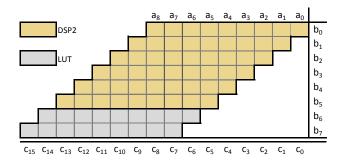

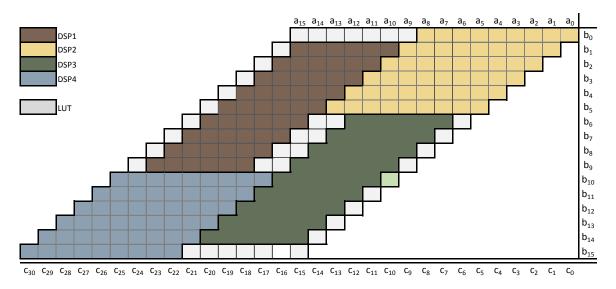

#### Multiplication

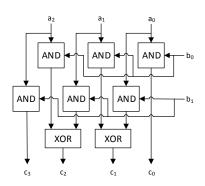

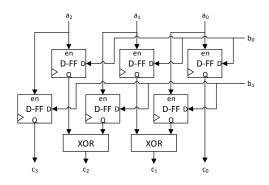

FPGAs usually contain multiple DSPs to perform arithmetic operations. Because the multiplication in a binary extension field is different to an arithmetic operation, the DSPs cannot be used and specially designed  $GF(2^n)$ -multipliers are implemented with LUTs. In finite field arithmetic a multiplication consists of shift operations and additions. The difference to an arithmetic multiplier lies in the additions and the fact that there are no carry bits. The truth table of a bitwise multiplication in a binary extension field in shown in table 3.1a and is identical to an AND-operation.

The nature of the multiplication gives the possibility of implementing it sequentially by shifting, bit-wise multiplication and adding all sub-results together, or executing the whole functionality in parallel. The focus of this work is on the parallel implementation in order to gain a higher throughput and a more efficient use of LUTs within the FPGA. The resulting structure for a  $3 \times 2$  polynomial multiplier is shown in figure 3.1, where the bitwise multiplication is performed with an AND-operation and the addition with a XOR-operation.

Figure 3.1: Parallel  $2 \times 3$  bit polynomial multiplier architecture, build with logic gates.

The size of the multiplier increases with the square of the input size, assuming both inputs with identical widths. It is illustrated in figure 3.1. The growth in size strongly affects the processing of wider words, such as 128 bit. Furthermore, due to the longer paths in parallel architectures the minimal possible clock (clk) period increases. In table 3.2 the multiplier sizes after synthesis and implementation and the reachable minimum clock periods are summarized for the investigated bit-widths.

| bit-widths       | LUT       | LUT                             | minimal         |

|------------------|-----------|---------------------------------|-----------------|

| of multiplicands | synthesis | $\operatorname{implementation}$ | clk period [ns] |

| 8                | 29        | 33                              | 2.2             |

| 16               | 118       | 133                             | 2.7             |

| 32               | 450       | 483                             | 3.5             |

| 64               | 1729      | 1747                            | 4.6             |

| 128              | 7175      | 7195                            | 5.6             |

Table 3.2: Size of a  $GF(2^n)$ -multiplier in dependency of the bit-widths from the inputs, measured in 6-input LUT.

By limiting the possible x-values to a certain bit-width a decrease in size can be achieved. This method was already used before in [77]. It has no impact on the secrecy of the scheme, but it restricts the amount of possible generated shares since every share needs a different x-value to be unique. In table 3.3 the resulting size after synthesis of an asymmetric multiplier is shown.

As shown in table 3.3 the restriction of the x-values comes with a high reduction of LUTs. Limiting the possible x-values to results of the power of two,  $x := \{2^n\}, n < bit - width$ , an even higher decrease of LUTs could be gained. It would reduce the multiplication effort to the minimum, as it would result in processing only shift operations, which could be realized without any logic and only wiring. The main disadvantage is the relatively small set of possible x-values (8 in GF(2<sup>8</sup>), 128 in GF(2<sup>128</sup>)) resulting in a small amount of different generated shares.

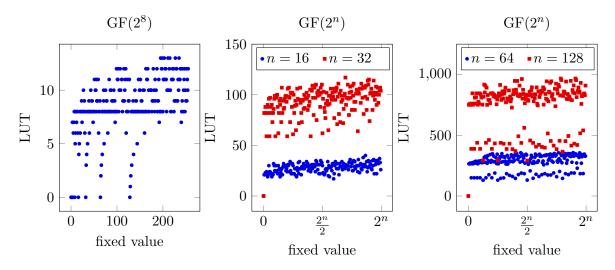

Another way of restricting x-values includes the usage of predefined static points. A multiplier with a static value fixed on one input results in a high decrease of required logic, but leads to the loss of flexibility at run time.

The final size of such a multiplier is strongly dependent on the actual fixed value. To gain an idea of its complexity, table 3.2 presents synthesis results with one value fixed at a specific point. In  $GF(2^8)$  all 255 possible values were synthesized, in  $GF(2^{16})$  to  $GF(2^{128})$  200 values, equally divided over the corresponding field, were synthesized.

| bit-                |     | first multiplicand |     |     |      |      |  |  |  |

|---------------------|-----|--------------------|-----|-----|------|------|--|--|--|

| widths              |     | 8                  | 16  | 32  | 64   | 128  |  |  |  |

|                     | 2   | 6                  | 11  | 19  | 33   | 65   |  |  |  |

|                     | 4   | 16                 | 32  | 64  | 128  | 208  |  |  |  |

|                     | 6   | 21                 | 41  | 81  | 159  | 319  |  |  |  |

| q                   | 8   | 27                 | 51  | 99  | 224  | 386  |  |  |  |

| second multiplicand | 12  |                    | 78  | 170 | 317  | 577  |  |  |  |

| plic                | 16  |                    | 114 | 200 | 392  | 775  |  |  |  |

| ltij                | 20  |                    |     | 284 | 559  | 1117 |  |  |  |

| nm                  | 24  |                    |     | 337 | 678  | 1327 |  |  |  |

| pu                  | 28  |                    |     | 394 | 777  | 1535 |  |  |  |

| COI                 | 32  |                    |     | 450 | 882  | 1742 |  |  |  |

| $\mathbb{R}^{-1}$   | 48  |                    |     |     | 1304 | 2602 |  |  |  |

|                     | 64  |                    |     |     | 1731 | 3520 |  |  |  |

|                     | 96  |                    |     |     |      | 5361 |  |  |  |

|                     | 128 |                    |     |     |      | 7239 |  |  |  |

**Table 3.3:** Size of an asymmetric  $GF(2^n)$ -multiplier according to the bit-widths of its inputs respectively,measured in 6-input LUT.

Figure 3.2: Size of a polynomial multiplier with one input fixed at a specific value (x-axis) for different Galois fields, measured in 6-input LUT.

For the rest of this thesis the x-value was restricted to 8 bit, resulting in 255 possible shares. The size was considered to be sufficient in a typical cloud based data storage setting and the decrease of up to 5.3% of originally needed LUTs in  $GF(2^{128})$  brings high performance benefits as well.

#### Reduction

The reduction in a binary extension field accords to a modulo operation, where the value to be reduced is divided by the irreducible polynomial. The irreducible polynomial must be of degree n in a  $GF(2^n)$ . Usually a set of irreducible polynomials are available for a binary extension field

and from a mathematical point of view all are equally suitable for defining the field. From the practical point of view, the weight of the polynomial and the number of nonzero coefficients have a direct influence on the complexity of the modulo operation and its hardware implementation. To implement one static irreducible divisor polynomial results in even more reduction potential of the circuit.

Such a modulo operation by a static divisor can be implemented efficiently as a linear feedback shift register (LFSR). The number of nonzero coefficients in the divisor polynomial equals the amount of XOR-connections in the feed-back loop. To that end, this approach needs n cycles to generate the results, where n is the number of input bits.

The polynomial division and modulo operation is a common problem, as it is used for many other applications, for example in the cyclic redundancy check (CRC). Consequently the polynomial division was part in a lot of research to investigate the realization in less clock cycles. In [81] a parallel implementation is described, which calculates the result within one clock cycle by using only static XOR-connections. The algorithm to find these connections was used for this work and is described below.

- 1. Consider the input data D of n bits as an  $1 \times n$  vector and the irreducible polynomial as an  $1 \times m$  vector.

- 2. Calculate n modulo results subsequently for the input data set  $2^i, i = 1...n$ , and store the bits of each result in a vector  $V_i$ . There will be i vectors V with the size  $1 \times m$ .

- 3. Create a  $n \times m$  matrix M, where each column consists of the vector V.

- 4. Store the product of the matrix M and the input data D in a vector R,  $R = M \otimes D$ , which is the result. The symbol  $\otimes$  denotes a matrix multiplication, where the multiplications are performed by AND-operations and additions by XOR-operations. As a result only those input bits remain for each output bit where the corresponding bit was set in the matrix M. Only those bits have to be XOR connected in hardware in order to produce the remainder R.

A Java program was developed in order to pre-calculate the required XOR-connections subsequently for all implemented fields. The resulting XOR-connections can be found in the appendix.

As mentioned before, the size of the chosen irreducible polynomial influences the complexity of the circuit. In [62] small irreducible polynomials were investigated for different binary extension fields. For each investigated and developed field in this work ( $GF(2^8)$ ,  $GF(2^{16})$ ,  $GF(2^{32})$ ,  $GF(2^{64})$  and  $GF(2^{128})$ ) the irreducible polynomial was chosen from [62] and a summary can be found in table 3.4.

| bit-width | irreducible polynomial     |

|-----------|----------------------------|

| 8         | $x^8 + x^4 + x^3 + x$      |

| 16        | $x^{16} + x^5 + x^3 + x$   |

| 32        | $x^{32} + x^7 + x^3 + x^2$ |

| 64        | $x^{64} + x^4 + +x^3 + x$  |

| 128       | $x^{128} + x^7 + x^2 + x$  |

Table 3.4: Used irreducible polynomials in this work.

The resulting size of the reduction circuit, measured in 6-input LUT, is shown in table 3.5 for each investigated Galois field. The input bit-width also influences the size, here input bit-width  $2 \times (n-1)$  is assumed, which corresponds to a polynomial multiplication output for n input bits.

| Galois fields   | $GF(2^8)$ | $GF(2^{16})$ | $GF(2^{32})$ | $GF(2^{64})$ | $GF(2^{128})$ |

|-----------------|-----------|--------------|--------------|--------------|---------------|

| Input bit-width | 15        | 31           | 63           | 127          | 255           |

|                 |           |              |              |              |               |

| LUT needed      | 14        | 36           | 32           | 127          | 253           |

Table 3.5: Size of the reduction circuit in different Galois fields, measured in 6-input LUT after synthesis.

#### Share Generation

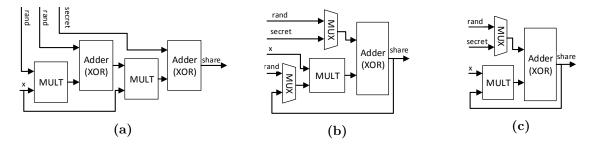

The character of equation (3.2) is best suited for a sequential computation in a feed-back loop, shown in figure 3.3b. One multiplier is used for performing all required multiplication steps subsequently. After each multiplication a reduction has to be performed, followed by an addition. The benefit of such an architecture are the arbitrary selectable threshold values at runtime, as only the amount of needed clock cycles changes. A drawback of such a scheme is the fact, that all operations have to be performed within the same cycle for an efficient capacity utilization of all units, because of the feed back loop. This leads to the disability of efficient pipelining.

On the other hand, an architecture fully capable of pipelining is shown in figure 3.3a, where architecture (b) is unrolled. In comparison to (b) the threshold value has to be chosen at synthesis time, which strongly effects the synthesis result in terms of space. Moreover, the data management becomes difficult. To alleviate data management issues, the design was build with a sequential approach.

Figure 3.3: Multiple architectures for a share generation. (a) presents a pipelined architecture. while (b) and (c) are sequential architectures with a feed back loop.

As shown in figure 3.3b, two multiplexers are needed for the share generation. The value of the first summand has to be selected between the random values and the secret itself. On the other hand, the multiplier is fed with a random number in the first cycle of an evaluation round and the previous addition result in all other cycles. In this work a slight adjustment to this architecture was made, shown in figure 3.3c, which consists of only one multiplexer. Obviously this comes with the cost of the multiplier not being used the in first cycle of the evaluation. However, the data management becomes easier and one random value or secret is applied at a time, thus providing many advantages as well. It is of special benefit for looking up the next step of Computational Secret Sharing. Moreover, it becomes more LUT  $\times$  number of cycles efficient for threshold values above a certain limit.

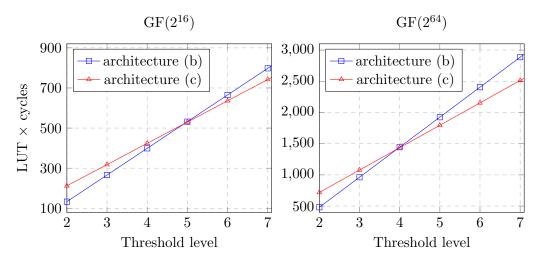

While architecture (b) needs k-2 cycles to calculate a share, architecture (c) needs k-1 cycles, where k is the threshold value in the secret sharing scheme. Higher values for k decrease the relative difference between these needed cycles and the saving of the second multiplexer is of greater influence. The relation is demonstrated in figure 3.4, exemplary for Galois fields  $GF(2^{16})$  and  $GF(2^{64})$ , where architecture (b) becomes more LUT × cycle efficient after a certain threshold value k of 4 or 5.

Figure 3.4: A comparison of the performance from architecture (a) and (b) for the share generation in dependence of the threshold value from the secret sharing scheme. The performance is measured in the cycle LUT product.

In a secret sharing setting for cloud applications, threshold values above or equal to four are expected. Combined with better management and adaptability to the Computational Secret Sharing scheme, architecture (c) was favoured and implemented.

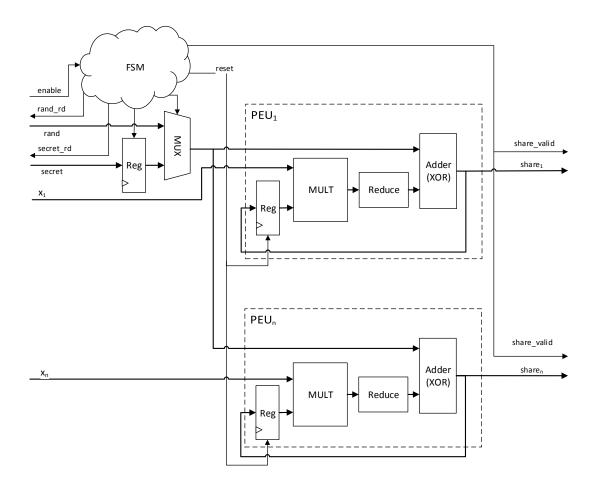

The architecture of the final Share Generation Unit (SGU) is described in the following and presented in figure 3.5. In this work, the design is parametrizable for the used Galois field, the bit-width of the x-values and the number of parallel share generations. A finite state machine (FSM) controls the sharing process, while multiple Polynomial Evaluation Units (PEU) can be used to generate multiple shares at a time. Each PEU contains only elements that are needed to be unique for each share. It is beneficial to construct them parallel, as all need the same random and secret values at a time, which leads to only one required multiplexer for all PEUs. Moreover, the random values don't have to be saved for later rounds.

If a share construction is requested, the signal *enable* is set to high. The circuit starts to load the secret into a register and the first random word, while both read operations are confirmed via the corresponding *rand\_rd* and *secret\_rd* signal. Next, the FSM controls the multiplexer in order to distribute the random values for k - 2 cycles and the secret at the last round. After the last round the corresponding share is at the output and the *share\_valid* signal confirms the share. The register at the multiplier input is directly reset in preparation of the next round. The next round is initiated if the enable signal is high again.

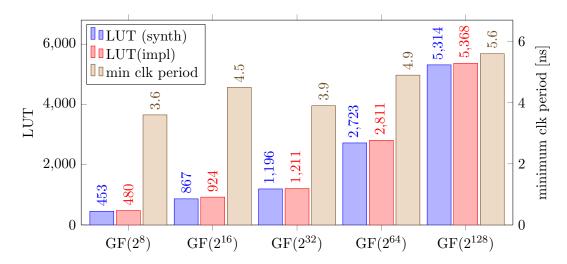

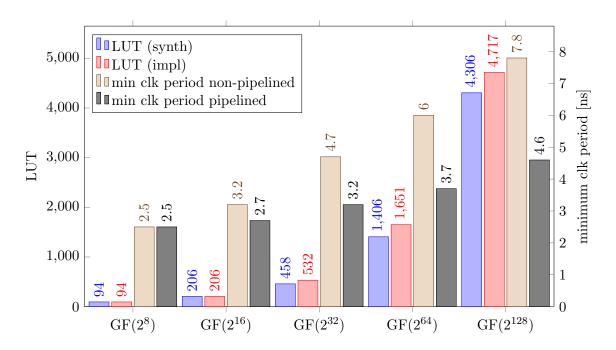

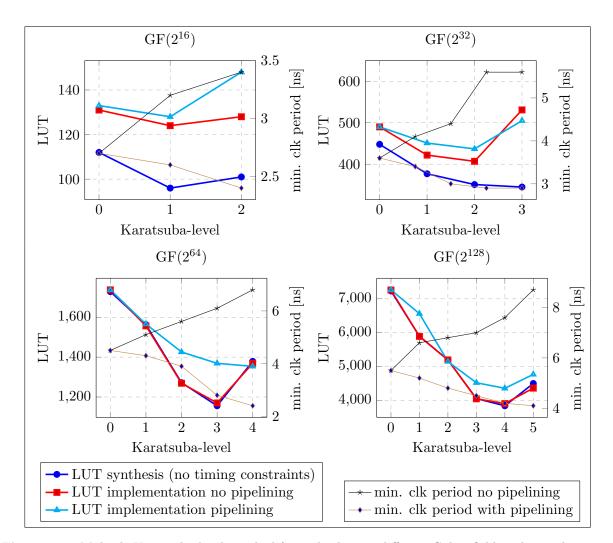

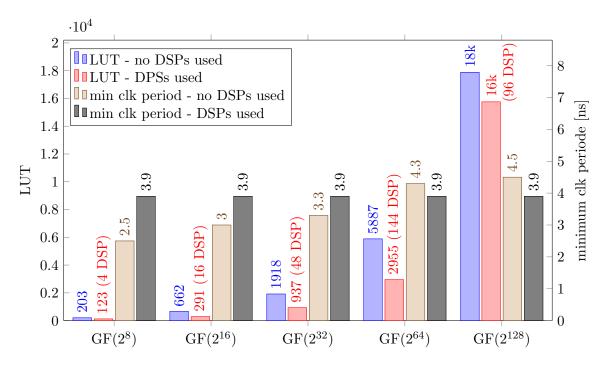

The resulting size in terms of 6-input LUT, as well as the minimal possible clock period is demonstrated in figure 3.6, for the construction of 10 shares in parallel. Remarkable is the slight increase in resources and the decrease of the clock period for  $GF(2^{16})$  compared to  $GF(2^{32})$ , mainly because of the efficient implementable irreducible polynomial in this field.

Figure 3.5: Architecture of the Share Generation Unit.

## 3.3 Secret Reconstruction

For the recovery of the original secret an interpolation is applied. In [77] various interpolation techniques were analysed in terms of their complexity and scalability. It was shown that the Lagrange interpolation is most suitable for this application. The Lagrange interpolation is performed in two steps. First basis-polynomials are computed as in (3.3) regarding the available points. By using the the shares as weights for the basis-polynomials, the y-value at the interested point is reconstructed by multiplying each shares with its corresponding basis polynomials and adding products together, shown in (3.4).

$$l(i) := \prod_{\substack{0 \le m \le k, \\ m \ne j}} \frac{x - x_m}{x_j - x_m}$$

(3.3)

$$L(x) := \sum_{j=0}^{k} y_{i} l_{i}(x)$$

(3.4)

The basis polynomials remain unchanged as long as points from the same x-value, regardless the y-value, are used. However, every time different points are included in the interpolation, all

Figure 3.6: Size of the SGU in 6-input LUT for the synthesis and implementation and the minimal possible clk period. In the evaluated design 10 shares were constructed parallel.

of the basis polynomials have to be recalculated. At this point a practical assumption for a high performance increase is applied.

It is assumed that the applied x-values don't change with every processed word. This comes from the assumption, that all shares, stored on one specific server contains the same x-value and data in a network setup are usually transmitted in packets. The size of an Ethernet frame is typically about 1500 bytes, which would accord in  $GF(2^{32})$  to about 1500/4 = 375 words. When reconstructing a file, the source of the shares are not changed at a per word basis. They would at least change with every packet or more realistic they won't change during a hole reconstruction process. The distributed setup is due to security and reliability reasons and there is no need to change servers frequently, except if required by outer circumstances. For that reason, the computational intense calculations of the basis polynomial are outsourced to a processing system (PS) within the FPGA, and the available logic is used for computations continuously.

The implementation of the resulting operations into logic are addition, multiplication and reduction, similar to the previous section of the share generation. The operations addition and reduction remain unchanged. The multiplication optimization methods applied for the share generation are not applicable here, because a symmetric multiplier is necessary. However, there are multiple methods for further reduction of the size of a polynomial multiplier. This will be discussed in more detail in chapter 4. For the future design a multiplier with several, so called, Karatsuba levels is used. These designs show a significant increase of the minimal clock period for higher bit-widths. However, because the multiplier is not used in a feed-back-loop, it can be efficiently pipelined to overcome timing problem.

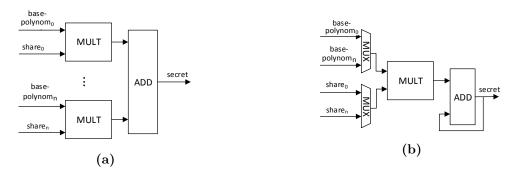

The weighting function of the shares with the basis polynomial consists of multiplications and additions. A use of k multipliers, illustrated in figure 3.7a, enables an efficient reconstruction of one share per cycle. However, it is possible to use only one multiplier and apply the coefficients subsequently, shown in figure 3.7b. An efficient pipelining of the multiplier is implemented since only an adder is in a feed-back-loop.

Figure 3.7: A sequential and parallel architecture for the secret reconstruction.

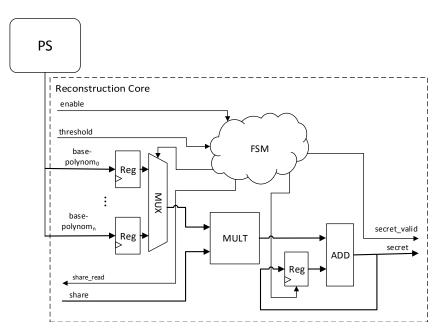

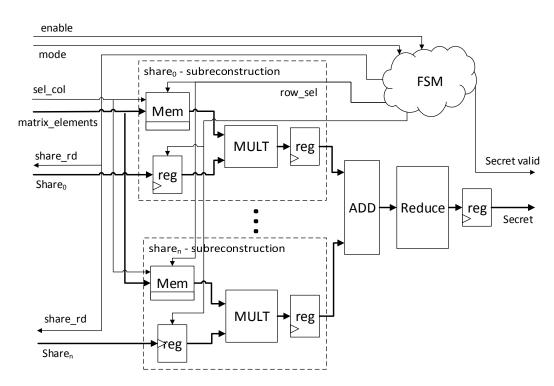

The architecture, as shown in figure 3.7b is selected in order to reach the same share generation and secret reconstruction speed as described below. It was designed generically to be able to work in all discussed Galois fields. A generic number of Karatsuba levels are applied in the multiplier and the opportunity to choose pipelining or not. The final architecture is shown in figure 3.8. The PS is the head of the reconstruction process and managing the computation of the basis polynomials. The basis polynomials are computed in the PS using a C-library from James S. Plank [26]. After computation the basis polynomials are loaded into the corresponding hardware registers via an AXI bus. The shares are supplied subsequently over the same bus. This assumption was taken to facilitate the circuits, but can be easily extended with a set of share registers and a multiplier.

If shares are available, the Secret Reconstruction Unit (SRU) is activated by setting the enable signal to high. The first base polynomial is now forwarded to the multiplier by the multiplexer. Additionally, the first share is aligned to the multiplier, and its read is conformed by setting the *share\_read* signal to high. The register at the adder input is reset according to the number of pipelining stages if the first multiplication result of the new reconstruction process is available on the adders input. With the input *threshold*, the threshold level is applied to the circuit. In the following cycles all weighted base polynomials are added together successively. Finally, the *secret\_ready* signal is set to high, signalizing the final reconstruction of the secret.

The resulting size in 6-input LUT and the achieved minimum clock period with the architecture is shown in figure 3.9 for a pipelined and non-pipelined version respectively. Due to the symmetric multiplier the size of the final Secret Reconstruction Unit increases quadratically. The influence of the pipelining stages results in a slightly bigger final design, because less logic optimization is possible. On the other hand, a significant increase of the possible clock frequency is possible.

#### 3.4 Evaluation

In order to evaluate and compare the presented implementations, both a secret sharing software implementation was compared to this hardware implementation and a full working FPGA implementations is realized, which communicates with external systems and is capable of secret sharing and secret reconstruction.

Figure 3.8: Architecture of the Secret Reconstruction Unit.

#### Hardware Software Comparison

For the evaluation against a computer program, a simple Shamir Secret Sharing algorithm was implemented, which can operate in all investigated Galois fields. Within this program, all additional tasks, such as the random number generation, read and write procedures to the hard disk or network and other data management, were excluded. This was in order to find the theoretical maximal throughput.

Various software libraries were tested in order to find an efficient implementation for the calculation in the Galois fields. The selected library for the implementation is from James S. Plank [26]. It contains three different multiplication strategies, each applied for different Galois fields. Fields up to 9 bit are implemented in look-up-tables, fields from 10 to 22 bit are implemented with logarithmic and inverse logarithmic look-up-tables and an addition and fields bigger or euqal to 23 bit are implemented with shift and addition operations. The software was running using multithreading and 100% utilization of each processor core on a computer with the following specifications:

- 1. Processor: Intel i5-4590, Quadcore, 3.3 GHz

- 2. RAM: 16 GB, DDR3

- 3. Operating System: Windows 7, 64 bit

- 4. Hard Disk: 512GB, SSD, Samsung 850 Pro

- 5. Thermal Design Power (TDP): 84 W

The hardware was implemented on the Zedboard using a Zynq®-7000 All Programmable SoC XC7Z020-CLG484-1 FPGA. The data management was neglected for the FPGA, but due to

Figure 3.9: Size of the SRU in 6-input LUT, for synthesis and implementation as well as the minimal possible clk period. It is shown for both, a pipelined and non-pipelined architecture.

reservations of structures and routing, an utilization from only 50% was assumed, resulting in 26600 available LUTs. For a theoretical comparison, the architecture results from the previous sections were used and simply extrapolated for a usage of of 26600 LUTs.

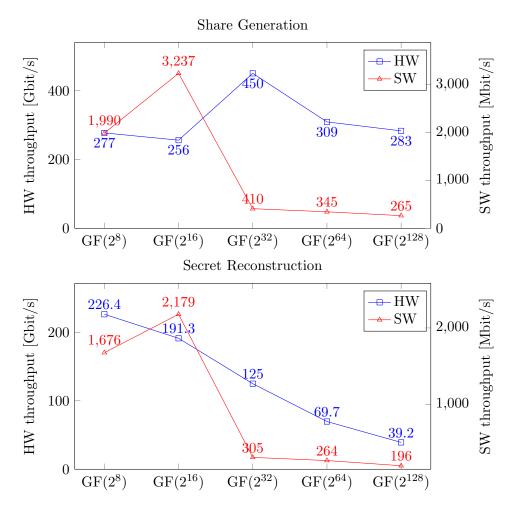

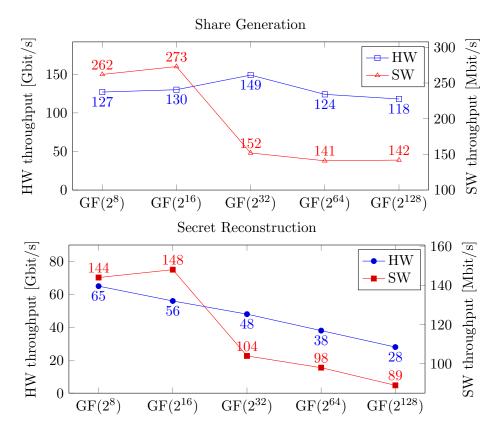

The final results are shown in figure 3.10. A SGU with a parallel generation of 10 shares was applied in the FPGA design. The throughput is measures in Gbit/s according to the output of a functionality. This is generated share bits for the SGU and reconstructed secret bits for the SRU.

Figure 3.10 shows an almost constant speed of the share generation in the FPGA, with a single peak at 32 bit. This effect of constancy is caused by the static size of 8 bit for the x-value. In the computer implementation a strong drop of the performance is notable at 32 bit. At this point look up table based calculations are not applicable anymore and the relatively slow shift based multiplications are necessary. Overall the FPGA design turns out to have a performance gain of a factor of about 100.

| Field         | Share Generation   |      | Secret Reconstruction |      |

|---------------|--------------------|------|-----------------------|------|

| -             | FPGA PC            |      | FPGA                  | PC   |

| $GF(2^8)$     | $8.2\mathrm{mW}$   | 42W  | $9.9\mathrm{mW}$      | 50W  |

| $GF(2^{16})$  | $10.7 \mathrm{mW}$ | 26W  | $13.3 \mathrm{mW}$    | 39W  |

| $GF(2^{32})$  | $6.4\mathrm{mW}$   | 205W | $22.1\mathrm{mW}$     | 275W |

| $GF(2^{64})$  | $9.0\mathrm{mW}$   | 237W | $43.3 \mathrm{mW}$    | 318W |

| $GF(2^{128})$ | $5.2\mathrm{mW}$   | 317W | $89.1 \mathrm{mW}$    | 429W |

Table 3.6: Power consumptions for a throughput of 1 Gbit/s.

Based on the throughput shown in figure 3.10 an estimation for the power consumption per throughput was made. The Intel i5 processor has a power consumption of 84 W and the power

Figure 3.10: The maximal theoretical throughput of a software and a FPGA implementation, for the share generation and secret reconstruction respectively. A parallel construction of 10 shares in the FPGA is assumed. The throughput is measured in share bits per second for the share generation and secret bits per second for the secret reconstruction.

consumption of the FPGA was estimated using Vivado. In table 3.6 the resulting power consumptions for a throughput of 1 Gbit/s are compared.

#### Implementation of a complete System on the Zedboard

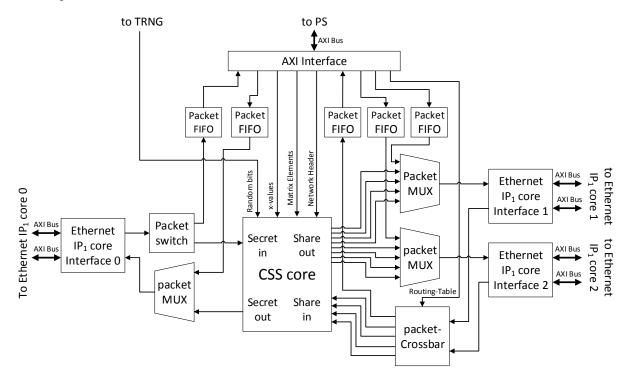

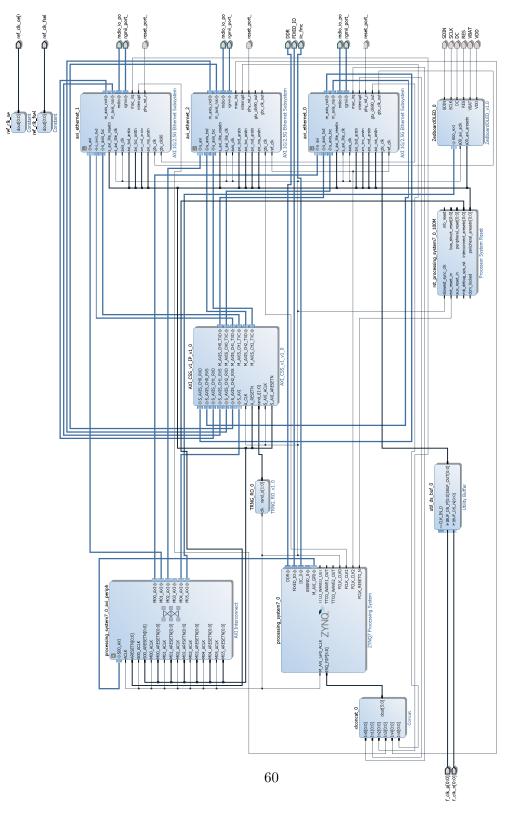

While the implementation for all investigated Galois fields were verified with simulation, for the practical proof of concept a fully working implementation on the Zedboard was made. For this purpose an AXI secret sharing intellectual property ( $IP_1$ ) core was build, which communicates via an AXI bus. The PS takes care of the communication to the outer world and applies all necessary data to the secret sharing core. These data includes the calculated basis polynomial, the x-values, the threshold level, the secret and the shares. A simple control and status register is accessible for the PS to enable the SGU or SRU. All secret and share data were buffered within the SSS core using First In- First Out (FIFO) on all inputs and outputs. The status of the FIFOs were accessible by the control and status register. A simple TRNG was included in the design, its structure will be discussed in detail in section 6.2.

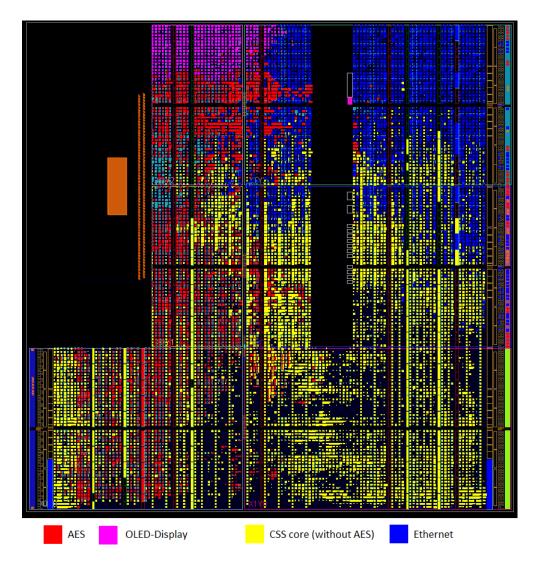

The implemented system works in  $GF(2^{32})$  for simplicity reasons, as the AXI bus of the PS has a width of 32 bit. The final usage, including the logic of the FIFOs and communication is shown in table 3.7. 8 shares were produced parallel and a threshold value of 4 was selected. With a used clock frequency of 200 MHz, the implementation achieves a throughput of 12.8 Gbits/s for the share generation, measured in shared bits produced per second and 1.6 Gbits/s for the secret reconstruction, measured in secret bits recovered per second. The device utilization is about 5.8% of the available LUTs.

|      | $\operatorname{SGU}$ | SRU | TRNG | SGU-FIFOs | SRU-FIFOs | AXI Bus |

|------|----------------------|-----|------|-----------|-----------|---------|

| LUT  | 934                  | 390 | 384  | 375       | 293       | 597     |

| BRAM |                      |     |      | 4.5       | 1         |         |

Table 3.7: The FPGA implementation result for a SSS core, listed by functional units.

## 4 Advanced Multipliers

In this chapter the polynomial multiplier realization within a FPGA and various improvement strategies are analyzed.

First mathematical algorithms to reduce the computational complexity are presented and the Karatsuba algorithm is discussed and evaluated in more detail as well as its implementation in the FPGA. In order to further decrease the final LUT count FPGA specific strategies are investigated based on including other design elements of the FPGA.

### 4.1 Introduction

The implementation of Shamir's Secret Sharing reveals the multiplier to be the bottleneck of the design, with the highest consumption of resources. Therefore other implementation techniques were investigated in order to reduce the amount of necessary LUTs for a multiplier.

While the classical multiplication straight forward approach has a quadratic complexity of  $O(n^2)$ , with n as the number of input bits, various algorithms for the reduction of the complexity of a multiplication exist. They include the Karatsuba algorithm [40], the Toom multiplication [71] and its generalization, the Tom-Cook algorithm [16] as well as improvements of it [83], the Schönhage-Strassen algorithm [61], the Knuth algorithm [43] and algorithms using the Fast Fourier Transformation (FFT) [11] [17].

In comparison, the Karatsuba algorithm is best suited for a practical implementation due to its simplicity. For that reason a performance gain with a Karatsuba multiplier is discussed in many papers equally for soft- and hardware, e.g. in [29] and [28]. It is applicable to any kind of multiplication including finite field applications. In section 4.2 the influence of the Karatsuba algorithm in different binary extension fields is examined.

In section 4.3 alternative methods to decrease the utilization of LUTs are investigated, based on the application of addition design elements within a FPGA for performing a polynomial multiplication.

## 4.2 Applying Karatsuba's Algorithm

In 1963 Karatsuba published an algorithm to reduce the complexity of a multiplication, known as the Karatsuba algorithm. The idea follows the 'divide and conquer' scheme. A multiplication

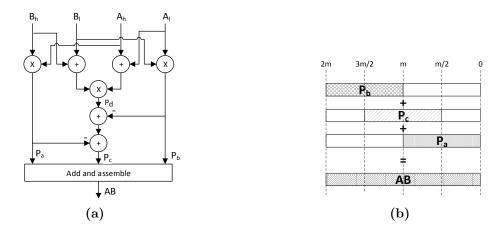

with a complexity of  $O(n^2)$  is broken down to smaller multiplications and additions, with a complexity of O(n). The resulting overall complexity of this scheme is  $O(2^{\log_2(3)})$ . Even with the theoretical improvement it is not guaranteed to reach the same complexity reduction within a FPGA resulting in a LUTs reduction. More complex data paths may result in longer delays. For this purpose the algorithm was investigated for a 6-input LUT. In the following procedure it is described how the Karatsuba algorithm works.

Consider two input multiplicands A and B with a bit-width of m. Both are divided into two parts with half of the bit-width  $A_h$ ,  $A_l$  and  $B_h$ ,  $B_l$ .  $A_l$ ,  $B_l$  represent the lower bits and  $A_h$ ,  $B_h$ the higher bits of A and B in equation (4.1). Mathematically, we denote such a split by a multiplication with  $R^m$ , where R represents the base of the used number system, e.g. 10 in the decimal system or 2 in the binary system, and m symbolizes the position of a single symbol within a number, e.g.  $1R^1 = 10$ .

We consider a and b written in lower cases as the digits of A and B respectively and the value x in the brackets (x) indicates the bit number.

$$A = A_h R^{\frac{m}{2}} + A_l = a_m + \dots + a_0$$

$$B = B_h R^{\frac{m}{2}} + B_l = b_m + \dots + b_0$$

$$A_h = a(m) + \dots + a(\frac{m}{2}), A_l = a(\frac{m}{2} - 1) + \dots + a(0)$$

$$B_h = b(m) + \dots + b(\frac{m}{2}), B_l = b(\frac{m}{2} - 1) + \dots + b(0)$$

(4.1)

The product AB of A and B is expressed as the product of its sum.

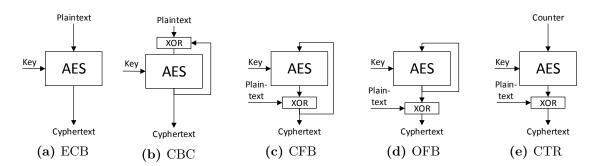

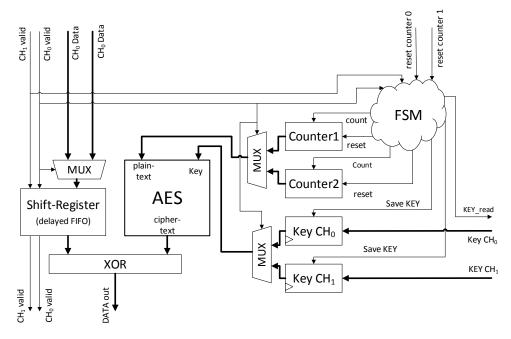

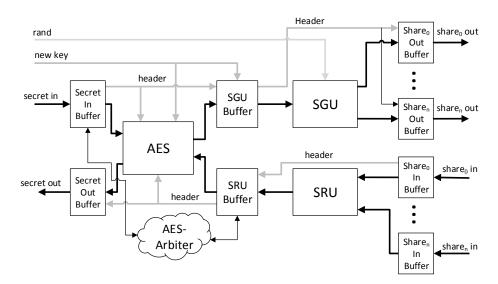

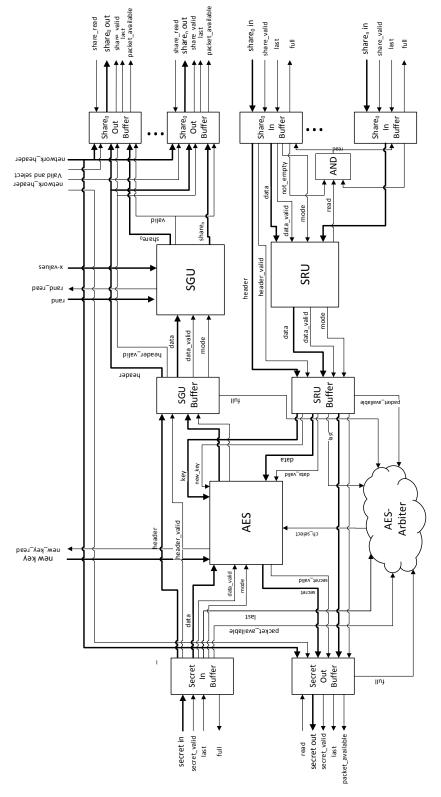

$$AB = (A_{h}R^{m} + A_{l})(B_{h}R^{m} + B_{l})$$