The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology. http://www.ub.tuwien.ac.at/eng

FAKULTÄT FÜR !NFORMATIK Faculty of Informatics

# Protecting 4-Phase Delay-Insensitive Communication Against Transient Faults

## DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

#### **Technische Informatik**

eingereicht von

## Florian Ferdinand Huemer BSc.

Matrikelnummer 0828465

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Ao.Univ.-Prof. Dipl.-Ing. Dr.techn. Andreas Steininger

Wien, 19. Jänner 2017

Florian Ferdinand Huemer

Andreas Steininger

# Protecting 4-Phase Delay-Insensitive Communication Against Transient Faults

## **DIPLOMA THESIS**

submitted in partial fulfillment of the requirements for the degree of

## **Diplom-Ingenieur**

in

#### **Computer Engineering**

by

### Florian Ferdinand Huemer BSc.

Registration Number 0828465

to the Faculty of Informatics at the Vienna University of Technology

Advisor: Ao.Univ.-Prof. Dipl.-Ing. Dr.techn. Andreas Steininger

Vienna, 19<sup>th</sup> January, 2017

Florian Ferdinand Huemer

Andreas Steininger

## Erklärung zur Verfassung der Arbeit

Florian Ferdinand Huemer BSc. Spengergasse 28/21, 1050 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Wien, 19. Jänner 2017

Florian Ferdinand Huemer

## Acknowledgments

First of all, I want to thank my parents for their great support throughout my studies. I would further like to thank my advisor for the opportunity to work on this very interesting topic. His excellent guidance, the continuous discussions and meaningful remarks were essential in the process of writing this thesis. Special thanks go to Jakob Lechner for his valuable suggestions and feedback.

## Kurzfassung

Mit ihrer Robustheit gegen Signallaufzeitschwankungen bieten asynchrone delay-insensitive (DI) Übertragungsstrecken vorteilhafte Eigenschaften im Vergleich zu synchronen Lösungen. Dabei ist allerdings zu beachten, dass dafür spezielle DI Codes notwendig sind. Diese Codes sind aber in der Regel sehr anfällig für transiente Fehler, die während einer Übertragung auftreten können, da bei vielen dieser Codes bereits ein einzelner Fehler (im schlimmsten Fall) eine völlige Änderung des Nachrichteninhaltes zur Folge haben kann. Wenn dem Empfänger einer solchen Nachricht keine zusätzlichen Informationen zur Verfügung gestellt werden, hat dieser keine Möglichkeit, diese Übertragungsfehler zu erkennen, was natürlich schwerwiegende Konsequenzen für ein System an sich sowie dessen Umgebung haben kann.

In dieser Arbeit werden daher Möglichkeiten zur Absicherung von DI Kommunikation untersucht. Darüber hinaus wird ein neuartiges, zweistufiges Kodierungsverfahren vorgestellt, das auf der Kombination von fehlererkennenden und DI Codes basiert. Diese Lösung nützt dabei die inhärente Fehlerwiderstandsfähigkeit von DI Codes aus und erreicht damit eine gute Kodierungseffizienz bei gleichzeitig niedrigem Implementierungsaufwand. Um die Fehleranfälligkeit der Codes zu analysieren und um gültige Lösungen zu ermitteln, kommen Methoden der Graphentheorie zum Einsatz. Im Vergleich zu existierenden Lösungen wird hier sehr genau darauf geachtet, keine Annahmen über das Signallaufzeitverhalten zu treffen. Die vorgeschlagene Lösung ist sehr generisch und kann prinzipiell mit jedem vierphasigen DI Code verwendet werden.

Mittels einer repräsentativen Auswahl von m-aus-n Codes wird gezeigt, wie das Kodierungsverfahren angewendet wird und welche Kodierungseffizienz dabei zu erwarten ist. Zusätzlich wird eine Metrik eingeführt, die es erlaubt geeignete Codes für gegebene Anforderungen an fehlertolerante Übertragungsstrecken zu identifizieren.

Weiters stellen wir eine Reihe von Sender- und Empfängerschaltungen vor, die verwendet werden können, um das neue Kodierungsverfahren zu implementieren. Zwei detaillierte Implementierungsbeispiele auf Gatterebene für Vertreter der m-aus-n Codeklasse demonstrieren dabei die Machbarkeit des Lösungsansatzes und geben einen Einblick in die zu erwartenden Implementierungskosten.

## Abstract

Compared to synchronous approaches, asynchronous delay-insensitive (DI) communication links have very interesting and desirable properties with respect to their robustness against timing variations and delay assumptions required to implement them. However, special DI codes have to be used to encode the data being transmitted. These codes are usually prone to transient faults occurring during an ongoing transmission, since, in the worst case, even a single transient fault is sufficient to completely change the contents of a message. Unless further redundant information is provided, the receiver has no means to detect such an erroneous transmission. This can, of course, have severe consequences on a system and the environment depending on it.

In this thesis we therefore investigate existing approaches to secure DI communication against transient faults and propose a novel two-step data encoding scheme that combines DI and error detecting codes. Our solution exploits the inherent fault resilience of DI codes to achieve a low overhead and hence good coding efficiency. We use methods from graph theory to analyze this fault resilience and identify appropriate solutions. In contrast to existing approaches we carefully avoid the introduction of timing assumptions to mask faults. The proposed coding scheme is generic and can, in principle, be used with any 4-phase DI code. We give examples on how to apply it to selected representatives of the important class of m-of-n codes and analyze the resulting coding efficiency. Additionally, we provide a metric that allows to identify which codes are well suited for fault-tolerant communication.

We, furthermore, provide a range of transmitter and receiver circuit variants that implement the presented coding scheme. In particular, we give detailed gate-level implementation examples for two m-of-n codes, that demonstrate the feasibility of our approach and give some insight into the required implementation overhead.

# Contents

| Kı | ırzfas       | sung                                        | ix   |  |  |

|----|--------------|---------------------------------------------|------|--|--|

| At | ostrac       | t                                           | xi   |  |  |

| Co | ontent       | s                                           | xiii |  |  |

| Li | st of H      | ligures                                     | xiv  |  |  |

| Li | st of T      | <b>Tables</b>                               | XV   |  |  |

| 1  | Intro        | oduction                                    | 1    |  |  |

|    | 1.1          | Motivation and Problem Statement            | 1    |  |  |

|    | 1.2          | Structure of the Thesis                     | 2    |  |  |

| 2  | The          | ory and Background                          | 3    |  |  |

|    | 2.1          | Coding Theory                               | 3    |  |  |

|    | 2.2          | Asynchronous Circuits                       | 7    |  |  |

|    | 2.3          | Fault Tolerance and Delay-Insensitive Codes | 18   |  |  |

| 3  | Related Work |                                             |      |  |  |

|    | 3.1          | Cheng & Ho                                  | 27   |  |  |

|    | 3.2          | Agyekum & Nowick                            | 28   |  |  |

|    | 3.3          | Pontes, Calazans & Vivet                    | 29   |  |  |

|    | 3.4          | Lechner et. al                              | 29   |  |  |

| 4  | A No         | ew Fault-Tolerant Coding Scheme             | 31   |  |  |

|    | 4.1          | Hardware Model and Fault Hypothesis         | 31   |  |  |

|    | 4.2          | Fault Model                                 | 33   |  |  |

|    | 4.3          | Encoding                                    | 35   |  |  |

|    | 4.4          | Decoding                                    | 40   |  |  |

|    | 4.5          | Decoding with Error Correction              | 45   |  |  |

| 5  | Link         | Architecture                                | 49   |  |  |

|    | 5.1          | Transmitter                                 | 49   |  |  |

|    | 5.2   | Receiver                | 55 |

|----|-------|-------------------------|----|

|    | 5.3   | Metastability Concerns  | 62 |

| 6  | Res   | ults                    | 65 |

|    | 6.1   | Theoretical Results     | 65 |

|    | 6.2   | Implementation Examples | 66 |

|    | 6.3   | Behavioral Simulation   | 70 |

| 7  | Con   | clusion and Future Work | 77 |

| Bi | bliog | raphy                   | 79 |

# **List of Figures**

| Asynchronous handshaking protocols       | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Asynchronous circuit model               | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Muller C-Element                         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Mutex                                    | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Muller pipeline                          | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4-Phase bundled data pipeline            | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4-Phase DI protocol                      | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Single bit dual rail pipeline (3 stages) | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2-Phase DI protocol                      | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                          | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                          | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>1</b>                                 | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                          | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1 11 0                                   | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Example SOGs $(f = 1)$                   | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

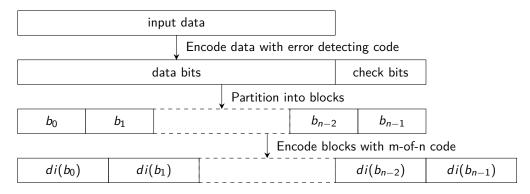

| Fault-tolerant coding scheme             | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

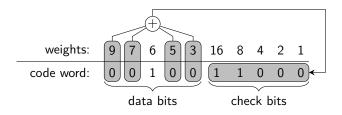

| 5-bit Zero-Sum encoding example          | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

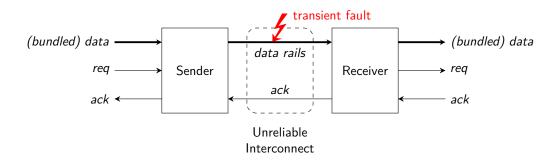

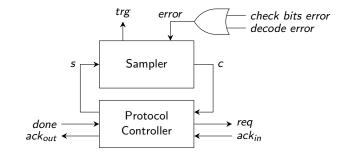

| Delay-insensitive link                   | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

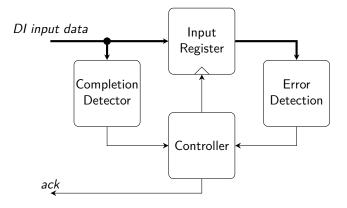

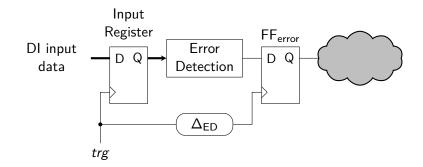

| Fault-tolerant receiver model            | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

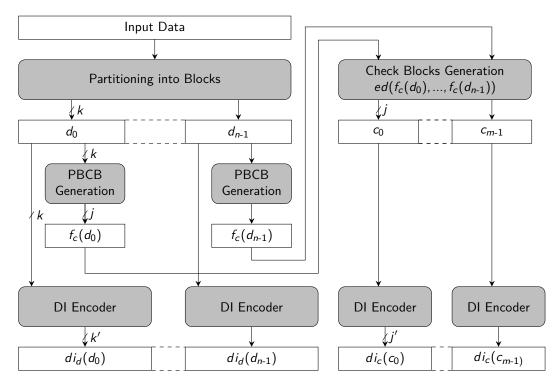

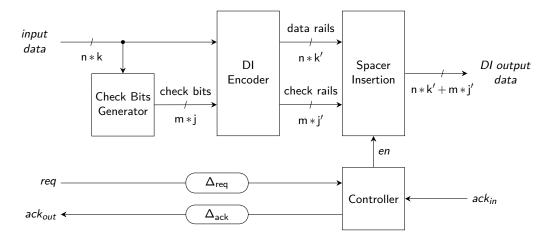

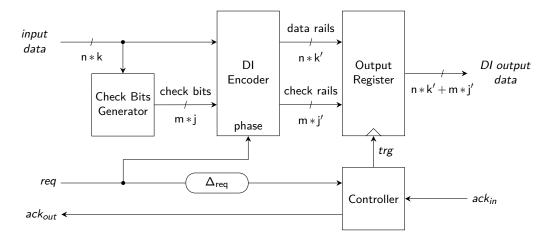

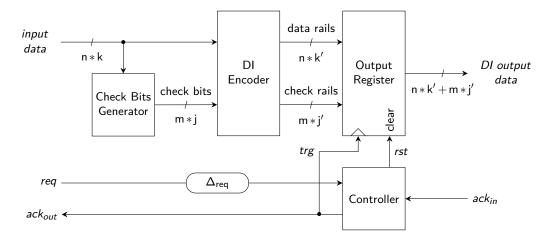

| Encoding overview                        | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

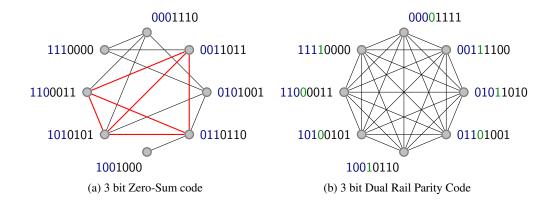

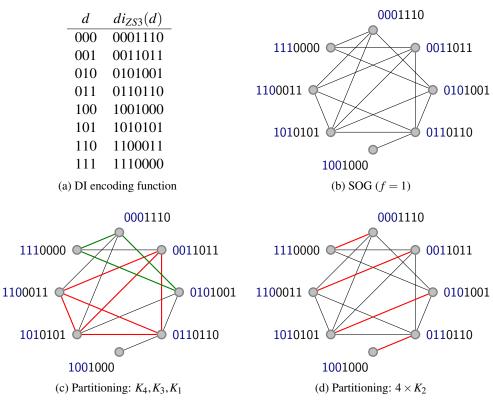

| Example: 3 bit Zero-Sum code             | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Example: 2-of-5 code                     | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                          | Asynchronous circuit modelMuller C-ElementMutexMuller pipeline4-Phase bundled data pipeline4-Phase DI protocolSingle bit dual rail pipeline (3 stages)2-Phase DI protocolLEDR/FSL state chartC gate specificationsDependability and security treeTransmission faults on a DI communication linkExample of overlapping code wordsExample of overlapping code wordsExample SOGs $(f = 1)$ Fault-tolerant coding scheme5-bit Zero-Sum encoding exampleDelay-insensitive linkFault-tolerant receiver modelEncoding overviewExample: 3 bit Zero-Sum code |

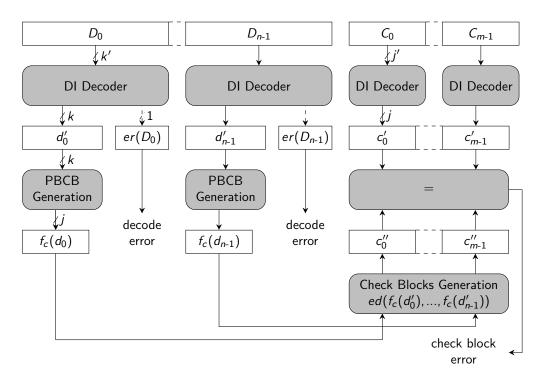

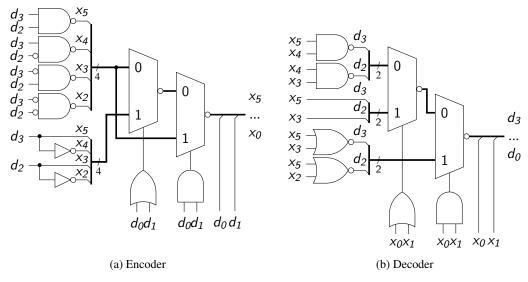

| 4.6  | Decoding overview                                              |

|------|----------------------------------------------------------------|

| 4.7  | Code word analysis example                                     |

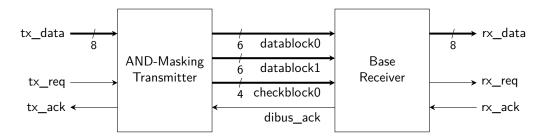

| 5.1  | AND-masking transmitter                                        |

| 5.2  | AND-masking transmitter controller                             |

| 5.3  | D flip-flop based transmitter 52                               |

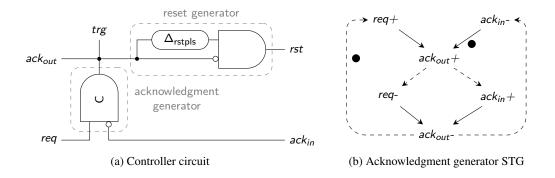

| 5.4  | D flip-flop based transmitter controller circuit               |

| 5.5  | Transmitter using D flip-flops with asynchronous reset         |

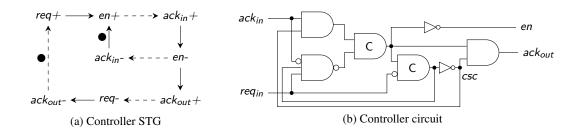

| 5.6  | Simple controller circuit                                      |

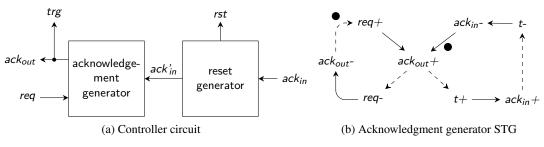

| 5.7  | Advanced controller circuit                                    |

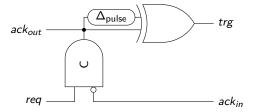

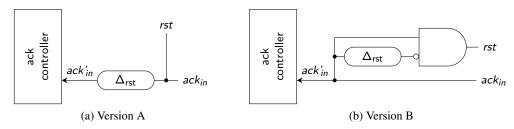

| 5.8  | Reset generator circuit variants                               |

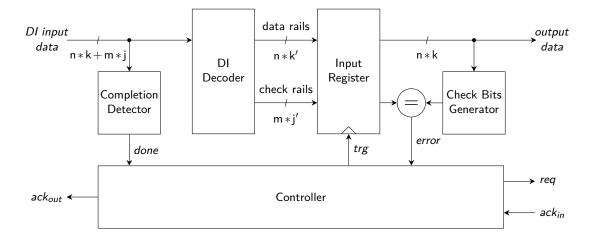

| 5.9  | Base receiver                                                  |

| 5.10 | Base receiver controller 56                                    |

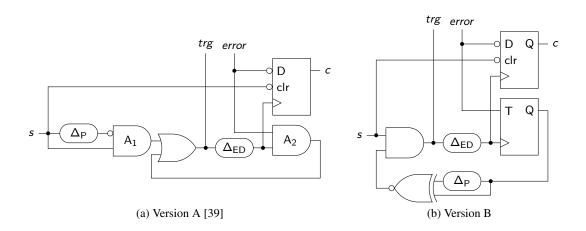

| 5.11 | Sampler circuit variants                                       |

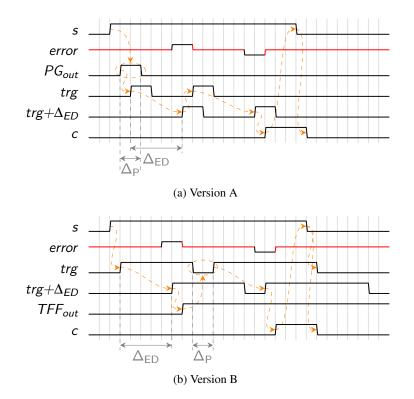

| 5.12 | Sampler timing diagrams                                        |

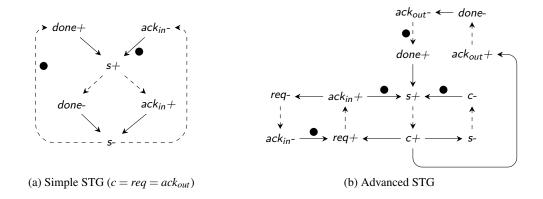

| 5.13 | Protocol controller STGs                                       |

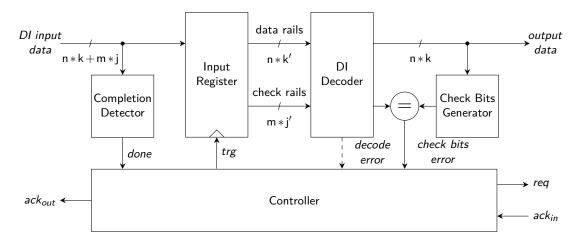

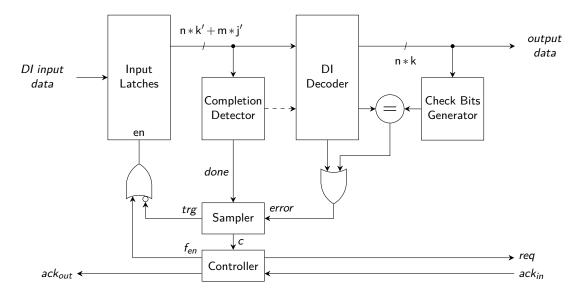

| 5.14 | Receiver with parallel completion detection and DI decoding 60 |

|      | Dual-use completion detector receiver                          |

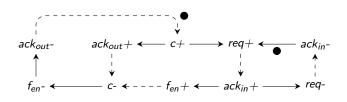

| 5.16 | Controller STG                                                 |

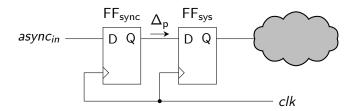

| 5.17 | Single stage synchronization                                   |

| 5.18 | Problematic metastability path                                 |

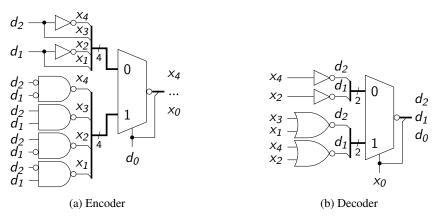

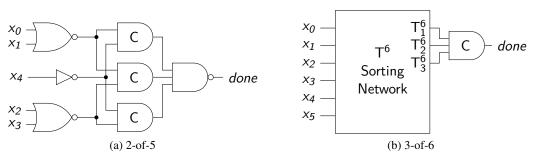

| 6.1  | 2-of-5 circuits $(f = 1)$                                      |

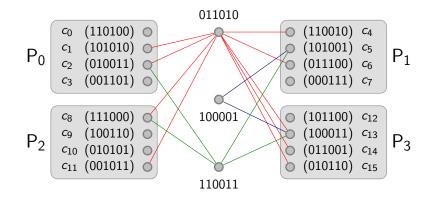

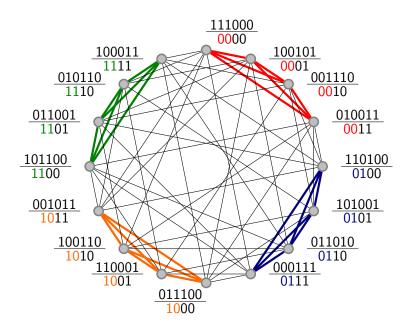

| 6.2  | 3-of-6 code partitioning and code word mapping                 |

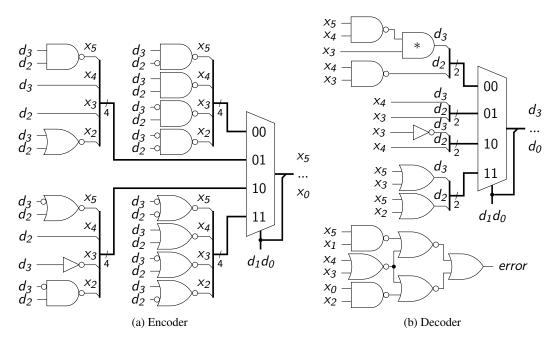

| 6.3  | 3-of-6 circuits $(f = 1)$                                      |

| 6.4  | Completion detector circuits $(f = 1)$                         |

| 6.5  | 3-of-6 circuits (no fault tolerance)                           |

| 6.6  | Simulated DI Link                                              |

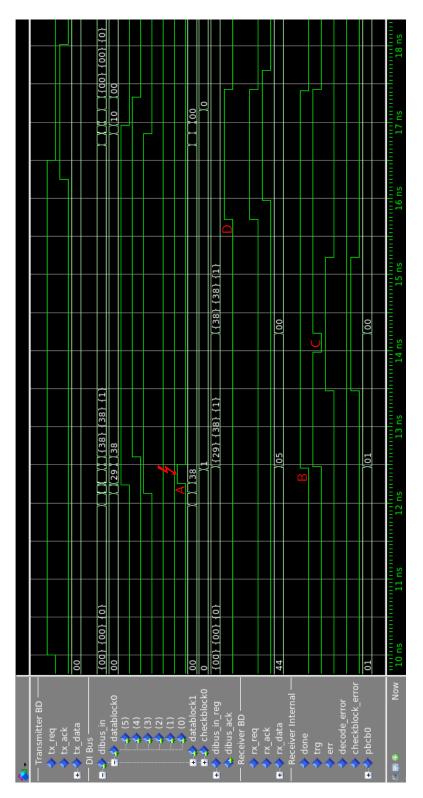

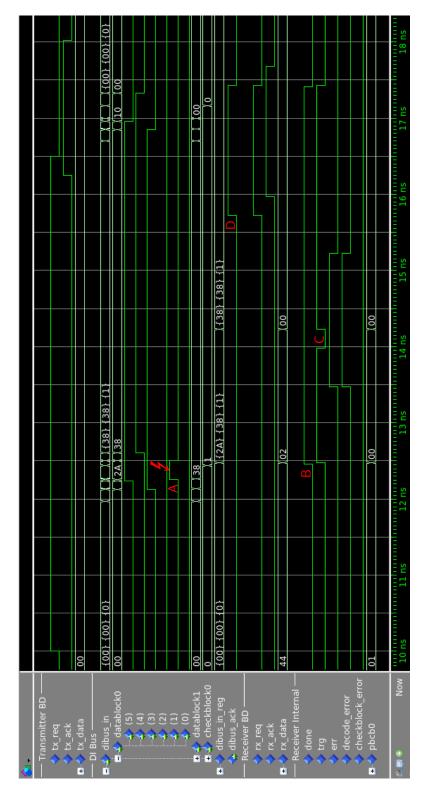

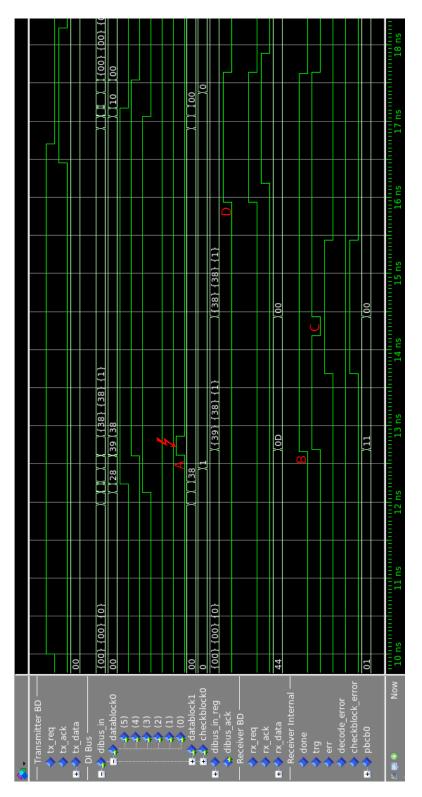

| 6.7  | Transmission fault generating a different valid code word      |

| 6.8  | Transmission fault generating an unused code word              |

| 6.9  | Transmission fault generating an invalid code word             |

# **List of Tables**

| 2.1 | Vertex degrees in m-of-n SOGs      | 23 |

|-----|------------------------------------|----|

| 2.2 | Maximal clique size in m-of-n SOGs | 23 |

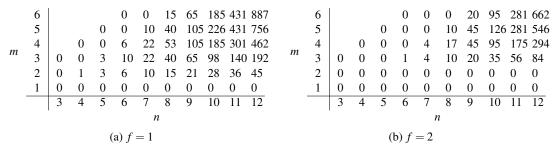

| 6.1 | SOG partitionings for m-of-n codes $(f = 1)$  | 66 |

|-----|-----------------------------------------------|----|

| 6.2 | SOG partitionings for m-of-n codes $(f = 2)$  | 66 |

| 6.3 | Implementation costs m-of-n codes $(f = 1)$   | 69 |

| 6.4 | Implementation costs for different bus widths | 70 |

| 6.5 | Efficiency comparison to existing solution    | 70 |

|     |                                               |    |

## CHAPTER

## Introduction

#### **1.1** Motivation and Problem Statement

Modern semiconductor technology allows the integration of an ever increasing number of transistors into a single integrated circuit. However, with these huge advances in technology, the traditional synchronous design approach to digital circuits faces new problems and challenges. Over the last decades the feature (i.e. transistor) size shrank from around 10  $\mu$ m in the 1970s to today's 22 nm [1]. While smaller transistors can operate at a much higher speed (resulting in a lower gate delay), the metal wires connecting them, i.e. the interconnect, suffer from this miniaturization trend. Thinner wires have a higher resistance which results in greater switching delays. This especially affects long distance wires, like communication links connecting functional units of a chip. In the beginning of integrated circuit design, due to relatively slow transistors, the interconnect delay was negligible. However, the continuous miniaturization led to the situation that it now exceeds the gate delay and became the dominant source of delay in integrated circuits. While gate delays are known very early in the design process, the interconnect delay is difficult to estimate and remains unknown until the actual layout process.

Another problem are process variations during production, as a consequence of which different chips from the same product line have different delays. Delays are also affected by environmental conditions such as temperature and supply voltage. To accommodate for such variations, delay assumptions and safety margins have to be chosen pessimistically, which may unnecessarily slow down the device (e.g. lower clock frequency).

The fundamental concept that makes synchronous design so practical to work with, is the common time base, i.e. the clock, that is used to coordinate all operations in a circuit. Today the distribution of the clock signal to all parts of a design accounts for a considerable part of the overall power consumption of a chip [2].

One option to tackle these problems are asynchronous circuits utilizing delay-insensitive (DI) codes [3, 4, 5]. As the name suggests these circuits don't need a global clock source to drive their operation. Additionally, DI codes offer an inherent robustness against delay variations. This is because the receiver of a DI code word can detect the arrival of complete and valid data solely by

checking the received bit pattern for certain properties. Examples for such codes are m-of-n and Berger codes [4]. On the other hand, the use of DI codes comes at the cost of a greater overhead and increased design complexity. Thus, it makes sense to use DI codes to implement global chip or inter-chip communication and use the synchronous or asynchronous bundled data [5] design approach for the actual functional units of a design. In literature this concept is often referred to as GALS (Globally Asynchronous Locally Synchronous) [5].

Another challenge for integrated circuit design are safety-critical applications, like transportation systems (cars, planes, trains etc.), space flight or (nuclear) power plants. For those applications dependable systems are needed because one failure in such a system can have severe consequences on human lives or the environment. Many of these systems also have to operate under harsh environmental conditions, like high radiation levels or ambient temperature fluctuations. Integrated circuits can be affected by permanent and transient faults which can both cause a malfunction of the chip. Permanent faults result in physical damage to the circuit and can not be corrected (although they may be tolerated to some degree). Transient faults only affect the circuit over a limited period of time. However, it is possible that they manifest themselves in a storage element (soft-error), i.e. the state of the circuit, and cause unintended circuit behavior. Dependable systems must be able to cope with faults to a defined extent and still be able to guarantee safe operation. As discussed in [6], transient faults in today's designs are mainly caused by cosmic radiation. The trend to smaller transistors and lower supply voltages further increases the sensitivity to radiation which makes fault-tolerant design also an issue for non-safety-critical applications. While fault-tolerant coding has already been studied intensively, the combination of fault-tolerant and DI coding has not yet been addressed sufficiently.

For these reasons, this work will investigate methods to build and improve fault-tolerant delay-insensitive communication links, which are able to cope with transient faults.

#### **1.2** Structure of the Thesis

First, Chapter 2 presents the theoretical foundation the following chapters build upon. Furthermore, a precise problem definition and a detailed analysis of current fault modeling techniques is provided. Chapter 3 covers related work that also aims at securing DI communication against faults. The main contributions of this thesis are provided in Chapters 4 and 5. While Chapter 4 introduces a novel fault-tolerant delay-insensitive coding scheme from a theoretical point of view, Chapter 5 presents circuits that can be used to actually implement the proposed coding scheme in hardware. Chapter 6 discusses the efficiency of our approach and shows two gate-level implementation examples. Finally, Chapter 7 concludes the thesis and gives a short outlook on what research directions can be explored further.

# CHAPTER 2

## **Theory and Background**

This chapter presents a summary of the theory and background information, required to understand the concepts and circuits discussed in the following chapters.

#### 2.1 Coding Theory

In this section we provide a brief introduction into the field of coding theory with a special focus on linear block codes. There is a variety of good references on this subject. We have based this section on the books by Blahut [7] and Roth [8]. Coding theory plays an important role in modern digital communication and storage systems. Digital communication channels, i.e. the physical media that are used to transport information (metal wires, air), are always affected by some form of disturbances (noise, interference, crosstalk, etc.). Likewise, digital storage systems suffer from similar problems (e.g. scratches on an optical disk, change in charge in a flash cell). If data would be transmitted or stored without any encoding, errors would directly change the contents of a message, which can have severe consequences on the overall system. Proper codes allow the receiver to detect and even correct erroneous messages. However, these properties also come at a price. A code always adds a certain amount of redundancy to information, which obviously increases the amount of data that needs to be transmitted. The component that takes the (unencoded) input data, i.e. the information or *data word*, and applies the desired code to create a *code word* is referred to as encoder. A decoder is then used to restore the original data word and apply error detection or correction.

A block code always takes a block of data (i.e. the data word) and converts it to a code word. Every data word is assigned exactly one code word. This means that the encoder does not have an internal state. The encoding of a data word is independent of the history of previously encoded information. This is in contrast to convolutional codes, where the encoding and decoding processes are dependent on the internal state of the encoder and decoder, respectively. The field of convolutional codes gives rise to a more general coding model. However, since this work only uses (linear) block codes, we won't go into further detail on this subject. Linear block codes are

widely used and some well known codes such as Parity, Hamming, Reed-Muller, Reed-Solomon, etc. fall into this category. In the following Section 2.1.1 provides a basic introduction to coding theory in general while Section 2.1.2 explains the special properties of linear codes, relevant to this work.

#### 2.1.1 Introduction

A code *C* is always defined over some alphabet *F* of size *q*. Since our discussion is focused on linear block codes, we restrict the alphabet to be a Galois or finite field, denoted by GF(q) or  $\mathbb{F}_q^{-1}$ . This implies that the size of the alphabet is always a prime power. The simplest finite field is  $\mathbb{F}_2 = \{0, 1\}$ , which contains exactly two elements and gives rise to the well known class of binary codes. We will refer to the elements of *F* as the symbols of the code. The code *C* is a (nonempty) subset of the vector space  $F^n$ , and its elements are referred to as code words. The size of *C* is denoted by *M*, whereas *n* is referred to as code or block length. In the following we will discuss some fundamental definitions important to coding theory.

**Definition 1** (Hamming distance). The Hamming distance d between two code words  $x = (x_1, ..., x_n)$  and  $y = (y_1, ..., y_n)$  of some code C is the number of positions where  $x_i \neq y_i$ , i.e. the number of positions where x and y differ.

The Hamming distance is a metric for how much two code words differ. It is always greater or equal to zero, symmetric (d(x,y) = d(y,x)) and satisfies the triangle inequality  $(d(x,y) \le (d(x,z) + d(z,y)))$ .

**Definition 2** (Hamming weight). *The Hamming weight of a code word*  $x = (x_1, ..., x_n) \in C$  *is the number of positions where x is not zero.*

In this context zero means, equal to the zero element of the algebraic structure which makes up the alphabet F of the code. Note that the Hamming distance and weight are related by Equation 2.1.

$$d(x,y) = w(y-x) \tag{2.1}$$

Consider, for example, the code words x = (0, 1, 2) and y = (2, 1, 1) of some code  $C \subset \mathbb{F}_3^3$ over  $\mathbb{F}_3 = \{0, 1, 2\}$ . Their respective Hamming weights are given by w(x) = 2 and w(y) = 3, while for their Hamming distance we have d(x, y) = 2. By calculating the Hamming weight of y - x = (2, 0, 2), the same value for the Hamming distance of x and y is obtained.

**Definition 3** (Minimum distance). The minimum distance of a code C (M > 1) is defined as the smallest Hamming distance between any two code word pairs of C.

$$d_{min}(C) = min_{x,y \in C, x \neq y} d(x,y)$$

<sup>&</sup>lt;sup>1</sup>Henceforth, we will only use the latter notation

The minimum distance determines a code's error detecting and correcting capabilities. Let f denote the number of errors affecting a code word x of some code C. A single error causes the symbol in one position of x to change into some other (arbitrary) symbol of F. For example, let  $C \subset \mathbb{F}_5^3$  be a code over  $\mathbb{F}_5 = \{0, 1, 2, 3, 4\}$ , then the transformation  $(0, 1, 2) \rightarrow (4, 1, 2)$  would constitute a single error (f = 1), while for  $(0, 1, 2) \rightarrow (4, 1, 3)$  a double error (f = 2) would be required. For every code C there exists a decoder that is able to correct up to  $\lfloor (d_{\min} - 1)/2 \rfloor$  (symbol) errors. If the decoder is only concerned with detecting errors rather than correcting them, this is possible for up to  $d_{\min} - 1$  errors. Intuitively this is easy to understand because we know that there exist (at least) two code words x and y in C with  $d(x, y) = d_{\min}$ . Hence,  $d_{\min}$  symbol flips are necessary to transform x to y. If x is affected by less than  $d_{\min}$  errors, no (valid) code word of C is reached and the error must be visible to the decoder. Detailed proofs for these propositions can be found in [8].

#### 2.1.2 Linear Block Codes

In the following we will focus our discussion on *linear* block codes. A block code *C* over a finite field  $\mathbb{F}_q$  is linear if *C* is a linear subspace of the vector space  $\mathbb{F}_q^n$ . Since *C* is a subspace of  $\mathbb{F}_q^n$ , there exists a set of vectors  $g_1, ..., g_k \in C$ , called the basis of *C*. Every code word in *C* can be written as a linear combination of these base vectors. Formally we can thus write

$$x \in C \Leftrightarrow x = \sum_{i=0}^{k} a_i * g_i$$

, where  $a_0, ..., a_k \in \mathbb{F}_q$ . (2.2)

The parameter k is called the dimension of C. Since every code word is generated by a unique linear combination of the base vectors (unique values for the scalars  $a_0, ..., a_k$ ), the code's size M is given by  $q^k$ . The parameters k and n are used to calculate the code rate R. This ratio basically measures the amount of actual information contained in a code word with respect to overall length of the code. Hence, it must always be a value smaller than or equal to one.

$$R = \frac{k}{n} \tag{2.3}$$

The value n - k is also referred to as the redundancy of the code.

The base vectors of C can be combined into the so called generator matrix G (Equation 2.4), which comprises k rows and n columns.

$$G = \begin{pmatrix} g_1 \\ \vdots \\ g_k \end{pmatrix}$$

(2.4)

Using this matrix the encoding function  $f : \mathbb{F}_q^k \mapsto \mathbb{F}_q^n$  can simply be defined by a matrix multiplication. As shown in Equation 2.5 the *k*-element row vector, representing the unencoded data word, is multiplied by *G* to generate the corresponding *n*-element code word (row vector).

$$f(x) = x * G \tag{2.5}$$

A code is completely specified by its generator matrix. If the generator matrix exhibits the form  $G = (I_k|A)$ , where  $I_k$  denotes the  $k \times k$  identity matrix then it is called *systematic*. Code words of systematic codes contain their corresponding (unencoded) data words as their first k elements, which can simplify the decoding process. This means that every element in such a code word is either a data or a check symbol, hence these codes are also called separable. Note that the check symbols are generated solely by the  $k \times (n - k)$  matrix A. If a linear code is not systematic it is always possible to transform it into an equivalent systematic code, i.e. a (different) code with the same properties.

Another very important matrix, that like the generator matrix, also completely defines a linear code is the parity-check matrix H. As shown in Equation 2.6 multiplying H with a transposed code word  $c^T$  yields the all zero vector iff c is a code word of C.

$$c \in C \Leftrightarrow H * c^T = 0 \tag{2.6}$$

This matrix can hence be used to perform error detection. A decoder can simply multiply the received code word with the parity-check matrix and check whether the result is zero. For systematic codes, the  $(n - k) \times n$  parity-check matrix can immediately be calculated from the generator matrix *G*.

$$H = (-A^T | I_{n-k}), \text{ if } G = (I_k | A)$$

(2.7)

A commonly used notation for linear block codes over  $\mathbb{F}_q$  with length *n*, dimension *k* and minimal distance *d* is  $[n,k,d]_q$ . To illustrate the presented concepts, consider the the following examples. Equation 2.8 shows two examples for generator matrices for the  $[5,4,2]_2$  parity and  $[7,4,3]_2$  Hamming code.

$$G_P = \begin{pmatrix} 1 & 0 & 0 & 0 & 1 \\ 0 & 1 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 & 1 \\ 0 & 0 & 0 & 1 & 1 \end{pmatrix} \quad G_H = \begin{pmatrix} 1 & 0 & 0 & 0 & 0 & 1 & 1 \\ 0 & 1 & 0 & 0 & 1 & 0 & 1 \\ 0 & 0 & 1 & 0 & 1 & 1 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 \end{pmatrix}$$

(2.8)

Both codes are systematic and encode 4 bits of information. The Hamming code offers a minimal distance of three, allowing the correction of one error or the detection of up to two errors. The parity code, on the other hand, is only able to detect single bit errors (correction is not possible). Note that the parity code's generator matrix  $G_P$  basically works for arbitrary field sizes. The 0 and 1 entries in the matrix simply have to be regarded as the zero and one-element of the particular field. Equation 2.9 shows the corresponding check matrices.

$$H_P = \begin{pmatrix} 1 & 1 & 1 & 1 & 1 \end{pmatrix} H_H = \begin{pmatrix} 1 & 1 & 0 & 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 1 & 0 & 1 & 0 \\ 0 & 1 & 1 & 1 & 0 & 0 & 1 \end{pmatrix}$$

(2.9)

In the next section another code class will be introduced, the so called unordered codes. These codes have a special property that makes them applicable to asynchronous circuit design.

#### 2.2 Asynchronous Circuits

Storage elements such as flip-flops or latches play a vital role in digital design. Without them it would not be possible to implement any state holding circuits such as state machines or pipelines. The fundamental problem that needs to be solved when constructing digital circuits is how to organize the transfer of data between those elements. To illustrate this problem, consider two storage elements (source and sink) connected back-to-back (i.e. the output of the first one is connected to the input of the second one). Now, for a data transfer to take place, there must be means to answer the following two questions.

- When is the source allowed to apply new data to its output?

- When is the sink allowed to consume the data at its input?

In [9] these two questions are referred to as issue and capture condition. Moreover, it is shown how different design styles approach and solve this problem.

The widely used synchronous design style uses a (global) clock signal that triggers both the issue and capture operation. This means that at the active clock edge every (enabled) storage elements consumes the data at its input (stores it internally) and applies the new data to its output. Because of this common time base, the synchronous design style offers a good abstraction and makes it relatively easy to design circuits. However, this abstraction is based on the assumption that the clock signal reaches all flip-flops of a design simultaneously. The low clock skew required to maintain this assumption is increasingly hard to maintain in modern semiconductor technology. This has led to the situation that the clock distribution network (i.e. the clock tree) of a chip now consumes a high portion (sometimes more than 25%) of the total power [10]. The maximal allowed clock frequency of a synchronous circuit is determined by the static timing analysis. A process that basically localizes the longest path (in terms of delay) between any two registers in a design, which is also referred to as the critical path. Obviously this value poses an upper bound for the maximal clock frequency a circuit can be operated with, because there must be enough time between two clock edges for all signals in a design to reach their destinations. However, to accommodate for PVT variations it is necessary to apply some safety margin to the delay of the critical path. If this value is chosen too pessimistic the circuit suffers a (maybe unnecessarily high) performance penalty. A margin that is too small may, on the other hand, have a negative impact on the yield of the chip. Note that another implication of the critical path is that a processing pipeline can only operate with the speed of the slowest stage.

Asynchronous circuits and design styles use local handshaking signals instead of a global trigger like the clock to coordinate the data transfer between storage elements. Here neighboring stages communicate locally to inform each other when the next data item is available and when the previous data item has been consumed. Because of this locality of control, asynchronous circuits don't suffer from many of the the problems inherent to the synchronous design style. This makes asynchronous design styles a worthwhile alternative in many application areas. Without the (global) clock net they are, for example, an interesting and promising approach for low power devices. The more flexible timing models allow for the design of very robust circuits with respect to PVT variations. It also makes sense to combine asynchronous and synchronous methodologies

in a single design to leverage the advantages of both worlds, which leads to the concept of GALS (Globally Asynchronous Locally Synchronous) circuits.

The remainder of this section is mainly based on [5], which provides an excellent introduction to the field of asynchronous circuits.

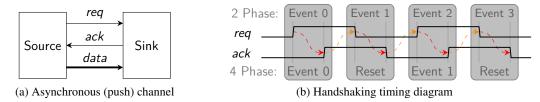

#### 2.2.1 Handshaking Protocols

All asynchronous circuits use some form of handshaking protocol to transfer data between storage elements. Depending one which component (source or sink) initiates the transfer push and pull channels can be distinguished. In a push channel, such as the one shown in Figure 2.1a, the source uses the request (*req*) signal to notify the sink that new data is available. After the sink has consumed the data it uses the acknowledgment (*ack*) signal to in turn notify the source that it is ready for new data. In a pull channel the sink requests new data from the source, hence the signal directions are reversed. However, since this work only uses push channels, we won't go into further details on this topic.

Generally the handshaking protocols, i.e. the actual sequence of transitions on the *req* and *ack* signals as well as their meaning can be classified as 2-phase or 4-phase. Figure 2.1b illustrates the difference between these two possibilities. In 4-phase protocols only two of the altogether four transitions involved in one handshaking cycle (hence the name 4-phase), carry actual meaning. The other two are only used to reset the handshaking signals to their initial values. The rising edge of the *req* signal is usually used as indicator for when the data is valid. Hence, when the *req* signal reaches the sink the data must already be stable at the sink's input.

The 2-phase protocol, on the other hand, does not incorporate an additional reset phase for the handshaking signals, which can lead to a performance advantage. Here every pair of transitions constitutes a complete handshaking cycle.

Figure 2.1: Asynchronous handshaking protocols

As we will see in Section 2.2.4.2 it is not always the case that the request mechanism is implemented by an explicit request signal. The request can also be implicitly encoded in the transmitted data and the receiver has to use a completion detector to decide whether the applied data can be consumed or if further transitions have to be awaited.

#### 2.2.2 Delay Models

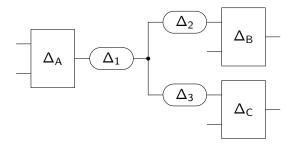

Asynchronous circuits can be classified on the basis of the delay assumptions imposed on them. The class of *delay-insensitive* (DI) circuits uses the weakest timing assumptions. The only

restriction on gate and wire delays is that they have to be positive and finite. For the example circuit, shown in Figure 2.2, this means that all gate delays  $\Delta_A$  to  $\Delta_C$  and wire delays  $\Delta_1$  to  $\Delta_3$  may be chosen completely arbitrary and the circuit would still work correctly. However, as shown by Martin [11], the class of circuits which can be constructed with this timing model is very small. This is because the only gates that can be used in DI circuits are inverters and C gates.

To overcome these limitations, isochronic forks [12] are introduced, leading to the class of *quasi-delay-insensitive* (QDI) circuits. With this extension to the DI timing model, arbitrary circuits can be constructed. While there are effectively no restrictions on the delays in DI circuits, QDI circuits require that (some selected) wire forks are isochronic, i.e. both signal paths after the fork must have the same delay. For the circuit in Figure 2.2 this means that  $\Delta_2 = \Delta_3$ . A detailed discussion of isochronic forks is given in [11].

Figure 2.2: Asynchronous circuit model

For the class of *speed-independent* (SI) circuits, we again have arbitrary gate delays, however the wire delays are assumed to be zero ( $\Delta_1 = \Delta_2 = \Delta_3 = 0$ ). Obviously, this timing model is the least realistic one, since interconnect delays play an important (and sometimes even dominating) role in modern chip technology. However, if the forks are regarded as isochronic, it is possible to combine the wire delays with the delay of the gate driving the wire (e.g. add  $\Delta_1$  and  $\Delta_2$  to  $\Delta_A$ ), which again yields a QDI circuit.

Finally we also want to mention the term *self-timed* (ST) circuits. The other models presented so far are precise (mathematical) concepts and apply to the gate-level of asynchronous circuits. ST circuits is a more general term and refers to circuits that need higher-level timing constraints or assumptions to work as intended. Such an assumption can for example state that the result of a certain (sub-) circuit must be available before another signal reaches its destination. These constraints are often enforced by the use of delay elements.

#### 2.2.3 Asynchronous Circuit Primitives

Before it is possible to discuss the implementation level aspects of asynchronous circuits, some basic circuit primitives must be introduced.

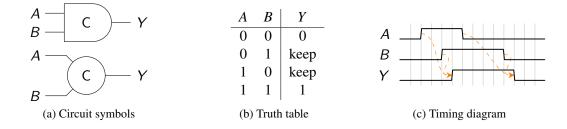

#### 2.2.3.1 Muller C-Element

A very basic gate found in nearly every asynchronous circuit is the Muller C-Element (henceforth simply referred to as C gate). Figure 2.3a shows the symbols that are commonly used for this

gate. In simple terms its operation can be described as an AND gate with hysteresis. As shown in the truth table in Figure 2.3b, in order to set the output of a C gate to one, both inputs must be set to one (similarly to an AND gate). However, to reset the output back to zero again, both inputs must be set to zero as well. If only one input changes its logical value the output of the gate does not change ("keep" entries in the truth table). Figure 2.3c further illustrates this behavior with a simple timing diagram. To implement this functionality the C gate obviously needs an internal storage to keep track of its current state.

Figure 2.3: Muller C-Element

There are basically three popular ways to implement the C gate in CMOS logic. Since a detailed discussion on the implementation details would go beyond the scope of this work, we refer to [13], which presents the different CMOS circuits and compares their advantages and disadvantages.

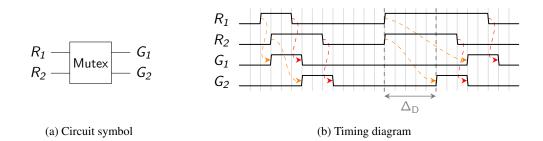

#### 2.2.3.2 Mutex

The other important component, we briefly want to present here, is the Mutex. As shown in Figure 2.4a it has two inputs ( $R_1$  and  $R_2$ ) and two outputs ( $G_1$  and  $G_2$ ). A rising edge (i.e. request) on one of the inputs is acknowledged (i.e. granted) by a rising edge on the associated output. The output is kept asserted until the input goes low again. The purpose of this component is to provide mutual exclusion for input requests. Thus at any given time at most one of its outputs can be asserted. This behavior is illustrated in the timing diagram in Figure 2.4b. In the left part of the figure there is a clear difference in the arrival times of the input requests. Hence  $R_1$  will be granted first and  $R_2$  has to wait until the first request is withdrawn. The right part shows what happens when both requests arrive virtually simultaneous. Similarly to the case in synchronous circuits when the clock and data edge arrive too close to each other at the inputs of a flip-flop, also the Mutex can go into a metastable state, where it is unable to decide which input request should be granted first. Like with flip-flops the result of this metastability can be a late transition on the output. However, unlike flip-flops, the outputs of a Mutex will not go into an undefined voltage range but rather both stay low until the metastability has been resolved. Note that this time period (marked  $\Delta_D$  in the timing diagram) can be arbitrary long.

Figure 2.4: Mutex

#### 2.2.4 Pipeline Implementations

There are various ways to use the protocols discussed in Section 2.2.1 to implement pipelined circuits. However, before we can discuss the implementation details of the different pipeline styles, we first need to introduce a very basic asynchronous circuit.

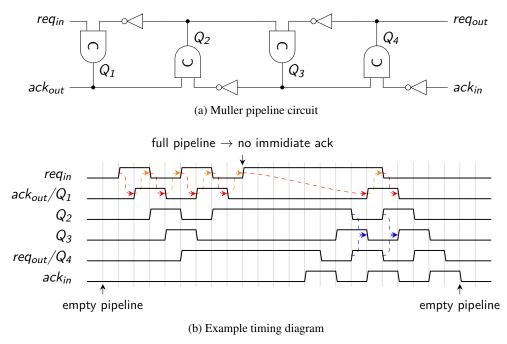

Figure 2.5a shows the Muller pipeline, as presented in [14]. Basically, the purpose of this circuit is to store and transport handshakes from its input ( $req_{in}$ ,  $ack_{out}$ ) to its output port ( $req_{out}$ ,  $ack_{in}$ ). To understand how it works consider the timing diagram in Figure 2.5b. For this diagram it is assumed that initially all C gates are set to zero and that the C gate and the inverter have a combined delay of one time unit. The circuit operates according to a very simple rule. Every C gate (i.e. stage) changes its output  $Q_i$  if  $Q_{i-1}$  and  $Q_{i+1}$  differ in value. Hence a C gate forwards a one from the preceding stage if the succeeding stage is zero (and vice versa for zeros). This behavior is highlighted for  $Q_3$  by (blue) arrows in the timing diagram. As the pipeline is initially empty the first rising transition on  $req_{in}$  can immediately ripple through the whole circuit until it appears at the output  $req_{out}$ . The input handshakes, as produced by the environment of the circuit, are marked with arrows. The following transitions on  $req_{in}$  fill up the pipeline. A full Muller pipeline can be identified by alternating logical states in each C gate. Notice that the full pipeline does not provide an acknowledgment for the last rising input transition at  $req_{in}$ . The input transitions can be viewed as waves traveling through the circuit. In the second half of the diagram the environment toggles the  $ack_{out}$  input to "read out" the stored transitions.

The Muller pipeline by itself is not a very useful circuit. However, it is nevertheless very important as it is an often reoccurring structure in asynchronous designs and forms the (basic) control circuit for many pipelines. In the next section, we will see how the Muller pipeline is basically everything that is needed to control the data flow though an asynchronous (bundled data) pipeline.

Finally it is important to stress that this circuit is in principle completely agnostic to the handshaking protocol. As can be seen in the timing diagram it is only a matter of interpretation if the input transitions form a 2-phase or 4-phase handshake. Moreover, notice that since the Muller pipeline is only built from C gates and inverters it is one of the few really DI circuits.

Figure 2.5: Muller pipeline

#### 2.2.4.1 Bundled Data Pipelines

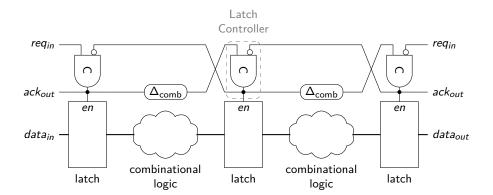

Figure 2.6 shows an example for an asynchronous 4-phase bundled data (BD) pipeline. Notice the control structure that generates the enable signals for the data latches. Except for the delay elements, it resembles the Muller pipeline from Figure 2.5. The purpose of the delay elements is to ensure that the request signals reach the next stage only after the associated data is stable and valid at the input of the latches. Since the data usually passes some combinational logic the delay element has to be tuned to the critical path of this circuit. This is why these circuits are also referred to as matched delay pipelines. Notice that in contrast to synchronous circuits a slow path between two storage elements only affects the delay (i.e. performance) of the associated stage and does not necessarily have an impact on the overall circuit. It is even possible to make the delay element data dependent (i.e. multiplex between different delays) to optimize the performance for different use cases.

Recall that a full Muller pipeline stores alternating values in its C gates. This means that if the presented pipeline becomes full, only every second latch contains data (the other latches are transparent). Note, however, that there is a similar situation with the master and slave latch of a flip-flop in synchronous pipelines.

There are a lot of different pipeline styles that can be found in literature. The original way to utilize the Muller pipeline as proposed by Sutherland in [14] was to use the 2-phase protocol in combination with special capture/pass registers. Another interesting approach is the MOUSETRAP pipeline proposed by Singh et. al [15], which uses XOR gates instead of C gates to implement the latch controllers. Another approach, aimed at increasing the degree of

Figure 2.6: 4-Phase bundled data pipeline

decoupling between stages in 4-phase pipelines was proposed by Furber et. al. [16]. This paper uses Signal Transition Graphs (see Section 2.2.5) to model and implement more sophisticated latch controllers (compared to the single C gate in Figure 2.6), that ultimately also allow for a pipeline to fill up all its stages.

A data item that travels through a pipeline is often referred to as data token. An empty place in a pipeline is called a bubble. Data tokens travel in forward direction through a pipeline and replace bubbles, which hence move backwards. This means that a functional asynchronous pipeline always needs at least one bubble for data tokens to move to. A pipeline ring without bubbles is deadlocked.

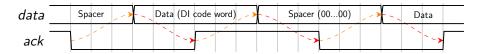

#### 2.2.4.2 4-Phase Delay-Insensitive Codes

In contrast to the bundled data circuits discussed in the previous section 4-phase (or return-to-zero) DI circuits don't use an explicit request signal. The request is rather implicitly encoded in the transmitted data and it is the responsibility of the receiver to decide when this data is complete (i.e. valid) and can thus be consumed. This process is referred to as completion detection and is only possible if the code that is used to encode the transmitted data has certain properties. Two successive code words (data phase) are always separated by a spacer (zero or null phase), which does not carry any information and is usually encoded by logical zeros on all bus wires. Figure 2.7 shows a timing diagram of the 4-phase protocol. Note that the arrival times of the transitions on

Figure 2.7: 4-Phase DI protocol

the individual bus wires, also referred to as rails, at the receiver are unknown and don't matter for the correct operation of the protocol. The fact that it is not necessary to impose any timing assumption (except for some isochronic forks) on QDI circuits makes them very robust against (PVT) variations. The completion detector (CD) at the receiver is attached to all data rails and has exactly one output, which will be referred to as the *done* signal throughout this thesis. As soon as the bit pattern on the data rails forms a complete (i.e. valid) code word the *done* output is asserted. The signal is then kept asserted until the CD detects the spacer word.

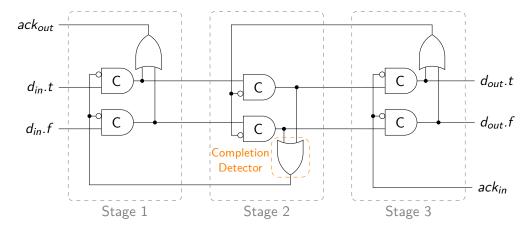

The simplest DI code is the dual rail (DR) encoding, which is widely used for asynchronous circuit design. As the name suggests the DR code uses two rails to encode one bit of information. In the data phase of the 4-phase protocol exactly one of the two rails makes a transition to one. The CD for a DR bit can thus be implemented by a simple OR gate. The individual wires of a DR bit are also referred to as the true and false rail. Figure 2.8 shows a three stage one bit DR pipeline. Notice that this pipeline can also be viewed as two interlocked Muller pipelines.

Because of its simplicity and the systematic encoding it is also possible to perform logical operations on DR encoded data, although with a lot more overhead than with combinational logic in synchronous or BD designs. The simplest, but also most expensive (in terms of area overhead) is the Delay Insensitive Minterm Synthesis (DIMS) [17]. DIMS uses an array of C gates to exclusively map every possible (valid) input data word to a dedicated signal (one-hot code). In a second stage OR gates map this code to the desired output signals. The actual logical function depends only on these OR gates. Note that, despite the name, circuits obtained by applying this design style are only QDI. The forks in the input rails which are used to connect the inputs to the C gate stage must be isochronic. Further note that the DIMS design style is not restricted to function blocks operating on DR coded data and can in principle be applied to every 4-phase DI code. In particular it can also be used to construct CDs for arbitrary DI codes.

A more efficient design style was proposed by Theseus Logic [18], with the disadvantage of requiring special threshold gates. Another very efficient approach was proposed in [19], which has the big advantage of requiring only standard gates. Note that we don't use the term combinational logic for these types of functions blocks because the 4-phase protocol requires this logic to contain storage elements (i.e. C gates), to keep track of the current protocol phase.

Figure 2.8: Single bit dual rail pipeline (3 stages)

Clearly the DR encoding is not the only DI code. The DR code is basically one representative of the class of constant-weight (m-of-n) codes, which are all DI. Other examples are Berger and

Zero-Sum codes, which will be presented in more detail in Section 3.2.

In the following we will discuss the mathematical properties that make a code DI. Verhoeff [4] shows that a DI code has to be unordered.

**Definition 4** (Unordered Bit Vectors). Let  $x = (x_0, ..., x_{n-1})$  and  $y = (y_0, ..., y_{n-1})$  be two bit vectors of length n. Further let  $S_x = \{i|x_i = 1\}$  and  $S_y = \{i|y_i = 1\}$  be two sets that only contain the bit positions where the associated vector is one. The bit vectors x and y are unordered iff  $S_x \notin S_y$  and  $S_y \notin S_x$ . If  $S_x \subset S_y$  we say that y covers or contains x, denoted by  $x \leq y$ .

The sets  $S_x$  and  $S_y$  in Definition 4 are referred to as the support of x and y [20]. Note that the term unordered bit vectors comes from the relation of these two sets. If there can be established an *order* between the support  $S_x$  and  $S_y$  (i.e. one is a subset of the other) then the associated bit vectors cannot be unordered.

**Definition 5** (Unordered Code). A code *C* is unordered iff every pair of code words  $x \in C$  and  $y \in C$  ( $x \neq y$ ) is unordered (i.e.  $x \not\leq y$  and  $y \not\leq x$ ).

From this definition the following theorem immediately follows.

## **Theorem 1.** The minimal Hamming distance $(d_{min})$ between any two code words in an unordered code is two.

*Proof.* Assume that there exist two code words  $c_1$  and  $c_2$  in some unordered code C with a Hamming distance of one. Hence in order to transform  $c_1$  into  $c_2$  one must either change a one in  $c_1$  to a zero or a zero into a one. For the first case this would mean that  $c_1$  is contained in  $c_2$  and vice versa for the latter case. However, now we arrive at a contradiction because if code words are contained in one another C cannot be unordered.

A very important property of DI codes is that the result of their (bit wise) inversion as well as concatenation is again DI. The size of a concatenated code, i.e. the number of representable symbols, is obtained by multiplying the sizes of the individual codes. Completion detection is then performed separately on the individual (sub-)codes and the results are joined by a C gate.

There are many properties to analyze when assessing the quality of a DI code. If function blocks should operate on the encoded data (e.g. in a 4-phase QDI processor) then the DR code is generally the only viable option. Other DI codes are, with some exceptions [21], not well suited for this task but are rather only used to transmit information in a DI fashion. This is because more sophisticated codes often have some desirable properties with regard to data transmission. When transmitting data a high coding efficiency and a low (dynamic) power consumption are of interest. As already discussed in Section 2.1 the coding efficiency *R* relates the number of bits encoded by a certain code word to the total number of rails required to transmit it. To minimize dynamic power during a transmission the number of transitions in the data phase should be kept as low as possible. This code property is captured by the power metric *P* which specifies the number of transitions required to transmit one bit of data. For the DR code *R* = 0.5 bits/rail and *P* = 2 transitions/bit. Note, however, that there is a certain trade-off between these two parameters *P* and *R*. The 1-of-16 code has, for example, a rather low coding efficiency (*R* = 0.25), while requiring only two transitions to transmit four bits of information (*P* = 0.5). The 3-of-6 code, on

the other hand, has a far better coding efficiency (R = 0.66) but requires six transitions for the same amount of information (P = 1.5).

Other very important properties of DI codes are the overhead for completion detection as well as for encoding and decoding to and from e.g. the binary representation of the data. There are several publications proposing and discussing efficient CD designs [22, 23, 3, 24].

#### 2.2.4.3 2-Phase Delay-Insensitive Codes

For the sake of completeness we also want to briefly mention 2-phase DI codes. As shown in Figure 2.9, these protocols don't use a spacer to separate the data phases, which can obviously lead to a performance gain. However, there are of course also some drawbacks associated with these protocols. Generally, the required CDs as well as the encoder and decoder circuits are more complex and have a higher overhead than for 4-phase codes.

Figure 2.9: 2-Phase DI protocol

Basically, 2-phase protocols can be classified as transitional or level encoded. Using transitional encoding only signal transitions (rising and falling) transmit information. They actual state of the rails does not carry any information. Hence, here the notion of code words is a little different when compared to 4-phase codes, were a code word basically referred to a certain state of the data rails. Notice that a 4-phase code word can also be defined by the subset of rails that need be one. With this definition in mind, a 2-phase transitional code word can be defined as the subset of rails that need to make a transition. Hence, every DI code (in the sense of Definition 5) can be used for a 2-phase transitional protocol. Because of this similarly it also possible to adapt 4-phase CDs for transitional encodings [24].

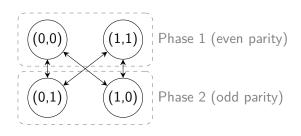

Level encoded protocols like Level Encoded Dual Rail (LEDR) and Level Encoded Transition Signaling (LETS) [25] use a different approach to separate two successive data phases. Here the set of code words is divided into two groups, where each of these groups is assigned a phase. The protocol then alternates between code words of these two phases. This means that there are always two code words that convey the same logical information.

LEDR or FSL (Four State Logic) use two rails (data and parity) to encode one bit of information. The data rail carries the binary representation of the transmitted information, while the parity is used to indicate the current phase. Figure 2.10 shows a state chart of the encoding scheme. Note that only one rail (data or parity) toggles its logical value per phase. The states on the left encode logical zeros and while the states on the right encode logical ones. Note that the CD for a single LEDR bit can be implemented by an XOR gate.

Further details on 2-phase coding schemes can be found in [25]. Furthermore, [26] provides a brief comparison of different 2-phase and 4-phase coding schemes.

Figure 2.10: LEDR/FSL state chart

#### 2.2.5 Control Circuit Synthesis

Control circuits play an important role in asynchronous circuits design. This section will briefly discuss a process that can be used to automatically create these circuits from a more abstract specification.

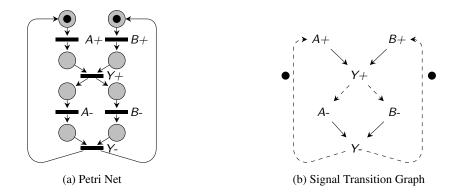

Consider the example of a Muller C gate. The timing diagram of Figure 2.3c, describing the behavior of the C gate, can also be formalized in a Petri net (PN), which is shown in Figure 2.11a. Basically a PN is a directed graph that can be used to model concurrent systems. It consists of places (gray circles) and transitions (black bars). The PN is "executed" as tokes flow through it. Tokens (black circles) are stored in places. A transition can fire if there are tokens on all its inputs. If that is the case the tokens are removed from the inputs and placed at the outputs of the transition.

Figure 2.11: C gate specifications

An STG is a special PN, where some restrictions apply. Here the transitions model real signal transitions and the edges of the graph basically indicate the causal and temporal order of these events. For a PN to be a meaningful STG it must be free from deadlocks, never have more than one token in a place and the signal transitions must strictly alternate between rising (+) and falling (-) transitions. Moreover, it must be guaranteed that once a transition is enabled it must fire, i.e. it may not be disabled again by another signal transition. All these restrictions as well as "input free choice" (not presented here) are discussed in more detail in [5].

For STGs, such as the one in Figure 2.11b, the places are not explicitly drawn. Every edge can be considered to contain a place. The initial state is indicated by the tokens on the appropriate edges.

Note that the STG (as well as the PN) also has to model a (well-behaved) environment of the circuit. In the example at hand the environment simply sets both inputs when the output of the C gate is zero and resets them when the output is one. By convention we draw transitions that must be fulfilled by then environment with dashed lines.

The advantage of STGs over PNs is that they can automatically be converted into (speedindependent) circuits. For this task tools like Petrify [27] or Workcraft [28] can be used. Workcraft is particularly interesting since it provides a graphical front-end to Petrify and also offers STG and circuit editors.

#### 2.3 Fault Tolerance and Delay-Insensitive Codes

This section first introduces important concepts and terminology regarding the field of fault tolerance and dependable computing. After establishing this basis we then take a closer look at how faults affect delay-insensitive communication systems and how to deal with them.

#### 2.3.1 Introduction and Terminology

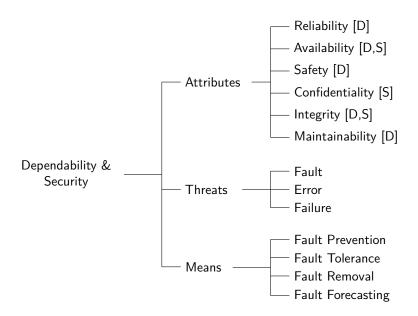

Avizienis et. al. define dependability in the following way [29]. Dependability of a system is the ability to avoid service failures that are more frequent and more severe than is acceptable.

Figure 2.12 shows an overview of the different aspects of dependability as well as security. These concepts can be characterized with respect to the *attributes* a system (or service) must provide, *threats* to these attributes and *means* to uphold (correct) operation and avoid failures despite the presence of these threats. Note that although security and dependability are related concepts their main priorities lie on different aspects (i.e. attributes). This fact is indicated by the letters D and S in Figure 2.12. Detailed definitions for these attributes can be found in [29].

The terms fault, error and failure have a certain, well-defined relation to each other. A failure is the transition of a system that delivers a correct (i.e. intended) service to a state where this service is no longer provided or provided in an incorrect way. Failures are caused by errors. An error refers to an unintended system state, e.g. an erroneous value in the register file of a processor. If the processor uses this value in a subsequent instruction the system may exhibit a failure (e.g. a deadlock). Errors are in turn caused by faults. Faults can be classified as internal or external to a system. However, for an external fault to cause an error there must already be an associated internal vulnerability (i.e. fault) present in the system. Furthermore, we can distinguish between transient and permanent faults. Permanent faults are caused by physical damage to a system (e.g. a stuck-at fault in a digital circuit) and cannot be recovered without physical repair. Transient faults have, as the name suggests, only temporary effects on a system and thus also disappear without active intervention. An error is the manifestation of a fault in a system's state. This event is referred to as fault activation. Note that a failure of a subsystem can cause a fault on higher system level.

Figure 2.12: Dependability and security tree [29]

Transient faults in integrated circuits, which are the main focus of this thesis, are mainly caused by external sources. These include for example radiation effects, electromagnetic interference, electrostatic discharge, supply voltage drops and temperature changes. Due to the aggressive technology scaling in recent years, semiconductors became especially sensitive to radiation-induced faults [6]. Radiation, i.e. ionized particles hitting a circuit, can cause an unintended (short) voltage pulse on the affected node of the circuit. This pulse is referred to as Single Event Transient (SET). The situation where a SET directly hits a storage element and (directly) changes its state or causes an erroneous value at some other node of a circuit that is then captured by a storage element is referred to as Single Event Upset (SEU) or soft error. However, note that, due to temporal, logical or electrical masking not every SET may necessarily result in a soft error.

Figure 2.12 also lists the means that can be applied to mitigate faults or the effects thereof. In this thesis the concept of fault tolerance is used. However, this does not mean that arbitrary faults can be tolerated. The *fault hypothesis* exactly defines which types of faults a system can cope with and how many are to be expected within certain amount of time. Detailed discussion of the other concepts can again be found in [29].

#### 2.3.2 Transient Faults and Delay-Insensitive Communication

As already discussed in Section 2.2.4.2, there are no assumptions on signal delays in (4-phase) DI communication schemes. Transitions of the individual rails of a DI bus may arrive at the receiver in any order and a CD is used to decide whether the input bit pattern is a valid (i.e. complete) code word or if further transitions have to be awaited.

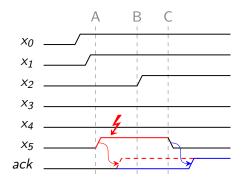

The fact that a single transition, if considered as the last one, completes a transmission, makes DI codes specially prone to (single) faults. To illustrate this problem, consider the example transmission of a 3-of-6 code word shown in Figure 2.13.

Figure 2.13: Transmission faults on a DI communication link

First two valid transitions happen on the rails  $x_0$  and  $x_1$ . Hence, only one transition is missing to complete a 3-of-6 code word. At *A* a transient fault strikes, which causes rail  $x_5$  to go high and completes the code word. Without further information the receiver is not able to identify this error and may erroneously and prematurely assert the *ack* signal (dashed line). After the last valid transition happens on rail  $x_2$  (*B*) the code word becomes invalid and the receiver would (theoretically) be able detect that something went wrong. At *C* the transient fault vanishes and the correct code word emerges at the receiver's input. Hence, in our proposed approach (presented in Chapter 4) the receiver will be provided with just enough redundant information to detect that a transmission was affected by transient faults and to delay the *ack* signal to the point in time where all faults have vanished.

Another challenge that arises with DI codes is how the encoded data is affected by faults. Assume that the fault-free code word 111000 is mapped to the data word 0000 and the erroneous code word 110001 is mapped to 1111, then a single transient fault caused a quadruple bit error in the encoded data. This example demonstrates that the mapping of code words to data words is critical and that special care must be taken, when constructing fault-tolerant DI communication systems.

To characterize and reason about the fault resilience of DI codes the next section presents a graph theoretical approach to model their, rather unique, fault behavior.

#### 2.3.3 Safe Overlap Graph

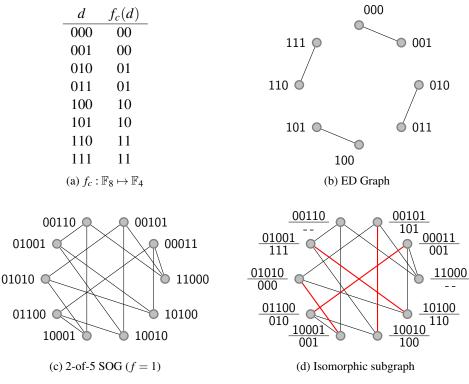

In [30] Lechner et. al. present a comprehensive analysis on how transient faults can affect the transmission of 4-phase DI code words. In the following we discuss these concepts in extended detail, because they are essential to the proposed coding scheme.

The Safe Overlap Graph (SOG) offers a compact way to characterize the fault resilience of a DI code. However, before the SOG can be defined formally, the notion of overlapping code words must be introduced (Definition 6).