master thesis is available at the main library of Vienna University of Technology. http://www.ub.tuwien.ac.at/eng

FAKULTÄT FÜR INFORMATIK

**Faculty of Informatics**

# Reliable devices for safe communication in networks

## DIPLOMARBEIT

zur Erlangung des akademischen Grades

# Diplom-Ingenieur

im Rahmen des Studiums

## Technische Informatik

eingereicht von

## Markus Klein

Matrikelnummer 0726101

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Wolfgang Kastner Mitwirkung: Univ.Ass. Dipl.-Ing. Dr.techn. Lukas Krammer, Bakk.techn.

Wien, 29.09.2015

(Unterschrift Markus Klein)

(Unterschrift Betreuung)

# Erklärung zur Verfassung der Arbeit

Markus Klein Spaunstraße 101, 4020 Linz

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit - einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Markus Klein)

# Danksagung

"Manch Ding braucht viel Weile" und so hat sich auch die vorliegende Master-Arbeit über einen viel zu langen Zeitraum erstreckt. Diese Zeit, geprägt von universitärer und außeruniversitärer Arbeit, in der die eigene Master-Arbeit nur allzu oft liegen blieb und das wissenschaftliche Arbeiten aus den täglichen Gedanken verdrängte, war von vielen Tiefen durchwachsen, wie keine andere Zeit in meinem bisherigen Leben. So manchen Selbstzweifel galt es zu überwinden und Motivation zu finden, war wahrlich nicht leicht. Trotz allem habe ich mein Ziel diese Arbeit zu einem Abschluss zu bringen, nie aufgegeben.

Dies alleine zu bewerkstelligen, wäre allerdings ein Ding der Unmöglichkeit gewesen.

Ich bedanke mich daher aufrichtigst bei meinen Eltern, die mich über die lange Zeit des zähen Werdens dieser Arbeit, aber auch im gesamten bisherigen Lebensweg, in allen Belangen immer unterstützt haben und mir, mit weisen Worten und aus eigener Erfahrung sprechend, immer wieder Mut gemacht haben und immer an mich geglaubt haben. Leider gelang es mir nicht immer die Hilfestellungen in jenem Maß anzunehmen, wie es notwendig gewesen wäre.

Danke, dass ihr mich meinen Weg gehen habt lassen und immer als Wegweiser zur Verfügung standet, wenn ich ihn brauchte.

Ich danke meiner lieben Katharina für das Durchhaltevermögen und das Verständnis für meine so zahlreichen Stunden und Abende, die ich vor dem Computer für meine Vielzahl an Tätigkeiten zubrachte. Danke, dass du mich trotzdem immer wieder in die Arme schließt und mit mir den Weg gehst.

Ein großes Dankeschön geht an meine Betreuer Lukas Krammer und Wolfgang Kastner, die trotz dieser langen Zeit und den vielen Pausen nicht müde geworden sind, meine Arbeit zu einem guten Ende zu begleiten.

Schlussendlich möchte ich meinen Freunden Johannes und Gerald für ihr Entgegenkommen danken. Den Freiraum und das Vertrauen zu bekommen, neben den gemeinsamen Projekten noch seine Ausbildung unterzubringen, ist nicht selbstverständlich. Aus unseren erfolgreichen Projekten konnte ich immer wieder positive Energie schöpfen.

Vielen Dank! Markus

# Abstract

Embedded systems are part of our daily life and they pervade almost all areas of living. Mobile phones, cars, debit cards, medical equipment, energy meters and the intelligent fridge are just a few examples. These embedded systems also come in a variety of designs, from tiny single chip applications to wide-spread distributed solutions.

All these systems have one thing in common - some may call it even a requirement - they have to be able to communicate. Communication is the key-factor, no matter if this communication happens within a system or with other connected systems or even with the environment. Integration is getting tighter and tighter in any case and demand for even more integration is never ending.

Another demand these systems share is the fact that those system are getting cheaper. Obviously, the manufacturers of these systems have to reduce costs, with the consequence that safety-margin in the production are reduced to save material. This results mostly in less lifetime of products and also error-proneness is rising. The overall reliability is therefore getting worse.

A small part of those networked embedded systems though plays a special role. These are those systems which actually care about human safety. Typically those safety systems are not very visible to the average person as they work rather in the background. They are to be found in cars, airplanes, the processing-industry or the fire-safety domain. Clearly, this special role implies some additional requirements those systems have to fulfil.

This thesis takes a closer look at communication and reliability of such safety-critical embedded systems, taking the fire-safety domain as a reference use case. System requirements within this domain combine all properties mentioned above in a special way: frequent communication over longer distances, low-priced hardware, but high reliability demands.

The thesis suggests a combined software- and hardware-framework, which improves reliability (and therefore also communication) of the devices in smaller embedded systems, which are connected in a larger network while keeping the necessary hardware costs low. The requirements in the fire-safety domain are regulated in various standards, which will be explained and used to describe the challenge of constructing such systems.

# Kurzfassung

Embedded Systems sind aus unserem täglichen Leben nicht mehr wegzudenken. Sie durchdringen beinahe sämtliche Bereiche unseres Lebens. Mobiltelefon, Auto, Bankomatkarte, Herzschrittmacher, Smartmeter und der intelligente Kühlschrank sind nur einige Beispiele. Diese embedded Systems sind in einer Vielfalt an Ausprägungen zu finden, von kleinen Einzel-Chip Anwendungen bis zu weiträumig verteilten Lösungen.

Alle diese Systeme haben eine Sache gemeinsam - manche würden es sogar eine Voraussetzung nennen: sie müssen in der Lage sein zu kommunizieren. Kommunikation ist ein Schlüsselfaktor, unabhängig davon, ob diese Kommunikation innerhalb eines Systems stattfindet oder ob mit anderen Systemen oder sogar mit der Umwelt kommuniziert wird. Die Integration wird jedenfalls immer dichter und dichter, und die Nachfrage nach mehr Integration steigt stetig.

Eine Eigenheit, die diese Systeme teilen, ist die Tatsache, dass sie immer billiger werden sollen. Notwendigerweise müssen Hersteller solcher Systeme daher Kosten einsparen, mit der Konsequenz, dass der Sicherheitszuschlag in der Produktion zunehmend geringer wird, um Material zu sparen. Daraus resultiert meist eine geringere Lebenszeit dieser Produkte, aber auch die Fehleranfälligkeit steigt. Daher nimmt die Zuverlässigkeit ab.

Ein kleiner Teil dieser embedded Systems spielt eine spezielle Rolle. Das sind jene Systeme, die für die Sicherheit von Menschen sorgen. Typischerweise sind solche Systeme im Normalfall für den Durschnittsbürger nicht sonderlich sichtbar, da sie eher im Hintergrund arbeiten. Solche Systeme lassen sich in Autos, Flugzeugen, der Prozess-Industrie oder im Brandmelde-Bereich finden. Naheliegend ist daher auch, dass solche Systeme zusätzliche Anforderungen erfüllen müssen.

Die Arbeit fokussiert auf die Kommunikation und Zuverlässigkeit von Geräten in solchen sicherheitskritischen embedded Systems, wobei der Feuersicherheits-Bereich als Referenz-Beispiel herangezogen wird. Die Systemvoraussetzungen aus diesem Bereich kombinieren alle zuvorgenannten Eigenschaften auf spezielle Weise: häufige Kommunikation über längere Distanzen, günstige Hardware, aber hoher Zuverlässigkeitsbedarf.

Diese Arbeit stellt eine kombinierte Software- und Hardware-Grundstruktur vor, die die Zuverlässigkeit (und damit auch die Kommunikation) von Geräten in kleineren embedded Systems verbessert, die in einem größeren Netzwerk miteinander verbunden sind und dessen Hardwarekosten niedrig sind. Die Anforderungen im Feuersicherheits-Bereich sind in mehreren Normen geregelt, die vorgestellt und verwendet werden, um die Herausforderungen der Konstruktion solcher Systeme zu beschreiben.

# Contents

| 1 | Intr                                            | oduction 1                       |  |  |  |  |  |

|---|-------------------------------------------------|----------------------------------|--|--|--|--|--|

|   | 1.1                                             | Definition of safety             |  |  |  |  |  |

|   | 1.2                                             | Target application domain    3   |  |  |  |  |  |

|   | 1.3                                             | Problem statement and motivation |  |  |  |  |  |

| 2 | Standard specifications 7                       |                                  |  |  |  |  |  |

|   | 2.1                                             | EN 54                            |  |  |  |  |  |

|   | 2.2                                             | IEC 61508                        |  |  |  |  |  |

|   | 2.3                                             | Other standards                  |  |  |  |  |  |

| 3 | Functional safety - state of the art methods 19 |                                  |  |  |  |  |  |

|   | 3.1                                             | Definition of terms              |  |  |  |  |  |

|   | 3.2                                             | Hardware methods                 |  |  |  |  |  |

|   | 3.3                                             | Approaches for fault detection   |  |  |  |  |  |

|   | 3.4                                             | Software architecture            |  |  |  |  |  |

|   | 3.5                                             | Other concepts                   |  |  |  |  |  |

|   | 3.6                                             | Applications for fieldbuses      |  |  |  |  |  |

| 4 | Con                                             | cept 33                          |  |  |  |  |  |

|   | 4.1                                             | Requirements analysis            |  |  |  |  |  |

|   | 4.2                                             | Proposed model                   |  |  |  |  |  |

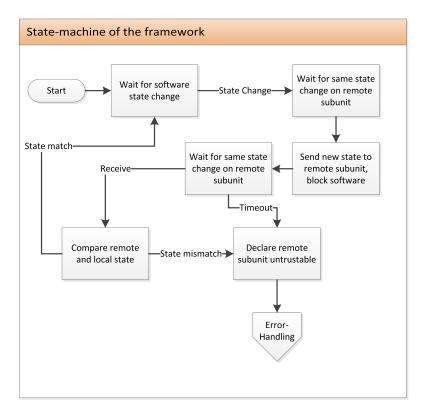

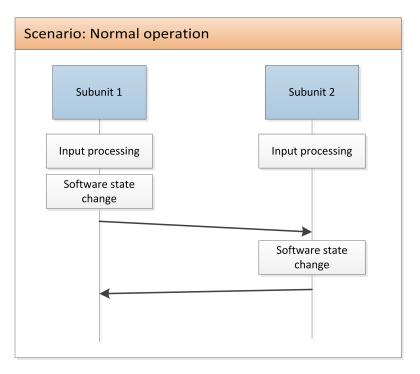

|   | 4.3                                             | Behavior of the framework        |  |  |  |  |  |

|   | 4.4                                             | Booting the CIE                  |  |  |  |  |  |

|   | 4.5                                             | Shut down of a subunit           |  |  |  |  |  |

| 5 | Results 47                                      |                                  |  |  |  |  |  |

|   | 5.1                                             | Analysis of the concept          |  |  |  |  |  |

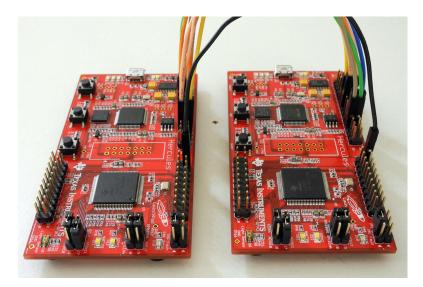

|   | 5.2                                             | Proof of concept                 |  |  |  |  |  |

|   | 5.3                                             | Evaluation                       |  |  |  |  |  |

| 6 | Conclusion 65                                   |                                  |  |  |  |  |  |

|   | 6.1                                             | Lessons learned                  |  |  |  |  |  |

|   | 6.2                                             | Outlook                          |  |  |  |  |  |

| Acronyms        | 71 |

|-----------------|----|

| List of Figures | 72 |

| List of Tables  | 73 |

| Bibliography    | 75 |

# CHAPTER

]

# Introduction

The human need for safety and security shows its characteristics more than ever. Feeling safe and secure is a salving mood and tends to relieve many sorrows, although it is obvious that a 100% safety and security can never be achieved. Safety is also always coupled with trust. One has to trust a system for being and feeling safe, but nothing is worse than being lulled into a false sense of safety and security.

Safety can have a variety of forms, such as:

- The safety of a tether

- The safety of driving a well constructed vehicle

- The safety of a machine to not cause harmful accidents

- The safety of governmental protection through police or military

## **1.1 Definition of safety**

The Oxford Dictionary defines safety as:

The condition of being protected from or unlikely to cause danger, risk, or injury.

Wikipedia extends this definition and defines safety as:

Safety is the state of being "safe" (from French *sauf*), the condition of being protected against physical, social, spiritual, financial, political, emotional, occupational, psychological, educational or other types or consequences of failure, damage, error, accidents, harm or any other event which could be considered nondesirable. Safety can also be defined to be the control of recognized hazards to achieve an acceptable level of risk. This can take the form of being protected from the event or from exposure to something that causes health or economical losses. It can include protection of people or of possessions. [4]

Naturally, institutions with focus on a certain area of expertise have a slightly more selective view on safety. The International Electrotechnical Commission (IEC), for instance, defines the term safety in a way that is clearly targeted for the Functional Safety Standard and its strong relationship to risk assessment:

Freedom from unacceptable risk of physical injury or of damage to the health of people, either directly, or indirectly as a result of damage to property or to the environment. [19]

Safety is therefore a relative term. It may even depend on the perception if somebody feels safe or not. Each of the definitions above clearly relaxes the strong term by adding phrases of "likeliness" and "risk".

Because safety is such a fundamental topic in human life, it is reasonable that today's technical applications have to be checked on their impact on safety. For many areas, there are regulations and standards that set a lower bound to what is required for an application in regards to functional safety. The standards are updated in rather short intervals and additional standards for more fields of application are released regularly.

Although the requirements are getting stricter over time and manufacturers are trying to achieve higher levels of safety, there are some limitations for manufactures that hinder them to reach the next level of safety with their application. These limitations may be of spatial, energetic or financial kind. For example, it might not be possible for a manufacturer to fund a desired SIL-3 for an application that only requires SIL-1 by standards (details on SIL are described in Chapter 2), as the required investments would overprice the product, which in turn would prevent a successful placement on the market. Another example for a combined spatial and energetic limitation are **embedded devices**, which are omnipresent in today's safety critical environments. These devices may not have enough space around them to be supplied by a bigger or redundant power supply or battery.

An important, yet unfortunate, aspect of safety - although a common aspect for lots of other examples in daily life as well - is that safety is always a **trade-off**. A trade-off between effort and safety gained by this effort, or - even more visible for a customer - a trade-off between convenience and safety. Well known examples for this trade-off in our daily life are safety belts, helmets and similar "tools". A helmet is a good safety tool, but it is usually not really convenient to wear or to carry around. A helmet represents the trade-off of reduced convenience but increased safety.

#### **Functional safety**

As already outlined above, it is our goal to get today's safety related systems as safe as possible. That is, the risk that a system's intended functionality is not present anymore is as low as possible or as reasonably achievable. This goal is subsumed by the IEC under the term "Functional Safety", which is specified as:

... the part of the overall safety that depends on a system or equipment operating correctly in response to its inputs.

Functional safety is the detection of a potentially dangerous condition resulting in the activation of a protective or corrective device or mechanism to prevent hazardous events arising or providing mitigation to reduce the fight consequence of the hazardous event. [19]

The definition already summarizes well what it means to care about functional safety. Still, on closer examination, the question arises what those "hazardous events" actually are, depending on the context, and what instruments are suitable to mitigate or even prevent such events. In this point the whole complexity of this topic is hidden. Determining what is generally to be considered a "dangerous condition" and to what extent it is reasonable to require a system to implement certain measures is the scope of the IEC 61508 standard [20], which will be described in Chapter 2.

## **1.2 Target application domain**

Fire plays the major role in human evolution. Humans always loved and used fire, while at the same time fearing it for its destructive nature. The importance of fire is depicted in Wikipedia as:

The control of fire by early humans was a turning point in the cultural aspect of human evolution that allowed humans to cook food and obtain warmth and protection. Making fire also allowed the expansion of human activity into the dark and colder hours of the night, and provided protection from predators and insects. [3]

With fire, and the fear of it, comes the need for protection against (unintended) fires. As of today, people are used to the fact that many safety instruments to prevent and/or fight fires are established in our environment. Examples range from simple smoke detectors over fire extinguishers, via semi-automatic fire doors to fully automated sprinkler and other fire extinguishing systems. Putting special focus on fire safety within buildings, the law in most countries of the world regulates a minimum set of equipment that has to be available for fire safety, depending on the type and usage of a building.

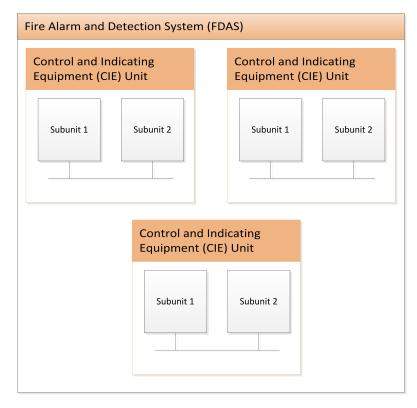

More and more of these systems nowadays are fully automated. Consequently, all bigger functional buildings are therefore equipped with so called "Fire Detection and Fire Alarm Systems (FDASs)". These systems may incorporate thousands of sensors and actuators and therefore need a certain degree of automation in order to be manageable. It should be clear to the reader by now that these FDASs are safety critical by nature as their **non-functionality** or wrong functionality will **increase the likeliness "to cause danger, risk, or injury"**.

This thesis targets safety in the FDASs domain with a specific focus on the hardware responsible for information exchange with an FDAS.

#### FDAS in building automation

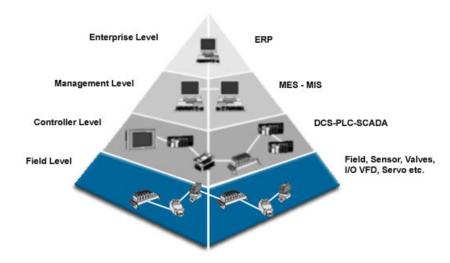

In buildings, the FDASs are part of the overall building automation system. As depicted in Figure 1.1, an FDAS is situated in the lower layers of the classical "automation pyramid" used to describe automation in buildings, in particular the sensors (e.g. smoke detectors) and actuators (e.g. fire doors) being on the "field level" whereas Control and Indicating Equipment (CIE) being situated in the "controller level" or even above, depending on the actual functions performed by each device.

Figure 1.1: FDAS are located in the field and controller levels of the automation pyramid [14]

Before programmable controllers have been introduced in the fire alarm domain several years in the past, these systems where rather isolated systems with little to no interfaces to other systems. Today, where Microcontroller Units (MCUs) are omnipresent in any kind of automation system, also the interfaces between systems evolved and integration of systems in general got a boost. This trend of course does not skip FDASs, where features like connecting such a system to a shared network - e.g. the Internet - or connecting distributed subsystems via shared networks are commonly asked by customers.

Clearly this integration is feasible for gaining efficiency, but also allows for more advanced safety features. As example, one can consider the cooperation of an FDAS with a Heating, Ventilation and Air Conditioning (HVAC) system in case of smoke alarms. The FDAS can switch off all the air conditioners to prevent further dissemination of smoke.

Inevitably the growing number of interfaces and interactions within or among systems raises complexity and error-proneness, making it even more important to provide solid means of dangerous condition detection to prevent hazards.

## **1.3** Problem statement and motivation

Typically the fire alarm domain has direct impact on human life and health and needs to guarantee safety in everyday life. Fire safety equipment has to provide its services in rather tough environments, which tend to

- have equipment distributed in big and unstructured areas,

- be comprised of multiple diverse subsystems from different manufacturers,

- be susceptible to power outages and

- have a variety of interfaces to third party systems,

which are by far not optimal for easily achieving high safety levels.

Besides the challenges in deploying such a system, it is even more critical to distribute information correctly within such FDASs (e.g. fire alarm messages). Therefore, one of the critical paths in such projects is proper communication. As most of the systems at larger scale are networked in the one or the other way, it seems important that **fault tolerant communication mechanisms** are deployed. That comprises of network structure, network protocols, but of course also the devices connected by these networks. Consequently, it must be ensured that at least those devices, which are crucial for the overall system functionality, are fault tolerant as well, in a sense that overall communication is neither interrupted nor disturbed by a faulty device. The devices in this view shall of course not be limited to safe communication, but must of course provide safe data handling in general as well. Therefore, it does not suffice to guarantee data transmission is fault tolerant, but the devices being responsible for sending and receiving the data (data source and data sink) must be fault tolerant as well, otherwise the overall fault tolerance of the system would be limited by the availability of the non-fault tolerant devices. For instance, it does not make sense to have a perfect fault tolerant transmission channel, if the data sent through such a channel is already corrupted due to some error on the sending device.

As integration of FDASs into other systems is a major trend, the combination bears new safety risks as well. Combining non-safety critical applications now with safety critical applications also takes existing standards to their limits, as those well established documents were originally crafted with the assumption of strict separation of those applications. To put it differently, they assumed an encapsulated environment, where service disruptions could only stem from a limited, well known, set of sources. The new risks implied by this combination of systems therefore even more require thorough design of the safety-critical parts, to ensure functional safety.

Today, there is lots of knowledge on how to construct safety critical applications. Specifically in the domain of IT systems this knowledge covers all fields from hardware construction to software design. Some of the approaches are only theoretical, whilst others are practical. The basis of the research conducted in this area even reaches back to the 1980s.

Still, each field of application of this knowledge requires targeted solutions, whose implementation is highly depending on the environment set out by the application. The fire safety domain is one field of application, providing its own challenges when it comes to implementing safe and interconnected systems.

As this thesis **focuses on the fire safety domain**, it tries to evaluate possible approaches for gaining more safety in FDASs, going beyond what is required by standards today and still respecting the restrictions imposed by the environment by improving the reliability of the most important devices of FDASs, the CIE, which are the crucial nodes within the communication infrastructure of an FDAS. Increasing fault tolerance within those devices should open the doors for higher levels of safety and finally strengthens the trust into these important, yet rather invisible, devices.

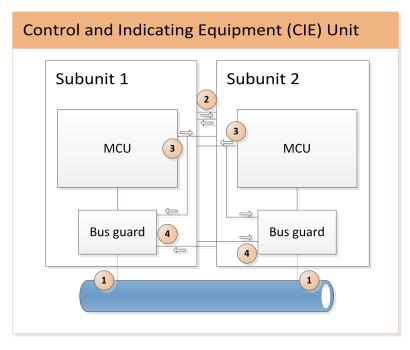

This thesis presents a concept on what can be done to make CIE - based on modern MCUs - fault tolerant, in order to help reach the overall goal of a bullet proof communication within FDASs, with communication being the critical path for the availability and reliability of the overall system.

#### **Methodical approach**

At first point an analysis of applicable standards for the fire alarm domain is given to define a basis of requirements requested by legislators. Furthermore, a literature study about state of the art safety concepts in hardware and software is presented.

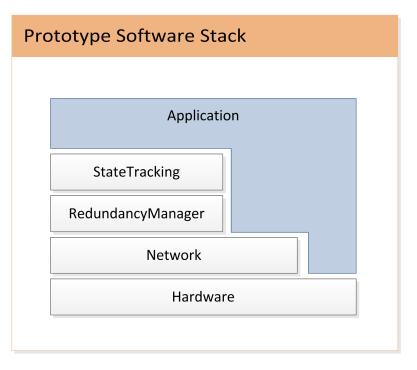

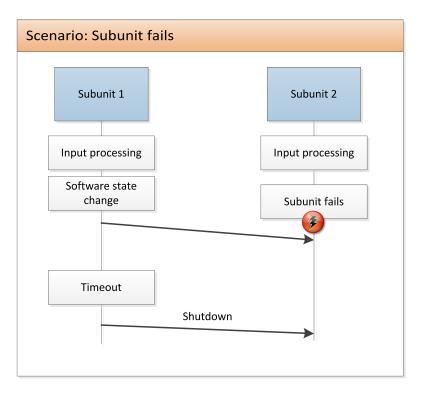

In consequence, the presented state of the art concepts are analysed for applicability in the target domain of FDASs. Based on this analysis, a concept for CIE, specifically shaped for this application domain, is presented. A prototype implementation, based on modern hardware, shows the key features and offers the basis for an evaluation of the presented concept, and additionally serves to document the system's behaviour in several typical fault scenarios.

Finally, the limits of the chosen concept are identified and an outlook to further possibilities of improvement is given.

# CHAPTER 2

# **Standard specifications**

This chapter presents standards currently applicable to Fire Detection and Fire Alarm Systems (FDASs) and standards around Functional Safety in general. These standards set the minimum requirements faced when building FDASs. Albeit there might be further regulations by local laws or national standards, the focus is on international standards as those are generally reflected in the national regulations as well.

The "Regulation (EU) No 305/2011 of the European Parliament and of the Council of 9 March 2011 laying down harmonised conditions for the marketing of construction products and repealing Council Directive 89/106/EEC Text with EEA relevance" [1] requires all products in the European Union (EU) to conform with harmonized technical standards (where such exist) in order to qualify for a CE mark. The CE mark is the prerequisite, which allows free movement of the product within the markets of the EU.

The harmonized standard for FDASs is the **EN 54 Fire detection and fire alarm systems** standard. Any FDAS product needs to comply with the EN 54 standard in order to receive the CE mark of the EU. On top of that the EN 54 standard is widely recognized and therefore qualifies these products to be sold outside the EU as well.

Besides the EN 54 standard, an FDAS has to comply to several other standards mostly defined by national building regulations.

For Austria, those standards are:

- TRVB-123 00 "Fire Detection Systems" [8]

- TRVB-114 06 [7]

For Germany, those standards are:

• DIN 14675 "Fire detection and fire alarm systems - Design and operation" [16]

- VDMA 24200-1 "Gebäudeautomation Automatisierte Brandschutz- und Entrauchungssysteme - ABE" [36]

- DIN VDE 0833-2 "Alarm systems for fire, intrusion and hold up" [15]

- VdS 2095 "Guidelines for automatic fire detection and fire alarm systems" [37]

In terms of Functional Safety there is the international "mother of all" standard **IEC 61508**. It is an application independent - yet technology bound - standard, which builds the foundation of a variety of derived standards, each of them tailored towards a specific field of application.

A brief listing of standards related to Functional Safety - most of them being derived from IEC 61508 - includes:

- US RTCA DO-178B North American Avionics Software

- US RTCA DO-254 North American Avionics Hardware

- IEC 62304 Medical Device Software

- IEC 62425 Railway Signaling Systems

- IEC 61513 Nuclear Systems

- ISO 26262 Road Vehicles Functional Safety

- IEC 61511 Functional safety Safety instrumented systems for the process industry sector

- IEC 62061 Safety of machinery Functional safety of safety-related electrical, electronic and programmable electronic control systems

- ISO 13849-1, -2 Safety of machinery Safety-related parts of control systems. Nontechnology dependent standard for control system safety of machinery

As there exists no specific Functional Safety standard for FDASs, standards like VDMA 24200-1 provide guidelines on how to handle functional safety in these systems. It is worth noting that most guidelines are again based on the non-normative parts of IEC 61508, hence, concepts, methods and terms of IEC 61508 are used in these guidelines.

## 2.1 EN 54

The EN 54 standard comprises 25 parts in total<sup>1</sup>, covering all components involved in FDAS. Each part describes one component or piece of equipment in detail.

The introduction to EN 54 is in part 1 [10] and describes the standard to specify amongst others:

<sup>&</sup>lt;sup>1</sup>Part 6a and part 8 of EN 54 have been withdrawn.

- Requirements, test methods and performance criteria against which the effectiveness and reliability of the component parts of FDAS can be assessed, and

- Requirements and test methods against which the ability of components to be combined into an effective system can be assessed.

In the course of this thesis, the main focus is on the so called "Control and Indicating Equipment (CIE)". This equipment is specified to be **responsible** for monitoring the "correct functioning of the system" and "warning of any faults", which clearly points out that functional safety is the major topic of this very equipment. Therefore, a closer look will be taken at the regulations in EN 54 part 2 "*Fire detection and fire alarm systems - Control and indicating equipment*" [11], as those regulations define most of the important guidelines for building CIE.

### EN 54 part 2

The standard EN 54 part 2 defines its scope as:

This European Standard specifies requirements, methods of test, and performance criteria for control and indicating equipment for use in fire detection and fire alarm systems installed in buildings. [11]

The standard first defines general requirements how the state of the CIE has to be displayed and indicated. This covers audible indications as well as indications on displays and lamps.

The subsequent chapters describe the various functional conditions a system can be in. This is the list of recognized conditions by the European Standard:

- fire alarm condition

- fault warning condition

- disable condition

- test condition

- quiescent condition

The standard continues to elaborate on standardized input/output interface and design requirements. A separate chapter is dedicated to software controlled CIE and outlines more specific design requirements for this type. Finally, the last chapter deals with tests and extensively describes all sorts of mandatory tests to be performed with the product in order to achieve standard compliance.

The following paragraphs show a selection of requirements from the standard, which specifically influence functional safety and are therefore important for this thesis.

Section 5.1.1 in EN 54 part 2 demands that a CIE needs to be able to unambiguously indicate fire alarm and fault warning conditions. Moreover, the time limit to indicate such a fire alarm

condition may not exceed ten seconds. After a reset operation, indication of the current condition has to be re-established within 20 seconds.

Chapter 8 of EN 54 part 2 is of special interest, as it is listing the requirements for coping with various faults and how these have to be detected, indicated and resolved. In general, the CIE should enter the fault warning condition within 100 seconds from detecting a fault situation. Section 8.4 requires the equipment to emit an audible indication for at least one hour in case of a complete loss of the main power source and Section 8.5 stipulates how software faults have to be indicated.

In case faults can be indicated on some other equipment, Section 8.9 requires the FDAS to also indicate de-energized CIEs. Section 12.5 additionally states that a fault in any transmission path of the system shall not affect the correct functioning of the CIE or any other transmission path. The re-establishment of function of operational devices after an interruption may not exceed 300 seconds.

For software controlled CIE, Section 13.4 requires a separate monitoring device with a separate timebase to monitor software execution. Furthermore, the software has to enter a safe state if a system fault is detected. Section 13.5 deals with memory aspects for program and data. A requirement is that memory containing site specific data has to be continuously verified for correctness in an interval not exceeding one hour.

Since this thesis deals with software controlled CIE only, this packed list of facts will serve as a minimum basis for the further concept.

## 2.2 IEC 61508

The IEC 61508 standard plays a different role in the fire alarm domain. While it is not strictly required by EN 54's testing procedures or software requirements, it seems obvious that the ideas of a standard entitled "*Functional safety of electrical/electronic/programmable electronic safety-related systems*" shall be applied to state of the art CIEs being comprised almost entirely of programmable electronics with the sole purpose of providing safety. The German standard VDMA-24200-1 explicitly deals with safety requirements in Chapter 6 and refers to IEC 61508 in Section 6.2.

The origins of the standard reach back to 1984, where Hölscher and Rader described requirements for microcontrollers in safety related systems [18]. The standard evolved from the process control industry, yet it has to be pointed out, that the IEC 61508 standard is a generic one. Therefore, it requires interpretation in some areas, in order to match the actual application. For many industries derived standards have been released, which contain the interpretation of IEC 61508 and add further requirements specific to that industry.

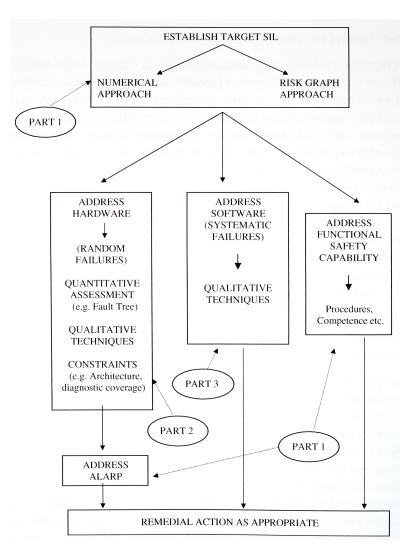

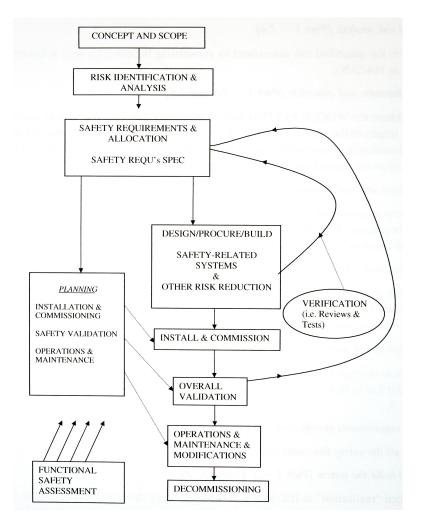

The standard covers the complete safety life-cycle and is split into seven parts, where only the first three parts have normative character. Figure 2.1 shows which topics are addressed by the parts of the standard. The basic concepts dealt with in the standard are **risk assessment** and

**safety functions**. Safety functions may include electronic technology and are used to lower a certain risk that hazardous events cause severe consequences (such as death) by bringing the **equipment under control** into a safe state.

Figure 2.1: The Parts of IEC 61508 [33, P. 17]

The types of failures we are looking at are random hardware failures and systematic failures. The random hardware failures can be assessed in terms of failure rates, whereas the systematic failures can only be addressed by applying sufficient rigor throughout the design process. Safety has to be considered throughout the whole life-cycle of a product, for that reason the safety life-cycle covers the complete life-cycle.

A central goal of the standard is to ensure that non-tolerable risk - which is to be found out by risk assessment - is reduced As Low As Reasonably Practicable (**ALARP**).

One of the central terms in the IEC 61508 standard is the term **Safety Integrity Level (SIL)**. The "Safety Critical Systems Handbook" nicely describes how this term is to be understood:

The maximum tolerable failure rate that we set, for each hazard, will lead us to an integrity target for each piece of equipment, depending upon its relative contribution to the hazard in question. These integrity targets, as well as providing a numerical target to meet, are also expressed as "safety-integrity levels" according to the severity of the numerical target. [33]

The safety-integrity levels are specified from SIL 4 to SIL 1. The "Safety Critical Systems Handbook" defines them as:

- SIL 4 is the highest target and requires state of the art techniques to achieve it. This level is usually avoided as the effort involved to reach this target, is massive.

- SIL 3 requires sophisticated design techniques.

- SIL 2 only requires good design and operating practise on a level such as would be found in an ISO 9001 management system.

- SIL 1 is the lowest target level, but still implies good design practise.

- Anything below SIL 1 is considered to be not safety related as of IEC 61508.

The general process is to first conduct hazard and risk assessments, which yield a target SIL. The SIL then defines how the life-cycle and its processes have to be set up in order to be able to justify that the final system attains the target SIL.

For hazard and risk assessment, the standard suggests to use either qualitative or quantitative analysis techniques and provides examples. One of the qualitative approaches is a method, where a set of categories of likelihood of occurrence is set in relation to a set of four categories of consequences (catastrophic, critical, marginal, negligible). The resulting matrix provides information how tolerable a certain risk is and assigns a class for this in each cell of the matrix. The classes being from one (unacceptable) to 4 four (acceptable). For instance: Having occasional occurrence combined with catastrophic consequences is assigned to Class 1, unacceptable.

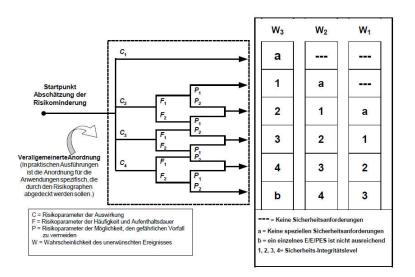

Contrary to the qualitative risk assessment method described above, the VDMA-24200-1 standard requires risk assessment based on risk graphs. The authors outline that "real risk assessments have shown that the majority of FDASs have to fulfil SIL 1" [36, S. 12], albeit some situations - e.g. when deviating from construction laws - might require higher levels as well.

An example risk graph, as suggested in IEC 61508 part 5, is in the appendix of VDMA-24200-1 (see Figure 2.2), which is specifically targeted for FDASs.

In order to define the requirements for each SIL, another distinction is made by the standard: The demand rate. The standard separates the demand rates into only two groups. The **high demand rate** applies to all systems that operate continuously or where the safety function is demanded more than once per year. The **low demand rate** is used for all other systems. For each demand rate the standard defines the maximum failure rate and the PFD as listed in Table 2.1.

#### Risikograph nach EN 61508 - Teil 5

Figure 2.2: VDMA-24200-1: Example for a risk graph to assess a target SIL [36]

| SIL | dangerous failures / hr (high demand rate) | probability of failure on demand (low demand rate) |  |

|-----|--------------------------------------------|----------------------------------------------------|--|

| 4   | $>= 10^{-9} \text{ to} < 10^{-8}$          | $>= 10^{-5} \text{ to} < 10^{-4}$                  |  |

| 3   | $>= 10^{-8} \text{ to} < 10^{-7}$          | $>= 10^{-4} \text{ to} < 10^{-3}$                  |  |

| 2   | $>= 10^{-7} \text{ to} < 10^{-6}$          | $>= 10^{-3} \text{ to} < 10^{-2}$                  |  |

| 1   | $>= 10^{-6}$ to $< 10^{-5}$                | $>= 10^{-2} \text{ to} < 10^{-1}$                  |  |

Table 2.1: SIL specification for low and high demand rates according to IEC 61508

Probability of failure on demand (PFD) is the same as probability of being failed at a random chosen moment, which is the same as unavailability. The PFD is dimensionless and is given by:

$$PFD = UNAVAILABILITY = (\lambda MDT)/(1 + \lambda MDT) \cong (\lambda MDT)$$

$\lambda$  is the failure rate and MDT is the mean down time, which includes the mean time to repair (MTTR), and usually  $\lambda$  MDT << 1 holds true.

The safety function of FDAS is classified as low demand rate system by VDMA-24200-1 (Appendix F.2), due to the fact that the demand, namely a fire incident, will occur only rarely on average.<sup>2</sup>

<sup>&</sup>lt;sup>2</sup>Obviously, the classification whether a low demand rate or a high demand rate is applicable is not very clear. For instance, SafetyLON, a network protocol for safety related applications within the building automation domain, was defined to be a high demand rate system [29], albeit its domain includes fire safety as well.

Section 7.4 of IEC 61508 part 2 outlines requirements for design and development. The following list is a summary of those requirements as denoted in [33].

- Use of "in-house" design standards.

- On manual or auto-detection of a failure of the safety system, the design should ensure system behaviour which maintains the overall safety targets. This implies additional monitoring or a shut down of the equipment under control.

- Sector specific requirements have to be observed.

- The system design should be structured and modular.

- Systematic failures caused by the design should be tackled by monitoring the functionality with extra circuitry. The complexity of this monitoring varies depending on the target SIL.

- Systematic failures caused by environmental stress: Components should be designed for the environment in question. Generally, components reaching a CE marking approval (or similar) would be expected to meet this requirement.

- Communications. The failure rate of the communications process has to be addressed.

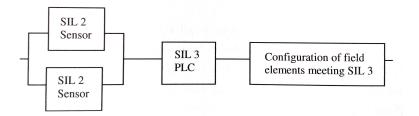

- Synthesis of elements: The standard allows configurations involving parallel elements, where each of them demonstrates a particular SIL in respect to systematic failures, to claim an increment of one SIL. Prerequisite is that a common cause analysis has been conducted to demonstrate independence. An example is shown in Figure 2.3

Figure 2.3: Two SIL 2 elements achieving a SIL 3 result. [33, P. 51]

A special focus is on the architecture of the design, the standard dedicates Section 7.4.4 to this topic.

Besides the reliability calculations established for hardware, the standard specifies minimum levels of redundancy together with levels of fault tolerance. This is subsumed by the term Safe Failure Fraction (SFF). The SFF is defined as:

$$SFF = \frac{Total revealed hazardous failures + Total safe failures}{Total failures}$$

| Type A SFF | SIL for Simplex HFT 0 | SIL for (m+1) HFT 1 | SIL FOR (m+2) HFT 2 |

|------------|-----------------------|---------------------|---------------------|

| < 60%      | 1                     | 2                   | 3                   |

| 60% - 90%  | 2                     | 3                   | 4                   |

| 90% - 99%  | 3                     | 4                   | 4                   |

| > 99%      | 3                     | 4                   | 4                   |

| Type B SFF |                       |                     |                     |

| < 60%      | Not allowed           | 1                   | 2                   |

| 60% - 90%  | 1                     | 2                   | 3                   |

| 90% - 99%  | 2                     | 3                   | 4                   |

| > 99%      | 3                     | 4                   | 4                   |

Table 2.2: Requirements for SFF

where "Total revealed hazardous failures" are potentially dangerous failures revealed by autotest, "Total safe failures" being the number of failures resulting in a safe state and the "Total failures" comprising the aforementioned PLUS the unrevealed hazardous failures.

There is another distinction into two types of components. Type A applies to components where failure modes and behaviour under fault conditions are well defined and failure data is available. The remainder of components is classified as Type B. Depending on the type, Table 2.2 shows the maximum SIL which can be claimed depending on the SFF. The number m specifies the number of failures which lead to system failure, (m + 1) designates redundancy, the number of elements.

Part of the overall safety is of course also operations. Depending on the target SIL, the systems are required to provide feedback or even correctional actions to operator activities. This is the place where the "human factor" has to be considered. An example here are the fly-by-wire systems of airplanes (typically SIL 3 to 4). These systems, for instance, prevent the pilots from stalling the plane.<sup>3</sup> Quantification of human error is not a requirement of IEC 61508, but the consideration of human error is required and mentioned in various places in normative parts one to three of the standard.

Planning and implementing the software should also include semi-formal methods as well as coding standards and structured programming. Dynamic objects, interrupts, pointers and recursion should be avoided as much as possible. The used programming language should be restricted to a subset to minimize unsafe usage. An example is the MISRA-C standard from the automotive sector that describes such a subset of the programming language C. For SIL 3 and 4, it is furthermore strongly recommended to use certified tools only.

#### The Life-cycle approach

The IEC 61508 standard is based on a safety life-cycle approach. The reason for that is that qualitative safety criteria, such as avoidance of systematic failures, have to be tackled mostly on

$<sup>^{3}</sup>$ To stall an airplane means to increase the angle of attack (raise the nose) to a point, where the air flow over/under the wings stalls, causing the plane to actually stop flying. This condition is deliberately used in aerobatics flight, but is to be avoided for normal flights like on airliners as it could cause the plane to crash.

the management level and throughout the design phase of a product. Therefore, this approach aims to control all phases of the life-cycle, which influence safety. The phases comprise of the process from safety specification and assurance throughout the development and operations to decommissioning. The standard describes a model for the life-cycle and identifies all activities throughout the life-cycle based on this model. This assures that decisions made in the planning and design phase are in the end fulfilling the target failure probabilities. A simple life-cycle is depicted in Figure 2.4. It is worth noting that the Functional Safety Assessments are to be carried out in all phases.

Figure 2.4: Safety life-cycle [33, P. 11]

The life-cycle has to be applied to all electrical and programmable aspects of the safetyrelated equipment. In case such equipment is embedded in another system, the life-cycle applies to the system as a whole. That involves also mechanical and pneumatic equipment. Keep in mind though, that each safety function has its own SIL target, so different management functions might be necessary for each safety function.

All steps in the life-cycle are to be verified by functional safety assessments. Following this methodology helps to improve the quality of the product as well as it helps to detect mistakes (systematic failures) at an early stage. Depending on the intended SIL, the assessments have to be undertaken by dedicated safety managers or even external certification institutions.

#### Software

Any software involved in safety functions needs to comply to the requirements of IEC 61508, too. Part 3 of the standard is called "Software requirements" and deals with systematic failures. The level of software verification needed may vary enormously and might even reach to the adoption of formal methods, which is common for SIL 4 safety function for instance in airplanes<sup>4</sup>. For lower levels, common automated tests and unit-testing will already suffice and are generally accepted.

#### Tests

When striving towards the requirements of SIL 3, the complexity of the checking mechanisms and test methods significantly jump up and the used methods have to be extended to involve:

• Memory checks with checksums or parity bits

This comprises of methods to detect or even tolerate memory corruption of all kinds. Checksums may be calculated on the content of the memory on fixed intervals allowing to detect unexpected corruption of any data. The checksum of course needs to be stored, so this yields the necessity for planning on extra memory depending on the granularity of the memory blocks to be checked. The bigger the area that is covered by a checksum, the less memory is required to store those checksums, but on the other hand, writing data is slowed down as the checksums have to be updated as well, which takes longer for bigger areas of memory. Parity bits may have the advantage here that those are easy to implement in hardware, hence the time to create those is not a problem.

• Signal checks

Any data sent around on communication interfaces has to be checked for validity. Means for achieving this can be parity checks or reasoning about the adequateness of a signal in the given state of an application. So these checks can happen at the various levels of abstraction.

• I/O module tests

All I/O modules shall have appropriate test circuitry which allows testing their functionality. For instance, SPI interfaces may provide internal loopback functionality (inside the circuit or even on pin level) to test the receiving and sending unit of the interface.

<sup>&</sup>lt;sup>4</sup>A big European airplane manufacturer seeks help from German universities (Prof. Dr. Reinhard Wilhelm) in order to reach SIL 4 for the primary flight control system. The code for the primary flight control is said to be verified by formal methods to a large extent. [2]

• Sensor/Actuator tests

As with I/O modules, connected sensor or actuator devices shall provide self-test capabilities, which allow periodic monitoring of their functionality.

• Fault injection tests

These kind of tests involve active injection of faults into the system (which are expected to be covered by the fault hypothesis) and the verification whether the system under test reacts as specified. Assuming a redundant network connection a possible fault injection testing vector would be to forcefully disable a connection line in order to assert that the equipment really correctly performs the expected fail-over.

• and many more

Besides complex monitoring of the equipment under control, there are other means that help to reach the targeted SIL. On the architectural level, one important design method is modularization, albeit the IEC 61508 standard (Part 2) asks to keep the number of modules in a "limited size" for SIL 1 and 2. Moreover, these modules are required to have a certain documented field experience. Instead of packing all the intelligence of safety into the safety functions (monitoring), an even better approach would be to improve the equipment under control, such that the risk imposed by it is lowered. This has direct impact on the risk assessment and therefore lowers the (necessary) complexity of the safety functions. Note that this especially holds true for integrated systems, where equipment under control and safety function are not separated. e.g. a monitoring software is running on the same Central Processing Unit (CPU) as the control software.

## 2.3 Other standards

Apart from EN 54 part 2 and IEC 61508 some other standards are crucial for FDASs and their CIE. For a reliable system, "power management" is an important asset. Therefore, EN 54 part 4 [9] specifies Power Supply Equipment (PSE). It requires at least two power sources per CIE unit, where at least one of them has to be connected to the public grid and another one has to be a rechargeable battery (Section 4.2.4). Each of them must be capable of operating the CIE within its specification (Section 4.2.5).

Despite the existence of the mandatory European standard EN 54, the individual countries additionally established national standards for FDASs. Some of those standards just extend on the regulations of EN 54, whilst others include their own provisions independently.

# CHAPTER 3

# Functional safety - state of the art methods

The field of functional safety and the technologies used and developed to tackle the challenges linked with it, have undergone big improvements in the last decades, while the importance of safety and security grows every day as embedded systems conquer our everyday life and everyday needs. Specifically systems that require high reliability and therefore having targets of Safety Integrity Level (SIL) 3 to 4 face a very tough problem: "The system as a whole must be more reliable than any one of its components." [23]

This chapter will present an overview of state of the art techniques and methods used in the context of functional safety. These methods specifically focus on design and implementation methods. The chapter does not cover aspects like material quality, which of course is crucial for safety of a product as well, but is not directly a factor of functional safety.

## **3.1** Definition of terms

As with every field of expertise, it is necessary to speak the same language in order to avoid confusion. In the safety area, a few terms are of special importance, which are described as follows:

• Fault

"Condition that can cause an element or an item to fail." [20]

• Error

"Discrepancy between a computed, observed or measured value or condition, and the true, specified, or theoretically correct value or condition." [20]

• Failure

"Termination of the ability of an element, to perform a function as required." [20]

#### • Fault hypothesis

"An assumption about the types and numbers of faults that must be tolerated by the planned system." [22]

#### • Fault-Containment Region

Fault-Containment Regions are a concept to define boundaries in a systems, where errors do not propagate over and therefore do not cause the next part in the system to fail as well.

The subsequent chapters will use these terms extensively to describe various aspects. The reader should put special focus on the subtle difference between fault and failure.

### 3.2 Hardware methods

To achieve a high level of safety, a variety of methods and guidelines exist on the hardware level that can be utilized to reduce the likelihood of random hardware failures - which occur throughout the runtime of a product - and to avoid systematic failures - which are shortcomings in the design and development phase. On ASIC/chip level, the following list provides a selection of those methods.

- Throughout the design phase: Validation of the whole code with simulation The designed chip layout is validated by simulating the design with accordant simulation tools for Hardware Definition Languages (HDLs) like Questa. For FPGA designs, Model-Sim would be an example for a well known simulation tool. With these simulation tools, it is possible to detect or its of the design which were been to fort earth of the method.

- it is possible to detect critical paths in the design, which may be the first spot in the system to be the cause of a random hardware failure due to limit exhaustion.

- Design for testability [38] [25]

The HDL design is created with testability in mind. The tests to be conducted are defined precisely and the design is built with account for ease of test execution. This may also include built-in testing structures, which are finally disabled within the shipped product.<sup>1</sup>

- Functional tests on module and top-level Designated testbeds are established for each module additionally to a testbed for the overall system. This allows detailed testing of the modules while the system test helps to rule out emergent effects caused by the combination of modules.

- Avoidance of asynchronous circuits For safety critical systems, only synchronous chip designs are recommended as it might be impossible to verify correctness with asynchronous constructs.

- Consideration of gate and wire delays The timing calculations for HDL designs as well as Printed Circuit Board (PCB) designs

<sup>&</sup>lt;sup>1</sup>This is usually done via so called fuses, which provide the possibility to enable or disable parts of digital logic after a chip has been produced. Commonly a laser ray is used to burn such fuses. Popular applications of this technique range from "shaping a product to one's needs" to "removing test circuits".

should consider the delays imposed by wires and gates. HDL synthesis tools like Quartus usually take care of gate delays automatically for calculating the maximum clock frequency of a synchronous design.

- Separate physical blocks on the substratum for each channel and monitoring block This precaution tries to prevent negative effects like errors in the system influencing a monitoring circuit.

- Distance of physical blocks shall be large enough to avoid crosstalk This measure helps to avoid crosstalk effects and reduces the probability that two or more blocks are affected by a common cause fault.

- On-chip redundancy

Lifetime of certain elements might not always fulfil the estimation. Deploying units redundantly on a chip allows to switch the operational unit or to validate results of those units for correctness. See Section 3.3 for details of redundancy concepts.

- Flipped orientation of redundant elements on the die The physical orientation of an element might be crucial when it comes to sporadic events like cosmic radiation. [40]

Positioning redundant elements in different orientations on the die (flipping each by 90° for instance) will lower the chance that all elements are affected the same way and helps to prevent common cause failure.

- Avoidance of unsymmetrical wiring

- Verification of the complete ASIC Testing the complete ASIC against the specification.

Still, when using cheaper hardware components one may fail to reach the desired SIL.

For achieving a defined level of integrity either highly reliable hardware with a low residual error probability has to be used or comprehensive online self tests have to be performed. The chosen standard microcontrollers must perform online self tests in order to detect as much hardware faults of the CPU internals as possible. [35]

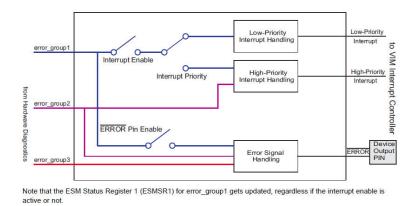

These kinds of self tests can be implemented in hardware or software. Generally, hardware implementation is to be preferred, as those tests have access on a lower level and can be executed faster or even in parallel to normal CPU execution. Dedicated safety Microcontroller Units (MCUs) provide a big set of embedded self tests for many MCU components.

Besides testing the hardware and improving its reliability, it is of course also necessary to track proper execution of the overall functionality, which mostly is comprised by software. The following section will deal with approaches to detect faults on a higher level.

## 3.3 Approaches for fault detection

In order to detect or even tolerate faults in a system and make it more safe, lots of ideas and approaches have been proposed over the decades. This section will present some approaches and outlines their solutions and the problems they solve.

Fault detection and tolerance always requires some form of redundancy in a system. In the simplest incarnation the correct functionality of a system during runtime can be checked by employing monitoring. In hardware, this usually is a separate, distinct circuitry. The requirements imposed on such a monitoring circuitry differs for complexity depending on the desired SIL. In software, fault detection is usually solved by examining memory and calculating checksums for data. Code-wise the detection is a bit more involved, but there are pure software solutions for transient and permanent error detection as well. [30]

A simple monitoring system in hardware would be a watch-dog. A watch-dog is typically a separated logic that consists of a timer and a reset line at its most basic style. The monitored application has to reset the watch-dog's counter within a certain amount of time, otherwise the watch-dog logic initiates a reset of the application as corrective action. The concept is well known from railways where this is called "dead man's control". A train is stopped automatically if the locomotive driver does not trigger the watch-dog switch regularly. The corrective action taken by a watch-dog varies of course. For some applications the watch-dog may trigger some fail-safe circuitry and additionally starts a second watch-dog which monitors the the fail-safe function again. Besides that, a watch-dog may also do some recording of program state to ease fault detection or post-mortem analysis. Watch-dogs can also be combined with software services to allow for more fine-grained corrections if software faults can be detected by such services. The outer watch-dogs serves as last resort and monitors the software services only. Yet the simple watch-dog leaves us with an issue, which was described by Lu in 1982:

Major issues in the design of watchdog processors are the selection of operations to be checked for errors, the means of encoding and transmitting information from the main processor to the watchdog, and the programming of the watchdog. [27]

A slightly different watch-dog approach is suggested by Michel, T. [28] which describes a watchdog processor that is specifically targeted to software flow control on an Intel 80386sx microprocessor, with the special goal to avoid performance issues. So essential the watch-dog concurrently monitors the program flow on the processor and solving the above issue by leveraging knowledge about the internals of the processor.

In terms of functional safety, a watch-dog is generally considered a good design practice and thus suffices for most applications with a SIL 1 target.

On the software side, a promising approach has been presented by Nahmsuk Oh [30] in 2000. The idea is to save cost for hardware in space applications and use "Commercial Off The Shelve (COTS)", cheap, non-shielded hardware only. As radiation is a major topic for space applications, transient errors - like bit-flips - have to be detected. Oh proposes three techniques to

detect hardware faults in software, based on signatures and code duplication, with one of the techniques reaching 98% fault coverage in injection tests.

A different kind of redundancy and to gain safety, is to actually use multiple instances of the actual equipment. The setup changes in a way that error-checking can now be done by comparison, where error-checking component - called voter - does not need to know about the internals of the system. This has the additional benefit that such a true redundancy covers all aspects of the equipment, hardware and software. Any fault in any component can potentially be detected, as long as the output shows sufficient discrepancy to the voter.

Redundant systems can be categorized by the number of faults they may tolerate. IEC 61508 uses the term XooY ("X out of Y") to categorize the systems. This means that X out of Y systems have to fail for the overall system to be inoperable. Typical examples and their applications are:

- 1001: Single channel processing.

- 1002: If one of the two systems fails, the whole system is disabled (used for automatically guided vehicles).

- 2002: If both systems fail, the whole system is disabled (used for gas-turbines).

- 2003: At least two systems have to be operable (used for airplanes and chemical plants).

- 2004: Three out of four systems must be operable (typically required for space shuttles and nuclear power plants).

The following sections describe typical redundancy implementations.

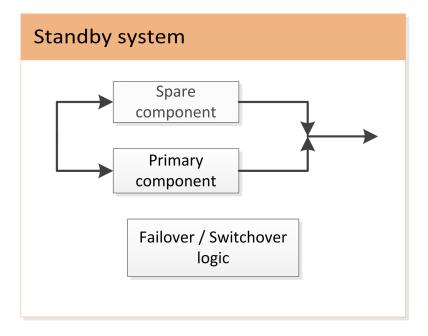

### Standby redundancy

A simple possibility of redundancy is the standby pattern. The general idea of the standby pattern is to have a replica of the active system available in spare, which can be activated whenever the primary system fails. However, to automatically switch between the primary and the spare component, some additional logic is required. Figure 3.1 shows the setup of such a system. The standby pattern is a dynamic redundancy concept, as it involves reconfiguration (switching the component) after a fault has been detected. According to IEC 61508, this is a 2002 system.

The distinction between hot and cold standby refers to the state the spare system is held in. For cold standby, the spare system is generally not active and needs to be initialized once it is activated. Contrary, the hot standby scheme refers to a system, where the spare system is active too, such that any operation performed by the primary system is also performed by the spare system. Both systems are fed with the same inputs at the same time. This ensures the spare system is up to date and a possible switchover can be made with minimal delay as no initialization is necessary.

Figure 3.1: System setup for standby redundancy.

For hot standby systems, some literature suggests to include the switchover logic into the spare system, such that the external logic can be omitted. This kind of setup (hot standby with integrated switchover logic) is very similar to the Dual Modular Redundancy (DMR) scheme described below and hence the terms may be used interchangeably.

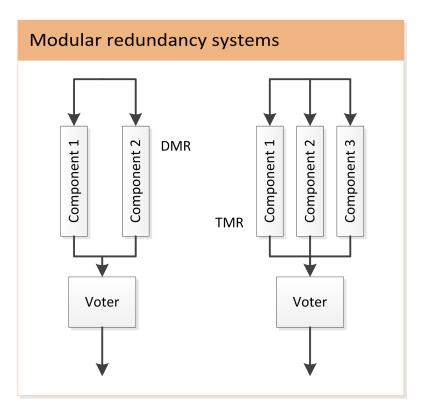

#### **Dual and Triple Modular Redundancy**

Modular redundancy refers to a system setup that has multiple instances of the same component working in parallel which are synchronized. A voter is responsible to determine the final output of the whole system. Popular setups are dual and triple modular redundancy. The N-modular redundancy concept is, contrary to the standby concept, a static redundancy concept as the fault is not propagated to the output.

DMR consists of two components working in parallel and is capable of **detecting** a fault, but is not able to correct for this error. The voter is not able to determine which component is wrong and which right. The difference between DMR and hot standby is rather subtle and mostly relates to the amount of synchronization performed between the components. As described in Section 3.3 on the preceding page, a hot standby system might be constructed to be similar to a DMR system.

While a DMR system is not capable of **tolerating** a fault in general, a Triple Modular Redundancy (TMR) system is able to actually tolerate a single fault by adding one more component. This is the accepted standard for fault tolerance in system architecture.

Figure 3.2 shows the setup of DMR and TMR. The TMR setup allows the voter to decide which component is faulty, as the non-faulty components' outputs match. It can furthermore switch to

Figure 3.2: System setup for dual and triple modular redundancy

a DMR strategy until the faulty component has been repaired, so at least error detection is still possible in case one component has failed. The TMR scheme can be extended to achieve even higher levels of fault tolerance by adding more components.

H. Kopetz [23] defines the architectural services that are needed to implement TMR:

- Provision of an independent Fault-Containment Region for each one of the replicas This ensures that the replicas do not influence each other and assures true independence.

- Synchronization infrastructure

The synchronization of the replicas is crucial as it is the basis for deterministic behaviour, i.e., the voter needs to know when the output of the replicas is ready to make a decision.

• Predictable multicast communication

A one-to-many communication allowing each node in the system to talk to all nodes. This can be understood as a fully connected graph of the communication channels in the logical structure of a system.<sup>2</sup> The predictability is important as everything else would be an asynchronous communication pattern, which brings a lot of undesired properties.

<sup>&</sup>lt;sup>2</sup>This does not imply that the actual communication system is really a fully connected network. The goal is to ensure that every node can list to all other nodes, regardless whether it is the recipient of the message or not.

- Replicated communication channels Of course the channels need to have redundancy as well, since a single communication channel would introduce yet another single point of failure, which would contradict the goals of TMR.

- Voting support

- Deterministic (which includes timely) operation The various steps of operation have to be deterministic in order to be able to guarantee fault tolerance. This excludes asynchronous communication and generally requires known worst-case execution times.

As can be concluded from this list of services, TMR or bigger redundancy implies a lot more hardware effort and involves significantly higher costs than standby redundancy. This is a main reason why lower levels of redundancy is generally preferred if the system and the indented functionality permits that.

# 3.4 Software architecture

While the methods above mostly focus on transient failures, hence physical issues, this section takes a look at possibilities to avoid systematic failures.

Software does not fail randomly, hence any fault is always a consequence of a wrong implementation, or even worse, a wrong specification. These systematic failures have to be tackled throughout the design phase of the life-cycle. There is only one exception, a random hardware fault might alter state, which causes the software to execute in an undesired manner.

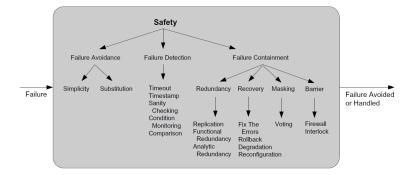

#### Safety tactics

In [39], Wu and Kelly present a guidance on how to develop a basic safety strategy in software architecture design. They describe so called "safety tactics", which connect software safety and software architecture. The safety tactics focus on the three aspects elicitation, organisation and documentation and can be organized as a hierarchy shown in Figure 3.3.

The derived safety tactics should then be used to create software patterns, which are subsequently used to design the software architecture.

In [34], from 1995, a number of industrial applications were inspected for used software patterns. The survey included a wide spectrum of applications in various sizes (in terms of code size) and important system characteristics. The introduction of that paper already states one important fact about architectures: "When poorly understood, these aspects (component interaction and interconnection) of design are major sources of errors." The paper defines four categories of structures, where each of them can be described in different perspectives. The identified categories are: conceptual architecture, module interconnection architecture, execution architecture and code architecture.

Figure 3.3: Hierarchy of safety tactics [39]

Twenty years later, the available technology vastly changed and these categories of architectures are integrated into frameworks and methodologies, which purport several aspects of these architecture descriptions into new concept.

#### **Development process and patterns**

Every software development process involves a methodology which defines the basic workflow how code is created. In the recent years a whole new class of such methodologies emerged, all of them named with a three letter code ending with the characters DD (standing for "-driven development"). The first character makes up the difference and the focus of each framework. Those are: BDD (Behaviour), FDD (Feature), DDD (Domain), MDD (Model) and TDD (Test)

Those methodologies of course mostly stem from the classic application software development industry, but still some approaches might be useful for safety related applications as well. For instance, test-driven development is an approach, which has one rule as essence: "Write the test first." This assumes that a suitable testing framework is at hand, which allows to write the specification in the form of tests, before starting to implement the actual functionality. Since safety systems need to be tested thoroughly anyway and best practise, like unit-testing, should be applied to the development process according to IEC 61508, employing a methodology like TDD seems to be a good choice to ensure high software quality.

Besides the workflow used to create the software, IEC 61508 also suggests a clear structure of the software in modules as a good design practise for software. Good ways to structure software for various appliances are usually described by so called patterns.

On the top level, the architectural patterns describe the general scheme how the components of a software application should interact. The goal of those patterns is usually to address hardware, performance or availability limitations on a high level of abstraction. Popular and commonly known architectural patterns for instance are: Event-driven architecture, Model-View-Controller, Microservices, Service-oriented architecture, and so forth.

Design patterns are located on a lower abstraction level than architectural patterns and are used to either simplify the structure of code or to build code in a way that is easier to understand for a developer used to the pattern. Lowering the complexity barrier is a major factor in avoiding systematic failures. It must be noted though, that a wrong usage of patterns may also increase complexity of software.

Design patterns are available for all possible levels of software engineering. Clearly, since object-oriented programming is the predominant design paradigm for application software, many patterns exist around this topic. To name a view popular: Factory method, Object pool, Singleton, Facade, Proxy, Template method, Scheduler, etc.

For safety systems it seems adjuvant to leverage such patterns as well. Specifically the concurrency design patterns - like Scheduler or Thread pool - are of interest for embedded systems as well. Mostly such patterns are already incorporated into existing libraries or even operating systems.

## **3.5** Other concepts

The introduction to this chapter already foretold the problem that targeted integrity levels may not be achievable by single systems, even though they leverage one or more of the above presented methods. In order to reach those higher integrity levels, the system needs to be decomposed into modules, which are connected together. The resulting system is called a distributed system, i.e., independent subsystems are connected to each other with a suitable communication medium.

With distributed systems and the communication channels involved, we face a whole new category of problems that arise in such systems. To name only a few of them: [6]

- Leader election

- Mutual exclusion

- Consensus

- Clock synchronization

A solution for these problems is again a prerequisite to enable the service required for TMR as listed above. It should be clear to the reader that none of these problems is easy to solve. A huge amount of research has been and is still being conducted in this problem area. [13] [31] [32]

## **3.6 Applications for fieldbuses**

Several fieldbus systems are available on the market, which employ safety properties either in their core or as extension. A selection shall be outlined in the following.

#### SafetyLON

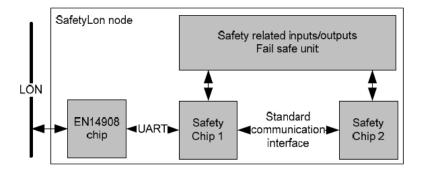

The Local Operating Network (LON) is a fieldbus system standardized in EN 14908. The Safety-LON project aims to extend LON with a so called "safe node" [29], which provides means to

achieve compatibility with IEC 61508 SIL 3. The focus of SafetyLON is on safe communication by extending the network protocol LonTalk and the network nodes with safety properties.

A first description explains that due to backwards compatibility any existing network must be extendable, hence establishment of a dedicated safety-network is not feasible. Therefore the prevalent hardware is extended. The components of a SafetyLON node are depicted in Figure 3.4.

Figure 3.4: Components of a SafetyLON node [29]

SafetyLON employs a 1002 system in hardware by adding two more MCUs. The software stack is modified to comprise of three layers, one of them being the Safety Layer taking care of safe communication. For the application software, the safe communication is therefore fully transparent. The protocol for safe data transfer is embedded into the standard LonTalk (protocol tunnelling).

As the chosen hardware does not provide excessive means of self-test functionalities, the safety software has to provide all self-test routines. This of course comes with loss of performance.

#### **CAN based solutions**

Based on the CAN bus technology there are several solutions for safety related applications. Two of those are "CANopen safety", standardized in EN 50325-5 [12], and "SafetyBUS p".

Within a SafetyBUS p network only safety-related devices are used exclusively, which are already multi-channel internally. Parallel processors process data simultaneously and only if output signals do match an output is generated. This is a 1002 system.

CANopen safety employs functional safety communication based on CANopen (EN 50325-4). It employs the basic idea to transmit each safety-related message twice. The second message has bit-wise inverted data. On reception, the two messages are compared. The CANopen-Safety-Protocol (CiA 304) is used. The standard does not specify any safety guidelines or requirements for the devices themselves, but uses two CAN controllers internally for redundancy.

#### PROFIsafe

PROFIsafe is specified in IEC 61784-3 and is a pure software solution. It only adds various safety precautions on top of the existing protocol for better fault detection.

#### openSAFETY