The approved original version of this thesis is available at the main library of the Vienna D~I~S~S~E~R~T~A~T~I~O~N

# Characterization and Modeling of Charged Defects in Silicon and 2D Field-Effect Transistors

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik von

## Yury Illarionov

Grunbergstra $\beta$ e 19-21/2/10 A-1120 Wien, Österreich

geboren am 5. Juni 1988 in Leningrad, USSR

Wien, im December 2015

TŲ UB

Die approbierte Originalversion dieser Dissertation ist in der Hauptbibliothek der Technischen Universität Wien aufgestellt und

**FU**UB

http://www.ub.tuwien.ac.at

University of Technology. http://www.ub.tuwien.ac.at/eng

## Abstract

This work has been conducted at a time when scaling of Si MOSFETs according to Moore's Law is close to its end. Hence, the research focus is shifting from nanoscale Si MOSFETs to next-generation transistors based on 2D materials. Although these technologies are dramatically different from one another, the question of reliability is essential for both types of devices. However, the typical dimensions of modern nanoscale Si MOSFETs are already far below 100 nm, while the channel lengths of next-generation 2D FETs are still in the micrometer range. Hence, in the former case the reliability is dominated by single discrete defects and in the latter case one has to deal with the impact of continuously distributed defects.

In the course of this dissertation we characterize the reliability of both nanoscale Si MOSFETs and next-generation 2D FETs with graphene and molybdenum disulphide  $(MoS_2)$  channels.

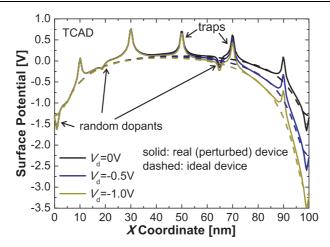

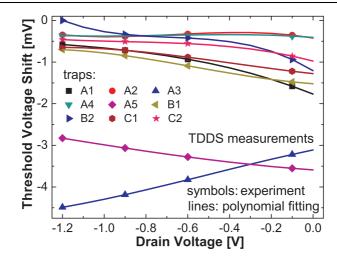

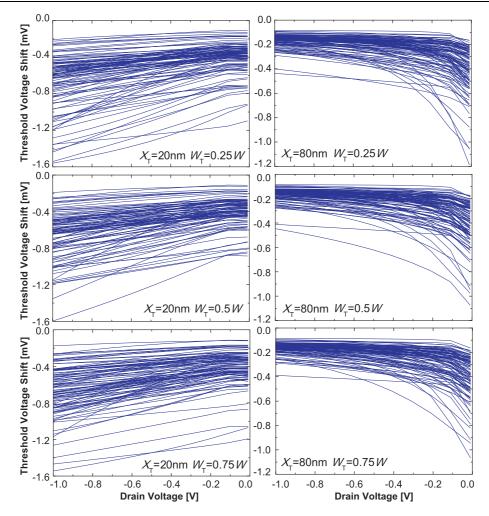

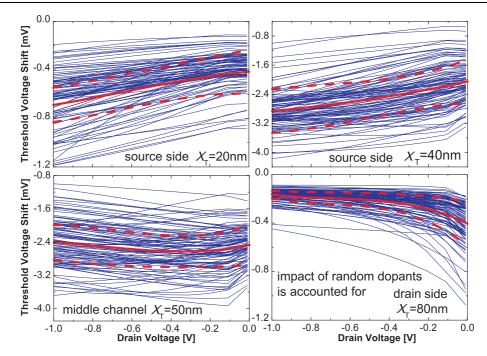

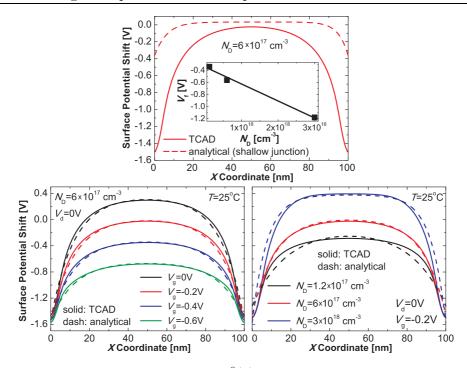

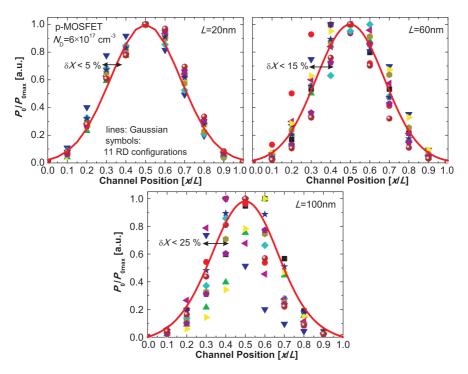

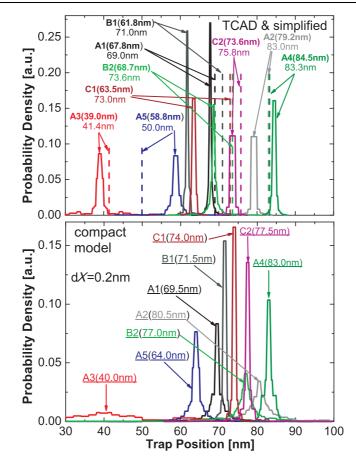

First we study the impact of charged traps and random dopants on the performance of nanoscale Si MOSFETs. Based on the results of TCAD simulations, we introduce a precise technique which allows for evaluation of the lateral trap position from the experimental data obtained using time-dependent defect spectroscopy. While our method fully accounts for the impact of random dopants, the typical uncertainty is several percents of the channel length.

Next we switch our attention to graphene FETs and analyze their reliability with respect to bias-temperature instabilities (BTI) and hot carrier degradation (HCD). Our analysis shows that the degradation/recovery dynamics of BTI and some HCD mechanisms can be captured using the models previously developed for Si technologies. Also, we show that HCD in graphene FETs can either accelerate or suppress BTI degradation, depending on the bias condition. In some cases this leads to a non-trivial impact on charged trap density and carrier mobility, both of which are correlated to each other.

Finally, we study the reliability of  $MoS_2$  FETs, which are more suitable for applications in digital circuits compared to graphene transistors. While analyzing the hysteresis and BTI in these devices, we demonstrate that our  $MoS_2$  FETs are more stable compared to their previously reported counterparts. Moreover, we show that use of hexagonal boron nitride as a gate insulator significantly improves the reliability of  $MoS_2$  FETs, especially at lower temperatures. Lastly, we introduce the proof of concept for modeling of the reliability characteristics of  $MoS_2$  FETs using advanced simulation software previously developed for Si MOSFETs.

The results obtained for 2D FETs allow for a general understanding of their reliability at the beginning stage of research. However, sooner or later circuit integration of these new devices will request considerable scaling of their dimensions and dramatical improvement of the technology level. As so, reliability of 2D FETs will be also dominated by single defects. Thus, we can expect that our trap location technique developed for nanoscale Si MOSFETs, as well as the described modeling approach, can be applied for next-generation 2D FETs in future.

## Zusammenfassung

Gemäß des Moorschen Gesetzes steht die weitere Skalierung von konventionellen Si MOSFETs kurz vor einer fundamentalen Grenze. Der Forschungsschwerpunkt verschiebt sich daher immer weiter in Richtung Transistortechnologien, welche auf 2D Materialen basieren. Obwohl diese Technologien grundlegend verschieden sind, bleibt die Analyse der Zuverlässigkeit beider Bauteile ein essentieller Bestandteil der Forschung. Allerdings ändert sich durch die unterschiedlichen Bauteilabmessungen die Beschreibung der Degradationsprozesse. Während bei modernen Si MOSFETs im Nanometerberich diskrete Defekte das Verhalten dominieren, beeinflusst ein kontinuerliches Defektspektrum die Funktionalitt von 2D FETs mit Kanallängen im Mikrometerbereich.

In diesem Kontext befasst sich die vorliegende Dissertation mit der Charakterisierung der Zuverlässigkeit beider Technologien, state-of-the-art SI MOSFETs sowie Graphene- und Molybdän Disulfid- (MoS<sub>2</sub>) FETs.

Im ersten Teil dieser Arbeit analysieren wir den Einfluss diskreter geladender Defekte und zufällig verteilten Dopanden auf das Verhalten von Si MOSFETs im Nanometerbereich. Mit Hilfe von TCAD Simulationen entwicklen wir eine präzise Methode die laterale Position eines Defektes aus TDDS (time-dependent defect spectroscopy) Experimenten zu extrahieren. Durch die Berücksichtigung von random dopants bewegt sich die Unsicherheit dieser Technik im Bereich weniger Prozente der Kanallänge.

Als nächstes richten wir unsere Aufmerksamkeit auf Graphen-FETs und untersuchen deren Zuverlässigkeit bezüglich Bias Temperature Instabilities (BTI) und Hot Carrier Degradation (HCD). Unsere Analyse zeigt, dass das dynamische Verhalten von BTI und HCD grötenteils durch bestehende, Silizium basierte, Modelle korrekt wiedergeben werden kann. Weiteres wird deutlich, dass die Wechselwirkung zwischen HCD und BTI zu einem nicht-trivialen Verhalten führen kann. Abhängig von den Bias Bedingungen kann HCD in Graphen-FETs den Effekt von BTI verstärken oder unterdrücken. In machen Fällen führt dies zu einer komplexen Korrelation zwischen geladener Defektdichte und Ladungsträgermobilität.

Im letzten Kapitel beschäftigen wir uns mit einer zweiten, in digitalen Schaltungen gebräuchlicheren, Art von 2D-FETs,  $MoS_2$ -FETs. Bei der Analyse des Hysterese- und BTI-Verhaltens stellt sich heraus dass diese Bauteile stabiler als ihre Graphene Pendants sind. Darüber hinaus zeigen wir dass der Einsatz von hexagonalem Bornitrid als Gateisolator die Zuverlässigkeit von  $MoS_2$ -FETs maßgeblich verbessert, speziell bei niedrigen Temperaturen. Mittels modernen Simulationssoftware, entwickelt fr Si MOSFETs, erbringen wir schließlich den positiven Machbarkeitsbeweis  $MoS_2$ -FETs hinsichtlich ihrer Zuverlässigkeit zu modellieren.

Die Resultate dieser Arbeit erlauben ein allgemeines Verständnis und ersten Einblick in das Degradationsverhalten von 2D FETs. Um diese Strukturen allerdings in bestehende Schaltungen zu integrieren muss sowohl die Skalierung der Bauteile als auch die Technologie drastisch verbessert werden. Dadurch wird, analog zu modernen Si MOSFETs, der Einfluss von einzelnen Defekten die Funktionalität dominieren. Es ist daher zu erwarten dass sowohl unsere Methode zur Bestimmung der lateralen Defektposition als auch die vorgestellten Modelle bei zukünftigen 2D Technologien zum Einsatz kommen.

## Acknowledgement

The work of the individual still remains the spark that moves mankind ahead even more than teamwork

Igor Sikorsky

First and foremost I would like to thank my parents. Without their support and understanding I would not have been able to reach even a minor part of my educational and scientific achievements.

I am also very grateful to my colleagues from Ioffe Physical-Technical Institute, who supported me from the beginning of my scientific carrier. Many thanks to Dr. Sergey M. Suturin, Prof. Nikolay S. Sokolov, Dr. Mikhail I. Vexler and Prof. Igor V. Grekhov for sharing with me their outstanding research experience.

To great length I am grateful to Professor Tibor Grasser for granting me a Ph.D position at the TU Wien. He always supported me with useful advices during the whole time I have been working on this dissertation. Also, he provided me with a very interesting research area focused in 2D materials.

I also want to thank all my colleagues from the Institute for Microelectronics (TU Wien). I am especially thankful to Dr. Stanislav Tyaginov for his support during my endeavor into the subject of reliability, to Michael Waltl for technical and programming assistance during my measurements. I am grateful to Gerhard Rzepa, Alexander Grill and Dr. Wolfgang Goes for their crucial contribution to modeling of MoS<sub>2</sub> transistors and to Dr. Alexander Makarov for his help with LaTeX.

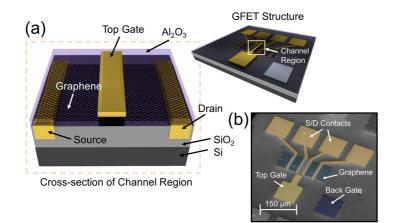

This work would not we possible without participation of Anderson D. Smith, Sam Vaziri and Prof. Mikael Ostling from KTH, who provided me graphene devices, and Marco M. Furchi from TU Wien, who fabricated MoS<sub>2</sub> transistors.

Also, I gratefully acknowledge useful discussions with Prof. Max C. Lemme (University of Siegen), Prof. Thomas Mueller (TU Wien), Dr. Ben Kaczer (imec) and Dr. Hans Reisinger (Infineon).

Last but not least, I am indebted to Dmitry Polyushkin, Andreas Pospischil and Stefan Wagesreither from TU Wien for their technical support at the beginning stage of my graphene experiments.

## Contents

| Abstract        |                              |                                                                                                                                                                                                                                                                                                                                                                     |                                            |  |  |  |

|-----------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|--|--|

| Zusammenfassung |                              |                                                                                                                                                                                                                                                                                                                                                                     |                                            |  |  |  |

| Ad              | Acknowledgement              |                                                                                                                                                                                                                                                                                                                                                                     |                                            |  |  |  |

| Contents        |                              |                                                                                                                                                                                                                                                                                                                                                                     |                                            |  |  |  |

| 1               | Intro                        | oduction                                                                                                                                                                                                                                                                                                                                                            | 1                                          |  |  |  |

| 2               | <b>Cha</b> 2.1<br>2.2<br>2.3 | rged Carrier Transport and Single Defects in Si FETsCharged Carrier Transport: General Equations and Models2.1.1Single-Particle Schroedinger Equation2.1.2Boltzmann Transport Equation and Method of Moments2.1.3Drift-Diffusion ModelModeling of Random Dopants and Discrete TrapsCharacterization of Preexisting Defects Using Time-Dependent Defect Spectroscopy | <b>3</b><br>3<br>4<br>4<br>5<br>7          |  |  |  |

| 3               | Mai                          | n Reliability Issues in Si MOSFETs and Their Modeling                                                                                                                                                                                                                                                                                                               | 8                                          |  |  |  |

|                 | 3.1<br>3.2                   | Overview of Reliability Issues                                                                                                                                                                                                                                                                                                                                      | 8<br>8<br>9<br>9<br>10<br>10               |  |  |  |

|                 | 0.2                          | 3.2.1       Universal Relaxation Model                                                                                                                                                                                                                                                                                                                              | 10<br>10<br>11<br>13                       |  |  |  |

| 4               | Nex                          | t Generation FETs Based on 2D Materials                                                                                                                                                                                                                                                                                                                             | 17                                         |  |  |  |

|                 | 4.1                          | Overview of 2D Materials: Graphene, MoS2 and Beyond4.1.1Graphene: Structure and Main Properties4.1.2MoS2 as a Further Step Beyond Graphene4.1.3Phosphorene, Silicene and Germanene: New Era in Semiconductor Science4.1.4Hexagonal Boron Nitride as a Next-Generation 2D Insulator                                                                                  | 17<br>18<br>20<br>21<br>22                 |  |  |  |

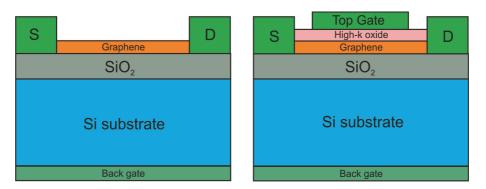

|                 | 4.2<br>4.3                   | Properties of Graphene FETs                                                                                                                                                                                                                                                                                                                                         | 23<br>23<br>24<br>26                       |  |  |  |

| _               |                              |                                                                                                                                                                                                                                                                                                                                                                     |                                            |  |  |  |

| 5               | 1mp<br>5.1<br>5.2            | act of Charged Traps and Random Dopants on the Performance of Si MOSFETsPrevious Descriptions and their DisadvantagesExperimental Technique                                                                                                                                                                                                                         | <ul><li>28</li><li>28</li><li>29</li></ul> |  |  |  |

| Contents |

|----------|

|----------|

|                  | 5.3<br>5.4<br>5.5<br>5.6 | TCAD Simulations                                                                             | 30<br>32<br>38<br>38<br>42<br>45<br>46  |  |  |

|------------------|--------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------|--|--|

| 6                | Relia                    | ability of Graphene FETs                                                                     | 47                                      |  |  |

|                  | 6.1                      | Introduction                                                                                 | 47                                      |  |  |

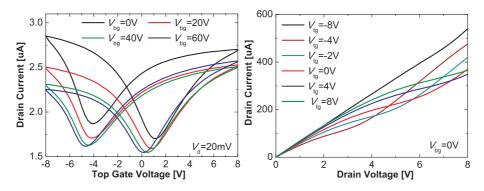

|                  | 6.2                      | Investigated Devices: Fabrication and Basic Characteristics                                  | 48                                      |  |  |

|                  | 6.3                      | Experimental Technique                                                                       | 50                                      |  |  |

|                  | 6.4                      | Modeling of Carrier Distribution in GFET Channel                                             | 52                                      |  |  |

|                  | 6.5                      | Bias-Temperature Instabilities on the High-k Top Gate                                        | 58                                      |  |  |

|                  |                          | 6.5.1 Typical Impact on the Device Performance and Reproducibility                           | 59                                      |  |  |

|                  |                          | 6.5.2 Temperature Dependence and Fitting with CET Map and Universal Models                   |                                         |  |  |

|                  | 6.6                      | Bias-Temperature Instabilities on the $SiO_2$ Back Gate $\ldots \ldots \ldots \ldots \ldots$ | 65                                      |  |  |

|                  |                          | 6.6.1 Stress Oxide Field Dependence and Recovery                                             | 65<br>60                                |  |  |

|                  | 67                       | 6.6.2 Comparison with Top Gate BTI                                                           | 68<br>60                                |  |  |

|                  | 6.7                      | Hot-Carrier Degradation                                                                      | $\begin{array}{c} 69 \\ 69 \end{array}$ |  |  |

|                  |                          | 6.7.2 Degradation under Different Polarities of HC and Bias Components                       | 09<br>72                                |  |  |

|                  |                          | 6.7.3 Impact of HCD on Charged Trap Density and Carrier Mobility                             | 79                                      |  |  |

|                  |                          | 6.7.4 Similarities to BTI and Fitting with General Models                                    | 81                                      |  |  |

|                  | 6.8                      | Chapter Conclusions                                                                          | 83                                      |  |  |

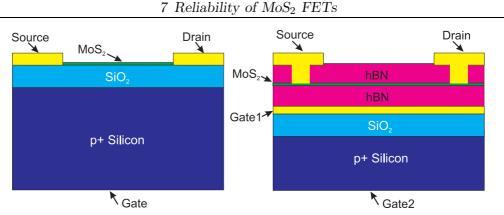

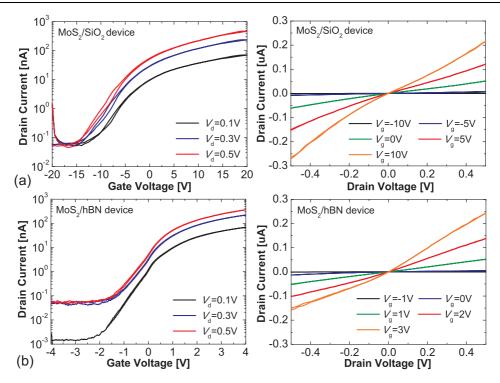

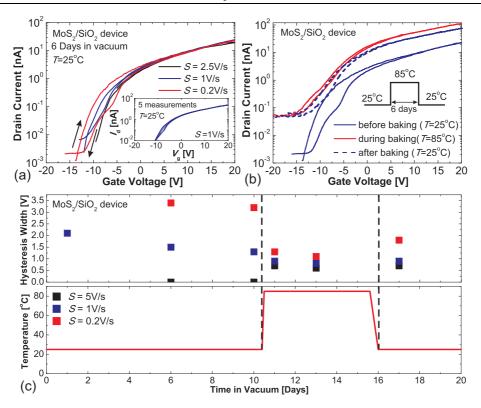

| 7                |                          | ability of $MoS_2$ FETs                                                                      | 85                                      |  |  |

|                  | 7.1                      | Introduction                                                                                 | 85                                      |  |  |

|                  | $7.2 \\ 7.3$             | Investigated Devices: Fabrication and Basic Characteristics                                  | 86<br>87                                |  |  |

|                  | 7.3<br>7.4               | Experimental Technique                                                                       | 88                                      |  |  |

|                  | $7.4 \\ 7.5$             | Analysis of Bias-Temperature Instabilities                                                   | 93                                      |  |  |

|                  | 7.6                      | Modeling of BTI Characteristics Using Minimos-NT                                             | 97                                      |  |  |

|                  | 7.7                      | Chapter Conclusions                                                                          | 98                                      |  |  |

| 8                | Con                      | clusions and Outlook                                                                         | 100                                     |  |  |

| Bibliography     |                          |                                                                                              |                                         |  |  |

| Own Publications |                          |                                                                                              |                                         |  |  |

| Cι               | Curriculum Vitae         |                                                                                              |                                         |  |  |

## **1** Introduction

Since the beginning of mass production of silicon (Si) metal-oxide-semiconductor field-effect transistors (MOSFETs), the dimensions of these devices have been continuously scaling according to Moore's Law. Hence, already in the nineties the typical channel lengths reached sub-100 nm range, which opened a new era of nanoscale MOSFETs. Their integration into the digital and analog circuits allowed for a significant miniaturization of the final products of the modern microelectronics industry. However, the probability of functional failure of these devices is larger, since scaling has made the impact of single defects on the channel electrostatics more crucial. Therefore, investigation of device reliability has become essential. The main ingredients of any reliability study of modern nanoscale MOSFETs are experimental characterization and modeling of charging/discharging of individual defects, both of which typically lead to a drift in the device characteristics. However, investigation of reliability is not possible without accounting for device-to-device variability, which is also very important in scaled devices. In this context, the first part of this work deals with modeling of the impact of the position of single defects on the reliability of nanoscale MOSFETs in the presence of randomly distributed discrete dopants, which are considered one of the main sources of variability. Comparison of the simulation results with the experimental data will allow for the derivation of a technique suitable for the evaluation of the lateral positions of these single defects.

Although the International Technology Roadmap for Semiconductors (ITRS)[84] requires further scaling of modern MOSFETs down to 5 nm channel lengths, simultaneous achievement of high transistor performance targets with these devices is extremely complicated. Therefore, in the meantime the device research community has a clear understanding that scaling of conventional Si MOSFETs according to Moore's Law is close to its end. Extension of these limits requires switching of attention to principally new transistor technologies, which could fulfill the requirements on miniaturization and high device performance simultaneously. A very interesting approach is the implementation of new two-dimensional (2D) semiconductors as channel materials for next-generation transistors. This idea has been intensively developed since 2004, when the electric field effect in high-mobility graphene was discovered by K. Novoselov and A. Geim<sup>[133]</sup>. The first practical step in this direction was taken in 2007, when the group of M. Lemme reported the first graphene field-effect device[108]. This triggered the introduction of numerous next-generation 2D FETs. However, although within the next few years a number of other successful attempts at fabricating graphene FETs were undertaken, it has been clear since the beginning that graphene devices are only suitable for integration into analog circuits. The reason for this is the lack of a bandgap in graphene, which does not allow for the high on/off ratio necessary for digital circuits to be reached. Hence, research attention has shifted to other 2D semiconductors with sizable bandgap allowing for the limitations of graphene to be overcome. The most widely used is molybdenum disulphide  $(MoS_2)$ , which was shown to be suitable for use as a channel material in 2011, when the first  $MoS_2$  FET was reported by A. Kis and colleagues [141]. Subsequent studies have shown that graphene FETs can be outperformed by MoS<sub>2</sub> devices with respect to transconductance and on current value, despite significantly smaller mobility. However, the level of fabrication technology of next-generation 2D FETs is obviously below the standards for Si technologies. Hence, contrary to modern nanoscale Si MOSFETs, the typical channel length of both graphene and  $MoS_2$  FETs are in the micrometer range. While the characterization of reliability of these devices is extremely important, the impact of single defects on their performance is not yet the most crucial issue (as it was for Si technologies in the seventies and eighties). Therefore, the building of methodology for a reliability study for these new devices has to be started from scratch, while also dealing with the issues of Si MOSFETs that have been known for decades. Thus, in the second part of this work a detailed analysis of the reliability of both graphene and  $MoS_2$  FETs will be performed. A majority of attention will be paid to experimental analysis of the impact of bias-temperature instabilities (BTI) and hot-carrier degradation (HCD) on the performance of next-generation 2D FETs. However, the experimental results will be supported by simulations.

The period of time in which this dissertation has been written falls exactly within the overlap between the era of ultra-scaled Si MOSFETs and the era of next-generation 2D FETs. While characterization of reliability is of key importance for both types of devices, in the former case one has to deal with the impact of single defects, while in the latter continuously distributed multiple defects are in the meantime more crucial. Therefore, both these questions will be touched upon in the course of this work.

The structure of this dissertation is organized as follows. The first three chapters contain a description of the theoretical background and an overview of previous research. Inclusion of such information is necessary to understand the results obtained by the author. Namely, Chapter 2 presents a brief description of the main approaches used for the simulation of the charged carrier transport through the channel of modern nanoscale Si MOSFETs in the presence of individual defects and randomly distributed discrete dopants. Basic information about the Boltzman transport equation (BTE), drift diffusion (DD) and density gradient (DG) models will be provided. In addition, the main principles of the time-dependent defect spectroscopy (TDDS), which is now used as the main experimental technique to characterize single defects in nanoscale MOS-FETs, will be discussed. Chapter 3 provides an overview of the main reliability issues in modern Si MOSFETs, followed by a description of the analytical models used for their modeling. Most essential in the context of this work are the universal relaxation model, the capture/emission time (CET) map model, and the four-state non-radiative multiphonon (NMP) model, all of which are discussed in detail. The main idea is that although the described models have been previously developed for Si MOSFETs, they will be useful for understanding of BTI and HCD in next-generation 2D technologies. In Chapter 4 a brief review of 2D materials (graphene, MoS<sub>2</sub>, hexagonal boron nitride [hBN] and others) and their properties will be provided. This will be accompanied by an overview of previous research on graphene and  $MoS_2$  FETs and their reliability. The next three chapters describe the results obtained within this work. Chapter 5 is devoted to characterization and modeling of single defects in modern nanoscale Si MOSFETs. The simulation results obtained for similar devices with a single trap and a number of configurations of randomly distributed discrete dopants are discussed. Based on comparison of these results with experimental data obtained using TDDS, a technique allowing for the evaluation of the lateral trap position with a high accuracy is derived. Chapter 6 includes a detailed analysis of BTI and HCD in graphene FETs. The experimentally measured stress/recovery data for both issues are shown to agree with universal relaxation and CET map models developed for Si technologies. Moreover, a detailed classification of HCD mechanisms in graphene FETs is provided, in particular with the help of the adjusted DD model. The results on hysteresis stability and BTI analysis in  $MoS_2$  FETs with  $SiO_2$  and hBN insulators can be found in Chapter 7. While BTI results are accompanied by modeling using the universal relaxation model, it is also shown that the reliability characteristics of  $MoS_2$  FETs can be reproduced using our simulator Minimos-NT employing the four-state NMP model. Finally, the main results are summarized.

## 2 Charged Carrier Transport and Single Defects in Si FETs

The first part of this work will be devoted to the characterization of preexisting defects in Silicon metal-oxide-semiconductor field-effect transistors (MOSFETs), and evaluation of their lateral positions. This study requires both modeling of charged carrier transport through the device channel in the presence of random dopants and single defects, and experimental analysis. Information on main simulation and experimental techniques used will be provided within this chapter.

### 2.1 Charged Carrier Transport: General Equations and Models

### 2.1.1 Single-Particle Schroedinger Equation

The channel of modern Silicon MOSFETs typically presents a multi-particle system with randomly distributed dopants and defects. This system can be described by the time-dependent Schroedinger equation, which generally reads [14]

$$\left(-\frac{\hbar^2}{2m_0}\nabla_{\boldsymbol{r}}^2 - \frac{\hbar^2}{2M_0}\nabla_{\boldsymbol{R}}^2 + \boldsymbol{H}_{ee}(\boldsymbol{r}) + \boldsymbol{H}_{ei}(\boldsymbol{r},\boldsymbol{R}) + ...\right) \Psi(\boldsymbol{r},\boldsymbol{R}) = i\hbar \frac{\partial \Psi(\boldsymbol{r},\boldsymbol{R})}{\partial t}, \qquad (2.1)$$

where  $m_0$  and  $M_0$  are the masses of electrons and ions, respectively. While  $\boldsymbol{r}$  expresses the positions of electrons and  $\boldsymbol{R}$  the positions of ions,  $\boldsymbol{H}_{ee}(\boldsymbol{r})$ ,  $\boldsymbol{H}_{ii}(\boldsymbol{R})$  and  $\boldsymbol{H}_{ei}(\boldsymbol{r},\boldsymbol{R})$  denote electron-electron scattering and the interactions of ions with other ions and electrons, respectively.

However, the solution of the multi-particle Equation 2.1 is extremely complicated. Therefore, by separation of wave functions for electrons and holes, and using Hartree-Fock and Slater approximations [119], it is typically transferred into a single-particle Schroedinger equation for electrons

$$\left(-\frac{\hbar^2}{2m_0}\nabla_x^2 + V(\boldsymbol{x}) + V_{\text{ext}}(\boldsymbol{x},t) + H_{\text{sc}}(\boldsymbol{x},\boldsymbol{k})\right)\Psi(\boldsymbol{x},\boldsymbol{k},t) = i\hbar\frac{\partial\Psi(\boldsymbol{x},\boldsymbol{k},t)}{\partial t}, \quad (2.2)$$

where  $\Psi(\boldsymbol{x}, \boldsymbol{k}, t)$  is the wave function of a single electron,  $V_{\text{ext}}(\boldsymbol{x}, t)$  is the external electrostatic potential and  $H_{\text{sc}}(\boldsymbol{x}, \boldsymbol{k})$  is a scattering Hamilton operator which combines other interactions between different particles. The quantities  $\boldsymbol{k}$  and  $V(\boldsymbol{x})$  denote the reciprocal wave vector and ionic potential [119], respectively. Furthermore, another Hamilton operator

$$H_{\rm m}(-i\nabla_x) = -\frac{\hbar^2}{2m_0}\nabla_x^2 + V(x)$$

(2.3)

is introduced, where

$$H_{\rm m}(-i\nabla_x)\Psi(\boldsymbol{x},\boldsymbol{k}) = H_{\rm m}(\boldsymbol{k})\Psi(\boldsymbol{x},\boldsymbol{k})$$

(2.4)

and  $H_{\rm m}(\mathbf{k})$  presents a dispersion relation in the *m*-th band, which allows for the inclusion of the full band structure of the semiconductor (i.e. all conduction and valence bands) [119]. This dispersion relation is given by the type of channel material [14].

#### 2.1.2 Boltzmann Transport Equation and Method of Moments

The single-particle Schroedinger Equation 2.2 can be used to derive the Boltzmann Transport Equation (BTE), which describes electron transport in a semiconductor. While the detailed stepby-step derivation of BTE can be found in [119, 14], in general form this equation reads [14]

$$\frac{\partial f^{\mathrm{m}}(\boldsymbol{x},\boldsymbol{k},t)}{\partial t} + L\{f^{\mathrm{m}}(\boldsymbol{x},\boldsymbol{k},t)\} = Q\{f^{\mathrm{m}}(\boldsymbol{x},\boldsymbol{k},t)\}, \qquad (2.5)$$

where  $f^{\mathbf{m}}(\boldsymbol{x}, \boldsymbol{k}, t)$  is the carrier distribution function in the *m*-th band,  $Q\{f^{\mathbf{m}}(\boldsymbol{x}, \boldsymbol{k}, t)\}$  is the operator describing scattering processes from a statistical point of view and  $L\{f^{\mathbf{m}}(\boldsymbol{x}, \boldsymbol{k}, t)\}$  is a free-streaming operator given as

$$L\{f^{\mathrm{m}}(\boldsymbol{x},\boldsymbol{k},t)\} = v_{\mathrm{gr}}^{\mathrm{m}}(\boldsymbol{x},\boldsymbol{k}) \cdot \nabla_{\boldsymbol{x}} f^{\mathrm{m}}(\boldsymbol{x},\boldsymbol{k},t) - \frac{\boldsymbol{F}(\boldsymbol{x},t)}{\hbar} \cdot \nabla_{\boldsymbol{k}} f^{\mathrm{m}}(\boldsymbol{x},\boldsymbol{k},t).$$

(2.6)

Here  $v_{gr}^{m}(\boldsymbol{x}, \boldsymbol{k})$  is the group velocity in the *m*-th band and  $\boldsymbol{F}(\boldsymbol{x}, t)$  is an external force given by the gradient of  $V_{\text{ext}}(\boldsymbol{x}, t)$  from Equation 2.2.

Thus, BTE describes both electron scattering by  $Q\{f^{\mathrm{m}}(\boldsymbol{x}, \boldsymbol{k}, t)\}$  and free transport of electrons in between scattering events by  $L\{f^{\mathrm{m}}(\boldsymbol{x}, \boldsymbol{k}, t)\}$ , and can be written for any of the conduction or valence bands. A self-consistent solution of the BTE for electrons and holes coupled with the Poisson equation allows for a detailed analysis of charged carrier transport through the MOSFET channel. However, discretization of the original BTE 2.5 leads to a multidimensional system of equations which requires significant computational resources. Therefore, most typically used carrier transport models are obtained by simplification of this system. This can be done using the method of moments [162]. This method denotes  $j^{\text{th}}$ -order moments of the carrier distribution function  $f(\boldsymbol{x}, \boldsymbol{k}, t)$  as

$$\langle \chi_j \rangle = \int \chi_j f(\boldsymbol{x}, \, \boldsymbol{k}, \, t) d^3 k$$

(2.7)

with  $\chi_j$  being the  $j^{\text{th}}$ -order weight function. Hence, using  $\chi_1 = 1$  leads to the first moment of the distribution function, which is either electron or hole concentration (*n* and *p*, respectively). The second moment is obtained by using  $\chi_2 = \mathbf{k}$  and denotes the average drift velocity of carriers  $\langle v_n \rangle = \mathbf{J}_n/q$  or  $\langle v_p \rangle = \mathbf{J}_p/q$ , with  $\mathbf{J}_n$  and  $\mathbf{J}_p$  being the current density for electrons and holes, respectively. Weighting of the distribution function with  $\chi_3 = E(\mathbf{k})$  leads to the third moment, which presents the average energy for electrons ( $\langle E_n \rangle$ ) or holes ( $\langle E_p \rangle$ ). Although the higher order moments can be obtained in a similar manner, these first three are typically enough for the derivation of the most widely used carrier transport models.

#### 2.1.3 Drift-Diffusion Model

The drift-diffusion (DD) model is one of the carrier transport models that can be derived from BTE using the method of moments. The main equations of the DD model are the continuity equations for electrons and holes

$$\nabla \boldsymbol{J}_{\mathrm{n}} = q \left( R + \frac{\partial n}{\partial t} \right), \tag{2.8}$$

$$\nabla \boldsymbol{J}_{\mathrm{p}} = -q \Big( R + \frac{\partial p}{\partial t} \Big), \tag{2.9}$$

which present the first two moments of the BTE, and the Poisson equation

$$\nabla(\varepsilon(\boldsymbol{x})\nabla\psi) = q(n-p+C). \tag{2.10}$$

Here R is the recombination rate,  $\varepsilon$  is the dielectric constant and C denotes the concentration of fixed charges. The unknown quantities are the carrier concentrations n and p and the electrostatic potential  $\psi$ , while the electron and hole current densities are given by

$$\boldsymbol{J}_{\mathrm{n}} = q n \mu_{n} F + q D_{n} \nabla n, \qquad (2.11)$$

$$\boldsymbol{J}_{\mathrm{p}} = qp\mu_{p}F - qD_{p}\nabla p, \qquad (2.12)$$

where the drift term is associated with the electric field F and the diffusion term is given by the concentration gradient.  $\mu_{n}$ ,  $\mu_{p}$  and  $D_{n}$ ,  $D_{p}$  are the electron and hole mobilities and diffusion coefficients, respectively.

Since the DD model incorporates only the first two moments of the BTE, it can not capture energy transport. Nevertheless, the self-consistent solution of equations 2.8- 2.10 allows for a reliable description of charged carrier transport through the device channel at reasonable computational costs. Therefore, the DD model is typically employed to reproduce the device electrostatics for its implementation into reliability models, especially when studying bias-temperature instabilities [60, 15].

The DD model is incorporated into our deterministic TCAD simulator Minimos-NT [83], which will be used when performing simulations of the output characteristics of Si MOSFETs and when studying the impact of single defects on their performance. Also, an attempt to extend the DD model for the case of graphene FETs will be made within this work, although without implementation into professional simulation software.

It should be noted that some more complex models, e.g. the hydrodynamic transport model employing three moments of the BTE, are also incorporated into Minimos-NT [83]. However, their consideration is beyond the scope of this work.

### 2.2 Modeling of Random Dopants and Discrete Traps

The Poisson equation 2.10 generally accounts for all charged particles in the device channel by regarding their macroscopic densities (e.g. the density of ionized impurities is described by their concentration C). However, this approach is only applicable for Si MOSFETs with large enough channel lengths. At the same time, for nanoscale MOSFETs with channel lengths of around 100 nm and smaller, the amount of charged impurities can be small [9, 11, 153]. Hence, one has to deal with randomly distributed discrete dopants [15], which for brevity can be denoted as "random dopants". They can originate, for example, from doping of semiconductor substrates using ion implantation.

In nanoscale devices, random dopants can severely impact the channel electrostatics, which are one of the main sources of device-to-device variability [9]. Namely, they can perturb the channel potential [9] and form a percolation path for the current[15]. This leads to different values of the threshold voltage  $V_{\rm th}$  for nominally identical devices with different configurations of random dopants. Hence, accounting for the impact of random dopants on the device electrostatics is extremely important when simulating charge carrier transport through the channel. As will

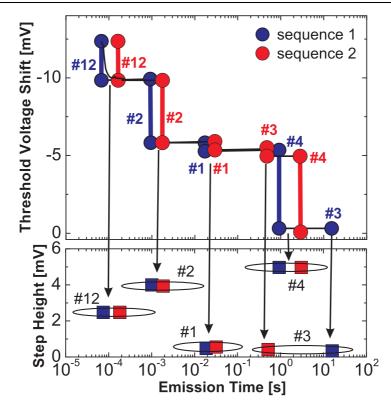

Figure 2.1: Two typical threshold voltage shift recovery traces measured using TDDS on the same nanoscale p-MOSFET (reproduced from [67]) contain discrete steps (top). They can be attributed to discharging of single defects. The extracted step heights and emission times form a spectral map containing fingerprints of each individual defect (bottom).

become clear from the analysis below, this is the key figure of merit for the characterization of preexisting defects in nanoscale MOSFETs and evaluation of their lateral positions.

Placement of random dopants into the device channel is typically done by discretizing the macroscopic channel doping concentrations ( $N_{\rm D}$  for n-MOSFET or  $N_{\rm A}$  for p-MOSFET) and using the Monte Carlo algorithm [187] to calculate the position of each particular dopant (details can be found in [14]). However, the accuracy of this method is strongly dependent on the mesh spacing of the simulation grid used. Nevertheless, the authors of [9, 11] have shown that a spacing smaller than 1 nm is typically sufficient to capture the magnitude of device-to-device variability in nanoscale MOSFETs.

A randomly placed dopant presents a point charge with the Coulomb potential, which can be screened by numerous carriers having discrete energies [14]. Hence, a classical or semiclassical description would lead to a failure of numerical solution for the Poisson equation. Therefore, modeling of random dopants using a semi-classical simulator incorporating the DD model typically requires accounting for a quantum correction of the Coulomb potential. The most suitable methodology for this is the density gradient (DG) model [9, 11, 184, 19], which allows to obtain quantum corrected drift-diffusion equations (see [14]).

Another source of device-to-device variability in nanoscale MOSFETs is associated with charged traps [121], which also have a discrete distribution along the channel. Their electrostatical interactions with random dopants can lead to variations of the threshold voltage, while the proximity of a charged trap to the dominating percolation path formed by random dopants strongly impacts the drain current [15]. In the course of this work we perform our simulations

either for perturbed device with a single discrete trap placed right at the channel/oxide interface or for unperturbed device.

## 2.3 Characterization of Preexisting Defects Using Time-Dependent Defect Spectroscopy

The channel of a modern nanoscale MOSFET contains a number of preexisting defects introduced during fabrication. Charging/discharging of these defects may significantly impact device reliability and also lead to a time-dependent variability [167]. Hence, characterization of preexisting defects is extremely important.

Time-dependent defect spectroscopy (TDDS) [67, 68, 181] is one of the most versatile methods for characterization of individual defects in nanoscale MOSFETs. The typical TDDS experiment includes charging of traps at a higher gate voltage followed by their discharging at a lower voltage. During this the subsequent charge-emission transient is recorded. Multiple repetitions of these charging/discharging sequences allow one to obtain good statistics on capture and emission times for each individual trap.

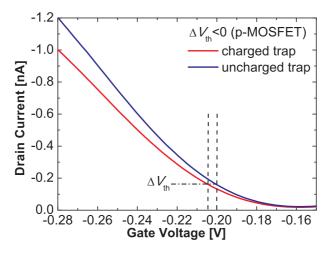

A typical evolution of the threshold voltage after charging of preexisting defects using TDDS is shown in Figure 2.1. Clearly, the recovery consists of a number of discrete steps, while each of these steps is attributed to discharging of an individual trap. Since this behaviour is reproducible when using subsequent TDDS sequences on the same device, one can extract the corresponding step heights and emission times and build a spectral map (Figure 2.1(bottom))[67]. This spectral map contains unique fingerprints for each of the defects in the device channel. Also, repetition of TDDS measurements at different drain voltages allows for the extraction of  $\Delta V_{\rm th}(V_{\rm d})$  characteristics, which will be analyzed within this work. In particular, we will clearly show that the dependence of step height on the drain bias contains the full information on the lateral defect position.

## 3 Main Reliability Issues in Si MOSFETs and Their Modeling

A significant part of this work will be devoted to reliability studies of next-generation 2D FETs. Since so far no reliability theory has been developed for these new technologies, we will start by using general models previously developed for Si MOSFETs. Hence, in this chapter a brief background of the main reliability issues in Si technologies and their modeling will be provided.

## 3.1 Overview of Reliability Issues

Understanding of reliability models requires basic knowledge on the main reliability issues observable in modern Si MOSFETs. The related information will be provided in this section.

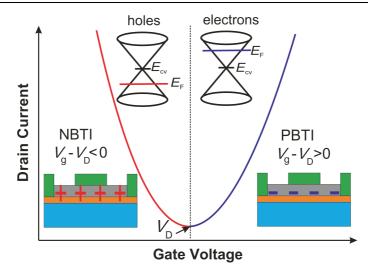

#### 3.1.1 Negative Bias-Temperature Instability

Negative bias-temperature instability (NBTI) is one of the most crucial degradation mechanisms observed in modern CMOS devices. Pure NBTI degradation typically occurs if the device is examined at high enough temperatures and if considerable negative gate voltages are applied when the source and drain terminals are grounded. While leading to a shift of the threshold voltage and variation of the subthreshold swing, NBTI may significantly impact device performance. If the device operates in extrem working conditions<sup>1</sup>, the impact of NBTI can be very strong. However, when the stress is removed, the device parameters tend to return back to their initial values, i.e. NBTI degradation is recoverable. During the last decade investigation of NBTI has attracted a considerable amount of attention [89, 59, 80, 60, 65, 66, 79, 76, 7, 58]. One of the main reasons for this is the agressive scaling of the devices, which requires the use of thinner gate oxides, thereby leading to larger oxide fields.

The impact of NBTI on the device characteristics is associated with the trapping of carriers by oxide traps [173, 63] (e.g. E' centers and switching oxide traps), which can exchange charges with the channel, and interface states [61] (e.g.  $P_{\rm b}$  centers). The positive charge variation associated with oxide traps is

$$\Delta Q_{\rm ox}(t) = q \int \int \Delta D_{\rm ox}(x, E_{\rm t}, t) f_{\rm ox}(x, E_{\rm t}, t) (1 - x/d_{\rm ox}) dx dE_{\rm t}, \qquad (3.1)$$

where  $f_{\text{ox}}(x, E_{\text{t}}, t)$  is the occupancy of oxide traps,  $\Delta D_{\text{ox}}(x, E_{\text{t}}, t)$  is the density of states in the oxide and  $d_{\text{ox}}$  is the oxide thickness. Since oxide traps are located in the oxide bulk and have larger time constants, their occupancy can not follow the Fermi level. Conversely, the charging and discharging of interface states is very fast. Hence, the captured variation of positive charge

$<sup>^1{\</sup>rm The}$  typical operation ranges of modern MOSFETs are the temperatures between 0 and 200  $^{\rm o}{\rm C}$  and gate oxide fields up to 10 MV/cm.

follows the Fermi level  $E_{\rm F}$  and can be given by

$$\Delta Q_{\rm it}(t) = q \int \Delta D_{\rm it}(E_{\rm t}, t) f_{\rm it}(E_{\rm F}, E_{\rm t}, t) dE_{\rm t}, \qquad (3.2)$$

where  $f_{\rm it}(E_{\rm F}, E_{\rm t}, t)$  is the occupancy of interface states and  $\Delta D_{\rm it}(E_{\rm t}, t)$  the time-dependent density.

The strongest impact of NBTI is observed for p-MOSFETs, which typically operate at negative gate voltages. However, some NBTI degradation, although less significant, can be observed for n-MOSFETs [34, 80] (in that case negative gate voltage corresponds to the accumulation region).

#### 3.1.2 Positive Bias-Temperature Instability

Positive bias-temperature instability (PBTI) is a counterpart of NBTI which occurs at positive gate voltages. Although this degradation issue is expected to impact n-MOSFETs, it has already been shown in [34, 80] that for SiON devices threshold voltage shifts induced by PBTI in n-MOSFETs can be several orders of magnitude smaller than NBTI shifts in p-MOSFETs. Moreover, they are even smaller than PBTI shifts in p-MOSFETs, which correspond to accumulation stress voltage and hence are not of any practical interest. Therefore, investigation of PBTI in Si MOSFETs with SiON insulators is much less intensive compared to NBTI studies. However, PBTI is often reported to be a serious reliability issue in Si MOSFETs with high-k gate insulators[75, 175]. Furthermore, it will be shown that this degradation issue can be very crucial in next-generation 2D FETs.

### 3.1.3 Hot-Carrier Degradation

Hot-carrier degradation (HCD) is a reliability issue which takes place if a non-zero voltage is applied at the drain. Since most device operation conditions assume some voltage applied at the gate, HCD typically occurs in conjuction with NBTI or PBTI [1].

HCD is associated with defects situated closely to the channel/oxide interface and becomes more pronounced for larger drain voltages. During device operation this interface is bombarded by highly-energetic (i.e. "hot") carriers, which leads to a rupture of hydrogene (Si-H) bonds and the formation of dangling bonds, i.e. interface states [1, 172, 171]. These interface states are inhomogeneously distributed along the channel with a maximum density in the proximity of the drain [171, 16]. The latter occurs because the electric field near the drain is largest, making carrier energies higher.

Trapping of carriers by interface states created by HCD leads to a shift of the threshold voltage. On the other hand side, scattering of carriers on charged interface states reduces transconductance and mobility. However, contrary to NBTI and PBTI, HCD in Si MOSFETs is typically non-recoverable, since only a strong permanent component associated with a number of dangling bonds is present.<sup>2</sup>

<sup>&</sup>lt;sup>2</sup>Some recent papers (e.g. [194]) show that HCD in Si MOSFETs tends to recover at higher temperatures. However, the underlying physical mechanisms require more detailed understanding.

### 3.1.4 Other Reliability Issues

Other reliability issues which are typically observed in Si MOSFETs are time-dependent dielectric breakdown (TDDB), random telegraph noise (RTN) and 1/f noise. However, they will not be studied in the course of this work.

TDDB is a degradation mechanism which leads to the failure of the gate dielectric resulting from operation for a long time [155, 156].<sup>3</sup> Obviously, in real device operation conditions, TDDB usually acts in conjuction with BTI and/or HCD.

RTN is observed in extremely scaled devices, where the capture and emission of carriers by individual traps results in a discrete modulation of the drain current at fixed drain or gate voltage. Contributions of multiple traps may lead to a multi-level RTN [78]. However, this is not an issue for large devices with a great number of defects.

1/f noise (or flicker noise) is the counterpart of RTN which is characterized by a continuous spectral density behaving as 1 over frequency (1/f) [154, 186]. Contrary to RTN, it can be observed in large area devices.

## 3.2 Modeling of BTI in Si MOSFETs

In this section we will provide information on general models which are employed to describe BTI degradation/recovery dynamics in Si MOSFETs. In the following chapters these models will be adjusted to characterize the reliability of next-generation 2D FETs.

#### 3.2.1 Universal Relaxation Model

The universal relaxation model [61, 64] has been derived for fitting of NBTI degradation/recovery in Si technologies. In order to distinguish between the degradation during the stress and relaxation phases, the authors of [61] operate with the degradation magnitude accumulated during the stress  $S_0(t_s)$  and relaxation magnitude  $R_0(t_s, t_r)$ . It is assumed that the relaxation starts as soon as the stress voltage is removed. Hence, the relaxation magnitude is treated as a function of both stress time  $t_s$  and relaxation time  $t_r = t - t_s$ .

However, most experimental techniques typically introduce some measurement delay  $t_{\rm M}$  between the end of the stress and the beginning of recovery observation. Since the recovery of NBTI degradation starts faster than microseconds after the BTI stress is removed [146], some fraction of recovery is lost.<sup>4</sup> Hence, one has to operate with  $R_{\rm M}(t_{\rm s}) = R_0(t_{\rm s}, t_{\rm M})$  and  $S_{\rm M}(t_{\rm s}) = S_0(t_{\rm s}, t_{\rm M})$  [61] when normalizing the obtained recovery data by the first measurement point. Also, a fractional recovery  $r_{\rm f}(t_{\rm s}, t_{\rm r}) = R_0(t_{\rm s}, t_{\rm r})/R_{\rm M}(t_{\rm s})$  can be introduced [146, 61].

According to [33], the normalized NBTI recovery obtained using different stress times has the same dependence on the normalized relaxation time  $\xi = t_r/t_s$ . However, the recovery of NBTI is typically not complete, and has some permanent component  $P(t_s) = S_0(t_s) - R_0(t_s, 0)$  [143, 62, 58]. Therefore, in the spirit of [33] and taking into account the permanent component, the

<sup>&</sup>lt;sup>3</sup>Obviously, a very strong oxide field would lead to an immediate breakdown of the gate dielectric. However, the critical oxide fields are typically known and hence this issue can be avoided.

<sup>&</sup>lt;sup>4</sup>Below it will be shown that this measurement delay can be very important when characterizing BTI and HCD recovery in graphene FETs.

authors of [61] have introduced a general universal relaxation function, which is given by

$$r(\xi) = \frac{R_0(t_{\rm s}, t_{\rm r})}{S_0(t_{\rm s}) - P(t_{\rm s})} = \frac{R_0(t_{\rm s}, t_{\rm r})}{R_0(t_{\rm s}, 0)}.$$

(3.3)

After a number of attempts have been made to empirically find the exact form of universal relaxation function [2, 169, 170], in [61] it has been demonstrated that the one suitable for the whole spectra of experimental data available for NBTI is

$$r(\xi) = \frac{1}{1 + B\xi^{\beta}},\tag{3.4}$$

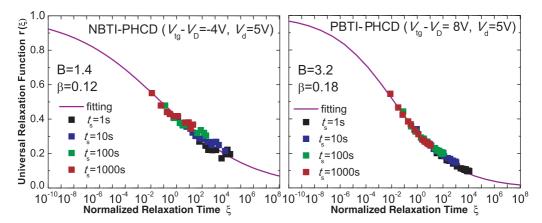

where B and  $\beta$  are the fitting parameters which have to be adjusted for each particular case<sup>5</sup>, while  $r_{\rm f}(t_{\rm s}, t_{\rm r}) = r(\xi)/r(\xi_{\rm M})$  with  $\xi_{\rm M} = t_{\rm M}/t_{\rm s}$ . Equation 3.4 can be successfully applied to fit normalized NBTI recovery in Si technologies and also to predict time to failure of the device. However, one should note that in [61] equation 3.4 has been empirically derived assuming a zero permanent component. At the same time, according to equation 3.3,  $P(t_{\rm s})$  has to be subtracted from the experimental data before analyzing universality.

Another important consequence following from the universal relaxation model is that it allows for the extrapolation of the degradation magnitude at a zero measurement delay. While the degradation magnitude is expected to follow a power law  $S_0(t_s) = At_s^n$ , in [61] it has been shown that experimentally observed threshold voltage shifts measured at  $t = t_M$  can be expressed by

$$S_{\rm M}(t_{\rm s}) = S_0(t_{\rm s})r(t_{\rm s}, t_{\rm M}) = \frac{At_{\rm s}^{\rm n}}{1 + B\xi_{\rm M}^{\beta}},$$

(3.5)

with B and  $\beta$  given by equation 3.4. This expression allows to combine experimental data measured with different delays  $t_{\rm M}$ .

One should note that although the universal relaxation model was originally developed for NBTI in p-MOSFETs, in [64] it was also found to be suitable for capturing both NBTI and PBTI in p- and n-MOSFETs.

### 3.2.2 Capture/Emission Time Map Model

The capture/emission time (CET) map model [69] assumes that BTI is due to both interface states and oxide traps which can exchange charges with the channel. Each of these defects is assumed to have two stable states, i.e. charged and neutral. The charge exchange events between different states are treated as first-order non-radiative multiphonon (NMP) processes [66] with the capture and emission times given by

$$\tau_{\rm c} = \tau_0 \exp\left(\frac{E_{\rm c}}{k_{\rm B}T}\right),\tag{3.6}$$

$$\tau_{\rm e} = \tau_0 \exp\left(\frac{E_{\rm e}}{k_{\rm B}T}\right). \tag{3.7}$$

Here  $\tau_0$  is the effective time constant which weakly depends on BTI stress conditions, and  $E_c$  and  $E_e$  are capture and emission energy barriers, respectively.

In the CET map model, BTI is assumed to be the collective response of different oxide traps and interface states, while capture and emission are considered as thermally activated processes [66, 147]. Hence, the distributions of  $E_c$  and  $E_e$  are employed to obtain CET maps using

<sup>&</sup>lt;sup>5</sup>According to [61], the typical values for B are within 0.3–3 and for  $\beta$  within 0.15–0.2.

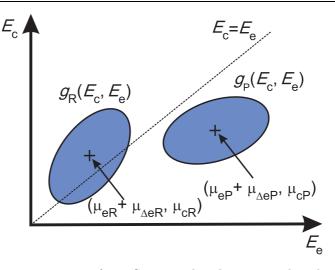

Figure 3.1: Schematic representation of two Gaussian distributions used in the CET map model. One  $(g_{\rm R}(E_{\rm c}, E_{\rm e}))$  is for the recoverable component and the other  $(g_{\rm P}(E_{\rm c}, E_{\rm e}))$  is for the permanent component.

equations 3.6–3.7. This allows to avoid direct modeling of widely distributed time constants  $\tau_{\rm c}$  and  $\tau_{\rm e}$  and also leads to a built-in temperature dependence of the model. At the same time, the dependence on stress voltage has to be introduced by adjusting model parameters [69].

Initially, the CET maps were extracted numerically by differentiating the obtained recovery traces for threshold voltage shift [147]. The analysis of the results obtained at different temperatures has shown that the capture and emission times are correlated. Namely, a decrease of the emission time at higher temperature leads to a reduced capture time [96] and vice versa. Therefore, it was suggested to express this correlation by linking the activation energies of capture and emission processes as  $E_e = E_c + \Delta E_e$ , with  $\Delta E_e$  being an uncorrelated part of  $E_e$ . Since many experimental features of BTI degradation/recovery dynamics could be captured by a Gaussian distribution, the authors of [69] assume that the quantities  $E_e$ ,  $E_c$  and  $\Delta E_e$  are normally distributed with the mean values  $\mu_e$ ,  $\mu_c$  and  $\mu_{\Delta e}$ , and standard deviations  $\sigma_e$ ,  $\sigma_c$  and  $\sigma_{\Delta e}$ , respectively. This allows for the constructing of a bivariate Gaussian distribution, which is given by

$$g(E_{\rm c}, E_{\rm e}) = \frac{1}{2\pi\sigma_{\rm c}\sigma_{\Delta \rm e}} \exp\Big(-\frac{(E_{\rm c}-\mu_{\rm c})^2}{2\sigma_{\rm c}^2} - \frac{(E_{\rm e}-(E_{\rm c}+\mu_{\Delta \rm e}))^2}{2\sigma_{\Delta \rm e}^2}\Big).$$

(3.8)

Obviously, the marginal distributions  $g(E_e)$  and  $g(E_c)$  can be obtained by integrating  $g(E_c, E_e)$ over  $E_c$  and  $E_e$ , respectively. At the same time, the main parameters of  $g(E_e)$  can be expressed by  $\mu_e = \mu_c + \mu_{\Delta e}$  and  $\sigma_e^2 = \sigma_c^2 + \sigma_{\Delta e}^2$ .<sup>6</sup>

However, fitting of the BTI recovery in Si technologies typically requires two bivariate Gaussian distributions given by equation 3.8. As shown in Figure 3.1, one  $(g_{\rm R}(E_{\rm c}, E_{\rm e}))$  is necessary to express the contribution of the recoverable component and the other is used for the permanent component  $(g_{\rm P}(E_{\rm c}, E_{\rm e}))$ . Typically, the mean values and standard deviations for these two distributions are different, i.e. one has to operate with  $\mu_{\rm cR}$ ,  $\mu_{\rm cP}$ ,  $\sigma_{\rm cR}$ ,  $\sigma_{\rm cP}$  and so on.

Taking into account equations 3.6-3.7, which link the time constants with corresponding activation energies, bivariate Gaussian distributions of  $E_c$  and  $E_e$  can be used to calculate the CET map. Obviously, this CET map will present nothing else than a combination of two bivariate

<sup>&</sup>lt;sup>6</sup>Below we will see that this correlation between  $\sigma_e$  and  $\sigma_c$  can be readjusted, which will allow to fit HCD recovery in graphene FETs.

Gaussian distributions for  $\tau_c$  and  $\tau_e$ . Hence, the threshold voltage shift can be obtained by integrating these distributions over all defects with  $\tau_c < t_s$  and  $\tau_e > t_r$ , and reads

$$\Delta V_{\rm th} = A_{\rm R} \int_{-\infty}^{t_{\rm s}} \int_{t_{\rm r}}^{\infty} g_{\rm R}(\tau_{\rm c}, \tau_{\rm e}) d\tau_{\rm c} \, d\tau_{\rm e} + A_{\rm P} \int_{-\infty}^{t_{\rm s}} \int_{t_{\rm r}}^{\infty} g_{\rm P}(\tau_{\rm c}, \tau_{\rm e}) d\tau_{\rm c} \, d\tau_{\rm e}, \tag{3.9}$$

where  $A_{\rm R}$  and  $A_{\rm P}$  are the fitting parameters which express the magnitudes of the contributions associated with the recoverable and permanent components, respectively.

However, in some cases it is more convenient to integrate the original distributions obtained for the activation energies. Thus the equation 3.9 can be rewritten as

$$\Delta V_{\rm th} = A_{\rm R} \int_{-\infty}^{a_{\rm R}} \int_{b_{\rm R}}^{\infty} g_{\rm R}(E_{\rm c}, E_{\rm e}) dE_{\rm c} dE_{\rm e} + A_{\rm P} \int_{-\infty}^{a_{\rm P}} \int_{b_{\rm P}}^{\infty} g_{\rm P}(E_{\rm c}, E_{\rm e}) dE_{\rm c} dE_{\rm e}, \qquad (3.10)$$

where  $a_{R|P}$  and  $b_{R|P}$  are obtained by recalculating the integration limits using equations 3.6–3.7 and given by

$$a_{\rm R|P} = k_{\rm B} T \log\left(\frac{t_{\rm s}}{t_{0\rm R|P}}\right),\tag{3.11}$$

$$b_{\rm R|P} = k_{\rm B} T \log\left(\frac{t_{\rm r}}{t_{0\rm R|P}}\right). \tag{3.12}$$

In general, integration in equations 3.9–3.10 has to be done numerically. However, in [69] one can find an analytical approximation.

According to the description above, the CET map model allows for the simulation of  $\Delta V_{\rm th}(t_{\rm r})$  recovery traces for different stress times. Hence, by adjusting the distribution widths and positions (i.e. mean values and standard deviations) one can approximate the measured BTI recovery. Moreover, extrapolation of  $\Delta V_{\rm th}$  at zero measurement delay is possible, similarly to the universal relaxation model. However, a significant advance of the CET map model compared to the universal relaxation model is that the former incorporates a temperature dependence, which results in more stable fits.

#### 3.2.3 Four-state NMP Model

The models described above allow for the fitting of a wide range of NBTI and PBTI stress/recovery characteristics. However, they are not always consistent with a number of features which have been extracted from TDDS measurements when characterizing single defects. The most important of them is associated with significant differences in emission times for the defects with similar capture times as well as bias dependence of emission times for some defects. Hence, a more general four-state NMP model was derived in [66].

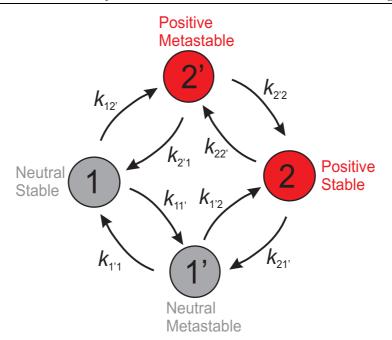

The four-state NMP model considers interaction of a single carrier with an individual defect. Contrary to the two-state CET map model, this defect is assumed to have four different states. Namely, both neutral and charged configurations of the defect are characterized by one stable and one metastable state. In Figure 3.2 this situation is illustrated for the case of hole trapping. One can see that there are eight different transitions which may occur. While all the transitions between stable and metastable states of one configuration (11', 22', 1'1 and 2'2) are associated with structural relaxation of the defect, transitions between the states with different configurations (12', 2'1, 1'2, 21') correspond to a charge exchange between the defect and the device channel. Also, each of these transitions is described by a certain transition rate  $k_{ij}$ . These transition rates are calculated by assuming that the defect time dynamics can be

Figure 3.2: Schematic configuration of a single defect assumed in the four-state NMP model (the case of hole trapping is considered). Charging and discharging of the defect occurs through a metastable state. For example, in the positive metastable state 2' the defect can either go through a structural relaxation and become stable (state 2) or emit a hole and return back to neutral stable state 1. In a neutral metastable state 1' it can either capture a hole and become positively charged and stable (state 2) or return back to state 1 by experiencing structural relaxation. The transitions between two stable or two metastable states are disregarded.

described using a continuous-time Markov process X(t) [55], i.e. the defect can only be in one state at a certain point in time. Hence, the probability of finding the defect in a certain state  $p_i(t) = P\{X(t) = i\}$  and  $\Sigma_i p_i(t) = 1$ , where i = 1, 1', 2, 2'. Following the theory of Markov processes described in [55], the authors of [66] derived a master equation for all four probabilities  $p_i(t)$ , which reads

$$\frac{\partial p_i(t)}{\partial t} = \sum_{j=1}^4 \left( p_j(t)k_{ji} - p_i(t)k_{ij} \right). \tag{3.13}$$

The rates for each of the transitions marked in Figure 3.2 can be calculated using NMP theory<sup>7</sup>. It has been found that the transition rates for the transitions between stable states and metastable states of opposite configurations depend on the applied gate voltage and can be given by

$$k_{12'} = \sigma_{\rm p} v_{\rm tp} p \exp\left(-\frac{\varepsilon_{12'}}{k_{\rm B}T}\right),\tag{3.14}$$

$$k_{1'2} = \sigma_{\rm p} v_{\rm tp} p \exp\left(-\frac{\varepsilon_{1'2}}{k_{\rm B}T}\right),\tag{3.15}$$

$$k_{2'1} = \sigma_{\rm p} v_{\rm tp} p \exp\left(-\frac{\varepsilon_{12'}}{k_{\rm B}T}\right) \exp\left(-\frac{E_{\rm T} - E_{\rm F} - \varepsilon_{\rm T2'}}{k_{\rm B}T}\right),\tag{3.16}$$

$$k_{21'} = \sigma_{\rm p} v_{\rm tp} p \exp\left(-\frac{\varepsilon_{1'2}}{k_{\rm B}T}\right) \exp\left(-\frac{E_{\rm T}' - E_{\rm F}}{k_{\rm B}T}\right).$$

(3.17)

<sup>&</sup>lt;sup>7</sup>The details can be found in [56].

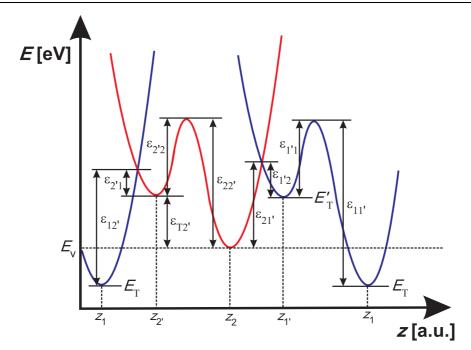

Figure 3.3: Definition of potential barriers used in the four-state NMP model. The adiabatic potentials describing different states are plotted versus a reaction coordinate. The potential describing neutral states (1 and 1') is plotted twice, since the transitions between  $1 \leftrightarrow 2'$  and  $2 \leftrightarrow 1'$  are characterized by different reaction coordinates.

Furthermore, the transitions between stable and metastable states of one configuration are only activated by temperature and can be written  $as^8$

$$k_{11'} = v_0 \exp\left(-\frac{\varepsilon_{11'}}{k_{\rm B}T}\right),\tag{3.18}$$

$$k_{1'1} = v_0 \exp\left(-\frac{\varepsilon_{1'1}}{k_{\rm B}T}\right),$$

(3.19)

$$k_{22'} = v_0 \exp\left(-\frac{\varepsilon_{22'}}{k_{\rm B}T}\right),\tag{3.20}$$

$$k_{2'2} = v_0 \exp\left(-\frac{\varepsilon_{2'2}}{k_{\rm B}T}\right).$$

(3.21)

Here  $\sigma_{\rm p}$  is a hole capture cross-section,  $v_0 \approx 10^{13} \,\mathrm{s}^{-1}$  is the attempt frequency [56], and p and  $v_{\rm tp}$  are hole concentration and thermal velocity, respectively<sup>9</sup>. The trap levels in neutral stable and metastable states are given by  $E_{\rm T}$  and  $E'_{\rm T}$ , while  $\varepsilon_{ij}$  are the activation barriers. The configuration of these parameters is shown in Figure 3.3, where the adiabatic potentials for different states of the defect are plotted versus the reaction coordinate z.

The bias dependent barriers  $\varepsilon_{12'}$  and  $\varepsilon_{1'2}$  are calculated by quadratic expansion of the adiabatic potentials around the minima corresponding to different states  $(z_i)$ , while the other barriers are obtained as explicit parameters [66]. Then the calculated transition rates can be used to express individual contributions of each defect state to the time constants [66].

Although originally the four-state NMP model was developed to capture the experimental features of single defects observed in TDDS data, its complexity allows for a reliable description

<sup>&</sup>lt;sup>8</sup>Similarly to equations 3.6-3.7.

<sup>&</sup>lt;sup>9</sup> Trapping of electrons is considered by four-state NMP model in a similar manner.

of a wide spectrum of effects related to the trapping of carriers in the device channel. Hence, PBTI and NBTI can be properly modeled using this approach. Also, a major advantage of the four-state NMP model compared to the CET map model and other previously used approaches is that it can be coupled with DD simulations. This allows its implementation into professional simulation software and makes the four-state NMP model potentially suitable for the simulations of next-generation 2D FETs reliability. Although a number of further efforts still have to be undertaken to adjust this model to 2D channel geometries, in this work the validity of this approach will be illustrated on an example of  $MoS_2$  FETs.

It should be noted that although in Si technologies modeling of HCD requires a separate description<sup>10</sup>, we assume that in 2D technologies the absence of dangling bonds makes BTI and HCD more similar. Therefore, according to our current understanding, the models derived for BTI in Si MOSFETs, after some adjusting, should be suitable to capture the dynamics of both BTI and HCD in 2D FETs. Especially valuable in this context is the four-state NMP model.

<sup>&</sup>lt;sup>10</sup>The most advanced models currently used are based on the solution of the BTE using a spherical harmonic expansion method [16]. This avoids the time-consuming Monte-Carlo simulations of non-equilibrium distribution functions, and increases the accuracy.

## 4 Next Generation FETs Based on 2D Materials

A significant portion of this work will be devoted to the characterization of the reliability of next-generation FETs based on 2D materials, which are currently being intensively studied. Therefore, in the course of this chapter a brief review of 2D materials from graphene and beyond, which are suitable for applications in modern micro- and nanoelectronic devices, will be provided. Also, an overview of research on transistors with graphene and  $MoS_2$  and their properties will be provided. This information will be useful for understanding the results described in the following chapters.

## 4.1 Overview of 2D Materials: Graphene, MoS<sub>2</sub> and Beyond

The term "2D materials" combines a wide range of crystalline materials with exciting electrophysical, magnetic and optical properties [20, 71]. Although the first studies of 2D materials are known since the late sixties [123, 185], an intensive research in this direction has started only in the last decade [195, 22, 99, 182]. The main reason for this is the understanding that sooner or later conventional scaling of Si devices, as known from Moore's Law, will come to an end. This creates a demand to go beyond conventional CMOS technology by using principally different material systems. In particular, the primary advantage of 2D materials, i.e. the creation of atomically thin channel layers below 1 nm and the stacking of them in versatile ways, has introduced an extremely rich spectrum of new possibilities in modern science and technology [22].

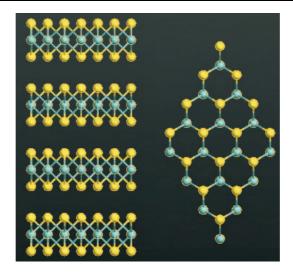

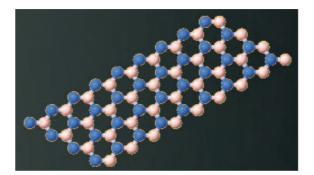

Based on literature reports [133, 21, 3, 130, 12, 18, 22, 32, 35, 49, 126, 190, 135, 87, 138, 51, 88, 91, 99, 182, 20], the major fraction of 2D materials can be classified into three main subclasses. The first and the largest of them is 2D chalcogenides, which include such semiconducting transition metal dichalcogenides (TMDs) as MoS<sub>2</sub>, WS<sub>2</sub>, WSe<sub>2</sub>, MoSe<sub>2</sub> [3, 35, 49, 51, 91], metallic dichalcogenides like NbSe<sub>2</sub>, TaS<sub>2</sub>, NiSe<sub>2</sub>, NbS<sub>2</sub> [22, 35, 49] and layered semiconductors (GaSe, GaTe, InSe, etc)[49]. The second subclass combines graphene-like materials, including graphene itself[133, 12, 18, 88, 28], its derivatives (e.g. wide bandgap fluorographene[130]), boron carbon nitride (BCN)[87], hexagonal boron nitride (hBN) [32, 126, 182] and graphene oxide [138]. Finally, 2D oxides like, e.g. metallic oxides (MoO<sub>3</sub>, WO<sub>3</sub>, TiO<sub>2</sub>, etc)[135], Perovskite-type oxides (LaNb<sub>2</sub>O<sub>7</sub>, Ca<sub>2</sub>Ta<sub>2</sub>TiO<sub>10</sub>, etc) [135] and hydroxides (Ni(OH)<sub>2</sub>, Eu(OH)<sub>2</sub>, etc.) [49] form the third class of 2D materials. Also, research attention has now shifted to principally new 2D materials, like phosphorene [115, 145], silicene [179, 38, 85] and germanene [31].

Since in the course of this work we are dealing with next-generation 2D FETs, those 2D materials suitable for application either as a device channel or gate dielectric are of the largest interest. Therefore, the following detailed description will be mainly devoted to such channel materials as graphene and semiconducting TMDs (mainly  $MoS_2$ ). Although devices based on phosphorene, silicene and germanene will not be studied in this work, some brief information about these materials will be provided. This should be useful for understanding of the future development

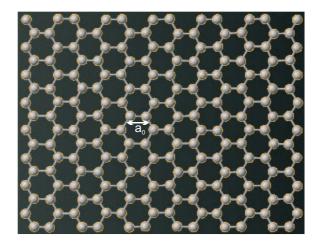

Figure 4.1: 2D hexagonal structure of graphene formed by carbon atoms (reproduced using Quantum-Wise Virtual Nanolab). The lattice constant  $a = \sqrt{3}a_0 = 2.46$  Å.

of 2D transistor technologies in general. In addition, the properties of hBN, which is now considered as a next-generation 2D gate insulator [126], will be briefly discussed.

### 4.1.1 Graphene: Structure and Main Properties

Graphene was already theoretically predicted in 1969 [123], when a detailed analysis of previously published low-energy electron diffraction (LEED) data from single-crystal metallic substrates exposed to hydrocarbons [72, 128] was performed. However, the field effect in highly-stable graphene layers was first reported only in 2004 [133]. Since then graphene has attracted considerable attention due to its unique physical and electrical properties, such as an extremely high room-temperature carrier mobility [50, 133] and high saturation velocity [36].

Graphene is a 2D crystalline allotrope of carbon with a hexagonal lattice structure consisting of a single layer of carbon atoms (Figure 4.1). Each of these atoms has three  $\sigma$ -bonds with its closest neighbours and one  $\pi$ -bond with an orientation outside the 2D plane of graphene. The former is associated with a combination of s,  $p_x$  and  $p_y$  orbitals of carbon atoms, while the latter is made by the last  $p_z$  electron. Thus,  $sp^2$  bonding of carbon atoms, together with their tight packing in hexagonal lattice (distance between two closest neighbours is just  $a_0 = 1.42$  Å), leads to an extremely high stability of graphene layers. On the other hand side, hybridization of  $\pi$ -bonds leads to the formation of  $\pi$ - and  $\pi^*$ - bands. These bands make free transport of carriers possible, leading to most of the fascinating electrical properties of graphene [28].

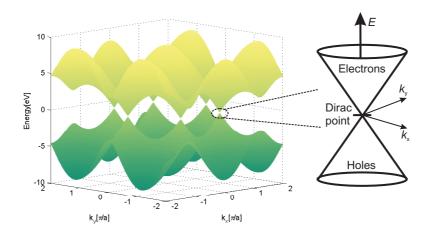

The band structure of graphene can be calculated from the solution of the Schroedinger equation using the tight binding approach [180], which takes into account only the interactions between the closest neighbours. The resulting energy dispersion expressed using the x and y components of the wave vector k reads

$$E(k_{\rm x},k_{\rm y}) = \pm \gamma \sqrt{1 + 4\cos\left(\frac{\sqrt{3}ak_{\rm y}}{2}\right)\cos\left(\frac{ak_{\rm x}}{2}\right) + 4\cos^2\left(\frac{ak_{\rm x}}{2}\right)},\tag{4.1}$$

where  $\gamma = 3 \text{ eV}$  is a tight binding parameter and  $a = \sqrt{3}a_0 = 2.46 \text{ Å}$  is the lattice constant. This energy dispersion is shown in Figure 4.2. Clearly, at the edges of the Brillouin zone the conduction and valence bands touch each other, which means that the bandgap of graphene is equal to zero. The corresponding energy is conventionally known as the Dirac point, or

Figure 4.2: Left: Band structure of graphene reproduced based on the dispersion relation 4.1 following from the solution of the Schroedinger equation using the tight binding approach. Right: Schematic representation of the linear energy dispersion (equation 4.2) in the proximity of the Dirac point.

charge neutrality point[132]. When an intrinsic graphene is in equilibrium, its Fermi level is alligned at the Dirac point, which corresponds to the middle of the bandgap in conventional semiconductors.

Near the Dirac point, equation 4.1 can be approximated as

$$E(k) = \pm \hbar v_{\rm f} k, \tag{4.2}$$

where  $\hbar$  is the Planck constant,  $v_{\rm f} = 10^8 \,{\rm cm/s}$  is the Fermi velocity in graphene [132] and k is the absolute value of the wave vector having the components  $k_{\rm x}$  and  $k_{\rm y}$ . This linear dispersion law is similar to that of photons. Therefore, electrons and holes in the proximity of the graphene Dirac point have zero effective mass, while their velocity is independent of the energy. This is in contrast to parabolic dispersion laws containing an effective mass, which are typical for most other systems.

While in a conventional 2D electron gas with a parabolic dispersion law the density of states is independent of energy, in the case of graphene the linear dispersion law leads to a linear dependence of the density of states versus energy [6]

$$D(E) = \pm \frac{g_{\rm s} g_{\rm v} E}{2\pi \hbar^2 v_{\rm f}^2},\tag{4.3}$$

where  $g_s = g_v = 2$  are spin and valley degeneration degrees, respectively. Therefore, at zero energy no carriers are present.<sup>1</sup> At the same time, electrons and holes in graphene have to be considered as fermions with zero effective mass, which leads to the following equations for their concentrations n and p, respectively [196]

$$n = \int_0^\infty \frac{D(E)}{1 + \exp\left(\frac{E - E_{\rm F}}{k_{\rm B}T}\right)} dE, \qquad (4.4)$$

<sup>&</sup>lt;sup>1</sup>Here the energy is equal to zero at the Dirac point (sometimes referred as  $E_{cv}$ ), while being larger than zero for electrons (conduction band) and smaller for holes (valence band). Thus in equations 4.1– 4.3 "+" should be taken for electrons and "-" for holes.

$$p = \int_{-\infty}^{0} \frac{D(E)}{1 + \exp\left(\frac{E_{\rm F} - E}{k_{\rm B}T}\right)} dE.$$

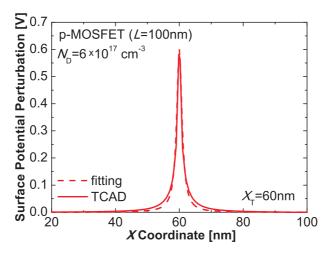

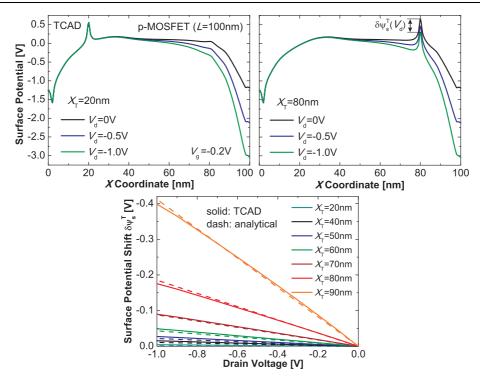

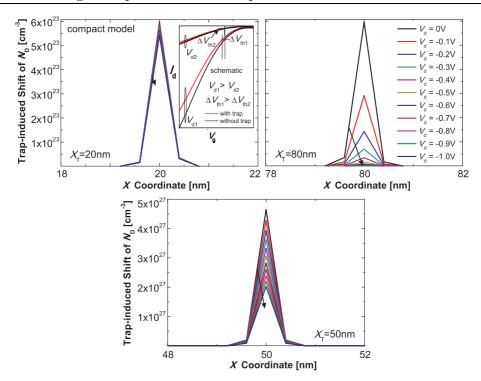

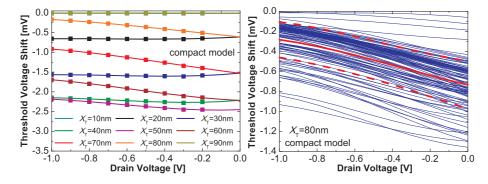

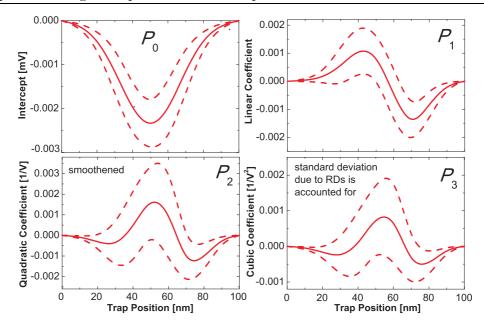

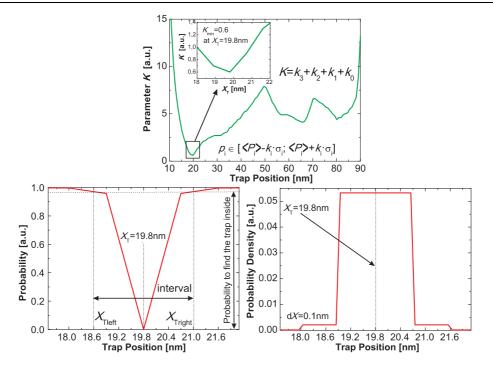

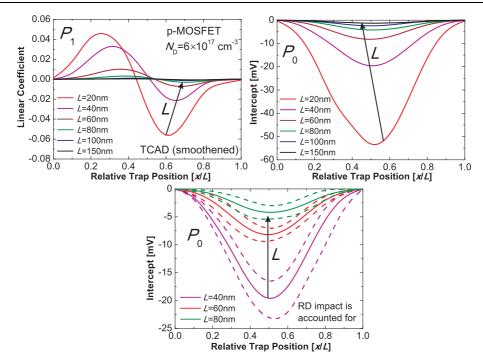

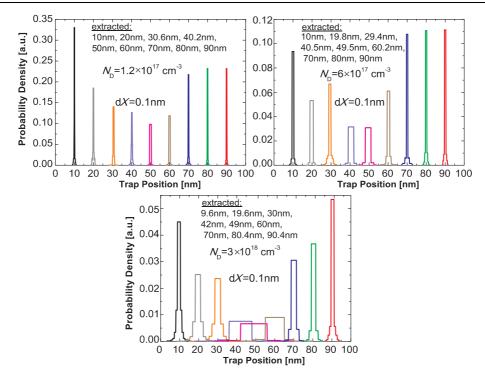

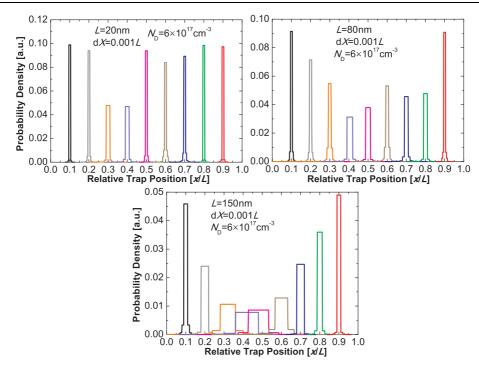

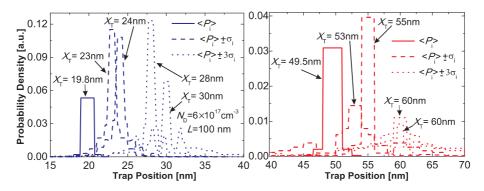

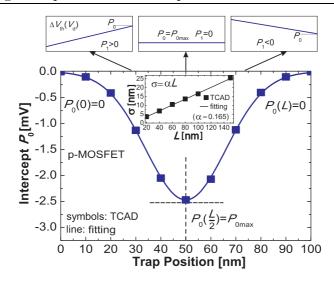

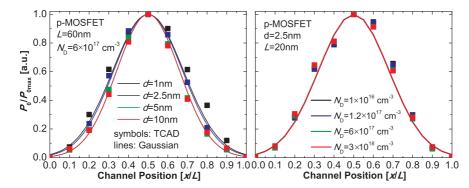

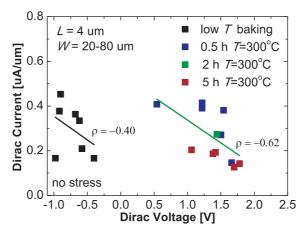

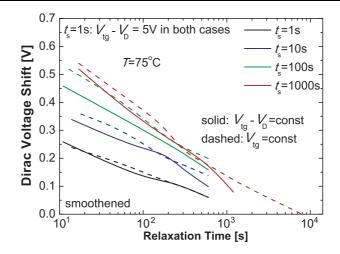

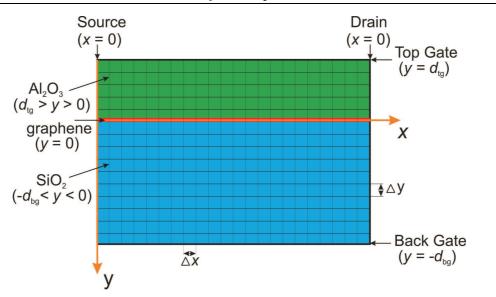

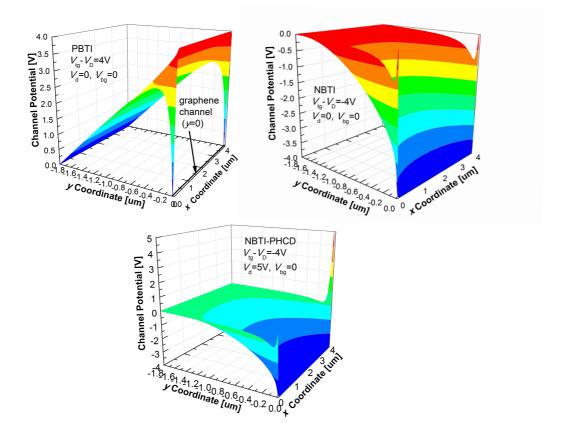

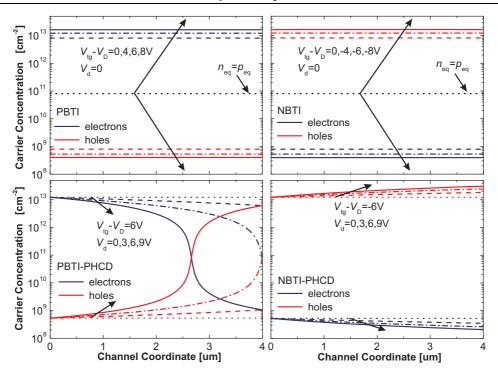

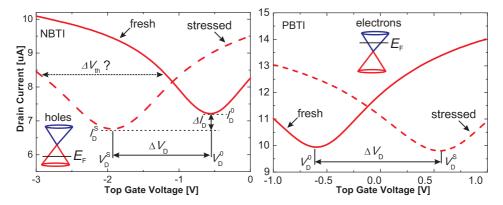

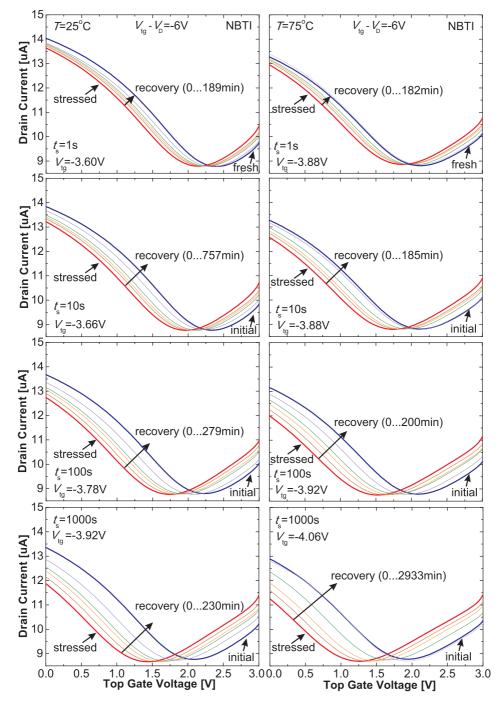

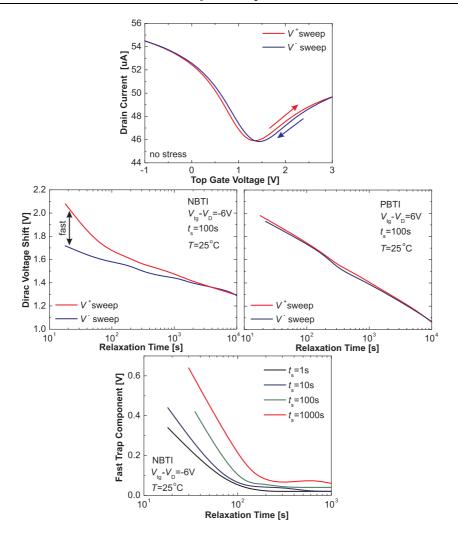

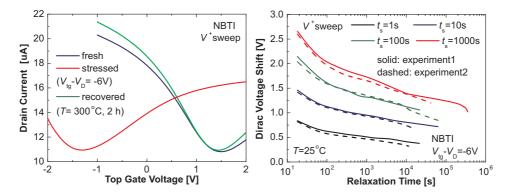

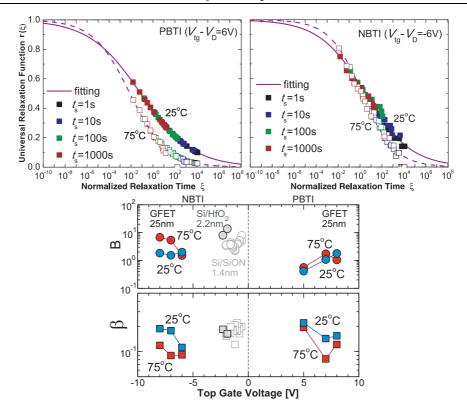

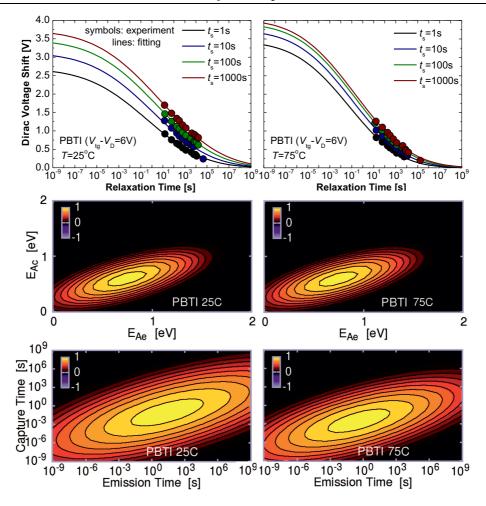

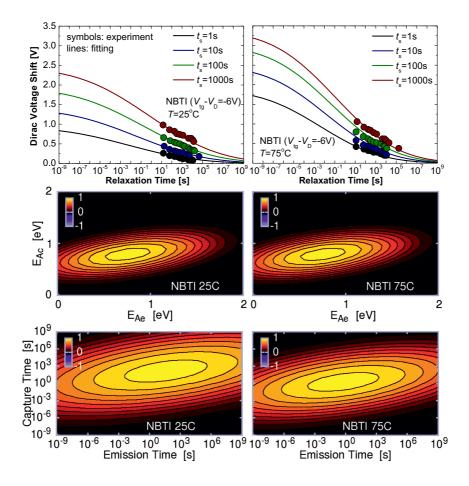

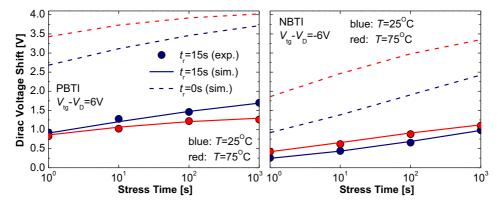

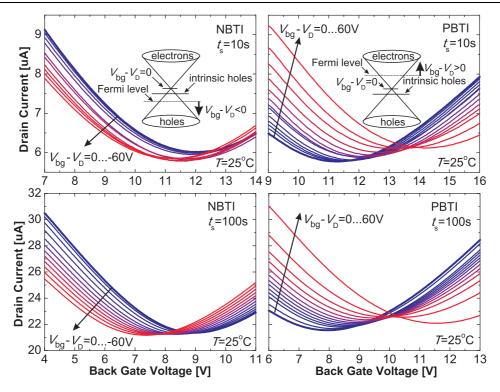

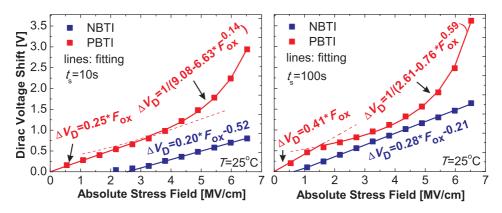

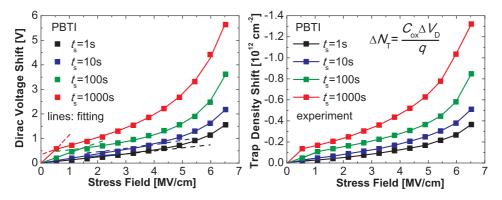

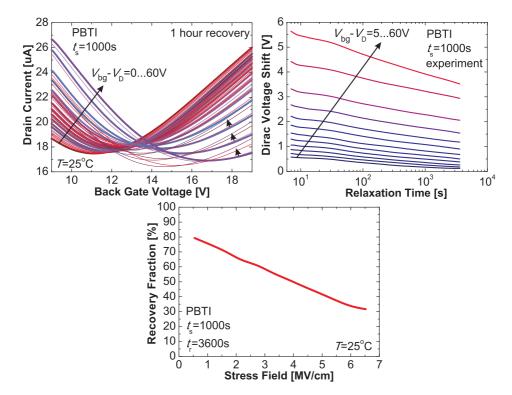

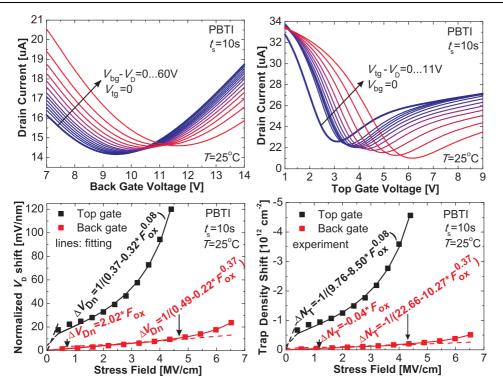

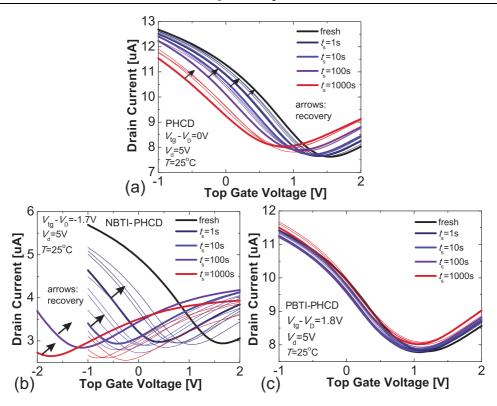

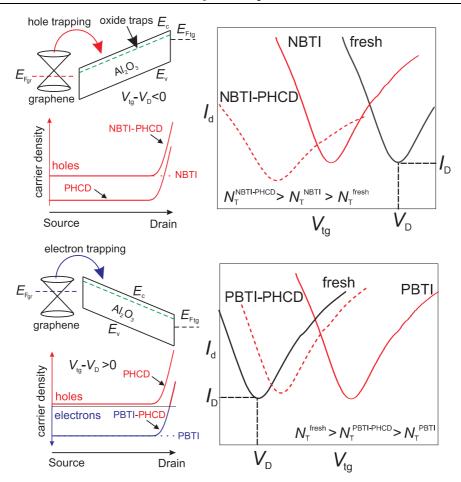

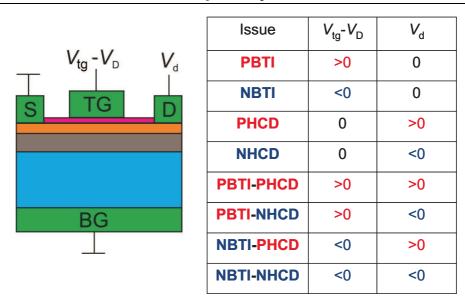

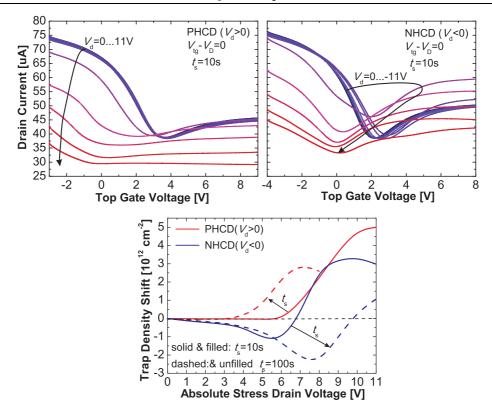

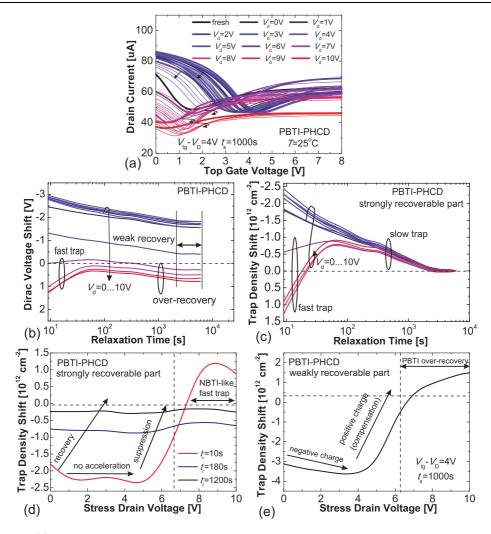

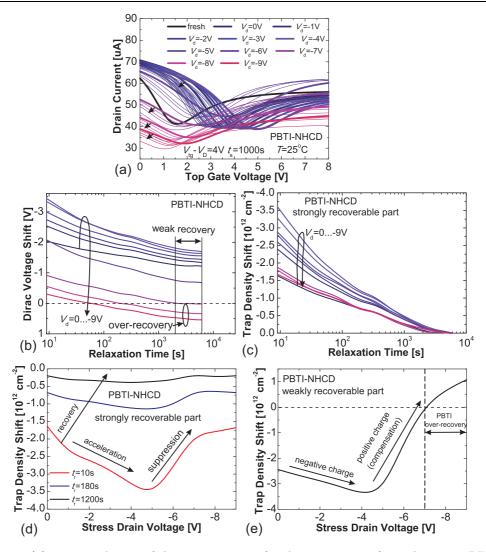

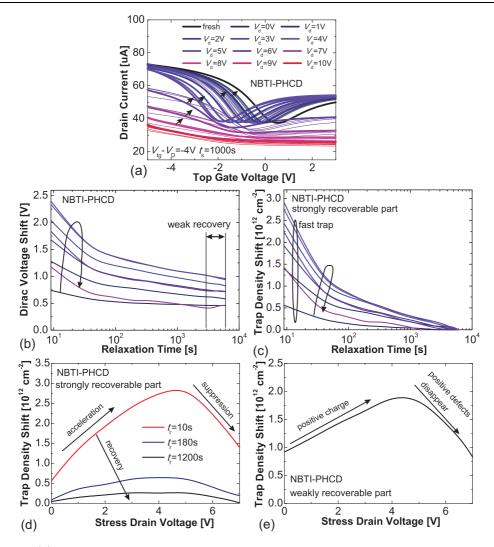

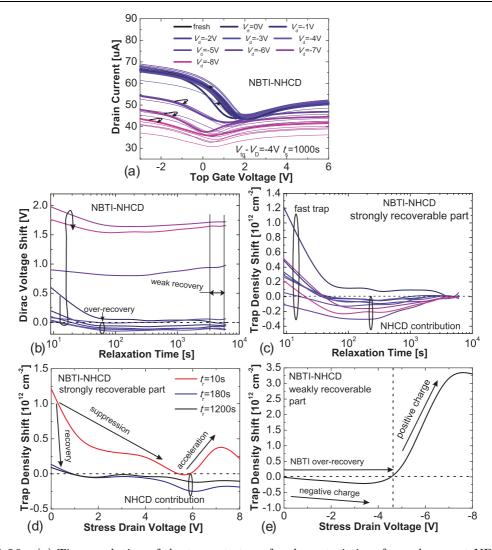

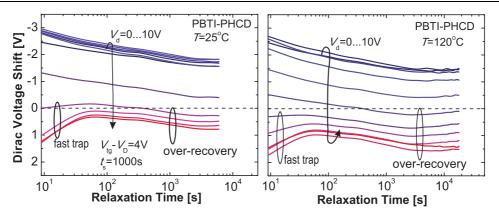

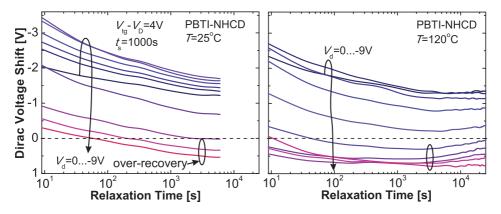

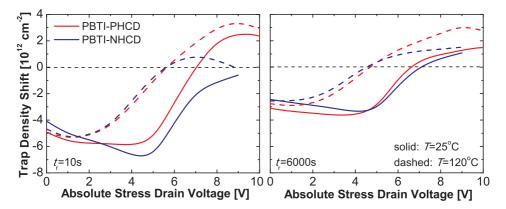

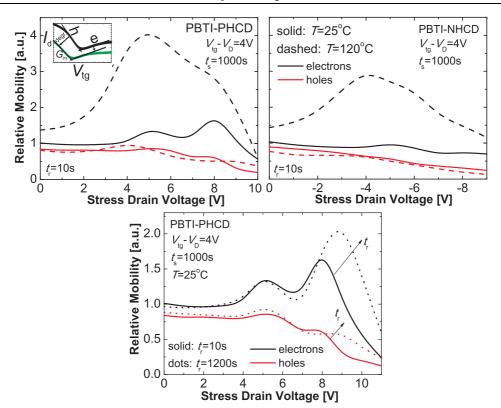

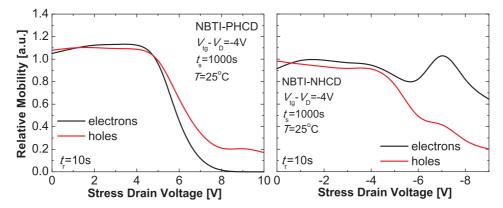

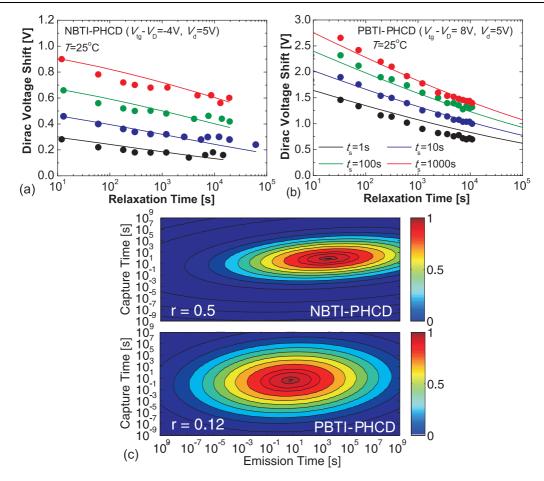

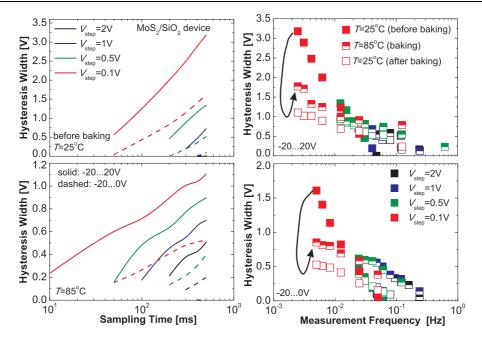

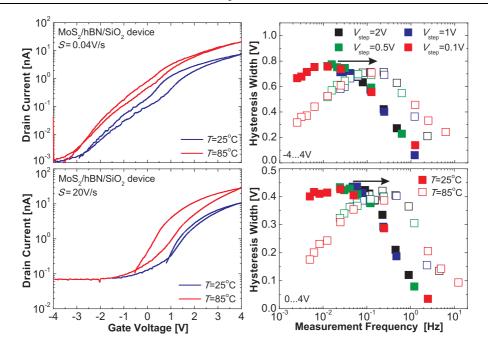

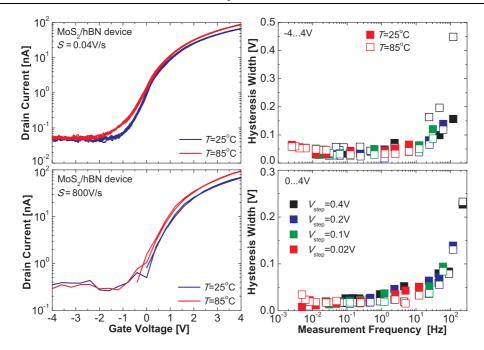

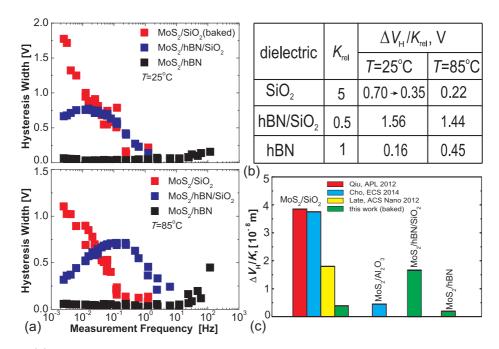

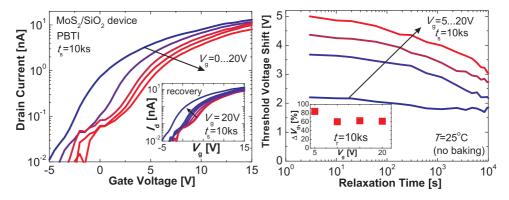

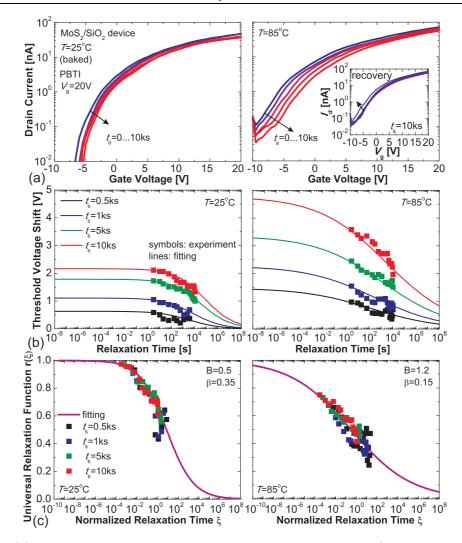

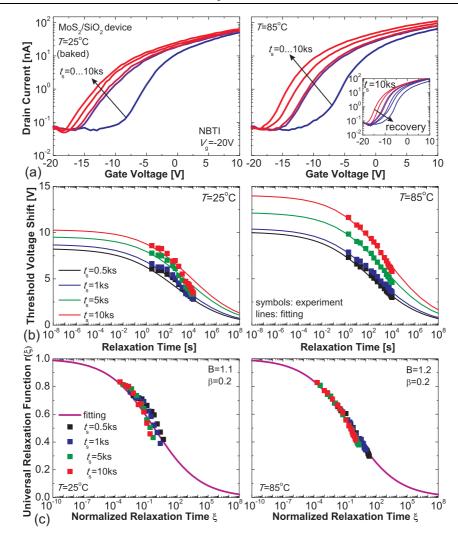

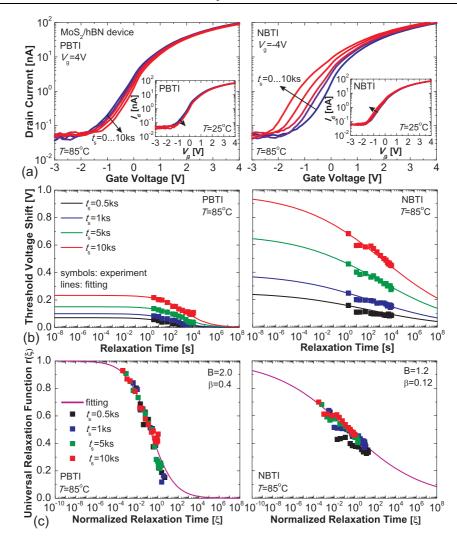

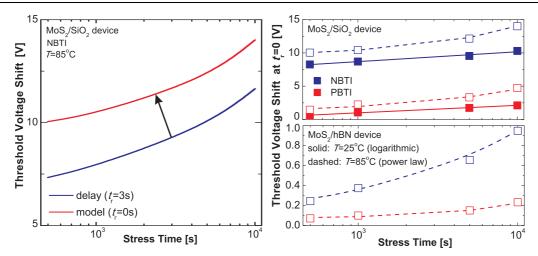

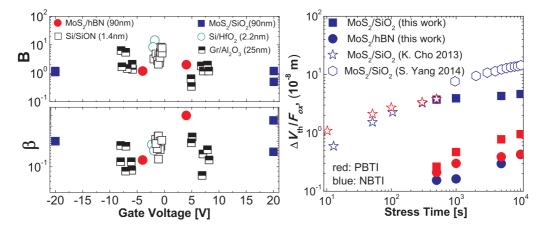

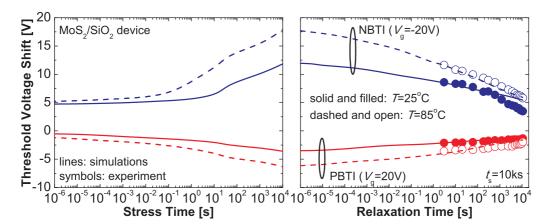

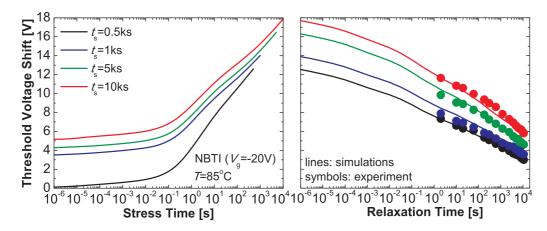

(4.5)