The approved original version EMCEna or master thesis is available at the EMCEna or Vienna University of Technology Microwave and Circuit Engineering http://www.ub.tuwien.ac.at/eng Vienna University of Technology

Gusshausstrasse 25 1040 Vienna www.emce.tuwien.ac.at

# DIPLOMA THESIS

## FPGA-based Load-Pull Measurement System

Gernot Vormayr 0425210

September 28, 2015

Supervisors Ass.Prof. Dipl.-Ing. Dr.techn. Holger ARTHABER Univ.Ass. Dipl.-Ing. Dr.techn. Thomas FASETH

This work is licensed under the Creative Commons Attribution-ShareAlike 4.0 International License. To view a copy of this license, visit http://creativecommons.org/licenses/by-sa/4.0/.

#### Abstract

Load-pull is a non-linear measurement setup which operates by presenting a specific impedance to a device under test. One type of such setups is active load-pull which retransmits a modified received wave back to the device under test. Generally, a load-pull system is intended to characterize non-linear devices like transistors and can also be used to test devices under different operating conditions. Traditional load-pull measurement systems are narrowband in nature.

During the course of this thesis an active FPGA based load-pull measurement system capable of synthesizing reflections with a constant reflection coefficient over a bandwidth of 20 MHz was developed and verified in measurements. The goals were achieved by synthesizing and filtering the reflection waveform digitally in baseband. This filtering allowed to apply phase correction to the synthesized waveforms for a cyclic signal which was used to achieve a zero phase delay between the reflected wave and a later cycle of the received wave at the load reference plane. Furthermore, an iterative target algorithm based on measurements using an also realized 1-port vector network analyzer was developed to achieve accurate reflection coefficients. This algorithm needs no calibration and allows the verification of highly non-linear devices under test which can exhibit load dependent behaviour.

The digital reflection generation was implemented in hardware on an FPGA. In combination with an efficient pipelined design this allows for fast update rates. Additionally, software running on a processor contained within the FPGA was developed to control the digital hardware via Ethernet which is needed for automated test bench setups.

Finally, the implementation was verified by comparing the realized reflection coefficients to measurements carried out using a commercially available vector network analyzer connected to the load-pull setup as the device under test.

#### Kurzfassung

Load-Pull ist eine nicht lineare Messtechnik bei der einem Prüfobjekt während einer Messung verschiedene Terminierungen angeboten werden. Aktive Load-Pull Systeme lösen diese Aufgabe mit zurück transmittieren einer modifizierten Version des Ausgangssignals an das Prüfobjekt. Diese Art Messung wird benötigt um nicht lineare Bauteile, wie z.B. Transistoren, zu charakterisieren und kann auch verwendet werden um Bauteile unter realen Bedingungen zu testen. Traditionelle Load-Pull Systeme sind von ihrer Natur aus eher Schmalbandsysteme.

Im Zuge dieser Diplomarbeit wurde ein aktives Load-Pull Messsystem aufgebaut und charakterisiert, das Reflexionen über eine Bandbreite von 20 MHz mit konstanten Reflexionskoeffizienten erzeugen kann. Dies wurde mittels digitaler Reflexionssynthese und Filterung im Basisband erzielt. Die Filterung ermöglicht das Ausgleichen der Gruppenlaufzeit verursacht durch Kabel im Messaufbau unter Nutzung eines zyklisch periodischen Eingangssignals durch angleichen der Phase des synthetisierten reflektierten Signals an zukünftige Signalperioden. Weiters wurde ein iterativer Algorithmus entworfen, der, basierend auf Messungen eines zusätzlich implementierten Netzwerkanalysators, den gewünschten Reflexionskoeffizienten erreichen kann. Dieser Algorithmus setzt keine Kalibration voraus und wird benötigt um Prüfobjekte mit lastabhängigem Verhalten testen zu können.

Die digitale Reflexionsynthese ist in einem FPGA implementiert. Diese effiziente, pipeline-basierende Implementierung erlaubt hohe Aktualisierungsraten. Weiters wurde eine Kommunikationssoftware entwickelt die auf dem in dem FPGA integrierten Prozessor läuft. Damit wird die Fernsteuerung der digitalen Hardware mittels Ethernet ermöglicht was in automatisierten Prüfaufbauten benötigt wird.

Abschließend wurde das Messsystem verifiziert indem die erzeugten Reflexionskoeffizienten mit Messungen eines kommerziell erhältlichen Netzwerkanalysators verglichen wurden.

#### Acknowledgements

I would like to thank my parents for their support during my long journey through university. Especially I would like to thank Katharina for proofreading this thesis and for giving me the strength to withstand the sprint during the end of my study.

Additional thanks go to my supervisors who always responded quickly to my questions, provided me with lots of suggestions, and helped me understanding RF.

I also wish to thank the members of the microwave laboratory for their continuing help, support, and food supply despite their lack of use of the microwave oven for cooking.

# Contents

| 1 | Introduction                                                                                                                                             | 1                          |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2 | FPGA-based Load-Pull Measurement System2.1One Port VNA2.2Analog Part2.3Digital Part                                                                      | 7<br>9<br>14<br>16         |

| 3 | FPGA Implementation                                                                                                                                      | 22                         |

|   | 3.1 Digital Signal Processing Chain3.1.1 Data Acquisition3.1.2 Overlap Add3.1.3 Vector Signal Generator Interface                                        | 23<br>25<br>28<br>31       |

|   | 3.1.4 Auto Module                                                                                                                                        | 33<br>34<br>35             |

| 4 | Software Implementation                                                                                                                                  | 36                         |

|   | 4.1 Kernel Module       4.1.1 Memory Access         4.1.1 Memory Access       4.1.2 Register Access         4.1.2 Register Access       4.1.3 Interrupts | 37<br>38<br>41<br>43       |

|   | 4.2 Network Daemon and Web-Interface                                                                                                                     | 44                         |

|   | 4.3 Matlab Algorithms       4.3.1 One Port VNA         4.3.2 Target Algorithm       4.3.3 Filter Calibration                                             | 47<br>47<br>49<br>50       |

| 5 | Verification of the Measurement System                                                                                                                   | 52                         |

| - | <ul> <li>5.1 One Port VNA Verification</li></ul>                                                                                                         | 53<br>55<br>56<br>57<br>60 |

| 6 | Conclusions and Outlook                                                                                                                                  | 63                         |

#### Contents

| Α  | Sources and Documentation                      | <b>65</b> |  |

|----|------------------------------------------------|-----------|--|

|    | A.1 Source Codes                               |           |  |

|    | A.2 Register Assignment and Protocol Reference | 65        |  |

| В  | Build Instructions                             | 70        |  |

|    | B.1 Hardware                                   | 70        |  |

|    | B.2 Software                                   | 70        |  |

| С  | Used Equipment                                 | 71        |  |

| Bi | Bibliography                                   |           |  |

# **List of Figures**

| 1.2                                                          | S-parameters of a 2-port                                                                                                                                                                                                                                                                                                                                                     | $     \begin{array}{c}       1 \\       3 \\       4 \\       5 \\       5     \end{array} $ |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10 | Generic block diagram ELP                                                                                                                                                                                                                                                                                                                                                    | $7\\8\\10\\12\\15\\16\\17\\18\\18\\20\\21$                                                   |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                | FPGA design overview and digital signal processing chainmain module overview and digital signal processing chainBlock diagram of the inbuf moduleBlock diagram of the core moduleOverlap add algorithm hardware implementationBlock diagram of the outbuf moduleBlock diagram of the processor module                                                                        | 22<br>24<br>26<br>29<br>30<br>31<br>34                                                       |

| 4.1<br>4.2<br>4.3                                            | Soft- and hardware architecture including communication paths<br>Screen shot of the web interface                                                                                                                                                                                                                                                                            | 37<br>46<br>50                                                                               |

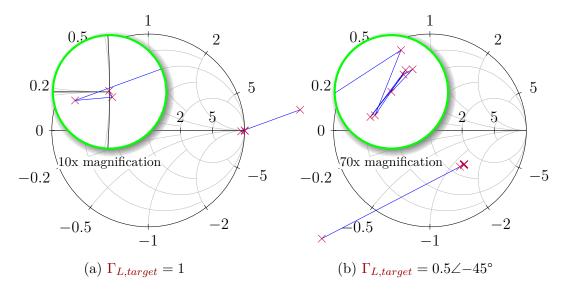

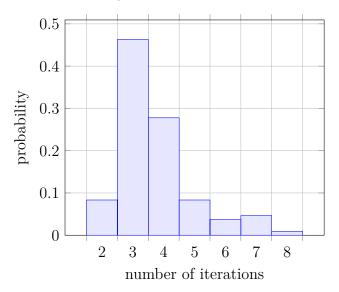

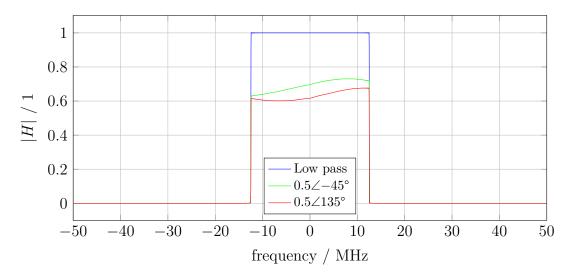

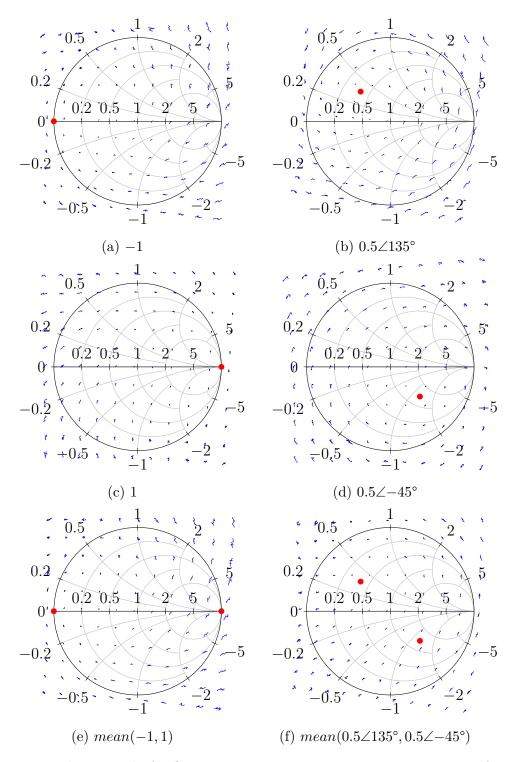

| $5.1 \\ 5.2 \\ 5.3 \\ 5.4$                                   | Measurement system verification test setup $\ldots \ldots \ldots \ldots \ldots \ldots$<br>Exemplary trajectories of the target algorithm $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$<br>Histogram of algorithm iterations needed to find a specific $\Gamma_L$ $\ldots$<br>Uncalibrated and calibrated filter transfer functions $\ldots \ldots \ldots \ldots \ldots$ | 52<br>56<br>57<br>58                                                                         |

### List of Figures

| 5.5 | 11 by 11 grid of reflection measurements over maximum range of $\Gamma_{L,set}$ |

|-----|---------------------------------------------------------------------------------|

|     | values with calibrated filter at distinct calibration points                    |

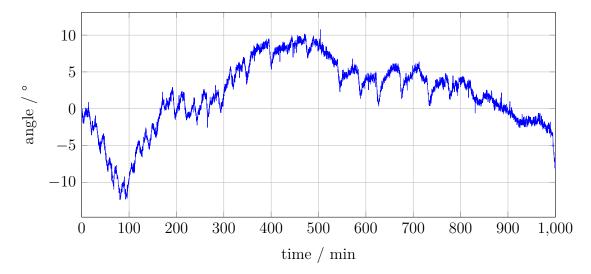

| 5.6 | Phase drift of $\Gamma_L$ over time $(\Gamma_{L,start} = 1)$                    |

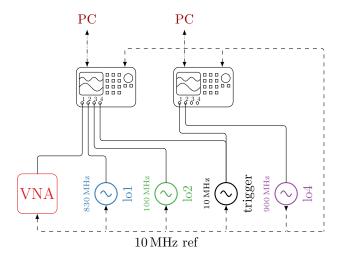

| 5.7 | Phase drift measurement setup                                                   |

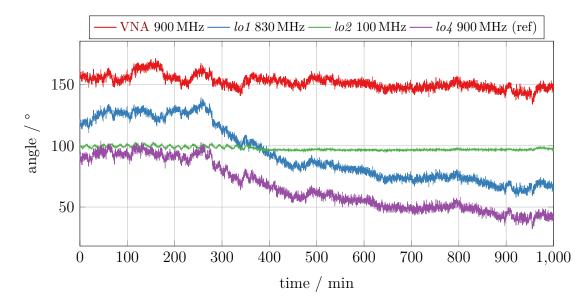

| 5.8 | Phase drift of signal generators over time                                      |

|     |                                                                                 |

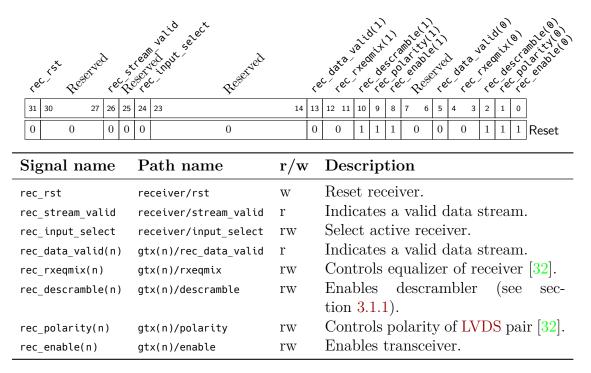

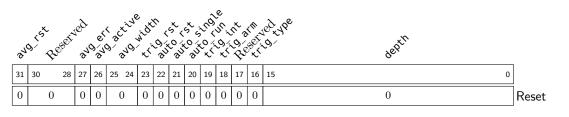

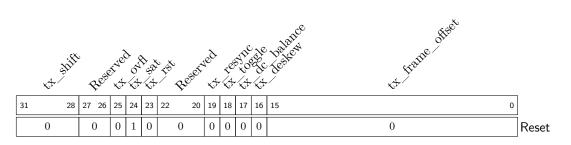

| A.1 | Register 0 $(0x00)$                                                             |

| A.2 | Register 1 $(0x04)$                                                             |

|     | Register 2 $(0x08)$                                                             |

| A.4 | Register 3 $(0x0C)$                                                             |

| A.5 | Register 4 $(0x10)$                                                             |

| A.6 | Register 5 $(0x14)$                                                             |

| A.7 | Interrupt Register $(0x220)$                                                    |

## Acronyms

- **ADC** analog-to-digital converter. 9, 15–19, 22, 23, 25–28, 31, 36, 54, 55, 64, 69, 71

- API application programming interface. 36, 44

- **CF** compact flash. 35

- **CPU** central processing unit. 22, 23, 33, 34, 44

- DAC digital-to-analog converter. 9, 20

- **DC** direct current. 8, 14–16, 24, 33, 68

- **DDR** double data rate. 33

- **DFT** discrete Fourier transform. 10, 11

- **DRAM** dynamic random access memory. 34

- **DUT** device under test. 2–5, 7, 8, 11–13, 19, 20, 37, 47, 49, 50, 52, 53, 55, 56, 60, 63, 71

- **ELP** envelope load-pull. 7, 8, 14, 16, 52

- **EMT** electromechanical tuner. 4

- **FFT** fast Fourier transform. 10, 19, 20, 25, 28–31, 47, 48, 55, 57, 67

- **FIR** finite impulse response. 7, 19, 25, 55, 57

- **FPGA** field programmable gate array. 9, 18, 21–24, 26–28, 32–37, 45, 46, 50, 52, 55, 60, 63, 64, 70, 71

- **GPIO** general-purpose input/output. 34, 35

- **HTML** HyperText Markup Language. 45

#### Acronyms

- **IF** intermediate frequency. 7, 8, 14–17, 19, 52, 53

- **IP** internet protocol. 45

- **IQ** in-phase/quadrature-phase. 7–9, 16, 19, 21, 22, 24, 25, 28, 30–33, 63, 67

- JSON JavaScript Object Notation. 36, 45, 46

- **LED** light emitting diode. 35

- **LO** local oscillator. 19, 23, 71

- **LP** load-pull. 2–7, 19

- LUT lookup table. 29

- LVDS low voltage differential signalling. 16, 17, 21, 33, 66

- MW microwave. 1, 2

- **OS** operating system. 23, 35, 36, 46, 65

- **OSERDES** output serializer/deserializer. 33

- **PA** power amplifier. 2, 3, 63

- PC personal computer. 8–10, 17, 22–24, 36, 52, 61

- **PLB** processor local bus. 23, 26, 27, 31, 35

- **RAM** random access memory. 22–25, 27–29, 32, 34

- **RF** radio frequency. 1, 2, 14–16, 52, 57, 64

- **ROM** read only memory. 34

- S-parameter scattering parameter. 1, 2, 48, 53, 63

- **SATA** serial AT attachment. 17, 18, 22, 25, 26

- **SMA** sub-miniature version A. 17, 18

- **SNR** signal-to-noise ratio. 19, 55

- TCP transport control protocol. 46, 63

- **UI** user interface. 36

- VHDL very high speed integrated circuit hardware description language. 22, 32, 65

- **VNA** vector network analyzer. 2, 8–10, 12, 15, 17, 37, 47, 52–56, 58, 60–63, 71

- **XPS** Xilinx Platform Studio. 34, 35, 43

## List of Symbols

- a incident wave. 1–12, 14, 15, 17, 21, 48–50, 52

- b reflected wave. 1–12, 14, 15, 17, 48–50, 52

- $\mathcal{DFT}$  discrete Fourier transform. 11, 19

- f frequency. 10, 11, 13, 53, 54

- $f_0$  fundamental frequency, center frequency. 7, 8, 15, 16, 52

- $f_s$  sample frequency. 10, 16

- $\Gamma$  complex reflection coefficient. 2, 13, 14

- $\Gamma_L$  complex load reflection coefficient. viii, ix, 3–15, 17, 21, 22, 24, 32, 36, 37, 47–53, 55–60, 62–64, 68

- j imaginary unit. 7–9, 13, 17, 22, 24

- L overlap add block size. 19, 20, 25, 30, 31, 45, 46, 55, 60, 65, 67

- N number of samples, periodicity of signal. 10, 11, 20, 28, 31–33, 47, 55, 60

- $n_{\rm fft}$  fast Fourier transform size. 19, 20, 25, 29, 31, 47, 55, 60, 67

- S scattering matrix. 1, 2, 11–13, 47, 49, 56

- x[n] sampled signal x at sample position n. 11, 19, 20, 23

- Z complex impedance. 2, 13

- $Z_0$  complex characteristic impedance of system. 1–3, 13

- $Z_L$  complex load impedance. 3, 5, 7, 8, 10, 13, 15, 17, 52

## **1** Introduction

At radio frequency (RF) and microwave (MW) frequencies, the circuit theory with lumped elements, where voltage and current do not vary over the physical dimension of the elements, is of limited value. The wavelength at these frequencies is of the order of the circuit element dimensions. This means that transmission line theory has to be used instead [1]. This theory applies circuit theory to infinitesimally small pieces of the lumped elements and introduces the concept of forward and backward traveling power waves.

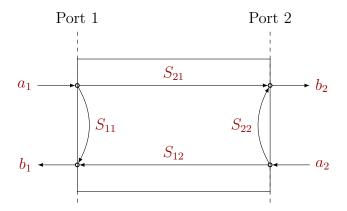

For this reason, instead of impedance- and admittance matrices, scattering parameters (S-parameters) are commonly used in RF and MW circuit engineering to describe N-ports (see figure 1.1 and equation (1.1) for a 2-port).  $a_k$  denotes the incident and  $b_k$  the reflected power wave. The complex valued  $S_{kk}$  represents the part of  $a_k$  that gets reflected at port k, where as  $S_{kl}$  is the part of  $a_l$  that is transmitted to  $b_k$ . A set of S-parameters is only valid for a specific frequency, the characteristic impedance  $Z_0$  of the system, and a well defined reference plane (port 1 and port 2 in figure 1.1).

Figure 1.1: S-parameters of a 2-port

$$\begin{pmatrix} b_1 \\ b_2 \end{pmatrix} = \begin{pmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{pmatrix} \begin{pmatrix} a_1 \\ a_2 \end{pmatrix}$$

(1.1)

For a 1-port there is only the parameter  $S_{11}$ , which is equivalent to the reflection co-

#### 1 Introduction

efficient  $\Gamma$  and can be also expressed by the input impedance  $Z_{in}$  (see equation (1.2) as shown in [1]). This does not necessarily hold for 2-ports, since for a generic multi-port configuration, also reflections from the devices connected at the other ports can be seen.

$$\Gamma = S_{11} = \frac{Z_{in} - Z_0}{Z_{in} + Z_0} \tag{1.2}$$

One way to evaluate the S-parameters at a specific frequency would be connecting the reference impedance  $Z_0$  to the ports which are not under test. For example, to measure  $S_{11}$  of a 2-port, a matching impedance equal to the ports reference impedance has to be connected to port 2. According to equation (1.2) the reflected wave  $a_2$  at port 2 is zero in this case. This means that measurements at port 1 can only see the reflections caused by  $S_{11}$ . Consequently  $S_{11}$  can now be calculated by measuring the incident and reflected wave at port 1 (see equation (1.3)) [2].

$$S_{11} = \left. \frac{b_1}{a_1} \right|_{a_2 = 0} \tag{1.3}$$

$$S_{21} = \left. \frac{b_2}{a_1} \right|_{a_2 = 0} \tag{1.4}$$

Because of connectors and cabling it is often impossible to connect exact matches. Therefore, S-parameters are measured by sending a power wave into port 1 of the device under test (DUT), measuring  $a_k$  and  $b_k$ . After that the measurement is repeated with port 2. With measurements from both ports and calibration measurements, which are necessary to account for systematic errors in the measurement setup, it is possible to determine every S-parameter. Vector network analyzers (VNAs) use this method and can make automated measurements at various frequencies.

As long as a network behaves linearly, what is typical for small incident signals, the S-parameters fully describe this network at a specific frequency. Thus S-parameters can also be used to model transistors, as long as those exhibit controlled and linear behaviour. For example, transistors used in class-A power amplifiers (PAs) behave nearly linear and S-parameters can therefore be used to describe the small signal behaviour. But those PAs exhibit a very low efficiency of around 50 %. In modern RF and MW applications the efficiency is increased with specially designed input and output matching networks, that improve the performance. This comes at the cost of non-linear behaviour of the transistor in use [3].

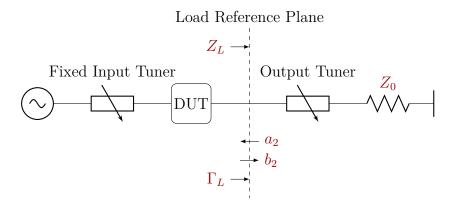

Because of these non-linearities more complex models and verification systems are needed. One way to measure the characteristics of a non-linear device is the so called load-pull (LP) technique (see figure 1.2). This measurement system presents a controllable load impedance (output tuner) to the DUT. The fixed input tuner is needed to match the input of the DUT to the source. LP can be used for obtaining the DUT characteristics and/or for verifying an implementation. LP also allows to test the DUT under realistic operational conditions.

Figure 1.2: Load reflection coefficient

The equations (1.5) and (1.6) show the relations between the load reflection coefficient  $\Gamma_L$ , the incident wave  $a_2$ , the reflected wave  $b_2$ , and the load impedance  $Z_L$  at port 2 of figures 1.1 and 1.2.  $Z_0$  is the reference impedance of the system where the DUT is going to be used [4].

$$\Gamma_L = \frac{a_2}{b_2} \tag{1.5}$$

$$\Gamma_L = \frac{Z_L - Z_0}{Z_L + Z_0}$$

(1.6)

The output tuner in figure 1.2 synthesizes a desired  $\Gamma_L$  either by varying the phase and magnitude of the reflected wave  $a_2$  or by varying the load impedance  $Z_L$ . This means, that it is possible to build a LP setup by either using a passive tuner, or feeding a modified wave back to the DUT.

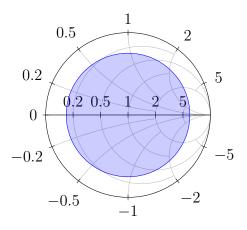

There are various types of LP measurement setups, which have different characteristics. One important feature of a LP setup is the repeatability of reflection coefficients. The repeatability is needed to ensure accurate application specific device models. Another important factor is the tuning range, which depicts the maximal achievable range of the reflection coefficient  $|\Gamma_L|$  (e.g. figure 1.3). Usually passive LP systems have a more limited tuning range than active ones, but provide a better repeatability [3]. Tuner resolution is an additional performance characteristic of LP measurement systems. High resolution is needed since PAs are often highly sensitive to impedance variations. However a high resolution incurs a high number of measurement points which increases the overall measurement time. Power handling capability is another extremely important factor. The LP setup has to be capable to sustain the power presented to the tuner without damage. Which LP setup to choose for a specific DUT depends on these requirements.

Figure 1.3: Achievable tuning range passive LP system

Passive LP systems are based on the block diagram in figure 1.2. Depending on the desired measurements, additional circuit elements like directional couplers, power meters, and oscilloscopes are needed. For higher power measurements additional amplifiers might also be needed. These additional components, the cabling, and connectors add additional loss on the reflection path, leading to achievable reflection levels  $|\Gamma_L| < 1$  with a maximum usually around 0.75 at the load reference plane [5] (see figure 1.3).

Typically used tuners consist of a transmission line and a probe that introduces a mismatch by adding a parallel susceptance. Varying the position of the probe along the transmission line changes the phase of the impedance mismatch and the distance the magnitude [4]. Automated positioning can be achieved by adding motors. These tuners are called electromechanical tuners (EMTs). Those have to be calibrated before use and typically synthesize around 10,000 points [3].

If higher  $|\Gamma_L|$ -levels are needed (even levels >1), active LP setups have to be used. There are two categories: Closed- and open-loop.

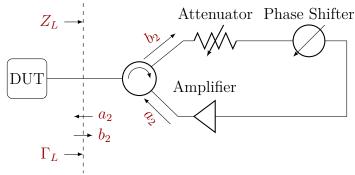

Active closed loop LP setups synthesize a modified reflected wave  $a_2$  by modifying the phase and magnitude of  $b_2$  and feeding it back to the DUT. The functional block diagram, which can be seen in Figure 1.4, is an example of such an active closed loop LP setup. With the circulator the power wave  $b_2$  is fed to a variable attenuator, a phase shifter and an amplifier. These elements modify the phase and the magnitude of  $b_2$ , which is again fed back to the DUT with the circulator. Because of limited isolation provided by real world circulators the loop will oscillate if the loop gain exceeds the isolation [3]. The isolation can be improved with an additional isolator after the amplifier. Another way to improve the stability of the loop is to introduce a bandpass filter into the loop which prevents oscillations at frequencies outside the band of interest.

#### 1 Introduction

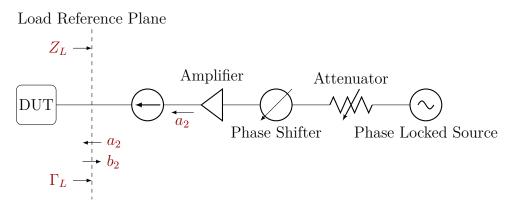

Figure 1.4: Active closed loop LP block diagram

Active open loop LP setups work by synthesizing a phase coherent wave with an external signal generator (see figure 1.5). The open loop approach has the advantage, that no loop oscillations are possible, since there is no closed loop. It works by synthesizing a signal with a source that is locked to the generator driving the source port of the DUT. Phase and magnitude can be adjusted with the attenuator and phase shifter. Additionally the amplifier has to be protected from possibly damaging input signals with an isolator. A disadvantage of the open loop system is that the synthesized waves  $a_2$  are not derived from  $b_2$ . This implies that the reflection coefficient  $\Gamma_L$  not only depends on the phase shifter and attenuator settings, but also on the DUT itself. Therefore, an iterative approach is needed to achieve desired  $\Gamma_L$  [6].

Figure 1.5: Active open loop LP block diagram

In order to provide a realistic termination with an LP setup the variation of the reflection coefficient  $\Gamma_L$  should be minimized at the load reference plane. Because of phase variations caused by cable connections needed to reach the DUT, all of the above mentioned setups are only capable of synthesizing narrowband reflections. Therefore, a phase correction is needed for wideband measurements which are needed for modulated signals used in modern communication systems.

#### 1 Introduction

During the course of this thesis an active closed loop LP system that uses a digital filter for phase correction is presented. With this filter reflections with minimal  $\Gamma_L$  variation at the load reference plane over a bandwidth of 20 MHz can be synthesized. This wideband system works by modifying the incoming wave  $b_2$  according to the desired  $\Gamma_L$ , applying an overall negative phase correction at the load reference plane by filtering the signal, and sending the modified wave back to the device. The negative phase correction is only possible for a later repetition of the signal. Therefore, cyclic signals have to be used which allow completely compensating the group delay by matching the phase of the reflected wave  $a_2$  to the phase of the incident wave  $b_2$  at a later signal cycle at the load reference plane.

# 2 FPGA-based Load-Pull Measurement System

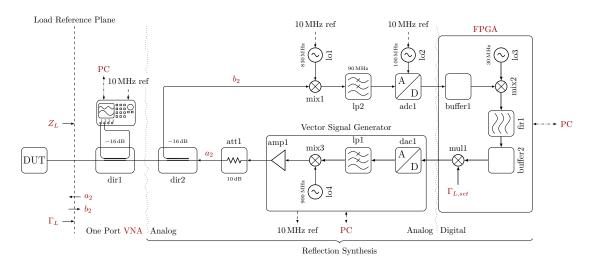

The aim of this thesis was to setup a wideband active LP measurement system, capable of providing a bandwidth of 20 MHz. As mentioned in chapter 1 traditional classic LP systems can only synthesize narrowband reflections. To overcome these limitations an envelope load-pull (ELP) measurement system, which synthesizes the reflections in the digital domain, was chosen as the base for this work. This approach solves part of the stability problem and the problem of the intermediate frequency (IF) calibration with a fully configurable digital finite impulse response (FIR) filter. Furthermore, this filter is capable of compensating the group delay caused by the measurement setup and the cabling needed to reach the DUT. This allows synthesizing constant reflection coefficients over a wide bandwidth, which in turn allows the use of modulated signals used in modern applications during measurements.

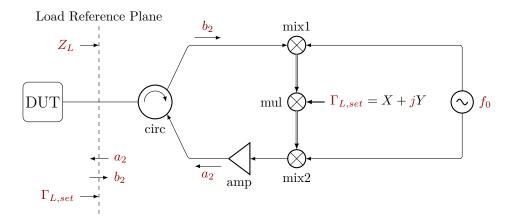

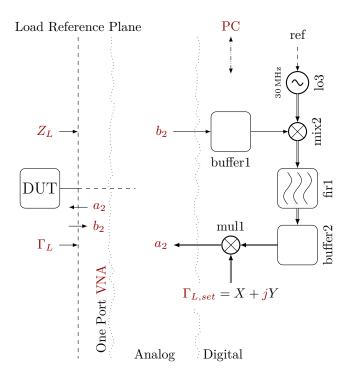

Instead of traditional active closed loop LP, this system synthesizes the load coefficient at baseband or IF. The basic principle of this ELP system can be seen in figure 2.1. A circulator is used to split the incident and reflected wave. The mixer mix1 is used for shifting the spectrum to the baseband and for in-phase/quadraturephase (IQ) demodulation. This IQ signal is then multiplied by the complex valued

Figure 2.1: Generic block diagram ELP

$\Gamma_{L,set}$  (mul1), thus creating a specific reflection coefficient  $\Gamma_L$ . Mixer mix2 is used for modulating the IQ signal and upconverting the signal back to the desired frequency [7].

The multiplication can be done in the analog domain, as has been described by [7]. But this has the disadvantage that an additional image will be generated by the multiplicator mul1 (figure 2.1), if there are amplitude imbalances in the output of the demodulator mix1. Since this image is very close to the carrier signal, it can't be filtered out [8].

Phase variation with the frequency at the reference plane caused by the cabling needed to reach the DUT prevents the ELP measurement system from synthesizing realistic terminations. Additionally, the frequency responses of the components used to build the measurement setup cause variations in the magnitude and phase of  $\Gamma_L$  with the frequency. Therefore, a negative phase correction and a magnitude correction is needed. The design in [9] solves this problem with a configurable digital delay line which is able to compensate the phase for cyclic signals. This works by matching the phase of the reflected wave  $a_2$  to the phase of the incoming wave  $b_2$  at a later signal cycle at the load reference plane. However, the design in [9] uses direct conversion, which creates additional direct current (DC) components in the IQ signals. Since these have to be removed by filters, the band around 0 Hz in the baseband is not usable for reflection synthesis. Furthermore, the delay line approach can only compensate phase differences and has a limited resolution.

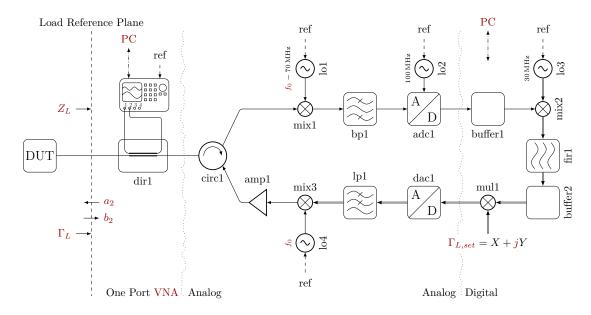

Figure 2.2: System overview

As can be seen in figure 2.2, instead of direct conversion a superheterodyne design with digital IF processing was used. With this design the band around 0 Hz is

usable and the measurement system can't exhibit IQ imbalances. Furthermore, the delay line was replaced by a fully configurable filter *fir1*. This filter is able to provide a negative phase correction for a later repetition of the measured signal  $b_2$ . Therefore, this filter allows synthesizing reflections with a nearly frequency independent  $\Gamma_L$  over the required bandwidth of 20 MHz for cyclic signals. The setup consists of three distinct parts:

- 1. A one port VNA, to measure the current  $\Gamma_L$ . This part is needed, to reach a specific  $\Gamma_{L,target}$  iteratively and is described in detail in section 2.1. The iterative algorithm can be found in section 4.3.

- 2. The analog part, which contains the mixers for the frequency shifting operation, necessary filters, a digital-to-analog converter (DAC), an analog-todigital converter (ADC), and an amplifier. A detailed description can be found in section 2.2.

- 3. A digital processing chain is implemented in an field programmable gate array (FPGA), which is controlled with a personal computer (PC) running Matlab. The FPGA implementation is described in chapter 3. The software running on the processor contained in the FPGA, as well as the Matlab code, in chapter 4.

## 2.1 One Port VNA

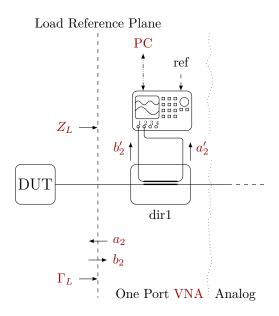

The one port VNA in figure 2.3 consists of a directional coupler dir1 and a sampling oscilloscope. The directional coupler is needed to split up the signal into the incident power wave  $b'_2$  and the reflected power wave  $a'_2$ . With the help of the oscilloscope both signals can be measured in the time domain. Additionally a PC connected to the oscilloscope is needed for extracting the wave parameters from the measured samples and the necessary error correction calculations, which are explained in the rest of this section.

According to

$$\Gamma'_{L} = \frac{a'_{2}}{b'_{2}}$$

$$= \frac{|a'_{2}|}{|b'_{2}|} e^{j(\arg a'_{2} - \arg b'_{2})}$$

(2.1)

only  $\frac{a'_2}{b'_2}$  is of interest for calculating  $\Gamma'_L$ . Since only the ratio of the magnitudes and the phase difference is needed, the exact point in time, when the signals are taken does not matter, as long as both are measured at the same time which is guaranteed

Figure 2.3: One port VNA part

by the use of the oscilloscope. Therefore, no special triggering or synchronization is necessary.

Magnitude and phase of the measured waves can be calculated by using the discrete Fourier transform (DFT). If multiple frequency components are of interest, the computational power needed can be lowered by using the fast Fourier transform (FFT). With both methods spectral leakage will occur, which is caused by the windowing since only a limited number of samples is used [10]. Another problem is that the frequency resolution  $\Delta f$  is limited by the sampling frequency and the number of recorded samples:

$$\Delta f = \frac{f_s}{N} \tag{2.2}$$

Higher resolutions can be achieved with a higher sample rate  $f_s$  and/or more samples N. Both are oscilloscope and setup dependent parameters and potentially increase the time needed for transferring the data to the PC. A preferably way to improve the results is applying a window function to the measured samples.

The window function used in this work (see section 4.3) is the flat top window. This window function has a very high amplitude accuracy [11]. Since it's frequency response is very flat in a small frequency range around the selected  $\Delta f$ -bin, frequency components leak into the surrounding bins with the same amplitude as in the original bin. This enables acquiring frequency components, that are not  $\Delta f$ -aligned [11]. In this work, the periodic version of the built-in Matlab flat top window flattopwin was used (see section 4.3 and [12]).

$$k = \left\lfloor \frac{f}{\Delta f} \right\rfloor \tag{2.3}$$

$$w[n] = \text{flattopwin}(N, \text{'periodic'})$$

(2.4)

$$A'[n] = \mathcal{DFT}(a'[n] w[n])$$

(2.5)

$$B'[n] = \mathcal{DFT}(b'[n] w[n])$$

(2.6)

$$\Gamma_{L,k}' = \frac{A'[k]}{B'[k]} \tag{2.7}$$

Using equations (2.2) to (2.7) the reflection coefficient  $\Gamma_L$  at frequency f (frequency bin k), with the measured N samples a'[n] of wave  $a'_2$  and b'[n] of wave  $b'_2$ , can be calculated. First, the frequency resolution  $\Delta f$  is needed, to calculate the index kof the frequency bin, which contains the frequency f. Next, the window function w with length N is obtained with the Matlab function flattopwin as mentioned earlier. This window function is element-wise multiplied with the input signal in equations (2.5) and (2.6) before applying the DFT. After the transformation A'[n]and B'[n] contain the signals in the frequency domain. Because of the linearity of the DFT [13], the value at index k can be directly used in equation (2.1) leading to equation (2.7).

The measurements acquired using this type of setup contain systematic errors. These are caused by mismatches and imperfections in the equipment, which are the limited directivity of the coupler and imperfect connectors and distort the measurements. Furthermore, the needed cabling causes the reference plane to be shifted to another place, than depicted in figure 2.3. Those errors can be corrected using vector error correction. By measuring the systematic errors with known calibration standards it is possible to calculate the error model and use this model to remove the systematic errors from the subsequent measurements [14].

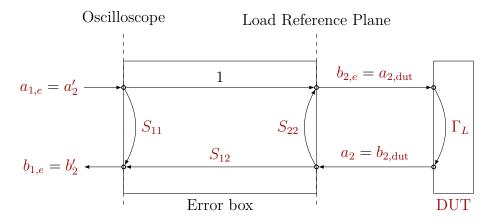

Figure 2.4 depicts the error model for the measurement system in figure 2.3. It consists of the DUT and an error box, containing all the systematic errors of the measurement system. This error model can cancel out three different errors:

- 1. Source match  $S_{22}$ , the mismatch between the measurement system and the DUT.

- 2. Directivity  $S_{11}$ , which characterizes signal leakage and imperfections in the coupler.

- 3. Reflection tracking  $S_{12}$ , which characterizes the difference in the frequency response between the two oscilloscope ports, including loss in the couplers, transmission lines, and other components.

Figure 2.4: Error box for the one port VNA

From the error model in figure 2.4 the following equations can be derived:

$$b_{2,e} = a_{1,e} + S_{22}a_{2,e} \tag{2.8}$$

$$b_{1,e} = S_{11}a_{1,e} + S_{12}a_{2,e} \tag{2.9}$$

$$a_{2,e} = \Gamma_L b_{2,e} \tag{2.10}$$

Equations (2.7) to (2.10) can be combined into

$$\Gamma_{L,\text{corr}} = \frac{S_{22} - \frac{b_{1,e}}{a_{1,e}}}{S_{11}S_{22} - S_{11}\frac{b_{1,e}}{a_{1,e}} - S_{12}}$$

$$= \frac{S_{22} - \Gamma_{L,k}^{-1}}{S_{11}S_{22} - \Gamma_{L,k}^{-1}S_{11} - S_{12}}$$

(2.11)

With the help of this equation the corrected reflection coefficient  $\Gamma_L$  can be calculated.  $\Gamma_{L,k}$  is the measured value from the oscilloscope (see equation (2.7)) and  $S_{22}$ ,  $S_{11}$ , and  $S_{12}$  denote the different error terms mentioned above, that have to be measured and calculated, which is discussed in the following paragraphs.

Since there are three error terms, at least three different measurements have to be taken. These measurements are usually conducted using short, open, and load reflection standards from commercially available calibration kits, where load is normally the characteristic impedance of the system [14]. Other impedances could also be used, which is done for example at higher frequencies with different shorts, because it is more difficult to characterize open and loads at these frequencies [15]. Another way commonly used in commercial VNA is the electronic calibration, where different impedances are available via a semiconductor switch through the same connector. With this technique it isn't necessary to change the connections between the different targets, therefore minimizing calibration time and risk for an operator error. Nevertheless, the calibration used in this work was carried out with short, open, and load (see Section 5.1). Open targets are usually specified by a frequency-dependent capacitance (see equation (2.12)) and a transmission line length. Short targets use the same specifications, but instead of a capacitance a frequency-dependent inductance is needed (see equation (2.13)). For loads, a shunt capacitance, a series inductance, a resistance, and the transmission line length are needed.

$$C = C_0 + C_1 f + C_2 f^2 + C_3 f^3$$

(2.12)

$$L = L_0 + L_1 f + L_2 f^2 + L_3 f^3$$

(2.13)

Because of the inherent transmission line, the impedance on the input of this line has to be calculated. As shown in [1] this can be achieved using equations (2.14) and (2.15). In these equations the impedances calculated from the capacitance/inductance provided by equations (2.12) and (2.13), the material dependent propagation velocity c, the frequency f and the transmission line length l are needed. Therefore the actual frequency dependent impedances can be calculated using the values from the data sheet of the used calibration kit.

$$\beta = \frac{2\pi}{\lambda} = \frac{2\pi f}{c} \tag{2.14}$$

$$Z_{in} = Z_0 \frac{Z_L + jZ_0 \tan(\beta l)}{Z_0 + jZ_L \tan(\beta l)}$$

(2.15)

These values don't incorporate eventual adapters needed for the measurements. Hence it is important to use the calibration kit with the correct (the same as the **DUT**) gendered connectors, or the connectors have to be additionally accounted for in the error corrections.

By using three different  $\Gamma_{L,k}$  measurements, acquired with each of the three different calibration standards in place of the **DUT** in figure 2.3, a system of three equations (2.16) to (2.18) can be set up from equation (2.11). The three different  $\Gamma_L$ and  $\Gamma_{L,k}$  represent the short ( $\Gamma_S$ ), the open ( $\Gamma_O$ ) and the match ( $\Gamma_M$ ) calibration standard.

$$\Gamma_{L_S} = \frac{S_{22} - \Gamma_{L,k_S}^{-1}}{S_{11}S_{22} - \Gamma_{L,k_S}^{-1}S_{11} - S_{12}}$$

(2.16)

$$\Gamma_{L_O} = \frac{S_{22} - \Gamma_{L,k_O}^{-1}}{S_{11}S_{22} - \Gamma_{L,k_O}^{-1}S_{11} - S_{12}}$$

(2.17)

$$\Gamma_{L_M} = \frac{S_{22} - \Gamma_{L,k_M}^{-1}}{S_{11}S_{22} - \Gamma_{L,k_M}^{-1}S_{11} - S_{12}}$$

(2.18)

Solving these equations for the error terms  $S_{11}$ ,  $S_{12}$  and  $S_{22}$  leads to equations (2.21) to (2.23) with the common term g from equation (2.20) and  $\Gamma_1$  from equation (2.19).

Those terms were used to enable a more compact representation. These equations were derived using Wolfram Mathematica and are implemented in a Wolfram Mathematica generated Mathworks Matlab module (see section 4.3).

$$\Gamma_1 = \frac{a_{1,e}}{b_{1,e}} = \Gamma_{L,k}$$

(2.19)

$$g = (\Gamma_{1_O} - \Gamma_{1_S})\Gamma_{1_M}\Gamma_{L_O}\Gamma_{L_S} + \Gamma_{L_M}((\Gamma_{1_M} - \Gamma_{1_O})\Gamma_{1_S}\Gamma_{L_O} + (\Gamma_{1_S} - \Gamma_{1_M})\Gamma_{1_O}\Gamma_{L_S})$$

(2.20)

$$S_{11} = \frac{(\Gamma_{1_O} - \Gamma_{1_S})\Gamma_{L_O}\Gamma_{L_S} + \Gamma_{L_M}((\Gamma_{1_M} - \Gamma_{1_O})\Gamma_{L_O} + (\Gamma_{1_S} - \Gamma_{1_M})\Gamma_{L_S})}{g}$$

(2.21)

$$S_{12} = \frac{(\Gamma_{1_O} - \Gamma_{1_M})(\Gamma_{1_M} - \Gamma_{1_S})(\Gamma_{1_O} - \Gamma_{1_S})(\Gamma_{L_M} - \Gamma_{L_O})(\Gamma_{L_M} - \Gamma_{L_S})(\Gamma_{L_O} - \Gamma_{L_S})}{g^2}$$

(2.22)

$$S_{22} = \frac{(\Gamma_{1_S} - \Gamma_{1_O})\Gamma_{1_M}\Gamma_{L_M} + (\Gamma_{1_M} - \Gamma_{1_S})\Gamma_{1_O}\Gamma_{L_O} + (\Gamma_{1_O} - \Gamma_{1_M})\Gamma_{1_S}\Gamma_{L_S}}{g}$$

(2.23)

### 2.2 Analog Part

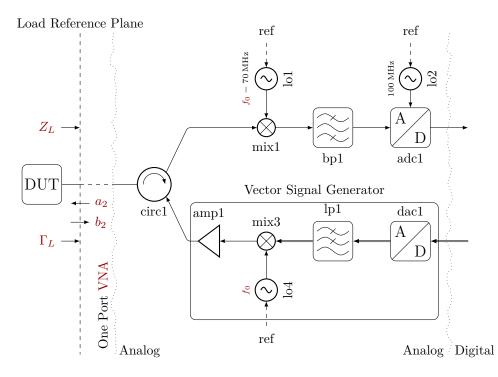

The analog part, which was designed for the ELP system can be seen in figure 2.5. It consists of everything needed to prepare the signal for analog-to-digital conversion and back. Furthermore it contains a circulator (*circ1*), which is needed for splitting the incident power wave  $b_2$  and the reflected power wave  $a_2$ . Instead of a circulator a directional coupler could be used (see chapter 5 for an example) [3].

The upper analog processing chain in figure 2.5 handles the incident power wave  $b_2$ . It is responsible for shifting the frequency spectrum of the power wave from RF to an IF of 70 MHz. This superheterodyne design, with baseband mixing implemented in the digital part (see section 2.3), was chosen because it exhibits no amplitude imbalances between I and Q. This setup has the additional feature, that the DC-component caused by the analog mixer *mix1* is outside the band of interest at IF. Therefore, there is no gap around 0 Hz in baseband and the whole bandwidth is usable. 70 MHz was chosen as IF, because it is a widely used IF in radar and microwave applications [16–19] leading to many available components for this frequency band and compatible microwave laboratory equipment [20].

After shifting the band of interest to the IF, the signal is converted from analog to digital (bp1 and adc1). For the sampling rate 100 MS/s was chosen, since it provides enough headroom to support the earlier mentioned bandwidth. Furthermore the chosen vector signal generator supports this sample rate at the digital input port.

Figure 2.5: Analog part

To fulfill the sampling theorem, this sampling rate is too low for the chosen IF, therefore bandpass sampling was used. This necessitates that a bandpass filter is used as alias filter bp1.

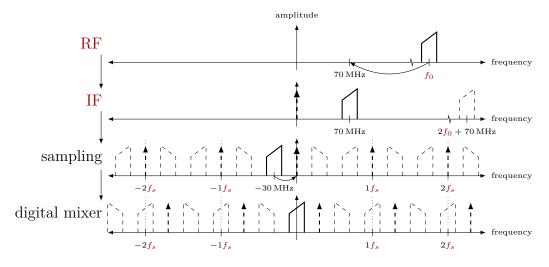

Figure 2.6 explains the frequency spectra for the complete down conversion chain (including the digital mixer). The first plot sketches the spectrum of interest in RF around the frequency  $f_0$ . After the mixer mix1, the spectrum of interest lies at 70 MHz and  $2f_0 + 70$  MHz, which is caused by the analog mixer. Because of this, even if only single tones within the determined bandwith around  $f_0$  are generated, at least a low pass has to be used as filter bp1. As mentioned earlier, the mixer also generates a DC component, which is depicted as vertical dashed arrow. During sampling spectral aliases occur. These are located at (k100 MHz + 70 MHz) and in mirrored form at (k100 MHz - 70 MHz). This mirroring would cause mixing of frequency components around ( $f_0-40 \text{ MHz}$ ) into the band of interest, if no bandpass filter is used. The last step is the digital mixer, which shifts the spectrum by -70 MHz which is equivalent to +30 MHz caused by the 100 MHz sampling. After that the band of interest lies around 0 Hz (see section 2.3).

The ADC chosen for this work was an LTC2274. This 16 bit ADC has an input bandwidth of 700 MHz and is capable of 105 MS/s [21]. With these specifications and above discussed filtering techniques for limitation of the signal bandwidth it is suited for sampling the IF of 70 MHz with the sample rate of 100 MS/s. This

Figure 2.6: Down conversion frequency spectra ( $f_s = 100 \text{ MHz}$ )

ADC has a JESD204 compliant high speed serial interface [21]. This interface uses 8b/10b line coding over a low voltage differential signalling (LVDS) connection [22]. The line coding is responsible for keeping a balanced number of ones and zeros on the line, therefore keeping a long term DC balance on the line. This allows transmitting the data stream through a high pass channel. Clock recovery is also possible, since this protocol ensures frequent transitions in the bit stream. Any other ADC capable of handling these requirements and a similar digital interface can be used as a drop in replacement for this ELP system.

Digital to analog conversion and up conversion is handled by the lower analog processing chain in figure 2.5. In this work the signal vector generator SMBV100A from Rohde & Schwarz with digital IQ input support (R&S SMBV-K18 [23]) was used for these tasks. Like for the ADC a different signal vector generator can be used as a drop in replacement, if it uses the same digital interface (see section 2.3).

## 2.3 Digital Part

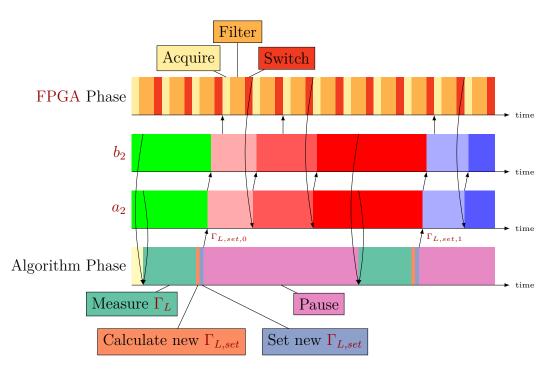

The digital part in figure 2.7 consists of a single 16 bit digital signal processing chain operating at 100 MS/s. It is responsible for the reflection synthesis. This reflection synthesis is achieved with the filter *fir1* and the multiplicator *mul1*. Furthermore it contains the mixer *mix2*. This mixer is needed for IQ-demodulation and down conversion from IF to baseband. The filter *fir1* needs a static digital representation of the samples for the filter calculations. Therefore, the additional sample buffers *buffer1* and *buffer2* are included into the signal processing chain.

Figure 2.7: Digital part

As can be seen in figure 2.7, a digital representation of the IF signal  $b_2$  is provided by the analog part. As mentioned in section 2.2 the LTC2274 with a JESD204 compatible high speed serial interface was chosen as ADC. Instead of special sequences marking word and byte boundaries during communication the receiver interface has to be synchronized before data can be received. During this synchronization mode a JESD204 compatible serial interface sends a specific code sequence instead of data. This code sequence can be used to detect word boundaries and byte ordering. This synchronization mode has to be requested explicitly via dedicated pins of the ADC. In order to minimize needed cabling a communication scheme was developed that initiates synchronization mode by briefly stopping the clock signal.

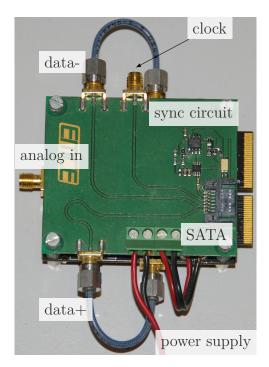

To minimize the hardware development time, a Linear Technology DC1151A-D evaluation board including the ADC was used in this work. This board consists of a sub-miniature version A (SMA) connector for the analog input, two SMA connectors for data+ and data- of the LVDS connection, an SMA connector for clock input and two pins to enable the synchronization mode. For easier wiring an adapter circuit board was designed to use a serial AT attachment (SATA) cable for clock and data. Furthermore, a synchronization circuit which implements the above mentioned synchronization method was developed.

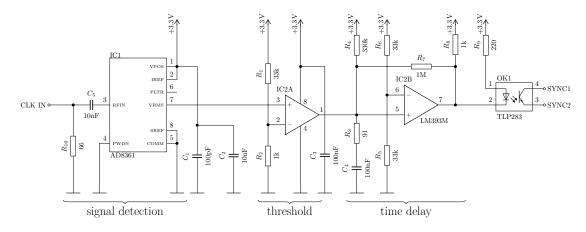

The synchronization circuit in figure 2.8 consists of three parts. The first part is the power detector IC1 which is connected via  $C_5$  to the TX+ pin of the SATA

Figure 2.8: Synchronization signal generator for ADC

connector. The TX– pin of the SATA connector is directly connected to an SMA connector. This enables clocking the ADC board using a clock signal delivered by the FPGA. The second part is the comparator IC2A. It is used to define a minimum threshold of about 15 mV<sub>RMS</sub> for valid clock signals which is determined by R1, R2, and the power detector IC1. The last part is a time delay element. This time delay starts after a valid clock signal is detected and lasts for about 30 ms. During this time the pins SYNC1 and SYNC2 are connected via the optocoupler OK1, which enables the synchronization mode of the ADC. The implemented adapter circuit board atop the ADC evaluation board can be seen in figure 2.9.

Figure 2.9: ADC adapter board with disconnected clock atop LTC2274 demo board

Samples provided via this connection by the ADC are stored in the sample buffer *buffer1*. As mentioned earlier this LP system needs a cyclic signal for reflection synthesis. Therefore, the buffer needs to store one or multiple periods of the signal. The signal periodicity additionally allows averaging the signal which helps improving the signal-to-noise ratio (SNR) of the ADC [24]. This averaging was implemented by increasing the sample size of this buffer to 19 bit. Furthermore, samples can be accumulated from up to eight consecutive signal cycles. Averaged samples can then be read by dividing the accumulated samples by the number of cycles.

After this buffer, the IF sampled data is IQ-demodulated into baseband with mixer mix2. The local oscillator (LO) lo3 synthesizes the needed -70 MHz ( $\equiv +30$  MHz with 100 MHz sampling) sine and cosine waveforms using a fixed lookup table. This approach has the advantage of a highly accurate IQ-demodulation without any amplitude or phase imbalances. After baseband conversion, a low pass filter would be needed to suppress the aliases generated from the sampling process, as can be seen in figure 2.6. This task can also be achieved with the configurable filter *fir1* in the next processing step. Therefore, the aliasing filter was left out of the design to keep resource usage at a minimum.

Next in the signal processing chain is the FIR filter *fir1*. As mentioned earlier this filter is needed to compensate the group delay and frequency responses caused by the measurement setup. In combination with a cyclic signal this filter is capable of synthesizing negative phase shifts which is needed to compensate the group delay introduced by cabling needed between the DUT and the measurement setup. Implementing FIR filters consisting of a high number of filter coefficients uses significantly more resources with a tapped delay line than with the FFT. Therefore, the filter *fir1* was implemented with linear convolution:

$$y[n] = h[n] * x[n] = \sum_{m=0}^{n_{\rm fft}-1} h[n]x[n-m]$$

=  $\mathcal{DFT}^{-1} \{ \mathcal{DFT}(x[n]) H[n] \}$  (2.24)

with

$$H[n] = \mathcal{DFT}(h[n]) \tag{2.25}$$

This filter is a causal FIR filter with the input x[n], the length  $n_{\text{fft}}$ , the impulse response h[n], and the output y[n]. The input samples x[n] represent the samples in buffer *buffer1* and the output samples y[n] the samples in buffer *buffer2*. To further reduce the needed hardware resources the implemented filter *fir1* uses the transfer function H[n] instead of the impulse response h[n] (see equation (2.25)).

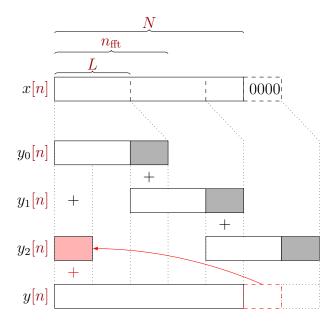

Since implementing the FFT in hardware uses a lot of resources, overlap add was used to allow for larger signal periods than  $n_{\rm fft}$ . As shown by [25] this algorithm splits the signal x[n] into non-overlapping subsequences of length L (see figure 2.10).

Figure 2.10: Overlap add algorithm (linear convolution, with circular in red)

Therefore, x[n] can be expressed by a sum of shifted finite-length sequences:

$$x[n] = \sum_{i=0}^{\infty} x_i[n-iL] \qquad x_i[n] = \begin{cases} x[k+iL] & k = 0, 1, \dots, L-1\\ 0 & \text{else} \end{cases}$$

(2.26)

Applying the linear convolution to this sum leads to

$$y[n] = h[n] * x[n] = \sum_{i=0}^{\infty} x_i[n - iL] * h[n] = \sum_{i=0}^{\infty} y_i[n - iL]$$

(2.27)

where  $y_i[n]$  is the linear convolution of  $x_i[n]$  with h[n]. Because every y[n] is of length  $N = L + n_{\text{fft}} - 1$ , equation (2.24) utilizing n-point FFTs can be used to calculate the results. Every convoluted subsequence  $y_i[n]$  overlaps by  $n_{\text{fft}} - L$ . Since this overlapping points are summed up by equation (2.27), this method is called overlap add. A visualisation can be seen in figure 2.10. The red part in the figure is the circular extension of the linear convolution, which is done by adding the  $n_{\text{fft}} - L$  points after the sequence y[n] to the beginning of y[n].

The filter *fir1* needs exclusive access to the output samples during computation. Another requirement is, that samples are continuously output to the DAC. This is needed to ensure that the DUT does not leave eventual operating points during measurements. Therefore, the buffer *buffer2* after the filter was implemented with double buffering. This means that this sample buffer consists of an active and an inactive buffer. The active buffer is used to continuously play back the output signal, while the inactive buffer can be used during the filter calculations. After a new signal period has been computed the buffers can be swapped without interrupting the output signal.

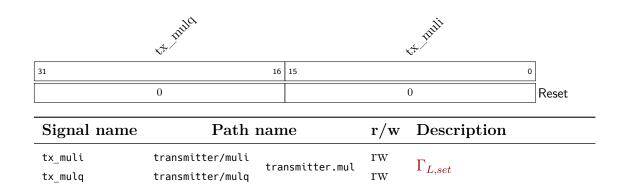

The last element in the processing chain is the complex multiplier *mul1*. This multiplier is responsible for the actual reflection generation. It allows adjusting the phase and amplitude of the reflection coefficient  $\Gamma_{L,set}$  by varying X and Y. Samples from *buffer2* are continuously multiplied with this reflection coefficient and output to the analog part as signal  $a_2$ .

The digital interface needed to forward the processed samples to the analog part was implemented according to the digital IQ interface supported by the used SMBV100A signal generator from Rohde & Schwarz. According to [26], this interface is implemented according to the channel link serializer described in [27]. This serializer uses eight LVDS data lines and one LVDS clock line. Each of the lines is clocked at 700 MHz for a sample rate of 100 MHz. An adapter board was developed for this work that allows connecting pin headers of an FPGA board with the needed mini D ribbon connector [26]. The connector and the wiring schema for the adapter were laid out according to the data sheet in [26]. One missing detail from the documentation, which was found out empirically during this work, is that the S\_CLK pin of the connector has to be connected to ground. This signal is marked for future use in the data sheet [26]. Without this ground connection the SMBV100A signal generator does not recognize a connected peripheral at the digital in a potential in the digital in the data sheet in [26]. A photo of the implemented pin header to digital IQ adapter including the fix can be seen in figure 2.11.

Figure 2.11: Digital IQ adapter circuit board with S\_CLK fix

The complete digital signal processing chain described in this section was implemented in an FPGA. A detailed description of the digital hardware implementation can be seen in chapter 3.

## **3 FPGA Implementation**

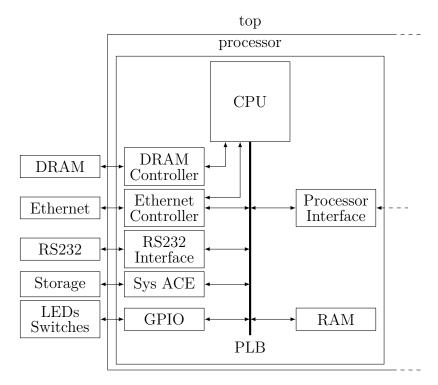

The digital part, as described in section 2.3, was realized in very high speed integrated circuit hardware description language (VHDL). It was specifically tailored to a Xilinx Virtex-5 FXT on an ML507 evaluation board. The FPGA model XC5VFX70T on this evaluation board provides the necessary high speed transceivers, sufficient block random access memories (RAMs), and dedicated digital signal processing hardware [28]. Furthermore the ML507 board contains an SATA connector needed for the ADC and pin headers with high speed differential signal routing to the FPGA which can be used for the digital IQ interface. Additionally, the board contains an Ethernet port enabling high speed data exchange with a PC. Although, according to [29], the SATA headers are only rated up to 1.5 Gbit/s, it was confirmed during tests that the necessary 2 Gbit/s, as required by the ADC [21], are also technically feasible. This FPGA also contains a hardwired PowerPC central processing unit (CPU), which was used for controlling the digital components and as a communication bridge to the PC.

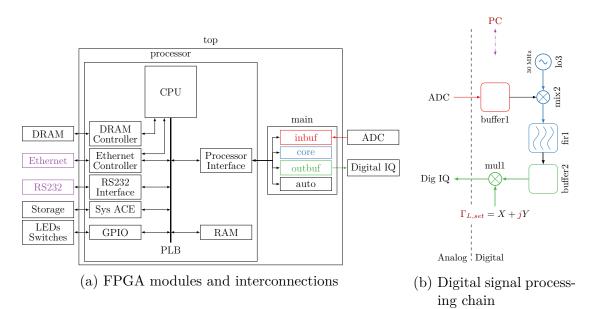

# Figure 3.1: FPGA design overview and digital signal processing chain with color coded modules

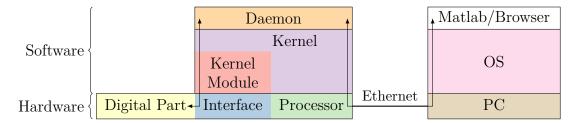

The design overview, as can be seen in figure 3.1a, describes the high level modules

#### 3 FPGA Implementation

of the design and connections between them. Names used in this design overview and the following overviews in this chapter are the actual module names used in the source code. The overall design was split into two parts. The first part is the digital signal processing chain in figure 3.1b (see section 2.3) implemented in the *main* module. The *main* module is described in section 3.1. The second part is the *processor* module which contains a complete embedded processor system. This module was used to implement the necessary protocols for communicating with a PC in software. It is described in section 3.2.

This design uses the unrelated clocks from the processor local bus (PLB) and the ADC. Therefore clock synchronization was needed to minimize the chance of metastable processes. This was achieved using a two-stage synchronizer as the base synchronization circuit. Signals with short pulses were synchronized with an additional pulse shaping to prevent lost pulses. Signal buses were synchronized with an open loop approach. This approach leaves out the acknowledgement of the synchronization which is sufficient for this design because the *processor* module is not fast enough to change the bus value within the synchronization period. Block RAMs in the used FPGA are true dual port memories. Therefore no synchronization is necessary for read access. If one port is used for writes to the memory the other port must not be used to access the same location at the same time [30]. Care was taken to avoid this situation by disallowing memory access from the other port during writes.

To ease software development a full operating system (OS) was used as software for the CPU. Linux was chosen as the OS for the *processor* module, since it is freely available and can be configured specifically for this target. As will be discussed in section 3.2 the *processor* design includes the modules needed to use Linux. An overview of the complete Linux implementation can be seen in chapter 4.

A reference to all hardware source codes and project files, which are needed to generate the hardware, can be found in appendix A.1.

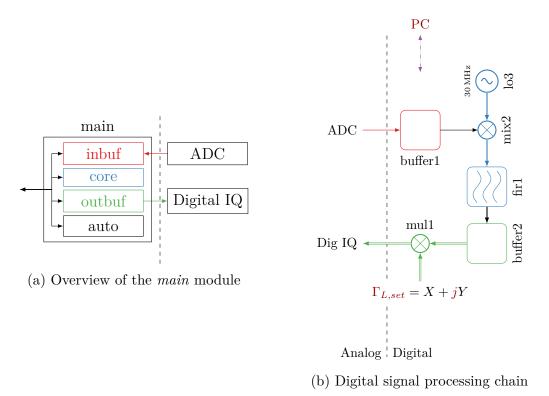

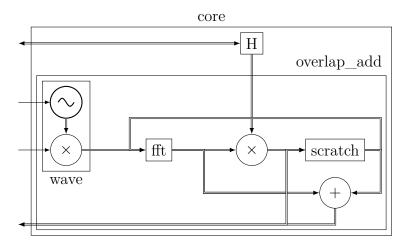

## 3.1 Digital Signal Processing Chain — main

The main module contains the digital signal processing chain. As can be seen in figure 3.2 the different parts of the processing chain (figure 3.2b) are mapped to three modules (figure 3.2a). The module *inbuf* contains the digital receive interface for the ADC and the sample buffer *buffer1*. This module is described in section 3.1.1. The *core* module contains the frequency mixer *mix2*, the LO *lo3*, and the digital filter *fir1* with the accompanying buffer *H* containing the transfer function H[n]. A detailed description can be seen in section 3.1.2. The third part is

the *outbuf* module. This module contains the sample buffer *buffer2*, the multiplier *mul1*, and the digital IQ interface and is described in section 3.1.3. The filter *fir1* is not capable of handling a continuous data stream (see section 3.1.2). Therefore the *auto* module was implemented to emulate continuous behaviour by sequentially activating the modules *inbuf*, *core*, and *outbuf*. A more detailed description of the *auto* module can be seen in section 3.1.4.

Figure 3.2: *main* module overview and digital signal processing chain with color coded modules

Necessary bit width truncations throughout the digital signal processing chain use convergent rounding. This rounding mode was used to prevent DC offsets. It rounds to even integers in case of a tie. For example rounding 4.5 with this method results in 4. The same would be true for 3.5. Thus rounding does not introduce an offset towards infinity or zero, as would be the case for round half up. Additionally, overflows are signalled and saturation is used where applicable.

The sample buffer size was chosen according to the available block RAM in the FPGA. A maximum number of 148 block RAMs capable of storing up to 36 kbit is available in the Virtex-5 on the ML507 board [28]. Those block RAMs can also be used as two independent 18 kbit block RAMs. As mentioned in section 2.3, the digital signal processing chain needs to support a sample width of 16 bit. Input averaging was chosen to support a maximum of 8 averages, resulting in an overall needed bit with of 19 bit for the input buffer. Since the output buffer uses double

buffering and needs to store IQ signals, two buffers with a bit width of 32 bit are needed. In order to achieve a high memory utilization, constrained by the possible block RAM bit widths, a single data bit of a buffer was realised with a 36 kbit and an 18 kbit block RAM. This leads to a total number of 124.5 block RAMs where 0.5 denotes an 18 kbit block RAM. This leaves enough for the embedded processor and the FFT implementation. Using this memory layout only a 2-to-1 multiplexer for the output is needed. Since the highest address line can be used as selection between both block RAMs, no address decoder is needed. This ensures fast operation of the overall memory. In one bit mode only 32 kbit (16 kbit) are available. This leads to a theoretical buffer depth of 49,152 samples. However as will be explained in section 3.1.2 (see also section 2.3), if circular convolution with a block size of L and an FFT size of  $n_{\rm fft}$  is used for the FIR filter, the full buffer depth is not usable. This is caused by the implementation of the overlap add algorithm which needs additional buffer space of  $L - n_{\rm fft}$  samples after the signal.

The memory buses of the *inbuf* module and the *outbuf* module are connected to the *core* module. The same bus connections are also exposed via a memory interface of the *core* module. To prevent access violations the exposed memory interface can't access the internal modules while one of them is active. Also further module activations are not possible during this period. With these restrictions in place no memory corruptions can occur. The *core* module also exposes every configuration and status signal of the internal modules. These signals are used by the processor interface described in section 3.2.1 for controlling the whole signal processing chain.

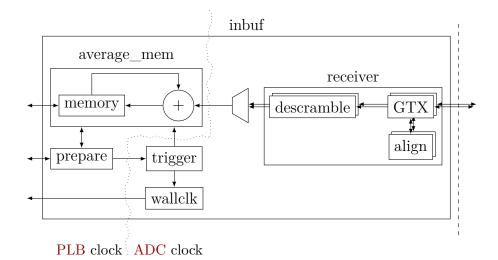

#### 3.1.1 Data Acquisition — inbuf

The *inbuf* module is responsible for serial to parallel conversion of the ADC data, descrambling, triggering, averaging, and storing the acquired samples. As can be seen in figure 3.3, this module consists of the main modules *receiver*, which handles receiving the data stream from ADC, and *average\_mem*, which handles storing the samples in a buffer and averaging. The additional modules *trigger*, *prepare*, and *wallclk* are responsible for controlling the data acquisition and keeping the time, which is needed for the IQ demodulation that will be explained in section 3.1.2.

The serial to parallel conversion of the received data was implemented using the built in GTX transceiver. Since the ML507 board features two SATA ports, two identical receivers were implemented. Since the GTX blocks need a lot of configuration settings, they were instantiated using the recommended method, which is the transceiver wizard documented in [31]. The settings used in this work were chosen according to the data sheet of the ADC [21]. The receiver was configured to handle the specifications as described in the section 2.3. These are 8b/10b line

Figure 3.3: Block diagram of the *inbuf* module

coding, a data width of 16 bit and a target line rate of 2 Gbit/s. Synchronization was configured for an enabled idle synchronization mode (ISMODE) of the ADC. In this mode the transmitter of the ADC sends idle ordered sets instead of commas during synchronization [21]. An idle ordered set is a special sequence used for synchronization consisting of a K28.5 comma followed by either D5.6 or D16.2 code word. A comma is a special code sequence of the 8b/10b line coding, which does not represent valid data [32]. To synchronize the GTX receiver according to these specifications, the comma alignment was set to align to even byte boundaries and to detect the K28.5 comma. After serial to parallel conversion, the endianness is converted to the internal representation. The recovered clock from the received data stream is used as the internal sampling clock. This setup allows the use of an externally provided sampling clock, by connecting it to the ADC instead of the clock provided by the ADC adapter circuit board mentioned in section 2.3. The receiver and the transmitter share the internal clock generation of the GTX. Therefore the transmitter had to be configured for the same line rate. To transmit a clock signal with the transmitter, the 8b/10b line coding was disabled for the transmitter and a fixed clock pattern was applied to the parallel input.

It is not possible to provide an externally generated clock directly to the SATA connected GTX transceivers because of design limitations of the ML507 evaluation board. Since using a clock, which is routed through the global clock network of the FPGA introduces jitter [32], an externally provided sampling clock connected to the ADC is the preferred mode of usage.

The module *align* controls the clock signal, which is transmitted using the GTX. This module contains a state machine that blanks the clock signal for 41 ms after a loss of sync of the receiver. In combination with the synchronization circuit

#### 3 FPGA Implementation

described in section 2.3 this clock blanking enables synchronization mode for the ADC. A loss of sync is detected if either a comma value or a value that is not part of the 8b/10b line coding is detected. After the blanking period the clock signal is reactivated and the GTX is put into alignment mode, which searches for the above mentioned comma K28.5. If no comma is detected during a further 41 ms period the synchronization re-starts from the beginning.

Succeeding the GTX transceiver, the *descrambler* module descrambles the data according to the data sheet of the ADC [21]. Data scrambling is used to lessen the noise caused by the digital transmission in the analog part. The scrambler implemented in the ADC is based on the generator polynomial given in equation (3.1) [22]. This scrambler can be bypassed if a different ADC is used.

$$g(x) = 1 + x^{14} + x^{15} ag{3.1}$$

Averaging the data is handled by the *average* mem module. This module consists of the above mentioned  $(19 \times 49,152)$  bit memory. Averaging is achieved by reading the appropriate sample from the buffer and adding it to the current value. For the first run the read sample is replaced with the value zero. Using this method the sampled values are accumulated over a configurable number of zero, two, four, or eight rounds. Averaging is achieved during memory access from outside the module by shifting the accessed values by zero, one, two, or three bit. This is equal to dividing the samples by the number of rounds used for averaging. This method needs to read the sample from the last round from the buffer while writing the current sample to the buffer. Therefore, both ports of the memory are needed by the implementation which implies that the synchronization technique using different ports for the different clock domains as described above is not feasible. Hence, the memory interface allowing access to the sample buffer from outside the *inbuf* module needs to share the ports with the averaging mechanism. Since those two parts don't share the same clock, clock multiplexing with dedicated FPGA hardware was implemented.

If the data acquisition is not in use, the *average\_mem* is powered by the PLB clock. Before data acquisition, the *prepare* module transitions the clock signal to the ADC clock. Undefined behaviour can occur if the timing conditions of the address signals of the block RAM are violated while the enable signal is high. This can lead to memory corruption even if write enable is not asserted [30]. Therefore, the enable signal of the block RAM is switched to low by the *prepare* module before the clock transition. Since this is not possible for an unstable ADC clock, the validity of the sample buffers is not guaranteed after connecting or disconnecting an ADC. After the data acquisition finishes, the *prepare* module transitions the clock signal back to the PLB clock. Write operations to the memory are ignored during data acquisition. Read operations during data acquisition don't interfere with the process but the read out data is invalid.

#### 3 FPGA Implementation

The trigger module generates the start signal for the average\_mem and the wallclk module. During the first run and after a reset, the trigger can either be triggered externally or internally. The external trigger is sampled from the pin AN33 of the FPGA, which is connected to HDR1\_64 on the evaluation board. After the first successful trigger, consecutive triggers are only generated at multiples of the configured signal period N.

Subsequent to a trigger event, the *wallclk* module takes a snapshot of the jiffy counter which marks the time the first sample of the current acquisition was acquired. A jiffy is 10 ns in this FPGA design which is the time needed for one sample for a sample period of 100 MHz. The 30 MHz signal for the IQ demodulation is not generated in real time. Therefore the snapshot of the jiffy counter is necessary for the *core* module to generate the 30 MHz signal with the correct phase (see sections 2.3 and 3.1.2).

The *inbuf* module is fully runtime configurable. Changing the active receiver or connecting an ADC resets the whole module automatically. This prevents undefined behaviour which could result from the clock change. Since the trigger source is only decisive for the first trigger event changing the source is only possible if the *trigger* module has not fired yet. Therefore, the trigger module should be reset after changing the source. Trigger events, averaging finished, and ADC connection status are reported with separate signals. The memory interface of the *inbuf* module has a 16 bit wide data bus, a 16 bit wide address bus, and a read access latency of 2 cycles. Accessing samples at addresses  $\geq 49,152$  result in undefined behaviour.

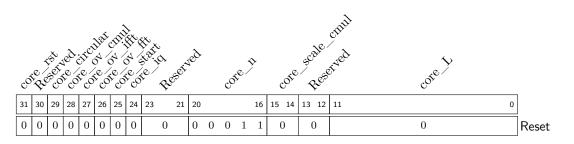

## 3.1.2 Overlap Add — core

An overview of the *core* module can be seen in figure 3.4. It consists of the buffer H, which is needed to store the transfer function, and the module *overlap\_add*, which contains the signal processing. The *overlap\_add* module itself contains the module *wave*, which is responsible for IQ demodulation, the *fft* module, which can calculate the FFT and inverse-FFT, a complex adder, a complex multiplier, and additional block RAM, needed as temporary buffer space (*scratch*).

The IQ demodulation module *wave* consists of a hard coded look up table, that generates a 30 MHz sine and cosine waveform for a sampling rate of 100 MHz. Furthermore it contains multipliers, which multiply the incoming samples with the sine and cosine waveforms, for converting the signal into I and Q samples. Instead of performing this demodulation in real time, it is performed during filter processing. To ensure the correct phase of the 30 MHz waveform it is evaluated at the point in time calculated from the jiffy counter and the position of the currently processed sample. The jiffy counter is contained in the *wallclk* module as explained

Figure 3.4: Block diagram of the *core* module

in section 3.1.1. This counter marks the time the first sample of the current signal was taken.

A Xilinx LogiCore IP was used as the fft module [33]. In order to minimize block RAM usage and increase the performance the pipelined version was used. A further reduction in block RAM usage was achieved by limiting the IP core to the minimum setting of three stages in block RAM. The remaining stages needed for this configuration are implemented in distributed RAM which results in a higher lookup table (LUT) usage of the fft [30,33]. Distributed RAM was preferred over block RAM because LUT usage was not a limiting factor in this design. The fft implementation was set to allow a modification of the FFT length at runtime, with a maximum length of 4,096. A further runtime configuration setting is, that this core can be switched between FFT and inverse FFT. This allowed using only one fft module. Therefore reducing the resource usage further. Every computational part of the FFT, called a butterfly, consists of an addition and a multiplication that preserves the magnitude of the complex valued input of the butterfly. The addition increases the needed bit width after every butterfly by one bit to represent every possible value. The multiplication can result in an overall bit width growth of one bit for the whole FFT if the magnitude represented by the complex valued input is greater than one. Combining both factors leads to equation (3.2) given in [33].

$$bits_{out} = bits_{in} + \underbrace{\log_2(n_{\rm fft})}_{\rm addition \ per \ butterfly} + \underbrace{1}_{\rm complex \ rotation}$$

(3.2)

According to equation (3.2), keeping every bit for an FFT length  $n_{\rm fft}$  of 4,096 and input width  $bits_{in}$  of 16 bit would result in a maximum output width  $bits_{out}$  of 29 bit. Using such high bit widths is not possible because of resource constraints. Therefore, scaling was used and is implemented with a divider after every group, where one group consists of two butterflies. Every divider can divide the samples by one, two, four, or eight. Since the possibility of overflows depends on the input

#### 3 FPGA Implementation

data the right scaling schedule can't be determined beforehand. According to [33] the best scaling schedule for the FFT and inverse FFT is found by starting with a divider schedule of one and incrementing the divider schedule until the computation stops overflowing. Input data for the FFT core needs to be in natural order and output data is in bit reversed order [33].

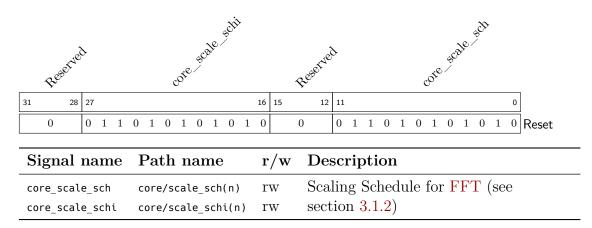

The complex multiplier was implemented with a runtime changeable scaling schedule. This schedule can be set to shift the result by 14 to 17 bits. Therefore, the transfer function should always be scaled to the maximum possible values. The best overall scaling schedule can be found by first configuring the scaling schedule of the FFT, then the complex multiplier and after that the inverse FFT.

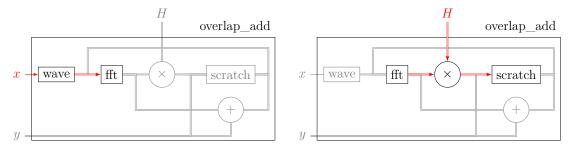

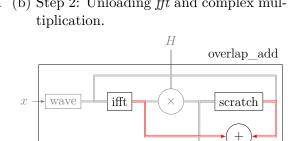

(a) Step 1: Up converting and filling fft with (b) Step 2: Unloading fft and complex mulsamples.

ifft

wave

x

$\boldsymbol{u}$

Н

overlap\_add

scratch

+

(c) Step 3: Loading the *fft* with the com- (d) Step 4: Unloading *fft* and adding the puted samples and loading scratch with the previous block.

overlapping part from *scratch*.

Figure 3.5: Overlap add algorithm hardware implementation

$\boldsymbol{u}$

The overlap add algorithm, as explained in section 2.3, was implemented with two separate state machines. This allows speeding up the process since some parts can be calculated in parallel. The first state machine controls the FFT and the complex multiplication part of the algorithm. It is called *fftncmul*. Inverse FFT and complex addition is handled by *ifftnadd*. The overall process is described in figure 3.5. Every block of size L needs to be processed within four steps. In the first step (figure 3.5a), the fft module is loaded with L IQ demodulated samples from the source memory x. According to the overlap add algorithm, after L samples the data input of the fft is switched to zero. After the fft module has finished

processing, the second step (figure 3.5b) starts. In this step the data is multiplied with H and stored in the scratch buffer. During the next step (figure 3.5c), the *fft* module is switched to inverse operation and the samples from the *scratch* buffer are loaded into the *fft* module. At the same time the *scratch* buffer is filled with the previous computed block from the target memory y. After the *fft* module has finished the computation, the last step (figure 3.5d) is executed. During this step the overlapping part from the previous block is added and the samples are unloaded into the target memory. Since the FFT module is pipelined, step one of the next block is started after step three of the current block has finished. This means, that the FFT module computes the samples of two different blocks at the same time. With this technique, the duration of the overlap add algorithm is reduced by one stage per L sized block. If the circular mode is enabled, then the block after the signal is added to the beginning (see section 2.3). Since this process needs  $L - n_{\rm fft}$ samples after the end of the signal, the sample buffer can't be used to the full extent.

The overall module is freely configurable and accepts FFT sizes 8, 16, 32, 64, 128, 256, 512, 1,024, 2,048, and 4,096. The signal size N has to be between 8 and 65,535 and the block size L between 1 and 4,096. There are no plausibility checks in the hardware, which means that wrong settings will lead to undefined behaviour. The *core* module can be stopped by issuing a reset signal. Numerical overflows are separately reported for FFT, inverse FFT, and complex multiplication.

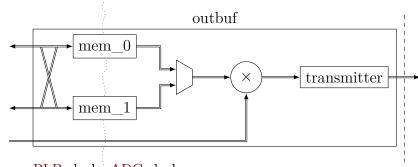

#### 3.1.3 Vector Signal Generator Interface — outbuf

The *outbuf* module consists of two independent sample buffers *mem\_0* and *mem\_1*, a complex multiplier and the digital IQ interface *transmitter*. The two sample buffers are both 32 bit wide, to store the 16 bit wide I and Q signals. Both can store up to 49,152 samples. A general overview can be seen in figure 3.6.

PLB clock ADC clock

Figure 3.6: Block diagram of the *outbuf* module

#### 3 FPGA Implementation