http://www.ub.tuwien.ac.at/en

FAKULTÄT FÜR !NFORMATIK Faculty of Informatics

# Simulated Fault Injection for Time-Triggered Safety-Critical Embedded Systems

## DISSERTATION

zur Erlangung des akademischen Grades

## Doktor/in der technischen Wissenschaften

eingereicht von

#### Iban Ayestaran Cipitria

Matrikelnummer 1228329

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Peter Puschner

Diese Dissertation haben begutachtet:

(Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Peter Puschner) (Prof. Dipl.-Ing. Dr. Gerhard Fohler)

Wien, TT.MM.JJJJ

(Iban Ayestaran Cipitria)

# Simulated Fault Injection for **Time-Triggered Safety-Critical Embedded Systems**

## DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

## Doktor/in der technischen Wissenschaften

by

#### Iban Ayestaran Cipitria

Registration Number 1228329

to the Faculty of Informatics at the Vienna University of Technology

Advisor: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Peter Puschner

The dissertation has been reviewed by:

(Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Peter Puschner) (Prof. Dipl.-Ing. Dr. Gerhard Fohler)

Wien, TT.MM.JJJJ

(Iban Ayestaran Cipitria)

## Erklärung zur Verfassung der Arbeit

Iban Ayestaran Cipitria Bidebieta Auzoa 1A, Aiestaran Enea. 20400 Tolosa

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit - einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

## Acknowledgements

This dissertation has been carried out in collaboration between the Electronics department of IK4-Ikerlan Research Center (Basque Country, Spain), and the Cyber-Physical Systems group of Vienna University of Technology (TU Wien). I would like to give thanks to all the people that contributed to its development.

First of all, I would like to thank my supervisor, Professor Peter Puschner from TU Wien, for his support during these years and his involvement in the supervision, including his trips to the Basque Country. Thanks also to Professor Gerhard Fohler from TU Kaiserslautern for his work as co-reviewer of this thesis.

Many thanks to Dr. Jon Perez, head of the Electronics area in IK4-Ikerlan, for his guidance, encouragement and full support. To Carlos Fernando Nicolas for all his advice, ideas, criticism and motivation that really made this thesis possible. To Christian El Salloum for his supervision during the first year of my work.

Many thanks to IK4-Ikerlan for giving me the opportunity to carry out a PhD in collaboration with TU Wien. I would like to mention all my colleagues in Ikerlan for their friendship and good atmosphere, and specially those that contributed somehow to my thesis, Gaizka, Mikel, Irune and Jan. Thanks also to the Cyber-Physical systems group of TU Wien for their hospitality, particularly to Haris, Bekim, Benedikt, Roland and Armin.

And finally, very special thanks to all my family, specially my parents Axun and Jose Luis and my sister Nerea for their comprehension, confidence, their optimism even in the difficult moments, and all the opportunities they gave me. To my girlfriend Stephanie, for her full support and motivation. To Pello, Kristina and Irati, for their valuable advice. And to my friends, Txorimaloak, for our interesting discussions in any other topic aside from work.

To all of you, eskerrik asko.

## Abstract

Safety-critical systems are dependable systems that could lead to loss of life, significant property damages or damages to the environment in case of failure, such as avionic and railway systems, offshore mills or nuclear power plants. Systems of this type must satisfy strict temporal constraints in order to guarantee certain safety properties. Besides, these systems must provide a certain degree of fault-tolerance, to guarantee that they keep a safe behavior even in the presence of faults in the system.

Historically, the control of safety-critical systems used to be handled by mechanical devices. However, due to the wide spectrum of possibilities that computer systems offer, these systems are nowadays commanded by computers. The most significant progress in this field may be the fly-by-wire system developed for the latest Airbus A380, which is fully controlled by a computer system. Moreover, the increasing functionality demanded by industry has lead to a considerable complexity growth. For example, highend cars had about 70 electronic control units (ECUs) back in 2006, and this number raised up to 100 by the year 2011.

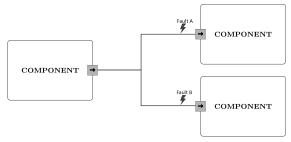

Therefore, tackling the complexity challenge and preserving time properties and constraints throughout the development process are key challenges in the field. With this goal, this research work presents the Platform Specific Time-Triggered Model (PS-TTM), a novel model-based development framework based on SystemC for time-triggered safety-critical embedded systems. The proposed modeling work-flow tackles the complexity challenge following the MDA process and the Y-chart paradigm, by raising the level of abstraction at the very first development stages and creating a purely functional Platform Independent Model (PIM). Once this abstract model is validated, HW-related concepts are integrated into the model and the Platform Specific Model is generated.

The work includes the PS-TTM Automatic Test Executor (PS-TTM ATE), a timetriggered testing and simulated fault injection framework for the validation of both platform independent and platform specific models of systems. The PS-TTM ATE provides a simulation environment that enables the test developers to check the behavior of the system under the considered circumstances. Besides, PS-TTM ATE includes a non-intrusive fault injection mechanism that allows testing teams to inject faults in the models during simulation, in order to evaluate the effectiveness of the fault-tolerance mechanisms implemented in them before assembling a system prototype.

## Kurzfassung

Sicherheitskritische Systeme sind Systeme, die im Fall einer Fehlfunktion zu tödlichen Unfällen, schwerwiegenden Eigentumsverlusten oder gravierenden Umweltschäden führen können. Beispiele für sicherheitskritische Systeme finden sich z.B. in der Luftfahrt, im Zugverkehr, in Offshore Windanlagen und Kernkraftwerken. Sicherheitskritische Systeme müssen strenge zeitliche Anforderungen erfüllen, um in jedem Moment die Sicherheit des Systems zu garantieren. Zusätzlich müssen sicherheitskritische Systeme einen gewissen Grad an Fehlertoleranz aufweisen, um auch im Falle eines Fehlers die Sicherheit des gesamten Systems gewährleisten zu können.

Früher basierten sicherheitskritische Systeme hauptsächlich auf mechanischen Elementen, während heutzutage mehr und mehr rein computergestützte Systeme eingesetzt werden. Einer der wichtigsten Fortschritte im Bereich rein computergestützter Systeme war sicherlich das Fly-by-Wire System des neuen Airbus A380, dessen Steuerungssystem vollständig computerbasiert ist. Zusätzlich zum Einsatz von computergestützten Systemen führt die zunehmende Funktionalität, die von der Industrie gefordert wird, zu einer beträchtlichen Steigerung der Komplexität aktueller sicherheitskritischer Systeme. Ein Auto der Oberklasse hatte zum Beispiel im Jahr 2006 um die 70 elektronische Steuergeräte, während diese Zahl im Jahr 2011 auf über 100 gestiegen ist.

Die Beherrschung der gestiegenen Komplexität bei gleichzeitiger Einhaltung aller zeitlichen Anforderungen ist eine zentrale Herausforderung für aktuelle sicherheitskritische Systeme. Mit dem Ziel, diese Herausforderung anzugehen präsentiert die vorliegende Forschungsarbeit das *Platform Specific Time-Triggered Model (PS-TTM)*, ein neuartiges modellbasiertes Entwicklungs-Framework in SystemC für zeitgesteuerte, sicherheitskritische Systeme. Zusätzlich zum Framework definiert die Forschungsarbeit einen neuartigen Workflow, der auf dem MDA-Process und dem Y-Chart Entwicklungsparadigma basiert. Der vorgeschlagene Workflow erlaubt die Beherrschung der Komplexität komplexer sicherheitskritischer Systeme dadurch, dass Systeme in den ersten Entwicklungsphasen mit plattformnabhängigen Modellen (PIMs) auf einem hohen Abstraktionsniveau modelliert werden. Nach der Validierung dieser abstrakten, plattformnabhängigen Modelle werden die Modelle um Hardware-spezifische Eigenschaften angereichert, um die plattformpezifischen Modele (PSMs) des Systems zu erhalten.

Neben dem Entwicklungs-Framework und dem Workflow beinhaltet die Forschungs-

arbeit den PS-TTM Automatic Test Executer (PS-TTM ATE), ein zeitgesteuertes Testund Fehlerinjizierungsframework zur Validierung von plattformunabhängigen und plattformspezifischen Modellen. Das PS-TTM ATE Framework stellt eine Simulationsumgebung zur Verfügung, mit der der Testentwickler das Verhalten des Systems in verschiedenen Situationen simulieren und validieren kann. Zusätzlich unterstützt PS-TTM ATE die nicht intrusive Fehlerinjizierung, welche es erlaubt, während der Simulation Fehler in die Modelle zu einzustreuen, um damit die Effektivität der im Modell implementierten Fehlertoleranzmechanismen zu untersuchen.

## Laburpena

Segurtasun kritikoko sistemak, akatsak jasanez gero kalte ekonomiko, ekologiko edo humanitario larriak eragin ditzaketen sistema txertatuak dira, sistema aeroespazialak, trenbide sareak, sistema eolikoak edota nuklearrrak esate baterako. Sistema hauek ezaugarri tenporal zehatzak bete behar izaten dituzte segurtasun maila jakin bat bermatu ahal izateko. Gainera, sistema hauek hutsegiteak modu jakinean jasateko gaitasuna izan behar dute, akats larrienak gertatuz gero ere jokaera segurua mantendu dezaten.

Duela urte gutxi arte, segurtasun kritikoko sistemen kontrola gailu mekanikoen ardura izan ohi zen. Azken hamarkadetatik hona, ordea, geroz eta ohikoagoa da sistema informatikoak erabiltzea sistema mota hauek kontrolatzeko. Adibide bezala, alor honetan lortu den aurrerapen nagusienetariko bat Airbus A380 hegazkinarentzat eraikitako *Fly-by-wire* sistema da. Sistema hauen berezko konplexutasuna handia izanik, gaur egun zailtasun hau areagotzen ari da, industriak eskatzen dituen funtzio gehigarrien ondorioz. Esaterako, 2006.urtean, luxuzko auto batek 70 kontrol elektronikoko unitate (ECU) inuguru zituen; 5 urte beranduago, 2011n, ECU kopurua 100etik gorakoa zen. Arrazoi hauengatik, gaur egungo segurtasun kritikoko sistemen garapenaren konplexutasun maila txikiagotzea, euren denbora-ezaugarriak murriztu gabe, erronka itzela da.

Helburu honekin, ikerketa lan honek Platform Specific Time-Triggered Model (PS-TTM) izeneko plataforma aurkezten du, denboraz jaurtiriko segurtasun kritikoko sistemak SystemC lengoaian garatzeko eta aztertzeko erreminta. Sistemen garapena errazteko asmoz, tesi honetan proposaturiko lan organigramak MDA eta Y-chart metodologiak jarraitzen ditu, garapen prozesuaren lehen etapetan modeloen abstrakzio maila igoz eta modelo funtzional soilak sortuz. Modelo funtzional abstraktu hauek hobetsita daudenean, hardware-arekin zerikusia duten kontzeptuak gehitzen zaizkie modelo horiei, abstrakzio maila modu kontrolatuan murriztuz.

Honetaz gain, lan honek PS-TTM Automatic Test Executor (ATE) deituriko plataforma aurkezten du. Plataforma hau PS-TTM bidez diseinaturiko sistema txertatuen jokabidea egiaztatzea ahalbidetzen duen test ingurune bat da. PS-TTM ATE-ak abstrakzio maila desberdinetan definituriko modeloetan akatsak txertatzeko eta simulatzeko gaitasuna du. Honi esker, diseinatzaileek euren sistemek akatsen aurrean erakusten duten erreakzioa aztertu eta akatsen aurkako mekanismoen eraginkortasuna ebaluatu dezakete, sistemen prototipo fisikoak eskuragarri izan aurretik.

## Contents

| 1 | 1 Introduction |                                                   |  |  |  |  |  |  |  |  |

|---|----------------|---------------------------------------------------|--|--|--|--|--|--|--|--|

|   | 1.1            | Motivation                                        |  |  |  |  |  |  |  |  |

|   | 1.2            | Goals of the thesis                               |  |  |  |  |  |  |  |  |

|   | 1.3            | Contribution                                      |  |  |  |  |  |  |  |  |

|   | 1.4            | Structure of the thesis                           |  |  |  |  |  |  |  |  |

| 2 | Bac            | kground and Basic Concepts 9                      |  |  |  |  |  |  |  |  |

|   | 2.1            | Dependability                                     |  |  |  |  |  |  |  |  |

|   | 2.2            | Fault Injection                                   |  |  |  |  |  |  |  |  |

|   | 2.3            | Cognitive Complexity                              |  |  |  |  |  |  |  |  |

|   | 2.4            | Model Based Design (MBD)                          |  |  |  |  |  |  |  |  |

|   | 2.5            | The Notion of Time                                |  |  |  |  |  |  |  |  |

|   | 2.6            | The Time-Triggered Architecture (TTA)             |  |  |  |  |  |  |  |  |

|   | 2.7            | SystemC                                           |  |  |  |  |  |  |  |  |

| 3 | Stat           | e of the Art 47                                   |  |  |  |  |  |  |  |  |

|   | 3.1            | Model Driven Architecture (MDA)                   |  |  |  |  |  |  |  |  |

|   | 3.2            | Architecture, Analysis and Design Language (AADL) |  |  |  |  |  |  |  |  |

|   | 3.3            | Distributed Application Layer (DAL)               |  |  |  |  |  |  |  |  |

|   | 3.4            | Fault-Tolerant Operating System (FTOS)            |  |  |  |  |  |  |  |  |

|   | 3.5            | Executable Time-Triggered Model (E-TTM)           |  |  |  |  |  |  |  |  |

|   | 3.6            | Simulated Fault Injection in VHDL Models          |  |  |  |  |  |  |  |  |

|   | 3.7            | Simulated Fault Injection in SystemC Models       |  |  |  |  |  |  |  |  |

| 4 | PS-1           | 63 GTM                                            |  |  |  |  |  |  |  |  |

|   | 4.1            | Introduction                                      |  |  |  |  |  |  |  |  |

|   | 4.2            | Overall Work-Flow                                 |  |  |  |  |  |  |  |  |

|   | 4.3            | The Meta-Model                                    |  |  |  |  |  |  |  |  |

|   | 4.4            | Characteristics of the PS-TTM                     |  |  |  |  |  |  |  |  |

|   | 4.5            | Modeling at Different Stages of the Development   |  |  |  |  |  |  |  |  |

|   | 4.6            | Mixed Abstraction-Level Simulation                |  |  |  |  |  |  |  |  |

| 5            | Test                  | ing and Simulated Fault Injection Framework   | 95  |  |  |  |  |  |  |  |

|--------------|-----------------------|-----------------------------------------------|-----|--|--|--|--|--|--|--|

|              | 5.1                   | The PS-TTM Automatic Test Executor (ATE)      | 95  |  |  |  |  |  |  |  |

|              | 5.2                   | Fault Injection Libraries                     | 106 |  |  |  |  |  |  |  |

|              | 5.3                   | Symmetric and Asymmetric Fault Injection      |     |  |  |  |  |  |  |  |

| 6            | Too                   | ling                                          | 117 |  |  |  |  |  |  |  |

|              | 6.1                   | Graphical SFI Campaign Designer Tool          | 117 |  |  |  |  |  |  |  |

|              | 6.2                   | Test Case Generator Script                    | 118 |  |  |  |  |  |  |  |

|              | 6.3                   | Test Result Interpretation Scripts            | 119 |  |  |  |  |  |  |  |

|              | 6.4                   | Graphical Modeling Tool (alpha version)       | 119 |  |  |  |  |  |  |  |

|              | 6.5                   | Integration of tools in the overall work-flow | 120 |  |  |  |  |  |  |  |

| 7            | Cas                   | e Study                                       | 123 |  |  |  |  |  |  |  |

|              | 7.1                   | European Train Control System (ETCS)          | 123 |  |  |  |  |  |  |  |

|              | 7.2                   | Modeling the system                           |     |  |  |  |  |  |  |  |

|              | 7.3                   | Results and Discussion                        |     |  |  |  |  |  |  |  |

| 8            | Con                   | clusion                                       | 151 |  |  |  |  |  |  |  |

|              | 8.1                   | Review                                        | 151 |  |  |  |  |  |  |  |

|              | 8.2                   | Analysis of the Contribution                  | 153 |  |  |  |  |  |  |  |

|              | 8.3                   | Future Work                                   | 154 |  |  |  |  |  |  |  |

| 9            | 9 List of Acronyms    |                                               |     |  |  |  |  |  |  |  |

| Bibliography |                       |                                               |     |  |  |  |  |  |  |  |

| Se           | Selected Publications |                                               |     |  |  |  |  |  |  |  |

| Cı           | irricu                | ılum Vitae                                    | 188 |  |  |  |  |  |  |  |

# **List of Figures**

| 2.1<br>2.2 | Causality chain of dependability threats (from [ALRL04])        | 10<br>13 |

|------------|-----------------------------------------------------------------|----------|

| 2.2        | A fault tree (from [BKSZN10])                                   | 13       |

| 2.3        | Representative Fault Injection Environment                      | 19       |

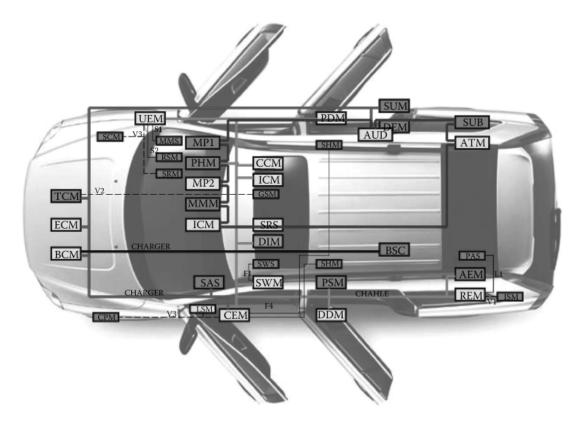

| 2.5        | Network infrastructure of the Volvo XC90 (from [HNSS09])        | 25       |

| 2.6        | Design work-flow of the Y-chart paradigm.                       | 28       |

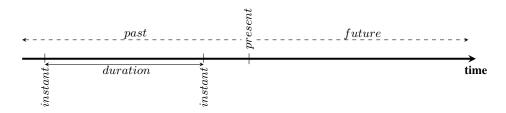

| 2.7        | Time flow                                                       | 29       |

| 2.8        | Models of time (from [Per11])                                   | 30       |

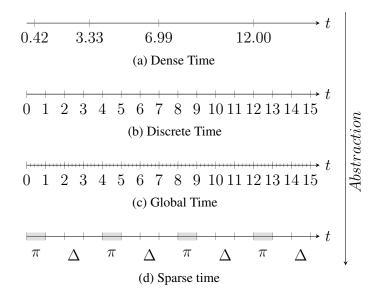

| 2.9        | Partially ordered schedule in SR models                         | 33       |

| 2.10       | Temporal firewall                                               | 35       |

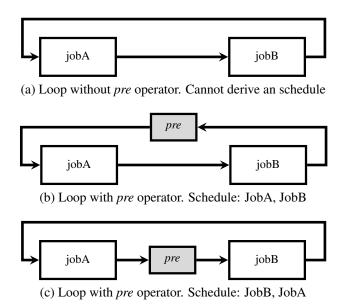

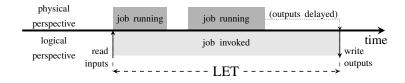

| 2.11       | LET: Logical Execution Time of a job                            | 36       |

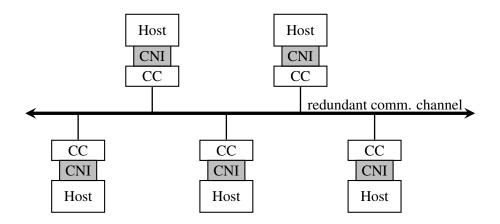

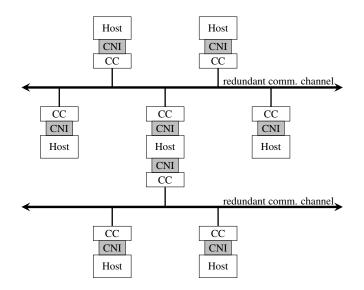

|            | Structure of a TTA cluster with five nodes                      | 41       |

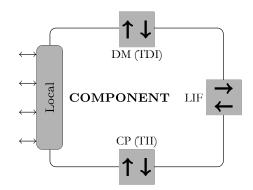

| 2.13       | Four interfaces of a TTA component                              | 43       |

| 2.14       | Structure of a TTA system with a gateway                        | 43       |

| 3.1        | Model Transformations according to the MDA (from [MM03])        | 49       |

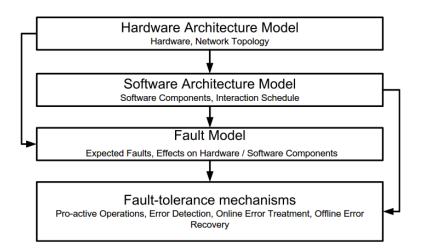

| 3.2        | Models of systems in FTOS and their dependencies (from [Buc08]) | 57       |

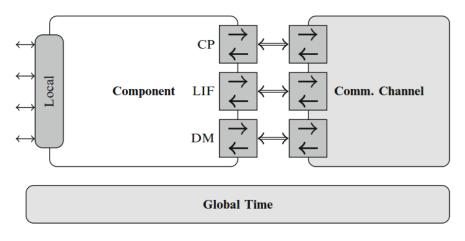

| 3.3        | E-TTM elements and relationships (from [PNOES10a])              | 58       |

| 5.5        | • · · · · · · · · · · · · · · · · · · ·                         |          |

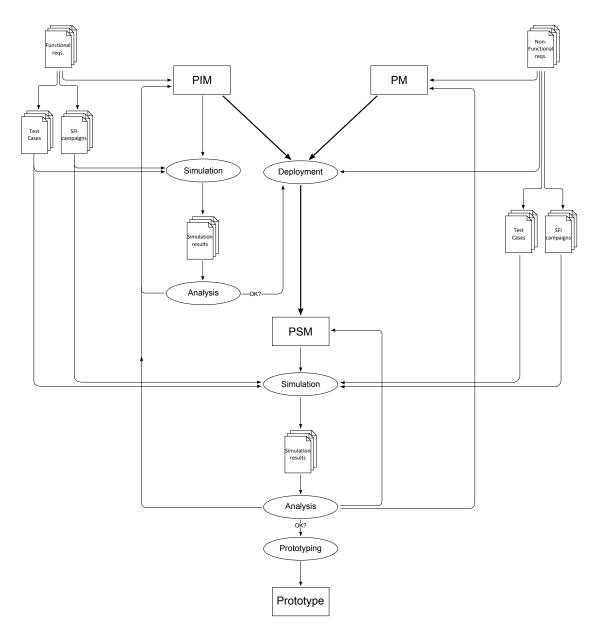

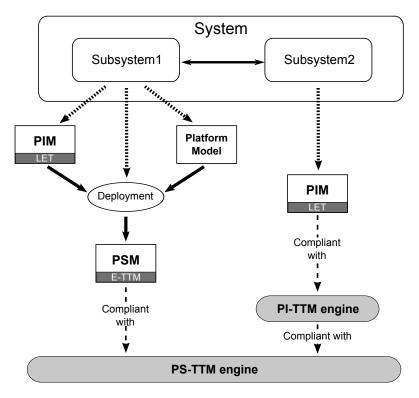

| 4.1        | Overall work-flow with the PS-TTM                               | 65       |

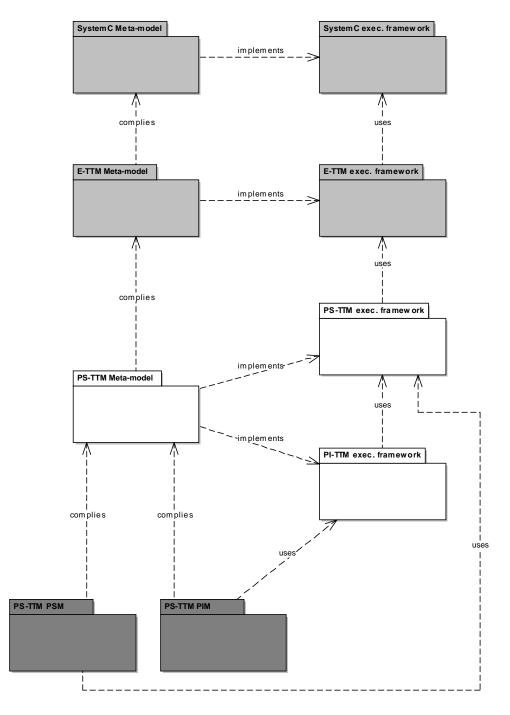

| 4.2        | PS-TTM meta-model, execution framework and models               | 67       |

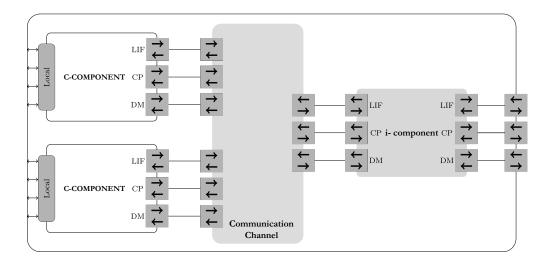

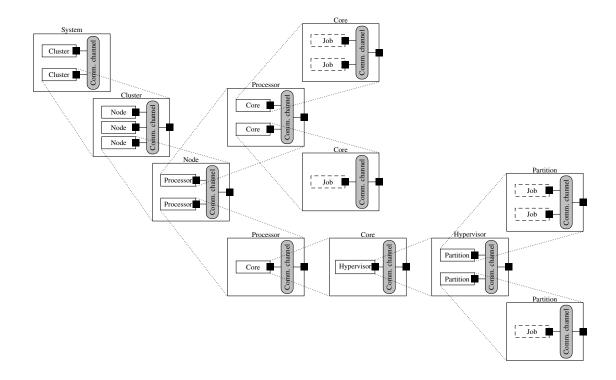

| 4.3        | PS-TTM: architecture of hierarchical components                 | 69       |

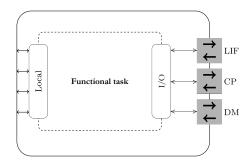

| 4.4        | PS-TTM: architecture of atomic components                       | 70       |

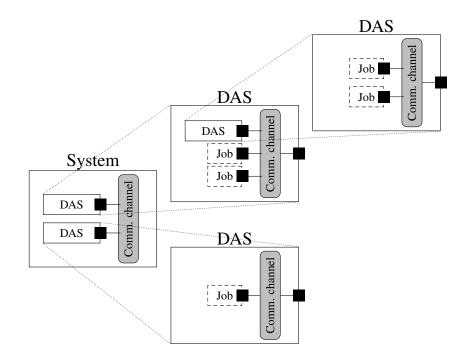

| 4.5        | Example of a PIM in the PS-TTM                                  | 74       |

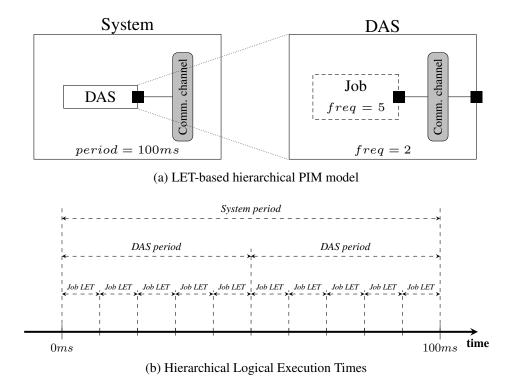

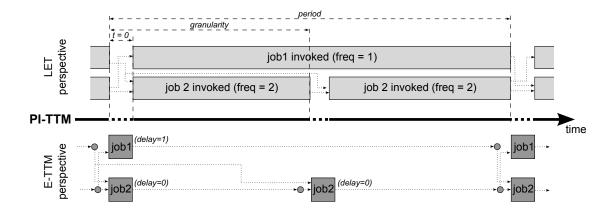

| 4.6        | Logical Execution Times in PS-TTM                               | 75       |

| 4.7        | PI-TTM: Management of LET-based PIMs                            | 77       |

| 4.8        | Example of a PSM in the PS-TTM                                  | 85       |

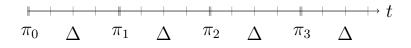

| 4.9        | Sparse time model in E-TTM ( $\pi = 0, \Delta = 4$ )            | 86       |

| 4.10       | Mixed abstraction-level simulation with PS-TTM                  | 93       |

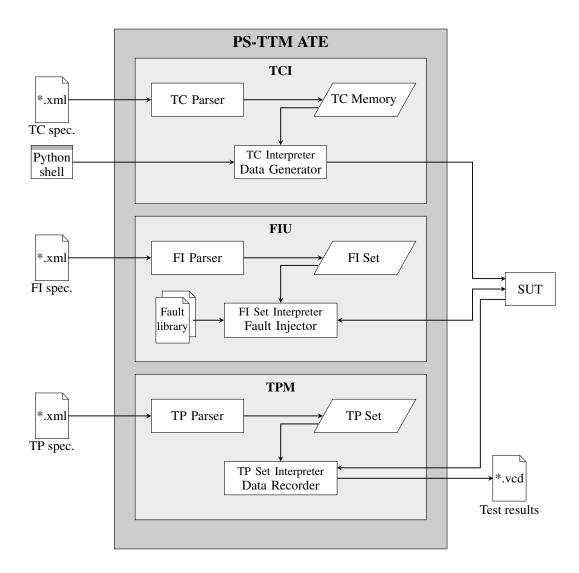

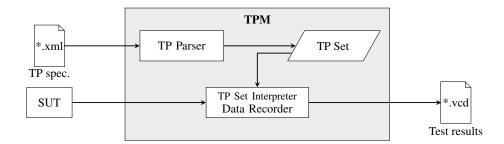

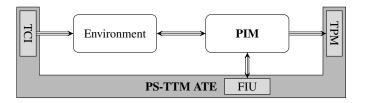

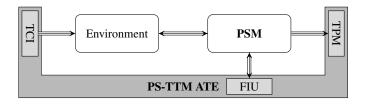

| 5.1        | PS-TTM Automatic Test Executor                                  | 96       |

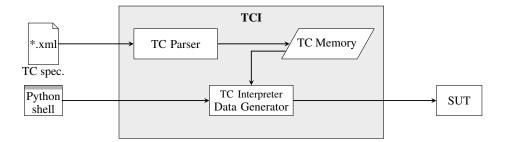

| 5.2        | Test Case Interpreter Module                                    | 97       |

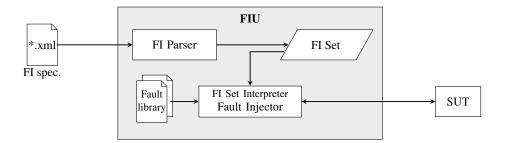

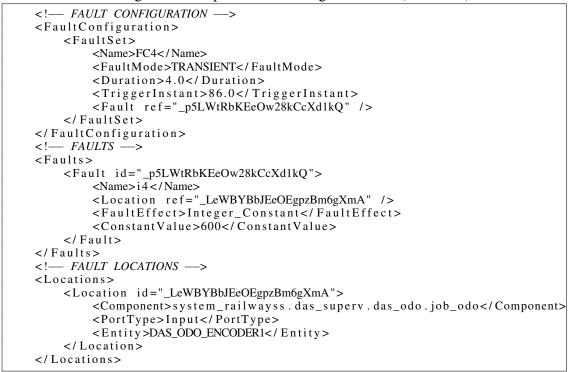

| 5.3  | Fault Injection Unit Module99                                                |

|------|------------------------------------------------------------------------------|

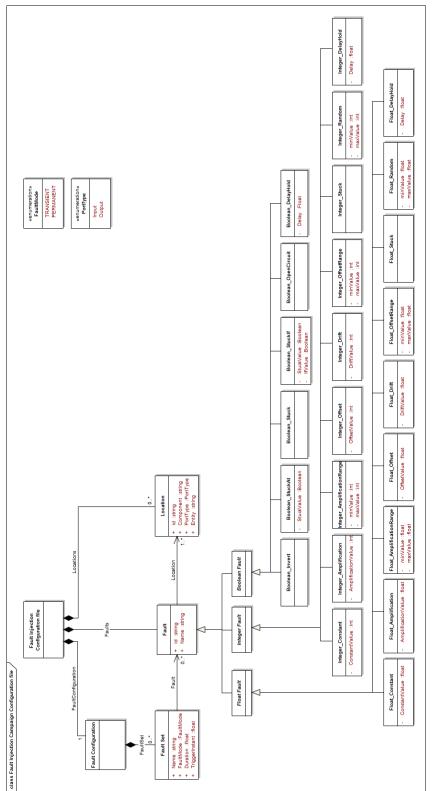

| 5.4  | UML Meta-model of Fault Injection Configuration XML files 103                |

| 5.5  | Test Point Manager Module                                                    |

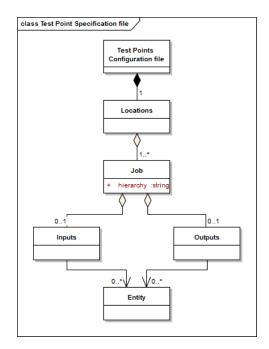

| 5.6  | UML Meta-model of Test Point Configuration XML files                         |

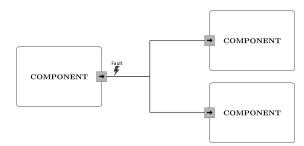

| 5.7  | Symmetric and Asymmetric Fault Injection                                     |

| 6.1  | Simulated Fault Injection Configuration Tool                                 |

| 6.2  | Integration of tools in the PS-TTM work-flow                                 |

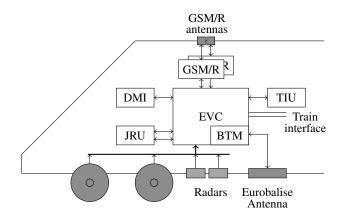

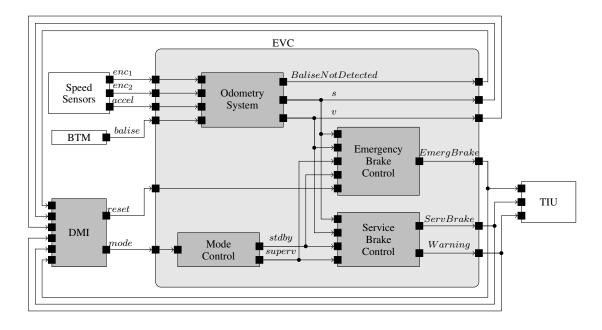

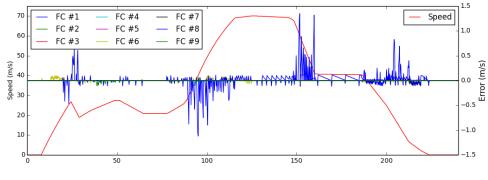

| 7.1  | ETCS on-board reference architecture                                         |

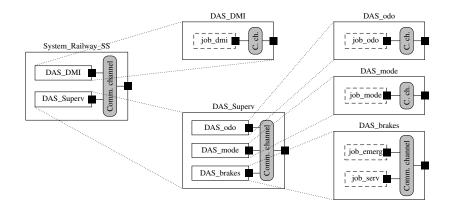

| 7.2  | Case Study: Functionality of the PIM 127                                     |

| 7.3  | Case Study: Platform Independent Model                                       |

| 7.4  | Composition of the testing and fault injection environment for the PIM 131   |

| 7.5  | Extract of the FMEA for the PIM                                              |

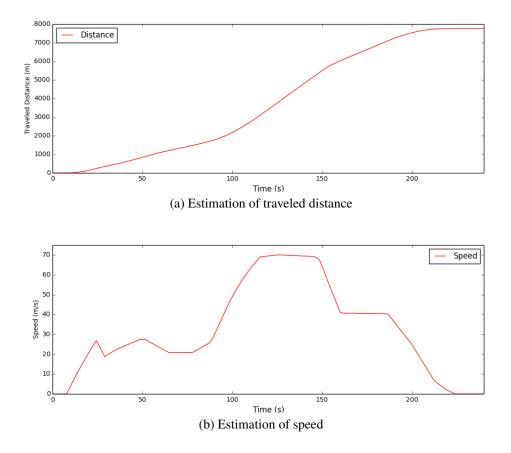

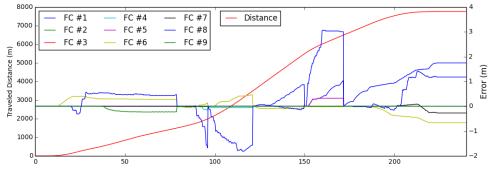

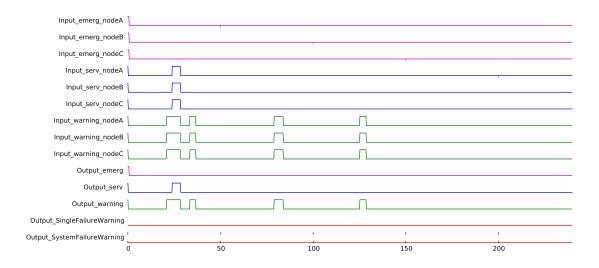

| 7.6  | Results of the fault-free simulation of the PIM                              |

| 7.7  | Estimation errors introduced by fault injection (PIM) 134                    |

| 7.8  | Case Study: Functional view emergency brake activation algorithm (PSM) . 135 |

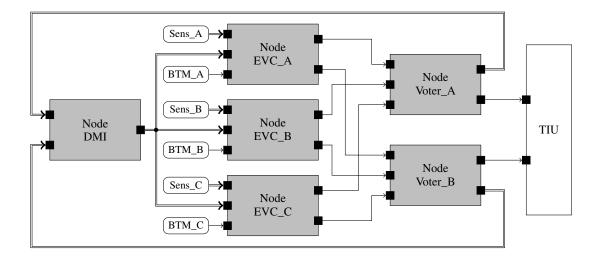

| 7.9  | Case Study: Platform Specific Model                                          |

| 7.10 | Composition of the testing and fault injection environment for the PSM 139   |

| 7.11 | Extract of the FMEA for the PSM                                              |

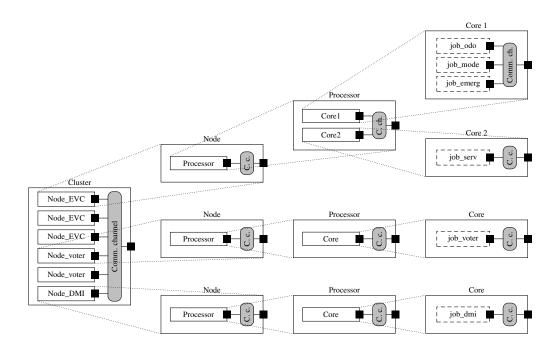

| 7.12 | Results of the fault-free simulation of the PSM                              |

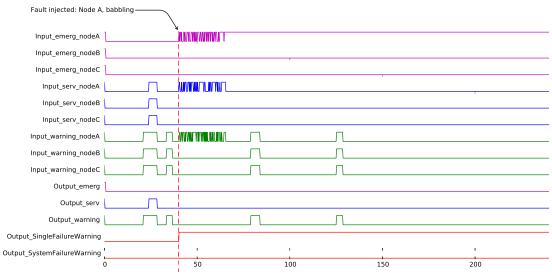

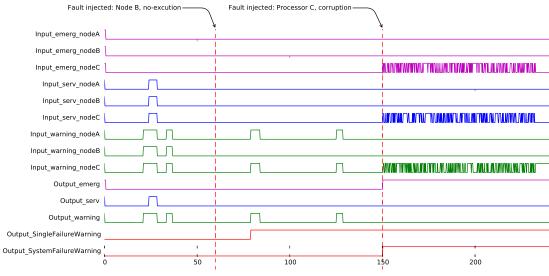

| 7.13 | Results of simulations with different fault campaigns 144                    |

## **List of Tables**

| 5.1 | Fault library for platform independent models                               | 112 |

|-----|-----------------------------------------------------------------------------|-----|

| 5.2 | Fault library for PSM models                                                | 114 |

| 7.1 | Fault injection campaigns for PIM model                                     | 133 |

| 7.2 | Fault injection campaigns for PSM model                                     | 142 |

| 7.3 | Temporal properties of failure detection in fault injection campaigns (PSM) | 142 |

## **List of Listings**

| 81  |

|-----|

| 98  |

| 101 |

| 105 |

| 115 |

| 130 |

| 138 |

| •   |

## CHAPTER

## Introduction

#### **1.1 Motivation**

An embedded system is a system that uses processors and special hardware for dedicated control functions, and interacts with a real-life environment [TLMP93, ZN08]. The capability of the semiconductor industry to reduce the size of integrated components has lead to a big increase in the number of components integrated in a specific silicon area, and follows the well-known Moore's law [Moo65]. This has enabled an augmentation in the functionality of embedded systems but has also prompted a considerable growth in their complexity.

Safety-critical embedded systems are dependable systems that could lead to loss of life, significant property damages or damages to the environment in case of failure. Therefore, safety-critical systems must satisfy a certain degree of fault-tolerance, as required by the safety standards. These systems have also suffered a complexity increase in the last years due to the new functionalities included in modern embedded systems. For example, high-end cars had about 70 electronic control units (ECUs) back in 2006 [Bro06], and this number raised up to 100 in the year 2011 [BCR<sup>+</sup>11]. This implies not only an increment on the cost and complexity of the systems, but also a growth of the amount of potential defects [EJ09]. Moreover, as Di Natale et al. point out in [DNSV10], it is expected that factors like the interdependency of functions and the cost of each ECU will lead to a transition from traditional federated architectures to integrated architectures where one ECU supports multiple functions, which may cause a growth in the complexity of ECUs.

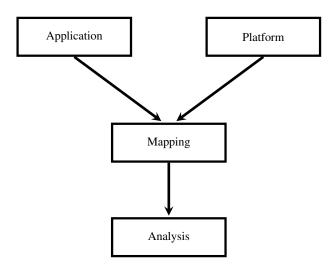

Therefore, tackling the complexity challenge [Kop08] while providing a consistent notion of time and preserving properties through the development process [HS07, JTM07] is a key challenge in the field [Per11]. In this context, the well known Y-chart development process [BCG<sup>+</sup>97, KDVvdW97] specifies the platform model and

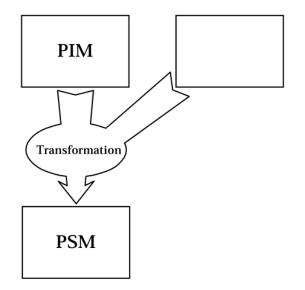

the functional model of the system separately, and combines both by means of a mapping model to obtain a model of a complete system. Moreover, Model Driven Development (MDD) approaches, such as the Model Driven Architecture (MDA) [MM03], are also based on the idea of a strict separation of behavioral and platform models. More specifically, MDA proposes the development of a Platform Specific Model (PSM) by applying transformations to a Platform Independent Model (PIM).

Since failures in safety-critical systems may cause human, environmental and economical damages, the dependability assessment plays a crucial role in their development. The correctness of system functions is usually addressed by formal reasoning. For example, relying on a formally specified Model of Computation (MoC), such as the time-triggered architecture (TTA), the synchronous reactive MoC (SR), or the logical execution time MoC (LET), enables reasoning about the temporal behavior of functional systems. However, when an exhaustive proof of correctness cannot be achieved, the modeling language should support simulation and testing [DNSV10].

Nowadays, it is estimated that verification and validation activities take approximately 50% of the total development effort of an embedded system [Enc03, Kop11]. For safety-critical systems, this percentage is even higher [Kop11]. Besides, the cost of finding and fixing defects increases exponentially as the development process progresses. In the worst case, [DES01] calculates that calling back a car that suffers from a safety-critical failure can imply a higher cost than the cost of its detailed testing activities. Therefore, advances on frameworks and methodologies for simulation and testing of system models at the early stages of development may provide a positive impact on the development of safety-critical embedded systems. In fact, a recent survey about embedded system design projects [Ham14] confirms that 63% of the embedded system developments.

The complexity of modern safety-critical systems, the high integration in silicon components and the limitations of software and hardware technologies force safety-critical systems to coexist with faults. This problem is addressed by the introduction of fault-tolerance mechanisms (FTMs) into the systems, as safety-standards recommend [IEC10, ISO09, CEN11]. In order to assess their effectiveness and so to evaluate the dependability of the system, fault-tolerance mechanisms need to be exercised by means of fault injection techniques.

Among the different fault injection approaches [BP03, HTI97], simulated fault-injection (SFI) enables performing this fault-tolerance assessment from the early stages of the design, therefore reducing the risk of a late and expensive detection of safety pitfalls. However, time-triggered modeling approaches and frameworks such as the Executable Time-Triggered Model (E-TTM) [PNOES10a, Per11] or Timing Definition Language (TDL) [Chr14] do not natively offer a framework for dependability assessment by simulated fault injection. Therefore, fault injection is usually carried out by manually modifying the system to insert the desired fault injection mechanisms in it [PAaP10]. This presents two important drawbacks. First, a new model needs to be created and compiled for each fault to be tested, which increases validation and verification costs. Second, since a new model is created and validated for each faulty case, in the end, the original model is never validated against faults, but only derived models are. This leaves a degree of uncertainty on the behavior of the original model against faults, since the designers might involuntarily change some functional property when creating the modified model.

Given this situation, this dissertation presents the Platform Specific Time-Triggered Model (PS-TTM), a novel modeling and simulation framework for the design and assessment of safety-critical time-triggered systems according to the MDA and the Y-chart development process. As suggested by these approaches, the design of systems in PS-TTM begins with the description of a purely functional model of the system. To do so, the herein presented framework includes the Platform Independent Time-Triggered Model (PI-TTM), a design and simulation environment for functional models based on the LET MoC. The PI-TTM has been built on top of the PS-TTM framework, in a way that it provides a seamless connection between platform independent and platform specific models.

Our simulation engine for PI-TTM and PS-TTM models enables the validation of fault-tolerance mechanisms by non-intrusive simulated fault injection from the early stages of the design, with a mechanism that prevents the designers from generating a new model for each fault to be injected, thus reducing the time and effort of validation activities and increasing the level of confidence on the results obtained in the tests. The fault injection campaigns can be applied to models at different abstraction levels, and are carried out by the time-triggered testing and fault injection framework included in this work, called the PS-TTM Automatic Test Executor (ATE).

Although different models of computation, languages and frameworks can be found in the state of the art for the development of safety-critical embedded systems (see chapters 2 and 3), the systematic preservation of time properties throughout the model down to the implementation is still a challenge. In this context, the Time-Triggered Architecture (TTA) provides a validated and certifiable core technology for the development of safety-critical embedded systems [JSPP04], based on the time-triggered MoC. To take advantage of this, the PS-TTM approach relies on the Executable Time-Triggered Model (E-TTM) [PNOES10a].

#### Why E-TTM?

The time-triggered MoC guarantees that time properties and constraints are intrinsically preserved down to the final implementation when the system is based on the TTA [Per11], what makes it an appropriate candidate for the design of safety-critical systems. Unlike other time-triggered modeling approaches, such as TDL [Chr14] or TMO [Kim97], which present some differences to the time-triggered MoC that limit their applicability [Per11], E-TTM provides a closer approximation to the time-triggered MoC.

Moreover, the E-TTM meta-model is developed in SystemC, which has become the de-facto standard for HW/SW system modeling. In addition to this, E-TTM provides different techniques such as abstraction, partitioning and segmentation to tackle the complexity challenge of modern embedded systems.

However, the E-TTM may be found too specific for the modeling of purely functional models of systems. For example, it requires the specification of a detailed timetriggered schedule, which may not be interesting at the earliest development stages. In that case, languages based on the synchronous reactive MoC (e.g., Lustre [HCRP91], Esterel [Ber98]) or on logical execution time (TDL [Chr14], HTL [GSVK<sup>+</sup>06]) give a higher abstraction to the designer, which makes them more suitable for the development of PIMs.

Hence, this approach relies on the LET MoC for the development of platform independent models, whilst platform specific models are developed relying on E-TTM.

#### Why LET?

Synchronous languages [BCE<sup>+</sup>03], such as Lustre [HCRP91, Hal05], Esterel [Ber98, Ber00] or the commercial tool SCADE Suite [wwww], are based on the SR MoC. The SR MoC relies on the synchronous hypothesis, which defines an abstraction where the execution of jobs and communication of data are considered instantaneous and simultaneously triggered. This way the notion of time is abstracted from the models so that the models can be understood as mathematical equations, which eases the formal verification of their properties. For this reason, synchronous languages are used for the design of functional models of dependable and safety-critical embedded systems.

However, the implementation of SR models requires matching the synchrony paradigm with the system architectures and the environment, which may be invalidated by the dynamics of the environment. Moreover, the deployment of SR models on distributed platforms that do not provide strict time determinism, or the implementation of interfaces for analog components (sensors or actuators) becomes cumbersome, in spite of the advances in research [DNSV10].

Therefore, in order to ease the design of platform independent models, PI-TTM relies on the LET MoC [KS12]. In the LET MoC, described in detail in section 2.5, the execution of functions takes a fixed logical duration regardless of their physical duration, whereas communication between components is instantaneous and is only triggered at the logical start and end points of jobs. This way, the LET MoC can be considered an abstraction of the Time-Triggered MoC.

The LET MoC has been adopted by a number of different approaches and languages, such as the Timing Definition Language (TDL) [RDPN10] and the Hierarchical Timing Language (HTL) [GSVK<sup>+</sup>06]. However, in order to ease the transition from the PIM

to the PSM, this thesis presents a new LET engine built as an abstraction of the E-TTM engine, which enables modeling LET based functional systems in SystemC. This way, the approach described in this dissertation provides a seamless connection between the LET based and E-TTM based models.

#### **1.2** Goals of the thesis

The main goal of this thesis is the "definition of an executable time-triggered safetycritical systems-modeling approach based on the Y-chart development process and the MDA, and the development of a testing framework which enables non-intrusive simulated fault injection at the different stages of the development for the verification and validation of such systems".

In order to tackle the challenges identified in the previous section, the modeling and simulation approach should meet the following characteristics:

- **G1. Time and value domain determinism**: Safety-critical systems must enable certification in accordance to applicable safety standards. Determinism eases the certification process by reducing the state space of systems.

- **G2.** Support strategies to tackle the complexity challenge: As described in section 1.1, complexity is one of the biggest concerns in the embedded systems field. Hence, the modeling approach must tackle this challenge by enabling different techniques identified in the state of the art, such as abstraction, partitioning and segmentation.

- **G3.** Be compliant with the MDA approach: MDA suggests separating the specification of the functionality of the system from the details of the target platform in order to reduce complexity and increase portability and re-usability. The approach developed within this thesis should comply with the MDA.

- **G4.** Allow extendability and specialization of platform components: As technology advances, new platforms and devices are developed. In order to support new components, the platform component library must be extendable. Moreover, platform component definitions must be generic and allow specialization to enable modeling at different abstraction levels.

On the other hand, the testing and simulated-fault injection framework should:

**G5.** Be compliant with the modeling and simulation approach: The main purpose of the testing and simulated fault injection framework is to enable the verification and validation of systems developed following our approach. Hence, the testing and simulated fault injection framework should avoid any incompatibilities

with the modeling framework, and thus provide a suitable environment to test the models developed following the modeling approach presented in this thesis against different test-cases and fault-configurations.

- **G6.** Enable non-intrusive fault injection: Non-intrusive fault injection techniques are the ones that completely mask their presence, so that they have no effect on the system behavior apart from the faults they inject. Since the model is not modified at all to get the faults injected, the results provided by these techniques are more reliable than the results provided by intrusive mechanisms. Therefore, this framework must enable non-intrusive fault injection.

- **G7.** Permit testing and simulated fault injection at all the stages of the development process (PIM and PSM models): As mentioned in section 1.1, fixing design pitfalls detected in the latest steps of the development requires a bigger effort. Hence, in order to enable the early detection of design flaws, testing and fault injection must be possible from the earliest stages of the design.

- **G8.** Provide repeatability of test cases and fault injection activities: In order to confirm that a bug in the system has been successfully fixed, it is important to repeat the tests or SFI activities that exhibited the faulty behavior of the system. To that end, test cases and SFI must be repeatable. The value- and time-domain determinism and timing synchronization between the model and the testing framework are key properties for this purpose.

- **G9. Provide a high level of observability**: The degree of observability of the internal signals of a system is a key property for the correct comprehension of its behavior, and certainly affects the time needed to locate and fix design bugs. Therefore, it would be highly advantageous to provide a high level of observability in order to reduce the verification and validation costs.

#### **1.3** Contribution

More specifically, the contributions provided by this thesis to the state of the art are the following:

• **Definition of the PS-TTM**, a modeling and simulation framework for time-triggered safety-critical embedded systems based on the Y-chart development process and the MDA approach (goal G3), over SystemC. The PS-TTM is time and value domain deterministic (goal G1), and supports different techniques to reduce the cognitive complexity of systems (goal G2). Taking advantage of its abstraction capabilities, the PS-TTM includes a library of generic platform components, which can be further specialized by the designers (goal G4).

- Creation of the PI-TTM library, an extension to SystemC to support the definition and simulation of Logical Execution Time based functional systems. This library enables developers to design the functionality of their systems in a separate model, thus reducing the complexity, as suggested by the MDA (goal G3).

- **Definition of the PS-TTM ATE**, a testing and simulated fault injection framework for PS-TTM and PI-TTM models (goals G5, G7), which enables non-intrusive fault injection on all the stages of the system development process without the need to make any modification to the system models (goal G6). The PS-TTM ATE is synchronized with the simulation engines of the PS-TTM, thus guaranteeing repeatability of test cases (goal G8), and provides mechanisms to observe the values of all the internal signals of the systems (goal G9).

- Provision of a seamless connection between the LET and E-TTM computation engines, which enables the simulation, testing and fault injection for systems containing components at different stages of development. This feature contributes to increase the re-usability of models, as suggested by the MDA (goal G3).

- **Development of an extendable executable fault library**, with faults collected from the state of the art, in order to verify and validate the behavior of systems under fault conditions. Providing this pre-defined fault library to test engineers reduces the verification and validation costs and increases the repeatability of fault injection activities (goals G7, G8).

#### **1.4** Structure of the thesis

This thesis is structured as described below:

- Chapter 2: This chapter gives an overview of the background and the basic concepts on which the work of this thesis is based. In particular, it focuses on explaining concepts regarding dependability and complexity, provides an overview of fault injection techniques, makes a review of model-based design (MBD) and gives an overview of different models of computation, mainly focusing on the time-triggered architecture.

- Chapter 3: This chapter analyzes the state of the art in modeling languages for safety-critical embedded systems and their simulation frameworks, and discusses different approaches in simulated fault injection on different modeling languages.

- Chapter 4: We describe in detail the PS-TTM, analyzing its meta-model, timingbehavior, syntax and semantics, and its PI-TTM abstraction level for functional

models. We also explain how PS-TTM is mapped to the MDA, and we analyze its capability to simulate mixed-abstraction level systems.

- **Chapter 5:** The testing and simulated fault injection framework is introduced in this chapter, describing its sub-components, fault libraries for PI-TTM and PS-TTM, syntax and time synchronization.

- **Chapter 6:** This chapter introduces the set of different tools developed during the completion of this thesis and describes their integration in the overall work-flow proposed in Chapter 4.

- Chapter 7: This chapter describes the case study made for the evaluation of the approach and discusses the results obtained in the simulations.

- Chapter 8: The thesis is concluded by summing up the main conclusions and suggesting possible future work.

# CHAPTER 2

## **Background and Basic Concepts**

This chapter analyzes the background on which this thesis is based, and explains the most fundamental concepts in the fields of dependable embedded systems and the Model Based Design (MBD).

#### 2.1 Dependability

The term dependability is widely used in the domain of embedded systems. However, the definition of the term has evolved through the years, as the following list shows:

- "Quality of the delivered service such that reliance can justifiably be placed on this service". [Lap85]

- "The property of a computer system such that reliance can justifiably be placed on the service it delivers" [LAK92]

- "The ability to deliver service that can justifiably be trusted" [ALR01, JTM07]

- "The ability of a system to avoid service failures that are more frequent and more severe than is acceptable" [ALRL04]

The paper written by Avizienis et al. [ALRL04] is usually taken by the embedded systems community as the reference for the definition of fundamental concepts regarding dependable and secure systems. Therefore, according to [ALRL04], dependability is considered an integrating concept that encompasses the following attributes:

- Availability: Readiness for correct service.

- Reliability: Continuity of correct service.

Figure 2.1: Causality chain of dependability threats (from [ALRL04]).

- **Safety**: Absence of catastrophic consequences for the user(s) and the environment.

- Integrity: Absence of improper system alterations.

- Maintainability: Ability to undergo modifications and reparations.

#### Threats of Dependability

According to Avizienis [ALRL04], the dependability of a system has three potential threats: failures, errors and faults. Benso et al. define these three components in [BP03] as follows:

- Fault: Physical defect, imperfection or flaw that occurs within some hardware or software component.

- Error: Deviation from accuracy or correctness.

- Failure: The non-performance or incorrect performance of some expected action.

Errors are considered manifestations of faults. Therefore, faults are classified as *active faults* or *dormant faults*, depending on their effect. A fault is active when it produces an error; otherwise, it is dormant. An active fault is either an internal fault (fault originated inside the system boundaries) that was previously dormant and that has been activated by the computation process or environmental conditions, or an external fault. Most internal faults keep switching between active and dormant states.

Errors caused by active faults may propagate inside the component due to the computation process, transforming themselves into other errors. This phenomenon is called *internal propagation*. When an error propagates internally to the service interface of the component, the error propagates to other systems connected to that interface. This is known as *external propagation*.

Failures occur when an error internally propagates to the service interface and causes a deviation of the provided service from the expected service. In that case, the failure in a system behaves as a fault for the subsequent systems.

This relationship between faults, errors and failures is known as the causality chain of dependability threats, which is depicted in Figure 2.1.

#### **Means of Dependability**

Over the years the community has developed different means to achieve each of the attributes of dependability. Those means are grouped into four major categories [ALRL04]:

- Fault prevention: Prevention of the occurrence or introduction of faults.

- Fault removal: Reduction of the number and severity of faults.

- **Fault forecasting**: Estimation of the present number, the future incidence, and the likely consequences of faults.

- Fault-tolerance: Avoidance of service failures in the presence of faults.

#### Determinism

Determinism has been widely explored by philosophers over the years. From a philosophical point of view, the world is deterministic if and only if, given a specified way things are at time t, the way things go thereafter is fixed as a matter of natural law [Hoe05].

In the field of computer science, a model is considered deterministic if and only if given a set of initial conditions at a specific instant, and a sequence of future timed inputs, the outputs at any future instant are entailed and are not influenced by randomness [Kop08].

Therefore, deterministic models enable to make reliable predictions about their future state. In fact, determinism is a sufficient condition for logical reasoning. This eases the analysis of the behavior of systems, and hence facilitates their validation. In contrast, non-deterministic models are more difficult to validate, since repeated test cases do not necessarily produce identical results. Thus, whenever possible, dependable and safety-critical systems should be built as devices that can be modeled deterministically.

#### **Reliability and Safety Analysis**

Different techniques have been developed to evaluate the dependability of systems. Since one of the most important characteristics of dependable systems is their dynamic behavior, nowadays the most interesting techniques for dependability analysis focus on the assessment of reliability and safety [BKSZN10].

The objective of this analysis is to qualitatively identify the types of system failures that can occur, or to quantitatively define the distribution of the times-to-failure of a component or system [BKSZN10]. The following sections briefly describe the most widely used reliability and safety analysis techniques.

#### Failure Mode and Effect Analysis (FMEA)

The design of safety-critical systems starts with the safety analysis such as fault tree analysis and/or failure mode and effect analysis (FMEA) of the envisioned application [Kop11]. In fact, the IEC 61508 safety standard (Functional safety of electrical/electronic/programmable electronic safety-related systems) [IEC10] recommends the FMEA as one way to assess the system reliability.

The FMEA (Failure Mode and Effect Analysis) is a systematic method of identifying and preventing product and process problems before they occur. FMEAs are focused on preventing defects, enhancing safety, and increasing customer satisfaction [MMB09]. The aim of the FMEA is to identify potential faults of the system and determine the resulting error effects before the faults occur, in order to prevent safety accidents and incidents.

The typical FMEA consists of the development of a document that follows a bottomup flow in the analysis of the system. The technique starts with the analysis of possible failure modes of components within the system, and continues upwards until the failure modes of the whole system are evaluated. The evaluation of the safety hazards is subjective, since it is based on the previous knowledge of the designers [RPV<sup>+</sup>13]. Therefore, the FMEA requires a team of experienced engineers to identify all possible failure modes of each component.

The FMEA process finishes with the development of the FMEA document, which is written in a specific FMEA worksheet. This document collects all the important information found during the FMEA process. Figure 2.2 shows a standardized empty FMEA worksheet.

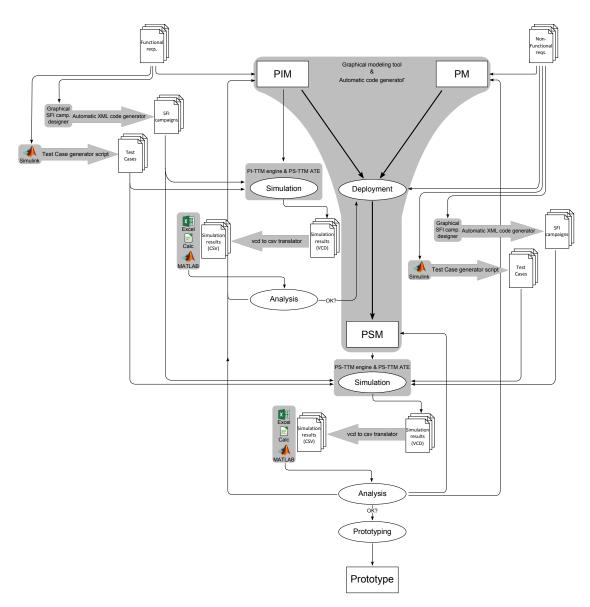

#### Fault Tree Analysis (FTA)

Besides the FMEA, the first stages of the development of safety-critical systems also requires the design of their Fault Tree Analysis (FTA). The FTA is a quantitative reliability analysis developed from a static view of the system. Similarly to the FMEA, the international IEC 61508 safety standard [IEC10] also recommends performing the FTA of the systems at the first stages of the design.

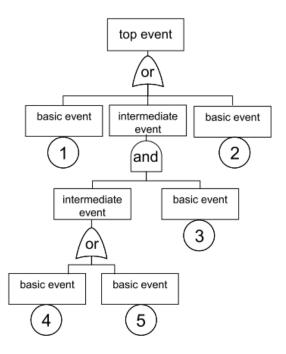

A fault tree is a diagram that displays the interrelationships between a potential critical event in a system and the causes for this event. The approach uses boolean logic to develop comprehensible diagrams, where causes and effects are linked by boolean logic (*and* and *or* gates). The FTA follows a top-down approach. The analysis begins at the system level, where an unwanted failure event is defined as the top event of the fault tree. Then, the subsystem failure events that can lead to that top event have to be identified and defined as sons of the top event. The process continues down the tree until a basic failure (usually a component failure) is found. Figure 2.3 shows an example of a fault tree.

| Г                                           |                     |                                                    |              |                | RPN                                                |   |   |   |   |   |   |   |   |

|---------------------------------------------|---------------------|----------------------------------------------------|--------------|----------------|----------------------------------------------------|---|---|---|---|---|---|---|---|

|                                             |                     |                                                    |              |                | Detection                                          |   |   |   |   |   |   |   |   |

|                                             |                     |                                                    |              | sults          | Occurrence                                         |   |   |   |   |   |   |   |   |

|                                             |                     |                                                    |              | Action Results | Severity                                           |   |   |   |   |   |   |   |   |

|                                             | FMEA Number:        | FMEA Number:<br>FMEA Date: (Original)<br>(Revised) |              | Actio          | Action Taken                                       |   |   |   |   |   |   |   |   |

|                                             | Ľ                   |                                                    | (Revised)    | (Revised)      | Responsibility<br>and Target<br>Completion<br>Date |   |   |   |   |   |   |   |   |

|                                             |                     | FMEA                                               |              |                | Recommended<br>Action                              |   |   |   |   |   |   |   |   |

|                                             |                     |                                                    |              |                | RPN                                                |   |   |   |   |   |   |   |   |

| shee                                        |                     |                                                    |              |                | Detection                                          |   |   |   |   |   |   |   |   |

| ts Analvsis Work                            |                     |                                                    |              |                | Current<br>Controls,<br>Detection                  |   |   |   |   |   |   |   |   |

| Failure Mode and Effects Analysis Worksheet |                     |                                                    |              | FMEA Process   | Current<br>Controls,<br>Prevention                 |   |   |   |   |   |   |   |   |

| ailure                                      | 5                   |                                                    |              | 1EA P          | Occurrence                                         |   |   |   |   |   |   |   |   |

| Ë                                           | :                   |                                                    |              | FN             | Potential<br>Cause(s) of<br>Failure                |   |   |   |   |   |   |   |   |

|                                             |                     |                                                    |              |                | Severity                                           |   |   |   |   |   |   |   |   |

|                                             |                     |                                                    |              |                | Potential<br>Effect(s) of<br>Failure               |   |   |   |   |   |   |   |   |

|                                             | Process or Product: | FMEA Team:                                         | Team Leader: |                | Potential<br>Failure Mode                          |   |   |   |   |   |   |   |   |

|                                             | Proc                |                                                    |              |                | Component<br>and Function                          |   |   |   |   |   |   |   |   |

| L                                           |                     |                                                    |              | -              | Line                                               | 1 | 2 | 3 | 4 | 5 | з | 4 | 5 |

|                                             |                     |                                                    |              |                |                                                    |   |   |   |   |   |   | - |   |

Figure 2.2: Standardized blank FMEA worksheet

13

Figure 2.3: A fault tree (from [BKSZN10])

The aim of the FTA is to reveal hidden failures caused by combinations of faults or errors, and quantitatively calculate their occurrence probability. Fault trees can be formally analyzed with mathematical techniques. This way, the probability of the top failure events can be calculated by applying combinatorial techniques to the probabilities of their basic component failures.

#### Testing

Testing is an analytic means for assessing the quality of systems [UL07], and is one of the most important phases of the development of embedded systems. As Dijkstra pointed out in [Dij70] "testing can be used to show the presence of bugs, but never to show their absence". Therefore, testing is an activity that aims to improve the quality and increase our confidence in a system by identifying defects in them. Testing cannot be undertaken in isolation. Instead, in order to be in any way successful and efficient, it must be embedded in an adequate system development process and have interfaces to the respective sub-processes.

However, although testing is not capable of proving the correctness of a system but only bring out its bugs, it is a widely used technique. Actually, according to [JTM07], "testing is indispensable, and no software system can be regarded as dependable if it has not been extensively tested". This happens, according to Hoare [Hoa96], due to the fact that the contribution of testing is not limited to expose bugs; In fact, its biggest contribution is the feedback that it provides to the development process. In his words, "the real value of tests is not that they detect bugs in the code but that they detect inadequacies in the methods, concentration, and skills of those who design and produce the code." In practice, this means that when a subsystem fails too many tests, the developers do not simply attempt to patch the code. Instead, they look at the development process to determine where the error that eventually resulted in the failure was introduced, and they make the correction there. This might involve clarifying requirements, reworking a design, recoding one or more modules, and in extreme cases, abandoning the entire development and starting a new one from scratch.

A thorough test process is carried out in five different stages [BSI98, IST14, ZN08]:

- 1. Test planning: Includes the planning of resources and the laying down of a test strategy: defining the test methods and the coverage criteria to be achieved, the test completion criteria, structuring and prioritizing the tests, and selecting the tool support as well as configuration of the test environment.

- 2. Test specification: Is defining the corresponding test cases using the test methods defined by the test plan.

- 3. Execution of the test: Carrying out the test cases and test scenarios.

- 4. Recording the results: Test records serve to make the test execution understandable for people not directly involved (e.g., customer) and prove afterwards whether and how the planned test strategy was in actual fact executed.

- 5. Checking for completion and test closure: Consists of collecting the test data to consolidate experience, testware, facts, and numbers, and evaluate the test process and generate the necessary documentation.

#### Validation and Verification

Besides testing, validation and verification (V&V) are especially important in the domain of safety-critical systems due to their high dependability requirements (e.g., safety, reliability, security). Usually, these two terms are defined by two questions:

- Validation: Am I building the right system?

- Verification: Am I building the system right?

In other words, validation is concerned with checking whether the system meets the customer's actual needs, whereas verification is concerned with whether the system is well-engineered, error-free, consistent, etc. That is, verification helps to determine whether the software is of high quality, and validation ensures that the system is useful for the customer.

#### **Fault Hypothesis**

A Fault Containment Unit (FCR) is a collection of components that operates correctly regardless of any arbitrary logical or electrical fault outside the region [LH94]. Further, a fault in an FCR cannot propagate and cause a failure outside the FCR. Each FCR in a system must have independent power and clocking resources in order to properly define its boundaries, since shared hardware resources compromise the independence of FCRs.

Given that an embedded system may have more than one FCR, a fault in an FCR that causes a failure in that FCR becomes a fault for the system, due to the causality chain reviewed in section 2.1 (Fig. 2.1). Therefore, dependable systems must tolerate such faults. This fault-tolerance is achieved with the implementation of fault-tolerance mechanisms.

A typical fault-tolerance mechanism for dependable embedded systems is the Nmodular redundancy architecture. N-modular redundancy composes the system with N replicated components that perform the same function and provide the same service. A unique service result is obtained by a voting component, which takes a decision by reading the service outcome provided by all the replicated components and executing a predefined voting algorithm (e.g., majority voting). Triple Modular Redundancy (TMR) is a widely used N-modular redundancy type.

#### Fail-Safe and Fail-Operational Systems

Dependable, and more specifically, safety-critical systems, are typically subdivided into fail-safe and fail-operational systems. Most dependable systems enable to identify one or more safe states, which the systems should be able to reach in case of failure of one of its components. If such a state exists in a dependable system, the system is considered fail-safe. For example, if a failure is detected in a railway signaling system, it should be possible to notify all the drivers of the trains by lighting a red semaphore, which would make them brake and stop their trains, thus leading the system to a safe-state.

Other systems, however, do not have a safe state to which they can safely transit in case of failure. In these systems, at least an application of the computer that is controlling the system must remain operational and keep providing its service, even if it is in a degraded-mode service level. These systems, e.g., flight controls of aircrafts, are called fail-operational.

It must be noted that fail-safeness is not a property of the controlling computer system, but of the controlled system itself.

## 2.2 Fault Injection

Fault Injection is a widely accepted technique for the validation of the dependability of a system by observing its behavior in presence of faults. The technique consists of

performing experiments where artificial faults are deliberately introduced in the system and checking the resulting behavior. The occurrence of faults in the system life-cycle is accelerated by their deliberate introduction; as a consequence, the occurrence of errors and their propagation through the system are also accelerated and the response of the system against such faults can be evaluated.

As Hsueh [HTI97] pointed out, the usage of fault injection techniques enables developers to:

- identify dependability bottlenecks,

- study system behavior in the presence of faults,

- determine the coverage of error detection and recovery mechanisms, and

- evaluate the effectiveness of fault-tolerance mechanisms and performance loss in case of faults.

Faults are typically characterized in three different groups according to their duration [ZAV04]:

- Permanent faults: These types of faults are caused by irreversible damages in the hardware or software, so that they cannot be fixed unless the faulty component is replaced.

- Transient faults: These faults are caused by specific environmental conditions, and they rarely induce permanent damages to the affected components. Therefore, transient faults usually disappear when the conditions change. According to studies in the field, transient faults occur more often than permanent ones, and they are hardest to detect.

- Intermittent faults: These faults are the ones caused by unstable hardware or varying hardware states, and they behave as a sequence of transient faults. They are fixed by the replacement of the faulty component.

Although this characterization of faults in three groups according to their duration is the most common one, other approaches extend this with additional types, such as Kopetz in [Kop06]:

• Soft-permanent faults: The difference between permanent and soft-permanent faults is that permanent faults remain active until the affected HW component is replaced, whereas soft-permanent faults remain active until the state of the HW component is updated.

• Massive transient disturbances: These faults occur when an external event results in the correlated failure of two or more communication channels and possibly some node.

Fault injection techniques are divided into two main groups: execution-based and simulation-based [BP03]. Execution-based techniques consist of executing the system itself (or a prototype) and injecting faults in it during its execution. These techniques are oriented to evaluate the final design, but fixing an eventual design error in them is in general difficult, since the system is already in the latest stages of its development. On the contrary, simulation-based techniques introduce faults in models of systems instead of in the system itself. Simulation-based techniques take more time than execution-based ones, since the formers require to simulate the entire system. However, simulation-based techniques may be applied far earlier in the development process than execution-based methods, what facilitates fixing design errors detected during the fault injection activities.

Fault injection experiments are also typically classified as intrusive and non-intrusive. Intrusive techniques are those in which testing mechanisms leave some kind of footprint in the systems behavior, e.g., an alteration of its time properties. Non-intrusive techniques are the ones that completely mask their presence, so that they have no effect on the system behavior besides the faults they inject. In general, non-intrusive techniques provide more reliable results than intrusive ones, due to the fact that the formers do not affect to the behavior of the system (other than the injected faults). However, intrusive mechanisms are easier to implement than non-intrusive ones. In fact, in some cases non-intrusive techniques may be impossible to implement.

## **Basic Fault Injection Environment**

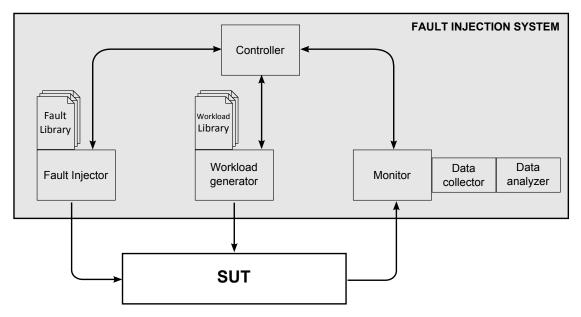

As Figure 2.4 shows, a representative fault injection environment is composed of 8 main components [HTI97, ZAV04]:

- Controller: Controls the experiment.

- Fault injector: Is responsible for injecting the desired faults into the system under test.

- Fault library: Provides a set of fault types to be injected in the system.

- Workload generator: Generates the workload in order to simulate the desired test case.

- Workload library: Contains a set of workloads to be used by the workload generator.

Figure 2.4: Representative Fault Injection Environment

- Monitor: Tracks the execution of simulation commands.

- Data collector: Collects the resulting data during the simulation.

- Data analyzer: Processes and analyzes the data: When the data analyzer works online, the controller might take into account the results provided by the analyzer in order to adapt the fault injection activities and the test cases according to the previously obtained results.

Fault injection techniques are generally divided into three sub-categories, depending on the design phase in which they are implemented: hardware-based fault injection (HWFI), software-based fault injection (SWFI) and simulation-based fault injection (SFI) [BP03].

## Hardware Based Fault Injection

The hardware based fault injection (HWFI) involves executing a system with specially designed test hardware that allows injecting faults into the system. HWFI is carried out in the latest stages of the product development, since it needs a functional prototype of the target hardware to be exposed to faults. The hardware prototype is tested by exposing it to physical disturbances, e.g., electromagnetic interferences, heavy ion radiation, pin forcing, which may lead to the destruction of the prototype.

The testing environment for HWFI requires additional hardware facilities to perform the fault injection and to store the resulting data. Hsueh [HTI97] identifies two different types of hardware fault injection depending on the hardware facilities used: Hardware based fault injection with contact and hardware based fault injection without contact.

#### Hardware based fault injection with contact

The fault injector has direct physical contact with the system under test and produces current or voltage changes in it. Since faults are directly managed by the fault injector, their duration and location is straightforwardly controllable. There are two main techniques to inject faults at pin level:

- Active probes: A flow of current is added to the selected pins via the probes attached to them. This technique is specially suited for stuck-at faults and bridges between two or more pins. This technique may cause damages in the target hardware if two non-compliant pins are bridged or an inappropriate amount of current is added to the pin.

- Socket insertion: This technique inserts a socket between the target hardware and its circuit board. The socket forces the analog signals that represent the desired logic values onto the pins of the target hardware, thus injecting the desired fault. Signals can be inverted, ANDed or ORed with adjacent pins, resulting in stuck-at, stuck-open or even more complex faults.

#### Hardware based fault injection without contact

In this type of hardware based fault injection, an external source exposes the target system to heavy-ion radiation, electromagnetic interference, anomalous thermal conditions or any other physical phenomenon that could cause internal spurious effects in the target hardware. Therefore, the fault injector has no physical contact with the system under test.

The main benefits of hardware based fault injection are listed in the following:

- Testing experiments provide precise and reliable results, since the methods are non-intrusive and no hardware abstraction is used.

- Test execution is fast (in general, faster than simulated fault injection).

- The system does not need to be modeled.

However, HWFI has several drawbacks:

- It may cause damages to the target platform.

- Accessibility to internal components is very limited.

- Additional hardware is required.

- Observability is very limited.

- Controlability of HWFI without contact is very low, since the precise location and occurrence instant of faults is not controlled by the fault injection tool.

- HWFI without contact is not repeatable, since there is not a precise control in the injection of faults.

- The fixing of bugs that are discovered in the latest stages of the development may be very expensive, since it may require a major re-design of the system.

#### **Software Based Fault Injection**

Software based fault injection (SWFI) is a technique that modifies or extends the software implemented in the system under test in order to provide the capability to modify its state while the system is operational. Since faults are directly applied in software, this type of fault injection does not require any additional hardware.

The SWFI technique only enables injecting faults in locations which are accessible by software. It enables introducing both hardware-related and software-related faults to the system, and a wide range of different faults can be applied to it, such as replication or loss of network messages, erroneous flags and error conditions, faults in memories, faults in registers and faults in the operating system. This type of fault injection is typically used in complex systems where interactions are understood through the details of implementation [BP03, PAaP10].

A prototype of the target hardware executes the software that has been modified / extended for SWFI. Since there are some differences between the original code and the modified one, the timing properties and the workload of the system can be affected, and in some cases this may result in behavioral differences when compared to the original software. For example, in case a faulty network channel is simulated by not sending any message through this channel, it may be the case that 'send' commands execute in shorter time than they used to take in the original software. This modification of its timing properties may have some collateral influence on the overall behavior of the system. Therefore, this technique is considered intrusive.

According to [HTI97], SWFI is classified in two groups, depending on the moment when faults are injected.

#### **Compile-time injection**

This method injects errors by modifying the source code or assembly code before the program is loaded and executed on the target platform. This way, an erroneous software image is loaded into the platform and the effect of hardware or software faults is

emulated when the image is executed. This technique is very well suited to emulate permanent faults, but it does not allow to trigger faults during program runtime.

#### **Runtime injection**

Additional commands are included in the target software which allow triggering different types of faults during runtime. The most common triggering mechanisms are:

- Time-out: A timer with a predefined time is placed in the code, which generates an interrupt when it expires. This interruption is used as a trigger that invokes a fault. The trigger can be both hardware or software based. The effect of the fault is in principle unpredictable, since the trigger is based on time instead of on the internal state of the program. This method is suitable to inject transient and intermittent faults.

- Exception/trap: The fault is triggered by a hardware or software exception. This method is well suited to trigger faults depending on the occurrence of a certain event, such as the entrance of the program into a certain state (software exception) or when a particular memory location is accessed (hardware exception).

- Code insertion: Instructions are added to the target software allowing fault injection to take place before particular instructions occur. This method is similar to compile-time injection, but faults are injected during runtime.

The main advantages of SWFI are:

- A wide range of faults can be injected, both hardware-related and software-related.

- No additional hardware is required. Implementation cost is low.

- Experiments are fast, almost real-time.

- Experiments are repeatable (except for the case of time-out SWFI).

- The system does not need to be modeled.

However, this technique also has the following disadvantages:

- The software running on the target hardware is not the final software, and this difference may influence the timing behavior of the system.

- Observability is limited, since many times there is no access to internal variables.

- Faults can only be injected in locations that are accessible by software.

- The time needed to implement each experiment may be long, since it may require re-writing and re-compiling code.

## Simulated Fault Injection

The simulated fault injection (SFI) technique (also known as simulation-based fault injection) consists of developing a model of the system under test at different abstraction levels, and inserting faults into the model instead of inserting them to the system itself. Since no hardware prototype is needed, this technique can be applied at early stages of the system development, which becomes a major benefit for designers since it reduces the risk of a late discovery of design flaws.

Three different methods are used by the community to inject faults in simulated models [BP03, GBGG01, MVS07]:

- **Simulator commands**: Uses commands provided by the simulator to modify the values of signals and variables at simulation time. The main advantage of this technique is that it does not require modification of the code. However, the usage of this technique depends on the functionalities offered by the simulator. The simulator commands work temporally, i.e., succeeding actions in the model may overwrite the variables. Therefore, fault injection by simulator commands is a good technique for simulating transient faults, but permanent fault injections are not covered [MVS07].

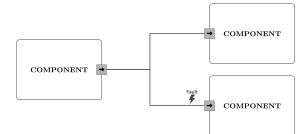

- **Saboteurs**: A saboteur is an additional component that is added to the system, which is capable of modifying the value or timing characteristics of signals or variables. The injection of the fault is managed by a control signal, which determines both the trigger instant and the duration of the fault. The main disadvantage of this technique is that the number of control signals grows as the quantity of saboteurs added to model grows, and this adds additional complexity to the model.

- **Mutants**: A mutant is a component that replaces another component of the system. When the mutant is active it behaves like the component in presence of faults, and when it is not activated it behaves like the original component. An additional control signal is used to trigger mutants. The main disadvantage of mutants is that, like for saboteurs, the number of control signals may be high if several different mutants need to be placed in the model. Moreover, the need to save the internal state of the system before commuting a mutant from non-active to active state may lead to high cost in space ant time.

Simulated fault injection can be applied to models at different levels of abstraction. The accuracy of the simulation and the detail of the faults to inject directly depends on the abstraction level of the model.

The following list summarizes the main advantages of simulated fault injection:

- SFI can be applied to models at different levels of abstraction (more or less detailed models).

- There is no risk to cause damage in the system, since no prototype is used.