#### **DIPLOMARBEIT**

# Safety-Betrachtungen unter Verwendung kommerzieller Hardware

eingereicht bei der Fakultät für Elektrotechnik der Technischen Universität Wien, ausgeführt zur Erlangung des akademischen Grades eines Diplom-Ingenieurs unter der Leitung von

O.Univ.Prof. Dipl.-Ing. Dr.techn. Dietmar Dietrich Univ.Ass. Dipl.-Ing.(FH) Dr.techn. Heimo Zeilinger

am

Institut für Computertechnik (E384)

durch

Bernd Thiemann, BSc. Matr.Nr. 0627763 Müllnergasse 31/14, 1090 Wien

#### Kurzfassung

Die Arbeit beschäftigt sich mit neuen Lösungen von Sicherheitssystemen für industrielle Anwendungen. Durch die immer umfangreicher werdende Automatisierung von industriellen Prozessen werden Regelungsaufgaben durch Mikrocontroller oder Industrie-PCs ersetzt. Es gilt zu garantieren, dass der PC durch eine Fehlfunktion keine Gefährdung für anwesende Menschen oder Material darstellt. Aktuell am Markt befindliche Sicherungssysteme garantieren diese Fehlerbeherrschung durch speziell entwickelte Software und Hardware. Die Hardware muss auf Fehlerfreiheit, bzw. Verhalten bei einem Fehler analysiert werden. Bei State of the Art CPUs ist dies aufgrund der Komplexität nicht mehr möglich. Der hier verfolge Ansatz beruht auf der Idee, die Software dahingehend zu erweitern, dass Hardwarefehler zuverlässig erkannt werden können. Durch die Fehleraufdeckung in Software soll zusätzlich eine größtmögliche Hardwareunabhängigkeit erreicht werden. Das geplante Konzept sieht Informationsredundanz vor. In der Software werden während der Ausführung statische Informationen mit den dynamischen des zu regelnden Prozesses kombiniert. Dieses Konstrukt zur Fehleraufdeckung in Software wird "Coded Processing" genannt und wird im Eisenbahnbereich und in der industriellen Automatisierung erst spärlich eingesetzt. Eine Evaluierung wird durchgeführt, um zu prüfen, ob eine hardwareunabhängige Lösung anhand von Coded Processing möglich ist und diese den Standards für funktionelle Sicherheit genügt. Die theoretische Untersuchung wird mittels Fehlermodellen durchgeführt. Für die praktische Analyse wird eine Codierung inklusive Beispielapplikationen implementiert und Fehler während der Ausführung injiziert, anhand derer die Fehleraufdeckungswahrscheinlichkeit bestimmt wird. Basierend auf diesen Daten wird eine Abschätzung getroffen werden, ob eine Zertifizierung nach Safety Integrity Level (SIL) 2/3 laut International Electrotechnical Commission (IEC) 61508 möglich ist.

#### **Abstract**

In this thesis new solutions for safety controllers for industrial applications will be analyzed. Due to the increasing use of automation in industrial processes microcontrollers will be replaced by industrial PCs. In this context it is important, that an error in the computer does not cause any risk to people or material nearby. The error behavior of state-of-the art safety controllers is guaranteed through specialized hardware and software. The hardware has to be analyzed in detail to evaluate the absence of errors respectively the erroneous behavior. With state-of-the art processors this is not possible any more. The complexity of the internal structures has become overwhelming. The approach in this thesis is based on the idea to extend the software with special routines, so hardware errors can be detected with a determined probability. Due to the error detection in software, hardware independence should be achieved. The intended design is based on information redundancy in which the dynamic data of the industrial process are combined with static, predetermined information. This concept is called "coded processing" and is sparely used in railway applications and industrial automation. In the end an evaluation is made, if a hardware independent safety controller including coded processing is possible. The theoretical analysis is done by different fault models. For the practical analysis an example application will be implemented, which uses coded processing. During the execution of this application typical hardware faults are be injected to observe the fault reaction. Based on this data an estimation is done, if a certification according to SIL 2/3 laut IEC 61508 would be possible.

# Inhaltsverzeichnis

| $\mathbf{A}$ | bkür | zungen                                                                            | IX |

|--------------|------|-----------------------------------------------------------------------------------|----|

| 1            | Ein  | leitung                                                                           | 1  |

| 2            | Tec  | hnologieanalyse                                                                   | 5  |

|              | 2.1  | Normen und Begriffe                                                               | 5  |

|              |      | 2.1.1 Begriffe und Definitionen                                                   | 5  |

|              |      | 2.1.2 IEC 61508 - Funktionale Sicherheit sicherheitsbezogener elektrischer/ elek- |    |

|              |      | tronischer/ programmierbarer elektronischer Systeme                               | 6  |

|              |      | 2.1.3 EN 13849 - Sicherheit von Maschinen, Sicherheitsbezogene Teile von Steue-   |    |

|              |      | rungen                                                                            | 8  |

|              |      | 2.1.4 Redundanz                                                                   | 9  |

|              |      | 2.1.5 Fehlerarten                                                                 | 12 |

|              |      | 2.1.6 Systemtests                                                                 | 13 |

|              |      | 2.1.7 Fehler realer Systeme                                                       | 14 |

|              |      | 2.1.8 Beispiel einer Sicherheitssteuerung                                         | 16 |

|              | 2.2  | Fehlermodelle                                                                     | 17 |

|              | 2.3  | Coded Processing                                                                  | 19 |

|              | 2.4  | Softwarekomponenten                                                               | 28 |

| 3            | Kor  | $\mathbf{nzept}$                                                                  | 31 |

|              | 3.1  | Basisannahmen für weitere Arbeit                                                  | 31 |

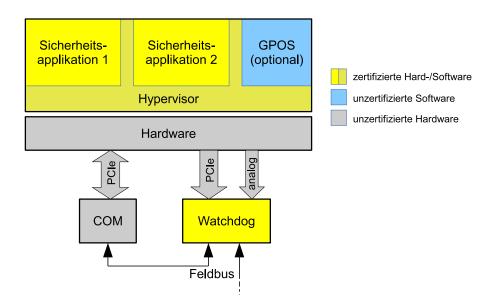

|              | 3.2  | Architektur                                                                       | 33 |

|              | 3.3  | Watchdog                                                                          | 35 |

|              | 3.4  | Codierung                                                                         | 38 |

| 4            | Kor  | nzeptanalyse                                                                      | 43 |

|              | 4.1  | Fehlermodelle auf Systemebene                                                     | 43 |

|              | 4.2  | Fehlermodel aus IEC 61508                                                         | 46 |

|              | 4.3  | Kontrollfluss                                                                     | 51 |

| 5            | Um   | setzung                                                                           | 53 |

|              | 5.1  | Testaufbau                                                                        | 53 |

|              | 5.2  | Mathematik Bibliothek                                                             | 54 |

|              | 5.3  | Fehleriniektionssoftware und Testsuite                                            | 56 |

|                  | 5.4   | Beispielanwendung                                           | 59         |

|------------------|-------|-------------------------------------------------------------|------------|

|                  | 5.5   | Parametersuche                                              | 61         |

| 6                | Eva   | lluierung                                                   | 63         |

|                  | 6.1   | Parameterwahl                                               | 63         |

|                  | 6.2   | Ausführungszeit                                             | 65         |

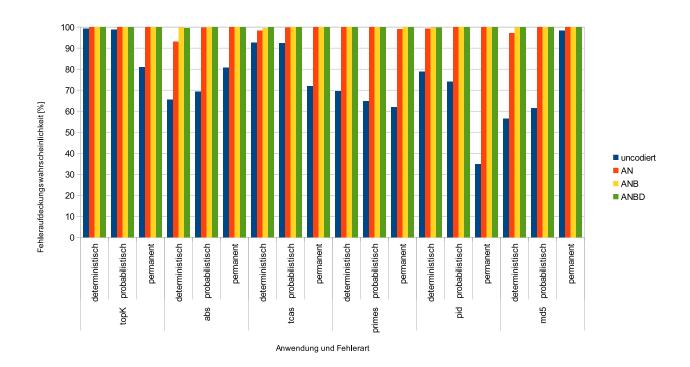

|                  | 6.3   | Fehleraufdeckung                                            | 66         |

|                  |       | 6.3.1 Matrizenmultiplikation                                | 67         |

|                  |       | 6.3.2 Sicherheitsapplikation                                | 70         |

|                  |       | 6.3.3 Fehlerinjektion in codierte und uncodierte Ausführung | 73         |

|                  |       | 6.3.4 Diskussion des Messverfahrens                         | 75         |

|                  | 6.4   | Abschätzung der Umsetzbarkeit                               | 76         |

| 7                | Cor   | nclusio                                                     | <b>7</b> 9 |

| $\mathbf{A}_{]}$ | ppen  | dix Glossar                                                 | 83         |

| W                | isser | nschaftliche Literatur                                      | 85         |

| In               | terne | et Referenzen                                               | 89         |

# Abkürzungen

ABS Antiblockiersystem.

**ADC** Analog-Digital Converter.

ALU Arithmetical Logical Unit.

**BB** Basic Blocks.

**CCF** Common Cause Failure.

**COTS** Commercial off-the-shelf.

**CPU** Central Processing Unit.

CRC Cyclic Redundancy Check.

**DC** Diagnostic Coverage.

**DMA** Direct Memory Access.

**DRAM** Dynamic Random Access Memory.

**ECC** Error Correcting Code.

**EN** Europäische Norm.

FIT Failure in Time.

**FMEA** Failure Mode and Effects Analysis.

**FPGA** Field Programmable Gate Array.

GCC GNU Compiler Collection.

**GPOS** General Purpose Operating System.

**HFT** Hardwarefehlertoleranz.

$I^2C$  Inter-Integrated Circuit.

**IEC** International Electrotechnical Commission.

**IP** Intellectual Property.

**LLVM** Low Level Virtual Machine.

MMU Memory Management Unit.

**PC** Personal Computer.

PCIe Peripheral Component Interconnect Express.

**PFH** Propability of Failure per Hour.

**PL** Performance Level.

**RAM** Random Access Memory.

**SDC** Silent Data Corruption.

SEU Single Event Upset.

**SFF** Safe Failure Fraction.

SIL Safety Integrity Level.

SIMD Single Instruction, Multiple Data.

SMBus System Management Bus.

**SPS** Speicher Programmierbare Steuerung.

**SRAM** Static Random-Access Memory.

SSE Streaming Single Instruction, Multiple Data (SIMD) Extensions.

TÜV Technischer Überwachungsverein.

TMR Triple Modular Redundancy.

## 1 Einleitung

Die Arbeit beschäftigt sich mit der Analyse neuer Ansätze zur Realisierung sicherheitstechnischer Systeme im Bereich der industriellen Automation. In den letzten Jahren ging der Trend bei Sicherheitssystemen für funktionale Sicherheit weg von der hart verdrahteten Not-Aus-Relais Technik hin zu Softwarelösungen. Diese sind deutlich einfacher bei der Installation und flexibler im Betrieb. Das Verhalten des Systems im Notfall wird durch ein sicherheitskritisches Programm festgelegt. Eine Umstrukturierung des Sicherheitskonzepts bedarf keiner Neuverkabelung mehr, sondern eines Software-Updates. Durch die verringerte Anpassungszeit und das feingranulare Reagieren auf Sicherheitsrisiken ist es möglich geworden industrielle Maschinen benutzerfreundlicher zu gestalten.

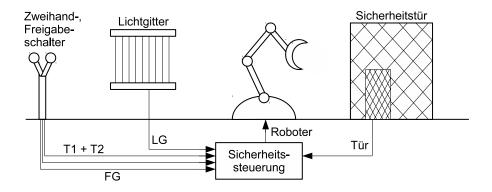

Die Aufgabe eines Sicherheitssystems ist es, einen industriellen Prozess, unabhängig von der Art der Gefahr, die davon ausgeht, zu sichern. Die Gefahr kann ein chemischer Prozess, wie zum Beispiel einen Kessel, der bei Überdruck bersten kann, oder eine bewegte, mechanische Einheit, wie einem Roboter, darstellen. Unabhängig von der Anwendung muss das Sicherheitssystem die Prozess- und Umgebungsparameter überwachen und im Falle einer Abweichung vom Normbetrieb einen sicheren Zustand anfahren. Um dies garantieren zu können, muss das Sicherheitssystem selbst sicher sein, um nicht durch eine Fehlfunktion eine Gefahr auszulösen oder eine drohende Gefahr zu übersehen.

Denkt man an industrielle Fertigungen, ist ein Arbeiten zwischen Mensch und Roboter Hand in Hand derzeit trotz der ausgeklügelter Sicherheitssysteme nicht möglich. Für den sicheren Betrieb von Robotern sind diese durch diverse Schutzmechanismen, wie Lichtgitter oder Käfige, von der Umgebung getrennt. Soll ein sicherer Betrieb gewährleistet sein, muss die Reaktionszeit der Sicherheitssysteme weiter gesenkt werden. Eine Möglichkeit wäre, Steuerung und Sicherheitssystem, welche bisher getrennt voneinander arbeiteten, zu verschmelzen. Da die Steuerung vor allem bei dynamischen Roboterbewegungen sehr rechenintensiv ist, muss diese auf rechenstarken Computersystemen durchgeführt werden. Bei Sicherungssystemen hingegen liegt der Schwerpunkt vermehrt auf Eigensicherheit als auf Performance, ein Fehler in Hardware oder Software darf idealerweise keinesfalls zu einem Sicherheitsrisiko führen. Dies wird erreicht, indem ältere, betriebsbewährte Hardware verwendet wird, welche durch penible Analyse auf weitgehende Fehlerfreiheit geprüft wird.

Die somit entstehenden Anforderungen an die Steuerung - hohe Performance - und an das Sicherheitssystem - nachweisbare Fehlerfreiheit - scheinen sich auf den ersten Blick auszuschließen.

In dieser Arbeit wird ein Konzept entwickelt, welches diesen, auf den ersten Blick unvereinbaren Ausschluss auflöst. Da eine Immigration des rechenintensiven Steuerungsprogramms nicht auf die vergleichsweise langsame, sichere Hardware verlagert werden kann, muss die umgekehrte Lösung in Betracht gezogen werden. Das Sicherheitsprogramm muss auf die rechenstarke Hardware portiert werden und trotzdem den gewünschten Sicherheitsstandards genügen. Dies stellt einen neuen Schritt in der Entwicklung sicherer Systeme dar, welcher nur durch eine neue Art von Sicherungsmethoden bewerkstelligt werden kann. Eine Umsetzung davon ist das sogenannte "Coded Processing". Obwohl das mathematische Prinzip dahinter seit den 1960iger Jahren bekannt ist, wurde es in diesem Umfeld und vor allem Umfang noch nie eingesetzt. Damit bestünde die Möglichkeit fehlererkennende Software zu schreiben, die unabhängig von der verwendeten Hardware arbeitet. Folglich muss es möglich sein, auch bei moderner, ungeprüfter Hardware eine Fehlererkennungsrate, welche gleich oder besser als die geprüfte Hardware ist, zu erreichen. Ist die Hardware von Sicherheits- und Steuerungsfunktion erst verschmolzen, kann auch die Software der beiden Aufgaben vereint werden. Gegenüber dem bisherigen System, bestehend aus einer aktiven Steuerung und einer davon unabhängigen Überwachungseinrichtung, kann die Reaktionszeit des Gesamtsystems verbessert werden. Zusätzlich muss nicht wie üblich im Fehlerfall ein Nothalt ausgeführt werden, sondern es kann eine gezielte fehler- bzw. risikomindernde Aktion ausgeführt werden.

Damit das System auch verwendet werden darf, muss es gewissen Normen für die funktionale Sicherheit erfüllen. Die wichtigste Norm in diesem Gebiet ist die IEC 61508 [IEC10a] und sie stellt die Basis für weitere Normen dar. In diesem Zusammenhang soll untersucht werden, welche Voraussetzungen ein Sicherheitssystem nach der Norm erfüllen muss und welches SIL erreicht werden kann.

Ziel dieser Arbeit ist das Entwickeln und Evaluieren eines Konzeptes, welches formal den Anforderungen von SIL 2/3 entspricht. Die Sicherheit soll rein von der Software abhängen, wodurch eine einfache Austauschbarkeit der Hardware erreicht wird. Als Hardware können aktuelle Commercial off-the-shelf (COTS) Komponenten angenommen werden, welche über hohe Rechenleistung und ausreichend Speicher verfügen. COTS Hardware besteht aus komplexen Elementen, welche zusätzlich noch Intellectual Property sind, wodurch die inneren Strukturen als nicht bekannt angenommen werden müssen. Systematische Fehler innerhalb der Hardware müssen als vorhanden, aber unbekannt behandelt werden. Die Softwarelösung muss diese und weitere Fehler erkennen und im Falle des Auftretens einen sicheren Zustand einnehmen. Für die Anwendbarkeit in industriellen Prozessen muss die Reaktionszeit beziehungsweise die Fehleraufdeckungszeit im Millisekundenbereich liegen.

Zur Evaluierung dieser Forderungen wird eine Mathematikbibliothek nach den Gestaltungsgrundsätzen des "Coded Processing" implementiert. Dem Anwender soll es möglich sein mit wenigen Anpassungen am Applikationsprogramm die Berechnung codiert durchzuführen. Anhand dieser Mathematikbibliothek werden Laufzeitvergleiche zwischen codierter und nativer Ausführung durchgeführt, um Fehleraufdeckungszeit im Millisekundenbereich nachzuweisen. Für die Überprüfung, ob die in den Normen gestellten Anforderungen erfüllt werden, wird eine quantitative und qualitative Analyse durchgeführt. Einerseits wird das entwickelte Konzept den Gestaltungsleitsätzen der Normen gegenübergestellt, andererseits soll eine Simulation inklusive Fehlerinjektion nachweisen, dass das Konzept den quantitativen Forderungen genügt.

Am Beginn der Arbeit steht eine steht eine Technologieanalyse. Diese beinhaltet einen Überblick über den Aufbau aktueller sicherheitstechnischer Komponenten und deren Argumentation um das nötige Sicherheitslevel zu erreichen. Des weiteren beinhaltet sie eine Beschreibung von Coded

Processing und deren Codierungsverfahren. Es werden die Eigenschaften verschiedener Codierungen untersucht und gegeneinander verglichen. Ebenso ist eine Recherche über die zu beachtenden Normen, mit Schwerpunkt auf der IEC 61508 [IEC10a], welche die Vorschriften für die Safety Integrity Levels enthält, durchzuführen. Zusätzlich muss die Normen EN 13849 [EN08] behandelt werden, da Konformität zu dieser Norm oft gefordert wird. Die Erkenntnisse dieses Arbeitsschritts sind in Kapitel 2 zusammengefasst. Darauffolgend wird anhand dieser Informationen ein Konzept erstellt, welches die Anforderungen nach SIL 2/3 bei größtmöglicher Hardwareunabhängigkeit erreichen soll. Eine ausführliche Beschreibung des erarbeiteten Konzepts ist in Kapitel 3 angeführt. Eine Analyse des Konzepts wird auf der Basis von Fehlermodellen aus der Wissenschaft und der IEC 61508 durchgeführt und wird in Kapitel 4 diskutiert. Für die praktische Untersuchung wird eine Mathematik-Bibliothek erstellt, welche die Berechnung von zwei Beispielapplikationen codiert durchführt. Während der Ausführung werden Fehler durch eine spezielle Software injiziert, wie sie typisch bei Computersystemen auftreten. Details zu der Bibliothek, der Applikationen und der Fehlerinjektion ist dem Kapitel 5 zu entnehmen. Die entstandenen Daten der codierten Berechnung und der Fehlerinjektion werden unter Berücksichtigung des entwickelten Konzepts betrachtet und somit eine Abschätzung der Umsetzbarkeit durchgeführt. Dies ist in Kapitel 6 nachzulesen.

### 2 Technologieanalyse

Dieses Kapitel gibt einen Überblick über die technischen Grundlagen von aktuellen Sicherheitssystemen. Bevor jedoch auf die technischen Details aktueller Sicherheitslösungen eingegangen wird, werden die in diesem Segment wichtigen Normen IEC 61508 [IEC10a] und Europäische Norme (EN) 13849 [EN08] diskutiert. In diesem Zusammenhang werden die wichtigsten Termini, welche für die weitere Arbeit wichtig sind, erläutert. Darauf folgt eine Vorstellung der häufigsten High-Level Architekturen von Sicherheitssystemen und die Grundlagen zu "Coded Processing".

### 2.1 Normen und Begriffe

Die Normen stellen ein Regelwerk zusammen, mit welchem der Hersteller der Produkte beweisen kann, dass sie Stand der Technik sind. Produkte, welche nicht dem Stand der Technik entsprechen, können nicht zertifiziert werden [Rei12, S. 253]. Die Haftung im Falle eines Versagens läge somit beim Hersteller. Bei zertifizierten Produkten trifft den Hersteller aufgrund der strengen Regeln beim Entwurf und der Fertigung keine Schuld. Hersteller sicherheitskritischer Elemente sind somit auf eine Zertifizierung ihrer Produkte durch den Technischer Überwachungsverein (TÜV) angewiesen.

Dieser Abschnitt gibt einen Überblick über die relevanten Standards und deren Anforderung um die funktionale Sicherheit zu garantieren.

#### 2.1.1 Begriffe und Definitionen

Das Sicherheitssystem, oft auch Sicherheitssteuerung genannt, ist einer Speicher Programmierbaren Steuerung (SPS) nicht unähnlich. Doch im Vergleich zu einer SPS ist der Aufgabenbereich eingeschränkt. Es wird nichts aktiv gesteuert, es wird überwacht und im Fehlerfalle die Gefahrenquelle abgeschaltet. Der Schwerpunkt einer Sicherheitssteuerung liegt auf der Fehleraufdeckung. Tritt im Betrieb ein Fehler im Sicherheitssystem auf, muss dieser erkannt werden, bevor dadurch eine Gefährdung entstehen könnte. In der deutschen Sprache ist der Begriff "Fehler" weitläufiger als im englischen. Im Englischen unterscheidet man zwischen "Fault", "Error" und "Failure", welche im Deutschen mit "Fehler", "Abweichung" und "Ausfall" übersetzt werden [IEC10a, Teil. 4]. Der Fehler (Fault) ist als "Verlust der Fähigkeit die geforderte Funktion auszuführen" definiert [Wra10, S. 295]. Ausgelöst durch einen Fehler (Fault) kann eine Abweichung (Error) auftreten,

welche einer Nichtübereinstimmung aus erwartetem und tatsächlichem Wert entspricht [Wra10, S. 291]. Auf diesen Fehlzustand kann der Ausfall (Failure) folgen, welcher als "Beendigung der Fähigkeit einer Funktionseinheit eine geforderte Funktion auszuführen" [Wra10, S. 291] festgelegt ist. Um einen Fehler während des Betriebs aufzudecken werden Diagnosetests durchgeführt. Die Wahrscheinlichkeit damit einen Fehler zu entdecken wird durch den "Diagnosedeckungsgrad" bestimmt [Wra10, S. 292].

Tritt ein Fehler auf, muss das System in einen Sicherheit bietenden Zustand, den "sicheren Zustand" überführt werden, dessen Sicherheit als "Freiheit von nicht akzeptierbarem Risiko" [Wra10, S. 299] verstanden wird. Durch einen hohen Diagnosedeckungsgrad können Fehler detektiert werden, welche möglicherweise nicht zu einer Abweichung, gefolgt von einem Ausfall geführt hätten, wodurch sich die Verfügbarkeit reduziert. Diese ist definiert, mit welcher Wahrscheinlichkeit man das System zu einem zufälligen Beobachtungszeitpunkt im korrekt arbeitenden Zustand vorfindet [Bör04, S. 5]. Im Weiteren werden die Begriffe "sicherheitskritisch", "sicherheitsrelevant" und "sicherheitsbezogen" Synonym verwendet.

### 2.1.2 IEC 61508 - Funktionale Sicherheit sicherheitsbezogener elektrischer/ elektronischer/ programmierbarer elektronischer Systeme

Die IEC 61508 [IEC10a] besteht aus insgesamt 7 Teilen. Bei Teil 1 bis 4 handelt es sich um den normativen, bei Teil 5 bis 7 um den informativen Teil. Der informative Teil ist nicht zwingend zu befolgen, gibt aber eine Vielzahl von Richtlinien für die Entwicklung an. Der informative Teil ist eine Hilfestellung an den Entwickler und gibt Beispiele für Realisierungen an. Ziel ist es die Anzahl der systematischen und zufälligen Fehler auf ein vertretbares Mindestmaß zu reduzieren. Abgeleitet von dieser Norm existieren spezifischere Auslegungen für die Bereiche Prozessindustrie IEC 61511 [IEC03], Maschinenbau IEC 62061 [IEC10b] und Kraftfahrzeuge ISO 26262 [ISO12].

Mit der IEC 61508 wird der Begriff des Safety Integrity Levels SIL eingeführt, deren Skala von 1 bis 4 reicht. SIL 1 stellt die geringste Sicherheitsstufe dar und SIL 4 die höchste. SIL 1 muss von Einrichtungen erfüllt werden, bei welchen im Fehlerfalle Verletzungen von Einzelpersonen zu erwarten sind. Bei SIL 4 ist im Fehlerfalle mit Verletzung und Tod mehrerer Personen zu rechnen. Die Einteilung, welches SIL ein Produkt erreicht, errechnet sich aus der Propability of Failure per Hour (PFH) und der Safe Failure Fraction (SFF). Tabelle 2.1 und Tabelle 2.2 geben die vorgeschriebenen Werte an. Die PFH gibt an, wie wahrscheinlich ein gefährlicher Ausfall pro Stunde auftritt. Mit der SFF wird angegeben, mit welcher Wahrscheinlichkeit ein Systemausfall ein "sicherer Ausfall" ist. Sichere Ausfälle können in drei Gruppen eingeteilt werden: sichere entdeckte Ausfälle, sichere unentdeckte Ausfälle und unsichere entdeckte Ausfälle. Es wird davon ausgegeangen, dass nicht alle Fehler aufgedeckt werden (können). Dies stellt aber kein Problem dar, wenn von dem Fehler und dessen Auswirkungen keine Gefahr ausgeht. Tritt ein gefährlicher, jedoch entdecker Fehler auf, können immer noch Maßnahmen zur Beherrschung oder Schadensbegrenzung durchgeführt werden. Einzig die gefährlichen unentdeckten Fehler sind mit allen Mitteln zu verhindern. Die SFF berechnet sich wie in 2.1 dargestellt. Die Rate der sicheren (safe) Ausfälle wird durch  $\lambda_S$  repräsentiert,  $\lambda_{DD}$  für die Rate der gefährlichen, entdeckten (dangerous detected) Ausfälle und  $\lambda_D$  für die Rate der gefährlichen Ausfälle. Ob ein Fehler entdeckt wird, bevor Gefahr besteht, hängt von der SFF ab. Um eine hohe SFF zu erreichen, werden Selbsttestfunktionen eingebaut. Diese können von einem einfachen Watchdog-Timer bis zu einer vollständigen Ablaufkontolle der sicherheitstechnischen Anwendung reichen. Mit Hilfe der Selbstestfunktionen ist in begrenzem Maßstab möglich Fehler gemeinsamer Ursache aufzuspüren. Fehler gemeinsamer Ursache (Common Cause Failure (CCF)) stellen in jedem System eine große Gefahr dar.

Hardwaremäßig redundant oder diversitär aufgebaute Systeme könnten zum Beispiel von einer Betriebspannungsunterbrechung gleichzeitig betroffen sein.

$$SFF = \frac{\sum \lambda_S + \sum \lambda_{DD}}{\sum \lambda_S + \sum \lambda_D} \tag{2.1}$$

Im Folgenden dieser Arbeit wird vor allem auf Teil 2 der IEC 61508 Rücksicht genommen, denn diese beschäftigt sich mit den Anforderungen an die Hardware sicherheitskritischer Steuerungen. Trotz des hier gewählten Lösungsansatzes die zertifizierte Hardware ablösen zu wollen und dessen hohe Fehleraufdeckung in Software nachzubilden, muss bei dem Softwareentwurf speziell auf die Fehler der Hardware eingegangen werden. Fehler, welche bei bisherigen Sicherheitssteuerungen bereits in Hardware abgefangen wurden, müssen nun in Software behandelt werden. Somit ist es wichtig sich mit den Hardwarefehlern auseinanderzusetzen und wie sich diese in höheren Softwareschichten auswirken.

In der IEC 61508 werden zwei Typen von Bauelementen unterschieden. Für ein Typ-A Element müssen alle möglichen Ausfallsarten eindeutig definiert und das Verhalten im Fehlerfalle bekannt sein. Somit können nur einfach aufgebaute Elemente wie Widerstände, Kondensatoren, etc. als Typ-A bezeichnet werden. Ein Element ist Typ-B, wenn die Ausfallsarten und das Verhalten im Fehlerfalle nicht definiert ist oder aufgrund der Komplexität nicht definiert werden kann, beispielsweise Mikroprozessoren, integrierte Schaltkreise, etc. Wird ein sicherheitskritisches Produkt aus Typ-A und Typ-B Elementen aufgebaut, muss davon ausgegangen werden, dass das ganze Produkt Typ-B wird. Ein Industrie-Personal Computer (PC) ist ein sehr komplexes Produkt und somit als Typ-B (Tabelle 2.2) zu behandeln.

**Tabelle 2.1:** Ausfallsgrenzwerte bei kontinuierlichem Betrieb oder hoher Anforderungsrate [IEC10a, Teil 1, S. 37]

| SIL | PFH                                   |  |  |

|-----|---------------------------------------|--|--|

| 4   | $\geq 10^{-9} \text{ bis } < 10^{-8}$ |  |  |

| 3   | $\geq 10^{-8} \text{ bis } < 10^{-7}$ |  |  |

| 2   | $\geq 10^{-7} \text{ bis } < 10^{-6}$ |  |  |

| 1   | $\geq 10^{-6} \text{ bis } < 10^{-5}$ |  |  |

**Tabelle 2.2:** Maximal zulässiger SIL für ein aus Typ-B Elementen aufgebautes (Teil-) System [IEC10a, Teil 2, S. 27]

| SFF         | Hardwarefehlertoleranz |       |       |

|-------------|------------------------|-------|-------|

|             | 0                      | 1     | 2     |

| < 60 %      | nicht erlaubt          | SIL 1 | SIL 2 |

| 60% - < 90% | SIL 1                  | SIL 2 | SIL 3 |

| 90% - < 99% | SIL 2                  | SIL 3 | SIL 4 |

| ≥ 99 %      | SIL 3                  | SIL 4 | SIL 4 |

Die Anforderungen an die SFF, bezogen auf das SIL, zeigt die Tabelle 2.2. Die Hardwarefehlertoleranz (HFT) von N sagt aus, wie viele Fehler ein System tolerieren kann um die sichere

Ausführung nicht zu gefährden. Treten nun N+1 Hardwarefehler auf, kann die Sicherheitsfunktion beeinträchtigt werden. In dieser Arbeit muss von einer HFT von Null ausgegangen werden. COTS-Hardware ist nicht nach den Regeln der Norm entworfen und bietet keinerlei Rüstzeug um selbst bei Multi-Core-Systemen als zweikanalig argumentiert zu werden. Daraus folgend ist eine SFF von mindest 99 % gefordert. Dieser Wert ist sehr hoch und erlaubt bei der Entwicklung des sicherheitskritischen Systems keine Unachtsamkeiten.

# 2.1.3 EN 13849 - Sicherheit von Maschinen, Sicherheitsbezogene Teile von Steuerungen

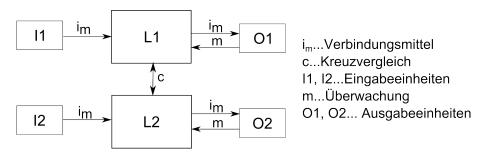

Die EN 13849 [EN08] besteht aus zwei Teilen. Teil eins behandelt allgemeine Gestaltungsleitsätze und Teil zwei die Validierung und löst die EN 954 ab. In der EN 13849 werden die Sicherheitslevel nach Kategorien 1 bis 4 und Performance Level (PL) a bis e angegeben. Entsprechend der Forderung nach SIL 3 der IEC 61508 wäre hier ein PL von e gefordert. Die EN 13849 schreibt den strukturellen Hardwareaufbau entsprechend Abb. 2.1 für die einzelnen PL vor. Die Querverbindung c zwischen den Logikeinheiten L1 und L2 steht für die gegenseitige Überwachung der Systeme. Jede Logikeinheit ist Watchdog für die andere und kann im Fehlerfall den sicheren Zustand einleiten. Der in der Norm gezeigte Aufbau ist jedoch nicht die zwangsläufig für die Hardware anzuwenden, es ist als logisches Schaltbild anzusehen und kann jederzeit verändert werden, sofern nachgewiesen werden kann, dass Sicherheit nicht eingeschränkt wird.

Abbildung 2.1: Logischer Aufbau eines Kategorie 4 Systems entsprechend EN 13849 [S. 46]

Weiters ist gefordert, dass ein einzelner Fehler nicht zum Verlust der Sicherheitsfunktion führt. Bei einer Anhäufung unerkannter Fehler darf das System nicht die Sicherheitsfunktion verlieren. Die CCF sowie die MTTF<sub>d</sub> muss "hoch" sein, dies wird als  $> 90\,\%$  definiert. Trotz der vorgeschriebenen, zweikanaligen Architektur stellen CCFs den wunden Punkt dieses Aufbaus dar. Die besten Gegenmaßnahmen werden im Anhang F aufgezählt:

- physikalische Trennung der Signalpfade um Kriechströme zu verhindern

- Diversität zwischen den Kanälen

- Entwurf und Erfahrung mit den Bauteilen

- Analyse der Ausfallsarten durch Effektanalyse

- Ausbildung der Monteure

- Umgebungsschutz vor EMV, Temperatur, Feuchtigkeit

Diese Aufzählung ist natürlich keinesfalls vollständig, sie soll nur einen Überblick über die zu berücksichtigenden Fehlerquellen ermöglichen. Die Anforderungen sind nur durch zertifizierte Hardware erreichbar. Da dies hier keine Option ist, müssen andere Mittel gefunden werden, wie sie in Kapitel 3 vorgestellt werden.

Es zeigt sich, dass kein Sicherheitssystem fehlerfrei sein kann, jedoch muss idealerweise jeder aufgetretene Fehler detektiert werden und darf nicht zu einem Sicherheitsrisiko führen. Eine Möglichkeit mit Fehlern umzugehen ist diese zu tolerierten. Ein fehlertolerantes System kann einen oder mehrere detektiere Fehler tolerieren und die Sicherheitsfunktion weiter ungehindert ausführen. Ein fehlertolerantes System muss eine oder mehrere Formen der Redundanz beinhalten.

#### 2.1.4 Redundanz

Ein redundantes System verfügt immer über zusätzliche Funktionalität, welche im fehlerfreien Betrieb nicht benötigt wird. Allgemein existierten vier Formen von Redundanz [Bör06, S. 65]

- Hardware-Redundanz,

- Software-Redundanz,

- Zeitredundanz,

- Informations redundanz.

Ein hardwareredundates System besitzt zusätzliche Hardwarekomponenten. Fällt eine Komponente aus, kann eine weitere die Funktion übernehmen. In diesem Zusammenhang existiert der Begriff der HFT. Eine HFT von n bedeutet, dass n Fehler toleriert werden können, beziehungsweise bei n+1 Fehlern muss mit dem Verlust der Sicherheitsfunktion gerechnet werden.

Bei Software-Redundanz ist das gleiche Programm mehrere Male vorhanden. Bleibt eines aufgrund eines Fehlers stehen, kann das zweite die Berechnung zu Ende führen. Bei Software bietet sich zusätzlich heterogene Redundanz, auch Diversität genannt, an. Hierbei wird das Programm mit gleicher Funktionalität, aber unterschiedlichem Quellcode mehrfach implementiert. Günstige und dennoch effektive Diversität kann durch die Verwendung unterschiedlicher Compiler oder Compilerparameter [GG09] erreicht werden.

Bei Zeitredundanz besteht noch zusätzliche Zeit bis die Daten ausgegeben werden müssen. So kann das Programm erneut gestartet werden und noch vor der Deadline die Ergebnisse liefern. Liegen die Daten mehrfach vor, spricht man von Informationsredundanz. Redundanz kann neben der Fehlertolerierierung auch zur Fehleraufdeckung verwendet werden. Die häufigsten Redundanz-Architekturen werden nun diskutiert.

#### Redundanzarchitekturen

Bei den hier vorgestellten Architekturen wird nur auf die Berechnungslogik genauer eingegangen. Das gezeigte ist ebenso auf die Eingangs- und Ausgangsmodule anwendbar, der Schwerpunkt dieser Arbeit liegt jedoch auf der Berechnungslogik. Um eine ausreichende Fehlererkennung zu erreichen, wird oft ein oder mehrere Elemente mehrfach ausgeführt. Die parallel arbeitenden Komponenten können zur Fehleraufdeckung oder Fehlertoleranz verwendet werden. Bei der Fehleraufdeckung wird das Ergebnis der mehrfachen Berechnung verglichen und im Falle einer Ungleichheit

die Fehlerreaktion ausgeführt. Die Fehlererkennung ist Voraussetzung für Fehlertoleranz. Nur bei einem erkannten Fehler kann mittels Fehlertoleranz entgegengewirkt werden.

Die einfachste Form eines Eingangs-Ausgangs-Systems, welches keine Redundanz besitzt, jedoch in weiterer Folge der Arbeit noch wichtig wird, ist das 1001-System in Abb. 2.2.

**Abbildung 2.2:** 1001 System [Bör06, p 158]

Das Eingangsmodul besitzt die physikalischen Schnittstellen zur Umgebung. Im Modul können z. B. Analog-Digital-Wandler verbaut sein. Die Übertragung der Daten von Eingang zur verarbeitenden Logik wird typisch über ein Bus-System durchgeführt. Da es sich hierbei um sicherheitskritische Daten handelt, wird ein entsprechendes Sicherheitsprotokoll verwendet. In der Verarbeitungslogik wird aus den Eingangsdaten ein Ausgangsabbild berechnet und wiederum über ein sicherheitskritisches Protokoll an das Ausgangsmodul übergeben. Aufgrund der Abhängigkeit jedes Blocks zum vorhergehenden kann in dieser sogenannten 1-out-of-1 (kurz 1001)-Architektur kein Fehler erkannt und somit toleriert werden.

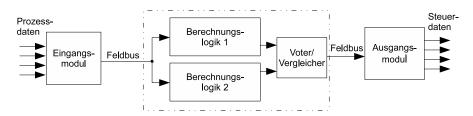

Ist die Hardware für die Berechnung doppelt ausgeführt, aber nur eine Berechnung für eine korrekte Funktion notwendig, spricht man von einem 1002-System Abb. 2.3. Dieser Aufbau ist häufig in sicherheitskritischen Systeme zu finden.

Abbildung 2.3: 1002 System

Die zweite Berechnungseinheit kann dem Aufbau der ersten entsprechen. Diesen Fall nennt man homogene Redundanz. Ist der interne Aufbau unterschiedlich, das Verhalten jedoch gleich, wird es heterogene Redundanz, oder diversitäre Redundanz genannt. Beide Berechnungseinheiten generieren ein vollständiges Ergebnis und leiten dieses an den Voter/Vergleicher weiter. Hier wird entschieden, wie mit den Ergebnissen weiter vorgegangen wird. Im Falle einer Übereinstimmung wird das Ergebnis an den Ausgang weitergeleitet. Falls die berechneten Ergebnisse voneinander abweichen, stehen zwei Optionen zur Auswahl. Einerseits kann der Voter seine Stimme für eines der beiden Ergebnisse abgeben und dieses an den Ausgang weiterleiten. Die Entscheidung wird anhand von Vorwissen getroffen, um zu erkennen, welches Ergebnis das Falsche ist. Dieser Aufbau erhöht die Verfügbarkeit, als auch die Komplexität des Voters, da er mehr als nur vergleichen muss. In 1002-System wird ein Voter nur selten eingesetzt, ein 1003-System eigenet sich dafür besser, da hier eine Mehrheitsentscheidung getroffen werden kann. Werden die Ergebnisse einem Vergleicher zugeführt, vergleicht dieser die Übereinstimmung und löst im Falle einer Abweichung

eine Fehlerbehandlung aus. In industriellen Anwendungen wird meist ein Not-Stop ausgeführt, um den Prozess in einen sicheren und gefahrlosen Zustand überzuführen. Die somit gesteigerte Sicherheit und reduzierte Verfügbarkeit ist ein grundsätzliches Problem von Sicherheitssteuerungen. Der Aufbau besitzt jedoch einen Schwachpunkt: die korrekte Funktion des Vergleichers/Voters kann nicht überprüft werden. Trifft er die falsche Entscheidung oder verfälscht die richtigen Ergebnisse, sind keine Sicherungsmaßnahmen mehr vorhanden um den Fehler abzufangen. Hinzu kommt noch, dass nur Endergebnisse auf deren Richtigkeit überprüft werden. Für eine erhöhte Fehleraufdeckung empfiehlt es sich, ebenso während der Berechnung Zwischenergebnisse zwischen den Berechnungseinheiten auszutauschen und so etwaige Fehler aufzudecken, bevor ein falsches Ergebnis an die Auswertung geliefert wird.

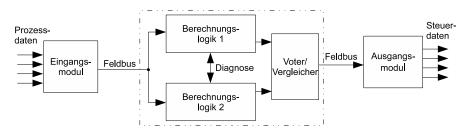

Die Erweiterung um die Diagnose wird im Architekturnamen durch ein angehängtes "D" symbolisiert. In einem 1002D System wie in Abb. 2.4 werden von den Berechnungseinheiten Zwischenergebnisse über den Diagnose-Kanal ausgetauscht. Es ist zu berücksichtigen, dass trotz der Querverbindung keine negative Beeinflussung der Einheiten stattfinden darf. Darum wird hier meist einfache, auf Polling basierende, Kommunikation angewendet. Bei Interrupt-Mechanismen sind für einen "Babbling Idiot" anfällig. In diesem Fall würde eine Einheit ununterbrochen senden und unterbricht aufgrund eines Interrupts immer die andere Einheit, wodurch diese an der korrekten Ausführung gehindert wird.

Abbildung 2.4: 1002D System

Die Fehleraufdeckung ist höher als ohne Quervergleiche, der Schwachpunkt des Systems, der Voter, ist in dieser Architektur ebenso vorhanden und kann durch einen Einzelfehler zu letalen Systemausfällen führen.

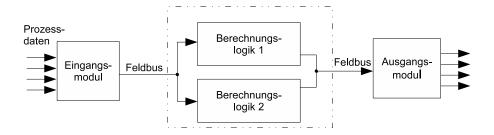

Ein in der Industrie sehr häufig zu findender Aufbau ist die 2002-Architektur, optional als 2002D ausgeführt (Abb. 2.5). Ein großer Vorteil ist, dass der Vergleicher/Voter nicht benötigt wird. Die Berechnungseinheiten arbeiten weiterhin parallel und unabhängig voneinander. Doch anstatt das volle Ergebnis an den Ausgang zu liefern, gibt jede Berechnungseinheit nur eine Hälfte des Ergebnisses aus. Beispielsweise liefert Berechnungslogik 1 den ersten Teil und Berechnungslogik 2 den zweiten. Vor der Übertragung werden diese Teile in ein Datenpaket kopiert und über den Feldbus übertragen. Verlief die Berechnung korrekt, findet das Ausgangsmodul zwei Teilergebnisse, welche sich gegenseitig vervollständigen. Ist bei der Berechnung jedoch ein Fehler aufgetreten und die Teilergebnisse passen nicht zueinander, kann der Ausgangsknoten den Fail-Safe-Zustand einleiten. Diese Methode setzt voraus, dass das sicherheitskritische Feldbussystem Übertragung doppelter Daten unterstützt. Dies stellt aber kein Problem dar, da die Norm IEC 61508 für höchste Sicherheitsanforderungen über Black-Channel<sup>1</sup> indirekt doppelte Datenübertragung fordert [EN11].

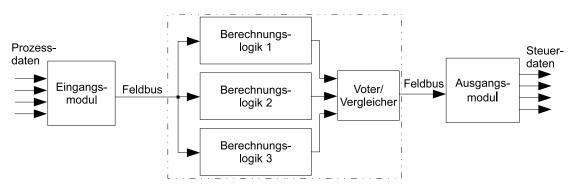

Das Hinzufügen eines dritten Hardwarekanals wie in Abb. 2.6 ist nur bei Systemen mit höchsten Sicherheits- und Verfügbarkeitsanforderungen gefordert. Beispielsweise kann bei Flugzeugen im

<sup>&</sup>lt;sup>1</sup>Verfahren zur Übertragung sicherheitskritischer Daten über nicht gesicherte Kommunikationskänale

Abbildung 2.5: 2002 System

Flug nicht ohne weiteres ein sicherer Zustand angefahren werden. Es muss selbst in Fehlerfall eine Restfunktionalität vorhanden bleiben um sicher landen zu können. Das dabei verwendete 2003-System wird auch Triple Modular Redundancy (TMR) genannt und besitzt eine ausgeklügelte Verschaltung der Voter, um im Fehlerfall den defekten Kanal vollständig zu isolieren und eine Beeinflussung der noch korrekt arbeitenden Einheiten zu verhindern. In typischen industriellen Anwendungen sind drei Hardwarekanäle jedoch nicht notwendig, da so gut wie alle Prozesse einen sicheren Zustand besitzten, welcher im Fehlerfall angefahren werden kann. Eine Vervielfachung der Hardware schützt jedoch nicht vor CCFs.

**Abbildung 2.6:** 2003 System [Bör06, p 161]

#### 2.1.5 Fehlerarten

Die Fehlerarten eines Sicherheitssystems lassen sich nach ihrer Ursache und ihrem zeitlichen Auftreten klassifizieren. Das Auftreten der folgenden vier Punkte muss durch entsprechende Maßnahmen verhindert werden [Sch11, S. 7].

- Transienter Fehler: ein Fehler ist transient, wenn er nach einmaligem Auftreten nicht mehr vorhanden ist. Transiente Fehler sind immer zufällig auch wenn sich durch schlechtes Design, wie zum Beispiel systematischen Fehlern, die Wahrscheinlichkeit für transiente Fehler erhöht. Transiente Fehler zu detektieren ist eine der Herausforderungen, auf welche in dieser Arbeit besonderes Augenmerk gelegt werden muss. Ein Fehler dieser Kategorie wäre zum Beispiel ein Bit-Flip im Speicher.

- Permanenter Fehler: ein permanenter Fehler ist dauerhaft im System vorhanden. Ursache dafür kann einerseits ein systematischer Fehler im Design sein, andererseits ein zufällig im

Betrieb aufgetretener Defekt, welcher, im Gegensatz zu einem transienten Fehler, von Dauer ist. Permanente Fehler sind leichter zu detektieren als transiente, da durch das dauerhafte Auftreten die Wahrscheinlichkeit mehrere Daten zu korrumpieren größer ist. Stuck-at-Fehler sind eine häufige Form von permanenten Fehlern.

- Systematischer Fehler: systematische Fehler wirken sich immer permanent im System aus. Sie entstehen während der Entwicklungsphase und sind dauerhaft vorhanden. Durch strukturierte Entwicklung und ausführliche Tests der Einzelkomponenten können diese Fehler reduziert werden. Ein Fehler im Sourcecode fällt in diese Kategorie.

- Zufälliger Fehler: die zufälligen Fehlern stellen eine große Gefahr dar und müssen deswegen besonders intensiv behandelt werden. Im Gegensatz zu systematischen Fehlern können diese Fehler nicht durch ausführliche Tests in der Designphase aufgedeckt werden, obwohl ein schlechtes Design zufällige Fehler begünstigen kann.

Die größte Gefahr geht von den zufälligen, transienten Fehlern aus. Auswirkungen können nicht nur verfälschte Daten sein, sondern auch ein veränderter Programmablauf. Ein Bit-Flip im Speicher kann durch die heute weit verbreitete von-Neumann Architektur Daten wie auch Instruktionen verändern. Aufwendige Hardware- und Softwarelösungen sind notwendig, um diese Fehler beherrschen zu können.

#### 2.1.6 Systemtests

Die vollständige Funktionsfähigkeit der Sicherheitssteuerung muss idealerweise zu jedem Zeitpunkt im Betrieb garantiert werden. Um dies zu ermöglichen, werden Selbsttests eingebaut um die Einzelelemente zu überprüfen und einen Fehler zu finden, bevor er sich in einer sicherheitskritischen Berechnung auswirken kann. Die Ausführung dieser Tests kann entweder online durchgeführt werden, das heißt während des Normalbetriebs und es muss keine gesteuerte Maschine gestoppt werden oder offline, wobei die Sicherheitsapplikation während des Selbsttests angehalten wird. Die muss jedoch nicht zwingend von außen erkennbar sein. Bisher bestehende Systeme besitzen meist offline-Tests. Dazu wird die Sicherheitsapplikation angehalten oder eine Ruhephase des Systems ausgenutzt, in welcher einzelne Module nicht benötigt werden. Sie finden offline statt, da nicht benötigte Teile getestet werden; die Applikation muss jedoch nicht angehalten werden, somit gehen Selbsttests nicht mit dem Stillstand der Maschine einher. Beispielsweise werden nicht benötigte Teile im Random Access Memory (RAM) mittels Galpat oder Walking-Bit auf Stuck-at-Fehler oder Übersprechen von Daten- und Adressleitungen untersucht. Für den Test der Arithmetical Logical Unit (ALU) können Berechnungen mit bereits vorher bekannten Ergebnissen durchgeführt werden. Ein Vergleich zwischen den vorher und aktuell berechneten Daten zeigt die Fehlerfreiheit der ALU.

Diese Tests zeigen meist nur systematische, permanente Fehler auf. In seltenen Fällen können zufällige, während des Selbsttests auftretende transiente Fehler detektiert werden die zu einem Sicherheitshalt des Systems führen. Ein Löschen des Speichers bereinigt das Problem, da es die Eigenschaft der transienten Fehler ist, nur für einen Zeitraum vorhanden zu sein. Der Schwerpunkt von offline-Selbsttests ist das Aufdecken von permanenten Fehlern. Darum könnte das Detektieren eines transienten Fehlers als störend interpretiert werden. Dem ist jedoch nur bedingt so, denn wäre der transiente Fehler in der Applikation aufgetreten, hätte er zu Sicherheitsrisiken führen können. Dies zeigt die Schwäche von offline-Tests: permanente Fehler können unabhängig von der Applikation aufgedeckt werden, transiente Fehler können nur durch Zufall entdeckt werden und

deren Aufdeckung ist ohne weiteren Nutzen.

Um transiente Fehler während der Sicherheitsapplikation aufzudecken, sind online-Tests notwendig. Einer der wichtigsten online-Tests ist der Vergleich der Ausgangsdaten zwischen redundanten Berechnungspfaden, wie in Abschnitt 2.1.4 ausführlich erklärt. Besser wäre es, Fehler früher aufzudecken noch bevor ein Endergebnis ausgegeben wird. Für den RAM des Systems kann dies im einfachsten Fall z. B. mittels Parity-Bit oder speziellen Error Correcting Code (ECC)-Speichermodulen erreicht werden, wie sie im Serverbereich weit verbreitet sind. Die ALU im Betrieb zu testen deutlich komplexer. Eine häufig verwendete Technik ist das Mehrfachausführen von Berechnungen. Dies führt zur Fehleraufdeckung in der Annahme, dass der transiente Fehler nur einmal auftritt. Das Beste aus der Welt der Online- und Offline-Tests zu kombinieren ist der Ansatz des Coded Processing und wird in 2.3 näher erläutert.

#### 2.1.7 Fehler realer Systeme

Das System besteht aus mehreren Teilen, welche unterschiedlichen Fehlerarten und -raten unterworfen sind. Dementsprechend müssen auch die Fehleraufdeckungsmaßnahmen je nach Element angepasst werden, wobei es sich bei Central Processing Unit (CPU) und Speicher um die zwei wichtigsten Elemente eines Computersystems handelt.

In der Publikation [RV07] von Valzco und Faure werden die logischen Elemente einer CPU analysiert und die Fehlermöglichkeiten der einzelnen Module quantitativ untersucht. Die Grundbausteine, aus welchen eine CPU besteht, lauten Register, Adress- und Datenbusse, Integer-/Floating-Point Unit, Instruktions-Cache, Daten Cache, Steuerwerk und Debug Unit. Jedes dieser Elemente hat aufgrund seines unterschiedlichen Aufbaus und Funktion bestimmte Schwächen für Bitfehler. Register: Register sind bei so gut wie jeder Berechnung oder Datenmanipulation involviert, damit verbunden ist eine starke Auswirkung von Single Event Upset (SEU). Am gefährlichsten ist es, wenn gegen Ende der Berechnung, kurz vor der Ausgabe ein Bitfehler passiert. Es ist schwierig den Fehler zu entdecken und eine Fehlerbehandlung einzuleiten. Die Fehlerauswirkung kann ebenso nicht eingegrenzt werden, da die Register Daten, Instruktionen und Adressen bearbeiten und somit das zukünftige Verhalten bei einem Bitfehler unvorhersehbar ist.

Adress- und Datenbusse: dieser Teil beinhaltet meist nur wenige Register, nur ein paar Latches um Adressen zu speichern. SEUs in diesen Latches führen zu falschen Daten/Adressen Schreib/Lesevorgängen. Adressfehler können durch eine Memory-Protection erkannt werden, jedoch nur, wenn der erlaubte Speicherbereich verlassen wird. Fehlerhafte Zugriffe im zugeteilten Speicherbereich bleiben unbemerkt.

Integer Unit, Floating-Point Unit: Fehler in diesen Elementen sind schwer, oder gar nicht von selbst zu erkennen. Weder Hardware oder Betriebssystem bieten eine Möglichkeit hier Abweichungen zu erkennen. Eine SEU Erkennungswahrscheinlichkeit von 0% [Joã09] zeigt die Wichtigkeit von zusätzlichen Schutzmaßnahmen.

Instruction Cache: dieser besteht aus zwei Teilen, einem großen Static Random-Access Memory (SRAM) für die geladenen Daten und einem Tag-Array, welches die Gültigkeit der Daten im SRAM festlegt. Veränderungen durch SEUs in den Tag-Arrays können zu zwei Fehlerarten führen.

- Eine Instruktion wird fälschlicherweise als ungültig bezeichnet. Daraus folgt ein Neuladen der Instruktion aus dem externen Speicher und eine Verzögerung im Programmablauf.

- Wird ein Tag von ungültig auf gültig gesetzt, wird ein veralteter Befehl ausgeführt und der Programmfluss fehlerhaft.

Für die Daten im Instruktion-Teil des Caches entstehen vier Fehlermöglichkeiten:

- Veränderung der Instruktion bei ungültig gesetztem Tag führt zu keiner Veränderung im Programmablauf,

- verfälschte Instruktion ist nicht mehr Teil des Instruktion-Sets führt zu einer Exception/Trap,

- der SEU tauscht die Instruktion und ein falscher Befehl wird ausgeführt und

- der SEU verändert die Operanden der Instruktion.

Zusammengefasst führen die Fehler wieder zu falschen Outputs oder Verlust der Sequenz (veränderter Programmfluss).

Data Cache: ähnlicher Aufbau wie bei dem Instruktion Cache in Daten- und Tag-Array. Fehler im Tag-Array können Daten fälschlicherweise gültig bzw. ungültig machen. Fehlermöglichkeiten im Allgemeinen gleich dem Instruktion Cache.

Steuerwerk: Diese beinhaltet möglicherweise komplexe Algorithmen zur Steuerung des Prozessors (pre-fetching, out-of-order execution,...). Durch den komplexen Aufbau können Fehler sich vielseitig auswirken: falscher Programmablauf, Trap/Exception, etc.

Debug Unit: SEUs können spezielle Prozessormodi ausführen, welche möglicherweise nicht dokumentiert sind. Daraus entstehen unvorhersehbare Outputs und Brüche im Programmfluss.

Aufgrund der hohen Packungsdichte am Wafer stellt der Speicher einen besonders kritischen Teil eins Computers dar, weshalb er hier genauer analysiert wird. Der Festwertspeicher stellt ein geringes Risiko für unentdeckte dar, da er nur einmal geschrieben und ab dann nur noch gelesen wird. Um Fehler in den Daten festzustellen bieten sich Prüfsummen wie z. B. die zyklische Redundanzprüfung an, wodurch Fehler mit nur geringem zusätzlichen Speicher- und Rechenaufwand entdeckt werden können.

Deutlich kritischer ist der Arbeitsspeicher zu betrachten. Hier wird die Information in Form von Anwesenheit bzw. Abwesenheit von Elektronen dargestellt. Moderne Arbeitsspeicher sind als Dynamic Random Access Memory (DRAM) aufgebaut, in welchen die gespeicherten Elektronen in Kondensatoren geladen werden. Diese Ladung kann nur wenige Millisekunden gehalten werden, wodurch eine Auffrischung notwendig wird [HJL02, S. 455]. Diese stetige Auffrischungen gepaart mit schnellen Lese - und Schreibvorgängen sind besonders fehleranfällig. Wird nur ein Kondensator falsch geladen, oder verliert seine Ladung zu schnell, werden die Nutzdaten verfälscht. Ebenso sind Schreib- und Lesefehler nicht unbeachtet zu lassen: es besteht die Möglichkeit, dass aufgrund eines fehlerhaften Transistors in der Adressleitung bei bestimmten Schreib-/Lesekombinationen eine falsche Stelle bearbeitet wird. Google Inc. [Bia09] berichtet von einer Abhängigkeit der Fehler von Temperatur und Alter. Wie zu erwarten ist, führt eine erhöhte Temperatur zu höheren Fehlerraten. Google konnte hier eine Verschlechterung um Faktor drei feststellen. Das Alter der Speicherelemente wirkt sich ebenso auf die Bit-Fehler-Rate negativ aus. Nach bereits 10 Monaten kann eine erhöhte Fehlerrate festgestellt werden. Nach nur 20 Monaten wird bereits ein 6-fach erhöhter Wert (im Vergleich zum Ausgangswert) festgestellt.

Sieht man von den irdischen Fehlerquellen ab, existiert noch eine weitere Gefahr, welche die Nutzdaten im Speicher verfälschen kann. Ionisierende Strahlung, wie sie bei radioaktiven Zerfall oder auch Sonnenstürmen vorkommt stellt eine vollkommen unberechenbare Gefahr dar, welche zu transienten Speicherfehlern führen kann. Trifft ionisierende Strahlung auf eine Speicherstelle, kann diese den gespeicherten Wert verändern [Sch07]. Wie stark diese Fehlerquelle zu

berücksichtigen ist hängt von einer Vielzahl von Faktoren hab. Einerseits ist die Strukturbreite wichtig, denn bei kleineren Strukturen werden weniger Ladungsträger zur Darstellung eines Bits benötigt, welche dann leichter verfälscht werden können. Mit sinkender Strukturbreite sinkt auch die Betriebsspannung, welche die Problematik mit ionisierender Strahlung weiter verschärft. Tezzaron Semiconductor [Sem05] berichtet in für DRAM eine Soft Error Rate von  $2, 3 \cdot 10^{-12}$  pro Bit pro Stunde (entspricht 2.300 Failure in Time (FIT)<sup>2</sup>/Mbit). Daraus ergibt sich bei 1 Gbit Speicher ein Fehler alle 435 Stunden, oder 20 Bitfehler im Jahr. Google Inc. [Bia09] beobachtete in deren Serverfarmen durchschnittlich 25.000 FIT bis 75.000 FIT/Mbit entgegen der bisherigen Annahme von 200 FIT bis 5.000 FIT.

Auf den Speicher muss daher besonderes Augenmerk gelegt werden, da zukünftige Speichermodule noch geringere Strukturbreiten aufweisen werden und somit die Fehleranfälligkeit weiter steigt. Zusätzlich werden zukünftige Sicherungsprogramme ausführlicher, wodurch der benötigte Speicher steigt und dadurch die Wahrscheinlichkeit einen transienten Bitfehler im sicherheitskritischen Speicherbereich anzutreffen. Abhilfe kann ein ECC-RAM liefern, welcher Speicherfehler erkennt und selbstständig korrigieren kann. Dieser RAM ist im Serverbereich bereits weit verbreitet da hier eine Anhäufung von Speicherfehlern über die Zeit zur sogenannten "Datenbankerosion" führen kann. In der Sicherheitstechnik konnte dieser Speicher nicht Fuß fassen, da die Fehlererkennung rein Bitfehler aufdeckt. Falsche Adressierung oder systematische Fehler sind nicht erkennbar, wodurch kein Weg an redundanten Speichermodulen vorbeiführte. Das Gleiche gilt natürlich ebenso für Parity gesicherten Speicher, wobei hier die Hamming-Distanz im Vergleich zu ECC stark verringert ist.

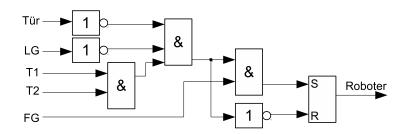

### 2.1.8 Beispiel einer Sicherheitssteuerung

In diesem Punkt soll eine typische am Markt befindliche Sicherheitssteuerung analysiert und deren Komponenten für hohe Fehleraufdeckung aufgezeigt werden. Es zeigt in welchen Punkten sich das in Kapitel 3 entwickelte System von am Markt befindlichen abhebt.

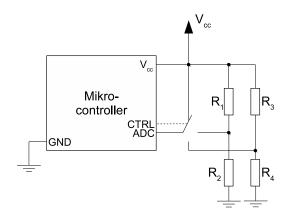

Entsprechend der IEC 61508 Teil 2 lassen sich die Eckdaten einer standardisierten Sicherheitssteuerung skizzieren. Zum einen besteht sie aus zwei hardwaremäßig unabhängigen Kanälen, woraus eine HFT von eins folgt. Laut Tabelle 2.2 ist somit für SIL 3 eine SFF von 90% < 99%gefordert. Ob die beiden Kanäle als 1002D- oder 2002D-Architektur geschaltet sind, bleibt Entscheidung des Herstellers. Als Prozessoren eignen sich leistungsstarke Mikrocontroller z. B. der Firma ARM [5]. Diese sind weit verbreitet und die gefundenen Fehler im Prozessorkern (Silicon Errata) sind gut dokumentiert. Zusätzlich zu den digitalen Bauelementen sind analoge nötig um die Umwelteinflüsse messen zu können und im Falle einer Verletzung der geforderten Grenzwerte einen Nothalt einzuleiten. Analog-Digital Converter (ADC) werden einerseits eingesetzt, um die Betriebspannung zu überwachen, andererseits um die Temperatur des Chips, des Gehäuses und der Umgebung zu messen. Die Richtigkeit dieser Messung ist sicherheitskritisch, weshalb zusätzlich Referenzspannungsquellen eingesetzt werden, um periodisch die ADCs zu testen. Ein möglicher Aufbau dieser Testschaltung ist in Abb. 2.7 dargestellt. Der Messeingang des ADCs kann über den CTRL-Ausgang entweder an die Versorgungsspannung  $V_{cc}$  angeschlossen werden, oder an das Widerstandsnetzwerk. Im Normalbetrieb wird die Betriebsspannung zum Ground (GND) gemessen, für Selbsttests wird auf einen der beiden Spannungsteiler umgeschaltet. Die Widerstandsverhältnisse  $R_1$  zu  $R_2$  und  $R_3$  zu  $R_4$  sollten so gewählt werden, dass der Spannungsbereich des ADCs abgedeckt wird.

$<sup>^{2} 1</sup>Fit = 10^{-9} \frac{1}{h}$

Abbildung 2.7: ADC Testschaltung

Mit der Umgebung wird meist über ein Feldbussystem interagiert, welches für sicherheitskritische Daten zugelassen ist. Die Daten werden dann von einem sicheren Eingangsmodul aufgenommen und an die Sicherheitssteuerung geschickt. Die Ausgangsdaten werden von einem sicheren Ausgangsmodul empfangen und auf den Prozess angewendet. In seltenen Fällen befinden sich sichere Eingangs-/Ausgangsklemmen direkt an der Sicherheitssteuerung. Diese Lösung kommt jedoch nur bei kleineren Sicherheitsanwendungen zum Einsatz, bei größeren kann durch die Dezentralisierung der Verkabelungsaufwand reduziert werden. Der Übergang von interner Logik zu Ausgangsklemmen wird über Optokoppler geführt, um Störungen auf der Leitung keine Chance für Interferenzen mit der Berechnungseinheit zu geben.

Die Software auf den beiden Hardwareplattformen ist diversitär ausgeführt. Das Verhalten nach außen ist bei beiden gleich, die interne Verarbeitung jedoch nicht. Dazu werden unterschiedliche Programmierer-Teams angestellt, oder in einer günstigeren Variante nur die Compiler-Optionen variiert [GG09]. Somit wird die Wahrscheinlichkeit erhöht, dass sich Hardwarefehler in den unterschiedlichen Kanälen unterschiedlich auswirken, wodurch ein Fehler leichter aufgedeckt werden kann.

Neben der Steuerungsanwendung werden noch Diagnose-Programme ausgeführt, welche die Hardware testen, um permanente Fehler, welche im Betrieb auftreten, aufdecken zu können. Die Norm empfiehlt zum Beispiel für den RAM den Galpat-, oder Abraham Test [IEC10a, Teil 2, Tabelle A.6]. Dieser Test muss neben der Anwendung laufen und darf sie nicht beeinflussen.

Tritt ein interner Fehler auf, wird in den "Fail-Silent"-Modus gewechselt, dies bedeutet das Gerät verhält sich passiv und generiert keine Ausgangsdaten mehr. Das Ausgangsmodul schaltet nun nach einer gewissen Totzeit alle Ausgänge sicher ab.

#### 2.2 Fehlermodelle

Um die Auswirkungen von Hardwarefehlern zu untersuchen, muss ein Modell des PCs erstellt werden. Diesem Modell werden Fehler unterstellt und die Auswirkung dieser untersucht. Ein gutes Fehlermodell sollte einerseits der Hardware so weit wie möglich entsprechen, doch andererseits die Fehleranalyse so einfach wie möglich machen. Ein Fehlermodell ist unbrauchbar, wenn es zwar in der Fehleruntersuchung gut abschneidet, jedoch der Realität nicht ausreichend entspricht. Das in dieser Arbeit benötigte Fehlermodell muss einerseits sehr präzise sein, da ein

hoher Diagnosedeckungsgrad gefordert ist, andererseits muss es generisch sein, um für verschiedene COTS-Hardware zu gelten.

Das grundlegendste Fehlermodell auf Hardware-Ebene berücksichtigt nur einzelne Stuck-at Fehler und Bit-Flips [Gol06, S. 12]. Unter einem Stuck-at Fehler versteht man das permanente festhängen eines Bits. Eine Stelle in der Hardware, unabhängig ob es sich dabei um Register, Speicher, ALU, Bus oder ähnliches handelt, kann nur mehr einen Binärwert annehmen. Ein beschreiben oder löschen der fehlerhaften Stelle ändert nichts am Wert. Ein Bit-Flip stellt den unerwünschten Wechsel einer Bit-Stelle in der Hardware dar. Das Auftreten ist transient und wird beim nächsten Beschreiben korrigiert. Wird jedoch gelesen, kann sich der Fehler fortpflanzen und das System gefährden. Dieses Modell ist für die digitalen Sichtweise jeder Hardware anwendbar, jedoch nur selten praktikabel. Der interne Aufbau von COTS-Hardware ist meistens nur dem Hersteller bekannt, wodurch die Auswirkungen eines einzelnen Bitfehlers nicht nachvollziehbar sind. Selbst wenn die Hardware bis auf Transistorebene bekannt wäre, wäre die Komplexität dennoch undurchschaubar.

Einen Abstraktionsschritt höher über der Hardware existieren die System-Ebenen Fehlermodelle, sie stelle die in Abschnitt 2.1.7 erwähnten Fehler in verallgemeinerter Form dar. Das Modell besteht im Entwurf von [Gol06, S. 13] aus zwei Vertretern, einerseits den Datenfehlern und den Codefehlern (oder Instruktionsfehler). Bei den Datenfehlern wird von einem Fehler in einer Speicherstelle ausgegangen, unabhängig vom Ort wo die Daten gespeichert sind. Ein Codefehler verfälscht eine Instruktion im Programmcode. Auch hier ist nicht festgelegt wo der Fehler genau auftritt. Die Codefehler werden in zwei weitere Unterkategorien eingeteilt. Typ 1 verfälscht Instruktionen in dem ein Befehl durch einen anderen ersetzt wird. Der Kontrollfluss wird nicht verändert, das Rechenergebnis hingegen schon. Eine Ausnahme dieser Definition muss jedoch gemacht werden, falls das Rechenergebnis für den weiteren Kontrollfluss wichtig ist. Der Typ 2 behandelt Kontrollflussfehler, welche sich bei Sprungbefehlen auswirken. Es könnte beispielsweise die Zieladresse eines Sprunges verfälscht werden, oder die Sprungbedingung selbst wird manipuliert.

Ein sehr ähnliches Fehlermodell wird von Forin [For89] verwendet. Es besitzt drei Gruppen von Fehlern, Operationsfehler (Operation Error), Operatorfehler (Operator Errors) und die Operandenfehler (Operand Error). Die Operandenfehler sind den Datenfehlern, die Operationsfehlern den Codefehlern Typ 1 ähnlich sind. Die Operandenfehler von Forin können, im Gegensatz von den Datenfehlern, alle Instruktionen verfälschen, egal ob sie für den Kontrollfluss wichtig sind, oder nicht. Zusätzlich behandelt das Modell noch Spezialfälle wie verlorene Updates.

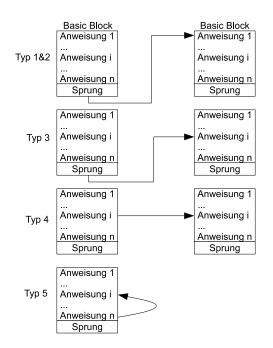

Die Wahrscheinlichkeit, dass sich ein Fehler auf den Kontrollfluss auswirkt, kann bis zu 78 % betragen [Mir92], weshalb für diesen Fall ein spezielles Fehlermodell entwickelt wurde. Es basiert auf der Annahme, dass sich ein Programm in sogenannte Basic Blocks (BB) einteilen lässt [Gol06, S. 63]. Ein BB besteht aus einer Ansammlung von Befehlen, welche bei der Ausführung nicht unterbrochen werden dürfen. Wird ein Block ausgeführt, wird immer bei der ersten Instruktion gestartet. Eine Sprungbedingung oder ein Unterprogrammaufruf darf sich nur am Ende des BB befinden. Der BB ohne den Sprungbefehl am Ende wird auch "Body" genannt, woraus sich zwei Sonderfälle ergeben. Befindet sich am Ende eines Block kein Sprung, stimmen BB und Body überein. Besteht der BB nur aus einem Sprung, existiert kein Body. Anhand dieses Soll-Verhaltens können fünf mögliche Fehlverhalten abgeleitet werden, dargestellt in Abb. 2.8.

Fehler in diesem Modell können entweder zu einem inter-Blockfehler oder intra-Blockfehler führen. Ein intra-Blockfehler führt dazu, dass Sprungquelle und Ziel sich in unterschiedlichen BB befinden (Typ 1 bis 4). Sprünge bei inter-Blockfehlern verlassen den gerade ausgeführten BB nicht (Typ

Abbildung 2.8: Fehlermodell für Basic Blocks [Gol06, S. 67]

5).

Typ 1 und 2 sind sich sehr ähnlich, bei beiden wird vom Ende eines BB zu dem Anfang eines anderen BBs gesprungen. Bei Typ 1 handelt es sich um einen verbotenen Sprung und bei Typ 2 um einen erlaubten, jedoch vom Soll-Programmfluss abweichenden Sprung. Ein Sprung vom Typ 3 führt von Endes des Quellblocks in die Mitte eines anderen BB und nicht an den Anfang. Geht der Sprung nicht vom Ende eines Blocks aus, sondern von dem Body, so handelt es sich laut Definition um einen Fehler Typ 4. Wird innerhalb des Bodys ein Sprung ausgeführt, welcher wieder in den Body des Eigenen führt, spricht man von einem Fehler Typ 5.

Mit den bereits vorgestellten Fehlermodellen lässt sich das Verhalten im Fehlerfall auf Systemebene gut darstellen. Gänzlich ignoriert werden jedoch Phänomene welche sich der digitalen Betrachtungsweise entziehen. Dazu Zählen die analogen Vorkommnisse, wie zum Beispiel Spannungsschwankungen, Jitter, Latch-up-Effekt<sup>3</sup> und viele mehr. Diese Effekte werden in der IEC 61508 [IEC10a, Teil 2, Tabelle A.1] aufgezählt und im Folgenden behandelt. Ziel ist es alle Anforderungen für eine Diagnostic Coverage (DC) von "hoch" zu erfüllen, wie diese für ein einkanaliges System gefordert ist.

Die Einträge in der Tabelle A.1 in der IEC 61508 [IEC10a] sind sehr generisch formuliert, da sie für eine Vielzahl von Sicherungssystemen gelten. Für die einzelnen Anwendungsfälle müssen die Angaben spezialisiert werden. Die Anforderungen dürfen nicht als Checkliste gesehen werden, viel wichtiger ist die Auseinandersetzung mit den Risiken und gezielte Gegenmaßnahmen zu Verbesserung des Gesamtsystems.

<sup>&</sup>lt;sup>3</sup>fehlerhafte Spannung am Halbleitersubstrat führt zur Zerstörung des Bauteils

### 2.3 Coded Processing

In der IEC 61508 [IEC10a, Teil 2, Tabelle A.4] [IEC10a, Teil 7, Clause A.3.4] wird die "codierte Verarbeitung" von sicherheitskritischen Daten mit dem Prädikat "hoher Diagnosedeckungsgrad" erwähnt, eine Erläuterung befindet sich im Folgenden.

Bei codierter Verarbeitung (englisch "Coded Processing") handelt es sich um Codes, welche den Nutzdaten hinzugefügt werden um eine Fehlererkennung zu ermöglichen. Optional kann anschließend eine Fehlerkorrektur durchgeführt werden. Ziel ist es, eine möglichst hohe Fehlererkennungswahrscheinlichkeit, unabhängig von der Hardware, zu erhalten. Zu allen Variablen im Benutzerprogramm wird redundante Information hinzugefügt, in welcher Form dies geschieht hängt von der Codierungsart ab. Alle Codierungen dieser Art beruhen auf der Idee den möglichen Zahlenraum einzuschränken. Es wird Information hinzugefügt, welche nur bestimmte Bitkombinationen erlaubt. Tritt im Speicher oder nach der Berechnung eine ungültige Kombination auf, kann von einem Bitfehler ausgegangen werden.

Der Unterschied von arithmetischen Codes, wie sie in dieser Arbeit vertieft behandelt werden, zu den anderen fehleraufdeckenden Codes besteht in der Speicherung und Verarbeitung der Prüfsumme. Bei den häufig verwendeten Prüfalgorithmen wie Cyclic Redundancy Check (CRC) oder Parity-Bit ist die Prüfsumme von den Nutzdaten getrennt im Speicher und wird ebenso getrennt, in einem zusätzlichen Rechenschritt, erzeugt. Man nennt diese Codes auch systematisch und separierbar [Gar66]. Bei separierbaren Codes werden die Nutzdaten getrennt von den Prüfdaten berechnet. Ein Code ist systematisch, wenn bei einer Datenbreite von n Bits k (wobei k < n) für die Prüfdaten verwendet werden und (n - k) Bitstellen für die Nutzdaten verbleiben [Rao72]. Bei arithmetischen Codes handelt es sich um einen nicht separierbaren, nicht systematischen Code, das heißt Nutzdaten und Prüfdaten werden in dem gleichen Rechenschritt erstellt. Die Prüfsumme wird mit den Nutzdaten verflochten und gleichzeitig bei jeder Weiterverarbeitung aktualisiert.

#### Relevante Forschungs- und Entwicklungsarbeiten

Das Gebiet der mathematischen Codierung für erhöhte Fehleraufdeckung bei Berechnungen wurde in den Anfängen des Computerzeitalters entwickelt, jedoch das volle Potential bisher nicht ausgeschöpft. David Brown legt den ersten Stein für codierte Verarbeitung im Jahr 1960 [Bro60]. In der Luftfahrt wurde das Konzept der codierten Verarbeitung ebenfalls untersucht [Liu72]. Die Gewichtsersparnis durch Fehlererkennung in Software anstatt redundanter Hardware ist im Flugverkehr ein großer Vorteil. In der weiteren Entwicklung wurde kodierte Verarbeitung für die Signaltechnik in Eisenbahnsystemen eingesetzt [For89]. Die hohe Fehleraufdeckung ermöglicht einen Einsatz in höchst sicherheitskritischen Systemen, wie sie Züge darstellen [Cla09].

Ein ausführliches Werk zu Coded Processing für Systeme der Gegenwart publizierte Schiffel [Sch11] von der Technischen Universität Dresden. In der Arbeit wird der Schwerpunkt auf AN-Codes und deren Erweiterungen gelegt. Es wurden zwei Software-Tools entwickelt, welche dem Programmierer die Arbeit des händischen Codierens abnehmen. Einmal wird das Programm in einem Interpreter ausgeführt, welcher zur Laufzeit die Codierung vornimmt. In einem zweiten Tool wird ein Compiler modifiziert, damit dieser zur Compilezeit die Codierung vornimmt. Mit diesen Tool werden mehre Beispielprogramme erstellt und die Fehleraufdeckung durch Fehlerinjektion sowie die Performance gemessen. Während in Schiffels Arbeit theoretisch das Gebiet der

Codierungen erarbeitet wird, wird in dieser Arbeit ein vollständiges Sicherheitskonzept im Einklang mit der IEC 61508 [IEC10a] entwickelt, welches nur als einen Baustein von vielen codierte Verarbeitung zur Sicherung enthält.

In der industriellen Sicherheitstechnik wurde Coded Processing bisher nur wenig Aufmerksamkeit geschenkt. Eine Ursache dafür ist der gesteigerte Ressourcenverbrauch verglichen mit uncodierter Berechnung [Sch11, S. 166]. Mit fortschreitender Rechengeschwindigkeit der CPUs werden Lösungen, basierend auf Coded Processing, attraktiver.

#### **Arithmetische Codes**

Arithmetische Codes besitzen die Eigenschaft trotz der Anwendung einer arithmetischen Operation erhalten zu bleiben. Mit dieser Eigenschaft können Rechenfehler, welche während einer Operation aufgetreten sind, detektiert werden. Man sagt die Codierung bleibt erhalten, wenn für die codierte Operation  $\oplus$  mit den codierten Variablen X', Y' und die uncodierte Operation + mit den uncodierten Variablen X, Y Eq. 2.2 gilt [Kor07, S. 74].

$$X' \oplus Y' = (X+Y)' \tag{2.2}$$

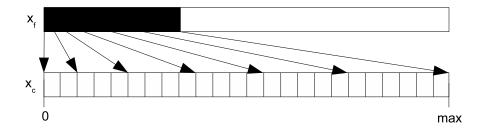

Die einfachste Form der arithmetische Codes, kurz "AN-Codes", basieren im ersten Schritt auf dem Prinzip, jede Variable  $x_f$  der Nutzdaten mit der Konstante A zu multiplizieren. Für A kann eine Ganzzahl frei gewählt werden (siehe Abschnitt 2.3), jedoch ist zu beachten, dass die Wahl die Fehleraufdeckungseigenschaften beeinflusst. Die Multiplikation von A mit der Variable  $x_f$  führt zu der codierten Variable 2.3.

$$x_c = A \cdot x_f. \tag{2.3}$$

Diesen Vorgang nennt man Codieren, wird aus  $x_c$  wiederum  $x_f$  extrahiert, spricht man vom Decodieren. Die Variable wird vor der ersten Berechnung codiert und erst am Ende des Steuerungszyklus dekodiert. Somit müssen die Ein- und Ausgangseinheiten des Sicherungssystems nicht über die Codierung informiert sein.

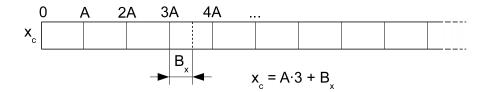

Die Variable  $x_f$  wird auf den ganzen verfügbaren Zahlenbereich verteilt, dies ist in Abb. 2.9 ersichtlich. Somit ist nicht mehr jede Zahl erlaubt, sondern nur mehr Vielfache von A. Bei der Wahl eines passenden As ist zu beachten, dass der verfügbare Zahlenbereich in der CPU nicht überschritten wird. Andererseits verlangt eine hohe Fehlererkennung ein großes A. Näheres zu einer optimalen Wahl von A wird in Teil 2.3 diskutiert. Es steht somit für die Variable  $x_f$  nicht der ganze vorhandene Zahlenbereich für die Nutzdaten zur Verfügung, sondern  $x_{fmax} = \frac{2^n}{A}$ , wobei n die Bitbreite der CPU angibt. Um die Auswirkung der Reduktion der nutzbaren Bitbreite gering zu halten, empfiehlt sich mindest eine 64 Bit CPU-Architektur, bzw. der Einsatz der SSE-Einheit, wie sie in allen aktuellen CPUs vorhanden ist. Diese kann Variablen mit ein Bitbreite von bis zu 128 Bit verarbeiten. Zusätzlich verfügen Intel CPUs mit Sandy Bridge Mikroarchitektur über eine 256 Bit breite "Vector Extension" [Int13, S. 2-14].

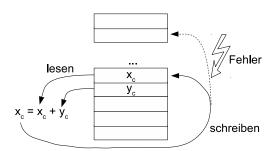

Die Rechnung mit AN-codierten Variablen ist trivial. Die Addition zweier codierter Variablen  $x_c$  und  $y_c$  berechnet sich wie folgt:

$$z_c = x_c + y_c = A \cdot x_f + A \cdot y_f = A \cdot (x_f + y_f) \tag{2.4}$$

Die Probe, ob diese Berechnung korrekt war, lässt sich mittels einer Module-Operation durchführen. Wenn die Bedingung 2.5 erfüllt ist, handelt es sich bei dem Ergebnis, wie auch bei den Ausgangsoperanden, um ein Vielfaches von A.

$$mod\left(A \cdot \left(x_f + y_f\right), A\right) = 0 \tag{2.5}$$

Abbildung 2.9: Prinzip der AN-Codierung

Die Wahrscheinlichkeit bei AN-codierten Daten einen Fehler aufzudecken ergibt sich als 1/A [Oze92]. Dies ist die Wahrscheinlichkeit, dass bei einem zufälligen Fehler ein anderes gültiges Codewort generiert wird. Bei der Addition und Subtraktion handelt es sich um die einfachsten Rechenoperationen mit codierten Variablen. Bei einer Multiplikation muss das Ergebnis vor der weiteren Verwendung korrigiert werden, da ein  $A^2$  Term entsteht, dieser muss mit einer Division durch A entfernt werden. Soll eine Division von codierten Zahlen durchgeführt werden, muss die Anpassung einer der Variablen vor der eigentlichen Division durchgeführt werden. Würden zwei AN-codierte Zahlen dividiert, wäre das Ergebnis uncodiert. Dieser Zustand muss während der ganzen Berechnung vermieden werden, denn er öffnet die Möglichkeit für unentdeckbare Fehler. Abhilfe kann geschaffen werden, wenn der Dividend vor der Division mit A multipliziert wird. Die Multiplikation führt jedoch zu einem unerwünschten Nebeneffekt: da die codierte Verarbeitung nur mit ganzzahligen Variablen durchgeführt werden kann, werden bei der Division, sofern Kommastellen entstünden, diese abgeschnitten. Somit kann ein Fall eintreten, in dem Eq. 2.6 gilt.

$$A \cdot Int\left(\frac{A \cdot x_c}{A \cdot y_c}\right) \neq Int\left(\frac{A \cdot A \cdot x_c}{A \cdot y_c}\right) \tag{2.6}$$

Wobei links in Eq. 2.6 die verbotene Division steht, da sich die As in der Klammer kürzen und für die Variable vorübergehend uncodiert vorhanden ist. Rechts ist die zu verwendende Division hinzugefügt, in welcher die Nutzdaten zu keinem Zeitpunkt uncodiert vorhanden sind. Wie sich aber zeigt, führt die rechte, erlaubte Division zu falschen Ergebnissen.

Um dies zu veranschaulichen, ein Beispiel:

Angenommen  $A=5, x_f=11$  und  $y_f=7$  daraus ergibt sich aus dem linken Teil von 2.6 mit  $x_c=55, y_c=35$  die Division  $5\cdot \left(\frac{55}{35}\right)=5\cdot (1)=5$ . In der Klammer steht 1, da die Division 55/35 in Integer 1 ergibt. Wird der rechte Teil von Eq. 2.6 berechnet, ergibt sich  $\frac{5\cdot 55}{35}=7$ , wenn die Nachkommastellen wieder verworfen werden. Man erkennt durch die unterschiedliche Stelle im Rechengang, an welcher die Nachkommastellen verworfen wurden, dass zwei unterschiedliche Ergebnisse entstehen. Würde man die Division uncodiert durchführen, wäre  $\frac{11}{7}=1$  das richtige Ergebnis. Wie sich zeigt, wäre bei der Probe die Division links mod(5,5)=0 korrekt und rechts mit der für Coded Processing optimierten Division mod(7,5)=2 falsch. Es ist somit erneut eine Korrektur notwendig. Dazu muss vom Dividend vor der Division um  $A \cdot mod(x_c, y_c)$  subtrahiert werden, wie in 2.7 ersichtlich.

$$\frac{x_f}{y_f} = Int\left(\frac{A^2 \cdot x_c - A \cdot mod(x_c, y_c)}{A \cdot y_c}\right)$$

(2.7)

Vorteil der AN-codierten Berechnung ist die vergleichsweise einfache Implementierbarkeit sowie die Vielzahl an möglichen Rechenoperationen. Ein Schwachpunkt hingegen ist die Erkennung falscher Operanden oder Operatoren. Wird beispielsweise der Operator vertauscht und anstatt

einer Addition eine Subtraktion durchgeführt, ist das Ergebnis weiterhin ein gültiges Codewort und die Probe durch Modulorechnen erkennt den Fehler nicht. Ebenso ist es durch die Probe nicht ersichtlich, ob ein falscher, AN-codierter Wert aus dem Speicher geladen und für die Berechnung verwendet wurde. Um dies zu erkennen muss die Formel 2.3 um eine weitere Konstante erweitert werden.

Wird der AN-Code um eine Konstante erweitert, spricht man von dem ANB-Code, welcher sich auf David Brown [Bro60] zurückführen lässt [Gar66]. Das B wird zu der AN-codierten Variable hinzuaddiert und wird Signatur genannt.

$$x_c = A \cdot x_f + B_x \tag{2.8}$$

$$1 < B < A \tag{2.9}$$

Für die Signatur gilt die Bedingung 2.9. Entgegen der Festlegung der unteren Grenze auf Null [Sch11, S. 33] zeigt sich Eins als bessere Wahl, da Eins das neutrale Element der Multiplikation darstellt (weiteres siehe in Anschnitt 4.1).

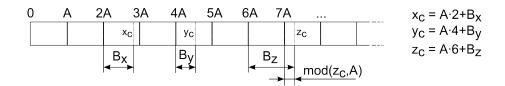

Das hinzugefügte B ist als Offset zu sehen, welcher die codierte Variable im Bereich zwischen  $A \cdot x_f$  und  $(A+1) \cdot x_f$  verschiebt. Veranschaulicht für  $x_f = 3$  wird dieses Konzept in Abb. 2.10. Durch die Verschiebung um  $B_x$  wird jede Variable einmalig. Werden zwei gleiche  $x_f$  codiert,

Abbildung 2.10: Prinzip der ANB-Codierung

müssen unterschiedliche Bs verwendet werden. Somit schränkt ein zu kleines A die zur Verfügung stehenden Signaturen ein, woraus folgt, dass die Berechnung niemals mehr als A-2 Variablen verwenden darf.

Diese Codierung ermöglicht es, in der Probe zusätzlich zu kontrollieren, ob die richtigen Variablen verarbeitet wurden. Eine Addition ergibt sich wie in 2.11 aufgeführt.

$$z_c = x_c + y_c = A \cdot x_f + B_x + A \cdot y_f + B_y \tag{2.10}$$

$$= A \cdot (x_f + y_f) + (B_x + B_y) \tag{2.11}$$

Die Probe zur Kontrolle der Berechnung ist wieder durch eine Modulooperation durchzuführen. Verlief die Berechnung korrekt, muss 2.12 erfüllt sein.

$$mod(A \cdot (x_f + y_f) + B_x + B_y, A) = B_x + B_y$$

(2.12)

Man erkennt, dass die fälschliche Vertauschung eines Operanden durch eine andere codierte Variable an dieser Stelle auffallen muss, da für jede Variable mit einer anderen Signatur beaufschlagt wird. Das Plus der Addition spiegelt sich ebenfalls in der Probe wider. So kann in einem Rechenschritt überprüft werden, ob auch der richtige Operator verwendet wurde. Bei einer Subtraktion  $x_c - y_c$  muss die Modulooperation gleich  $B_x - B_y$  sein. Neben dem Vorteil der Erkennung von

falschen Operanden und Operatoren entstehen bei der Durchführung von Multiplikationen und Divisionen ANB-codierter Variablen Probleme.

Werden zwei codierte Variablen multipliziert, sind im Ergebnis die A und B Terme vermischt vorhanden.

$$z_c = x_c \cdot y_c = (A \cdot x_f + B_x) \cdot (A \cdot y_f + B_y)$$

$$z_c = A^2 \cdot x_f \cdot y_f + A \cdot x_f \cdot B_y + A \cdot y_f \cdot B_x + B_x \cdot B_y$$

(2.13)

Anstatt des gewünschten Ergebnisses 2.14, mit welchem eine Probe einfach durchgeführt und durch Decodierung auf die Variablen zugegriffen werden könnte, ergibt sich nach der Multiplikation Eq. 2.13, in welcher Codierungsparameter unterschiedlicher Variablem verknüpft sind.

$$z_c = A \cdot (x_f \cdot y_f) + (B_x \cdot B_y) \tag{2.14}$$

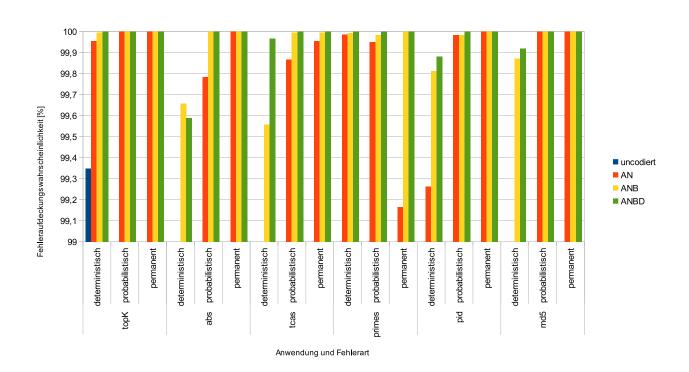

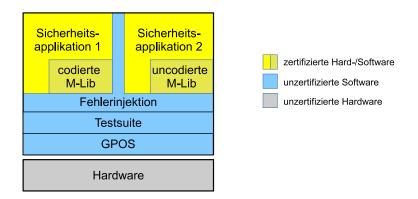

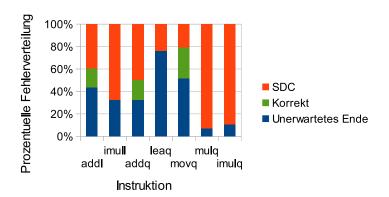

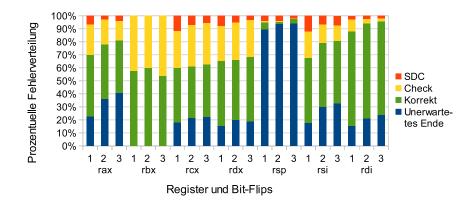

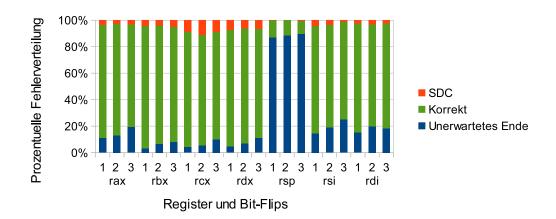

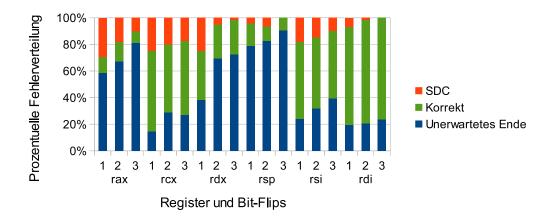

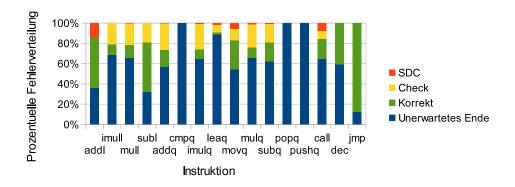

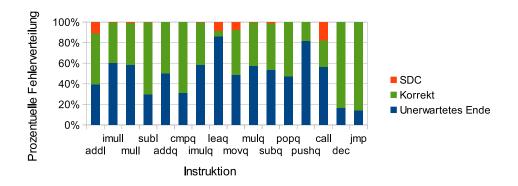

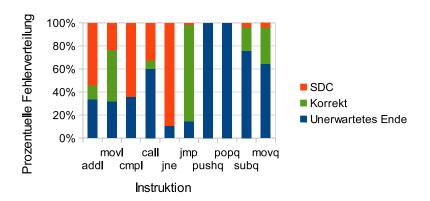

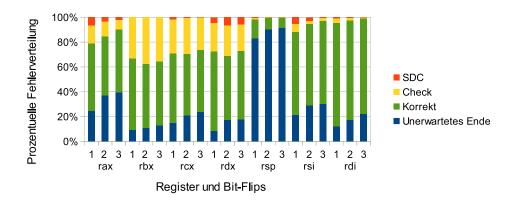

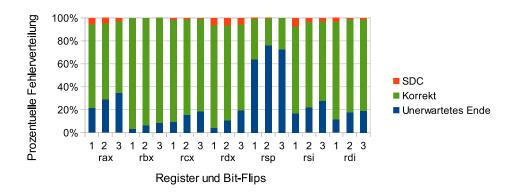

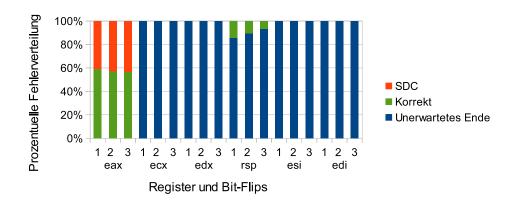

Die Korrektur, mit welcher 2.13 auf die Form 2.14 gebracht wird benötigt einen umfassenden Eingriff in das codierte Ergebnis. Die Terme  $A \cdot x_f \cdot B_y$ ,  $A \cdot y_f \cdot B_x$  und  $B_x \cdot B_y$  müssen durch eine Subtraktion entfernt und  $A \cdot B_x \cdot B_y$  hinzuaddiert werden. Eine abschießende Division durch A führt zu der gewünschten Form. Die Division ANB-codierter Variablen ist nicht möglich, diese muss entweder durch eine Subtraktion in Software nachgebildet werden, oder die Variablen werden vor der Division von ANB zu AN-codiert. Dieses Entfernen der Signatur erhöht die Wahrscheinlichkeit für unentdeckte Fehler und muss für höchste Fehleraufdeckung zusätzlich abgesichert werden.