http://www.ub.tuwien.ac.at/eng

FAKULTÄT FÜR INFORMATIK

**Faculty of Informatics**

# Efficient Interfacing Between Timing Domains

## DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

## Technische Informatik

eingereicht von

## Robert Kutschera

Matrikelnummer 0426125

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Ao.Univ.-Prof. Dipl.-Ing. Dr. techn. Andreas Steininger Mitwirkung: Univ.-Ass. Dipl.-Ing. Dr. techn. Thomas Polzer Univ.-Ass. Dipl.-Ing. Robert Najvirt

Wien, 02.06.2014

(Unterschrift Verfasser)

(Unterschrift Betreuung)

#### **Faculty of Informatics**

# Efficient Interfacing Between Timing Domains

## MASTER'S THESIS

submitted in partial fulfillment of the requirements for the degree of

## **Diplom-Ingenieur**

in

## **Computer Engineering**

by

## **Robert Kutschera**

Registration Number 0426125

to the Faculty of Informatics at the Vienna University of Technology

Advisor: Ao.Univ.-Prof. Dipl.-Ing. Dr. techn. Andreas Steininger Assistance: Univ.-Ass. Dipl.-Ing. Dr. techn. Thomas Polzer Univ.-Ass. Dipl.-Ing. Robert Najvirt

Vienna, 02.06.2014

(Signature of Author)

(Signature of Advisor)

# Erklärung zur Verfassung der Arbeit

Robert Kutschera Untere Weißgerberstraße 53-59/4/15, 1030 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

## Abstract

When interacting within a closed timing domain the timing requirements (esp. setup/hold requirements) of all stateful elements (memory) in different systems or components can be safely met. Examples are a globally synchronous clock domain or an asynchronous handshake domain. Often it is, however, necessary to exchange signals between two (or more) such timing domains, as within a GALS system (globally asynchronous locally synchronous) each component/subsystem has its own timing domain. This exchange of data inevitably leads to metastability problems at the interfaces. To prevent or handle the problems with metastability of stateful elements at the interfaces of a system synchronizers are needed. In this work a survey of the different existing interfacing solutions of synchronous and asynchronous systems, including all levels of synchrony (mesochronous, plesiochronous, heterochronous, rational) and the different handshake-protocols (2-phase, 4-phase) of asynchronous system design is created. In the survey the interfacing solutions are compared according to criteria such as MTBF (Mean Time Between Failures), throughput, latency, assumptions on their functionality. From this a suitable and efficient solution is chosen for each possible system combination between synchronous and asynchronous systems, to further make a general reference book about interfacing solutions.

## Kurzfassung

Die Kommunikation zwischen Elementen mit deren Setup/Hold- Anforderungen (Speicherelemente) kann innerhalb einer geschlossenen Timing Domain (Bereich mit einheitlichem Zeitverständnis, z.B.: Systemtakt) sicher bewerkstelligt werden. Oft ist es aber notwendig Signale zwischen verschiedenen Timing Domains auszutauschen, wie im Falle eines GALS-Systems (Globally Asynchronous Locally Synchronous) bei dem die verschiedenen Systemkomponenten jeweils unterschiedliche Timing Domains besitzen. Diese Übertragungen von Signalen können zu Metastabilitätsproblemen an den Schnittstellen führen. Um diesen Metastabilitätsproblemen entgegenzuwirken müssen die Signale an der Empfängerseite in die dort herrschende Timing Domain synchronisiert werden. Diese Aufgabe bewerkstelligen Synchronizer.

In der vorliegenden Arbeit wird als erster Schritt ein Überblick über bestehende Interfacing-Lösungen erstellt um diese durch analytische Modelle vergleichen zu können. Dazu werden verschiedene Vergleichskriterien wie MTBF (Mean Time Between Failures), Durchsatz und Verzögerung herangezogen. Dabei werden die Interface-Typen von synchronen Systemen (z.B. mesochronous, plesiochronous, heterochronous) und asynchronen Systemen (verschiedene Handshake-Protokolle) betrachtet. Nach dem Vergleich der gesammelten Lösungen kann eine Identifizierung geeigneter Lösungen für die unterschiedlichen Kategorien vorgenommen werden und so ein Nachschlagewerk verfasst werden.

# Contents

| Co | Contents                 |                             |                                                                 |                              |  |  |

|----|--------------------------|-----------------------------|-----------------------------------------------------------------|------------------------------|--|--|

| 1  | 1.1<br>1.2<br>1.3<br>1.4 | Proble:<br>Metho<br>Structu | ation                                                           | <b>1</b><br>1<br>2<br>3<br>3 |  |  |

| 2  |                          | •                           | nchrony                                                         | 5                            |  |  |

|    | 2.1                      | Classif                     | fication                                                        | 5                            |  |  |

| 3  | Mes                      | ochrono                     | ous Synchronizers                                               | 9                            |  |  |

|    | 3.1                      |                             | Concepts                                                        | 9                            |  |  |

|    | 3.2                      |                             | ed Descriptions                                                 | 11                           |  |  |

|    |                          | 3.2.1                       | Brute-Force Synchronizer                                        | 11                           |  |  |

|    |                          | 3.2.2                       | Delay-line synchronizer                                         | 11                           |  |  |

|    |                          | 3.2.3                       | Two-Register Synchronizer                                       | 13                           |  |  |

|    |                          | 3.2.4                       | Three Element FIFO Synchronizer                                 | 13                           |  |  |

|    |                          | 3.2.5                       | Adaptive Synchronization                                        | 15                           |  |  |

|    |                          | 3.2.6                       | Low-Latency and Low-Overhead Mesochronous Synchronizer          | 17                           |  |  |

|    |                          | 3.2.7                       | Four-Stage Mesochronous Synchronizer                            | 19                           |  |  |

| 4  | Rati                     | ochron                      | ous Synchronizers                                               | 21                           |  |  |

|    | 4.1                      | Basic (                     | Concepts                                                        | 21                           |  |  |

|    | 4.2                      | Detaile                     | ed Descriptions                                                 | 22                           |  |  |

|    |                          | 4.2.1                       | Rational Clocking                                               | 22                           |  |  |

|    |                          | 4.2.2                       | A Flexible Communication Scheme for Rational-Related Clock Fre- |                              |  |  |

|    |                          |                             | quencies                                                        | 26                           |  |  |

| 5  | Ples                     | iochron                     | ous Synchronizers                                               | 29                           |  |  |

|    | 5.1                      |                             | Concepts                                                        | 29                           |  |  |

|    | 5.2                      | *                           |                                                                 |                              |  |  |

|    |                          | 5.2.1                       | Plesiochronous FIFO Synchronizer                                | 30                           |  |  |

|    |                          | 5.2.2                       | Periodic Asynchronous Synchronizer                              | 32                           |  |  |

|    |                          |                             |                                                                 |                              |  |  |

|   |      | 5.2.3<br>5.2.4 | Low-Latency Plesiochronous Data Retiming                           | 33<br>35  |

|---|------|----------------|--------------------------------------------------------------------|-----------|

| 6 | Sync | hronize        | ers for Systems with Uncorrelated Clocks                           | 37        |

|   | 6.1  | Basic C        | Concepts                                                           | 37        |

|   | 6.2  | Detaile        | d Descriptions                                                     | 40        |

|   |      | 6.2.1          | Two Flip-Flop Synchronizer                                         | 40        |

|   |      | 6.2.2          | A Robust Synchronizer                                              | 41        |

|   |      | 6.2.3          | Register-Communication Between Mutually Asynchronous Domains .     | 43        |

|   |      | 6.2.4          | Fast Universal Synchronizer                                        | 46        |

|   |      | 6.2.5          | Micropipelines                                                     | 48        |

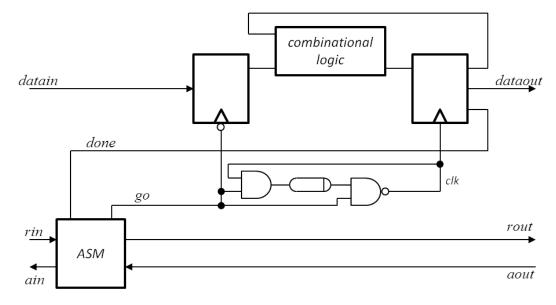

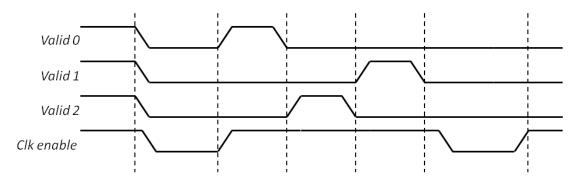

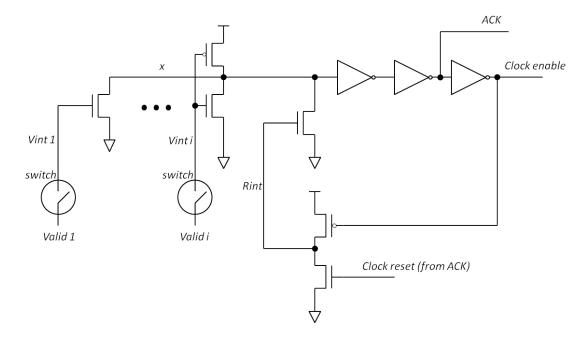

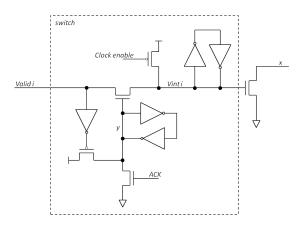

|   |      | 6.2.6          | High Rate Data Synchronization in GALS SoCs                        | 50        |

|   |      | 6.2.7          | Module with Stoppable Clocks                                       | 54        |

|   |      | 6.2.8          | Asynchronous Interlocked Pipelined CMOS Circuits                   | 55        |

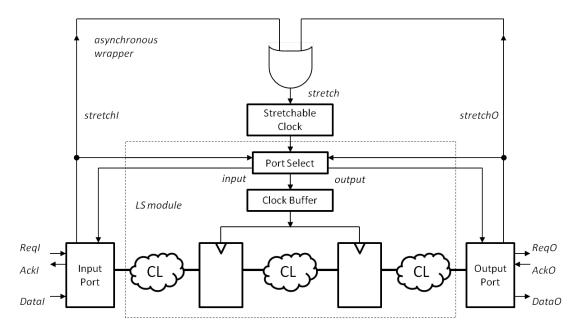

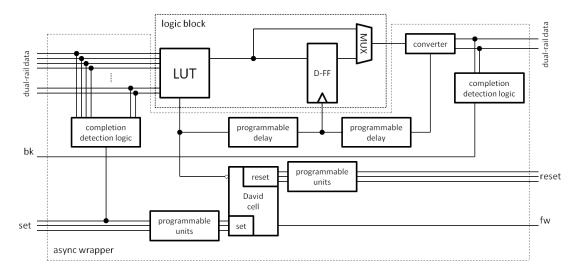

|   |      | 6.2.9          | Asynchronous Wrapper for Heterogeneous Systems                     | 57        |

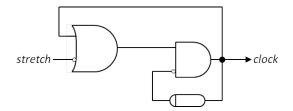

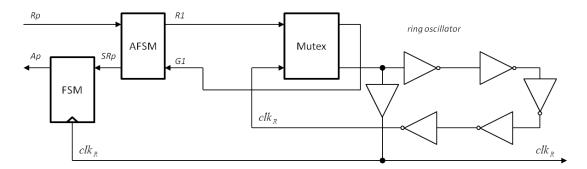

|   |      | 6.2.10         | Pausible Clocking: A First Step Toward Heterogeneous Systems       | 59        |

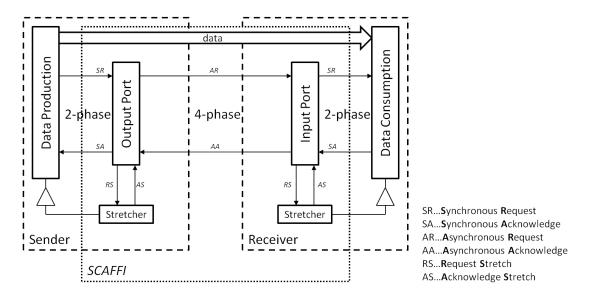

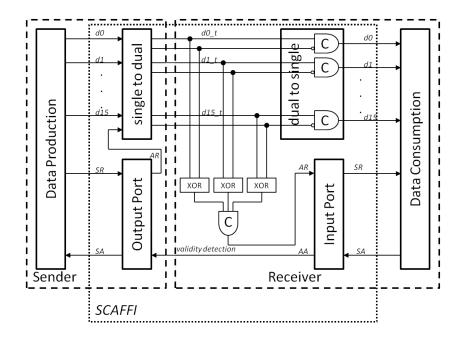

|   |      | 6.2.11         | SCAFFI: An Intrachip FPGA Asynchronous Interface Based on Hard     |           |

|   |      |                | Macros                                                             | 60        |

|   |      |                | Point to Point GALS Interconnect                                   | 63        |

|   |      | 6.2.13         | Interfacing Synchronous and Asynchronous Modules within a High-    |           |

|   |      |                | speed Pipeline                                                     | 66        |

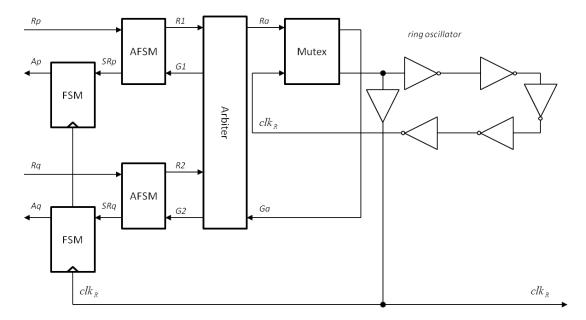

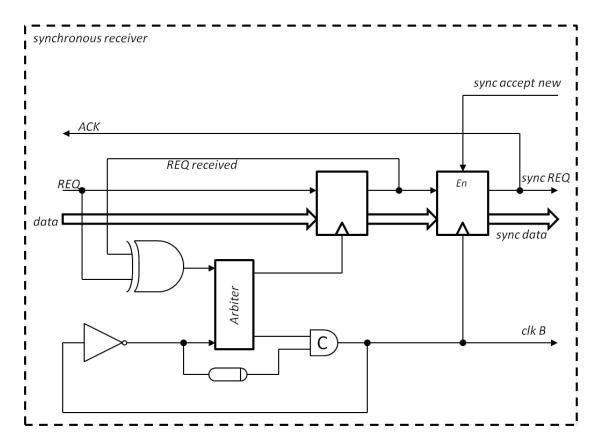

|   |      | 6.2.14         | Using Stoppable Clocks to Safely Interface Asynchronous and Syn-   |           |

|   |      |                | chronous Subsystems                                                | 69        |

|   |      |                | A Synchronizer Design Based on Wagging                             | 72        |

|   |      | 6.2.16         | A Fast Resolving BiNMOS Synchronizer for Parallel Processor Inter- | - 4       |

|   |      | ( ) 17         |                                                                    | 74        |

|   |      | 6.2.17         |                                                                    | 77        |

|   |      |                | Robust Interfaces for Mixed-Timing Systems                         | 77        |

|   |      |                | Pipeline Synchronization                                           | 81        |

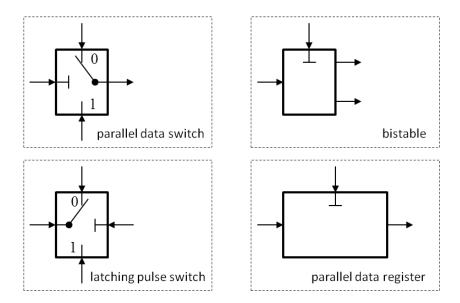

|   |      | 6.2.20         | The Even/Odd Synchronizer                                          | 82        |

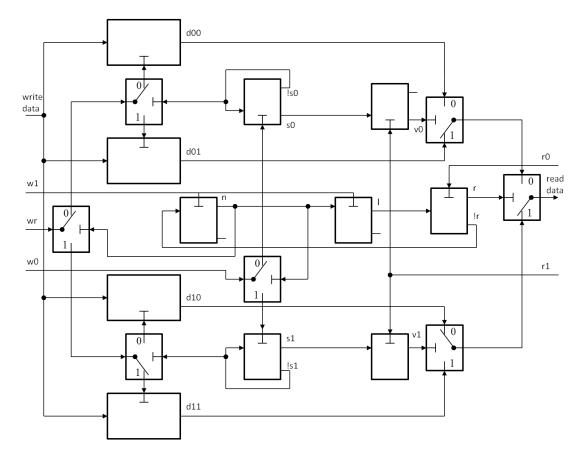

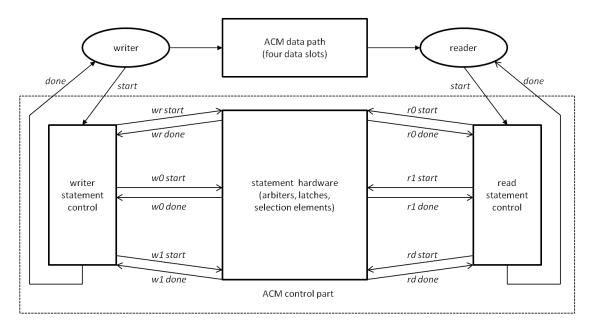

|   |      | 6.2.21         | Four-slot Fully Asynchronous Communication Mechanism               | 84        |

|   |      |                | Asynchronous Communication Mechanisms Using Self-timed Circuits    | 88<br>90  |

|   |      |                | Implementing a STARI Chip                                          |           |

|   |      |                | Efficient Self-Timed Interfaces for Crossing Clock Domains         | 92<br>94  |

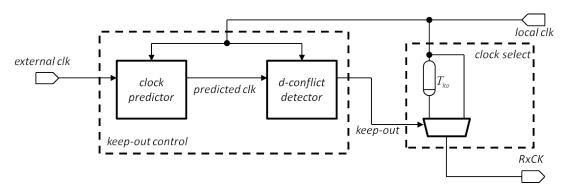

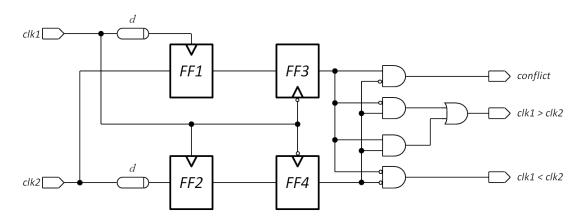

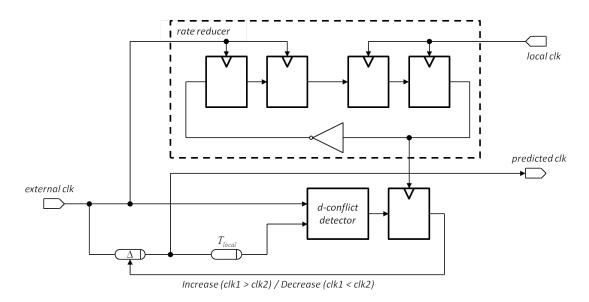

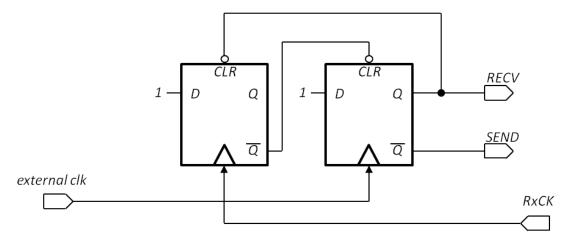

|   |      |                | A Predictive Synchronizer for Periodic Clock Domains               | 94<br>98  |

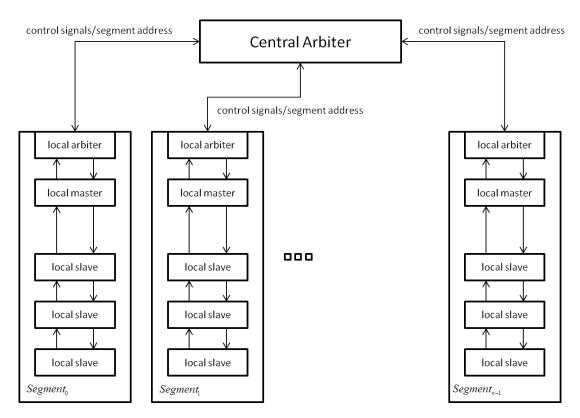

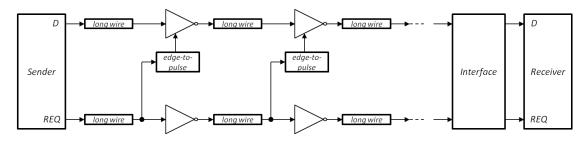

|   |      |                | On-Chip Segmented Bus: A Self-timed Approach                       | 98<br>100 |

|   |      | 0.2.27         | On-Chip Segmented Bus. A Sen-timed Approach                        | 100       |

| 7 | Sync | hronize        | ers for Self-Timed Systems                                         | 103       |

|   | 7.1  |                | Concepts                                                           | 103       |

|   | 7.2  | Detaile        | d Descriptions                                                     | 104       |

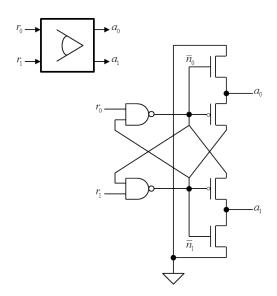

|   |      | 7.2.1          | Arbiter                                                            | 104       |

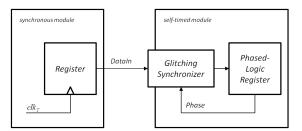

|   |      | 7.2.2          | Glitching Synchronizer                                             | 105       |

|   |      | 7.2.3          | Synchronization and Conversion Circuit                             | 106       |

|   |                    | 7.2.4                                               | A FIFO Ring Performance Experiment                                                                                                                                                                                                  | 108                                    |  |  |

|---|--------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|

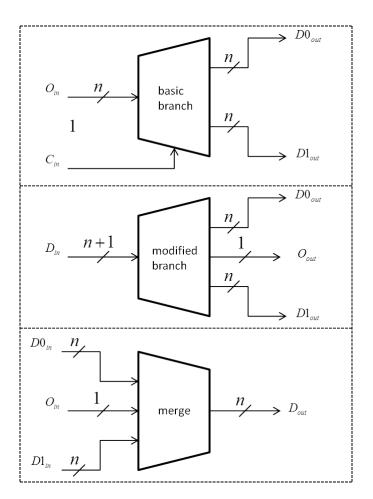

|   |                    | 7.2.5                                               | A Modular Synchronizing FIFO for NoCs                                                                                                                                                                                               | 110                                    |  |  |

|   |                    | 7.2.6                                               | Chain: A Delay-Insensitive Chip-Area Interconnect                                                                                                                                                                                   | 114                                    |  |  |

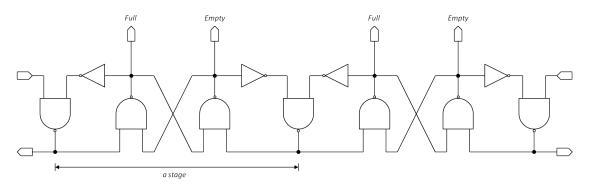

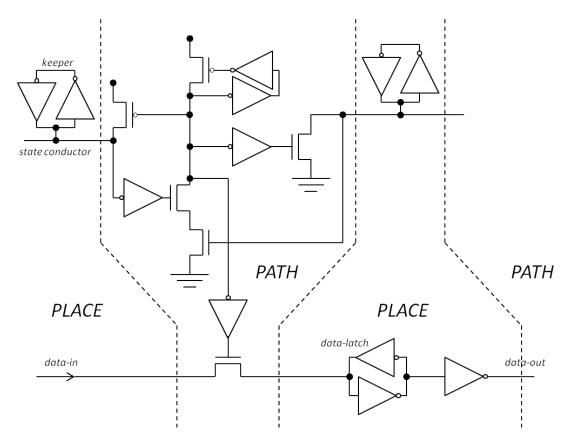

|   |                    | 7.2.7                                               | GasP: A Minimal FIFO Control                                                                                                                                                                                                        | 119                                    |  |  |

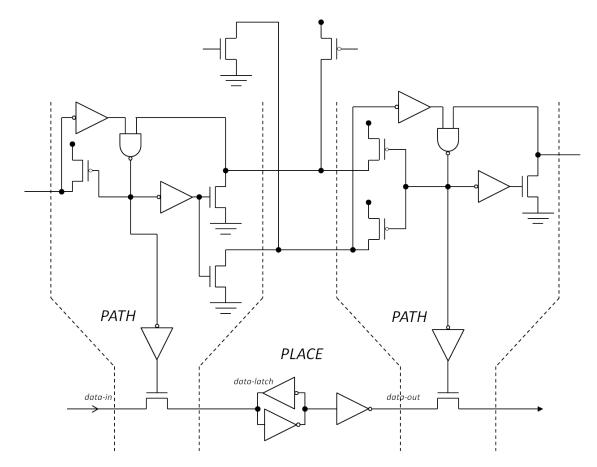

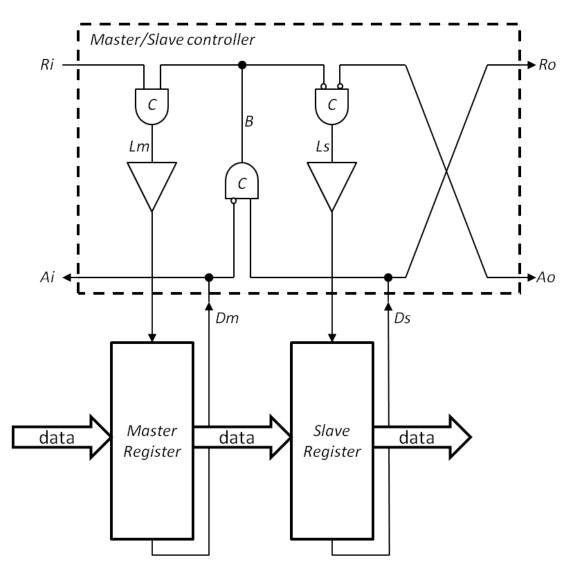

|   |                    | 7.2.8                                               | A Doubly-Latched Asynchronous Pipeline                                                                                                                                                                                              | 122                                    |  |  |

| 8 | Interconnects      |                                                     |                                                                                                                                                                                                                                     |                                        |  |  |

|   | 8.1                | Detaile                                             | d Descriptions                                                                                                                                                                                                                      | 125                                    |  |  |

|   |                    | 8.1.1                                               | Surfing Interconnect                                                                                                                                                                                                                | 125                                    |  |  |

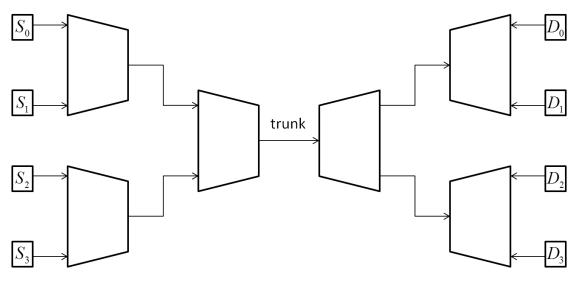

|   |                    | 8.1.2                                               | Practical Asynchronous Interconnect Network Design                                                                                                                                                                                  | 127                                    |  |  |

|   |                    | 8.1.3                                               | Asynchronous Current Mode Serial Communication                                                                                                                                                                                      | 128                                    |  |  |

|   |                    | 8.1.4                                               | Asynchronous FPGA Architecture with Distributed Control                                                                                                                                                                             | 130                                    |  |  |

|   |                    | 8.1.5                                               | FLEETzero: An Asynchronous Switching Experiment                                                                                                                                                                                     | 131                                    |  |  |

|   |                    |                                                     |                                                                                                                                                                                                                                     |                                        |  |  |

| 9 | Quie               | ck Refei                                            | rence Guide                                                                                                                                                                                                                         | 135                                    |  |  |

| 9 | <b>Quio</b><br>9.1 |                                                     | rence Guide                                                                                                                                                                                                                         | <b>135</b><br>135                      |  |  |

| 9 | -                  |                                                     | of Categories                                                                                                                                                                                                                       |                                        |  |  |

| 9 | -                  | Tables                                              | of Categories                                                                                                                                                                                                                       | 135                                    |  |  |

| 9 | -                  | Tables<br>9.1.1                                     | of Categories                                                                                                                                                                                                                       | 135<br>135                             |  |  |

| 9 | -                  | Tables<br>9.1.1<br>9.1.2                            | of Categories                                                                                                                                                                                                                       | 135<br>135<br>137                      |  |  |

| 9 | -                  | Tables<br>9.1.1<br>9.1.2<br>9.1.3                   | of CategoriesTable of Mesochronous SynchronizersTable of Plesiochronous SynchronizersTable of Synchronizers for Systems with Uncorrelated ClocksTable of Ratiochronous Synchronizers                                                | 135<br>135<br>137<br>138               |  |  |

| 9 | -                  | Tables<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4          | of CategoriesTable of Mesochronous SynchronizersTable of Plesiochronous SynchronizersTable of Synchronizers for Systems with Uncorrelated Clocks                                                                                    | 135<br>135<br>137<br>138<br>145        |  |  |

| - | 9.1                | Tables<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5 | of CategoriesTable of Mesochronous SynchronizersTable of Plesiochronous SynchronizersTable of Synchronizers for Systems with Uncorrelated ClocksTable of Ratiochronous SynchronizersTable of Asynchronous (Self-timed) Synchronizer | 135<br>135<br>137<br>138<br>145<br>146 |  |  |

## CHAPTER

## Introduction

## 1.1 Motivation

Most systems are not self-contained, thus communicate with their environment, which can be either another system or an external sensor or else. Often new incoming data occurs at arbitrary points in time (seen from receiver's point of view), so asynchronously to the local timing (clock or step in computation cycle). If a change on the data signal occurs within a time interval  $T_w$ around a sampling clock edge that triggers a memory element, it may latch an undefined voltage level and thus cannot resolve to one of the defined states within bounded time.

This effect is called *metastability*. Inside a memory element the signal wobbles around half  $V_{DD}$  or oscillates during metastability [28]. The logical value has not settled yet inside the memory element, a little disturbance (e.g. noise) is sufficient for the memory element to resolve to a defined but arbitrary value (this may cause erroneous or byzantine behaviour). It is safe to say, that if this takes longer than the clock-to-output delay for the memory element to resolve to the expected value one can conclude that it became metastable. To avoid metastable states within memory elements like flip-flops or latches, the incoming data has to be synchronized to the local timing (clocked or self-timed). Hence synchronizers are required at borders of timing domains. The design of synchronizers for different application demands has long been, and still is, an area of active research, and a wealth of approaches have been published. The focus of this thesis is to produce a guide that helps one to make the right decision on the choice of synchronizer that is perfectly suitable for a particular interface between different timing domains.

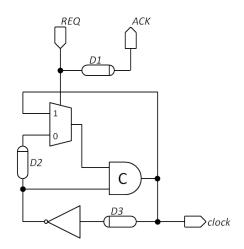

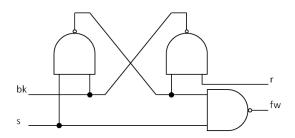

In some degree synchronizers are also needed in self-timed systems, because metastability is also present in asynchronous (self-timed) systems in case of external failure or interfacing to other timing domains. In contrast to clocked systems metastable states are based upon different reasons and apply to arbiters and Muller C-Elements. Arbiters are used to synchronize incoming data to the computational cycle of a self-timed system, they grant access to the system to an external request or prevent interrupts due to incoming requests. The arbiter may suffer from the *arbiter problem*, where it can not decide on a correct order of access to the single source within bounded time if the requests are not sufficiently separated in time.

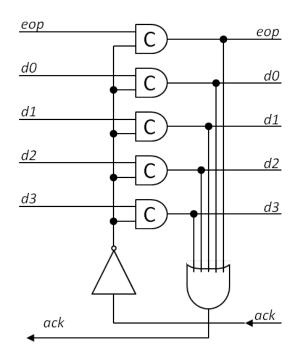

The Muller C-Element forms the basic building block of a control path in an asynchronous circuits, e.g. as element of an elastic pipeline, its storage element creates a potential for metastability, so its setup/hold time window must be respected. To rapidly resolve metastability and suppress metastable outputs for positive transistions as well as for negative transistions a Schmitt-Trigger at the output of a Muller C-Element can be employed [40].

Metastability has several effects on a self-timed system. Interpretation of metastable output voltage depends on actual threshold of the input stage, thus different stages have different interpretations, which may lead to Byzantine behaviour. Metastable voltages may propagate to the output stage and further to the next element. Oscillations with multiple periods may emerge in storage loops, whose length exceeds a critical length relative to the transistion times. From this we conclude that **Metastability** is defined as the state where signal voltage within a stateful circuit element is inbetween thresholds, thus the affected component is in an undefined state, a small perturbation (e.g. noise) is sufficient to let the output converge to one of the two stable states [12]. This process may take an arbitrary amount of time.

### **1.2 Problem Statement**

Meeting the timing requirements of stateful circuit elements within a system gets difficult as soon as it is necessary to exchange signals with another system or the environment.

Communication within *completely synchronous* systems is conceptually simple, but lacks modularity due to the constraints that are applied to the signalling. In completely synchronous systems careful clock distribution, i.e. a balanced clock tree, is required to ensure that each part or module of the system has exactly the same clock (in frequency and phase). Thus if a component is changed a complete redesign of the system (especially the clock tree) may be required. Other communication approaches have been proposed, they circumvent the constraints of completely sychronous systems and achieve an improvement in efficiency, but open the issue of crossing clock domain boundaries and thus require synchronizers to safely transmit data. These approaches may use separate clock domains with either related (e.g. rationally related) or uncorrelated clocks (e.g. a GALS system), where the system is divided in several independent modules, that operate fully independent/parallel (loosely coupled), each with its own clock. It is also possible to operate systems *completely asynchronous/self-timed* (i.e. no clocks). The modules in these systems operate in lock-step and require request-driven synchronization approaches (strongly/tightly coupled). Further these approaches can be mixed, hence a clocked system can sample asynchronous signals from its environment (e.g. a sensor) or a self-timed system and vice versa. Further there are several different possible implementations of the data link and the used communication protocol between the modules. A simple wire (single bit) or a bus structure or an asynchronous interconnect can be used to interface different modules/systems between each other or their environment. With these interconnects various communication protocol approaches come along. For instance when using a bus structure a handshake protocol (2-/4-phase) can be implemented. When using an asynchronous interconnect a Bundled Data approach (serial communication protocol) or a Level Encoded Two Phase Dual Rail protocol [14] or a Null Convention Logic protocol can be employed.

We see that synchronizing synchronous as well as asynchronous systems is a broad field of op-

tions, many solutions are available. Thus we need to categorize our system in terms of the timing domain of our system and of our communication partner and the used link and communication protocol between them. After evaluating these parameters we want to choose an appropriate synchronizer for our system, but which one is best to be used for which system? To answer this question a survey is done to gather existing synchronizer solutions and summarize and compare them, leading us to a general reference book about synchronizer solutions and interfacing techniques between different timing domains.

### **1.3 Methodological Approach**

In this thesis an extensive literature survey shall lead us to a general reference book about synchronizer solutions and interfacing techniques between different timing domains. We will start with a literature survey to discover possible existing synchronizers and interfacing solutions. To find the most adequate solution for each possible system combination, the discovered synchronizers are categorized (by their concept) and we compare them among each other. The comparison is done in terms of *Mean Time Between Failures* (MTBF), throughput and latency. The MTBF is the time between two consecutive sychronization failures within a system and is defined for systems with unrelated clocks as

$$MTBF = \frac{e^{\frac{t_{res}}{\tau_c}}}{T_0 \cdot f_{clk} \cdot f_{dat}},$$

where  $t_{res}$  is the resolution time, a duration in which the output has time to settle. Further  $\tau_c$ , time constant, and  $T_0$ , width of decision window are empirically determined flip-flop parameters. At last we have the frequency of the sampling clock  $f_{clk}$  and the data rate  $f_{dat}$ . Note that this formula is not applying to every relationship of receiver and transmitter frequency, only in case if the clocks are unrelated (see [3] for further details on this restriction). *Latency* denotes the time the synchronization process takes to synchronize a data item to the receiver's timing domain. The *Throughput* specifies the number of transmitted data items per time unit through a synchronizer.

#### **1.4** Structure of the work

This thesis is structured as follows, in Chapter 2, the survey of existing synchronizer solutions is started by a brief description of the classification of system synchronization, for each class a table is presented in Section 9 giving an overview of the result of the survey. In Chapter 3 the *Mesochronous Synchronizers* are described in detail. The *Plesiochronous Sychronizers* are described in Chapter 5. Chapter 6 holds the detailed descriptions of synchronizers that are used between systems with uncorrelated clocks. The *Ratiochronous Synchronizers* are described in detail in Chapter 4. Interfacing solutions for self-timed systems are described and analyzed in detail in Chapter 7. Different types of interconnects are described in Chapter 8. The thesis concludes in Section 10.

# CHAPTER 2

## **Levels of Synchrony**

## 2.1 Classification

Synchronizers have to cope with different amount of clock and delay variations. There are four types of clock and delay variations [26]. First of all the *skew* that is constant over time and emerges from delay inside a chip and communication. The second one is *jitter* that refers to delay that varies between clock cycles. The next variation principle is called *drift* which is similar to jitter but refers to slower variations of delay. The last mentioned source of delay variations are *fast switching* and *clock harmonics*. The differences between transmitter and receiver clock in terms of the stated variations denotes the class of a system. The following list presents a classification of system synchronization [12] [28], which forms the base for the survey below.

#### **Classification of System Synchronization:**

$\rightarrow$  Synchronous:

Transmitting as well as receiving systems have same clock frequency and are in phase. Safe communication is possible with out the need of explicit synchronization.

$\rightarrow$  Mesochronous:

Both communication partners employ clocks with the same frequency with an arbitrary but fixed phase shift. The clock (local or foreign) or incoming data signal has to be delayed by a constant time for safe sampling.

$\rightarrow$  Multisynchronous:

A multisynchronous system is composed of different modules which are using a globally generated clock that is distributed without underlying balanced clock tree, thus the clock of each module has an arbitary relative phase drift. Such a system has to cope with delay variations and correlation which evolve from such a clock distribution, such that the frequency of its clock is the same at each module but its relative phase is apriori unknown and may change. Within a system with multisynchronous clocking each module mostly generates its local clock by reshaping the global multisynchronous clock.

$\rightarrow$  *Ratiochronous (Rational Related):*

The clock frequencies of two systems are related by a ratio that is known at design time e.g. 1:3, it is simple to determine dangerous cycles, where metastability may occur and thus one can directly add a delay at this point of time. Thus  $\frac{f_m}{f_n} = \frac{M}{N}$  describes the ratio, where  $f_m$  is the transmitter's clock frequency and  $f_n$  is the receiver's clock frequency and M and N are integers. Hence a special case of *Heterochronous/Periodic* system synchronization.

$\rightarrow$  Plesiochronous:

Both systems have the same or nearly the same clock frequency. There is an arbitrary phase shift between the system clocks which is drifting slowly. To safely sample an incoming signal a continuously adjustable delay is needed for clock or data signals.

$\rightarrow$  *Heterochronous/Periodic*:

Systems are both clocked (periodic) at arbitrary nominally different frequencies. Synchronizers take advantage of the periodic nature of clock and data signals, to predict dangerous events which would lead to metastable states.

$\rightarrow$  Asynchronous/Clocked:

Communicating systems are in the same relationship as at *Heterochronous/Periodic*, but the synchronizer will not or cannot take advantage of the periodicity of the clocks, thus events occur at arbitrary times, which further requires a synchronizer that is capable of every frequency relationship (assume unrelated).

$\rightarrow$  Asynchronous/Self-Timed:

One or both communication partners are self-timed, means these systems do not employ clock signals and thus are event-triggered using either a handshake protocol (2-/4-phase) and/or a dual-rail implementation of the data path to maintain the delay-insensitivity property.

The major part of the above presented classes uses *seperate clock domains* (e.g. a GALS system), where the system is divided in several independent modules each with its own clock. The local clock of each module can either be generated within the module or derived from a central source that distributes a system wide clock to every module (i.e. unbalanced clock tree). Thus changes of modules are independent to the system and the other modules. Due to the modularity and the involved simplified signalling this approach is most commonly used in practice. A drawback is that the initial synchronization adds latency to the data transmission. The *asynchronous/self-timed* approach has several advantages compared to the clocked ones like less power dissipation, further the system remains in a quiescent state until triggered for a new data transmission. Although an asynchronous system is obviously event triggered in some degree

there is synchronization or arbitration required, to synchronize incoming events to the current computation cycle (run) and to arbitrate between asynchronous requests, basically to determine which signal was asserted first, as mentioned before. Several of the synchronizers presented in this thesis employ an asynchronous interconnect to interface different modules/systems between each other or their environment. The advantages of such an asynchronous communication path (and asynchronous logic in general) are less power consumption, average case performance, adaption to changing environmental conditions and reduced electromagnetic radiation, which make an asynchronous interconnect more attractive and valuable. Interfacing asynchronous systems needs distinct design methodologies [23] [24]:

First there is the *Bundled Data* (**BD**) approach, where data transmission is parallelized. With this approach a 2(NRZ)-/4(RTZ)-phase handshaking (request and acknowledgement) is introduced. To avoid race conditions between the data stream and handshake signals the gate as well as wire delays are bounded by assumption. The main problems with this approach are glitches, and therefore masking is needed.

Further the Level Encoded Two Phase Dual Rail (LEDR) protocol [14], which is a delayinsensitive (no clocking) protocol that uses a 2-phase handshaking (with NRZ). Gate and wire delays are unbounded and unknown but finite. The data transmission needs a completion detection logic. A dual-rail approach is needed to determine "no transition" from a late transition, that is two physical wires are employed to represent a single signal. Data in this phased logic [24] is represented in two phases,  $\varphi_0$  and  $\varphi_1$ , each includes both logical values. The phase of the signal changes with each transition, this is derived by a XOR operation on the two lines. Synchronization is easily done by waiting for all input signals to be in the same phase.

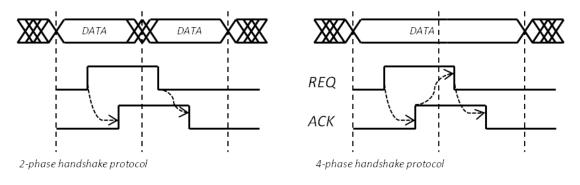

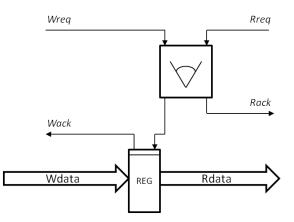

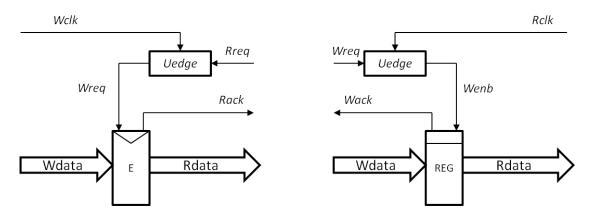

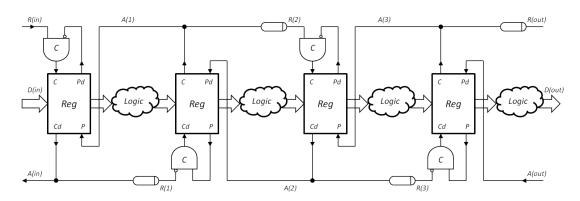

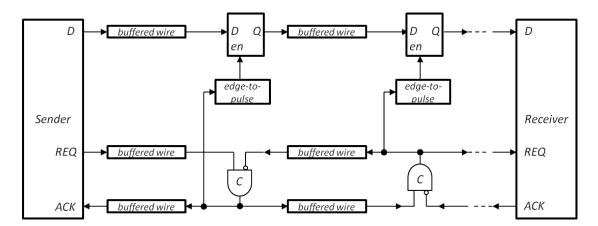

At last the *Null Convention Logic* (NCL) protocol, as the LEDR protocol it is a dual-rail approach, but uses a 4-phase handshaking (with RTZ). The protocol extends the boolean logic by a NULL value. The data stream consists of alternating waves of data and NULL (empty) words. These methodologies use a handshaking protocol, a *4-phase handshake* involves the following steps [27] (see Figure 2.1): At first a new data is available at the transmitter. From this the transmitter rises the request signal and keeps it up to signal a starting data transmission. The request is synchronized at the receiver and the bundled data stream from the transmitter is latched. After data transfer has finished the receiver rises its acknowledgement signal, which is synchronized at the transmitter. Data now may be removed from the output at the transmitter and the request signal is de-asserted and synchronized at the receiver. The receiver then de-asserts its acknowledgement signal which is further synchronized at transmitter. After these steps the transmitter is allowed to start this procedure all over again. A *2-phase handshake* on the other hand involves similar steps, but in contrast to the 4-phase handshake each transition on the request and acknowledgement lines signal a new request or acknowledgement.

Figure 2.1: Handshaking signals (2-/4-phase)

# CHAPTER 3

## **Mesochronous Synchronizers**

A mesochronous system consists of communication partners that employ clocks with the same frequency with an arbitrary but fixed phase shift. Synchronizers can exploit this relationship between the two clocks to efficiently synchronize data communication.

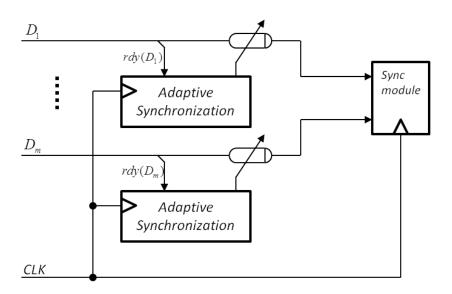

Thus *Mesochronous synchronizers* need two mechanisms to safely interface two systems. First they need a **phase estimation** mechanism, to determine by which amount the phase of the receiver clock is shifted in respect to the transmitter clock, there are different approaches given in sections 3.2.2, 3.2.5 and 3.2.6 (see Figures 3.2, 3.8 and 3.10 respectively) that employ a phase estimation circuit. From the result of the phase estimation the synchronizer educe how to adjust a delay in the data path or on the clock or control lines, that is formed either by an adjustable delay element (see 3.2.2 and 3.2.5) or alternative data paths(see 3.2.3, 3.2.4 and 3.10), to adjust the arbitrary phase shift between clock reference and data signal and keep signal transistions away from unsafe regions of the clock.

## 3.1 Basic Concepts

The mesochronous synchronizers presented in this chapter can be classified in three basic concepts:

- First the *Brute-Force Synchronizer*, the *Delay-Line Synchronizer* and the *Adaptive Synchronization* approach directly **modify the timing in the data stream** either by a cascade of flip-flops or a variable delay element in the data channel.

- The *Three-Element FIFO Synchronizer* and the *Four-Stage Mesochronous Synchronizer* both use a **ring buffer** sampling incoming data every cycle of receiver's clock to one of its latches in spite of possible metastable states and let it rest for one turn (the other latches are written in sequence) and thus let a possible metastability decay.

• The *Two-Register Synchronizer* and the *Low-Latency and Low-Overhead Mesochronous Synchronizer* control the input latches at the receiver module to safely sample new data, either by delaying the control input of the latch relative to the receiver clock or using a *strobe* signal, sent by the transmitter (synchronized by a *Brute-Force Synchronizer*) to enable the latch.

From each set of synchronizers associated with the different basic concepts one solution is picked as a representative in the following general discussion of properties. Details on the implementation and function of all solutions can be found in the subsequent subsections. Note that a calculation of the MTBF using the formula given in the introduction does not work for mesochronous system due to the correlated clocks [3], but if the synchronizer is properly configured it achieves an infinite MTBF in the data path.

From the set of synchronizers that directly modify the timing in the data stream the Adaptive Synchronization approach is chosen. This approach employs a learning phase to dynamically adjust the delay line on the data channel. Thus is able to react to changes in phase drift (also capable of plesiochronous timing relations) when employing a continuous learning phase, thus achieving an infinite MTBF and a latency of half a clock cycle maximum (variable delay element). A throughput of m bit per clock cycle can be attained with m parallel input data paths each employing an adapative synchronization block and a variable delay.

From the set of parallel staged synchronizers the *Four-Stage Mesochronous Synchronizer* is chosen for discussion. It is an enhancement of the *Three-Element FIFO Synchronizer*, with a fourth stage and a FIFO at the input of the receiver to enable data burst from the transmitter and a mechanism to support back-pressure. The *Four-Stage Mesochronous Synchronizer* is chosen as the reference of its concept class, due to its enhanced functionality and MTBF compared to the *Three-Element FIFO Synchronizer*. In detail the *Four-Stage Mesochronous Synchronizer* provides a infinite MTBF, a latency of three clock cycles and one word per cycle throughput (see table in [17]).

From the last group the Low-Latency and Low-Overhead Mesochronous Synchronizer is picked as a representative. It uses a strobe signal, that is generated in the transmitter timing domain and synchronized by a Brute-Force Synchronizer to the receiver timing domain, to determine whether it is safe to sample incoming data on either the rising or falling clock edge (or if only dummy data was sent). This mechanism has the advantage that synchronization is done completely off the data path, hence metastabilities can only occur at the strobe signal input. The MTBF in the strobe signal path is very high due to the used cascade of latches. The latency of the Low-Latency and Low-Overhead Mesochronous Synchronizer is in best case  $T_w$ , equal to the delay in the strobe signal path, and in average case  $\frac{T}{2} + T_w$  or in worst case  $T + T_w$  (see [7]). It supports "maximal throughput" [7] of one data token per clock cycle. For a detailed description and references of the comparative parameters of the chosen prototypes see the correspondening section below (Adaptive Synchronization 3.2.5, Four-Stage Mesochronous Synchronizer 3.2.7, Low-Latency and Low-Overhead Mesochronous Synchronizer 3.2.6).

## **3.2 Detailed Descriptions**

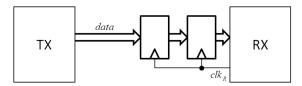

#### 3.2.1 Brute-Force Synchronizer

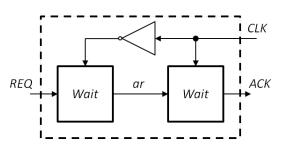

The Brute-Force Synchronizer or Waiting Synchronizer [12] employs two or more (like in the conservative version, see 6.2.1) flip-flops. A system employing a Brute-Force Synchronizer is depicted in Figure 3.1. At first the flip-flop samples the input signal (asynchronous) and waits (one clock cycle) for any metastable state to decay, then in the next clock cycle the (possibly) stable output of the first flip-flop is sampled by a second flip-flop adding another cycle of resolving time to the synchronization process and providing the data item to the receiver. This synchronizer does not take advantage of knowledge about periodicity of clocks. Disadvantages involved with this approach are enhanced delay and a non-zero probability of synchronization failure. Further if the phases of transmitter and receiver clock almost match and the synchronizer runs into "bad" timing the input data may be corrupted by a metastability event leading to inconsistency in the communication which introduces a criterion for exclusion and thus it should not be used. Its average delay is  $t_z = t_w + 2t_{dCQ} + t_{cy}/2$  (see [12]), where  $t_{dCQ}$  is the clock-to-output delay of the synchronizing latches and  $t_{cy}$  is the cycle time and  $t_w$ , the waiting time denotes the time a system is configured to wait until the output of synchronizer is sampled, typically about one clock cycle. In summary, the synchronizer has a non-zero probability of synchronization failure (thus a non-infinite MTBF), similar to the Two-Flip-Flop Synchronizer. The Brute-Force Synchronizer has an average latency of  $t_z$  and a very low throughput hence it synchronizes only one bit every three clock cycles.

Figure 3.1: Digital Systems Engineering [12]: Brute-Force Synchronizer

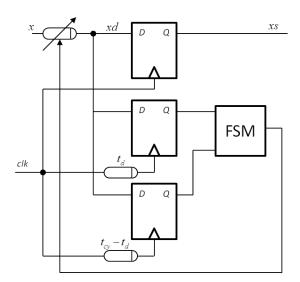

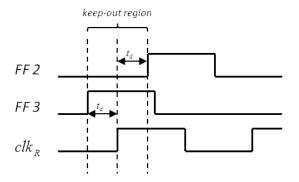

#### 3.2.2 Delay-line synchronizer

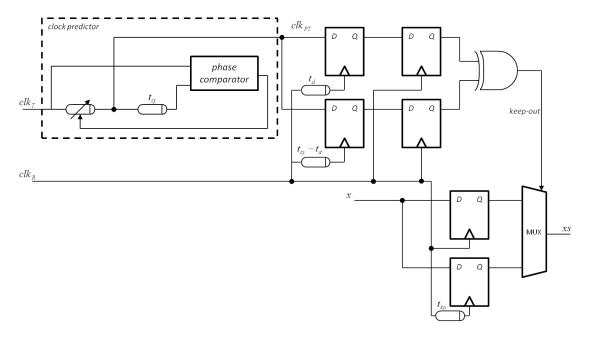

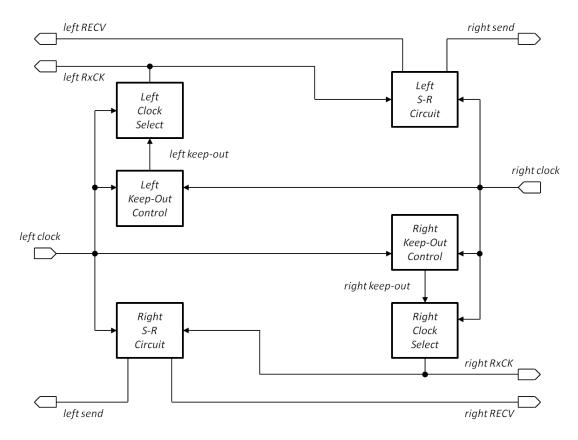

The *Delay-line Synchronizer* presented in [12] is used to synchronize mesochronous systems, a block diagram is depicted in Figure 3.2. It employs a variable delay-line on the data path with an adjustment range of a clock period. During its learning phase two flip-flops capture the variable delayed input with two different delayed versions of the clock to measure the relative phase of the delayed input and further adjust the variable input delay on the data path. If the delayed input signal changes during the keep-out region of the clock the two flip-flops will capture different values (the lower one will sample a different value) and signalling the FSM to adjust the delay so that it keeps the input out of the forbidden region. In detail the second and third flip-flop

span a window of  $\pm t_d$  around the rising edge of the original clock to simply define the *keep-out* region (see timing diagram in Figure 3.3). With a well chosen value for delay element  $t_d$  the setup and hold constraints can be reflected, hence  $t_d$  at the second flip-flop matches  $t_{hold}$  and  $t_{cy} - t_d$  at the third flip-flop is equal to  $t_{su}$ , iff  $t_d < t_{cy}/2$ . The synchronizer employs an average delay of  $t_z = t_{v(min)} + t_d + t_{dCQ} + t_{cy}/2$ , where  $t_{v(min)}$  is the minimum variable delay,  $t_d$  is the value of the delay element at the control input of the second and third flip-flop,  $t_{dCQ}$  is the clock-to-output delay of a flip-flop and  $t_{cy}$  denotes the cycle time. In summary, the Delay-line Synchronizer has a infinite MTBF, provides a data item per clock cycle with an average latency of  $t_z$ .

Figure 3.2: DSE [12]: Delay Line Synchronizer

Figure 3.3: DSE [12]: Delay Line Synchronizer - Timing Diagram

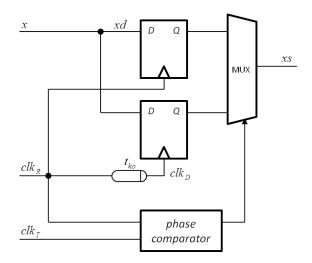

#### 3.2.3 Two-Register Synchronizer

The Two-Register Synchronizer [12] is similarly constructed as the Delay-Line Synchronizer but it delays the clock line instead of the data line, as one can see in Figure 3.4. There are two flip-flops or registers (for multiple data lines), one samples data on the rising edge of the clock, and the other one is triggered by a delayed version of the same clock edge, thus sampling data delayed at least by the width of the forbidden (keep-out) region of the flip-flop. A phase comparator measures the relative phase between the local clock and the transmitter clock of the incoming data stream once after reset and thus determines which of the flip-flops is safe to be selected by the multiplexer. The measurement phase may be repeated during operation to support variable phase shifts. Usually the upper (not delayed one) flip-flop is used unless there is an event on the data line during the keep-out region, in this case the lower one is chosen by the multiplexer. The average delay of the Two-Register Synchronizer is  $t_z = t_{ko}^2/t_{cy} + t_d + t_{ko}^2/t_{cy}$  $t_{dCQ} + t_{cy}/2$ , where the term  $t_{ko}^2/t_{cy}$  is the duration of the keep-out window multiplied with the probability that the lower flip-flop is chosen by the comparator,  $t_d$  is the delay of the flipflop,  $t_{dCQ}$  the clock-to-output delay and  $t_{cy}/2$  the half of the cycle time, which is the inherent synchronization delay of rounding up to the next cycle (see [12]). In summary, the Two-Register Synchronizer achieves an infinite MTBF in the data path, if the comparator has chosen correctly and the phase shift remains constant. On the other hand the phase comparator itself may get metastable, the MTBF in this case depends on the used technology. Further the synchronizer employs an average latency of  $t_z$  and a throughput of a data item each cycle.

Figure 3.4: DSE [12]: Two Register Synchronizer

#### 3.2.4 Three Element FIFO Synchronizer

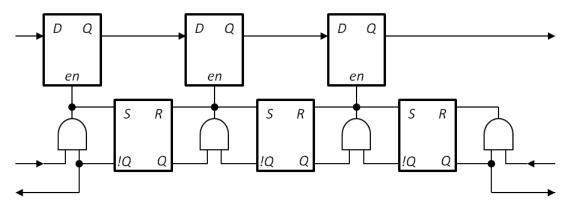

The *Three Element FIFO Synchronizer* [12] [28] uses a small ring-buffer to decouple transmitter and receiver timing. The synchronizer employed with three stages is depicted in Figure 3.5.

Incoming data items are written alternately into a couple of flip-flops. The flip-flop is chosen by a *transmit* pointer (xp) which is generated by a counter in case of a three-element (or higher) synchronizer. A further ring counter, which is driven by the local clock of the receiver, is controlling the multiplexer to select the flip-flop with the oldest sampled value for read. The pointer of the receiver (rp) should lag the pointer of the transmitter (xp) by at least one clock cycle. In fact this lag represents the available resolution time and should therefore be maximized. Obviously more stages allow for higher resolution time. Note that the pointers xp and rp need to stay in sync to avoid pointing to the same flip-flop. This is guaranteed by the assumption of a mesochronous environment. In this respect a higher number of stages allows for a longer distance between the pointers and hence better tolerance of long phase variations. To accommodate for the combinational delay introduced by the multiplexer another flip-flop stage is added to relax the contraints. On the other hand is also possible to reduced the number of stages to two. In this two-element FIFO synchronizer only two toggle flip-flops are needed to generate the xp and rp, instead of counters. With only two flip-flops the data latency is reduced, but problems may occur in case the two clocks are nearly in phase, because it is not guaranteed that the chosen value will be stable for an entire clock cycle at the multiplexer (may be overwritten before read). Hence the three-element (or higher) version might be the preferred choice. In summary, a possible metastable state in one of the flip-flops has n clock cycles to decay, thus the MTBF is clearly finite for the *Three Element FIFO Synchronizer*, where *n* is 3. Data is passed every clock cycle after the three stages are filled initially with a data latency equal to the number of stages (i.e. a data item stays in the FIFO for n cycles of the receiver clock).

Figure 3.5: DSE [12]: Three Element FIFO Synchronizer

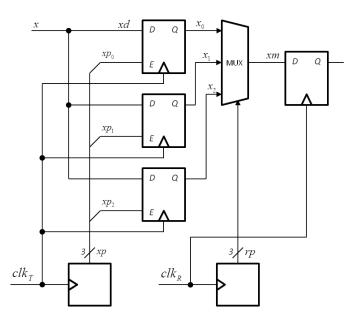

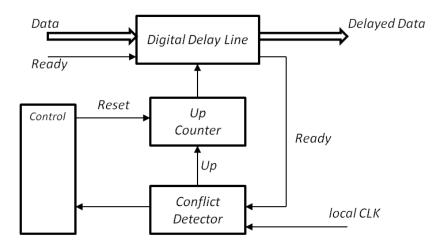

#### 3.2.5 Adaptive Synchronization

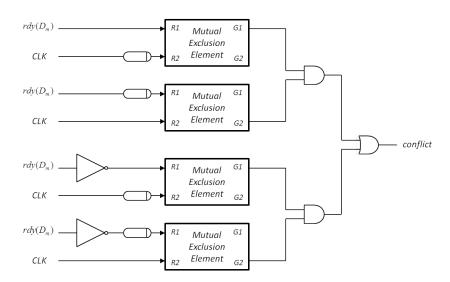

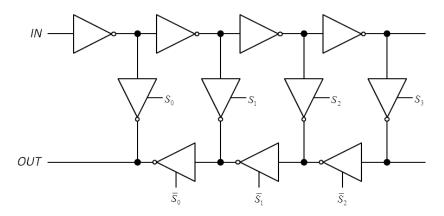

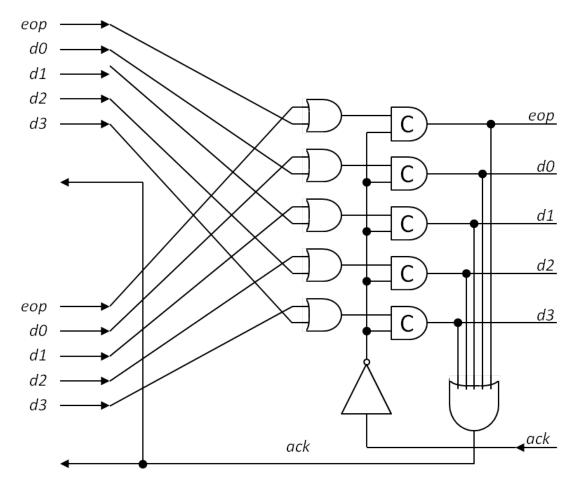

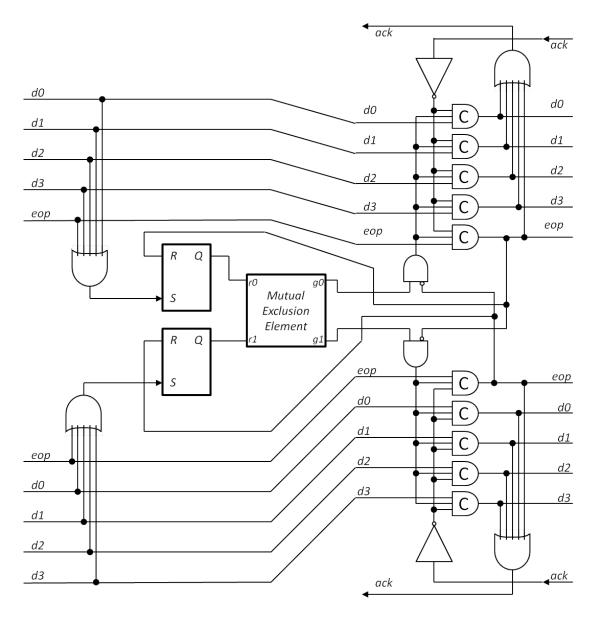

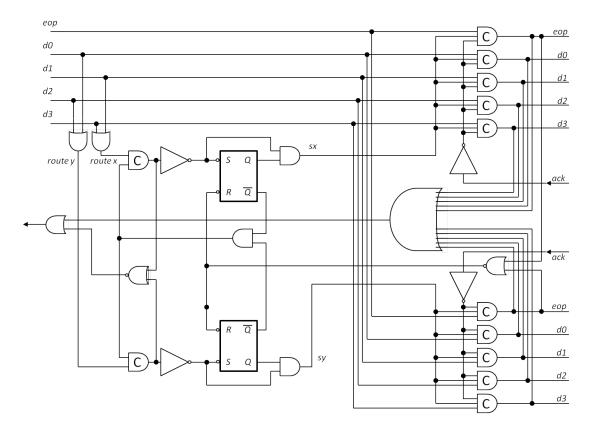

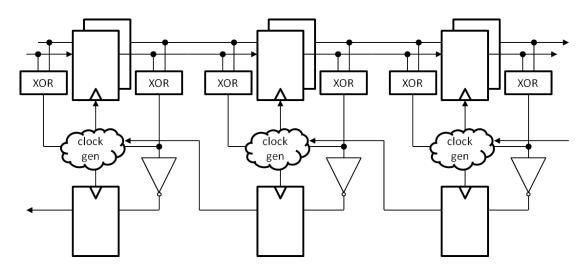

Adaptive Synchronization [26] is a proposed method to synchronize multi-synchronous modules within a system. Delay variations and correlation evolve from unbalanced clock distribution, such that the frequency of the system clock is the same at each module but its relative phase is apriori unknown and may change. In [26] the relative phase is supposed to be "stationary" which means that the relative phase can be seen as fixed over long periods of time. The transmitter module provides additionally to the data a ready signal to the receiver module. The ready signal and the local clock are provided to a conflict detector which activates a counter as long as a detected conflict lasts (see Figures 3.7 and 3.8). The counter is reset at the start of the adaption cycle by the controller. The counter value (one-hot encoding) directly increases the number of inverters within the digital delay line (see Figure 3.9) to delay the incoming data. The conflict detector employs four mutual exclusion elements, each two to detect conflicts at rising and falling edges. A conflict is detected if the time interval between a transition of the ready signal and transition of the local clock is shorter than the employed delay of the conflict detector (see Figure 3.3). In [26] there are five modes (learning phases) proposed in which adaption is achieved. There are "one time adaption" (after manufacture), "power-up adaption" (once after power is applied), "periodic training sessions", "triggered training sessions" and "continuous tracking" to accommodate a different amount of drift and different electrical schemes. In summary, the synchronizer employs a very high or up to infinite MTBF (depending on which mode of learning phase is used), a latency of maximal a half clock cycle (variable delay) plus a learning phase and thus passes data each clock cycle.

Figure 3.6: Adaptive Synchronization [26]: Structure

Figure 3.7: Adaptive Synchronization [26]: Adaptive Sensitivity Implementation

Figure 3.8: Adaptive Synchronization [26]: Conflict Detector

Figure 3.9: Adaptive Synchronization [26]: Digital Delay Line

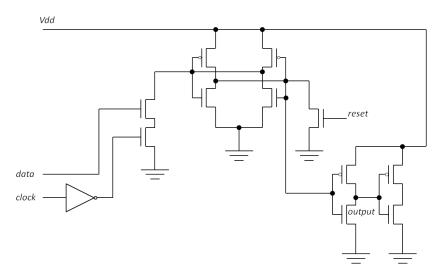

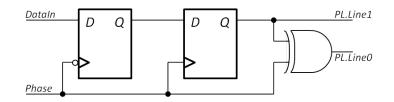

#### 3.2.6 Low-Latency and Low-Overhead Mesochronous Synchronizer

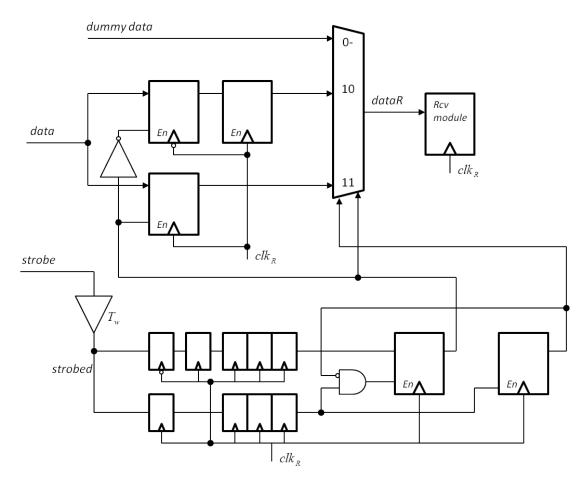

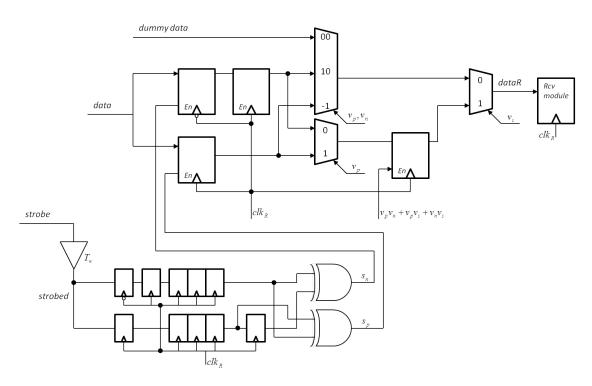

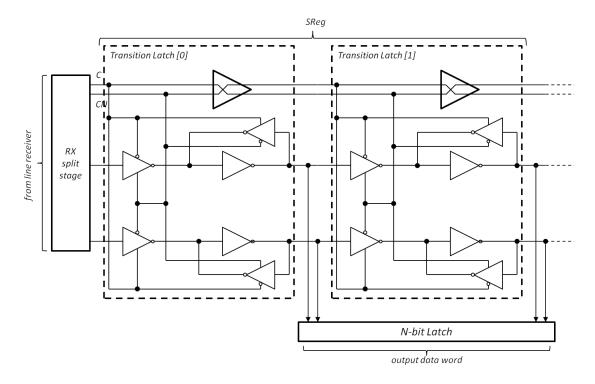

A low-latency and low-overhead mesochronous synchronizer is presented in [7]. It can be used in so-called globally non-synchronous system as GALS or systems with unbalanced clock trees, which bring performance enhancements and power savings in contrast to globally clock systems (with a balanced clock tree). Due to such an unbalanced clock tree each module of the system run with the same nominal frequency indeed, but with an unknown constant phase shift between them. The mesochronous receiver interface comes with an over-head of three flip-flops per data line, see Figure 3.10. The synchronizer does not employ backpressure or a handshaking mechanism and the transmitter is assumed to send data every clock cycle. It decides upon a learning phase when it is safe to sample further whether data should be sampled with rising or falling clock edge of receiver clock. A strobe signal that is generated by the transmitter, which ideally toggles with all data lines, is used to learn about when it is safe to sample. Note that the learning phase is necessary only once after reset in the mesochronous synchronizer. The strobe signal (bundled with data lines) changes from low to high and is sampled every rising and falling edge during the learning phase by the receiver. A delay  $T_w$  of a quarter of the cycle period time is inserted to ensure that a change of the strobe signal is first sampled on the falling edge. An additional flip-flop in this path is used to "move" the sample to be passed on the same rising edge as the sample taken a half clock cycle later (i.e. actually on the rising edge). The delayed signal is called *strobed*, that is used by the receiver to control the multiplexer that switches between the data input that is sampled on the falling and the other one that is sampled on the rising clock edge. During the learning phase two consecutive samples of the *strobed* signal are compared. These samples results in a sequence  $s_0, s_1, \ldots, s_i$ , where  $s_i$  is the first sample of the strobe signal that is high, thus  $s_0$  to  $s_{i-1}$  are low samples. If  $s_i$  is sampled by a rising edge of the receiver clock the rising edge is further used to sample data. The learning phase thus takes several clock cycles, in this phase only dummy data is received. Clearly the "strobed" signal may become metastable, thus must be synchronized by a cascade of flip-flops. The use of an additional control signal as strobe moves the synchronization issue and thus the probability of metastabilities away from the

data path. The total number of flip-flops needed for mesochronous interface is  $3 \cdot (number of data lines) + 6 + 2 \cdot (number of FF for strobed signal)$ . Since the learning phase happens only once after reset it does not effect the data latency. In summary, the *Low-Latency and Low-Overhead Mesochronous Synchronizer* avoids metastabilities at the data input by using a strobe signal to control the input flip-flop, at this path a very high MTBF is achievable (as mentioned before the MTBF cannot be calculated with the given formula and thus only an estimate is given). The initial latency of the synchronizer consists of a single learning phase after reset and in best case only  $T_w$  (delay of the strobe signal), average case  $T/2 + T_w$  or worst case is  $T + T_w$  [7]. The synchronizer operates with maximal throughput (a data item per cycle), an example in [7] shows data transfer at 1GHz.

Figure 3.10: Low-Latency and Low-Overhead Mesochronous and Plesiochronous Synchronizer [7]: Mesochronous Receiver

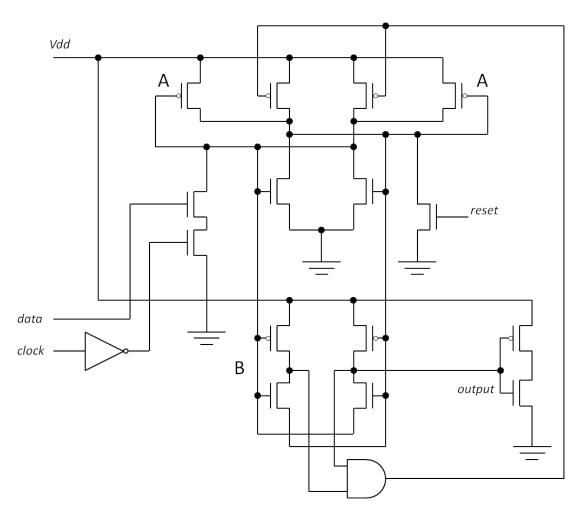

#### 3.2.7 Four-Stage Mesochronous Synchronizer

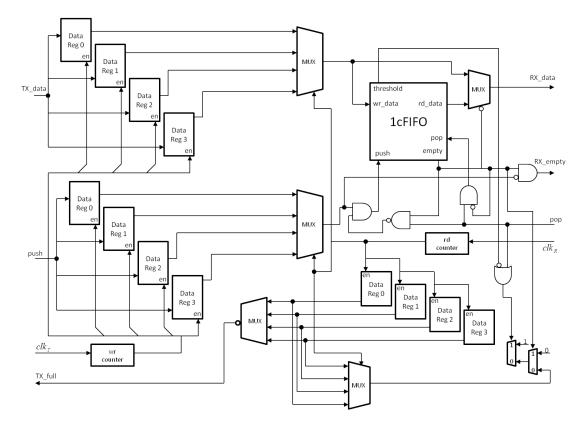

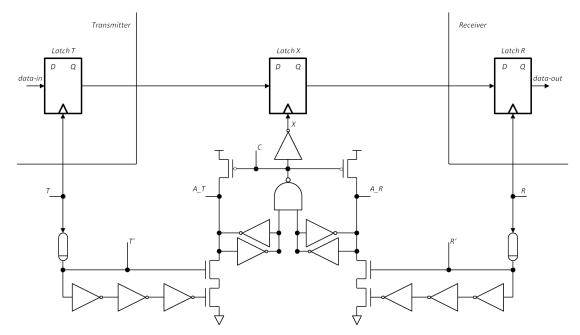

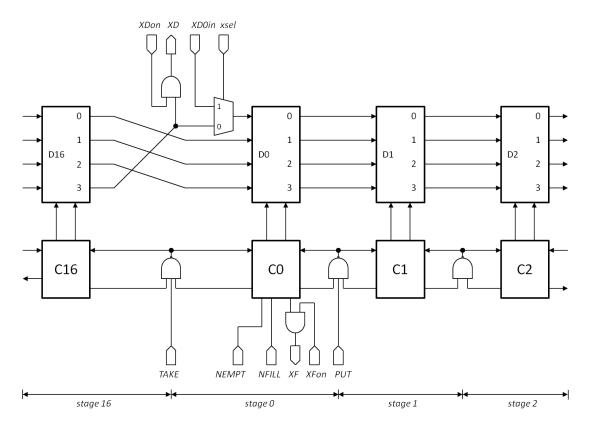

The Four-Stage Mesochronous Synchronizer (FSMS) presented in [17] provides full backpressure and buffering for data bursts, thus the receiver clock and the read/write pointers are never stopped or modified. Further it can be used for long range communication. If a FSMS is considered to interface between systems the most important design considerations are first the inital spread of read and write pointers and further the number of the used synchronizer stages (minimum of 4 stages). The FSMS employs two cyclic buffers, one for the transmitter and one for the receiver with each 4 parallel stages (registers), one can see a block diagram of the FSMS in Figure 3.11. The transmitter buffer uses four stages as data buffer for the data transfer and another four stages to buffer forward token, which indicate the validity of data items. Since a forward token shows data validity to the receiver it is used to push new data into the FIFO buffer, thus is linked with empty status line of the FIFO buffer and the *pop* signal. At the transmitter side the data transfer is done by writing data and *forward* token cyclically in one of the four stages, the stage is chosen by a cyclic counter, that is never stopped and then data and *forward* token will be transmitted to the receiver. Due to initial spread (chosen by design) of the read pointer data can settle and metastability decay before it is read from a transmitter stage into the receiver FIFO. The *forward* token indicates that the data item is valid in the corresponding data register (transmitter stage). Since the receiver clock is never stopped or modified data can arrive every cycles at the receiver side. The receiver can either read data directly from transmitter stage and process it or buffer it firstly into its FIFO. Further for the receiver to be capable of data bursts from the transmitter its FIFO needs to be deeper than the minimum four stages. The receiver may assert backpressure by sending a *backward* token containing logical 0 for "do not send", which is produced by de-asserting the pop signal. By this the data input is directed to the FIFO to buffer incoming data items which were currently pending in the transmitter buffer when the *backward* token was sent. Therefore the FIFO threshold must be L-4, where L is the size of the FIFO, to prevent data loss, thus its minimal depth is 4 or equal to the transmitter buffer. One *backwards* token is sent by one stage of the receiver buffer and blocks the corresponding stage in the transmitter buffer sending new data. For long wire communication (e.g. mesochronous NoC) the four stage synchronizer can either be employed at only one communication partner (transmitter or receiver) or in a split fashion. In the former case no modifications are necessary, in the latter an extension on the transmitter buffer (stages) depth will be necessary to compensate long delays. The FSMS can be further used to interface between *multi-synchronous* modules. Note that a system is *multi-synchronous* when a common clock is provided to its local modules without taking care of a balanced distribution. In this case six FIFO stages are needed to handle the occuring phase drifts during operation. Note that an additional phase shift by T adds two synchronizer stages, this results in a total number of stage of 4 + 2k, where k is an integer that numbers the phase drift  $[0, \pm kT]$ . The asynchronous reset must be synchronized by a 2 flip-flop brute force synchronizer to the transmitter as well as to the receiver domain to synchronously release the reset signal. To prevent metastability the read and write pointer of the used FIFOs must not be initialized to the same value, there has to be an initial spread of at least 2 stages. Forward latency varies in the range of (T, 3T) and depends on the initial pointer spread and relative phase difference. Throughput is maximized, one data item can be transferred on each clock cycle, but backpressure affects the throughput latency. A comparison table between the

four-stage mesochronous synchronizer and the 2-Clock FIFO is provided in [17]. In summary, the *Four-Stage Mesochronous Synchronizer* has an infinite MTBF, a average latency of three clock cycles and a throughput of one word per cycle [17].

Figure 3.11: Four-Stage Mesochronous Synchronizer [17]: Structure

# CHAPTER 4

# **Ratiochronous Synchronizers**

*Ratiochronous Synchronizers* are used to interface between clocked systems with rationally related frequencies.

## 4.1 Basic Concepts

There are two **Ratiochronous** Synchronizers presented in this chapter where the clocks of the communicating systems have to be rationally related, one from *Rational Clocking* that employs a fixed communication schedule placed in a LUT and furthermore the *GRLS* approach, which takes advantage of the periodic nature of the rational relation and uses a *strobe* signal to regulate data latching at the receiver.

From the two ratiochronous synchronizers presented in this thesis, the *GRLS* approach is chosen as the prototype for this category. The main advantage of the *GRLS* approach over the *Rational Clocking* technique is that it is able to cope with phase shifts in the rationally related clocks. Further the *Rational Clocking* technique implements a *lazy* algorithm, hence introduces a higher latency than the *GRLS* approach (length of input delay in best case). The *GRLS* synchronizer is based on the *Low-Latency and Low-Overhead Mesochronous/Plesiochronous Synchronizer* presented before, thus moves the synchronization away from the data channel and uses a *strobe* signal to control the input at the receiver. Both approaches provide optimal throughput (i.e. one data item per clock cycle).

The following section holds the detailed descriptions of these synchronizers, the parameters that are used for comparison are taken from the original resources.

### 4.2 Detailed Descriptions

#### 4.2.1 Rational Clocking

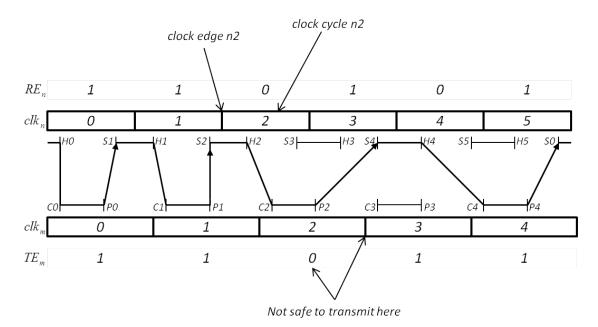

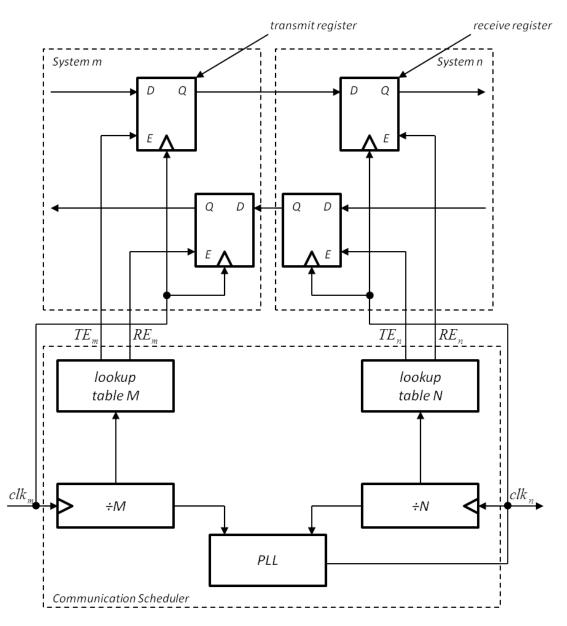

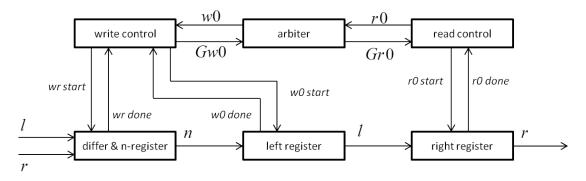

The proposed solution acts on the assumption that the frequencies of the clocks of two systems which tend to communicate are related by the ratio of two integers and that the phase relationship of these clocks is known. This can be used to exploit the predictability of points in time where it is not safe for the receiver to sample data and further create a schedule to time all communications and data transfers. This is called "rational clocking" [43] and relies on a given frequency ratio between the clocks of two modules  $f_1$  and  $f_2$ . Thus  $\frac{f_m}{f_n} = \frac{M}{N}$  describes the ratio, where  $f_m$  is the transmitter's clock frequency and  $f_n$  is the receiver's clock frequency. M and N are (small) integers that represent the same ratio as  $f_m$  and  $f_n$ . The communication schedule is generated upon the prediction of the relative position of the systems clock edges within M cycles on system m (employs clock with frequency  $f_m$ ) and N cycles on system n (with clock frequency  $f_n$ ) and shows safe and unsafe cycles for transmission. It can be derived in two ways either statically in a schedule diagram written to a LUT or dynamically at run time using graphical algorithms and a schedule plot. A schedule diagram contains the sequence of cycles and the corresponding values that state if it is safe to transmit/receive in this cycle. Within a cycle of the transmitter there is a transition window that defines when the transmitter latches data into the transmit register. At the receiver there is a decision window or setup-hold window defined around each clock edge during which the data must be stable at the input of the receiver to be sampled safely. If these windows overlap it is not safe to transmit data. So starting at the transmitter a sequence is derived where alternatingly transition windows and the next following decision window at the receiver (must not overlap) form a communication schedule (see Figure 4.1 and 4.4). This schedule is created at boot-up or is programmed into a ROM. On the other hand it is possible to generate a schedule at run-time. The advantage of this is that it has an O(log(n)) need in memory in contrast to the previous mentioned method which has a cubic growth rate in needs of memory bits,  $O(N^3)$  for a supporting ratio range of  $1 \dots N$ . Run-Time Scheduling uses a graphical algorithm similar to Bresenham's algorithm to generate a schedule plot. The schedule plot is a function f(t) defined by  $f(t) = t - (P_m + S_n)$  that is equal to the time the transmitter has to provide data stablely to the receiver.  $P_m$  is the end of the transition window and  $S_n$  the start of the decision window. The resulting straight line is drawn on a grid of  $M \times N$  lines. For each of the N vertical line a dot is set beneath f(t) on the nearest crossing point with one of the M horizontal lines of the grid. At these dots, which define points in time, it is safe to sample data. If two nearby dots are on the same horizontal line it is not safe to sample data on the later dot or no new data is available yet. For a detailed algorithm and implementation in hardware see [43]. The interface hardware employs a phase-locked loop to derive the clock of system N from the clock of system M. Two frequency-dividing counters are employed to indicate the current clock cycle of each system and form the index for the LUT. Each of the two LUTs generate a control signal for transmitter and receiver register, to enable the register when it is safe to sample or latch new data for transmission. Each system employs a *transmit* and a *receive* register (see Figure 4.2). The LUTs can be "generic" to take M and N as inputs and produce the signals for the appropriate ratio or they can be "programmable" where a LUT is loaded at bootup from a ROM providing different frequency ratios. When creating a communication schedule the starting transition window affects the throughput efficiency, so one needs to make a schedule for each transition window as starting point or uses the double-buffering technique, which guarantees 100% throughput efficiency. The double-buffering technique uses multiple registers to alternately sample data. When using average timing parameters (of components) two registers are sufficient, but [43] provides a formula to derive the appropriate number of registers for one's design. In the double-buffering technique the transmit register is doubled and further selected by an additional control signal generated by the LUT during operation (see Figure 4.3). If the transmission is not safe data is placed in the second register. This gives new possibilities for communication schedules (see Figure 4.4). The Run Time Scheduling introduces a delay which can be critical in fast, high performance systems.

Figure 4.1: Rational Clocking [43]: Schedule Diagram 1

Figure 4.2: Rational Clocking [43]: Interface Hardware

**Figure 4.3:** Rational Clocking [43]: Double Buffered Hardware (direction  $m \rightarrow n$  shown only)

Figure 4.4: Rational Clocking [43]: Schedule Diagram 2

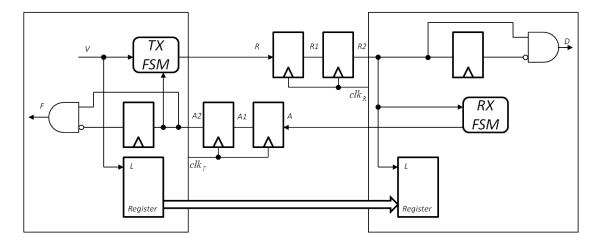

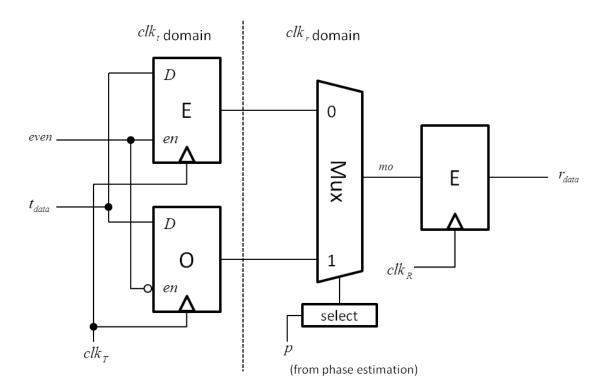

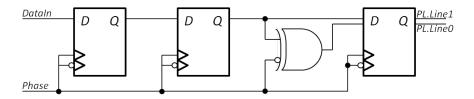

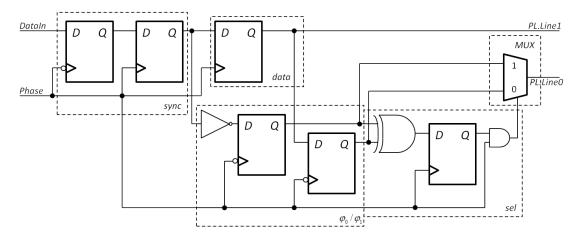

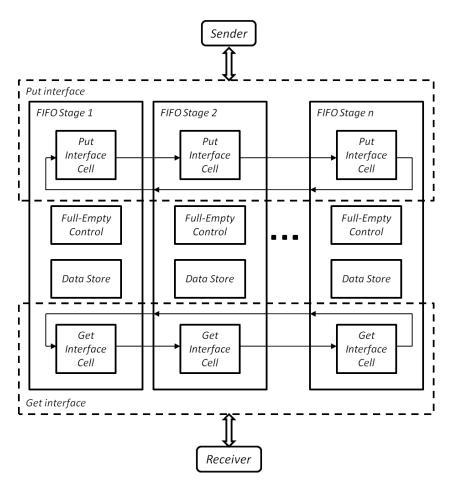

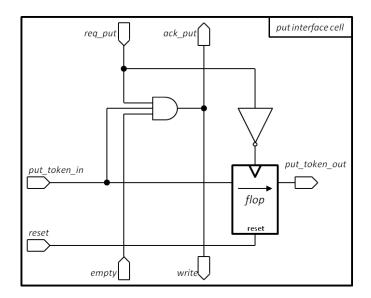

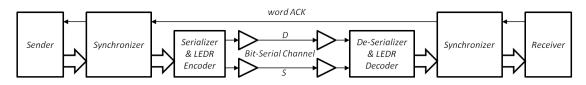

# 4.2.2 A Flexible Communication Scheme for Rational-Related Clock Frequencies

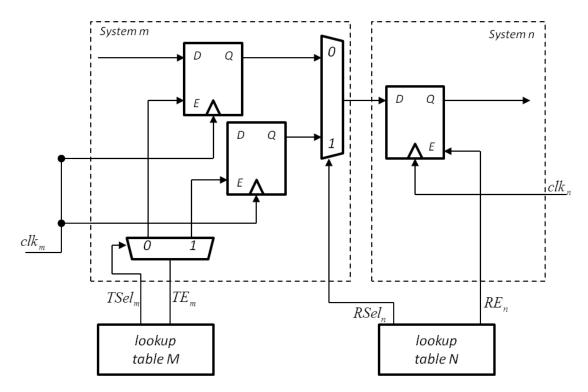

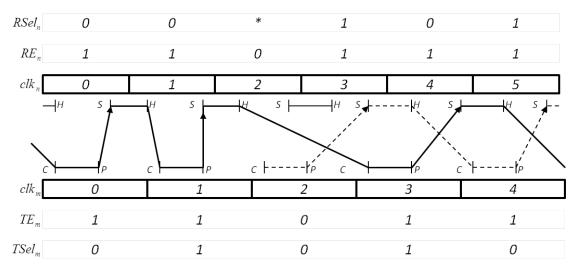

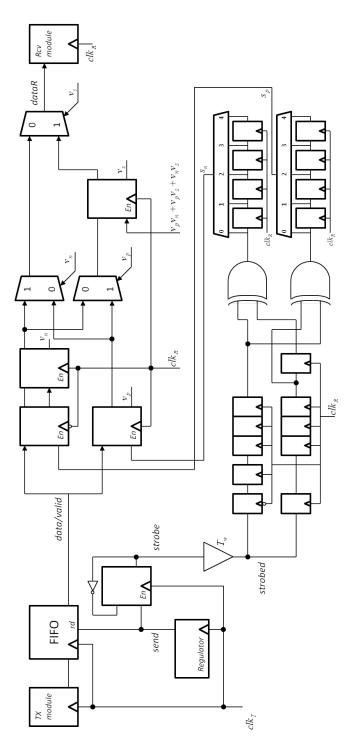

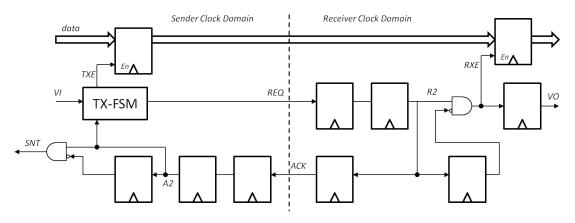

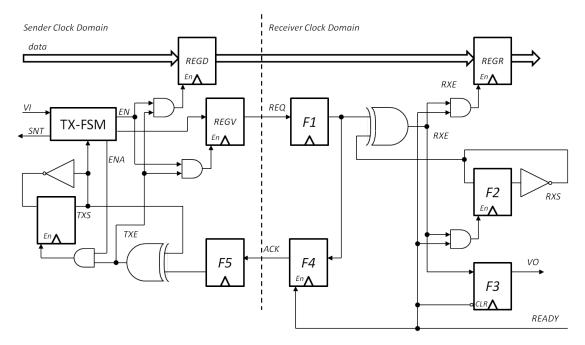

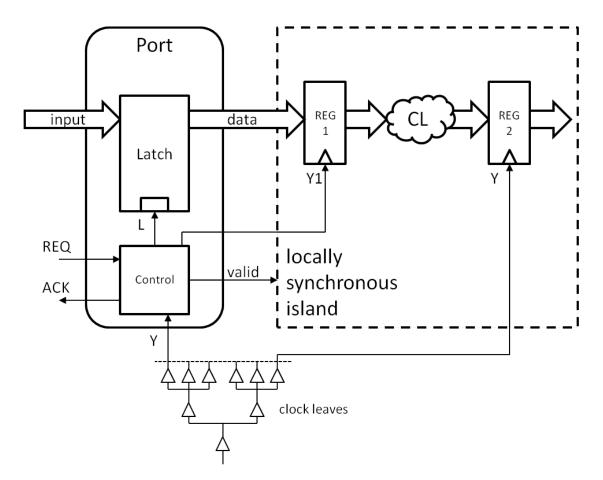

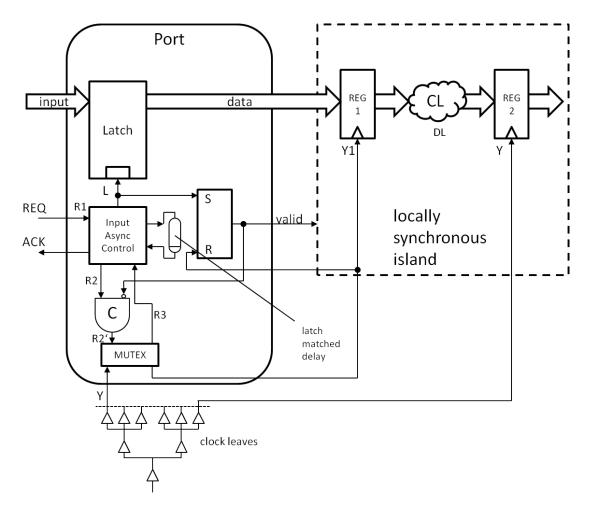

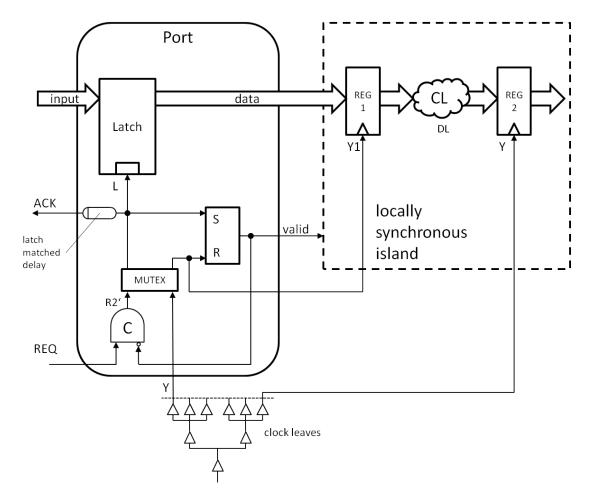

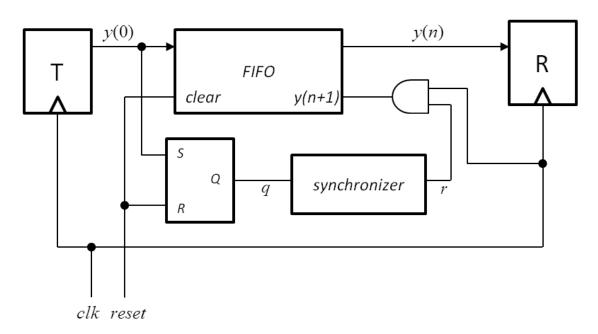

In [5] and [6] a design style is introduced called Globally-Rationchronous Locally-Synchronous (GRLS). It is located between the mesochronous and the GALS design style. Basically it constrains the frequencies used by the communicating modules to be rationally related, such that there is a global clock with frequency  $f_H$  that is determined by the least common multiple (lcm) of the frequencies of the receiver and the transmitter, where  $f_H = N_T \cdot f_R = N_R \cdot f_R$ . In contrast to the rational clocking technique from [43] presented in section 4.2.1 the GRLS interface can cope with unknown phase differences (skew) between the receiver and transmitter clock. The GRLS interface exploits the periodic nature of the rationally related systems/modules to safely interface them. The transfer rate is dictated by the slower communication partner. Note that the clock edges (of receiver and transmitter clock) align with period  $PC = N_R \cdot T_T = N_T \cdot T_R$ , where PC denotes the periodicity cycle. The interface operates as follows; the transmitter module passes a data item to its local GRLS transmitter including information if this data item is valid or not. The data item is placed in a FIFO preliminarily. The regulator circuit based on a regulation algorithm given in [6] generates a send signal, that is passed to toggle flip-flop and the read input of the FIFO where the data item is placed. The regulation algorithm generates a periodic signal to control the data flow at a rate of  $min(f_T, f_R)$ . Thus if the receiver is the faster module, the GRLS transmitter sends with a rate of its local clock. The toggle flip-flop is enabled by the periodic *send* signal and generates a *strobe* signal that is sent to the GRLS receiver besides the data item and the valid signal. The receiver samples all incoming data (and signals) at both the rising as well as falling clock edge. Thus the GRLS receiver may sample two valid data items in one clock cycle. But the receiver module cannot processes more than one data item per cycle hence a FIFO buffer is necessary. The FIFO only needs one cell due to the average rate property of the regulation algorithm, where the number of data items is limited to  $d \leq K + 1$  in a time  $K \cdot T_R$  with K as an integer. There are also three other properties given in [6] that were used to formally prove the regulation algorithm (for further details refer to [6]). The sampling of new data is enabled by the result of the analysis of the incoming *strobe* signal, which determines if it is safe to sample. It is safe to sample if the sample of the strobe signal at time  $t_i$  is different to the sample analysed a half clock cycle before. First the strobe signal has to be synchronized to the receiver's timing domain. After a delay  $T_w$  that is defined as  $t_{su} + t_{ho} < T_w < \frac{T_H}{2} - (t_{su} + t_{ho})$ the strobe signal is synchronized by multistaged synchronizer, several cascaded flip-flops. The strobed signal (the delayed strobe signal) is sampled on both clock edges, the current sample is then (after synchronization) compared with the previous sample (arrived a half cycle earlier) by XOR gates. After comparison the signal is further delayed by a programmable delay line using a cascade of flip-flops. The length of the delay line is determined by  $K \cdot N_T - N_S - 1$ , where  $N_T$ is the multiplier of the transmitters frequency to match the global common clock and  $N_S$  is the number of stages at the synchronizer for the *strobed* signal and K is an integer. This forms the selector value for the multiplexer to determine at which point in the delay line the analysis result is grabbed and passed to the data sampler as enable signal (either for rising or falling edge). The sampled data item is then either directly passed to the receiver module or buffered in the 1-cell FIFO depending on which clock edge the previous data item was sampled (i.e. two data items are sampled in the same clock cycle by two consecutive clock edges). One can see the interface

in Figure 4.5, it is based on the circuit from Low-Latency and Low-Overhead Mesochronous and Plesiochronous Synchronizer presented in 3.2.6 and 5.2.4 from [7] (see also Figure 3.10 and 5.6). So we conclude that the data flow is free from unwanted latency and metastability events. Metastable events only may take place at the input of the strobe signal, to ensure a high MTBF a Brute-Force Synchronizer with  $N_S$  stages is used. Notice that is might be problematic using a Brute-Force Synchronizer, because the clocks and thus the incoming events are not uncorrelated [3]. Further the data latency is not affected by the length of the learning phase (strobe analysis). Although the *strobe* signal shows if it is safe to sample the current data item is sampled with the strobe signal synchronized and analysed  $K \cdot PC$  before, this is guaranteed by the *periodicity* property of the regulation algorithm. There is only an initial latency that affects the data transmission once after startup, which is defined as  $t_s = t_i + K \cdot PC$ , where  $t_i$  is the point in time when the *strobe* signal is analysed. The transmitter then sends every cycle so that the analysis flow (and data flow) is not interrupted, also in cycles in which the transmitter has no new data to send, in this case the valid signal is simply de-asserted and thus the receiver module does not process the incoming data. [5] also provides implementation details and a latency analysis. In the worst case using 90 nm technology the GRLS approach works with at most 1 GHz as global frequency  $(f_H)$ . The latency is given as  $T_W$  in best case, and  $(\lceil \frac{N_R}{N_T} - 1 \rceil)T_T + T_R + T_W$ in worst case.

# CHAPTER 5

# **Plesiochronous Synchronizers**

In contrast to the mesochronous synchronizers, treated in Chapter 3, *Plesiochronous Synchronizers* have to handle slight drifts in clock phases. That involves that the delay within the synchronizer needs to be adapted during operation to cope with changing relation in phase and to avoid duplicated or dropped data items. Within heterochronous/periodic systems, where the communication partners are clocked at different frequencies, synchronizers take advantage of the periodic nature of clock signals, to predict points in time where it is unsafe to transmit data. Due to different system clocks there is a need of flow control at the interfaces either at the faster or the slower clocked module, in order to avoid duplicated or dropped data items. There are different ways to accomplish flow control for example a backpressure mechanism (like in 3.2.7) or a common sending speed equal to the speed of the slowest module. Some mesochronous synchronizers can be used, but mostly require modifications like update circuits, null insertion or explicit flow control.

# 5.1 Basic Concepts

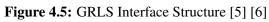

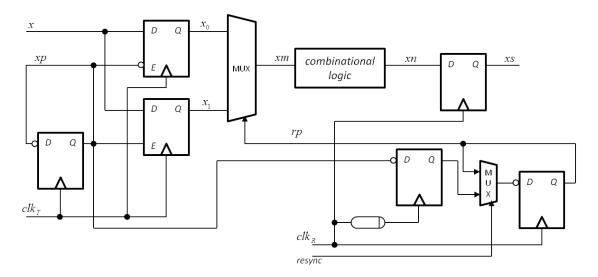

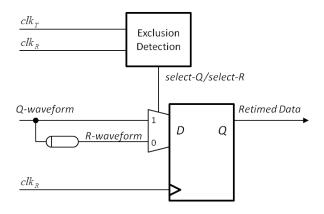

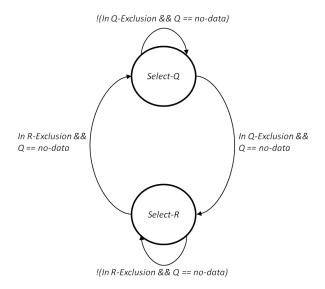

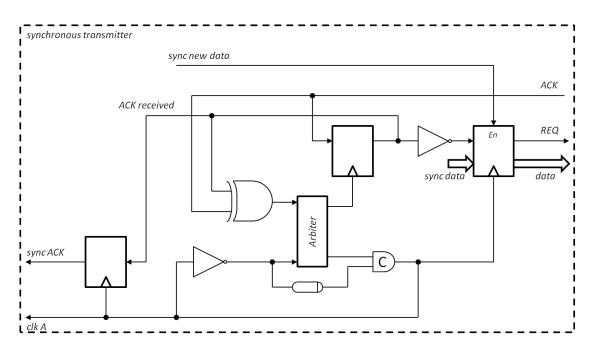

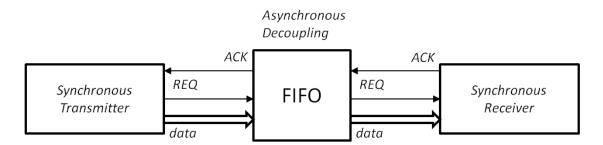

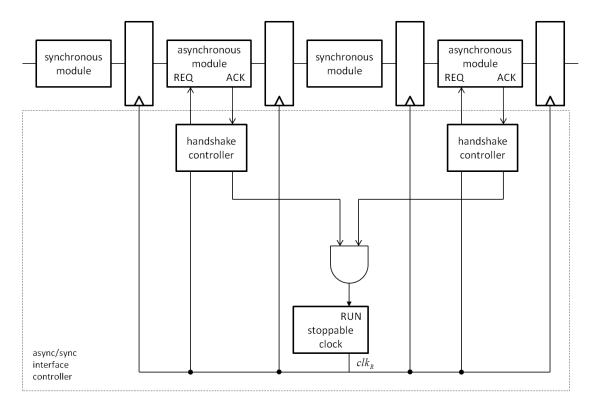

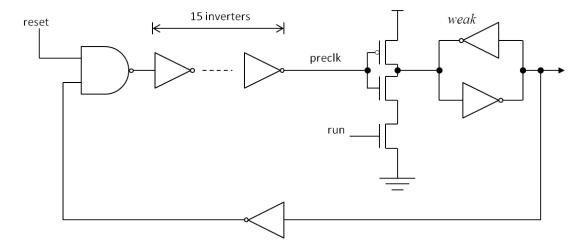

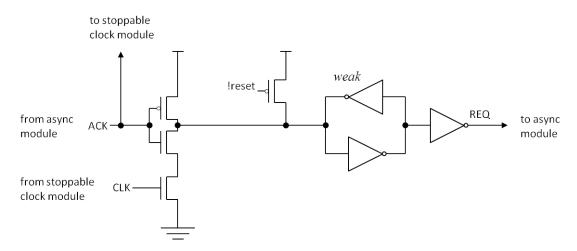

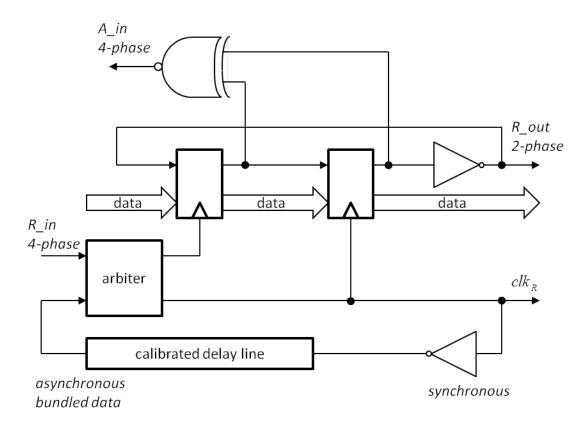

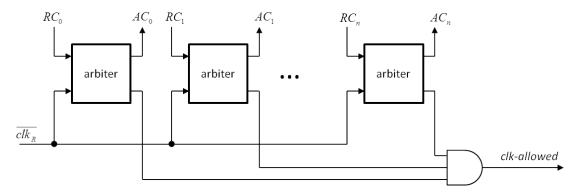

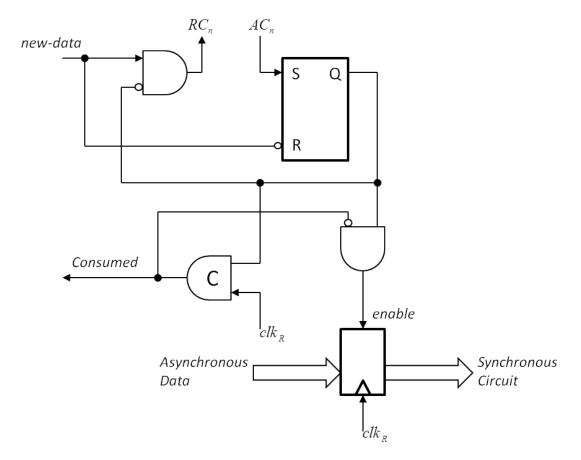

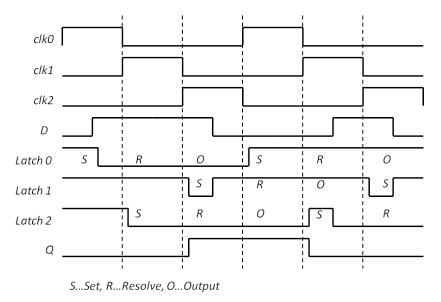

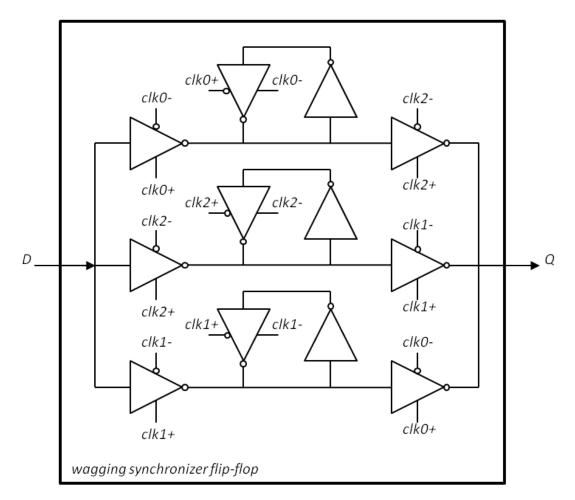

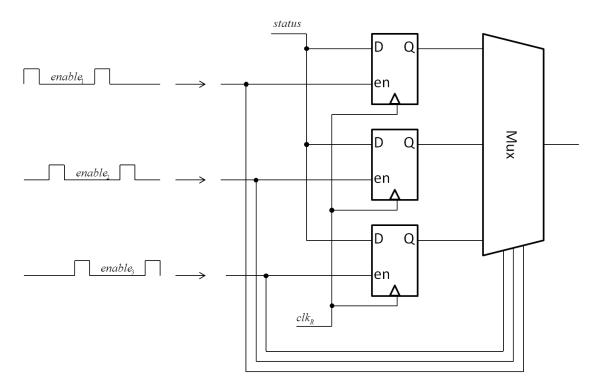

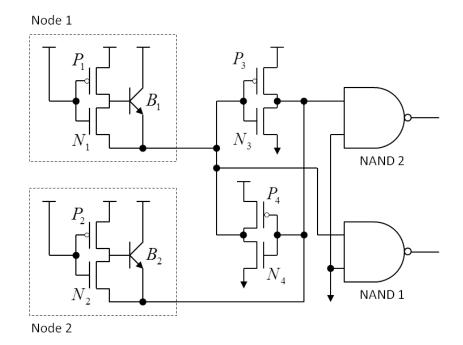

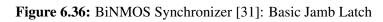

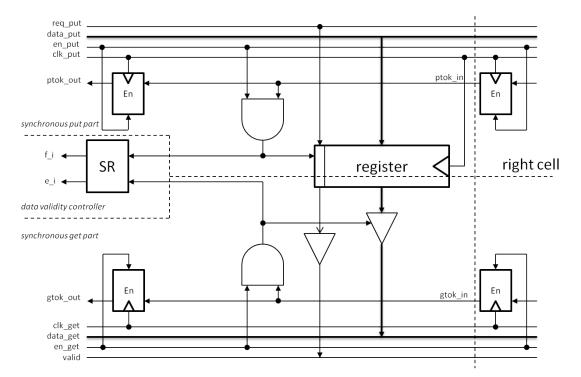

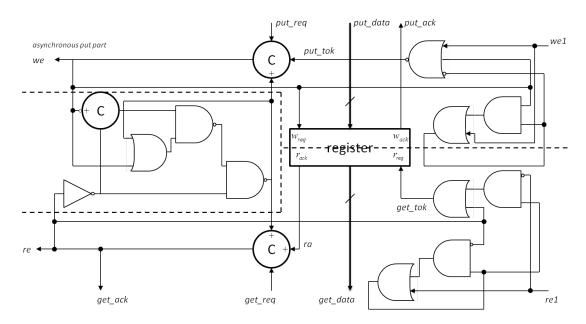

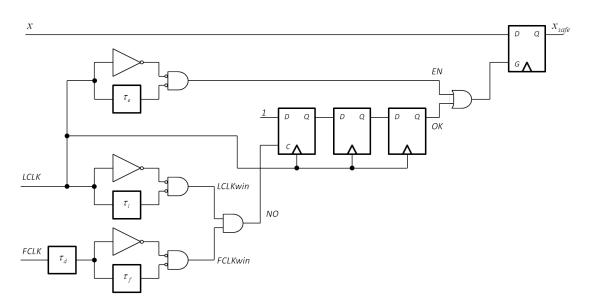

All the plesiochronous synchronizers presented in this chapter basically use the same concept. They synchronize a signal (transmitter's clock, resynchronization signal or strobe signal) from the transmitter to control a multiplexer that switches between a latch with the directly latched (unmodified) data item and a delayed version of it. The *Plesiochronous FIFO Synchronizer* uses a resynchronization mechanism to align the "read pointer" of the receiver to the "write pointer" of the transmitter, so that the receiver always samples the oldest value (more time for metastability resolution). The *Periodic Asynchronous Synchronizer* and the *Low-Latency Plesiochronous Data Retiming* approach directly influence the data stream by adding a delay upon the detection of a change of data within the exclusion region of the clock. At last the *Low-Latency and Low-Overhead Plesiochronous Synchronizer* works like the Low-Latency and Low-Overhead Mesochronous Synchronizer, but employs a continuous learning phase for the *strobe* signal that controls the input data latches (enable input) and further the used multiplexers.