**Building Robust GALS Circuits**

## Fault-Tolerant and Variation-Aware Design

## **Techniques for Reliable Circuit Operation**

### DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

## Doktor der technischen Wissenschaften

by

#### Jakob Lechner

Registration Number 0226071

to the Faculty of Informatics at the Vienna University of Technology

Advisor: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger

The dissertation has been reviewed by:

(Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger) (Prof. Jens Sparsø)

Wien, 29.04.2014

(Jakob Lechner)

## Erklärung zur Verfassung der Arbeit

Jakob Lechner Zur Spinnerin 22/11, 1100 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

## Acknowledgements

I would like to thank Prof. Andreas Steininger for his excellent supervision of my PhD research, his invaluable technical and scientific insights during our discussions and his support and encouragement, which never failed to boost my motivation. He significantly influenced my academic career at an early stage with his remarkable lecture on digital circuit design. In this lecture he was able to spark my interest for the field, which ultimately led to the completion of this thesis.

Many thanks have to be given to my colleagues and friends from the Embedded Computing Systems group, Markus Ferringer, Matthias Függer, Marcus Jeitler, Alex Kößler, Robert Najvirt, Rameez Naqvi, Thomas Polzer, Thomas Reinbacher, Varadan Savulimedu Veeravalli and Martin Zeiner. I want to thank them for all the helpful and inspiring discussions, the collaboration in research projects and the late hours spent together when a paper submission deadline was approaching. The great team spirit and companionship is what makes this research group special.

Furthermore, I would like to thank Prof. Ulrich Schmid for the opportunity to perform my research as a part of the FATAL project<sup>1</sup>. Thank you also has to be said to Traude Sommer for her administrative support and her efforts to remind me to go home when time was getting late.

With great appreciation I also want to thank Prof. Alex Yakovlev from the Newcastle University. Due to his support I was able to join his research group as a guest researcher for half a year. This visit<sup>2</sup> was a fantastic opportunity to meet and work with excellent researchers and allowed me to perform the final steps towards the completion of my thesis.

A big thank you goes to all my friends who spent time with me outside of the university and helped me to forget about my research once in a while and enjoy my free time.

Finally, I want to express my deepest gratitude to my parents, my brother and my sister for their lifelong support and love! Thank you!

<sup>&</sup>lt;sup>1</sup>This work received funding from the Austrian Science Foundation (FWF): FATAL project, no. P21694.

<sup>&</sup>lt;sup>2</sup>The visit in Newcastle was supported with a Marietta Blau Grant of OeAD – GmbH, funded by the Austrian Federal Ministry of Science and Research (BMWF).

## Abstract

Digital integrated circuits perform computations following a well-defined functional specification. Any deviation from the circuit's expected behaviour breaks the boundaries of this specification and can therefore lead to unknown and unwanted circuit states, miscomputations and ultimately a service failure. Today transient faults are responsible for most of the circuit failures. They are typically triggered by adverse external influences like radiation, electromagnetic interference or variations of supply voltage and ambient temperature during operation. Faulttolerance is the capability of a circuit to maintain its correct operation despite of such effects.

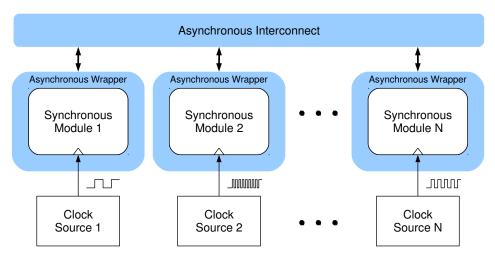

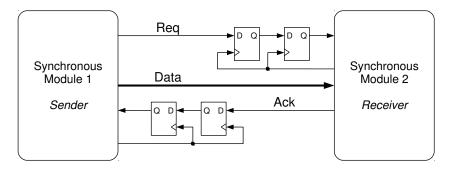

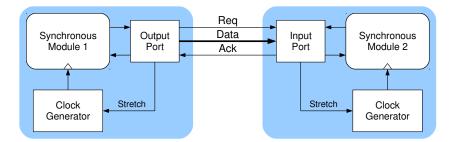

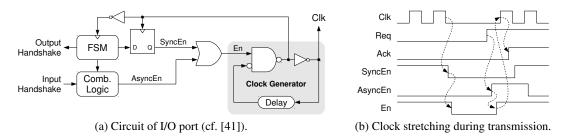

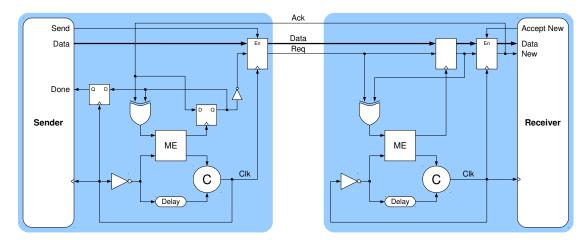

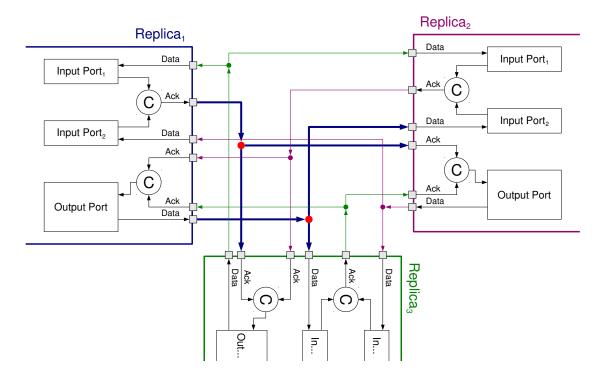

In this thesis we investigate fault-tolerance mechanisms applied to GALS-style circuits. GALS, short for *globally asynchronous locally synchronous*, is a design paradigm, which partitions a complex circuit into several locally synchronized modules and performs data transfers between these modules by means of asynchronous handshake channels. This is a systematic approach to reduce timing dependencies in circuits and therefore ease their physical implementation. Based on the fundamental structure of GALS circuits, this thesis is split into a part dedicated to fault-tolerant computation in synchronous modules and a part, where mechanisms for reliable data transfers in asynchronous communication channels are explored.

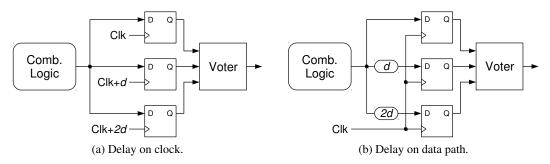

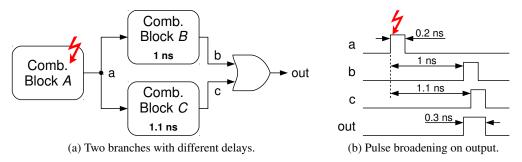

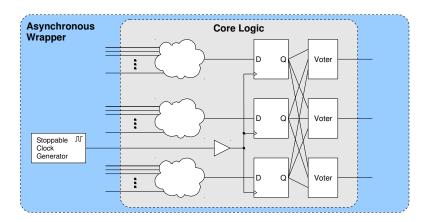

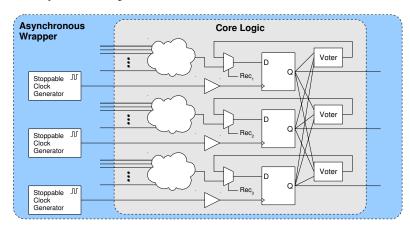

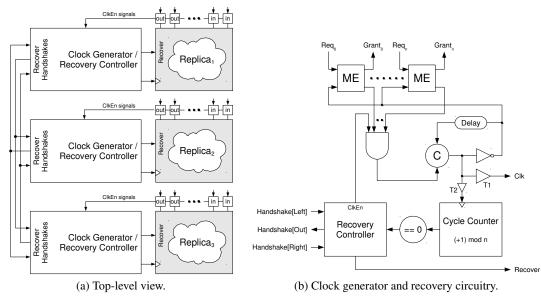

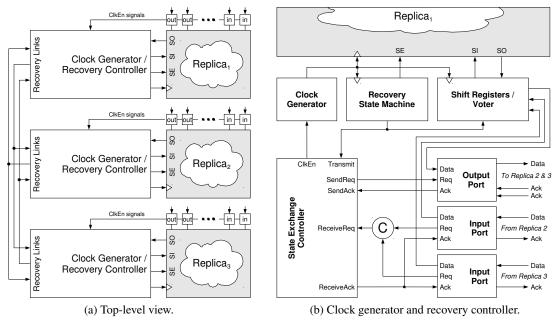

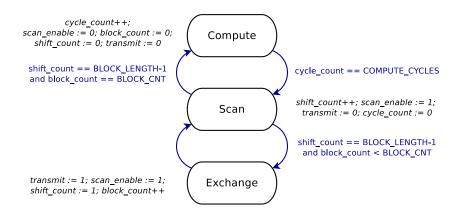

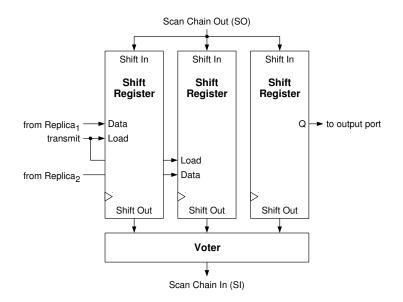

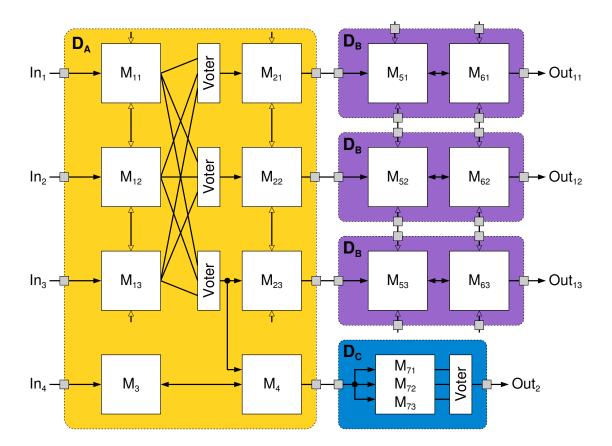

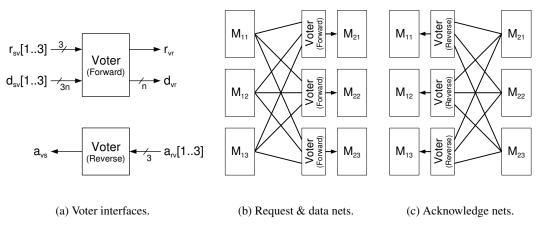

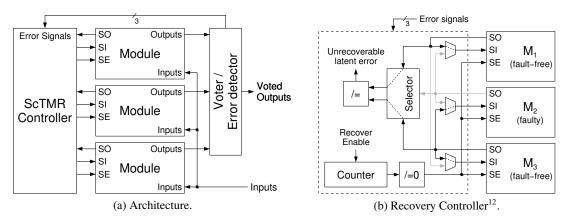

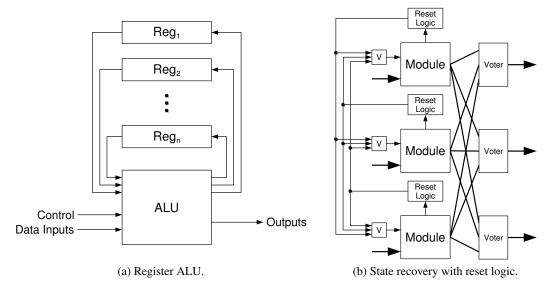

For fault-tolerant computation we propose two new *modular redundant* circuit architectures. The key concept in both cases is to apply full replication to all circuit elements of the targeted GALS module, including the clock source and the clock tree. In contrast to conventional modular redundant circuits, replicated units can therefore be operated with independent clock signals. This simplifies circuit timing and increases flexibility with respect to the physical partitioning of redundant components. State restoration is performed at dedicated checkpoints, which are interwoven with regular computation cycles. Stoppable clocks, commonly used in GALS circuits for safe data exchange among locally synchronous modules, provide the underlying framework for executing the recovery process at these checkpoints. While the proposed architectures share the same basic idea, we engage two different methods for state exchange and majority voting during the recovery and compare their area, performance and reliability properties.

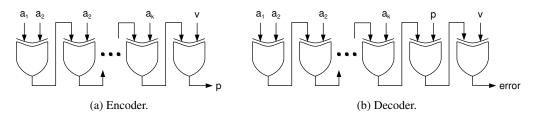

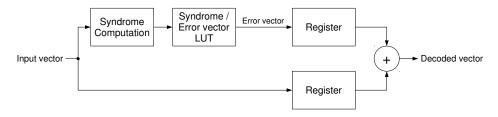

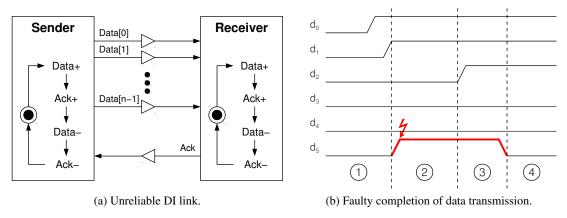

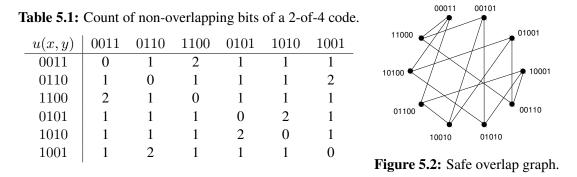

In the second part of the thesis we advocate for the combination of *delay-insensitive* and *error detecting codes* to build asynchronous communication channels between GALS modules. This approach integrates *variation tolerance* and *fault tolerance* and therefore provides a comprehensive form of robustness. First we present a systematic analysis of common delay-insensitive codes to determine their resilience against transient faults and what capabilities associated error detecting codes need to have to mitigate a certain number of such faults during a transmission. Based on these theoretical results, implementations for various encoder and decoder circuits are developed, which can offer protection against single or double faults.

## Kurzfassung

Digitale integrierte Schaltungen führen Berechnungen auf Basis einer genau definierten Spezifikation durch. Jegliche Abweichung vom erwarten Verhalten einer Schaltung kann diese Spezifikation verletzten und daher zu unbekannten und unerwünschten Schaltungszuständen, Fehlberechnungen und letztendlich zum Totalausfall der Schaltung führen. In den allermeisten Fällen sind heutzutage transiente Fehler, ausgelöst durch ungünstige externe Einflüsse wie Strahlung, elektromagnetische Interferenzen oder Spannungs- und Temperaturvariationen, verantwortlich für solche Ausfälle. Kann eine Schaltung ihre korrekte Funktion trotz dieser Effekte aufrecht erhalten, so spricht man von einem fehlertoleranten Design.

In dieser Arbeit untersuchen wir die Anwendung von Fehlertoleranz-Mechanismen im Kontext von sogenannten GALS-Schaltungen. Charakteristisch für GALS, abgekürzt für *global asynchron, lokal synchron,* ist die Aufteilung von komplexen Schaltungen auf mehrere lokal synchronisierte Module und der Einsatz von asynchronen Übertragungskanälen zum Datenaustausch. Dieser systematische Designansatz begrenzt Zeitabhängigkeiten auf einzelne Module und erleichtert somit die physische Umsetzung der Gesamtschaltung.

Im ersten Teil dieser Arbeit werden zwei neue Ansätze präsentiert, um GALS-Module mittels Mehrfachredundanz gegen Fehler zu schützen. Die Kernidee ist in beiden Fällen die vollständige Replikation aller Schaltungsbestandteile des entsprechenden GALS-Moduls, was insbesondere auch den Taktgeber und das Taktnetz einschließt. Im Gegensatz zu konventionellen redundanten Schaltungen, können replizierte Einheiten daher mit einem unabhängigen Taktsignal versorgt werden. Das vereinfacht das Zeitverhalten der Schaltungen und erhöht die Flexibilität bei der Aufteilung von redundanten Komponenten. Die Detektion und Korrektur von fehlerhaften Schaltungszuständen erfolgt zu bestimmten Kontrollpunkten, die zwischen den regulären Rechenvorgängen eingeschoben werden. Anhaltbare Taktgeneratoren, die häufig in GALS-Schaltungen für den sicheren Datenaustausch zwischen lokal-synchronen Modulen Verwendung finden, bilden die Basis für die Implementierung dieses Wiederherstellungsprozesses.

Zur zuverlässigen Kommunikation zwischen GALS-Modulen wird dann im zweiten Teil der Arbeit eine Lösung vorstellt, die zeit-insensitive (engl. delay-insensitive) und fehlerdetektierende Codes verbindet. Durch diesen Verband ist es dem Empfänger möglich sowohl Variationen im Zeitbereich, als auch Fehler im Wertebereich des übertragenen Signals zu tolerieren. Zunächst analysieren wir bekannte zeit-insensitive Codes systematisch auf ihre Widerstandsfähigkeit gegen Fehler und bestimmen die benötigte Stärke der komplementären fehlerdetektierenden Codes, um einer gewissen Anzahl von Fehlern während der Datenübertragung standzuhalten. Auf Basis dieser theoretischen Ergebnisse werden dann verschiedene Implementierungen für Kodierungs- und Dekodierungsschaltungen entwickelt und deren Eigenschaften evaluiert.

## Contents

| 1 | Intr                                                | oductio                        | n                                                        | 1  |  |  |  |  |  |  |  |

|---|-----------------------------------------------------|--------------------------------|----------------------------------------------------------|----|--|--|--|--|--|--|--|

|   | 1.1                                                 | Circuit                        | t Timing                                                 | 2  |  |  |  |  |  |  |  |

|   | 1.2                                                 | Depen                          | dable Circuits                                           | 3  |  |  |  |  |  |  |  |

|   | 1.3                                                 | Scope                          | and Methodology                                          | 4  |  |  |  |  |  |  |  |

|   | 1.4                                                 | Structu                        | ure of the Thesis                                        | 5  |  |  |  |  |  |  |  |

| 2 | Dep                                                 | Dependable Computer Systems 7  |                                                          |    |  |  |  |  |  |  |  |

|   | 2.1                                                 | Taxonomy of Dependable Systems |                                                          |    |  |  |  |  |  |  |  |

|   |                                                     | 2.1.1                          | Threats of Dependability                                 | 8  |  |  |  |  |  |  |  |

|   |                                                     | 2.1.2                          | Attributes of Dependability                              | 10 |  |  |  |  |  |  |  |

|   |                                                     | 2.1.3                          | Means to Attain Dependability                            | 14 |  |  |  |  |  |  |  |

|   | 2.2                                                 | Faults                         | in Integrated Circuits                                   | 17 |  |  |  |  |  |  |  |

|   |                                                     | 2.2.1                          | Transient Faults                                         | 17 |  |  |  |  |  |  |  |

|   |                                                     | 2.2.2                          | Permanent Faults                                         | 20 |  |  |  |  |  |  |  |

| 3 | Circ                                                | Circuits Background 2          |                                                          |    |  |  |  |  |  |  |  |

|   | 3.1                                                 | Async                          | hronous Circuit Design                                   | 21 |  |  |  |  |  |  |  |

|   |                                                     | 3.1.1                          | Delay Models and Classification of Asynchronous Circuits | 22 |  |  |  |  |  |  |  |

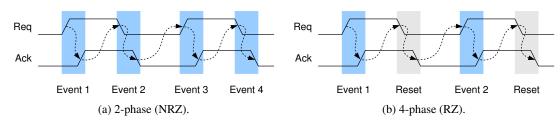

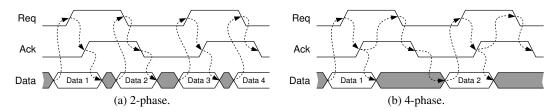

|   |                                                     | 3.1.2                          | Asynchronous Handshake Protocols                         | 23 |  |  |  |  |  |  |  |

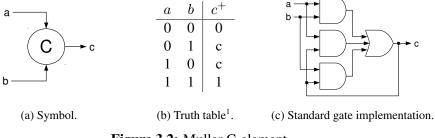

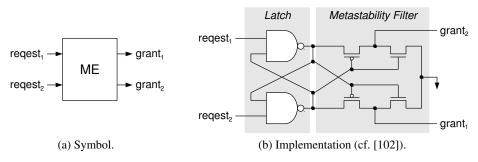

|   |                                                     | 3.1.3                          | Control Elements                                         | 24 |  |  |  |  |  |  |  |

|   |                                                     | 3.1.4                          | Datapath Implementation                                  | 25 |  |  |  |  |  |  |  |

|   | 3.2                                                 |                                |                                                          |    |  |  |  |  |  |  |  |

|   |                                                     | 3.2.1                          | Synchronization in Digital Systems                       | 29 |  |  |  |  |  |  |  |

|   |                                                     | 3.2.2                          | Brute-Force Synchronization                              | 30 |  |  |  |  |  |  |  |

|   |                                                     | 3.2.3                          | Pausible Clocking                                        | 31 |  |  |  |  |  |  |  |

|   | 3.3                                                 | Fault 7                        | Folerance in Integrated Circuits                         | 34 |  |  |  |  |  |  |  |

|   |                                                     | 3.3.1                          | Hardware Redundancy                                      | 34 |  |  |  |  |  |  |  |

|   |                                                     | 3.3.2                          | Temporal Redundancy                                      | 37 |  |  |  |  |  |  |  |

|   |                                                     | 3.3.3                          | Information Redundancy                                   | 38 |  |  |  |  |  |  |  |

| 4 | Fault-tolerant Computation in Synchronous Modules 4 |                                |                                                          |    |  |  |  |  |  |  |  |

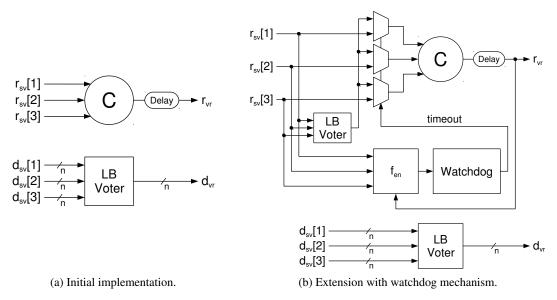

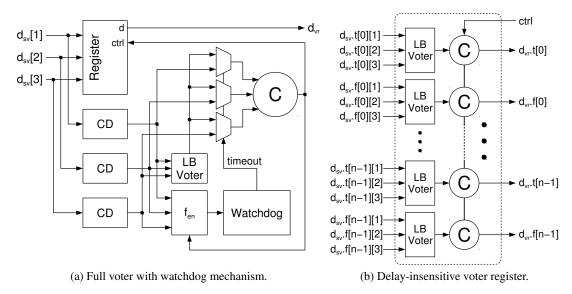

|   | 4.1                                                 |                                | ar Redundancy in GALS                                    | 43 |  |  |  |  |  |  |  |

|   | 4.2                                                 |                                | ach I: Parallel Recovery                                 | 45 |  |  |  |  |  |  |  |

|   |                                                     |                                |                                                          |    |  |  |  |  |  |  |  |

|   |            | 4.2.1  | Recovery Controller                                           |

|---|------------|--------|---------------------------------------------------------------|

|   |            | 4.2.2  | Timing Constraints48                                          |

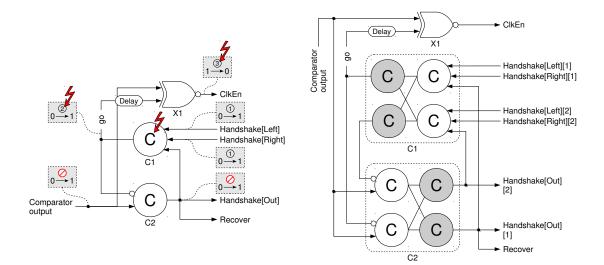

|   |            | 4.2.3  | Robustness of the Recovery Circuitry                          |

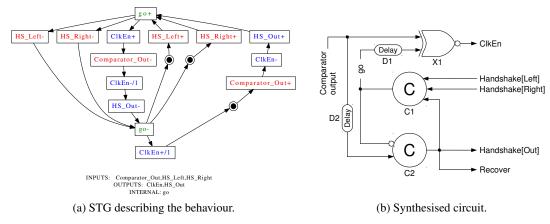

|   |            | 4.2.4  | Formal Verification of the Recovery Controller                |

|   |            | 4.2.5  | Area & Performance                                            |

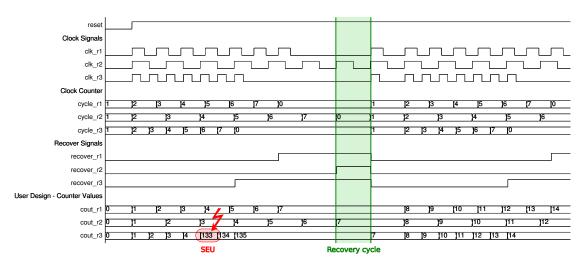

|   |            | 4.2.6  | Proof of Concept                                              |

|   | 4.3        | Appro  | ach II: Serial Recovery                                       |

|   |            | 4.3.1  | Recovery Controller                                           |

|   |            | 4.3.2  | Timing Constraints    61                                      |

|   |            | 4.3.3  | Robustness of the Recovery Controller                         |

|   |            | 4.3.4  | A Short Note on Long Faults (Permanent Defects)               |

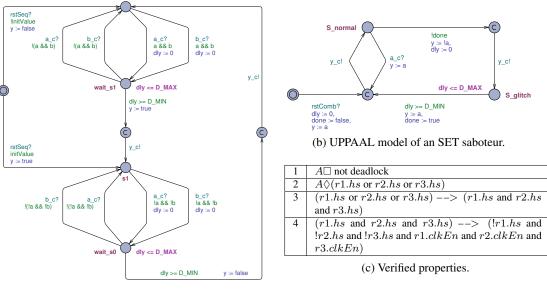

|   |            | 4.3.5  | Verification                                                  |

|   |            | 4.3.6  | Area & Performance                                            |

|   | 4.4        | Systen | n Architecture                                                |

|   |            | 4.4.1  | Selective Hardening of GALS Modules                           |

|   |            | 4.4.2  | Replica Partitioning                                          |

|   |            | 4.4.3  | Voting on Output Data                                         |

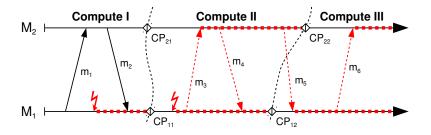

|   | 4.5        | Recove | ery Strategy                                                  |

|   |            | 4.5.1  | Recovery Period                                               |

|   |            | 4.5.2  | Minimising the Recovery State                                 |

|   |            | 4.5.3  | Replica Determinism                                           |

|   |            | 4.5.4  | System-Level Considerations                                   |

|   | 4.6        | Systen | n Evaluation                                                  |

|   |            | 4.6.1  | Design Automation                                             |

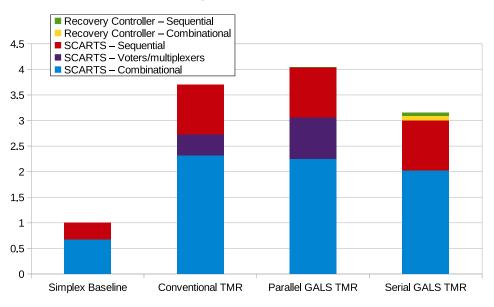

|   |            | 4.6.2  | Area & Performance                                            |

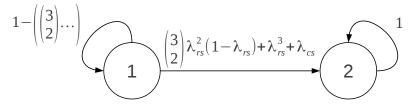

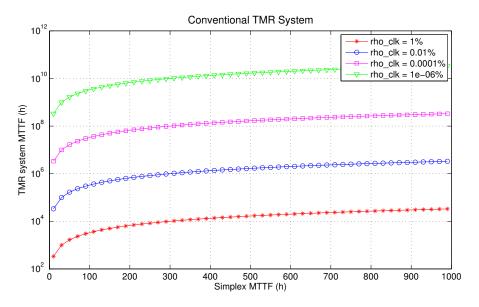

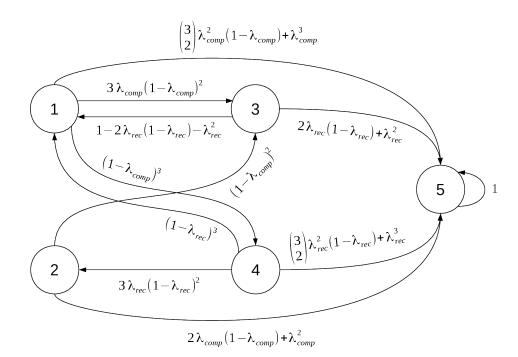

|   |            | 4.6.3  | Reliability                                                   |

|   | 4.7        | Relate | d Work                                                        |

| _ | <b>D</b> 1 |        |                                                               |

| 5 |            | •      | nchronous Inter-Module Communication Channels 101             |

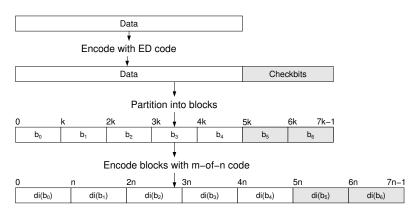

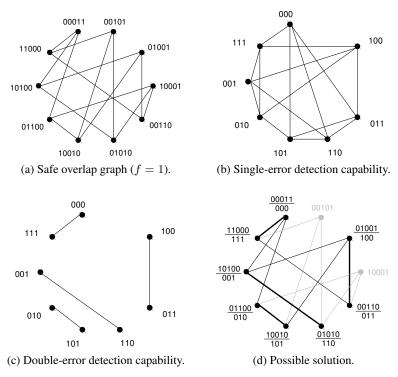

|   | 5.1        | -      | Insensitive Fault-Tolerant Codes                              |

|   |            | 5.1.1  | Problem Description: Transmission Faults                      |

|   |            | 5.1.2  | Formal Prerequisites                                          |

|   |            | 5.1.3  | Building Subcodes                                             |

|   | 5.0        | 5.1.4  | Combining DI and ED Codes                                     |

|   | 5.2        |        | ach I: Robust 4-phase Dual-rail Channels                      |

|   |            | 5.2.1  | Fault Model                                                   |

|   |            | 5.2.2  | Proposed Implementation                                       |

|   |            | 5.2.3  | Metastability-Tolerant Implementation                         |

|   |            | 5.2.4  | Implementation Details       120         Evaluation       121 |

|   | 5 0        | 5.2.5  | Evaluation                                                    |

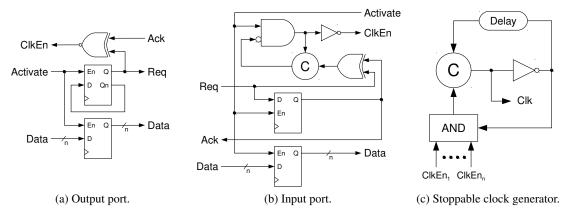

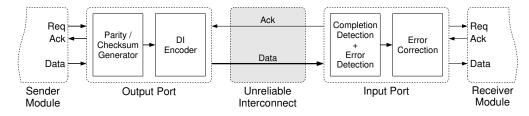

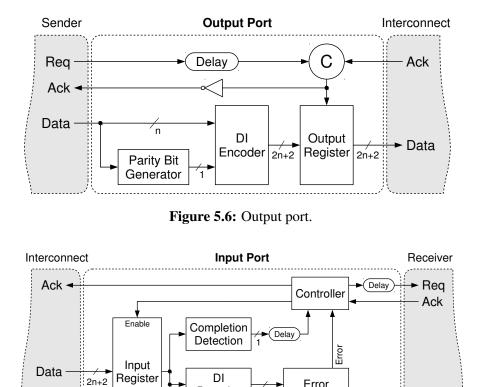

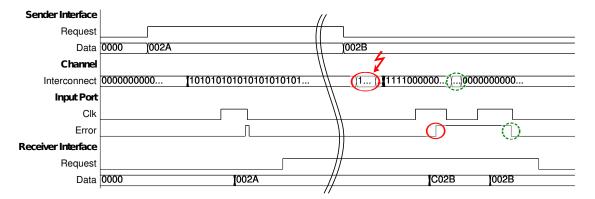

|   | 5.3        |        | ach II: A Generic Sender/Receiver Implementation              |

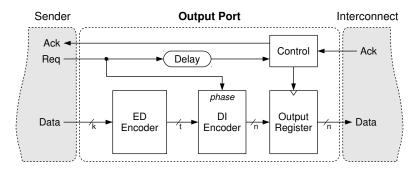

|   |            | 5.3.1  | Output Port                                                   |

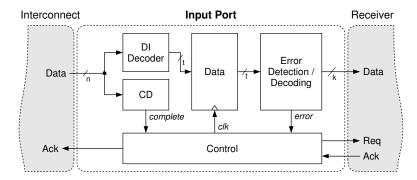

|   |            | 5.3.2  | Input Port                                                    |

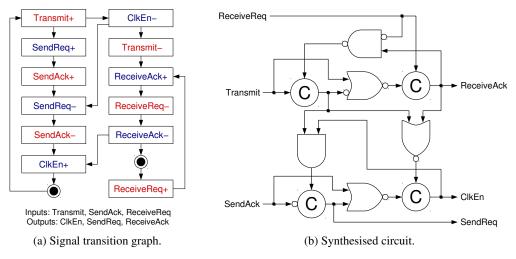

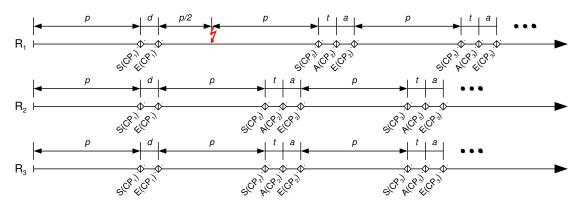

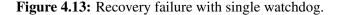

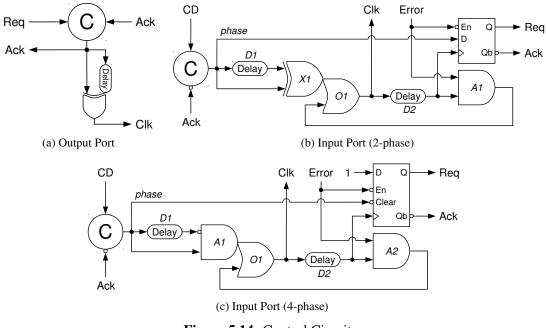

|    |                      | 5.3.3 Control Circuits                         | 126 |  |  |  |  |  |  |

|----|----------------------|------------------------------------------------|-----|--|--|--|--|--|--|

|    |                      | 5.3.4 Evaluation                               | 128 |  |  |  |  |  |  |

|    | 5.4                  | Related Work                                   | 129 |  |  |  |  |  |  |

| 6  | Sum                  | amary & Conclusion                             | 137 |  |  |  |  |  |  |

| 7  | Future Work          |                                                |     |  |  |  |  |  |  |

|    | 7.1                  | Mesochronous Modular Redundant Systems         | 141 |  |  |  |  |  |  |

|    | 7.2                  | Reconfigurable GALS Architectures              | 142 |  |  |  |  |  |  |

|    | 7.3                  | Recovery of Memory Cells                       | 143 |  |  |  |  |  |  |

|    | 7.4                  | Robust 2-phase Delay-Insensitive Codes         | 144 |  |  |  |  |  |  |

|    | 7.5                  | Comprehensive Evaluation of Robust DI Channels | 144 |  |  |  |  |  |  |

| A  | Additional Resources |                                                |     |  |  |  |  |  |  |

|    | A.1                  | Scripts for Fault-Injection Experiments        | 145 |  |  |  |  |  |  |

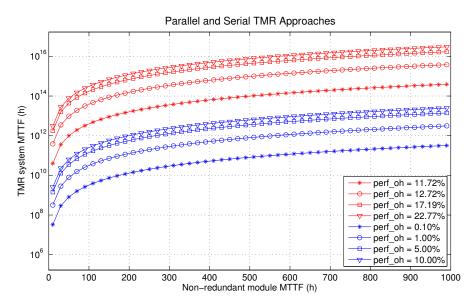

|    | A.2                  | Reliability Evaluations                        | 146 |  |  |  |  |  |  |

| Bi | Bibliography         |                                                |     |  |  |  |  |  |  |

## CHAPTER

## PTER

## Introduction

Integrated circuits have made their way into almost every aspect of our lives and have been able to fundamentally change the way how we work, spend our free time, obtain information and communicate. They can be found in general purpose hardware like classical personal computers, servers or notebooks, as wells as in mobile devices like tablets, smart phones or wearable computers. Mobile computers in particular have been transforming how we interact with the digital world in the past few years (and will potentially continue to do so in the years to come). Beyond that there is an abundance of applications in embedded systems, usually designed to perform a very specific function. These applications range from ordinary household appliances and consumer electronics like dishwashers, MP3 players, digital cameras, etc. to professional equipment used, e.g., in telecommunication or medical systems. Large numbers of embedded devices can also be found in all modern means of transportation like cars, aircraft or trains.

Semiconductor technology, the propellant behind this digital revolution and precursor of the information age, has undergone a remarkable and fascinating evolution in the past six to seven decades. Even though the first discoveries in the field of semiconductors date back to the 19th century [128], a pivotal moment for the emergence of integrated circuits, as we know them today, is the development of the transistor. In 1947 John Bardeen and Walter Brattain demonstrated the first transistor design at Bell Labs and only one year later William Shockley proposed an improved device, known as the bipolar junction transistor [93]. The fabrication of the first MOSFET device, just about a decade later in 1960, by John Atalla and Dawon Kahng then spurred an unprecedented technological race. Driven by advances in fabrication and process technology, transistor sizes kept shrinking continuously and the number of transistors that could be built into an integrated circuit grew exponentially. Just within fifty years industry went from chip designs with a couple hundred transistor to today's processors, graphics cards and FPGAs, containing several billions of transistor devices. Technology scaling and rising integration densities, allowing for powerful chip designs at reduced costs, were and still are the backbone of the semiconductor success story.

#### 1.1 Circuit Timing

The progress of semiconductors in the last decades, however, has not been possible without severe problems to solve, without tremendous efforts both in academic and industrial research institutions to deepen our understanding of physical processes, to develop increasingly intricate fabrication methods, and figure out ways to deal with rising design complexities. As industry today is determined to continue scaling following *Moore's Law* [74], the battle to keep pushing the boundaries is still astir and with every technology node new challenges appear.

An increasingly severe problem of chip designs fabricated at 90 nm and below is circuit timing. Timing plays a key part in the overall design process because computations are usually synchronized with the help of a global clock signal, which controls all sequential elements in the circuit. This clock, being a periodic signal, enforces a rigid time base for the switching activities of all other signals. Thus, timing of every signal in such a *synchronous* design needs to be carefully analysed to make sure that all signals comply with the timing constraints (setup/hold constraints) mandated by the clock signal. One reason why this analysis has become more and more difficult with recent technology nodes is the massive imbalance how gate and interconnect delays are affected by scaling. While gate delays generally have been on the decline with every new technology generation, the opposite is true for interconnect delays: Due to longer and thinner wires, as well as smaller wire pitches, interconnect RC delays have deteriorated significantly, as can be seen in [44, 45]. These scaling trends have shifted the earlier dominance of gate delays as the main contributor to total circuit delays towards interconnect delays. In recent technologies relative gate and interconnect delays differ by approximately three orders of magnitude [44]. This has severe impacts on the design flow of integrated circuits. While gate delays are known relatively early in the implementation process, basically right after synthesis, interconnect delays can only be modelled when the final chip layout has been performed, i.e., close to the end of the design flow. If unresolvable timing violations are uncovered at this stage, a complete redesign and reimplementation of the circuit might be unavoidable.

Another side effect of aggressive scaling are timing uncertainties, e.g., caused by process variations. To guarantee correct circuit operation these uncertainties have to be accounted for, usually by adding conservative timing margins (and thereby reducing the performance gains again, which we expect by downscaling feature sizes). Process variations originate from imperfections in chip fabrication, which can be traced back to random processes during the placement of dopants, or limited resolution of lithographic fabrication steps [121]. At nanometre scale these variations have a significant impact on crucial device parameters like oxide thickness, channel length and width, doping profiles, as well as interconnect geometries (wire width/thickness). The gate oxide thickness of transistors, e.g., can be controlled with an astounding accuracy of 1 to 2 atom layers. However, in 30 nm and below the gate oxide only consists of approx. 5 to 15 atom layers [121]. Consequently one or two layers more or less can already make a notable difference. The same is true for the placement of impurities in the channel region. With technology nodes below 90 nm the number of dopant atoms is less than hundred, somewhere in the order of a few tens of atoms [121]. Depending on the specific technology used, process variation-related timing uncertainties can account for up to 30% of the overall timing budget [108].

A final key challenge we want to address here is the design of clock trees [45]. The clock

signal is distributed to all sequential endpoints, which are usually scattered all over the entire chip area. To achieve high circuit performance the skew and jitter of the clock signal need to be rigorously minimised. However, when dealing with large clock trees and high frequencies, layout has become a rather cumbersome task. Growing interconnect delays and process variations, as discussed above, further complicate this design challenge: In large clock trees, sometimes with latencies of several clock cycles, process variations can have a detrimental effect on skew and jitter [13]. Therefore careful routing of the clock net is required, e.g., by using symmetric tree layouts like H-trees. Furthermore an optimal buffer placement and sizing has to be found to evenly distribute clock transitions and drive all loads connected to the clock net typically is the most active signal of the circuit. In extreme cases the clock tree's share of total power consumption has been reported to be as high as 40% [24].

Because of the above mentioned issues (and others we did not discuss), globally synchronous circuits with a single clock domain are mostly a thing of the past [109]. Nowadays circuit designers are dealing with complex synchronous systems that incorporate several clock domains, usually running at different clock frequencies. Exchanging data across clock domains requires manual insertion of synchronizer circuits to make sure that incoming data can be safely processed at the receiver side. For complex systems with many clock domain crossings this work can become rather tedious and also error-prone, with severe consequences on the circuit's reliability, if done wrong. The globally asynchronous locally synchronous design (GALS) paradigm offers a more robust and systematic approach to integration of separately clocked circuit modules: Communication between these locally synchronous modules is performed across asynchronous links, using handshake protocols to enable safe data transfers. This methodology decouples sender and receiver clock domains and eliminates the need for a global clock distribution network. Locally synchronous modules are clocked independently with individual clock frequencies adapted to their specific requirements and capabilities. With local modules that are more compact and smaller in size the design of the local clock tree is simplified [30] and wire lengths of intra-module interconnects can potentially be reduced. Timing problems thus become more manageable and constraints can be easier met. Since even the latest ITRS report mentions asynchronous global signalling as a desirable capability for future technologies [45], it can be expected that GALS architectures will gain in importance.

#### **1.2 Dependable Circuits**

Next to performance or power efficiency, dependability can also be an essential requirement for integrated circuits. In safety-critical systems, like airplanes or spacecraft, nuclear power plants, transportation systems etc. high dependability is of utmost importance since a failure can potentially threaten human lives, or cause significant environmental damages. Reliable operation also needs to be specifically addressed for systems that operate in harsh environments, like satellites in space, where increased radiation levels can cause malfunctions of onboard electronics. For other applications, where a failure does not necessarily lead to a severe catastrophe, high availability might still be required because service stops are extremely inconvenient for users or cause notable financial losses.

Since we are on the brink of exciting new developments like commercial space travel or autonomously driving cars, it can be expected that there will be a continuous, if not increasing, demand in dependable integrated circuit architectures, which will potentially have to meet more stringent requirements on computational performance and power-efficiency. However, while large complex designs with high processing speeds can be implemented in modern semiconductor technology, reliability has become a major concern. Due to aggressive technology scaling, leading to reduced feature sizes and reduced supply voltages, integrated circuits have become much more susceptible to faults [10, 94], both of transient and permanent nature. While in the former case, errors vanish after some time or can be corrected, permanent faults are caused by damages in the physical structure of the die and will not disappear. Today transient faults are responsible for most of the circuit failures [114]. They are typically triggered by adverse external influences like radiation, electromagnetic interference or variations of supply voltage and ambient temperature during operation. Radiation effects, typically referred to as single event effects, can produce unwanted voltage pulses in an integrated circuit that might lead to miscomputations and the corruption of the circuit state, which is maintained in storage elements like flip-flops or memory cells. Unaccounted voltage or temperature variations can compromise system timing in rigid synchronous circuits, again resulting in potential miscomputations and erroneous outputs.

To meet the demand of dependably operating circuit designs, fault tolerance has been an active and thriving research area in the past decades. One of the first seminal works on this subject was performed by John von Neumann and published in 1956 in a paper, which describes how reliable systems can be built from unreliable components [117].

#### **1.3 Scope and Methodology**

In this thesis we are going to present our research results on robust GALS-based circuit architectures, which tackle current and future circuit design challenges, especially related to timing, and also provide correct operation in the presence of external faults like single event effects or internal faults such as process variations. We were interested to explore how fault tolerance mechanisms can be applied to such circuit architectures and whether there are any benefits in comparison to fault tolerance in classical all-synchronous designs. As described above, GALS circuits consist of a) multiple synchronous modules, which perform computations, and b) asynchronous communication channels between these modules. Therefore, our research efforts were devoted to hardening these two integral circuit parts, i.e., the computation and communication components of a GALS system. It was a fascinating aspect of our research that this distinctive architecture of GALS systems allowed us to investigate quite different sets of fault tolerance mechanisms, which account for the fundamentally different function and structure of computation and communication systems: While we explored replication-based techniques for GALS modules (modular redundancy), building robust asynchronous communication channels mainly involved protection with error detecting and correcting codes. Even though the presented techniques can cope with permanent faults to some extent and there is a brief discussion on this in Chapter 4, we focus on the mitigation of transient faults, so called single event transients (SETs) and single event upsets (SEUs). Dealing with permanent faults requires quite different counteractive measures, which puts them out of scope for this work.

In order to evaluate the viability of the proposed fault tolerance techniques, the associated circuits were first modelled on register transfer- or gate-level and then synthesised and mapped to a suitable CMOS technology (90 nm in our case, using an industrial-grade standard cell library). Functional verification as well as performance analysis was then performed with the synthesised netlists. We are aware that the accuracy of pre-layout timing annotations is suboptimal, however, for the purpose of comparing different solutions we consider this approach to still yield meaningful results. Verification of the behaviour in the presence of faults was partly done by running exhaustive fault-injection experiments in a simulator, and partly with model checking techniques to formally prove desired liveness and safety properties for smaller subcircuits. Reliability evaluation was performed with Markov chain models to derive formulas for the mean time to failure (MTTF), based on failure and recovery rates as basic parameters.

#### **1.4** Structure of the Thesis

In Chapter 2 we will present a basic taxonomy of dependable computer systems, including concise definitions of relevant terms like *faults*, *errors* and *failures*. Most importantly the concept of reliability is introduced, along with mathematical definitions for MTTF, or reliability and failure rate functions. Furthermore we will address dependability threats in digital integrated circuits in this chapter, first to give an overview on the specific terminology that has been coined in this research area, and secondly to get the reader acquainted with the origins of faults and failure mechanisms in integrated circuits, both transient and permanent. Chapter 3 is intended to provide the necessary circuit-related background for the main part of the thesis. Thus, we give a brief introduction to asynchronous logic and handshaking protocols, present previous work on GALS systems and existing solutions with respect to communication issues between locally synchronous modules. A third section in this chapter then is devoted to fault-tolerant circuit design and the available techniques for leveraging either hardware, time or information redundancy.

The main pillars of this thesis are Chapter 4 and 5. As mentioned above, our research work is partitioned into fault tolerance techniques for locally synchronous modules and asynchronous interconnects. This thesis is structured accordingly. First we will present two approaches for incorporating modular redundancy into GALS circuits. While the system-level fault tolerance concept for both approaches is the same, they use different methods for state recovery, which lead to interesting differences in circuit structure and associated properties. In Chapter 5 we turn to asynchronous interconnects, where we strive for solutions that provide a comprehensive form of robustness, which combines both variation and fault tolerance. Our approach therefore advocates the fusion of delay-insensitive and error detecting/correcting codes. First a theoretical analysis is performed to elaborate what codes can be paired to achieve tolerance against a certain number of faults. Afterwards we present two link architectures along with specific circuits for sender and receiver components, ready to be integrated into I/O wrappers of GALS modules. An overview of the related work will be given at the end of each main chapter, where we elaborate on commonalities and differences in comparison to the methods we propose.

In Chapter 6 we summarise the presented research results and draw our conclusions. The thesis then ends with a short final chapter on possible directions for future work.

# CHAPTER 2

## **Dependable Computer Systems**

According to [8] dependability is the ability of a (computer) system to "avoid service failures that are more frequent and more severe than is acceptable". Basically dependability is a measure to what extent a user can trust that a system will deliver a service or a set of services that complies with the specification, or ultimately with the user requirements. In this chapter we will introduce elementary concepts of dependable systems in general and how they relate to digital circuits in particular. We want to present a concise taxonomy of the concepts and the terminology that will be used throughout this thesis.

#### 2.1 Taxonomy of Dependable Systems

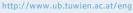

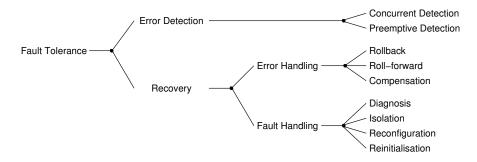

The availability of a concise taxonomy for concepts related to dependability along with a welldefined terminology is of vital importance for researchers and engineers working in this field. It allows the development of a clear understanding of the problems and challenges that have to be faced, and most notably provides a common view and vocabulary that enables experts to discuss general concepts and specific techniques, both new and old. Since dependability is a very broad area and a plethora of researchers and engineers have contributed to it in the last decades, the used terminology to describe certain concepts or phenomena is often slightly different or even inconsistent from author to author<sup>1</sup>. Thus, a first effort to develop a unified taxonomy was undertaken in 1980, when a joint committee on "Fundamental Concepts and Terminology" was formed by the Technical Committee on Fault-Tolerant Computing of the IEEE Computer Society and an IFIP work group on Dependable Computing and Fault Tolerance [8]. Since then many discussions have led to the continuous refinement of dependability concepts and also an integration of security aspects. The most recent publication, giving a comprehensive and elaborated description of the taxonomy dependable and secure computing, is [8]. An outline of this taxonomy is depicted in Figure 2.1. As can be seen, all aspects of dependability and security are partitioned into three fundamental categories: Attributes, Threats and Means.

<sup>&</sup>lt;sup>1</sup>A wide-spread imprecision, e.g., is the synonymous use of the terms "transient fault" and "soft error".

Figure 2.1: Taxonomy of dependability and security concepts.

#### 2.1.1 Threats of Dependability

Threats to the dependability of a system can be explained by three core concepts: *faults*, *errors* and *failures* [8]. Each of these concepts describes a specific class of phenomena, events or system states that occur during the transition of a system from a state of correct operation to a state where it no longer follows its intended function.

#### Failures

The service of a system can be expressed as a sequence of externally-visible state changes, as perceived by the users of the system. A service or system failure, short failure, therefore denotes the transition from a state where the system delivers a correct service, i.e., operates within its specified function, to a state of incorrect service [8]. The definitions of reliability, availability and safety we will present below all relate to the concept of failure. Failures can be described with a set of *failure modes*, which are characterised from different viewpoints, like the *failure domain*, consistency, or the severity of a failure's consequences. The failure domain is partitioned into content failures (with correct timing) and timing failures (with correct content). Obviously, content and timing failures can also occur simultaneously. In the best case a system simply stops its service (*halt failure*), in the worst case the behaviour becomes erratic [8] and wrong data is produced at wrong points in time (babbling idiot [111]). The concept of consistency refers to how a failure is perceived by the system's users. If all user see the same failing behaviour, this is called a *consistent* failure, otherwise the failure is classified as *inconsistent*. The latter failure type is quite difficult to detect and mitigate, since it can trick correct components into an inconsistent behaviour. In literature inconsistent failures often are referred to as two-faced, byzantine, or malicious failures [55].

#### Errors

An *error* is an incorrect system state, which in a digital computer system is typically manifested by wrong data stored in some kind of memory element, like a flip-flop or an SRAM cell. An error may lead to a failure, when it influences the system's service and its effects become externally visible. Thus, a system failure can also be understood as an error in some external service interface. If the presence of an error is indicated by some form of signal, an error is said to be *detected*. Undetected errors are called *latent errors* [8]. Note that an error does not necessarily need to cause a failure, as it could be overwritten before the erroneous data is processed.

#### Faults

In [78] a *fault* is described as "anomalous physical condition" that affects the system behaviour in some way and can ultimately lead to an error. If a fault causes an error, it is said to be *active*, otherwise the fault is *dormant*. In [8] faults are classified in elementary fault classes, such as:

- Phase of creation: A fault might occur during the *development phase* or during the *use phase*. The development phase includes all activities until a system can be deployed and is ready for use, e.g., initial concept, specification, implementation, verification, fabrication, installation, etc. The use phase begins when system starts its operations and provides its designated service to the respective end user(s).

- System boundaries: An important classification is based on the origin of a fault, which can be either inside or outside the system boundaries. In the former case we refer to *internal faults*, in the latter case to *external faults*. Internal faults might be design flaws, broken hardware components due to manufacturing defects or wearout, etc. External causes among others are incorrect inputs, or harsh environmental conditions such as temperature variations, radiation, or electromagnetic interference [78].

- Persistence: Faults can either be of *transient* or *permanent* nature. Transient faults are bounded in time and vanish without any explicit repair action [55]. Ionising radiation, e.g., is a typical source for transient faults. Permanent faults, like physical defects in a circuit, do not disappear on their own. They persist until the condition has been repaired.

- Phenomenological cause: Natural faults vs. human-made faults.

- Objective: *Malicious* vs. *non-malicious faults*. Malicious faults are caused by a human with the purpose to harm the system (the term "malicious" in this context should not be confused with "malicious (byzantine) failures").

#### The Relationship between Faults, Errors and Failures

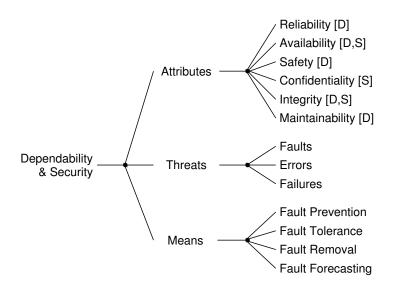

Figure 2.2a illustrates how a fault can lead to an error and consequently to a system failure. The fault can either originate from an internal source or can be caused by some event outside the system boundaries (external fault). The process when a fault turns into an error is called *fault activation*. Once some part of a system is erroneous, the error might be *propagated* to other parts

as a result of the system's computation steps. As soon as an error reaches a service interface, a failure occurs as the (sub)system deviates from its specified behaviour. This failure can then be understood as a fault for another subsystem that uses the services provided by the failed system. Figure 2.2b summarises the relationships between faults, errors and failures.

Figure 2.2: Faults, Errors and Failures.

#### 2.1.2 Attributes of Dependability

Attributes refer to properties a dependable and/or secure computer system might need to have to some extent, depending on the specific application and the users' requirements. The primary attributes identified in [8] are: *Reliability, Availability, Safety, Confidentiality, Integrity* and *Maintainability*. In Figure 2.1 we have tagged these attributes with capital D and S to highlight their relationship to either dependability or security. As can be seen some attributes are relevant for dependability, some for security, and some relate to both fields. Please note that this classification does *not* say that maintainability, e.g., is only important for dependable, and not at all for secure systems. The given allocation of attributes is only supposed to give an idea where the primary concerns of the respective systems lie. Note that security, even though it is a matter of vital importance, is currently not on our research agenda. Therefore, we will only discuss the mentioned attributes with respect to their significance for dependable systems.

#### Reliability

The ability of an item to perform a required function, under given environmental and operational conditions and for a stated period of time (ISO8402).

High reliability is crucial for systems where a single deviation from the expected behaviour would lead to catastrophic consequences, e.g., in airplanes or power plants. The attribute is associated with a reliability function R(t), which defines the probability that a system provides

the correct service until time t [92]. R(t) can be defined over the *time to failure* T, i.e., the time it takes from the start of operation until the system fails for the *first* time. T is usually interpreted as a continuous random variable with a probability density function f(t), called *failure density*. The associated distribution function F(t) thus gives the probability that a failure occurs in the interval (0, t] and is defined as

$$F(t) = P(T \le t) = \int_0^t f(u) \, \mathrm{d}u \quad \text{for } t > 0.$$

(2.1)

Since the reliability function R(t) denotes the probability that *no* failure occurs in interval (0, t] it can therefore simply be derived from F(t) by

$$R(t) = P(T > t) = 1 - F(t) = \int_{t}^{\infty} f(u) \,\mathrm{d}u \qquad \text{for } t > 0.$$

(2.2)

While the failure density defines the probability that a system will fail within a certain time, very often the probability that a system will fail in some interval  $(t, t + \Delta t]$ , given that it was fully operational until t, is of interest. This conditional probability can be expressed as

$$P(t < T \le t + \Delta t \mid T > t) = \frac{P(t < T \le t + \Delta t)}{P(T > t)} = \frac{F(t + \Delta t) - F(t)}{R(t)}$$

(2.3)

If this probability is divided by the length of the investigated time window  $\Delta t$ , we receive a probability per unit time. Note that this is no longer a probability but a *rate*, called *failure rate* [53]. Consider, e.g., the conditional failure probability to be 0.4 within a time of 2 days. Then the resulting failure rate would be 0.2 failures per day, or 1.4 failures per week, depending on the unit. A commonly used unit in reliability engineering is *Failures in Time* (FIT), which represents the failure rate in  $10^9$  hours, i.e., 1 FIT equals a rate of 1 failure in approx. 115000 years. We can now take the limit  $\Delta t \rightarrow 0$  of Equation 2.3 divided by  $\Delta t$ , which gives us the *failure rate function* z(t), sometimes also referenced as *(instantaneous) hazard rate* [116]:

$$z(t) = \lim_{\Delta t \to 0} \frac{P(t < T \le t + \Delta t \mid T > t)}{\Delta t} = \lim_{\Delta t \to 0} \frac{F(t + \Delta t) - F(t)}{\Delta t} \frac{1}{R(t)} = \frac{f(t)}{R(t)}$$

(2.4)

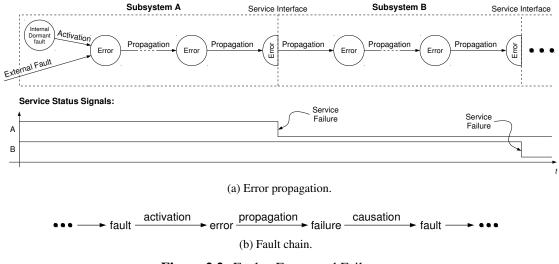

The failure rate function can assume various shapes. For modelling the failure rate over the lifetime of a system the bathtub curve is usually used (see Figure 2.3). Very often it is assumed that the failure rate function has a constant value  $z(t) = \lambda$ . This means that the probability of failure does not depend on how long ago the system has been put into operation, or in other words, there is no history that influences whether the system is more or less likely to fail at a particular point in time. A constant failure rate is useful for analysing system reliability in case faults are caused by external phenomena, like radiation or electromagnetic interferences, under certain (constant) worst-case conditions (see Section 4.6.3).

The time to failure T can be distributed in many different ways, depending on the specific system and the environment in which it is operating. Examples for possible distributions are: Exponential distribution, Gamma distribution, Normal distribution, Weibull distribution, etc. Most commonly an exponential distribution is chosen in reliability analysis, because it is mathematically very simple and gives a realistic failure model for most systems [92]. It is the only

**Figure 2.3:** Bathtub curve modelling failure rate over a system's lifetime across three typical intervals: I) Burn-in period, II) useful life, and III) wear-out period.

distribution with a constant failure rate and is therefore suitable to model the "useful life" part of a components life cycle (cf. Figure 2.3) [116]. In case of an exponential distribution the failure density f(t) with the parameter  $\lambda$  can be defined as

$$f(t) = \begin{cases} \lambda e^{-\lambda t} & \text{for } \lambda > 0, t > 0\\ 0 & \text{otherwise} \end{cases}$$

(2.5)

Consequently, the reliability function R(t) is

$$R(t) = P(T > t) = \int_{t}^{\infty} f(u) \, \mathrm{d}u = e^{-\lambda t} \qquad \text{for } t > 0,$$

(2.6)

which allows us to derive the failure rate function z(t):

$$z(t) = \frac{f(t)}{R(t)} = \frac{\lambda e^{-\lambda t}}{e^{-\lambda t}} = \lambda.$$

(2.7)

A key measure to describe a system's reliability is the *Mean Time to Failure* (MTTF), which is defined as the expected time to the first failure after the start of system operation. Formally the MTTF can therefore be defined as the expected value of the time to failure T:

$$MTTF = E(T) = \int_0^\infty tf(t) \,\mathrm{d}t. \tag{2.8}$$

Since f(t) can be written as

$$f(t) = \frac{\mathrm{d}F(t)}{\mathrm{d}t} = \frac{\mathrm{d}(1 - R(t))}{\mathrm{d}t} = -R'(t),$$

(2.9)

it is also possible to express the MTTF in terms of the reliability function:

$$MTTF = -\int_0^\infty tR'(t) \, \mathrm{d}t = -[tR(t)]_0^\infty + \int_0^\infty R(t) \, \mathrm{d}t$$

(2.10)

As the reliability function equals 0 when  $t \to \infty$ , the term  $[tR(t)]_0^\infty$  evaluates to 0, and the MTTF can therefore simply be stated as

$$MTTF = \int_0^\infty R(t) \,\mathrm{d}t. \tag{2.11}$$

In case of an exponential failure distribution the MTTF therefore is

$$MTTF = \int_0^\infty e^{-\lambda t} \, \mathrm{d}t = \frac{1}{\lambda}.$$

(2.12)

#### Maintainability

The ability of an item, under stated conditions of use, to be retained in, or restored to, a state in which it can perform its required functions, when maintenance is performed under stated conditions and using prescribed procedures and resources (BS4778).

Maintenance operations can either be *repairs* or *modifications* [8]. The former deals with the removal of faults (*corrective maintenance*) or with the detection and removal of dormant faults (*preventive maintenance*), the latter is concerned with adjustments due to environmental changes or augmentations of the system's function (*adaptive* and *augmentive* maintenance). Note that repair operations are similar to the recovery of erroneous states in fault tolerance mechanisms. However, we will follow the definition in [8] that maintenance involves the activity of an *external agent*, e.g., a repair man who replaces failed units.

#### Availability

The ability of an item (under combined aspects of its reliability, maintainability and maintenance support) to perform its required function at a stated instant of time or over a stated period of time (BS4778).

Formally the availability A(t) of a system can be expressed as the probability that the system is operational *at* time *t*. Note that if a system is permanently broken after a failure and cannot be repaired A(t) = R(t), i.e., the probability that the system is operational in the interval (0, t] [25]. Availability as dependability measure, however, only makes sense for systems where service interruptions are tolerable and a repair is possible. To quantify a system's dependability very often the *average availability* is used. This can be expressed as the fraction of time the system is available to provide correct service [55], i.e., as the ratio of *uptimes* to total time (*uptimes* + *downtimes*). The downtimes are typically modelled as the *Mean time to Repair* (MTTR), or alternatively as *repair rate*  $\mu$  [25]:

$$\mu = \frac{1}{MTTR}.$$

(2.13)

The repair rate depends on several factors, like the mean time it takes after a failure until repair is started, i.e., how fast the failure is detected and the responsiveness of maintenance staff. Other issues might be how fast spare parts are available in case of defects, and also the time it takes to fix the system, which is influenced by the maintainability. If failure and repair rates are constant, the average availability can simply be computed as follows [55]:

$$A_{average} = \frac{MTTF}{MTTF + MTTR}.$$

(2.14)

#### Safety

The *safety* attribute is an extension of reliability, where failures are partitioned into two categories: *fail-safe* and *fail-unsafe* [25]. In so-called *safety-critical* systems fail-unsafe failures can have dramatic consequences, like human injuries, loss of life, or environmental disasters. The safety function S(t) thus denotes the probability that a system is fully operational, or in case of failures behaves in a fail-safe manner during the time interval (0, t]. Safety-critical systems usually have to be certified by an independent certification agency [55].

#### Integrity

This attribute is concerned with the avoidance of "improper" system alterations [8]. Improper, in this context, typically means unauthorised.

#### 2.1.3 Means to Attain Dependability

#### **Fault Tolerance**

The aim of fault tolerance is to build systems that are able to avoid service failures in the presence of faults [8]. An essential requirement for designing such systems is the precise formulation of a *fault hypothesis* [55]. This hypothesis specifies what kind of faults the system is supposed to mitigate. Faults are therefore either *covered* or *uncovered* by the fault hypothesis. If properly designed and implemented, the system should be able to detect and recover errors that are the result of the activation of covered faults. For uncovered faults, on the other hand, the system behaviour is unspecified and can potentially lead to service failures. Obviously in a reasonable fault hypothesis the latter kind of faults should be highly improbable so that they do not pose a threat for dependable system operation.

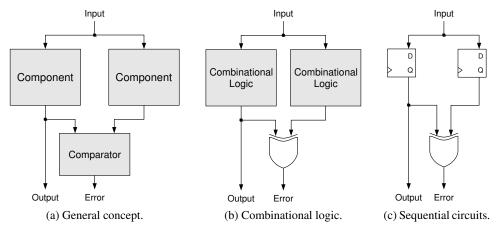

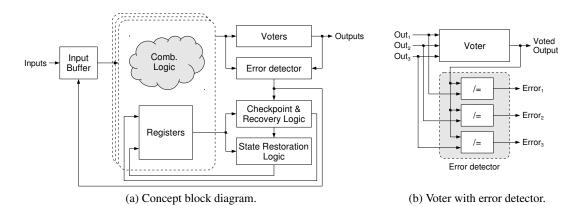

To be able to mitigate the effects of faults a fault-tolerant system thus needs to be equipped with mechanisms to detect internal errors and recover the system state before these errors can propagate to externally visible service interfaces. The key concepts involved in fault-tolerant system design are *error detection* and *recovery*. Figure 2.4 shows a classification of the most commonly used fault tolerance techniques. Error detection can either be done concurrently to the system operation or in a preemptive fashion, where the system stops to allow for detection of latent errors or dormant faults. *Preemptive error detection* is often performed at system start-up, but also during operation where, e.g., spare components are checked or memories are analysed as part of scrubbing routines [8].

Once an error is detected a recovery mechanism has to be executed to prevent the propagation of errors. Furthermore, it is essential to bring a system back to an error-free state before another fault is activated, as fault tolerance mechanisms can usually only cope with a limited number of concurrent faults (as specified in the fault hypothesis). Recovery mechanisms can be split into two groups: *error handling* and *fault handling* techniques. Classical error handling techniques

Figure 2.4: Classification of fault tolerance techniques.

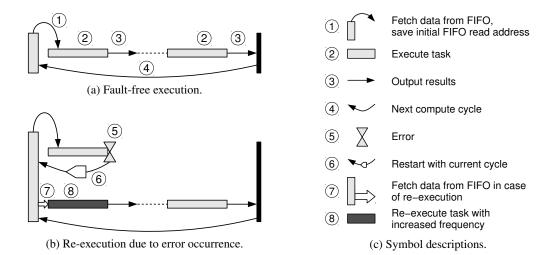

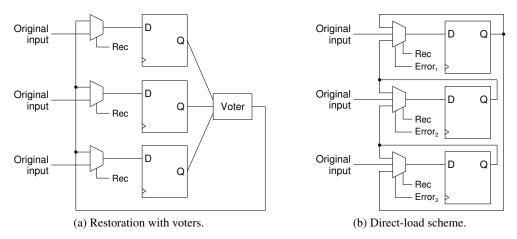

include *rollback* and *roll-forward* strategies. The fundamental concept for rollback mechanisms is *checkpointing*. A checkpoint simply is a complete snapshot of the system state at a specific point in time, which is stored in a safe memory for later use [56]. If an error is detected, the system state can be rolled back to the last checkpoint and computations are repeated from there on. Although the basic principle is simple, many difficult questions are entailed, like when and how often a checkpoint should be captured, or how can a checkpoint be generated in a distributed environment with many communicating processes. Furthermore, this approach leads to a performance degradation due to the execution time overhead when taking a snapshot and the recomputation when a rollback is necessary. For applications where such overheads are not acceptable roll-forward techniques can be employed. In these approaches error correction is directly applied on the current state when errors are detected [42]. Clearly some form of redundancy is required to be able to do this. The third error handling technique depicted in Figure 2.4, *compensation*, follows the idea of *masking* errors, again by using redundancy to identify and filter erroneous computation results. Rollback and roll-forward are typically applied on demand, whereas compensation can either be performed on demand or systematically. In the latter case masking actions are performed unconditionally at predefined points in time without prior detection of an error (cf. voting on output data).

When internal faults cause errors, fault handling can be performed following error detection to prevent that these faults will be activated again [8]. As can be seen in Figure 2.4 the steps involved in fault handling are *diagnosis*, *isolation*, *reconfiguration*, and *reinitialisation*. Diagnosis aims at identifying the location and type of a fault and isolation then tries to separate a faulty component from the system, so the fault becomes dormant. Reconfiguration replaces faulty units with spare components or redistributes tasks among active non-faulty components. Reinitialisation finally updates the state of the new system configuration.

*Redundancy* plays a key role in the design of fault-tolerant systems. Redundancy can either be *static*, where fault tolerance is structurally built into a system and directly masks fault effects [104], or *dynamic*. For dynamic redundancy active actions are required, like error detection and subsequent error and fault handling activities, as described above. Consequently, static and dynamic redundancy are also referred to as *passive* and *active* redundancy.

Depending on what resource is used to create redundancy, we can distinguish the following four forms: *hardware, time, information,* and *software redundancy*. Many advanced fault toler-

ance mechanisms often use a bundle of approaches, like static techniques along with dynamic ones, or a mix of hardware and time redundancy. This is called *hybrid redundancy* [104].

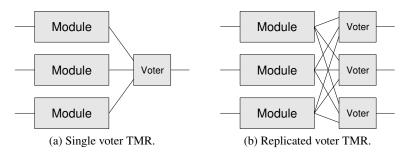

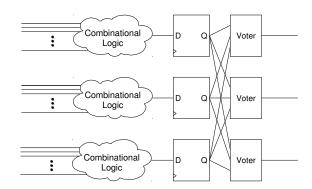

In hardware redundancy a computation is executed on multiple hardware components to be able to detect and counteract errors [56]. Typically this is achieved by replication of hardware units, which can be done on different levels, from transistor and gate to system level. The type and number of errors that can be mitigated hereby depends on how many physical copies are available. A well-known example for hardware redundancy are *modular redundant* systems.

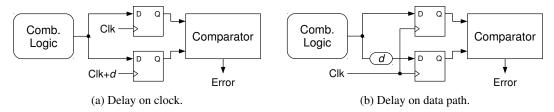

Alternatively to executing a computation on multiple hardware components, in time redundancy re-executions are done on a single component or processing node. Thus potentially high hardware overheads can be avoided. The downside, however, can be a substantial performance degradation. Also time redundancy is only effective against transient faults, where it can be assumed that a fault vanishes before re-execution is performed. Time redundancy can be applied systematically, i.e., when every computation is replicated and results of successive execution runs are compared, or, when other error detection mechanisms are available, it can also be implemented on demand (e.g., checkpoint and rollback recovery strategies) [56].

Information redundancy typically uses error detecting and error correcting codes to protect computations or data transfers against faults. These codes extend processed or transmitted data words with additional bits, which are some form of checksum of the encoded data bits. With these redundant bits and with the help of specific decoding algorithms it can be determined whether a data word contains errors or not. If the applied code is strong enough, i.e., if there is sufficient redundant information available, the locations of erroneous bits can be inferred, thus allowing for recovery of the correct data word. Note that information redundancy requires both additional hardware, for encoders and decoders, as well as extra computation time.

In many complex computer systems nowadays an integral part of the computation is performed in software. For high-reliability applications software redundancy is sometimes used as a means to mitigate software faults (bugs). This is achieved with the implementation of multiple functionally equivalent versions of the program code (design diversity), ideally by independent teams of programmers. The hope driving this approach is that it is unlikely for differently implemented program versions to contain the same type of bugs, i.e., fail for the same input [56]. The redundant program versions can be executed in parallel on different processors (hardware redundancy), or in sequence on the same processor (time redundancy).

#### Fault Prevention

Fault prevention includes all possible means to prevent that faults can occur in the first place [25]. During the development phase, e.g., this can be achieved by using rigorous specification of system requirements [91], structured design methods and careful verification with, e.g., code reviews or formal methods. During the use phase the probability of faults can be reduced by using robust hardware components that are not affected by adverse environmental conditions (electromagnetic interference, radiation, etc.), shielding of sensitive system parts, frequent maintenance operations, etc.

#### **Fault Removal**

Removal of faults to enhance dependability can be performed either during the development or during the use phase. In the former case faults have to be identified using verification, diagnosed and finally corrected. During the use phase fault removal is mainly conducted through maintenance, either preventive or corrective.

#### **Fault Forecasting**

The term fault forecasting describes various means to evaluate the behaviour of a given system in the presence of faults [8]. This can either be done with a *qualitative* or a *quantitative* evaluation, or sometimes a combination thereof. Qualitative evaluations aim to analyse conditions that could lead to a system failure, identify potential failure modes and classify and rank them with respect to their effect, frequency and severity. A general procedure that can be employed for this kind of evaluation is called *failure mode and effect analysis* [107].

Quantitative evaluation techniques on the other hand use probabilistic models of the system to derive numerical values to what extent a system satisfies the dependability attributes presented above. In this context these attributes are also called *measures of dependability* [8]. A wide-spread technique in reliability modelling, e.g., is the use of *Markov chains*. An aspect often involved in quantitative evaluation is *testing*, which delivers data on failure and maintenance processes, etc. This data can then be filled into system models to provide probabilistic estimates for dependability measures, based on realistic system or environmental parameters.

#### 2.2 Faults in Integrated Circuits

In this section we will move our discussion from the general concepts in dependable systems to the specific dependability issues we face in digital integrated circuits. A widely-used classification of circuit faults is the distinction of *transient* and *permanent* faults [25]<sup>2</sup>. We will follow this classification and briefly address some of the currently predominant causes for both types of faults in this section. Our focus, however, will be on transient faults since circuit faults with permanent effects are only a side issue in this thesis. Furthermore, we want to stress that the fault tolerance mechanisms presented in the Chapters 4 and 5 of this thesis were designed for mitigation of faults that occur during the *use phase* of a circuit. This excludes all sorts of development faults, like specification and implementation faults or defects that are introduced during circuit fabrication. While these are critical issues in circuit design, they are usually tackled with different countermeasures, which are out of scope for our work.

#### 2.2.1 Transient Faults

As described earlier, the duration of a transient fault is assumed to be bounded in time and is usually very short, e.g., below or around a nanosecond. There are various causes for transient faults

<sup>&</sup>lt;sup>2</sup>Sometimes *intermittent faults* are listed as a third class. However, with respect to the taxonomy presented above, they can also be described as dormant permanent faults that are activated from time to time, or as repeatedly occurring transient faults.

in integrated circuits, which are normally originating from outside the system boundaries (external faults). Examples are radiation effects, electrostatic discharge, electromagnetic interference, drops in supply voltage or temperature variations [25]. In particular, sensitivity of semiconductors to radiation has increased dramatically due to technology scaling over the last decades [10]. Thus, radiation effects have become a key threat of deep submicron circuits, even when they operate at sea level where radiation flux is much smaller than in space or at high altitudes.

#### Terminology

Since a lot of research has been done in the past decades on radiation effects in semiconductors, a whole body of technical terms has been coined in this area that have been widely adopted by most researchers and engineers working in fault-tolerant circuit design. The *JESD89A standard* [47], which defines procedures for testing and characterising the resilience of integrated circuits in (terrestrial) radiation environments, provides definitions of the most commonly used terms. Generally, radiation effects are referred to as *single event effects* (SEEs), which are defined as a "measurable or observable change in the state or performance" of an integrated circuit, caused by a single energetic particle strike [47]. Hence, all terms we will introduce below describe some kind of single event effect.

*Errors* that are caused by radiation-induced faults are typically called *soft errors*, often also referred to as *single event upsets* (SEU) [10]<sup>3</sup>. The term "soft" reflects on the fact that the circuit is not physically impaired, but a value stored in a memory cell, a latch or flip-flop, e.g., was changed and thus the circuit state is compromised. Obviously, this condition can be reversed or recovered by rewriting the correct value into the respective element. Soft errors can be classified by the way the circuit state is modified: Typically only a single storage cell is affected, which leads to a *single bit upset* (SBU). If more than one bit of information is altered, this is called *multiple-cell upset* (MCU), and in the case that the affected bits belong to the same data word this is described as *multiple-bit upset* (MBU) in the JESD89A standard. An important metric for the reliability assessment of an integrated circuit is the *soft error rate* (SER), which simply describes the rate at which soft errors occur. Clearly, the SER depends on a variety of parameters, like the radiation flux, the circuit topology, supply voltages, transistor sizes, doping profiles, etc. [50]. Characterising the soft error rates for a given circuit is a complex task, which is usually based on various circuit models and simulations along with an experimental validation.

A radiation effect that causes a voltage pulse at a node of a circuit is called *single event transient* (SET). In a sequential element this SET can directly result in a soft error. On the other hand, if the node is part of a combinational circuit, the SET might propagate through logic gates until it is eventually latched by a sequential circuit element, which then ends in a soft error. In the latter case, however, most SETs are never captured since they are filtered by *logical, temporal or electrical masking* effects as they progress on combinational paths [50].

<sup>&</sup>lt;sup>3</sup>The term soft error first appeared in 1978 [47] in a publication by May and Woods from Intel [69] on alpha particle-induced faults in DRAMs. The name single event upset was then introduced one year later by Guenzer, Wolicki and Allas [39] in a paper that also dealt with radiation faults in DRAMs, but caused by neutrons and protons.

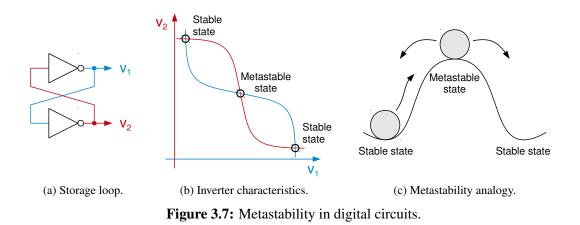

#### Effects of Radiation on Semiconductor Devices

Radiation-induced faults occur when ionised particles travel through the semiconductor material and lose energy along their track, which results in the deposition of charge in the form of electron hole pairs. In a terrestrial environment there are two major sources for ionised particles: I) alpha particles, which originate from radioactive isotopes in the die or the packaging, and II) secondary particles that are generated by collisions of neutrons with silicon, oxygen or dopant atoms in the die [80]. When the deposited charge is collected at p-n junctions of MOS transistors, a current/voltage pulse is created at that particular node [10]. Whether this pulse actually results in a harmful SET or even in a soft error, depends on the magnitude of the collected charge  $Q_{coll}$  and the node's sensitivity, which is influenced by various parameters like node capacitance, operating voltage or the strength of the feedback inverters in the storage loop of sequential elements. This sensitivity can be expressed in terms of a *critical charge*  $Q_{crit}$ , which needs to be exceeded by a radiation event to be harmful for the computation of the circuits, i.e.,  $Q_{coll} > Q_{crit}$ .

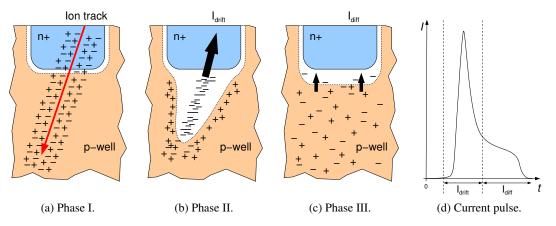

An SET pulse unfolds in three phases after an ionised particle hits the die, as can be seen in Figure 2.5. In the first phase charge is generated around the track of the particle. This is followed by a rapid charge collection process due to the electric field in the p-n junction, which creates a steep increase of the current at that node. During this process the depletion region forms a funnel-shaped extension into the substrate, which boosts the charge collection. This phase lasts for less than a nanosecond [10], after which the funnel collapses. The collection of the remaining charge can then be attributed to diffusion of electrons into the depletion region, which happens at a much slower rate. The final phase of the SET can therefore last hundreds of nanoseconds [10]. Figure 2.5d shows the junction current over these three phases, which is often approximated with a double-exponential function [119].

Figure 2.5: SET generation after a single event effect.

#### 2.2.2 Permanent Faults

Physical defects in integrated circuits can be caused by a variety of effects. Most commonly circuit defects are introduced during the fabrication process due to mask misalignment, over- and under-etching, or spot defects, e.g., caused by contamination with dust particles [56]. Permanent faults, however, can also occur during the use phase of a circuit, triggered by electrical, mechanical or thermal stress, or wearout/ageing mechanisms like *electromigration* (EM), *Hot Carrier Injection* (HCI), *Negative Bias Temperature Instability* (NBTI) or gate oxide breakdown [33]. Possible effects of permanent faults are open or short circuits, threshold voltage shifts, increased leakage currents, variability of carrier mobility, etc. [104].

Various fault models have been developed that provide an abstraction from the specific physical fault manifestations. This helps to analyse potential circuit defects and implement procedures for fabrication tests or for built-in self tests, which can be executed on a regular basis during circuit operation. The most popular model is the *single stuck-at fault model* (SSAF), where a single circuit signal is assumed to be permanently tied to a value of 0 or 1, while all other circuit signals are non-faulty. Even though this model is very simple it can detect a high percentage of manufacturing defects. In Chapter 4 we will perform fault-injection experiments based on this model. Other important fault models are: *Multiple stuck-at faults* (MSAF), *bridging faults, open* faults, *path-delay* faults and  $I_{DDQ}$  faults [36].

# CHAPTER 3

## **Circuits Background**

#### 3.1 Asynchronous Circuit Design

A fundamental principle in electrical engineering and computer science is the use of abstractions, which help us to focus on the relevant properties of a system when describing or solving a particular engineering problem. As a matter of fact, the design of many complex systems only becomes tractable due to the use of such powerful abstractions [2]. Most digital circuits, e.g., are based on two fundamental abstractions: a) All signal values or stored bits of information are assumed to be binary, with the respective physical representations denoted as 0 or 1 (*low* or *high*), and b) there is a clock offering a global discrete time base and all circuit state changes occur instantaneously at the ticks of this clock. These two abstractions have simplified the lives of many circuit designers in the previous decades and are the main characteristics of so-called *synchronous circuits*. In this class of circuits a square wave signal with a fixed frequency is used as clock, where rising or falling signal transitions denote the clock tick. All circuit operations like computations, communication among different components or sequencing of events are performed with the temporal granularity of these clock ticks.

Asynchronous circuits, on the other hand, do not depend on the notion of a global, discrete time [102]. Instead they use other mechanisms based on explicit control signalling and hand-shake protocols, which implement a closed-loop form of control in contrast to the open-loop control fashion of synchronous circuits [108]. Therefore circuit activities are not rigidly tied to predetermined points in time but are triggered by local events, like the availability of data for a particular component or an incoming request from the circuit's environment. Because of this adaptability and in the light of timing trends in recent technologies, asynchronous circuits are a promising alternative to traditional synchronous circuit designs. Potential benefits include [40, 102]:

• Lower dynamic power consumption – As asynchronous circuit are event-based and only perform operations when an actual request is active, switching activities can be significantly reduced. Synchronous circuits achieve a somewhat similar behaviour by clock

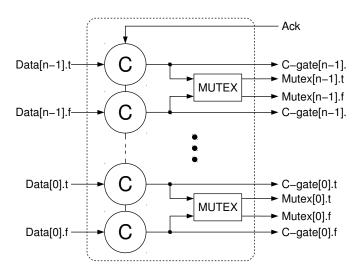

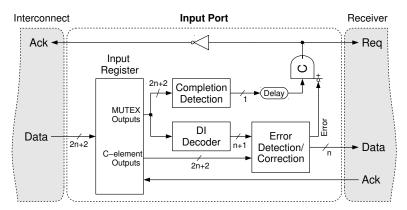

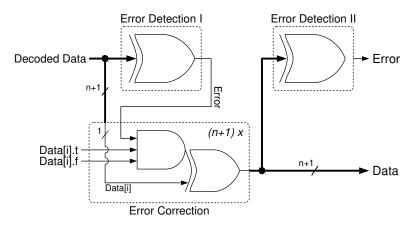

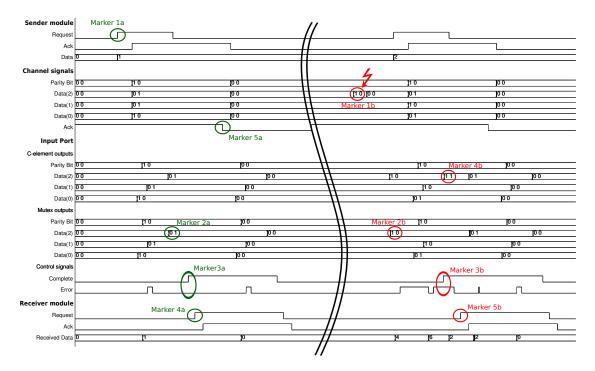

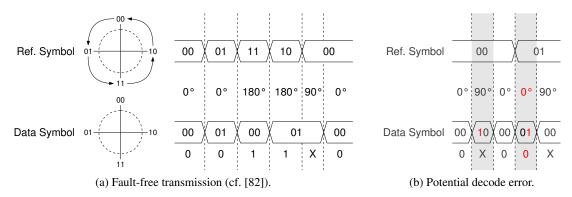

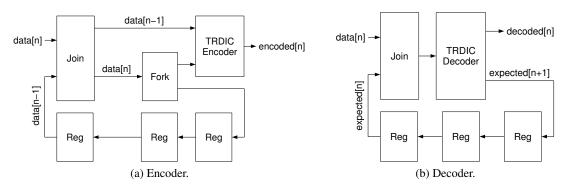

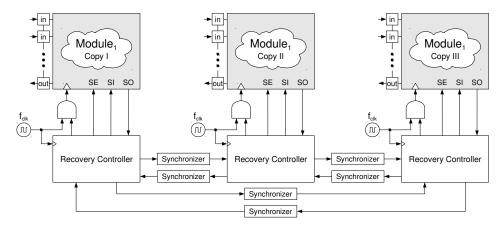

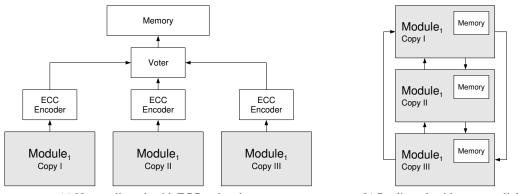

gating mechanisms. In asynchronous circuits, due to the ubiquitous presence of handshakes, deactivation of unused circuit parts is performed implicitly and potentially at a much finer granularity.