## Composability for Fail-Safe Safety-Critical Systems

## DISSERTATION

zur Erlangung des akademischen Grades

### Doktor der technischen Wissenschaften

eingereicht von

#### **Stefan Resch**

Matrikelnummer 0425306

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Ao. Univ. Prof. Dipl.-Ing. Dr.techn. Andreas Steininger

Diese Dissertation haben begutachtet:

(Ao. Univ. Prof. Dipl.-Ing. Dr.techn. Andreas Steininger) (Univ. Prof. Dipl.-Ing. Dr.techn. Wilfried Elmenreich)

Wien, 03.12.2014

(Stefan Resch)

FÜR INFORMATIK

Faculty of Informatics

# **Composability for Fail-Safe Safety-Critical Systems**

## DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

## Doktor der technischen Wissenschaften

by

Stefan Resch

Registration Number 0425306

to the Faculty of Informatics at the Vienna University of Technology

Advisor: Ao. Univ. Prof. Dipl.-Ing. Dr.techn. Andreas Steininger

The dissertation has been reviewed by:

(Ao. Univ. Prof. Dipl.-Ing. Dr.techn. Andreas Steininger) (Univ. Prof. Dipl.-Ing. Dr.techn. Wilfried Elmenreich)

Wien, 03.12.2014

(Stefan Resch)

## Erklärung zur Verfassung der Arbeit

Stefan Resch Koberweingasse 2/37, 1150 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

## Acknowledgements

Above all, I want to thank Andreas Steininger, Christoph Scherrer and Heinz Kantz for the opportunity to pursue my PhD studies and their encouragement throughout. To Andreas, in particular, for his invaluable support as supervisor and for always pointing me in the right direction. Also, to Christoph for constantly challenging me and directing my focus to the practical relevance of this work. And to Heinz for always providing insightful feedback and a fresh perspective.

I would also like to acknowledge Peter Tummeltshammer for the numerous fruitful discussions and much appreciated comments. Many thanks go to Michael Paulitsch for broadening my horizons by highlighting new aspects to the topic and to Jaime de Oliveira for initially introducing me to the world of virtualization.

Furthermore, thank you to my colleagues at Thales Austria who gave me valuable pointers and support, moral or otherwise, during this process: Bernhard Kaindl, Johannes Mach, Werner Spieß, Rossen Zlatev, Oscar Medina, Mike Rumpler, Nikolaus König, Werner König, Peter Metzner, Gerhard Wipplinger, Klaus Reichl, Christoph Sünder, Christoph Plattner, Frank Riechert and Andreas Messner.

A special thank you must go to all my family for their tremendous support and understanding during this time. To my friends, thank you for always providing diversions when most needed.

Finally, I am most grateful for Cristina's encouragement, patience and help from beginning to end. I could not have completed this thesis without you.

Part of this research was funded by the ARTEMIS Joint Undertaking (nSafeCer, Grant Agreement number 295373), and the Austrian partners' national funding agency Austrian Research Promotion Agency (FFG) on behalf of the Austrian Federal Ministry of Transport, Innovation and Technology (BMVIT).

## Abstract

Safety-critical systems must be carefully designed, developed and maintained in order to ensure that the threats posed by such systems are acceptably low. Certification demonstrates that these systems are fit for use. The methods of certification are applied to complete systems according to the applicable industrial standards. If parts of such a system change, substantial effort is necessary for re-certification, since the certification processes have to be repeated for the entire system.

Composability and mixed-criticality are strategies meant to support the integration and ease certification of safety-critical systems as sub-systems on one common platform, without affecting the safety or availability of the individual sub-systems. The introduction of mechanisms in order to achieve composability and mixed-criticality requires an additional layer in the architecture, responsible for the sharing of resources. This strongly affects sub-systems with strict timing requirements, such as triple-modular-redundant applications, which are widely used for fault-tolerant safety-critical computation.

This thesis investigates the requirements for achieving composability and mixed-criticality. It subsequently identifies solutions suitable for controlling the newly introduced effects. An appropriate system model and the metrics for the applications' performance are defined in order to analyze the properties of the proposed solutions. Based on the system model and the analysis results a contract concept is introduced, which allows the specification of applications, platforms and integrated systems based on provided and required resources. The validity of the analysis is evaluated with a prototype and simulation.

The results show that an out-of-the-box solution which guarantees the technical separation between applications with fast reaction time requirements is only feasible when executing at most one application per CPU-core for single and multi-core CPUs. Only when accepting changes in the architecture, applications or the applications' synchronization mechanisms, are other solutions available.

## Kurzfassung

Sicherheitskritische Systeme müssen sorgfältig entworfen, entwickelt und gewartet werden, um zu gewährleisten, dass von ihnen kein Risiko ausgeht. Die Zertifizierung eines Systems zeigt, dass es geeignet für den Einsatz ist. Die Methoden der Zertifizierung werden für ganze Systeme gemäß den relevanten Industriestandards angewendet. Sollte ein Teil eines solchen Systems geändert werden, so ist erheblicher Aufwand für die Rezertifizierung nötig, da die Zertifizierungsprozesse für das gesamte System wiederholt werden müssen.

Composability und Mixed-Criticality sind Strategien, welche die Integration und Zertifizierung von sicherheitskritischen Systemen als Subsysteme auf einer gemeinsamen Plattform unterstützen, ohne die Sicherheit oder Verfügbarkeit der einzelnen Subsysteme zu beeinträchtigen. Die Einführung von Mechanismen um Composability und Mixed-Criticality zu erreichen, erfordert einen zusätzlichen Layer in der Architektur, welcher die gemeinsamen Ressourcen verwaltet. Ein solcher Layer wiederum beeinflusst Subsysteme, welche strikte zeitliche Kriterien haben, wie beispielsweise dreifach redundante Applikationen. Dreifach Redundanz ist eine weit verbreitete Technik für sicherheitskritische Anwendungen.

Diese Arbeit untersucht die Voraussetzungen um Composability und Mixed-Criticality zu erreichen. Daraus folgend werden mögliche Lösungen erarbeitet, welche den Einfluss des neuen Layers begrenzen. Ein dazugehöriges Systemmodell sowie Metriken zur Messung des Applikationsverhalten werden definiert, um die Eigenschaften der vorgeschlagenen Lösungen zu analysieren. Auf Basis des Systemmodells und der Ergebnisse der Analyse wird ein Vertragskonzept vorgestellt, mit welchem Applikationen, Plattformen und integrierte Systeme anhand von verfügbaren und erforderlichen Ressourcen spezifiziert werden können. Die Ergebnisse der Analyse werden mit Hilfe eines Prototyps und Simulationen überprüft.

Die Ergebnisse zeigen, dass es eine direkte Lösung gibt, die die technische Separierung zwischen Applikationen mit kurzen Antwortzeitanforderungen garantiert. Maximal eine sicherheitskritische Applikation darf pro CPU-Core für Single- und Multicore CPUs integriert werden. Nur wenn man Änderungen in der Architektur, den Applikationen oder dem Synchronisationsmechanismus der redundanten Applikationen zulässt, kann man auch von anderen Lösungen wählen.

## **List of Abbreviations**

| AP          | Application                             |

|-------------|-----------------------------------------|

| <b>CBSE</b> | Component-Based Software Engineering    |

| СМ          | Communication Media                     |

| <b>COTS</b> | Commercial Off-The-Shelf                |

| <b>DMA</b>  | Direct Memory Access                    |

| EDF         | Earliest Deadline First                 |

| <b>FMEA</b> | Failure Mode and Effects Analysis       |

| <b>FS</b>   | Function-Set                            |

| <b>GSN</b>  | Goal Structuring Notation               |

| HMI         | Human-Machine Interface                 |

| IE          | Integration Environment                 |

| IMA         | Integrated Modular Avionics             |

| МСН         | Monitoring and Communication Handler    |

| MILS        | Multiple Independent Levels of Security |

| <b>MMU</b>  | Memory Management Unit                  |

| NIC         | Network Interface Controller            |

| РН          | TSM Protocol Handler                    |

| RM          | Rate-Monotonic                          |

| <b>RTC</b>  | Real-Time Clock                         |

| <b>RTOS</b> | Real-Time Operating System              |

| <b>SEU</b>  | Single Event Upset                      |

| TMR         | Triple Modular Redundancy               |

| TSM         | Token Synchronized Messages             |

| TTA         | Time Triggered Architecture             |

## Contents

| 1 | Introduction 1     |                                                          |  |  |

|---|--------------------|----------------------------------------------------------|--|--|

|   | 1.1 M              | lotivation                                               |  |  |

|   | 1.2 Pi             | roblem Statement                                         |  |  |

|   | 1.3 A              | im of the Work                                           |  |  |

|   | 1.4 M              | Iethodological Approach    3                             |  |  |

|   | 1.5 St             | tructure of the Work                                     |  |  |

| 2 | 2 State of the Art |                                                          |  |  |

|   | 2.1 St             | tandards                                                 |  |  |

|   | 2.2 Pa             | artitioning and Virtualization                           |  |  |

|   | 2.3 C              | ontracts                                                 |  |  |

|   | 2.4 Ti             | riple Modular Redundancy                                 |  |  |

|   | 2.5 Se             | cheduling                                                |  |  |

|   | 2.6 Pa             | artitioning and TMR                                      |  |  |

| 3 | Softwa             | re Composability 15                                      |  |  |

|   | 3.1 A              | ttaining Composability                                   |  |  |

|   | 3.2 R              | equirements for Function-Sets with a Safe State          |  |  |

|   | 3.3 Fa             | ailure Confinement Regions vs. Fault Containment Regions |  |  |

| 4 | Compo              | osability for TMR Architectures 23                       |  |  |

|   | 4.1 C              | ontemporary TMR Architectures                            |  |  |

|   | 4.2 T              | MR Architectures Leveraging Composability                |  |  |

| 5 | Targete            | ed Applications 31                                       |  |  |

|   | 5.1 Se             | etting a Train Route                                     |  |  |

|   | 5.2 A              | xle Counting                                             |  |  |

| 6 | System             | Model 35                                                 |  |  |

|   | 6.1 O              | bjectives                                                |  |  |

|   |                    | Node Scheduling                                          |  |  |

|   | 6.3 Fa             | ault Hypothesis                                          |  |  |

|   |                    | Iessage Transmission Times    38                         |  |  |

|   |                    |                                                          |  |  |

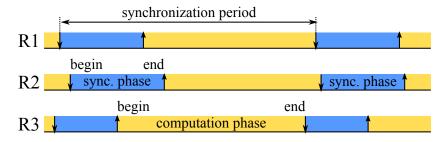

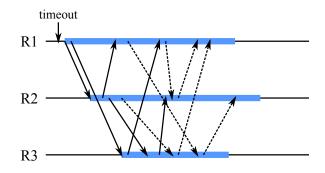

| 7  | Synchronization Mechanisms7.1Periodic Synchronization7.2Periodic Synchronization for Redundant Networks7.3Token Ring Synchronization with TSM7.4Influence of the Layer of Synchronization on Synchronization Precision | <b>41</b><br>41<br>45<br>46<br>52        |  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--|

| 8  | Proposed Concepts for Composable Solutions8.1Virtualization as Composability Layer8.2Safety Layer8.3Contract-based Certification8.4Composable Architectures                                                            | <b>53</b><br>53<br>55<br>56<br>56        |  |

| 9  | IE with Classic TMR Architecture9.1Static-Cyclic Scheduling9.2Preemptive Fixed-Priority Scheduling9.3Preemptive EDF Scheduling9.4Comparison of Scenarios Integrating the Example Applications                          | <b>57</b><br>57<br>62<br>66<br>66        |  |

| 10 | Dynamic IE10.1 Periodic Synchronization with Redundant Networks10.2 TSM                                                                                                                                                | <b>69</b><br>69<br>74                    |  |

| 11 | Contracts for Certification11.1Formal Contract Definition11.2Refinement for our TMR-based FSs11.3Alterations of the IE11.4Applying Integration Contracts11.5Limitations of the Presented Contract Concept              | <b>81</b><br>82<br>85<br>89<br>90<br>90  |  |

| 12 | Evaluation12.1Prototype Setup12.2Example Timing Measurements of Scheduling Operations12.3Static-Cyclic Scheduling12.4Preemptive Fixed-Priority Scheduling12.5Preemptive EDF Scheduling                                 | <b>91</b><br>92<br>93<br>94<br>98<br>104 |  |

| 13 | 13 Conclusion                                                                                                                                                                                                          |                                          |  |

| 14 | 14 Future Work                                                                                                                                                                                                         |                                          |  |

| Bi | Bibliography                                                                                                                                                                                                           |                                          |  |

## CHAPTER

## Introduction

We use services controlled by computers and software in our everyday life without even noticing or being aware of most of them [71]. Some services are used for convenience, such as vending machines, while others provide the foundation of our way of life, e.g. transportation. In the end, people develop and maintain these services with the intention of having people using them.

This thesis aims at supporting those responsible for constructing and providing such essential services.

#### 1.1 Motivation

Failure of a safety-critical system can result in harm to humans and the environment. To ensure that the resulting threats posed by such a safety-critical system are acceptably low, it has to be certified according to the applicable industrial standards. These standards define processes in order to classify systems in levels of criticality with respect to the potential damage a failure of the system could cause. SIL, ASIL and DAL are examples of classification schemes in standards of the railway, automotive and avionics domain. These levels define different processes and methods to be followed during a system's lifetime in order to keep its probability of failure acceptably low. Here, SIL4, ASIL D and DAL - Level A require the most effort, as they apply to systems where failures can have catastrophic consequences.

The methods of certification are applied to the whole system and the system is subsequently certified in its entirety. Should parts of the system change, substantial effort is necessary for re-certification. Either the certification process is repeated for the whole system, or, with a detailed impact analysis all system parts affected by the changes are determined, after which the certification process is performed on the corresponding parts. This system-centric view logically originates from the fact that the hazard is posed by the complete system. This results in systems of systems with federated architectures, possibly utilizing only a small fraction of the underlying hardware's performance.

*Composability* and *mixed-criticality* promise to reduce this certification effort and increase the level of integration together with hardware utilization. This can be achieved by merging

such systems of systems on one platform, thereby creating one integrated system consisting of sub-systems, as well as by splitting existing systems in different sub-systems, which are then assigned their specific criticality level. These sub-systems are certified independently according to their criticality level, and the overall system is certified based on the evidence provided by the certification process of the sub-systems. For this approach it is crucial, that the independence of the individual sub-systems is guaranteed. Composability addresses the composition and certification of such systems and corresponding sub-systems, whereas mixed-criticality is concerned with the integration of sub-systems with different levels of criticality.

Increasing computational power and chips incorporating several CPUs enable the tight integration of numerous functions of a system in the first place. The aim of composability and mixed-criticality is to achieve this integration without affecting safety and availability of the individual sub-systems or applications. Consequently, a suitable integration approach must adhere to the relevant industrial standards and support different applications, having versatile requirements towards their integrated environment. However, not all industrial standards, e.g. IEC 61508 [33–35], explicitly support composability and mixed-criticality.

#### **1.2 Problem Statement**

The focus of this thesis is the composable integration of fail-safe triple-modular-redundant (TMR) applications subject to certification. These (existing) applications have strong requirements on the properties of the internal communication channels and reactivity of individually synchronized application instances. Together with their lower-level software, the applications assume full access to the hardware resources. With the introduction of composability this full access is inevitably removed, as in fact, the sharing of resources is the key benefit of integration. The arising problems are now twofold. First, the applications' timely behaviour is affected due to the (now) restricted access to hardware resources. Secondly, this restriction changes the basis of the applications' safety concepts for certification.

#### 1.3 Aim of the Work

The goal of this work is to provide a technical and conceptual foundation for the (separate) certification and integration of several such triple modular redundant applications with non-critical applications. The solution shall combine the benefits of mixed-criticality and composability with that of reusing existing TMR applications. It must provide a balance between the following three different objectives:

- 1. Provide a technical foundation for independent certification (separation and predictability),

- 2. Fulfill the reaction time requirements of the applications (performance), and

- 3. Efficiently use the available hardware resources to take advantage of the integration (utilization).

#### 1.4 Methodological Approach

Starting with the general requirements for composability and mixed-criticality, possible approaches for different kinds of TMR methods replicating software are evaluated. Based on this evaluation general limits and opportunities of composable architectures are outlined. Within this general solution space, concepts suitable for fulfilling the requirements imposed by the targeted safety-critical TMR applications are identified and a corresponding system model for analysis is defined. Specific software TMR synchronization mechanisms and respective metrics are presented and justified for use in the composable environment. These strategies are then evaluated for the different architectures using the metrics and system model. Slightly adapted versions of the synchronization mechanisms are proposed and analyzed, which offer beneficial properties within a specific composable setting. Based on these insights, a formal definition of contracts for the composability approach is given together with a method for evaluating feasibility of application integration and architectural changes. Simulations and measurements with prototypes are used to demonstrate the accuracy of the architectural and synchronization analysis, as well as the suitability of the contract approach.

#### 1.5 Structure of the Work

In the next chapter an overview of the state-of-the-art of the many related research fields is given. Chapter 3 presents the general concepts for software composability, followed by the system properties of contemporary TMR architectures, when extended with composability, as well as TMR architectures leveraging composability in Chapter 4. The requirements of the chosen applications subject to integration are presented in Chapter 5, and the according system model in Chapter 6. Chapter 7 justifies and describes the three synchronization mechanisms subject to our analysis. The solutions proposed for composable integration of the applications are presented in Chapter 8, and the corresponding analysis described in Chapter 9 and Chapter 10, respectively. The contract model for independent certification for these solutions is defined in Chapter 11. Results of simulation and experimental evaluation are presented and discussed in Chapter 12. Chapter 13 concludes this thesis, and directions for future work are given in Chapter 14.

# CHAPTER 2

## State of the Art

Providing composability and mixed-criticality for safety-critical applications which use TMR for fault tolerance has many different aspects. We start with the support of composability in industrial standards in Section 2.1, followed by partitioning and virtualization, both of them techniques suitable for separating applications from each other, in Section 2.2. Current approaches for software abstraction with contracts are presented in Section 2.3. Section 2.4 gives an in-depth description of TMR systems and Section 2.5 is concerned with scheduling, given its impact on composable systems. Research regarding software TMR application on top of partitioned systems is presented in Section 2.6.

#### 2.1 Standards

Concepts and methods for mixed-criticality and composability are already used in the industry.

The avionics domain has adopted the concept of integrated modular avionics (IMA) defined in DO-297 [105] for the integration of different safety-critical components on one hardware/software platform. The ARINC 653 standards [10–12] define an application software standard interface for development and integration of software functions of mixed-criticality on such a common platform following the avionics standard [99]. Different roles and tasks are used for a clean separation of function provider, platform provider and system integrator. Additionally, file formats for exchanging certification-relevant data with respect to application, platform and system behaviour are defined. These standards and guidelines are supported by industrial products for IMA, e.g. the VxWorks 653 Platform [121].

AUTOSAR is an approach to define a platform standard for the automotive domain. This includes a common interface for electronic control units and for allowing software reuse by providing a runtime environment for applications [13, 27, 45]. With the ISO 26262 automotive standard the concept of SEooC (Safety Element out of Context) can be applied to certify a safety-critical element in isolation, based on assumptions of the operational context. The final evaluation is performed when the safety-critical element is used within a specific system, and

it includes verifying the correlation of the assumed context to the specific context within the system [41].

For the railway domain, the CENELEC EN standards [28–30] provide generic safety cases for incremental certification, which are suitable to construct a safety case for composability and mixed-criticality. The CENELEC EN standards are based on the IEC 61508 standards [33–35].

#### 2.2 Partitioning and Virtualization

Most standards address composability with a partitioning concept to isolate individual components for certification. Partitioning can be applied on board, as well as chip or software level. However, all approaches define clear boundaries between the individual partitions.

Initially, the software separation issue has been discussed by Rushby [106] with the introduction of the concept of separation kernels for security. The idea is to reach the same isolation for individual programs as with a federated architecture and ensure that the programs executed within the partitions cannot detect that they are actually located on an integrated platform. Another goal is to keep the code base of the separation kernel very small, so as to be able to formally verify its fulfillment of the separation requirements. This approach was further developed to the MILS (Multiple Independent Levels of Security) architecture [6, 7, 115] which uses such a separation kernel at the lowest level. Separation kernels in this architecture are usually based on microkernels, which also follow the design paradigm to execute most code in user mode and use partitioning [40,68,112]. This partitioning concept is also the basis of the integration concept for fail-operational systems suggested by Rushby [107] for avionics. There, the correct and timely execution of all safety-critical partitions is mandatory, and the system must remain operational even under (the hypothesized) faults. Time and space partitioning are also the core principles of the time-triggered architecture (TTA) [74]. In this architecture, clock synchronization and a system-wide static-cyclic schedule for communication and computation of safety-critical applications provide the foundation for guaranteed reaction times.

Kopetz et al. [75] developed a time-triggered System-on-Chip architecture that supports composability by partitioning the chip. Each safety-critical application is assigned its own processor, which is similar to a federated architecture, but the communication in-between the processors is provided by a time-triggered Network-on-Chip. This network is managed by a trusted network authority and only accessible for the individual applications via a trusted interface sub-system, which limits network access to predefined access patterns.

Another hardware-implemented solution for composability has been designed by Hansson et al. [59]. It achieves predictability by implementing specific schedulers for different resources, to ensure worst-case access and execution times for all requests made to the resources. The underlying scheduling strategies have been described in more detail by Akesson et al. [4]. As in the approach of the time-triggered System-on-Chip, applications do not share individual processors in the original design. This has been changed by Molnos et al. [89] by applying the technique of virtualization to successfully integrate several applications on the same processor. In the extension, a processor local static-cyclic scheduler provides constant CPU time for applications. Predictability for communication via the Network-on-Chip is achieved by computing a worst-case memory access time, since only direct memory access (DMA) requests are used for communication.

A prominent separation approach regarding virtualization is the use of hypervisors, also called virtual machine monitors [16, 86]. A hypervisor shares the same hardware machine between different operating systems, called guests, by providing each of them a virtual representation of the hardware machine, i.e. the virtual machine. The main difference between a hypervisor and an emulator is that with a hypervisor most of the guests' instructions are executed natively and the hypervisor only interferes with certain operations, which would effect the hardware state for all guests. Current CPUs provide special hardware functions to support the isolation between virtual machines and accelerate their interaction with the hypervisor and hardware resources [96]. Performance guarantees and isolation between virtualization [56,86]. The Xen hypervisor, most commonly used in non-safety-critical server environments, has also been extended with an ARINC 653 CPU scheduler and I/O driver to support development of ARINC 653 applications on regular PCs [114].

As discussed by Heiser and Leslie [60], the precise border between microkernels and hypervisors is not that clear and both may use hardware-supported virtualization techniques [58,61]. A comprehensive state-of-the-art in embedded virtualization has been given by Gu and Zhao [55]. Using virtualization for implementing a primary-backup fault-tolerant system has been suggested by Bressoud and Schneider [26]. Different methods for virtualization and the fundamental concepts of hardware virtualization support to increase hypervisor performance have been discussed by Adams and Agnesen [3].

Perez at al. [95] presented a certification strategy for mixed-criticality on a single multicore chip. It is a wind power control system subject to the IEC 61508 standard. Several steps towards their targeted mixed-criticality system are outlined, in which a certified hypervisor is executed on top of diverse cores (x86 and Leon3 in the example). This hypervisor provides safety-relevant features such as fault-tolerant synchronization of clocks and safe communication between partitions. Separate diagnosis partitions are provided for each core executing a safetycritical partition as well. The diagnosis partitions periodically trigger a watchdog provided for each individual core. A static-cyclic scheduler ensures sufficient CPU time for the safety-critical partitions.

The focus of recent research on partitioning is on guarantees for isolation and performance on multi- and many-core platforms [66, 77].

#### 2.3 Contracts

Various forms of contracts are used in software engineering, but all with the same two goals: a precise specification, and enabling software (component) reuse through interoperability.

Meyer [87] introduced contracts for object-oriented programming with the design by contract method, to explicitly expose the requirements and guarantees of objects and their clients. The contracts are expressed in terms of preconditions, postconditions and invariants of classes and methods. An exception mechanism is used when such contracts are violated.

Component-based software engineering (CBSE), applies the design by contract approach on a higher abstraction level, where applications are constructed from components within a specific component framework. According to the fundamental idea of CBSE, contracts are provided with components to express quality of service parameters, such as availability, in addition to their functional behaviour specified in the APIs [14]. However, many industrial standards for software engineering, e.g. CENELEC EN 50128 [30], have no such notion of contracts, but use general software component specification and documentation together with tests and reviews in the development and maintenance processes to ensure software and system quality.

Conmy et al. [36] suggested to add contracts to the IMA concepts, which list matching and non-matching software components' requirements and guarantees for composition. These lists contain statements on a fine granular level and each element is related to a failure mode. The aim of these contracts is to ensure that the components always provide mitigations for failure modes. This is the same goal as for applying failure mode and effects analysis for software components and subsequent specification of safety-related application conditions for safe operation in the railway standard [29].

The concept of contracts is also used with the Goal Structuring Notation (GSN) [54]. With GSN safety of a system is documented by step-wise decomposing the overall safety goals of this system into sub-goals and linking them to elements, which support that these goals are satisfied. Contracts are used to define interfaces between elements, as well as goals, to enable local alteration of the safety argumentation when necessary, without affecting other elements, goals or contracts [43]. This is an extension of the original GSN and its tabular contracts specified in [70]. Both types of contracts are used to argue that a certain system or component property is reached and are not designed for automating the certification process.

Using contracts to enable automatic software updates for individual tasks in a certified failsafe system has been presented by Neukircher et al. [91]. This approach was later extended for mixed-criticality [92]. The feasibility of the configuration change is evaluated based on the individual contracts before applying the upgrade. Monitoring ensures that the tasks which do not stay within the limits defined in their provided contracts are terminated. A similar contract approach has been used by Aldea et al. [5]. Each application provides a contract stating its scheduling requirements and is deployed only if the overall schedule is found to be feasible. However, contrary to the monitoring before, bandwidth servers are used to prohibit resource overconsumption by the individual applications.

Several aspects regarding contracts for system design and component-based design have been compiled and presented by Beneviste et al. [18]. A mathematical theory, based on the elements of contract theory [62] is given, for defining and composing contracts, as well as an overview of several modelling theories. An example regarding the automotive domain and AU-TOSAR also considers timing guarantees in its contracts. In these contracts, minimum and maximum times between occurrences of related events and events received via interfaces are specified using a machine-readable contract specification language.

#### 2.4 Triple Modular Redundancy

Triple modular redundancy (TMR) was originally introduced by von Neumann [118], and the general concept for software-implemented fault-tolerance by Wensley [120]. In software TMR systems, software components are replicated to provide the fault-tolerant functionality, as op-

posed to N-version programming [31], where different software components are developed to also cover faults regarding the software implementation. Schlichting and Schneider [108] presented the fail-stop processor, which stops when too many fault occur. It is constructed from several processors executing the same program and a protocol for reaching consensus. Schneider [109] also suggested the use of replicated state machines for implementing fault-tolerant services. An overview of methods and requirements for achieving fault tolerance with replication has been given by Poledna [97], covering triple modular redundant architectures with hardware lock-step, as well as software-only solutions on commercial off-the-shelf (COTS) hardware. An industrial example for a TMR system is the TAS Control Platform [48,72], which provides TMR for the railway applications built on top of it.

The primary goal of TMR is to keep the system operational in case of a single fault with respect to the *fault hypothesis*. The principle is to have three identical modules, or replicas, and mask the output of one failed replica by the outputs of the remaining two replicas. Such a fault can have various sources, such as a single event upset or hardware wear-out. Depending on the degree of independence of these replicas, detection and fail-over can be reached for different kinds of faults. Consequently, the architecture is separated into three fault containment regions, and it is essential that only one fails at a time. There are three threats to this principle:

- 1. In case of *near-coincident faults* two (or all) replicas fail due to faults of independent origin, i.e. random faults that happen to occur at about the same time. In theory, this is ruled out by the single-fault assumption, and in practice, the very low fault rates make this extremely improbable.

- 2. In case of *common cause failures*, we again encounter failures of two (or all) replicas, this time, however, these originate in the same single fault. An example of a common-cause fault is a software bug that makes all replicas behave in the same erroneous way. That is why fault containment between the replicas is so important.

- 3. In case of *spare exhaustion*, one replica did not recover from a previous fault and there are therefore, too few available to mask the current fault with the remaining replicas. This makes *replacement*, in case of permanent faults, and *recovery*, for permanent and transient faults, of the affected replica essential.

Synchronization in a TMR systems keeps the individual replicas in a comparable (or close) state regarding the time and value domain [97]. Executing CPUs in lock-step operation and adding hardware voters in-between them is one option for such a mechanism [122]. Virtual synchrony, based on group communication and local timeouts, is another approach [25]. It establishes synchronization within the software layer by ordering messages. A vast number of protocols and mechanisms have been defined and used for providing virtual synchrony and fault-tolerance in distributed computing environments [8, 24, 25, 101, 113]. Fault-tolerant synchronization of hardware clocks and subsequent synchronization of input data is a another approach for achieving synchrony [76, 79, 97]. This is also the basis for TMR synchronization in the TTA [17].

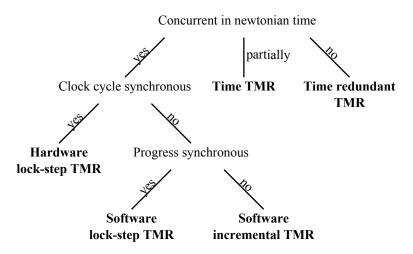

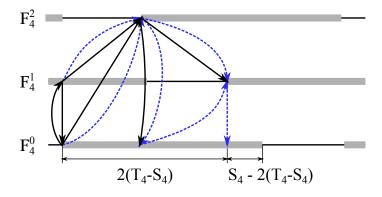

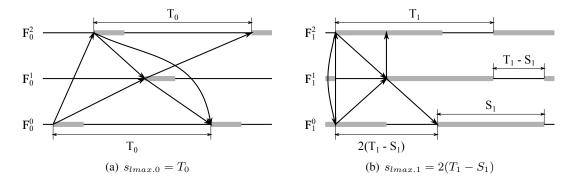

TMR methods for replicating software can be classified as shown in Figure 2.1. They differ in properties of fault containment, concurrency, synchrony and resource utilization.

Figure 2.1: TMR classification for software triplication.

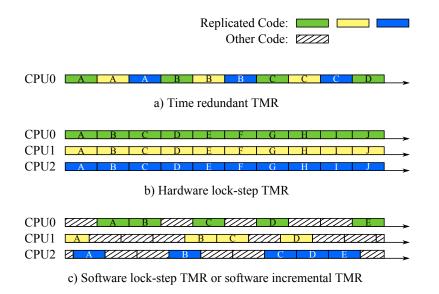

For the time redundant TMR method, instructions or software components are triplicated and executed one after the other on the same processor. Software-implemented voting over their results provides protection against transient hardware faults under the assumption that these affect only one instruction or component in the triple. Based on the same concepts as time redundant TMR, the Time TMR [37] has been developed, which executes some of the triplicated instructions in different computational units of a VLIW processor, reaching partial concurrency within the same processor. For hardware lock-step TMR, three CPUs are connected to the same clock source. The redundant voting is performed in special hardware outside the CPUs, that is connected via suitable buses. Less tightly coupled TMR systems, where voters are implemented in software, have to explicitly communicate between the replicas.<sup>1</sup> In software lock-step TMR, all replicated software components compute the same output, and only after voting has been performed do they continue operation. For software incremental TMR, the software components can be at different states of execution when exchanging their voting data. This full or partial synchronization can be performed periodically or sporadically. However, in both cases timeouts are needed to detect faulty replicas and guarantee reaction times. Thus, an important characteristic in these software TMR systems is the time needed for synchronization. Figure 2.2 illustrates how replicated code is executed in systems based on the presented different TMR methods.

As mentioned before, if long mission times are required, it is essential to provide recovery in the TMR approach in order to remain operational in the presence of several sporadic transient failures occurring over time, as well as during repair or replacement of a permanently faulty hardware module.

<sup>&</sup>lt;sup>1</sup>A motivation for implementing redundancy mechanisms in software instead of relying on specialized hardware has been given by Bernick et al. [20].

Figure 2.2: Execution of replicated code according to different TMR methods.

#### 2.5 Scheduling

Scheduling of safety-critical real-time applications strongly influences their behaviour, especially in the time domain. Various scheduling strategies are in use for real-time applications and composable environments. Liu and Layland [84] provided the task model and initial results for analysis of dynamic fixed-priority and EDF schedulers for real-time tasks on uniprocessors. They proved the optimality of fixed-priority scheduling with rate-monotonic (RM) priority assignment and preemptive EDF for uniprocessors, i.e. if any algorithm can find a feasible schedule, then also these schedulers will find one.

ARINC 653 defines a static-cyclic scheduling scheme with major frames and minor frames for composability. The tasks are assigned slices within this schedule to fulfill their scheduling criteria regarding period and time slice duration. The main challenge during integration concerning this schedule is to find one which satisfies the scheduling requirements of all tasks. Additionally, it is possible to switch between different off-line generated schedules to accommodate various operating modes. A detailed analysis of implementing this approach on the operating system level has been conducted by Baldovin et al. [15].

A comparison of static-cyclic with fixed-priority scheduling, for periodic tasks, has been performed by Locke [85], concluding that RM will result in tasks with higher task schedule jitter but also provides a better CPU utilization. Preemptive fixed-priority scheduling, together with runtime feasibility tests and slack sharing are the key characteristics of the scheduler provided with the real-time OS DEOS for the avionics domain [23]. In the presented examples, it achieves a significantly better utilization than schedules for a static-cyclic scheduler at the cost of system scheduling optimization.

Using servers for limiting resource access is an approach to provide guarantees in systems, where tasks could exceed their designated resource share otherwise [50, 102]. Abeni and But-

tazzo presented the constant bandwidth server to provide execution share guarantees at the cost of limiting execution times for EDF scheduled tasks [2].

Vestal showed that in some scenarios other than RM priority assignment can lead to feasible schedules [116], based on the assumption that applications with a higher criticality are more pessimistic when estimating their worst-case execution time.

Having several layers of schedulers is the focus of hierarchical scheduling [82, 83]. The central idea of this approach is to provide each application with its own scheduling strategy, such that the application-specific schedule and scheduling strategy are preserved when integrating them with other applications and to provide guaranteed resource shares. Integrating hierarchical scheduling and mixed-criticality in virtual environments has been performed by Lackorzyński [78]. The virtual guests and hypervisor are adapted to provide sufficient information to the hypervisor scheduler by letting the guest choose from a set of scheduling contexts. A general solution for mapping hierarchical mixed-criticality fixed-priority schedulers to such a context-aware scheduler setup has been proposed by Völp et al. [117]. Enabling virtual machines to request different resources during runtime is the focus of the concept suggested by Groesbrink et al. [53], where conflicts on these resource requests have to be resolved and the overall schedule of the system adapted accordingly.

A summary on the research regarding real-time scheduling on multi-core systems was given by Davis and Burns [39]. Naturally, providing guarantees on resource access for multi-core platforms is important [22]. For multi-core CPUs feasibility tests exist for (global) EDF and fixed-priority schedulers [9,21].

#### 2.6 Partitioning and TMR

A fault-tolerant prototype combining software lock-step TMR with the partitioning provided by an ARINC 653 RTOS (real-time operating system) has been implemented by O'Connel [94]. The RTOS is modified to synchronize the static-cyclic schedules on the three redundant and fully connected hardware boards. Voting and TMR message exchange for input and output data are implemented in privileged partitions running in the kernel space. To achieve the targeted synchronization precision for the schedules, low-level network driver functionality is included in the RTOS and raw Ethernet MAC frames are used for the periodic clock synchronization. The prototype does not provide a membership service or means of recovery, but it is suggested that a partition could be reset, if it reaches a certain threshold of faults. Reintegration would take place, if it provided valid output values for a certain time after such a reset. With regard to partitioning, the approach differentiates between *Software Fault Containment Regions* established by the partitioning and *Hardware Fault Containment Regions* provided by the individual hardware boards. Integrating several triplicated and independent applications on the same hardware infrastructure was not within the scope of this prototype.

Bauer and Kopetz [17] demonstrated that transparent software-based TMR for applications can be provided within the TTA, where the TTA inherently ensures strong time partitioning and clock synchronization. Synchronizing the schedulers of microkernels (PikeOS) using a time-triggered network has been presented by Theiling [111].

Miller et al. [88] suggested an approach for synchronizing TMR applications on top of static-

cyclic scheduled partitions in an IMA compliant system. The synchronization mechanism is triggered every scheduling round and starts the replicated execution, if a sufficient number of messages have been received. The fault hypothesis of this approach assumes fail-silent nodes.

An analysis on the influence of composability when applied to various TMR methods and presented architectures leveraging this approach was conducted, which results are also included in this thesis [103].

# CHAPTER 3

## **Software Composability**

This chapter gives a general introduction to the fundamental concepts of software composability and describes the prerequisites of step-wise and independent certification. Furthermore, the challenges of composable resource sharing and the relation between composability and TMR are discussed.

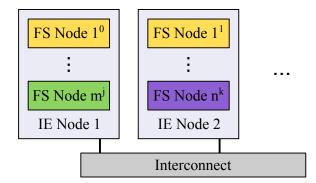

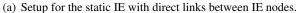

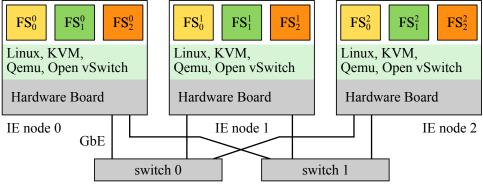

Safety is a system property. Therefore, a single system component can only fulfill a safety property within the context of the whole system application [81]. The intention of composability is to allow building safe and certified systems by careful integration of components, some of which provide safe and (pre)certified functions. As an immediate advantage, this facilitates the reuse of certified components. We call such a component *function-set* (FS), to emphasize that functions are provided by one or more entities, especially in a TMR architecture. These FSs are then deployed within an *integration environment* (IE) to build the whole system. Here, the possibility of sharing the same IE for different (sub-)systems, thus saving cost, space and energy, represents another advantage. An FS provides a (sub-)service within the application context and is assigned a criticality level according to the criticality of that service. Obviously, the proper provision of this service can only be guaranteed on the condition that the IE exhibits all the properties that have been assumed in the design of the FS. While this is relatively trivial to establish in the traditional federated architectures (i.e. using a separate IE per FS), it becomes an issue in integrated approaches, since the properties of the IE, as perceived by a single FS, are (dynamically) influenced by the other FSs during their execution. Therefore, to enable composability, every FS must be associated with an appropriate function-set contract, specifying its requirements to the IE for correct execution. We refer to the deterministic availability of resources from the IE as *predictability*<sup>1</sup>. This first constituent of composability becomes crucial when FSs or elements of the IE are to be changed. Note that in the interest of a simple FS contract static guarantees (i.e. high predictability) are beneficial, while more fine-grained, even dynamic requirements usually facilitate a better resource utilization. In addition, the former is easier to enforce by technical means (see later).

<sup>&</sup>lt;sup>1</sup>Unlike Akesson et al. [4], we define predictability with respect to available resources for FSs as provided by the IE and not as predictability of execution times and resource demand of FSs.

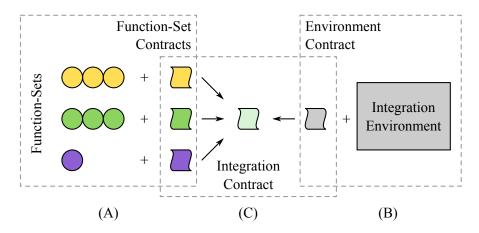

Figure 3.1: Certification strategy using contracts for mixed-criticality and composability.

The second constituent of composability, namely *non-interference*, concerns undesired effects that the execution of an FS may have on the IE and consequently on other FSs, specifically in case of failure. Again, one could, in principle, conduct a fine-grained, application-specific analysis on malign and non-malign cases to allow for the largest freedom. In practice, however, the most rigorous approach has proven most effective – a strict *failure confinement*<sup>2</sup>. Herein, each FS forms an individual *failure confinement region*, the failure of which remains local and has no effect on any of the others.<sup>3</sup> This property cannot be enforced within the FS itself, since restricting an FS's failure behavior is normally very expensive, and sometimes even impossible. Consequently, this task has to be fulfilled by the IE, which needs to implement technical provisions to *separate* the FSs from each other.

In the context of mixed-criticality, it is interesting to note that non-interference is a directional property: One may be very concerned about a non-safety-critical FS undermining the IE's assertions for a high-criticality FS, while at the same time it is – by definition – not as critical when the latter prevents the former from executing correctly. Failure confinement, however, does not appreciate this directionality; typically, the separation mechanisms are applied equally to all FSs, irrespective of their criticality.

Ultimately, the composability approach allows to split the certification of a system into three parts, as illustrated in Figure 3.1:

- (A) Each safety-critical FS is certified with respect to its FS contract, which specifies all the FS's requirements for safe operation. These requirements may cover computational and networking resources, as well as separation guarantees and the availability of special services such as watchdogs or real-time clocks.

- (B) An IE, e.g. hardware boards and middleware, is certified with its integration environment contract, stating the provided resources, services and failure containment properties, as

<sup>&</sup>lt;sup>2</sup>Like the "Gold Standard for Partitioning" defined by Rushby [107].

<sup>&</sup>lt;sup>3</sup>Please note that fault containment regions are defined with respect to the fault containment of TMR systems (see Section 3.3).

well as its feasibility evaluation method used for integration. The validity of this feasibility evaluation method is a key element when certifying the IE.

(C) The FS- and IE contracts are specified using generic properties, like network bandwidth, to enable reusing of FSs in different IEs. A concrete system is then certified by matching the IE contract with the FS contracts in an *integration contract*, using the feasibility evaluation method specified in the IE contract.

Please note that for each safety-critical FS step (A) is performed separately, as is step (B) for each specific integration environment. Furthermore, for each new or altered system step (C) must be implemented. This method needs more initial effort than certifying one system as a whole, Nonetheless, it is more efficient when building several slightly different systems, or altering existing ones. Additionally, a good utilization of the hardware resources within the IE is expected. The contracts here are based on the provided resources and features of the IE, unlike the contracts of contract-based design [19] which specify component interfaces and behaviour, and subsequently create new ones with various operations performed on other components. It is important to note that composability in our context is merely concerned with the separation issue, i.e. protecting one FS from the failure of another that shares resources with it. It is also not capable of tolerating faults in these resources, which is the goal of triple modular redundancy.

#### 3.1 Attaining Composability

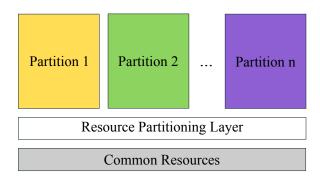

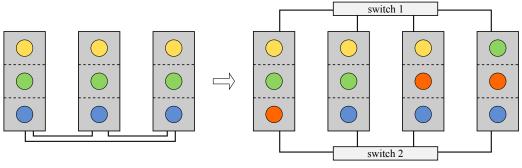

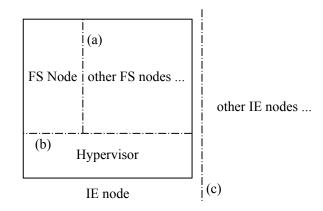

The general idea for constructing an IE is to implement a layer that provides failure confinement regions (*partitions*) within the IE, sufficiently mitigating the undesired effects of integration and independent of the specific hardware setup as shown in Figure 3.2.

Figure 3.2: Generic resource sharing concept with partitions.

Here, the non-interference and predictability requirements of the individual safety-critical partitions are fulfilled by the partitioning layer for the hardware resources. This layer takes care of services like partition scheduling, memory management and provision of virtual I/O services. This implies that the partitioning layer has more privileges than the partitions in order to maintain full control over the system. The partitioning could be implemented within an operating system, which has to ensure that all system calls are composable, e.g. a suitable microkernel OS. In

such solutions the kernel itself offers only a very limited set of functionality, i.e. inter-partition communication and direct device access. Consequently, the other shared system services must also be composable themselves. Alternatively, it is possible to implement such a partitioning layer using virtualization techniques, e.g. hypervisors. With virtualization, most of the low-level functionality is provided by the guest OS, which is encapsulated in the same partition as the application. As already pointed out in Chapter 2, microkernels can also use virtualization technology and the boundary is not that sharp. However, our focus is composability of TMR systems and not the actual implementation. As such, we will also not go into detail with possible security aspects of methods for non-interference.

In the following, we investigate the resources that are typically shared among FSs within a common integration environment, as well as suitable separation techniques for such resources.

#### Processing

A typical example here is a single processor that is shared by different FSs<sup>4</sup>. The clear advantage of sharing is the better utilization of the processor that may be too powerful for just a single FS. As the resource sharing is performed in the time domain, the FS contract and integration environment contract will have to be concerned with providing a suitable share of the processing power to the individual FSs, in terms of total computation time, as well as the availability of such computation time at certain instances in time. The mission of separation is to enforce this time sharing and prevent a failed FS from consuming another FS's share. This is clearly a scheduling issue. In the ARINC 653 standard a static-cyclic partition scheduling with major frames and minor frames is employed [114]. For safety-critical partitions a static-scheduling scheme has to be guaranteed, whereas other partitions could be scheduled differently. The final schedules obviously have to fulfill all safety-critical FSs' timing requirements. As presented in Chapter 2, many different scheduling schemes, like priority-based scheduling with additional mechanisms, such as constant bandwidth servers for ensuring predictability on a higher level.

#### Memory

In contrast to the case of processing treated above, memory is a stateful resource, which is why time sharing is not applicable. Instead, the physical memory (we refer to RAM in the following) must exhibit sufficient capacity to store all data from all FSs. The benefit of having one larger memory instead of several individual smaller ones is (a) saving control logic, and (b) achieving a reasonable level of occupancy even if individual FSs demand memory sizes that do not fit well to a power of 2. The mission of partitioning is to ensure that each FS can access only that portion of memory that has been exclusively assigned to it and is unable to access (in the worst case corrupt) the memory of other FSs. Typically, a Memory Management Unit (MMU) is used for this purpose.

<sup>&</sup>lt;sup>4</sup>We may as well imagine a set of processors with dynamic dispatching of tasks from different FSs. This is of course the more generic concept, however, the chosen simple example is sufficient to illustrate the key issues.

Strict non-interference also requires that CPU caches are either disabled in general, or they have to be flushed and restored at each partition switch to prevent memory access jitter. This is only necessary for safety-critical partitions with very stringent timing requirements.

#### **Devices and I/O**

For this type of shared resource we choose disk I/O, networking, hardware watchdogs and realtime clocks to illustrate a wide range of different properties and behaviours.

Basically, I/O resources can either be exclusively assigned to single partitions, in which case non-interference is trivially guaranteed, or the access has to be managed by the resource partitioning layer. This is typically implemented by providing a "virtual instance" of the resource to the individual partitions and managing the synchronization of the actual resource either directly in the partition layer or within a privileged partition. In this sense, *disk sharing* can be done with actual or virtual disk drivers. Similarly, *networking* can rely on the actual network interface or on virtual network interfaces, virtual switches and virtual routers.

Note that the virtual access is similar to the processing discussed above in that there is only a single resource available that is shared in a time multiplex fashion. Therefore, the contracts have to be concerned with bandwidth and transmission time guarantees. Again, additional requirements concerning the instants of availability may apply in a real-time context – hence, the scheduling issue emerges here again.

The *real-time clock* (RTC) is a particularly difficult device to share, since it is, by definition, a stateful device – which rules out its use in a time multiplexed fashion – but at the same time it cannot be replicated like, e.g., the memory space. Depending on the FS's requirements, three different options for the emulation of a RTC are possible:

- FSs requiring only reading the RTC and alarms and timers: For these FSs, the RTC emulation can be restricted to multiplexed reading of the clock and handling distribution of alarms and timers.

- FSs requiring reading and writing of the RTC but no preservation of time during power off:

Here, a clock with higher granularity than the RTC is needed for correct emulation of writing and reading the RTC. A FS writing a value to its emulated RTC expects the RTC's value to increase at a certain time after that. For example, a FS setting the RTC to 00:00:00 and reading its value 100ms later, still expects to get 00:00:00 as time value. Therefore, offsets between the emulated RTCs differ according to the value and time of occurrence of the respective FS write.

• FSs requiring reading and writing of the RTC, as well as preservation of time during power off:

This is the most difficult case, since a clock with higher granularity than the RTC is needed for write emulation, and the RTC and non-volatile memory are needed for preservation of the time value and offsets during power off.

Sharing a *hardware watchdog* raises similar issues. To enforce non-interference a watchdog has to be emulated for each partition within the partition layer. Still, a failure in the partition layer might cause a halt of computation, so an actual hardware watchdog has to be triggered systematically by the partition layer.

In addition to the regular I/O capabilities, the partitioning layer may provide means of interpartition communication. Here, it has to be ensured that these mechanisms are not used to undermine the composability concept of the partitioning, e.g. a partition providing non-composable I/O sharing for other partitions.

#### Summary

All these methods either have one or both of these demands:

- Extra hardware features, e.g., MMU or CPU support providing the partitioning layer with full control over the system<sup>5</sup>, or

- Extra scheduling, e.g., for sharing of the CPU, virtual networking or emulation of devices.

The impact of the presented additional hardware features on TMR applications is linear with respect to execution time, e.g., setting the MMU costs a few instructions per context switch of partitions. Consequently, we focus on scheduling in our analysis.

#### **3.2** Requirements for Function-Sets with a Safe State

In applications without a safe state, the correct and timely execution of all safety-critical FSs is mandatory and the system must remain operational even under (the hypothesized) faults. This clearly demands uncompromized predictability and strict partitioning.

Safety-critical systems with a safe state, in contrast, can handle cases where no results or outputs are provided by a safety-critical FS. The important property here is that no *incorrect* outputs are produced. This is normally ensured by fault-tolerance measures, e.g. TMR. The remaining, but very important, requirement on the partitioning layer is not to undermine the error detection and/or masking capabilities of these measures, e.g., by introducing common-mode failures.

If this aspect is ensured, the failure confinement regions might otherwise not require as strong separation as in the fail-operational case, with respect to scheduling and timing. For example, it may be tolerable to guarantee CPU scheduling with some probability, rather than cycle-wise assurance. Caches may remain enabled and do not need to be flushed on scheduling switches between partitions as memory access jitter may be tolerated. In case of overload it might, e.g., be possible to allow safety-critical partitions some CPU time in excess of the assigned slot, thus increasing the overall robustness of the system.

In the remainder of this thesis, the term *composability layer* is used rather than partitioning layer to emphasize that it is not necessarily required to achieve full partitioning in all cases.

<sup>&</sup>lt;sup>5</sup>Examples for CPU features enabling full control over the system are trap-and-emulate or a special execution mode [3].

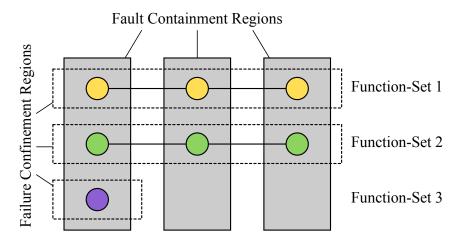

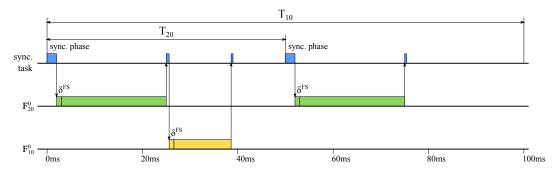

Figure 3.3: Function-sets in failure confinement regions and fault containment regions.

#### 3.3 Failure Confinement Regions vs. Fault Containment Regions

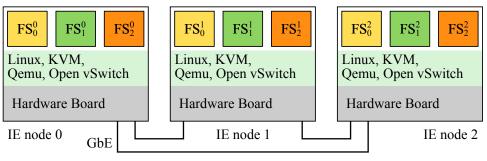

Composability is a concept orthogonal to TMR that aims, as already outlined, at achieving better resource utilization and ease of the certification process upon integration. These benefits equally apply for composability in TMR architectures. As illustrated in Figure 3.3, the IE may comprise replicated modules, and we have two orthogonal regions in a composable TMR architecture:

- The replicated hardware modules form *fault containment regions* required to prevent single points of failure in the TMR architecture. With a properly working TMR, the safe execution of a FS can be ensured even in case of a random fault in its IE.

- Within these hardware modules, each FS forms a *failure confinement region*. This establishes the non-interference required for composability. With non-interference, the safe TMR execution of a FS in presence of other FSs is guaranteed.

In this scheme, a safety-critical FS comprises three entities, each representing a computing channel. FS 1 and FS 2 are examples of this. Assume the fault containment regions are independent hardware boards, then the failure of one is observable as fault of one entity for FS 1 and 2. In contrast, a single event upset (SEU) in the memory of one entity is only observable by the affected FS, as the failure confinement regions provide isolation within the fault containment region.<sup>6</sup> Furthermore, if FS 2 fails due to a software error, the failure confinement regions provide protection for FS 1 and FS 3.

Note that, in our example, FS 3 comprises one computing channel only, as it is not safetycritical. This already indicates that having three computing channels per FS only illustrates the fundamental principle of this architecture, and many variations are possible. For the fault tolerance scheme, e.g., a simplex or duplex architecture could be chosen instead of TMR as well, as

<sup>&</sup>lt;sup>6</sup>This is also the reason we do not use the terms Software Fault Containment Regions and Hardware Fault Containment Regions as O'Connel [94], since composability may provide separation for software, as well as hardware faults.

is appropriate for the needs of the specific FS. More generally, there is a lot of freedom in aligning the failure confinement regions of the FSs with the modules' fault containment regions. One may, e.g., leverage the error detection capabilities of the applied fault tolerance scheme for localizing errors within partitions and only selectively stop and recover the affected partitions rather than re-booting and testing the complete system. As already described, a potential risk is that bugs in the composability layer may lead to common-mode failures, thereby undermining the fault tolerance concept. Strategies against such failures are, e.g., to use a certified composability layer, or one that is proven-in-use and incorporate suitable measures within the FSs.

## CHAPTER 4

## **Composability for TMR Architectures**

In the course of this chapter, we first take a close look at different TMR architectures and their behaviour when introducing composability, before discussing existing and novel TMR architectures enabled by the composability approach.

#### 4.1 Contemporary TMR Architectures

In a TMR system three replicas are executed within three different fault containment regions. To keep the three replicas of a TMR system close in the time and value domain, the following three key services are necessary:

- Synchronization of the input and output data (and/or state) of the replicas,

- Voting of the synchronized data, and

- Recovery, i.e. reintegration of a new replica or one that experienced a transient fault.

Contemporary TMR architectures vary largely with respect to their fault containment regions and synchronization approaches, as already discussed in Section 2.4. Consequently, when adding composability, different strategies are needed depending on these individual properties. We outline these strategies, the incurred overhead and other implications based on the characteristics of the TMR method for time redundant, hardware lock-step and software-based TMR.

#### **Time redundant TMR**

For time redundant TMR, software instructions (or components) are triplicated at compile time and voting instructions (or components) are added automatically. The triplicated instructions use different memory, which is also assigned during compilation. The fault containment regions in this architecture are instruction sequences and corresponding memory region for the state. As time redundant TMR uses only one processor, it can only mask transient hardware faults, e.g. SEUs. This method does not require special hardware and can be used on a COTS processor. The key services from above are established as follows:

- Synchronization is implicitly given with this method due to the order of execution on the same processor.

- Voting is performed for each instruction sequence or software component separately on the input data provided by all three replicas of the previous execution.

- For software components, recovery is performed by overwriting the memory of the faulty component with the voted memory values of the other two components. It is not necessary for instruction sequences, as all input is voted and these sequences' local state is only dependent on the input.

The overhead regarding memory and execution time introduced for voting is strongly dependent on the frequency of it being executed. Naturally, repair and replacement cannot be performed during the operational phase of the system.

Here, the potential conflict between fault tolerance and composability becomes apparent: Separation of memory and CPU can be ensured by a composable scheduler and an MMU, respectively. In this setting, however, both the scheduler, as well as the MMU represent single points of failure from the fault-tolerance point of view. While the scheduler (and potential further software-based composability services) can, just like the FSs, be protected by time redundant execution as well, the MMU remains problematic.

In general, the performance impact can be deducted from the scheduling scheme. With a static-cyclic scheduler, the reaction time can be derived from the maximum time between scheduled slices of the safety-critical FS entities and the slice duration. However, this can vary for specific FSs and also depends on the shared I/O devices. Mixed criticality can achieve good hardware utilization in this architecture, as only safety-critical FSs are triplicated, while non-critical FSs can use CPU and memory at native speed.

The *Time TMR* [37] architecture presented in Section 2.4 has the same properties regarding composability as time redundant TMR. Executing some instructions on different CPU components has no advantages regarding composability, when compared to time redundant TMR.

#### Hardware lock-step TMR

Hardware lock-step architectures are widely used in the industry [63]. They consist of triplicated CPUs and memory with hardware voters in-between. The software is stored and executed in two types of fault containment regions: different CPUs and different memory. This architecture tolerates both transient and permanent hardware faults. Naturally, as the fault tolerance is provided by the hardware, such special hardware boards are a prerequisite. Here, the three key services are provided as:

• Synchronization is achieved by operating the CPUs with the same clock (which is why the CPUs are sometimes located together on one hardware board), resulting in them issuing the same memory operation on the bus at the same time.

- Voting is performed in hardware voters between the CPUs and the memory operations and their value.

- Recovery is performed by stopping triple execution and reconstructing the state of the erroneous CPU from the other two.

A current industrial example for such a hardware lock-step board is the D602 from MEN Mikro Elektronik GmbH [51].

The inherent triplication of the lock-step architecture is an advantage and a drawback within the composability context at the same time. Safety critical FSs, as well as non-critical FSs, are all automatically triplicated and recovered, which degrades resource utilization. Fulfilling the composability requirements specified in Chapter 3 for each fault containment region locally, i.e. CPU, memory and I/O, is already sufficient for composability of the triplicated modular redundant system, since the triplication mechanism is not influenced by the composability layer – rather the composability layer is triplicated. As in the case of time redundant TMR, the performance impact is closely related to the composable scheduling and I/O sharing strategy.

#### Software-based TMR

The two software-based TMR methods discussed in this thesis, software incremental TMR and software lock-step TMR as presented in Chapter 2, share most of their properties, and so we do not need to differentiate here<sup>1</sup>.

In software-based TMR, a middleware software is running on three fully connected hardware boards, controlling the execution of the replicated application on top of it. The three hardware boards are the three fault containment regions. Such an architecture tolerates transient and permanent hardware faults, and a set of quasi-random software faults as described in [47]. This architecture has no special requirements on the underlying hardware. Furthermore, this approach enables to layer the system in such a way that the lower level hardware and OS could be replaced without much influence on the applications themselves [98]. The three key services are provided by the middleware:

• Synchronization is achieved by exchanging the input and output data of applications and time values of the local clocks via messages between the three instances of the middleware layer.

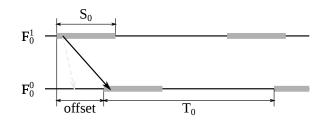

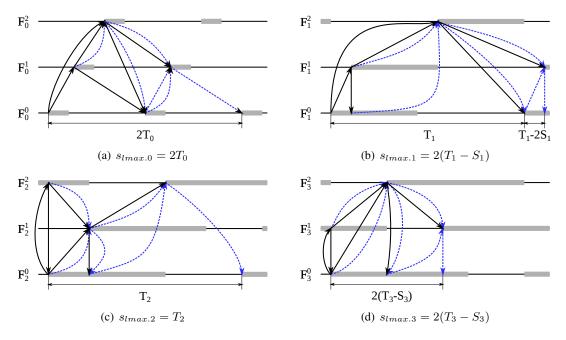

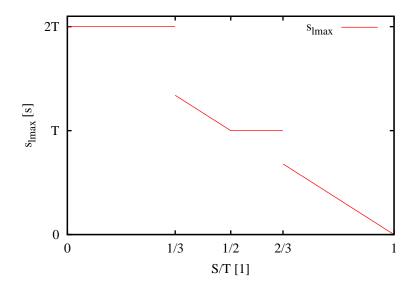

Defining a range in which the process of synchronization is performed periodically is the common solution for both event-based and time-triggered computation. For the latter, periodic synchronization is required by definition, whereas, for the event-based computation, a minimum period is required against overload and a maximum period to check for liveness of the individual replicas.

The correct choice of period is crucial for the operation of the TMR system. A short period leads to lots of message exchanges, scheduling of the middleware and, consequently, less

<sup>&</sup>lt;sup>1</sup>The differences of software lock-step and software incremental TMR are explained in detail at the end of Section 7.1.

CPU time for the application, while a long period results in long reaction times. It is the application developer's task to find the right balance.

The synchronization precision correlates with the reaction times of the individual middleware processes and communication latencies. Low scheduling latencies and jitter for the middleware processes on the different hardware boards are just as beneficial for the synchronization precision, as are low message transmission times and jitter between the hardware boards.

- Voting is executed on the application data and time values received via messages. Only the voted data and time values are passed to the application instances. The application must follow design constraints provided by the middleware to guarantee a replica-deterministic execution.

- Recovery is performed by the middleware without interruption of the active replicas. For this purpose, the middleware must know which replicated data needs to be recovered and has to have enough communication resources in addition to the regular bandwidth required for synchronization. With recovery and three hardware boards, maintenance actions can be performed online during system operation.

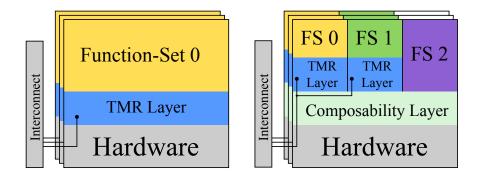

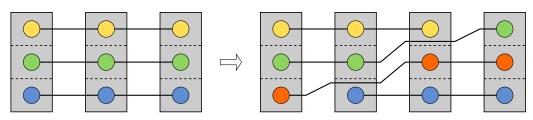

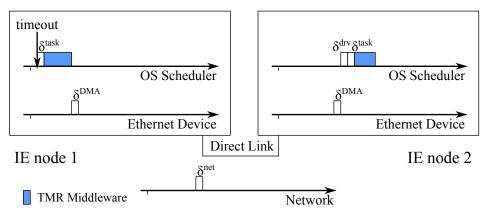

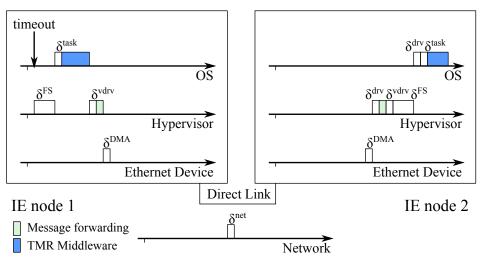

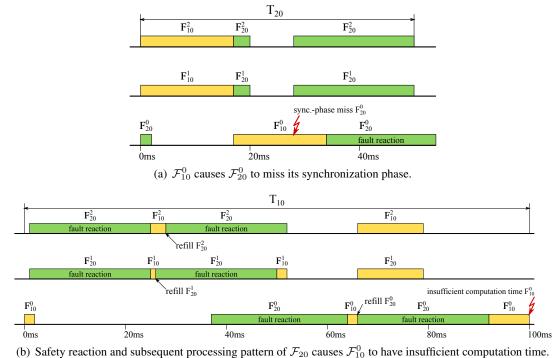

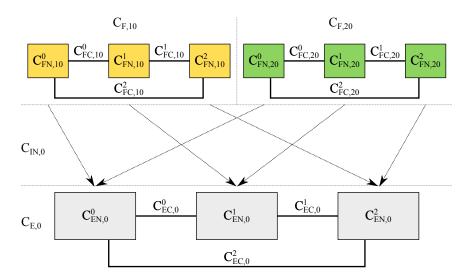

Figure 4.1: Software-based TMR without (left) and with (right) composability layer.

Figure 4.1 shows the introduction of the composability layer to software-based TMR below the triplication middleware, i.e. the TMR layer. While this enforces the desired separation of the TMR instances, the execution of the latter now relies directly on the composability layer, more specifically on its scheduling on the hardware boards and the message transmission times on the (shared!) communication links in-between. Thus, the composability layer has a direct influence on the TMR layer properties. Local non-interference for partitions, as described in Chapter 3 for the composability layer, is not sufficient for achieving good reaction times when integrating several independent triples. The execution of the triplicated applications depends on the composable scheduler, as well as on the synchronization mechanism of the corresponding TMR middleware.

The TMR synchronization process of the middleware is affected in the following two new ways in these architectures:

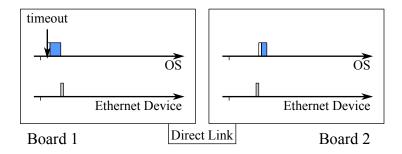

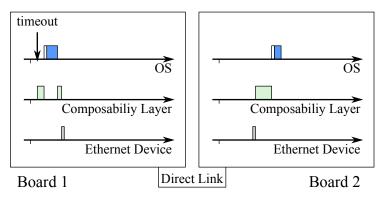

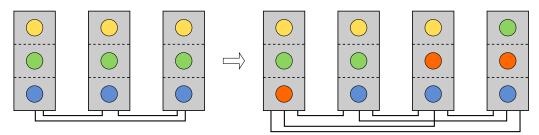

OS TMR Middleware Device

(a) Creating, sending and receiving a message upon a timeout with the OS executing directly on the hardware board.

OS TMR Middleware Composability Layer Device (b) Creating, sending and receiving a message upon a timeout with additional scheduling of the composability layer.

Figure 4.2: Additional scheduling with composability layer.

- By resource management in the composability layer, and

- By sharing the same communication interfaces and interconnect with other TMR middleware.

The change of scheduling with the introduction of the composability layer is illustrated in Figure 4.2. In this example, one instance of the TMR middleware layer sends a message to a corresponding instance on another board. It is the scenario for the start of the synchronization process. The additional steps with the composability layer are: scheduling the sending FS instance after the timeout occurred, forwarding the message on the sending side and scheduling the FS instance forwarding the message on the receiving side. While the time necessary for scheduling processes by the OS scheduler is short, scheduling operations by the composability layer are more expensive, since more operations are required for the context switch. Measurements regarding this difference are presented in Section 12.2 on page 93. Note, that in the illustration

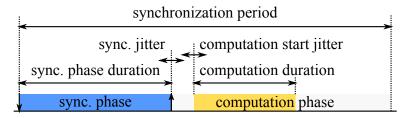

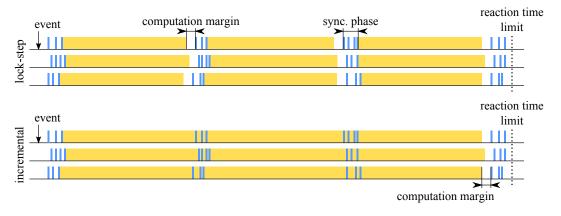

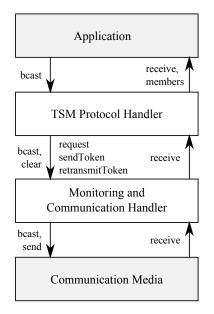

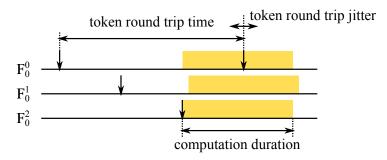

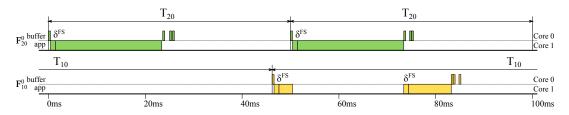

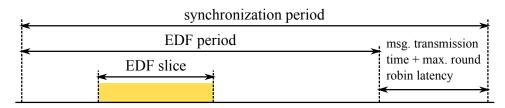

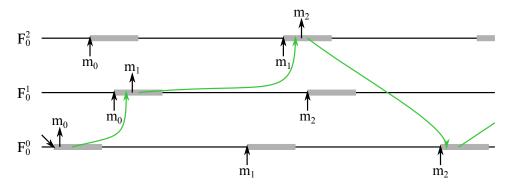

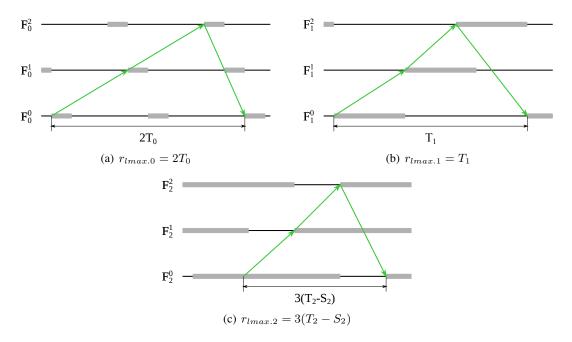

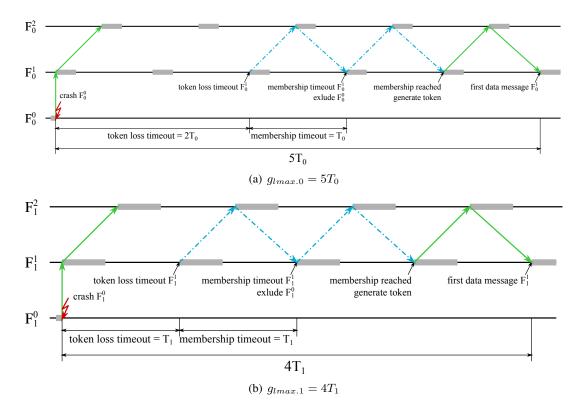

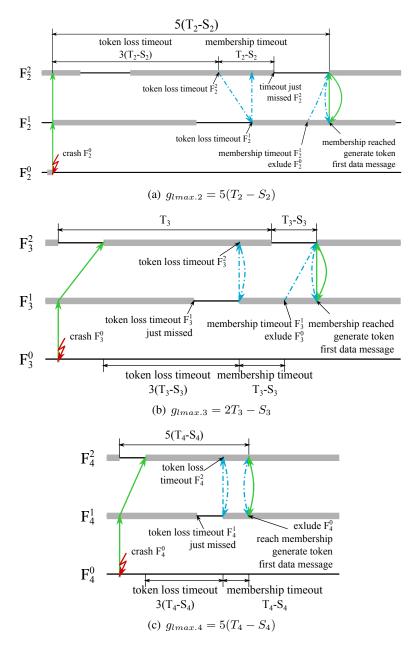

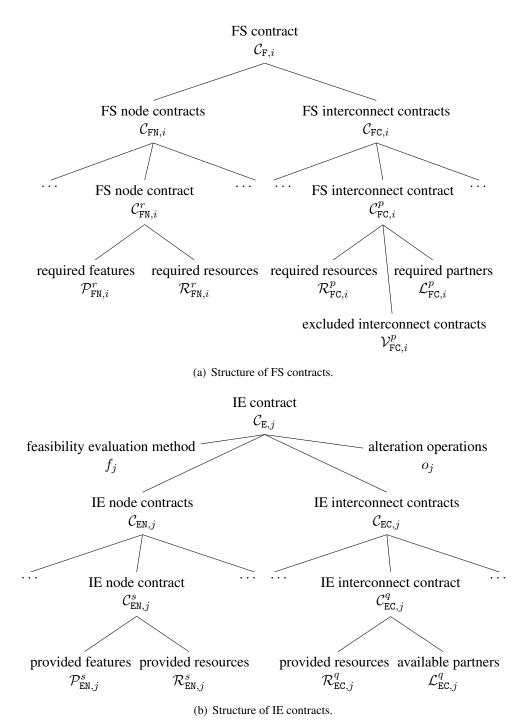

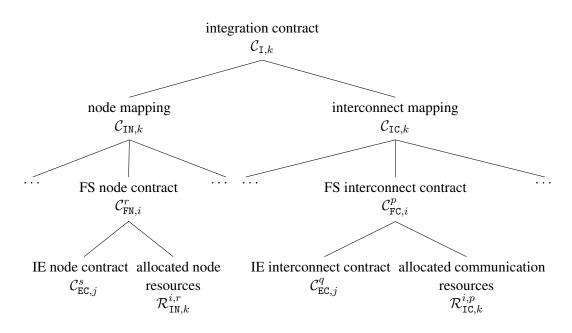

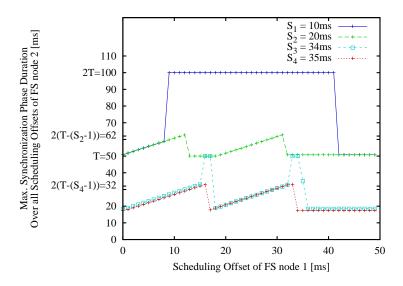

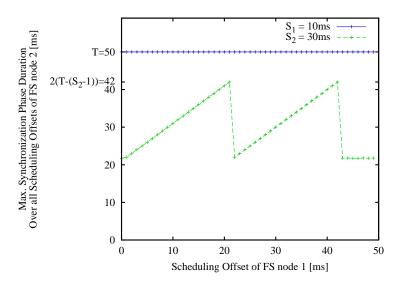

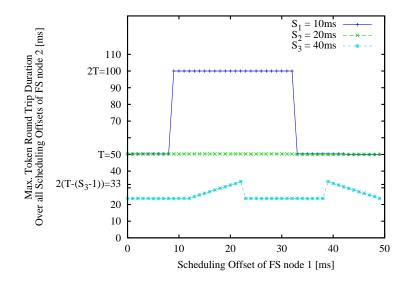

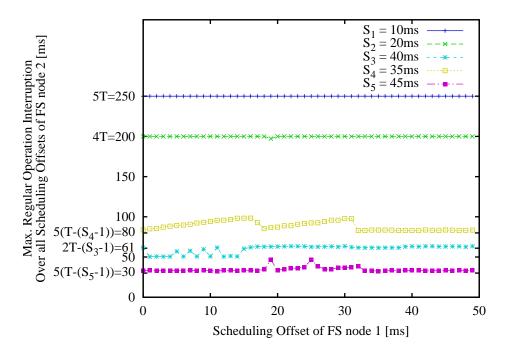

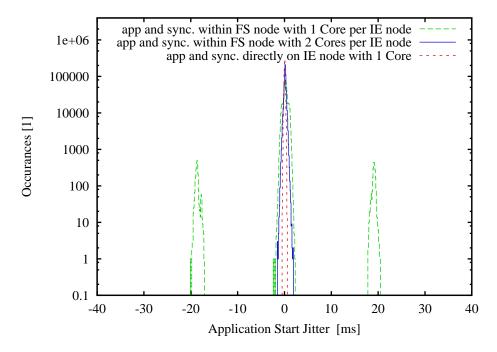

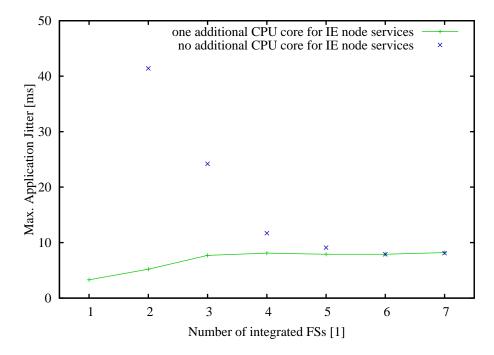

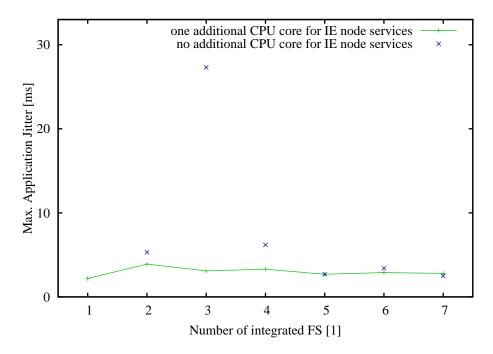

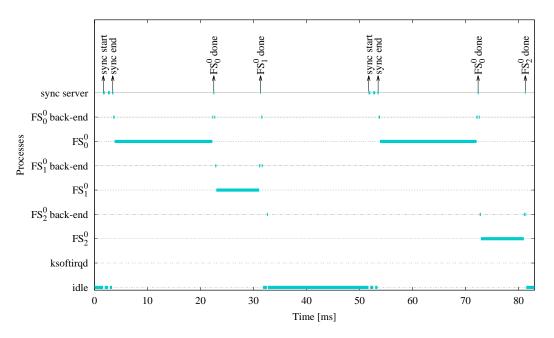

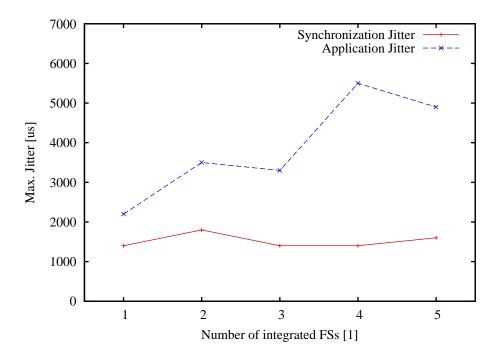

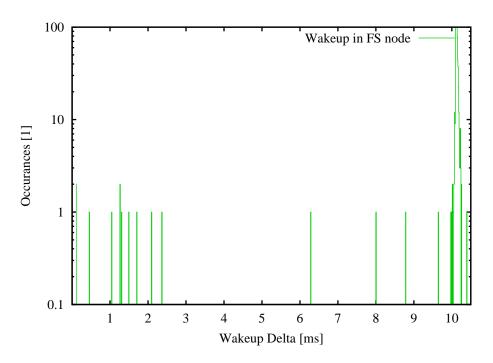

above no other integrated TMR replicas are active, which could delay the sending and receiving of messages even more.