Die approbierte Originalversion dieser Diplom-/ Masterarbeit ist in der Hauptbibliothek der Technischen Universität Wien aufgestellt und zugänglich. http://www.ub.tuwien.ac.at

TŲ UB

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology. http://www.ub.tuwien.ac.at/eng

# **DIPLOMA THESIS**

# A FPGA based DAQ system for mobile robot use

Submitted at the Faculty of Electrical Engineering, Vienna University of Technology in partial fulfillment of the requirements for the degree of Master of Sciences (Diplom-Ingenieur)

under supervision of

Em.O.Univ.Prof. Dipl.-Ing. Dr.techn. Gottfried Magerl, Projektass.Dipl.-Ing. Christian Walter Msc.

by

René Paul Hinterberger Matr.Nr. 0425858 Bruesslgasse 36/23, 1160 Vienna

## Kurzfassung

Ziel dieser Arbeit war die Entwicklung eines "A FPGA based DAQ system for mobile robot use" (FPGA basierendes Datenerfassungssystem für den Einsatz an mobilen Robotern). Obwohl dieses Gerät für eine Vielzahl von Anwendungen genutzt werden kann, war das primäre Ziel ein Datenerfassungssystem für Ultraschallsensoren welche auf einem mobilen Roboter befestigt sind. Um die Verwendbarkeit in einem weiten Bereich zu ermöglichen, wurde ein universeller Ansatz bei der Entwicklung des Hard- und Softwarekonzepts gewählt.

Die Hauptanforderungen für eine Verwendung mit Ultraschallsensoren sind: Ein digital zu analog und vier analog zu digital Konverter mit präziser Zeitmessung um Ultraschallsignale senden und empfangen zu können, bei denen Pulskompressionsverfahren für hochauflösende Laufzeitmessungen zum Einsatz kommen. Durch diese hochauflösenden Laufzeitmessungen kann die 3D Position des reflektierenden Objekts berechnet werden. Die Verwendung mehrerer Kanäle erhöht dabei die Zuverlässigkeit des Systems.

Anforderungen an das System sind: ein definierter und stabiler Phasengang, gleichzeitiges Abtasten auf allen Kanälen, geringes Kanalübersprechen, ein hoher Dynamikbereich (10Bit ADC) und hohe Abtastraten (>10MSPS). Um eine maximale Flexibilität des Systems zu erreichen wurde ein FPGA mit "Softcore" und eine USB Schnittstelle verwendet. Durch den Einsatz des FPGA können rechenintensive Operationen in Hardware abgebildet werden, wodurch der Mikroprozessor entlastet wird. Die USB Schnittstelle ermöglicht eine einfache Verbindung mit einem PC und MATLAB.

Der Prototyp welcher in dieser Arbeit entwickelt wurde, erlaubt es Datenraten von 400MBit/s pro Kanal zu verarbeiten, wodurch sich eine Systembandbreite von 1,6GBit/s ergibt. Durch die Verwendung von pinnkompatiblen Komponenten sind Datenraten bis zu 4,8GBit/s möglich.

#### Abstract

Goal of this thesis was to develop a working prototype of an "A FPGA based DAQ system for mobile robot use". Such a device is suitable for a wide variety of applications although our primary target was a data acquisition (DAQ) system for an ultrasonic sensor mounted on a mobile robot. To assure applicability in a larger number of projects a more universal approach was chosen for the design of the hard- and software concept.

The primary requirements for the ultrasonic sensors are: One digital to analog converter and four analog to digital converters, with precise timing to transmit and receive ultrasonic signals. These are further post processed using pulse compression methods for high resolution time-of-flight (ToF) measurements. Using such high resolution time-of-flight measurements the 3D position of a reflection point can be calculated. Additional channels can be used for enhancing the reliability of such a sensor.

Desirable properties of such a DAQ system are: well defined and stable phase, synchronous sampling on all channels, low channel crosstalk, high input dynamic range (10Bit ADC) and a high sample rate (>10MSPS). For maximum application flexibility a FPGA with a softcore and a USB interface was used. Using an FPGA allows implementation of computation expensive processes in hardware offloading the MCU load. The USB interface allows easy connection to a PC running MATLAB.

The prototype developed in this work allows data rates of 400MBit/s per channel resulting in a total system bandwidth of 1,6GBit/s. Using the same software in combination with pin-compatible components data rates up to 4,8GBit/s are feasible.

# **Table of Contents**

| 1. In | troduc   | ction                                        | 6  |

|-------|----------|----------------------------------------------|----|

| 1.1.  | The      | eory about time discrete systems             | 7  |

| 1.2.  | Har      | rdware / Software Codesign                   | 9  |

| 1.3.  | The      | eory about FPGA & VHDL                       |    |

| 2. C  | oncept   | t                                            |    |

| 2.1.  | Hardv    | vare/Software Codesign                       |    |

| 2.2.  | Partiti  | ioning                                       | 16 |

| 2.3.  | Hardv    | vare Concept                                 | 17 |

| 2.    | 3.1. Fl  | PGA                                          |    |

| 2.    | 3.2. Po  | ower supply                                  |    |

| 2.    | 3.3. P   | C Interface                                  |    |

| 2.    | 3.4. A   | nalog to Digital Converter                   |    |

| 2.    | 3.5. A   | nalog interface and Variable Gain Amplifier  |    |

| 2.    | 3.6. D   | igital to Analog Converter                   |    |

| 2.4.  | Softw    | are Concept                                  |    |

| 3. D  | etails o | on the Hardware Design                       |    |

| 3.1.  | FPO      | GA Board                                     |    |

| 3.2.  | Pov      | wer Supply                                   |    |

| 3.3.  | PC       | Interface                                    |    |

| 3.4.  | Dig      | gital to Analog Converter                    |    |

| 3.5.  | Ana      | alog to Digital Converter                    |    |

| 3.6.  | Ana      | alog input with Voltage Controlled Amplifier |    |

| 3.7.  | Pro      | grammable VHDL Hardware                      |    |

| 3.    | 7.1.     | MicroBlaze Softcore                          |    |

| 3.    | 7.2.     | Peripheral IP's                              |    |

| 3.    | 7.3.     | Multiport Memory Controller                  |    |

| 3.    | 7.4.     | Custom IP                                    |    |

| 4. D  | etails   | on the Software Design                       |    |

| 4.1.  | Inte     | erface PC <-> Softcore (uC)                  |    |

| 4    | .2.                    | Interface Softcore (uC) <-> custom IP                |    |

|------|------------------------|------------------------------------------------------|----|

| 4    | .3.                    | PC Software (MATLAB)                                 |    |

| 4    | .4.                    | uC Software (C)                                      |    |

| 5.   | Mea                    | asurements & Results                                 | 51 |

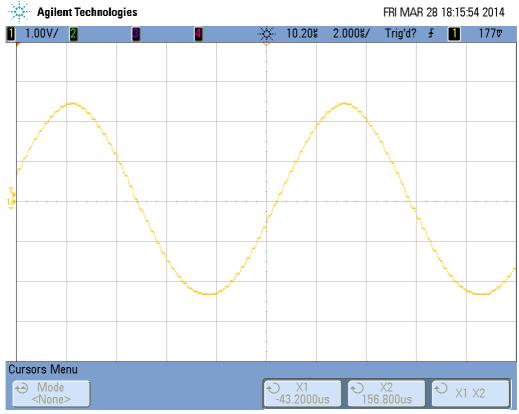

| 5    | .1.                    | Measurements of ADC & DAC                            | 51 |

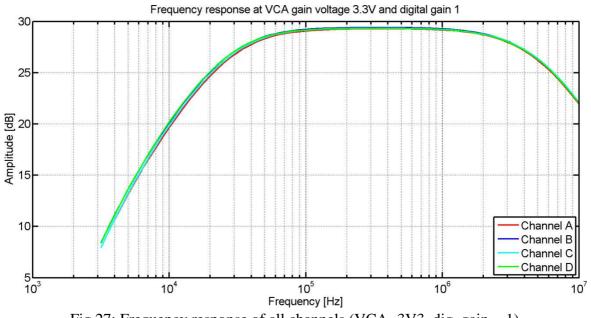

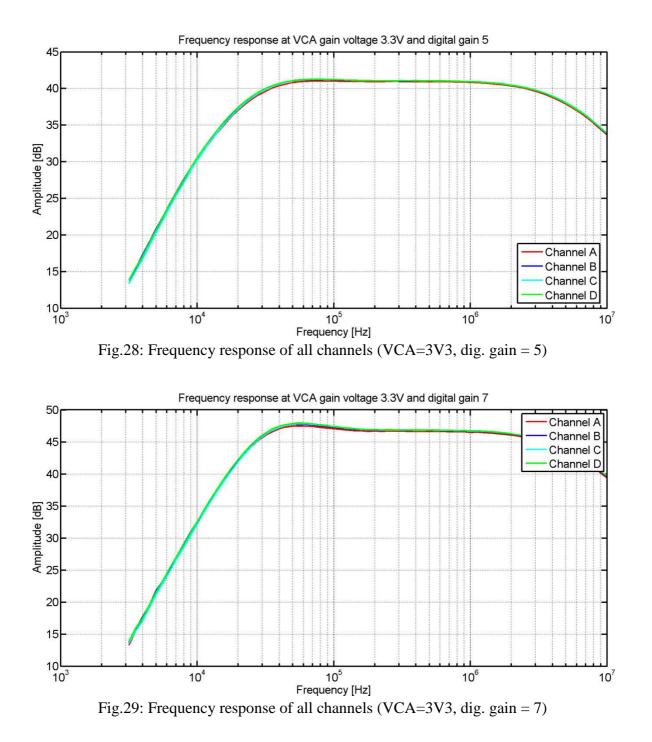

| 5    | .2.                    | ADC Frequency Response                               | 51 |

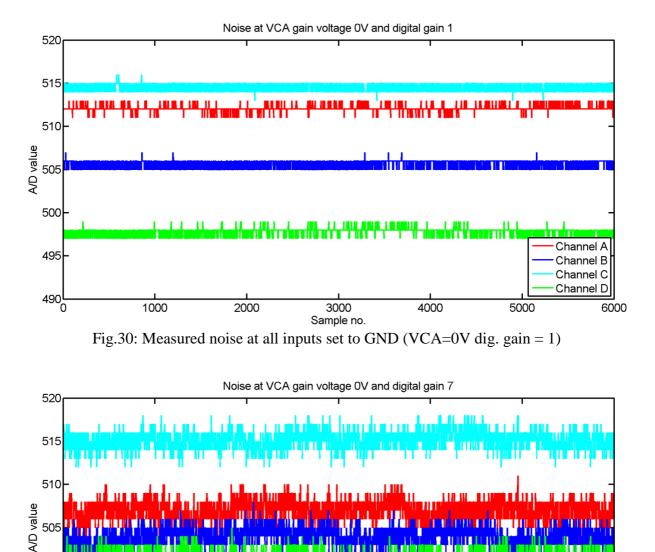

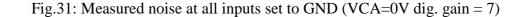

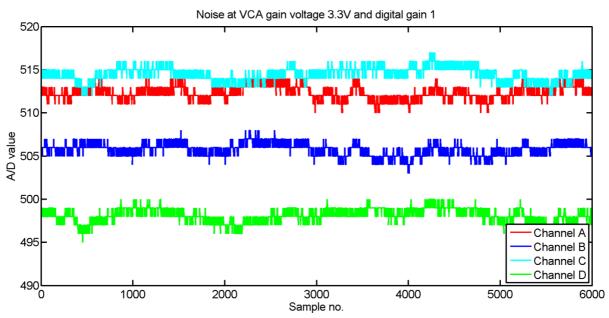

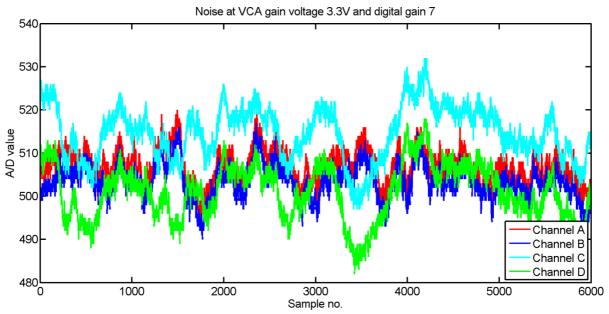

|      | 5.2.                   | .1. ADC Noise                                        |    |

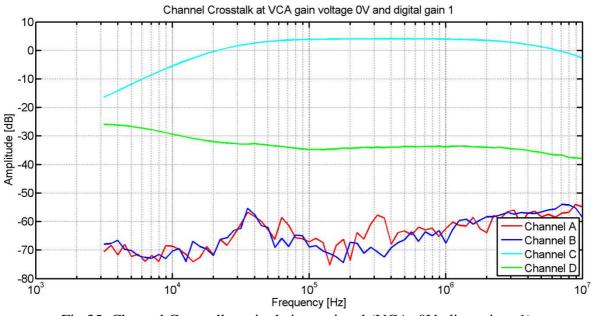

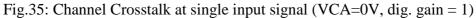

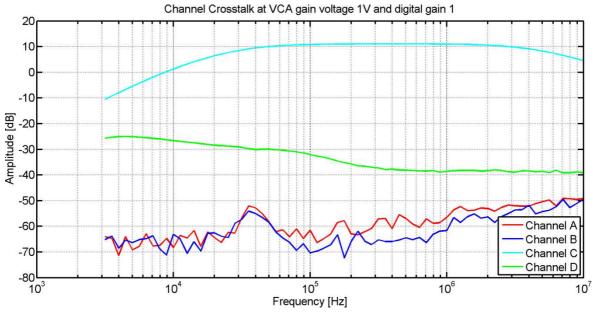

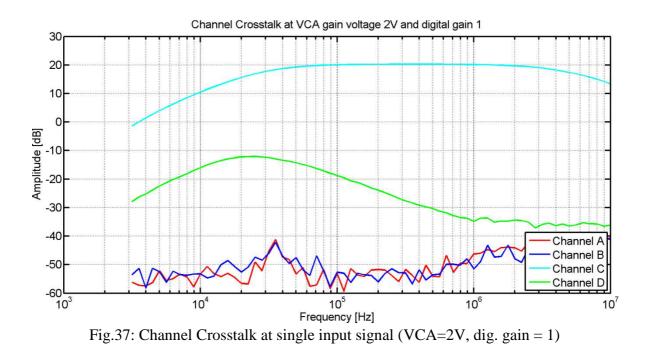

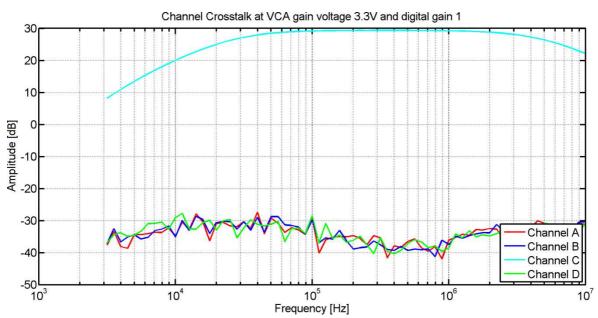

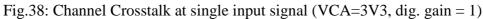

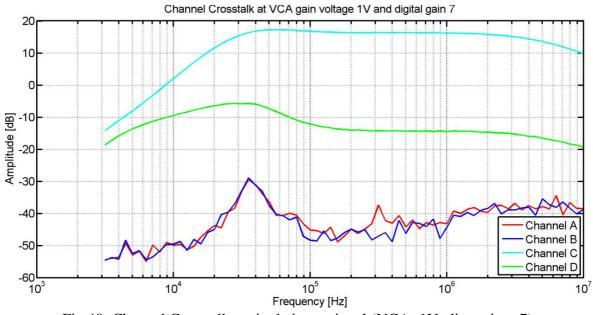

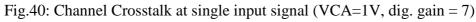

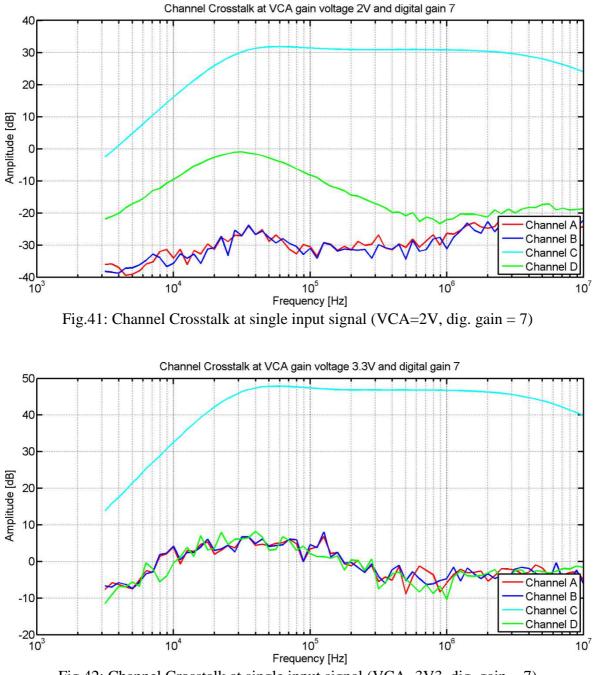

|      | 5.2.2                  | .2. Input Channel Crosstalk                          | 55 |

|      | 5.2.3                  | .3. DAC Measurements                                 |    |

| 5    | .3.                    | Measurements of power supply                         | 61 |

|      | 5.3.                   | .1. Current consumption at different operating modes | 61 |

| 5    | .4.                    | Data Transfer times                                  |    |

| 5    | .5.                    | Discussion of measurements                           |    |

| 6.   | Outl                   | tlook & Conclusion                                   | 64 |

| List | t of fi                | igures                                               |    |

| List | t of li                | iterature                                            |    |

| Ap   | pendi                  | ix A                                                 |    |

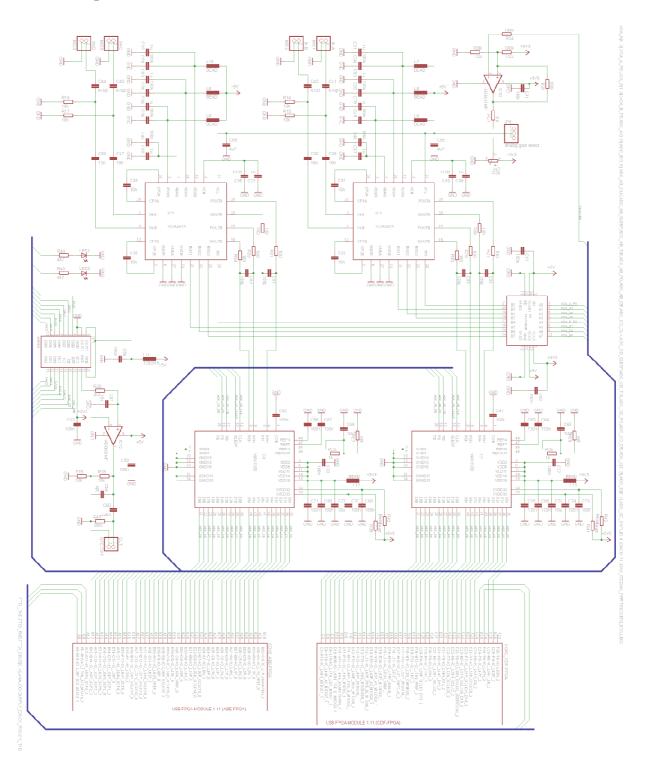

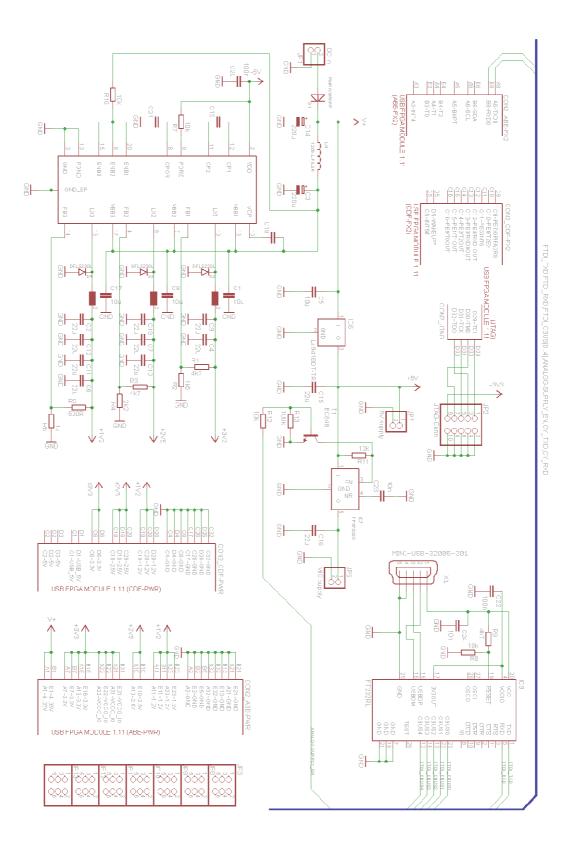

|      | Sche                   | nematic part I                                       |    |

|      | Sche                   | nematic part II                                      | 71 |

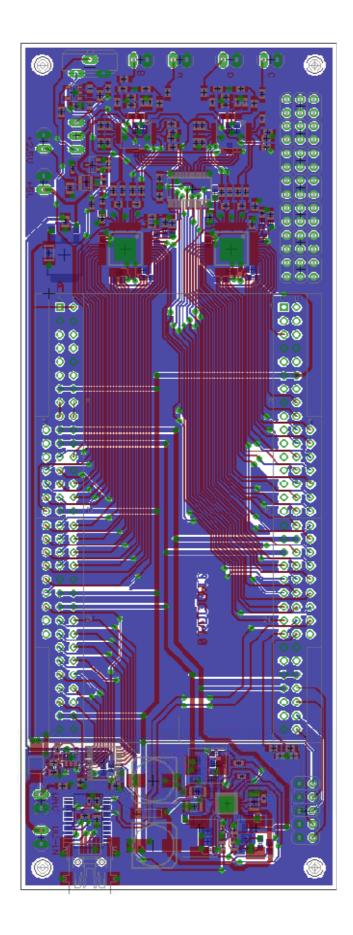

|      | Layout72               |                                                      |    |

|      | Picture of Prototype73 |                                                      |    |

|      | Pin                    | list of ZTEX evaluation board and FPGA               | 74 |

# Abbreviations

| ADC   | Analog to Digital Converter                                      |

|-------|------------------------------------------------------------------|

| ASIC  | Application Specific Integrated Circuit                          |

| A/D   | Analog / Digital                                                 |

| BGA   | Ball Grid Array                                                  |

| DAC   | Digital to Analog Converter                                      |

| DAQ   | Data Acquisition                                                 |

| DDR   | Double-Data-Rate                                                 |

| DMA   | Direct Memory Access                                             |

| DSP   | Digital Signal Processor                                         |

| D/A   | Digital / Analog                                                 |

| EMCE  | Institute of Electrodynamics, Microwave and Circuit Engineering  |

| ESL   | Equivalent Series Inductivity                                    |

| ESR   | Equivalent Series Resistance                                     |

| FPGA  | Field Programmable Gate Array                                    |

| FTDI  | Future Technology Devices International Ltd.                     |

| GPIO  | General Purpose Input/Output                                     |

| IEEE  | Institute of Electrical and Electronics Engineers                |

| IP    | Intellectual Property                                            |

| ISE   | Integrated Software Environment                                  |

| MPMC  | Multi Port Memory Controller                                     |

| MSG   | Message                                                          |

| MSPS  | Mega-Samples per Second                                          |

| NPI   | Native Port Interface                                            |

| PCB   | Printed Circuit Board                                            |

| PHY   | Physical Layer                                                   |

| PLB   | Processor Local Bus                                              |

| RAM   | Random Access Memory                                             |

| RISC  | Reduced Instruction Set Computing                                |

| SD    | Synchronous Dynamic                                              |

| SDRAM | Synchronous Dynamic Random Access Memory                         |

| THD   | Total Harmonic Distortion                                        |

| THT   | Through Hole Technology                                          |

| ToF   | Time of Flight                                                   |

| UART  | Universal Asynchronous Receiver Transmitter                      |

| USB   | Universal Serial Bus                                             |

| VGA   | Variable Gain Amplifier                                          |

| VHDL  | Very High Speed Integrated Circuit Hardware Description Language |

| VCA   | Voltage Controlled Amplifier                                     |

|       |                                                                  |

# 1. Introduction

Sound waves, which are above the human audibly range, are called ultrasonic waves. The wide range of applications, simplicity, robustness and competitive component pricing of ultrasonic systems often make them the first choice for a lot of applications.

The workgroup "Measurement and Control" at the Institute of Electrodynamics, Microwave and Circuit Engineering, focuses on the application and development of ultrasonic sensors for measurement and control.

Goal of this thesis is to develop "A FPGA based DAQ system for mobile robot use". It has to be especially tailored for this purpose to allow synchronously triggered sending and receiving of analog signals. This is required for time-of-flight (ToF) measurements. The system has to provide four analog inputs and one analog output with a minimum resolution of 10Bit@10MSPS at each channel. Small size, low power consumption and a USB interface are also required for this application.

A detailed research on existing systems providing the required functionality at an affordable price was the starting point of the development. It turned out that no existing hardware was available to fulfill these requirements. The FPGA evaluation boards for >10MSPS including multiple converters are located in the high performance end of the product spectrum and tend to cost more than one thousand Euros. Furthermore they are usually equipped with high end FPGAs, which are not supported by any free evaluation tools (e.g. Virtex family from XILINX is not supported by ISE-WebPACK[1]).

The following section gives a brief introduction into time discrete systems and sampling theory and may be skipped by the profound reader.

#### **1.1.** Theory about time discrete systems

When analog signals need to be processed they are most of the time first converted into a digital signal. The sampling of an analog signal is typically performed at equidistant time spaces  $\Delta T$ . The sampling frequency fs is the reciprocal value of the sampling time  $\Delta T$ . The amplitude resolution is defined by n, the number of bits available for the digitalization, as well as the full scale range  $A = 2^n n$ . After digitalization the analog value U of the signal is represented by the closest available digital value V.

$$U\to V=m*\frac{A}{n},\,m\leq n$$

The difference between the analog signal value and the corresponding digital signal value is the quantization error. To keep this error low, the resolution should be as high as possible. Contrary to this requirement, high resolution requires complex analog to digital converters which are more expensive.

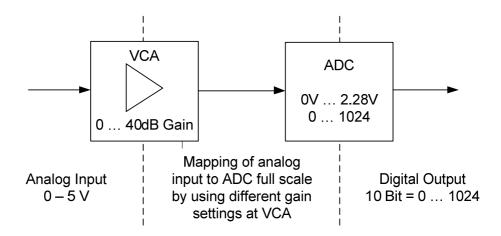

An important aspect to keep quantization error as low as possible is to adjust the input signal to match the full scale input voltage of the ADC. This pre-processing step ensures the maximum achievable dynamic range at the output of the ADC (see Fig.1 for an example).

Fig.1: Example of a voltage controlled amplifier to use full scale at small input signals

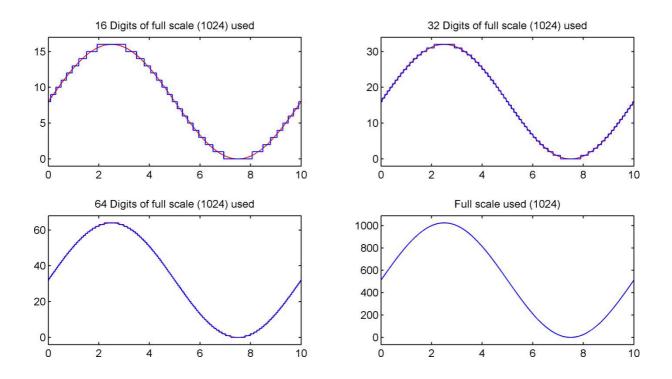

An example of the quantization can be seen in

Fig.2. If small input signals are forwarded to the ADC without amplification to match the full scale of the input of the ADC, the quantization error is very high. By amplification of these

small signals before forwarding them to the ADC, the quantization error can be reduced drastically.

Fig.2: Quantization error at different resolutions

Beside the correct amplification of the input signal, filtering is important to fulfill the sampling theorem of Nyquist- Shannon. If the sampling frequency fs does not match the filter cut off frequency fc < 2 \* fs, the sampled signal cannot be reconstructed correctly. In case of signal processing the base band signal contains aliased signal components which can impact further processing steps.

Depending on the type of analog to digital converter the resolution and sampling frequency are limited due to technological limitations. Fast conversion is typically done by parallel converters. These generate the corresponding digital value by comparing the input signal with  $2^n$  internally generated reference values. As there are also  $2^n$  comparators necessary, these converters are used at applications with low amplitude resolution (typical <10Bit). The conversion of the analog input signal is done within one clock cycle and the digital output value is provided directly at the parallel outputs. Therefore these converters are very fast.

Serial analog to digital converters require less than  $2^n$  comparators and usually have lower prices. There are several different architectures possible like the Single-Slope-Converter, the

Sigma-Delta-Converter or the Successive approximation ADC. The serial converters process the analog input signal in several steps to generate the corresponding digital output value. They are typically much slower in conversion compared to the parallel ones.

Analog to digital converters obtain the digital signal by using a "sample and hold process". This means the analog input is sampled at the clock edge and is held for digitalization until the next clock edge arises. Therefore the clock edge directly defines the moment when the analog signal is sampled. Looking at stationary input signals, a variation of the sampling point does not influence the conversion result. At transient signals a variation in the clock signal leads to an error in the digital signal. In this case the sampling at different time point's results in different digital signal values. A clock jitter therefore can lead to unwanted distortions in the digital output signal and needs to be kept as low as possible.

When looking at several ADCs working next to each other (like in the configuration used for this thesis) another error can occur. Unwanted coupling of the input signal from one channel to other channels generates errors at the output of the ADCs. There are several possible ways for the input signal to couple from one channel to others:

- coupling at the common power supply

- ground loops

- capacitive and inductive coupling in the layout and integrated circuits

The crosstalk attenuation is the "isolation" between the inputs of the system. As the coupling effects are frequency dependent and often appear in combination, the crosstalk attenuation needs to be examined at the full frequency range which the circuit was designed for.

## 1.2. Hardware / Software Codesign

The hardware / software codesign is described by [2] as a synonym for the development of the digital part of a complex system in software and hardware. During the concept phase it is necessary to define which parts need to be realized in software and which in hardware.

The "co" of codesign can be interpreted as "together" or as "coordinated". To find the optimal split between software and hardware, several different design approaches have to be taken into consideration. An assessment of each design approach leads to the most practical realization for the system under the given circumstances.

Due to continuous progress in technology of integrated circuits, it is possible to implement more complex tasks into integrated systems and therefore gain performance and lower cost simultaneously. Complex functions can be realized by using a variety of components that differ in their characteristics regarding:

- time to market

- flexibility (capable to handle different applications)

- device cost

- performance

Components which can be used to realize the required functions are:

- RISC processors

- DSPs

- FPGAs

- ASICs

RISC processors do have much higher flexibility compared to DSPs or FPGAs.

Short development time and low device cost at low quantities make it first choice for a lot of applications. They are typically designed for controlling of processes and do have comparatively low data throughput.

When looking at performance and data throughput, an ASIC is the most efficient way to realize a defined function. It is optimized to fulfill the required tasks and has no unnecessary functions which are not used. The device costs are lowest at high volumes. The disadvantages are the necessity for big investments during the development and a long time to market as the silicon is a custom design. Once an ASIC is designed it can only be used to realize the defined functions. A change in the required functionality leads to a redesign of the ASIC.

Performance and flexibility cannot be maximized at the same time and form the trade-off at the realization. Other criteria as time-to-market and power consumption also need to be taken into consideration as they can exclude some type of ICs at some applications.

#### **1.3.** Theory about FPGA & VHDL

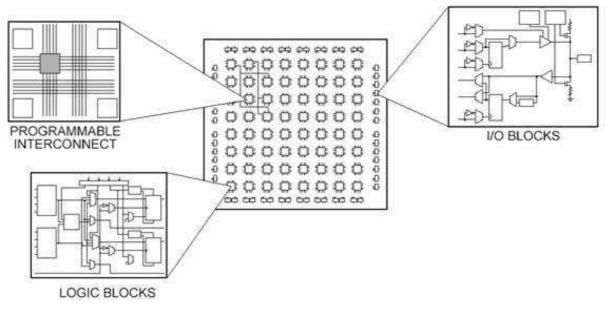

A Field Programmable Gate Array is an integrated circuit consisting of matrix organized logic blocks with horizontal and vertical connection structures in between. It has programmable interconnect points for the required connections between the blocks. At the edges of this matrix so called I/O blocks are placed to connect the logical cells to the periphery (see Fig.3).

Fig.3: Basic setup of an FPGA [3]

Basically any logical function can be generated by combining simple NAND gates. But the number of necessary NAND gates rises drastically with increasing complexity of the logical function. The logical blocks inside an FPGA are much more complex than simple NAND gates. They allow realization of simple and also complex functions with a reasonable number of logical blocks in combination. As the logical blocks can be combined in any order, it is possible to generate several functions completely independently from each other in one single FPGA chip. They are acting like several individual chips inside one package.

Without any program inside, an FPGA does not have any function at all. It just consists of unconnected logical blocks. During programming of the FPGA the interconnect points are set. Furthermore the configuration of the I/O blocks and logical blocks is done to realize the desired function. The huge amount of logical blocks in a state of the art FPGA makes it

possible to realize very complex functions, e.g. a complete microcontroller inside an FPGA. Even several independent microcontrollers can be realized inside one single FPGA.

The I/O blocks are also programmable and beside the configuration as input and output, they can be configured to work with different pull up/down resistors, voltage levels and impedances. The program containing the configuration is a binary file generated by a compiler. Depending on the manufacturer and type of FPGA, there are several different compilers available on the market. Nevertheless there is a manageable amount of programming languages for FPGAs (input for the compiler) which are popular. One of the most common programming languages, which is used for programming FPGAs, beside some other applications, is VHDL.

VHDL is the acronym for Very High Speed Circuit Hardware **D**escription Language. It is a hardware description language which allows describing the behavior of digital systems in text form. VHDL is defined since 1987 in the IEEE 1076 standard [4].

## 2. Concept

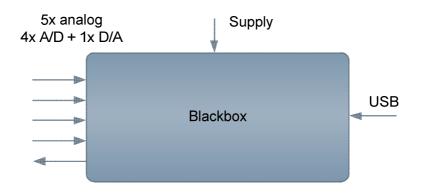

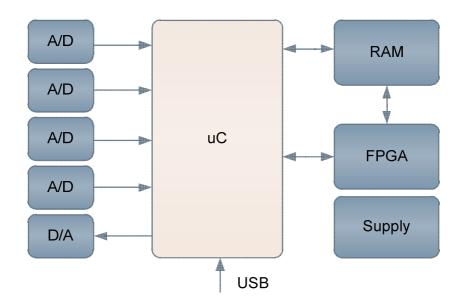

When designing the "FPGA based DAQ system for mobile robot use" with respect to the requirements which were given, a top down design was started with a black box (see Fig.4).

Fig.4: Black box approach with defined interfaces

The first idea was to use a microcontroller in combination with four A/D, one D/A converter, a fast RAM and an FPGA to perform the required signal processing. As the data rates at the required sampling frequency and resolution get very high when recording four channels in parallel (400MBit/s), a realization by using a microcontroller for handling the data seemed to be not feasible. Furthermore the RAM had to be either dual ported or all data had to be forwarded to the FPGA by the microcontroller (see Fig.5).

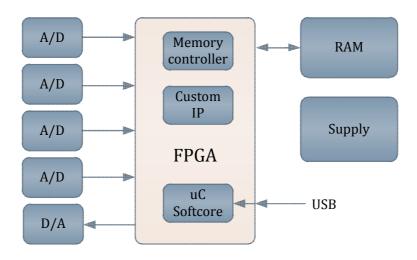

Fig.5: Block diagram of the setup with uC handling all data

Although state of the art microcontrollers provide DMA in combination with external memory, a better approach seemed to be using an integration of the microcontroller into the FPGA – a so called "softcore". In this case the microcontroller can be bypassed for the data transfer during recording and is not occupied with the handling of the data during recording. The data can furthermore directly be pre-processed by any functions implemented in the FPGA before storing it to the memory. At this approach a closer look to the correct Hardware/software codesign was the next logical step.

# 2.1. Hardware/Software Codesign

The hardware/software codesign defines which parts of the necessary function are handled by hardware and which in software. Using an FPGA allows high flexibility regarding the implementation of some logical functions into the FPGA instead of placing them on the PCB as real physical components. As an FPGA was part of the concept from the beginning for data processing, it was obvious to implement further functions inside the FPGA in order to reduce the number of external components. Some of the advantages and disadvantages of using an FPGA for this application can be seen in Tab. 1.

| Advantage        | Disadvantage           | Comment                                         |

|------------------|------------------------|-------------------------------------------------|

| Performance      |                        | Sampling rates >> 10MSPS can be achieved        |

| Flexibility      |                        | "Hardware" can be easily changed by             |

| Технонну         |                        | reprogramming the FPGA                          |

|                  |                        | User defined functions like clock-, memory and  |

| Custom IP        |                        | address generation or complex signal processing |

|                  |                        | can easily be implemented                       |

| Pre-defined IP's |                        | Customizable "softcores" and memory interface   |

| The-defined if 5 |                        | including DDR refresh pre-defined available     |

|                  | High power consumption | High efficient switching power supply           |

|                  | / several different    | necessary to keep total power consumption low   |

|                  | voltages required      | necessary to keep total power consumption fow   |

|                  | Cost                   | Basic FPGA necessary for signal processing.     |

| (Cost)           |                        | But additional cost to increase FPGA size to    |

| (0050)           |                        | implement additional functions, are lower than  |

|                  |                        | external components required for this functions |

|                  | BGA package at         | Use of evaluation boards including minimal      |

|                  | "mid size" FPGA        | functionality and workable pin out required     |

|                  | Complex development    | Reduce project setup to a minimum inside the    |

|                  | tools                  | development tools, to keep effort manageable    |

Tab. 1: Advantages and Disadvantages of an FPGA for this application

The analog input signal pre-processing as well as the A/D converter need to be realized as external components, but when it comes to controlling these external components and processing the input data, many functions can be implemented in form of programmable HW inside the FPGA.

The development tools from Xilinx provide some predefined softcores acting as a customizable complete microcontroller. Implementing such a softcore can avoid an additional external microcontroller and gives very high flexibility, as the HW of this microcontroller inside the FPGA can easily be tailored to the required function. Although a microcontroller would not be necessary for this application, as the complete functions could be implemented in VHDL as well, it is much more convenient to use one programmed in C (compilers are available inside the Xilinx development tools). Other IPs provided by Xilinx can be used for interfacing the external memory (see a block diagram of this setup in Fig.6).

Last but not least a custom generated IP programmed in VHDL can take care of the data processing and handling of the data transfer from the ADC/DAC interface to the memory interface to avoid high loads at the microcontroller.

Fig.6: Block diagram of setup with uC inside FPGA, all data handled by memory controller and custom IP

To optimize the function blocks inside the FPGA a suitable partitioning of these blocks has to be done. This partitioning will be discussed in the next chapter.

# 2.2. Partitioning

At the design of complex digital circuits the process of clustering objects into groups in a way that the object given function is optimized with respect to a set of design constraints is called partitioning.

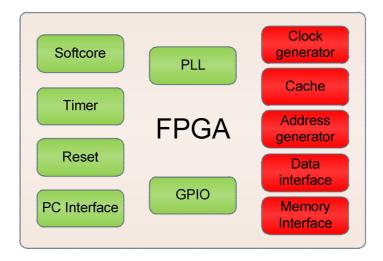

During concept phase the functions which had to be handled inside the FPGA to reduce external components and increase performance and flexibility, were defined. A list of these functions can be seen in Tab. 2(Functions implemented as custom IP are marked in green).

| Function            | Description                                                       |

|---------------------|-------------------------------------------------------------------|

| Memory interface    | Physical interface to the installed memory                        |

| PC Interface        | Interface to the external USB driver chip                         |

| PLL                 | Reference clock generation (single external crystal clock source) |

| Clock generator for | Generation of user selectable clock rates for external A/D and    |

| A/D & D/A           | D/A converters (low jitter required for precise data acquisition) |

| conversion          |                                                                   |

| Softcore            | Microcontroller to control the data acquisition and communicate   |

|                     | with the PC                                                       |

| Timer               | Peripheral device for the softcore for time dependent tasks       |

| Reset               | Ensure correct startup of IPs inside the FPGA                     |

| Cache               | Buffer of data from and to the DDR memory (buffer refresh         |

|                     | cycles of DDR)                                                    |

| Address generator   | Required for complete decoupling of softcore from memory          |

|                     | during fast data acquisition                                      |

| Data interface      | Mapping of 40 bit input data to the 16 bit memory interface       |

|                     | (possibility for data pre- processing)                            |

| GPIO                | Providing digital inputs and outputs (e.g. to configure external  |

|                     | assembled integrated circuits)                                    |

Tab. 2: List of functions implemented in the FPGA

Fig.7 shows a block diagram of the function blocks inside the FPGA. The blocks marked in red are responsible for handling the data during conversion. These blocks need to be fast and capable of processing high data rates. Except the memory interface, all red blocks are realized as one custom IP having one dedicated data and address bus for handling high data rates independently from the other blocks.

Fig.7: Block diagram of functions implemented in the FPGA. Blocks marked in red are involved during high speed data recording.

# 2.3. Hardware Concept

The HW can basically be split into six main sub elements:

- FPGA

- Power Supply

- PC Interface

- ADC

- Analog interface and VGA

- DAC

For each of these elements an investigation based on the requirements was made to evaluate the components that suit best for a universal design concept including an ultrasonic signal processing application.

#### 2.3.1. FPGA

To develop a complete hardware including a layout for an FPGA and RAM is a very time consuming task as most of the FPGAs are available only in a BGA package. This makes the layout very complex and fast prototyping almost impossible. Not only the package is critical to handle, but also certain layout rules to keep the required track impedances and lengths required by state of the art DDR memories need to be followed with great caution. To shorten this process it was decided to use an "off the shelf" FPGA evaluation board to avoid the complex layout and assembly of the FPGA and memory chip.

| Criteria                             | Reason                                            |

|--------------------------------------|---------------------------------------------------|

| small size                           | Suitable for mobile application                   |

| Interfacing connectors on main board | Benefit of easy manufacturing is lost otherwise   |

| manageable for hand soldering        |                                                   |

| min 30MB RAM                         | Capability of recording an ultrasonic signal at 4 |

|                                      | channels with 10Bit@10MSPS for ~ 500ms            |

| Fast RAM interface                   | Storage of unprocessed data at 400MBit/s          |

| Affordable price                     | No need to argue                                  |

As there is a very high variation of these boards available on the market some criteria had to be defined to sort out the suitable boards. A list of these criteria can be found in Tab. 3.

Tab. 3: List of criteria for selection of the FPGA evaluation board

The two market leaders for FPGAs are Xilinx [5] and Altera [6]. One of the advantages from Xilinx is the availability of a big IP catalogue including several different memory controllers. The Spartan 6 family includes also an integrated memory controller block to provide optimal memory performance without allocating a big amount of logical cells for this function. Therefore Xilinx Spartan 6 was preferred at the research of evaluation boards. One of the most promising boards for this purpose seemed to be a board from ZTEX [7]. They are available in several FPGA and RAM sizes. It is also possible to generate a complete stand alone device as some of their boards do have an SD card connector to store the FPGA configuration. An external microcontroller with EEPROM is also onboard to install the boot loader. For the development of the prototype finally the ZTEX board "1.11c" was chosen [8]. The FPGA assembled on this board is a XILINX Spartan 6 XC6SLX25 in combination with a 64MB DDR SD RAM which can handle data rates up to 800MByte/s. More powerful but still pin compatible versions of the board are also available at some higher costs. They are equipped for example with up to 128MB DDR2 RAM and XILINX Spartan 6 XC6SLX150 which has six times more logical cells than the XC6SLX25. During the software development it was confirmed that the XC6SLX25 is big enough to handle all required functions.

#### 2.3.2. Power supply

Although there is a power supply unit available from ZTEX which matches to the USB-FPGA-Module, it was decided to attach a new design for the switching power supply. The reason for this was the concern about interference of the ZTEX power supply with the front end amplifier. The ultrasonic signals which will be received by the microphones and amplified with the front end are in the range of 50-100 kHz. The ZTEX power supply uses fixed off-time, current-mode-controlled buck switching regulators which may generate distortions in a similar frequency range as there is no fixed switching frequency defined. Furthermore the design consists of three independent regulators which are not synchronized. Therefore the generated ripple of each single converter has an undefined phase shift to the others and can therefore generate unpredictable frequency components.

Another reason is the power supply of the components which are not placed on the ZTEX board need to be provided as well (e.g. A/D and D/A converters). To reduce possible distortions and the required layout space, a triple output step-down switching regulator with 550 kHz fixed switching frequency from Allegro was chosen (A4490).

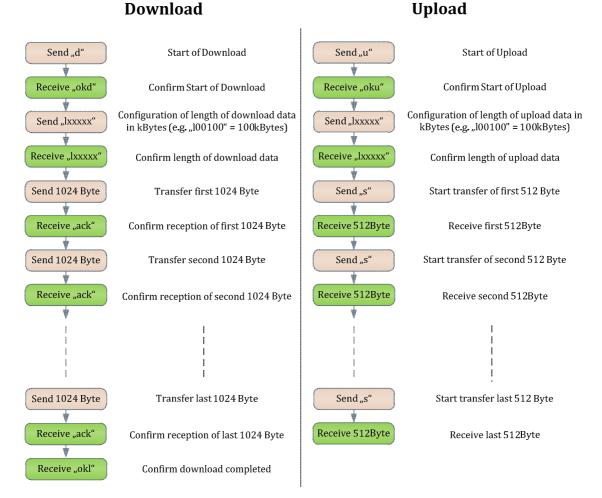

#### 2.3.3. PC Interface

The interface to a PC is required to enable down- and upload of data to and from the memory, and to send commands from and to the electronic.

The control interface does not need to be fast as only simple commands are sent from the PC to the electronic and back. When looking at the down and upload of data, speed does matter as the required amount of data is in a range of several megabytes (the chosen FPGA board from ZTEX does have 64MB RAM which can be increased to higher values at different board versions).Therefore a dedicated USB 1.0 interface was added to the design by using an FT232RL from FTDI (see [9]). It is used as standard serial interface with a data rate of 921,6kBit/s. It can easily be controlled at the PC (virtual com port) and also at the FPGA (standard UART at the softcore).

For higher data transfer rates, the onboard USB 2.0 interface of the ZTEX board can be used (up to 480MBit/s). To do so there is no change in the hardware necessary, but some modifications in the software on the PC (USB 2.0 driver) and in the FPGA binaries.

#### 2.3.4. Analog to Digital Converter

Due to the high number of IO's of the FPGA board, the interface of the A/D and D/A converter can be a parallel interface. This increases the number of tracks but nevertheless reduces layout complexity. Most of the FPGA (also Spartan 6 which is used here) do have high speed serial interfaces onboard which can handle data rates up to several GBit/s. Nevertheless when it comes to designing a layout for these interfaces, the design gets very tricky due to the impedance requirements of these tracks. A parallel interface reduces the clock frequencies dramatically and simplifies the layout as no specific impedances are necessary for the data lines. The clock line still needs to be routed carefully to avoid reflections which can lead to multiple clock triggers at low rise times.

The chosen analog to digital converter for this application is a MAX1183. It is designed for high-resolution imaging, multichannel IF sampling and also ultrasound application. The resolution provided is 10Bit at a conversion speed of 40Msps. There are several pincompatible versions available. The speed grade can be increased by simply replacing the chip (up to 120Msps is possible by using MAX1190).

Further advantages for this device are: low power consumption, 59.6dB SNR at  $f_{IN} = 20$ MHz, a compact design (two converters in one 48-pin TQFP package) and 0.02dB Gain and 0.25° Phase matching of the converters at 20MHz. (see also datasheet [10])

#### 2.3.5. Analog interface and Variable Gain Amplifier

To keep the distortions as low as possible the input of the analog to digital converter is differential. All disturbances which are picked up at the differential signal lines are attached to both lines equally and therefore do not affect the signal as long as the maximum input level of the next stage is not exceeded. The input signal coming from the connected microphones is single ended and the signal level does not match to the dynamic range of the ADC. Therefore an amplifier is necessary to match the input signal to the converter. As the signal level provided by the microphones may vary depending on the acoustic attenuation of the sent signal, a variable gain amplifier makes it possible to match the received signal level to the full scale input of the ADC. The additional equivalent noise caused by the quantization error of the ADC can therefore be reduced and the total performance of the system during the measurement increased. Furthermore when looking at other applications a higher dynamic range is more feasible.

In this application a variable gain amplifier with integrated input buffer from Burr-Brown (Texas Instruments) was chosen to provide the necessary amplification and input matching (single ended input – differential output).

At the input and output of the amplifier appropriate filters were placed to reduce the influence of low frequency distortion (below 20kHz) as well as anti aliasing effects at the ADC. These hardware filters may need to be adapted when using the system for other applications.

#### 2.3.6. Digital to Analog Converter

The digital to analog converter is necessary to generate an output signal which can be sent in the final application as "ping". As the waveform of this signal shall be "free programmable", a real digital to analog converter which gets its data from the memory seemed to be most suitable. As there are no special requirements to this converter a 10 Bit type with 20Msps and parallel interface was chosen (AD5433 from Analog Devices [10]).

Also in this case the chosen type has the benefit to provide pin-compatible versions with higher bandwidth and data rates. To decouple the output pin from the DAC and provide a low impedance board output with some ESD protection, a simple rail to rail amplifier was added at the output.

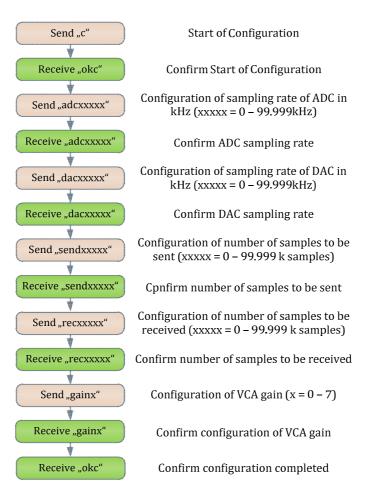

#### 2.4. Software Concept

There are three different types of software necessary to implement the requested functionality (three different programming languages):

- The user interface on the PC shall be provided in MATLAB

- The configuration and communication with the PC is done by using a softcore microprocessor inside the FPGA programmed in C (necessary compilers are provided by the Xilinx development environment)

- The custom IP which handles the data transfer, cache, address mapping and clock generation is "programmed" in **VHDL**

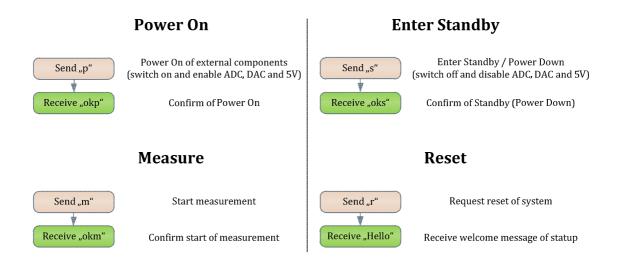

The main functions supported by the interface between MATLAB and the softcore were defined during the concept phase of the development. Every main function can be started by a single command and is proceeding according a defined protocol afterwards. An overview of the commands supported by the softcore can be found in Tab. 4.

| Main function | Description                                                             |  |

|---------------|-------------------------------------------------------------------------|--|

| Power on      | Switch on power supply for preamplifier, external 2.5V and 5V supply,   |  |

|               | enable VCA, enable ADC and DAC                                          |  |

| Standby       | Switch off supplies and disable VCA, ADC and DAC                        |  |

| Config        | Enter configuration mode:                                               |  |

|               | In this mode the softcore expects the configuration information about   |  |

|               | requested sampling rates, number of samples to be transmit and received |  |

|               | and the digital gain settings of the preamplifier                       |  |

| Download      | Start download procedure (transfer data from PC to onboard memory)      |  |

| Upload        | Start upload procedure (transfer data from onboard memory to PC)        |  |

| Measure       | Start measurement (output and input of DAC/ADC data at the configured   |  |

|               | sampling rate and number of samples)                                    |  |

| Reset         | Reset system                                                            |  |

Tab. 4: List of main functions supported by the softcore

The interface between the softcore and the custom IP is more simple but was defined at a later stage in the development because the design of the IP, as well as the memory interface had to be changed several times to achieve the required functionality. Nevertheless the configuration shall be mentioned here as follows:

It was realized with two HW signals as well as ten 32Bit registers. The first HW signal is connected to a GPIO pin on the softcore (configured as output) and also to a physical IO port pin of the FPGA to trigger the measurement. The second HW signal is connected to an interrupt pin at the softcore to provide an interrupt signal as soon as the measurement is finished. Four of the ten 32Bit registers are used to set the start and stop address of the transmit and receive data signals in the memory. The other six registers are used for the configuration of the clock speed for the A/D and D/A converters, as well as diagnosis and feedback during SW development.

#### 3. Details on the Hardware Design

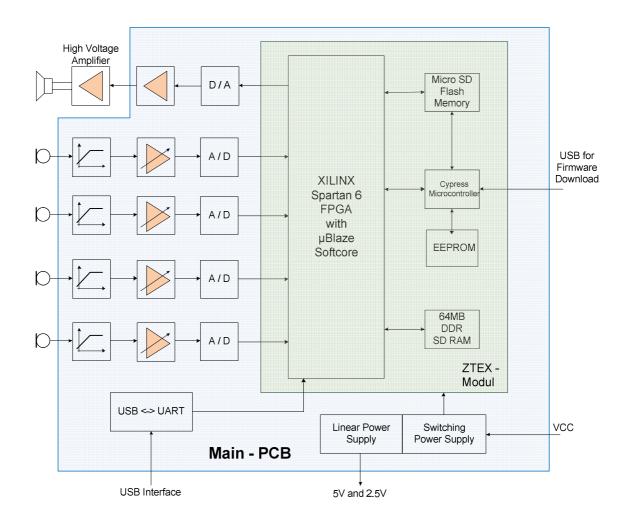

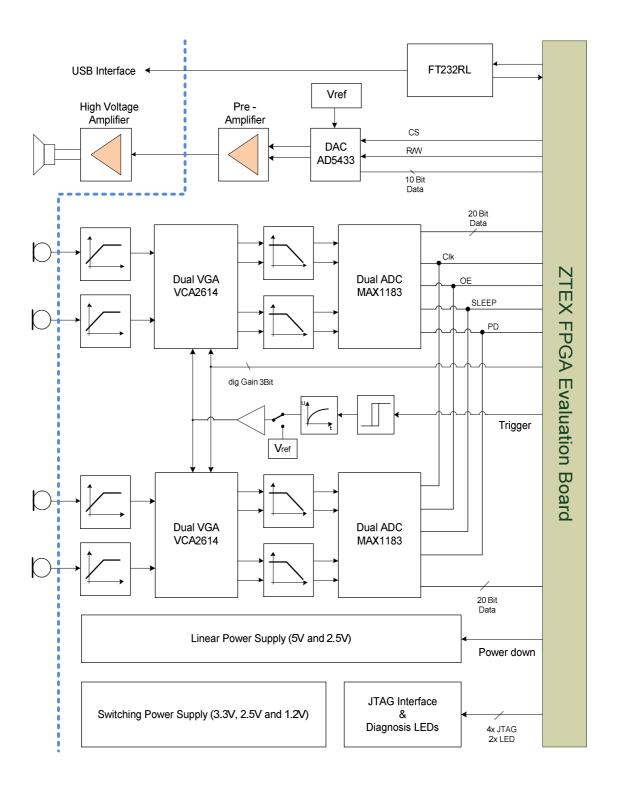

The main PCB has two layers with SMD components placed on both sides. The placement of the integrated circuits and signal paths on one side and only minor tracks and a ground plane on the other side result in a very robust design. The power supply filtering capacitors were placed as close as possible to the integrated circuits on both sides of the PCB. The FPGA evaluation board from ZTEX can be placed piggyback on the main PCB by THT connectors. The sensitive analog signal processing consists of the filter and amplifier for each channel and had to be placed at some distance to the switching power supply to avoid coupling of distortion signals. The digital to analog converter and the USB interface are less distortion sensitive and do not have placing restrictions. Beside the switching power supply, a linear voltage regulator provides 5V and 2.5V to supply the preamplifier and if necessary also the MEMS microphones with a low noise supply voltage. Fig.8 shows a general block diagram of the main PCB with the ZTEX FPGA Module.

Fig.8: Block diagram of hardware (complete setup)

A more detailed block diagram of the functions included on the main PCB can be found in Fig.9. The control lines of the ADC and DAC as well as the data lines are all connected to the FPGA module and are routed inside the FPGA to the softcore.

Beside the interfaces to the converters, amplifiers and USB driver some additional interfaces for trigger, power signal and debug are required. The trigger line is an output signal from the softcore which indicates the start of a measurement. Once an ultrasonic sound signal is transmitted, it is continuously attenuated during propagation. To enable some compensation of this attenuation a simple capacitor charging circuit provides a time dependent voltage (exponential function) which can be used to increase the gain of the voltage controlled amplifier during the measurement. The input voltage for the VCA can also be set to a stationary value which is adjusted by a simple potentiometer on the PCB.

When using the device for ultrasonic applications at the EMCE an external high voltage amplifier has to be used to drive the ultrasonic transmitter.

Fig.9: Detailed block diagram of hardware

#### 3.1. FPGA Board

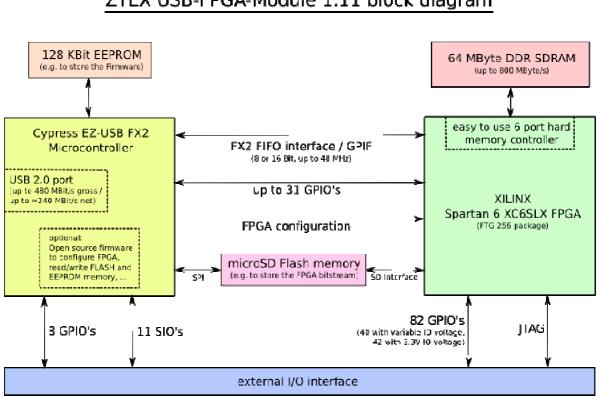

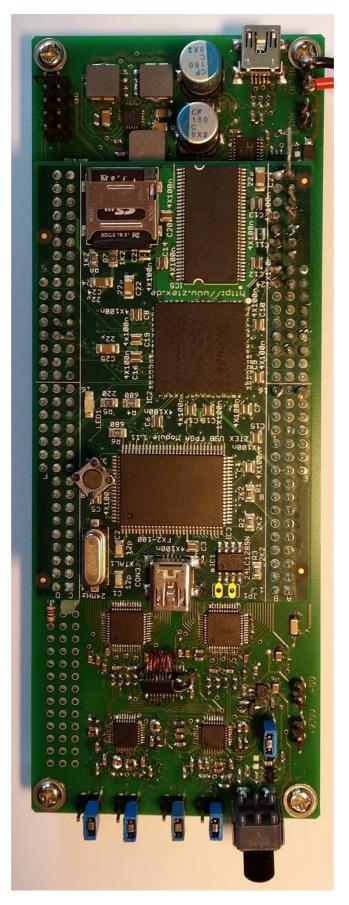

As mentioned in the concept the "ZTEX USB-FPGA-Module 1.11c" [8] was used for the design. See Fig.10 for a block diagram and Fig.11for a picture of the real device. Further details can be found on the ZTEX website [7].

# ZTEX USB-FPGA-Module 1.11 block diagram

Fig.10: ZTEX USB-FPGA-Module 1.11 block diagram [8]

Fig.11: Picture of ZTEX USB-FPGA-Module 1.11c [8]

The FPGA which is assembled on the Xilinx USB-FPGA-Module 1.11c is a Spartan 6 "XC6SLX25" containing 24,051 Logic Cells [11]. Detailed data can be found at [5]. Directly attached to the Spartan 6 is a 64MB DDR SD RAM from Micron which can handle data rates up to 800MByte/s. The Cypress microcontroller, as well as the flash and EEPROM memory are necessary to enable stand alone operation. During power up the microcontroller starts with a boot loader which is stored in the EEPROM. The "bitstream" for the FPGA is then loaded from the micro SD flash card into the FPGA. The FPGA can also be programmed by a JTAG interface which is connected to a JTAG connector on the main PCB. This interface was also used during development as it is very convenient for debugging. It was disabled after finalization of the software (prototype operates in standalone mode). For measurements at mobile robot application the device had to be able to run in a standalone mode, using a single connection to the PC only for controlling the device.

The onboard USB 2.0 interface is used for downloading the boot loader to the EEPROM and the "bitstream" to the micro SD Flash memory. It is also possible to extend the software of the Cypress microcontroller and use this USB 2.0 interface for communication with the FPGA at high speed rates (up to 480MBit/s). As the software effort increases drastically in this case also on the PC to handle the USB high speed interface, this option was not used for the prototype.

#### **3.2.** Power Supply

The power supply of the device contains a linear and a switching power supply. As the board should have low power consumption, most of the supply voltages are provided by the

switching voltage regulator. The linear voltage regulator is only used for supplying the analog frontend as well as the external active microphones (in case of ultrasonic application). As these parts only need to be supplied during a measurement the disadvantage of a very low efficiency at high input voltages can be accepted. The big advantage of a low distortion power supply at these parts of the circuit prevails. The linear regulation is done in a first step to 5.0V by using a L4941BDT low drop voltage regulator (450mV drop voltage @ 1A typ.) followed by a TPS73025 2.5V regulator. The 2.5V voltage is enabled by a control signal from the softcore inside the FPGA. The 5V remains on all time as the analog frontend amplifier supports a power down mode with low current consumption (<2mA per channel). This linear voltage regulator together with the used polarity protection diode defines the minimum and maximum supply voltage of the electronic ( $V_{CCmin} = 6.1V$ ,  $V_{CCmax} = 30V$ ).

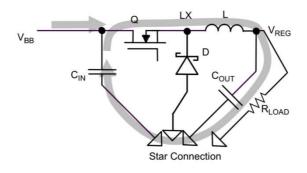

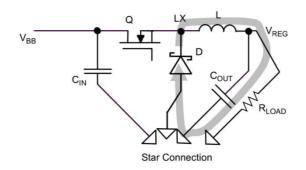

The main current is provided by the switching power supply. It is used to supply all other parts including the FPGA, except the analog pre amplifier. The IC used for this circuit is the A4490 from Allegro (capable to handle input voltages from 4.5V to 35V). The converter topology is a classic buck converter with external passive freewheeling diodes but internal power FETs. Due to its 4x4mm QFN package it is very compact in size. It provides three independent outputs which are clocked by a fixed frequency of 550 kHz at different pulse widths, to individually control the output voltages. The three clock signals are shifted 120° in phase to reduce the current ripple and distortions on the power input. The maximum output current is internally limited to 2.0A per channel.

Appropriate voltage dividers are used to generate the required voltages with respect of the regulator feedback voltage of 0.8V:

$$4k7 \& 1k5: \frac{0.8V*(4700+1500)}{1500} = 3.307V$$

$$4k7 \& 2k2: \frac{0.8V*(4700+2200)}{2200} = 2.509V$$

$$500R \& 1k: \frac{0.8V*(500+1000)}{1000} = 1.2V$$

As switching power supplies always include high current paths, ripple and distortion signals are highly dependent on the used components and the correct layout. To minimize these effects the coils, freewheeling diodes and filter capacitors were selected carefully to match for this application.

Coils: "IHPL-2525" series from Vishay -> high current, shielded setup and lowest DCR/ $\mu$ H in this package.

Freewheeling diodes: "DFLS230L" from Diodes Incorporated -> "Schottky Barrier" type with high current capability and low forward voltage drop.

Filter capacitors: "GRM Series" from Murata -> Low ESR and ESL

The layout recommendations in the datasheet of the A4490 were tried to be considered to minimize the current flow path during on and off phase of the internal FET [12].

Fig.12: Current flow path at FET on [12]

Fig.13: Current flow path at FET off [12]

It was possible to reduce the size of the complete switching power supply layout below 25x20mm by using both side assembly (see Fig.14 for a picture of the switching power supply layout area in ~ 1:1 scale).

Fig.14: Layout of switching power supply

#### **3.3.** PC Interface

The PC interface was kept as simple as possible as there is an existing high speed USB interface available on the FPGA evaluation board from ZTEX. A simple UART to USB chip from FTDI [9] seemed to be the most convenient solution to enable a simple interface to the PC and the electronic. The used FT232RL allows data rates up to 1MBit/s on the UART interface of the electronic (available as part of the softcore), and a virtual com port on the PC side (drivers for Windows provided by FTDI).

#### **3.4.** Digital to Analog Converter

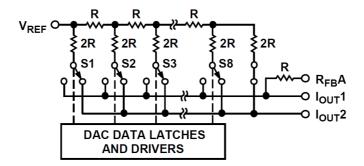

The DAC used in the setup (AD5433) is a typical R-2R digital to analog converter with a parallel interface and a resulting current output. In Fig.15 [10] the setup of the R-2R network inside the DAC can be seen.

Fig.15: R-2R network inside the digital to analog converter [10]

The output of the DAC in the standard configuration is a current signal. To get a corresponding voltage signal, a voltage switching mode has to be used. By using this configuration a positive reference voltage results in a positive output voltage. Therefore a single supply operation is possible. The output voltage of this configuration is directly dependent on the connected impedance. To avoid this dependency and to provide an independent low impedance output, an additional buffer is necessary. This buffer can also be used to amplify the output signal. As the input is directly connected with the resistor network, the impedance of the input is dependent on the code seen by the R-2R network. Therefore the input has to be driven by a low impedance source to provide correct corresponding output voltages at different codes. At the prototype the input is driven directly by the supply voltage (+5V) buffered by a low impedance L/C filter.

A rail-to-rail, single supply, wideband operational amplifier (AD8601) is used to buffer the output of the DAC and amplify by a factor two. The maximum dynamic range of the output

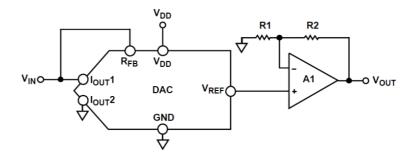

in this DAC configuration is only  $0...V_{IN}/2$  if no amplification is used. In Fig.16 the connection of the impedance buffer as mentioned in the datasheet [10] can be seen (At the prototype  $V_{IN}$  is connected to +5V, R1 and R2 are 10k Ohm each).

Fig.16: Connection of DAC to impedance buffer [10]

The digital 10 Bit interface of the AD5433 does also provide a read-back function which can be helpful in some applications, but was not used in the SW as the data interface is directly connected to the softcore. To increase resolution a pin compatible version with a 12 Bit interface can be assembled as well (AD5445, see also [10]). The schematic, layout and SW were prepared to handle the 8, 10 and 12 Bit version (for the prototype the 10 Bit version was assembled).

Beside the parallel data interface there are only two more lines necessary to control the DAC. One CS and one R/W signal. The R/W signal is used to configure read or write mode of the input latch. The CS signal can be seen as a clock line. At a low signal data can be written to the input latch. At rising edge of CS, data is latched and transferred to the DAC register. The DAC latches are not transparent, therefore a write sequence must include a falling and a rising edge to ensure that data is loaded into the DAC registers. The digital value is written into the DAC registers and output directly as analog value by using the R-2R network.

#### **3.5.** Analog to Digital Converter

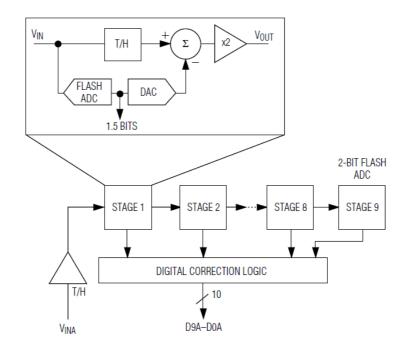

The ADC used in the electronic is a dual 10 Bit analog to digital converter from Maxim (MAX1183). It uses a nine-stage pipelined architecture (see Fig.17) which allows high speed conversion. The input voltage is "stored" by a "track and hold circuit" at the input and processed through the pipeline. As it is shifted to the next stage every half clock cycle the total latency of the conversion is 5 clock cycles. Each stage consists of a one and a half bit flash ADC to convert the input voltage of the stage into a digital code. A digital to analog converter in each stage converts the digital result back into an analog voltage, which is then subtracted from the input signal. Before it is forwarded to the next stage the resulting voltage is multiplied by two to match the next input stage.

Fig.17: Nine-stage pipelined architecture of ADC [13]

The full-scale range is dependent on the configuration of the chip. For the setup of the prototype the "Internal reference mode" (see datasheet [13]) was used, by connecting the REFOUT to the REFIN pin with a 1k $\Omega$  resistor. The resulting full-scale range in this configuration is the difference of (V<sub>DD</sub>/2+V<sub>REFIN</sub>/4) and (V<sub>DD</sub>/2-V<sub>REFIN</sub>/4). As V<sub>DD</sub> is 3,3V and the internal reference of the ADC is 2.048V the full-scale input range is 2,276V. (The full-scale input values here correspond to the peak to peak value of the input signal, not to the RMS value)

Same as for the other components, also for the analog to digital converter, the chosen IC is available in other pin compatible versions, which allow higher performance. The version assembled on the prototype is a MAX1183 (10Bit 40Msps). Other versions like the MAX1182, 1181, 1180 or 1190 allow sampling rates up to120Msps at 10Bit, but do have higher prices.

#### 3.6. Analog input with Voltage Controlled Amplifier

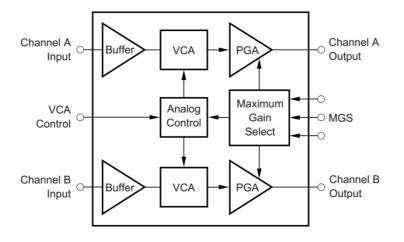

The Voltage Controlled Amplifier used in the circuit is a VCA2614. It has two analog channels including an input buffer, a voltage controlled attenuator and a programmable gain amplifier at each channel (see Fig.18)

Fig.18: Block diagram of dual channel VCA [14]

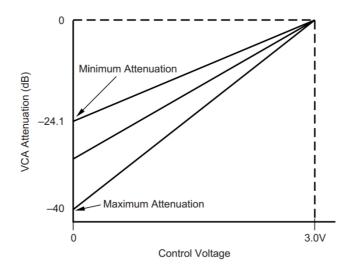

All internal blocks are AC-coupled. The coupling into the PGA stage requires an external capacitor if frequencies below 75kHz should be passed on to the PGA. By assembling a 10nF capacitor the usable bandwidth of the VCA was set from 40kHz to 40MHz (the output PGA rolls off at around 40MHz).The three MSG bits do not only select the gain of the PGA but also select the maximum attenuation of the VCA. The MSG therefore selects the overall gain range, while the VCA control voltage defines the actual gain as an ideal dB-linear transfer function (see Fig.19)

Fig.19: Swept Attenuator Characteristics [14]

For each selected digital gain code the maximum VCA attenuation (selected by  $VCA_{CNTL}=0V$ ) is the inverse of the selected PGA gain. Therefore at an input voltage of 0V the VCA + PGA gain is always 0dB, independent from the digital selected gain.

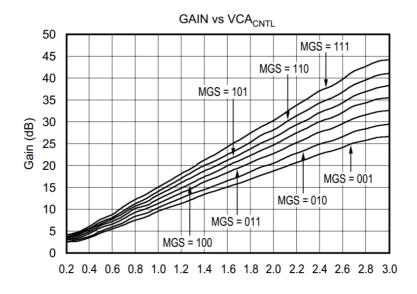

As a result of this the overall gain per channel is selectable by the MGS settings and the analog input voltage. Fig.20 shows some plots of the gain as a function of the input voltage at different MGS codes.

Fig.20: Plot of Gain vs. control voltage at different MSG[14]

At the prototype the gain control voltage can be either selected to be adjusted by a potentiometer, or set to the output of a buffered C charging circuit which is triggered by the start of the measurement. In case of using external microphones this allows to compensate some part of the propagation attenuation of the ultrasonic signal. As the output of the IC provides a differential signal it matches perfectly to the input of the analog to digital converter. A first order low pass filter with a cut off frequency of 21Mhz was used to avoid aliasing effects. The input is single ended and therefore can be directly connected to a single ended signal source (like the ultrasonic microphones).

To avoid unwanted distortion signals, frequencies below 40kHz were cut off by using a high pass filter at the input. In combination with the AC coupling capacitor at the PGA, a band pass characteristic was achieved in total with an attenuation of 40dB/decade at lower frequencies and a cut off frequency of 40kHz. The attenuation at higher frequencies is 20dB/decade with a cut off frequency of 21MHz.

The complete VCA2614 is supplied with 5V. Therefore the digital interface was assumed to expect also 5V digital signals (digital interface levels are not mentioned in the datasheet). To ensure proper functionality a 3V3 to 5V level shifter (74LVX4245) was used to match the logical voltage levels between the FPGA operating at 3V3 and the VCA operating at 5V.

#### 3.7. Programmable VHDL Hardware

The exact configuration of the VHDL hardware defined by the configuration of the IP cores as well as the VHDL source codes were asked not to be disclosed in this thesis. Nevertheless the reader should get a good overview about the system and the approach of resolving the requested problem.

The programmable VHDL hardware (defined by the VHDL code and the ISE project setup) was the most time consuming part of this thesis due to two reasons:

- The Xilinx development tools allow designing highly complex systems, but starting without any training it is a long way to get familiar with all necessary settings and to get a 3<sup>rd</sup> party hardware running in stand-alone mode.

- The high variety of IP cores, which should be chosen wisely at the beginning to achieve the required performance.

The Xilinx development tools contain several programs to setup and maintain a project including simulation, optimization, debugging, programming and versioning (Xilinx ISE v14.3 was used for the development of the software of the prototype). There are a lot of tutorials available in the internet, which allow new users to get a simple VHDL code running within a few clicks (e.g. [15]). The drawback from my point of view is the high number of different possibilities to put a simple VHDL code into practice in the Xilinx ISE, resulting in a huge number of "HowTo's and Tutorials" looking all very different. Another problem is the limitation of some tutorials to implement only some VHDL code on a specific target HW by using dedicated programming tools. The implementation of pre-defined IPs, custom IPs and a softcore running in stand-alone mode without any PC connection was only possible with the help of the online support from the Xilinx and ZTEX team.

As mentioned in chapter 2 "Concept", a very first approach for the setup was to use a physical external microprocessor with a dual ported memory for connecting the RAM to the microcontroller and the FPGA. By changing the concept to an integration of the microcontroller into the FPGA as a softcore, the question arose: How to access the memory? As the FPGA evaluation board from ZTEX was the most promising board to get good performance at reasonable costs, the physical memory chip was defined. The memory controller inside the FPGA was the only variance remaining. Coming from a first idea of a discrete setup with the memory attached directly to the controller and missing the second physical memory interface to the FPGA due to HW constrains, the self-evident concept was to use a memory controller to attach the RAM to the microcontroller, and DMA to transfer the data to the RAM at the desired speed. In this configuration, the data interface to the DAC.

The DMA configuration is well known and used in many applications to transfer high amount of data to and from the memory. This setup was put into practice with reasonable time effort and seemed to be performing well at the first tests. A closer look and tests with higher data rates soon revealed that the data transfer from the IOs of the softcore to the memory by using DMA was not sufficient to achieve the required data rates.

After a lot of investigations on the available memory controllers, a multi port memory controller (mpmc\_v6\_06\_a see [16]) seemed to be the best solution to integrate a multi port configuration in the FPGA. For the correct interfacing a custom IP was necessary to provide the direct connection between the external ADC's and the DAC to the memory controller. It was also obvious that the clock signals cannot be provided by the softcore and have to be derived from the main clock. To get selectable clock frequencies, the custom IP was extended by a clock processing function, to provide programmable clock frequencies. The 24MHz crystal assembled on the ZTEX FPGA board is used as a common clock source for all functions.

## 3.7.1. MicroBlaze Softcore

The softcore which was used for the prototype was a Xilinx MicroBlaze [17]. It is a 32-Bit-RISC processor providing features which can be configured, activated or deactivated before synthesizing [18]. Some of the main features are:

- Floating Point Unit

- Memory Management Unit

- Instruction and Data Cache

- 3 to 5 Stage Pipeline

- Barrel Shifter

- Integer Multiplier

- Integer Divider

- Pattern Comparator

- Hardware Breakpoints

- JTAG control via debug support core

- Interrupt signaling

## 3.7.2. Peripheral IP's

Additionally to the list of functions of the MicroBlaze, several peripherals had to be implemented to get similar functionality like an external microcontroller. These IP's are not directly located inside the MicroBlaze as they are individual IP blocks, but can be seen as part of the microprocessor inside the FPGA. In Tab. 5 those IP blocks are listed including the version number used for the prototype.

| IP Block                      | Version used in the SW    |  |

|-------------------------------|---------------------------|--|

| UART interface                | xps_uartlite_v1_02_a      |  |

| GPIO's                        | xps_gpio_v2_00_a          |  |

| Timer                         | xps_timer_v1_02_a         |  |

| Interrupt service controller  | xps_intc_v2_01_a          |  |

| Reset controller              | proc_sys_reset_v3_00_a    |  |

| BRAM controller               | bram_block_v1_00_a        |  |

| MicroBlaze debug module       | mdm_v2_10_a               |  |

| LMB BRAM Interface controller | lmb_bram_if_cntlr_v3_10_b |  |

| Clock generator               | clock_generator_v4_03_a   |  |

Tab. 5: MicroBlaze peripheral IP blocks

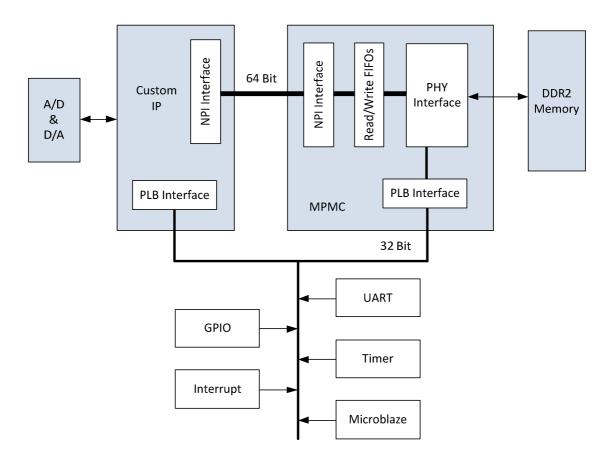

## 3.7.3. Multiport Memory Controller

The MPMC (mpmc\_v6\_06\_a) from Xilinx [19] can be used to access the attached memory with several different interfaces [20]. The configuration of the physical memory interface itself was done according the datasheet t[21] of the DDR2 memory chip that is assembled on the ZTEX FPGA board. Two ports were enabled to access the memory from the softcore and from the custom IP independently from each other. The interface to the softcore is a standard PLBv64 (XILINX Processor Local Bus [22]) interface running at a bus width of 32Bit. This interface is just connected to the PLB bus used in the setup to communicate with the other IPs (no dedicated PLB bus was used). Although it is not the fastest bus available, it is fast enough to transfer the data from the PC to the memory and vice versa, as the bottleneck of the data transfer in this case is the UART. In Fig.21 a block diagram of the used configuration can be seen.

The big advantage of this configuration is the direct read/write access to the memory. The MicroBlaze can easily access the data, by accessing the mapped memory address. The second port was configured as NPI (Native Port Interface) at a bus width of 64Bit (see datasheet [16]). Using this port configuration enables a very low-level direct access to the memory controller core, resulting in very high data rates but requiring also more complex configurations to control the interface.

The clock rates of the PLB and NPI bus were set to 75MHz, but can be increased to higher values if necessary. Due to constrains of the MPMC, the NPI must run at the same or at double frequency of the PLB bus. Therefore at double rate frequency, data rates of close to

10GBit are possible, even without changing the PLB frequency. In this case the DDR2 memory would be the bottleneck of the system.

The PHY memory clock frequency of the prototype was set to 300MHz. When using other boards than the 1.11cfrom ZTEX, also faster memory components are available (DDR3). Those still can be operated at their maximum clock frequency by using the architecture described in this thesis.

Fig.21: FPGA IP bus structure

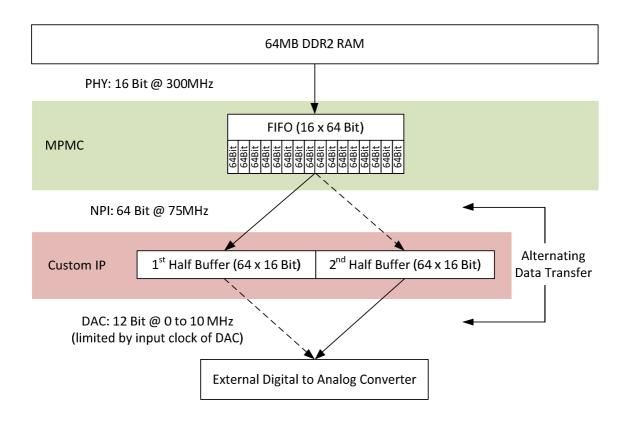

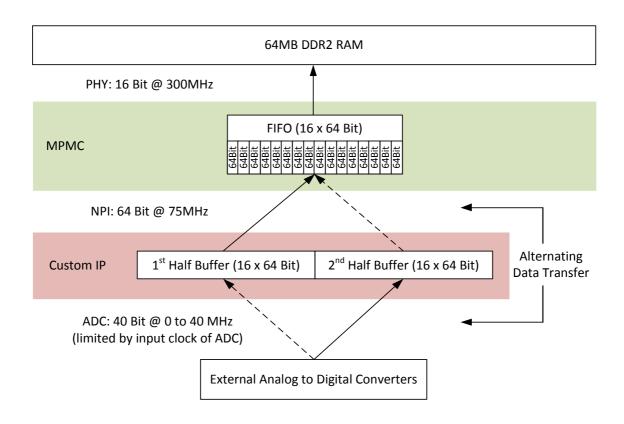

#### 3.7.4. Custom IP

The custom IP is a custom configured hardware part programmed in VHDL. Although it is really "programmed" during each start-up, it is mentioned here in the hardware chapter, as the code is only describing the behavior of the hardware.

The main functions are:

- Provide configurable clock signal for the external ADCs

- Provide configurable clock signal for the external DAC

- Transfer data from RAM to DAC

- Transfer data from ADCs to RAM

The above mentioned functions seem to be simple, but when using the NPI to access the MPMC things become more complex.

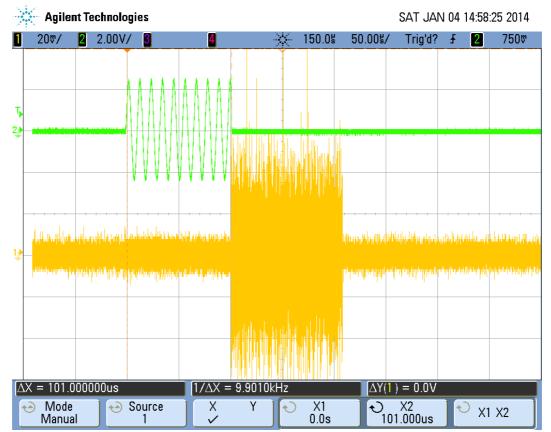

The clock signals for the DAC and ADC have to be generated in a defined sequence. As the ultrasonic application is based on very precise time of flight measurements of echo signals, the timing of the transmitted and received signals has to be very precise. It was a requirement to be able to adjust the length of the transmitted signal as well as the length of the recording of the echo. The recording of the echo received by the microphones and digitized by the ADCs has to start exactly after the last clock cycle of the DAC which generates the transmission signal. The duration of the transmission is defined by the number of samples divided by the sampling rate (same for the duration of the recording). The configuration of the duration of the clock signals and the clock frequencies have to be provided by the softcore (interface see chapter 4.2). The generation of the correct output clock was realized by a counter, counting the edges of the clock signal provided by the "Clock Generator IP" (see chapter 3.7.2). It is set back to zero every time it reaches a compare value. At each reset to zero the clock output from the IP toggles. The compare value for the counter is configured by the softcore. As the IP only gets a compare value, the input clock speed has to be defined also in the C code of the softcore to allow calculation of the compare values for the desired output clock frequencies. Within the test software this input clock frequency was set to 75MHz.

To signalize the start of a measurement, the trigger signal is used. The trigger signal is an output GPIO of the softcore. It is set by the softcore once the measurement command is received from the MATLAB interface. At a rising edge on the trigger line the custom IP starts to load the internal data buffers. Once the buffers are ready loaded, it starts to count the input clock and provides the required DAC output clock. In parallel the data is loaded on the parallel interface on every clock edge. The number of clock cycles at the output is again counted and monitored. When reaching a certain value (compare value provided by the softcore) the clock output of the DAC is stopped. At the last rising edge of the DAC clock output, the output for the ADC clock is started using the same principle. This time the data is read at every falling clock edge and stored to the internal buffers. Once the defied number of samples for the ADC is reached the IP signalizes the softcore the successful data transfer (see chapter 4.2).

To ensure correct routing of the clock signals inside the FPGA all clock signals were declared explicitly as "clock signals". A clock forward technique (ODDR2 buffer) was used to forward the clock signals from the clock generator to the custom IP and also to the external components (see [23]).

The DDR2 RAM stores the information in form of small charges which can be charged or discharged, representing 1 or 0. As these charges are volatile, the complete RAM needs to be refreshed continuously even if there is no modification to preserve the information stored. This refreshing is done automatically by the MPMC. The necessary information for correct refreshing timing is provided by the datasheet of the DDR2 RAM IC [21] and was set at the configuration of the MPMC IP. During refreshing of the RAM cells there is no reading or writing possible to the data inside the RAM cells. The MPMC is equipped with a read/write FIFO which can be used to cache some data in this case. To realize a continuous data transfer between the RAM and the external converters, some additional buffers were required beside the internal FIFO. The MPMC IP provides several data transfer sizes when using the 64 Bit NPI interface. Furthermore it is possible to choose between a "burst" or "cacheline" transfer.

For a write process at "cacheline" as well as "burst mode", first the FIFO needs to be filled with data (see datasheet [16]). Once the FIFO is full, the MPMC starts to store the data to the RAM. The finalization of the transfer from the FIFO to the RAM is signalized by a certain signal on the NPI interface. As the refresh cycles of the RAM are independent of this write process, the time until the FIFO can be accessed again can vary. Although the RAM interface is clocked with 300MHz the required time until the FIFO can be accessed again can take some time (several cycles). Therefore a continuous data transfer to the RAM area, it takes some time until the NPI interface signalizes that the FIFO is fully loaded and ready for read out, as there can be refresh cycles occurring during load of the FIFO. Again a continuous transfer of data cannot be guaranteed. Beside this, the latency time is signalized at some extra lines and needs to be awaited as well, before accessing data in the FIFO.

For the custom IP the "32-Word, Burst Read/Write" transfer mode was used. It should be mentioned that Xilinx defines a "word" as 32 Bit. Therefore a "32-Word, Burst Read/Write" transfers from or to the FIFO on the 64 Bit bus requires 16 clock cycles.

To ensure continuous data transfer, additional buffer stages had to be implemented. The reload strategy was kept very simple and is described on the next pages:

Once a positive edge is seen at the trigger line, and no data transfer is processed (positive edge on the trigger line would be ignored in this case), the start of a measurement is indicated. First data from the RAM needs to be forwarded to the external DAC (cached by the FIFO and the internal buffers). To load the data from the RAM to the FIFO, the correct address

needs to be provided to the MPMC on the NPI interface. The exact handling of the interface can be found in the MPMC datasheet from Xilinx (see [16]). The initial starting address is provided by the softcore. At the end of every RAM read procedure the read address is increased by the FIFO size, to access the correct data at the next read process.

After the read from the DDR2 RAM the data is forwarded from the FIFO into the buffer which has double size of the FIFO (256 Byte). This copy process takes place at the NPI clock rate of 75MHz with 64Bits transferred per clock cycle (64 Bit bus width of NPI). The read out of the buffer is done at the desired DAC clock speed and it is therefore independent from the writing process of the buffer. After the trigger signal indicates the start, first the complete buffer is filled with data. Once the buffer is full, the DAC clock cycle is started and the data is output to the DAC. When the first half of the buffer is completely forwarded to the DAC, it is reloaded with the next data from the MPMC FIFO. During this reload process the second half of the buffer is read again from the first half of the buffer and the second half is reloaded with data from the FIFO. This procedure repeats until the required number of data has been put out to the DAC. This is the case when the end address of the read process (address provided by the softcore) is reached. As the total reload time of the FIFO is much shorter than the read out time of half of the buffer, the data can be continuously transferred to the DAC at the configured DAC clock rate.

The time which is necessary to transfer data from the FIFO to the buffer at the 75MHz 64Bit NPI interface is 213ns + additional access times due to refresh cycles. The time to transfer the same amount of data at a sampling rate of 10MSPS to the DAC, is  $6\mu s$  (one 12 Bit DAC data word is stored as two Byte inside the RAM). Even at high RAM access times due to refresh cycles and worse case latency times (max 3 NPI clock cycles) the buffer is filled much faster than read out again. See Fig.22 for an overview of the data transfer.

Fig.22: Buffer concept at output of data from RAM to DAC

After the last edge of the DAC clock cycle the output of the ADC clock is started. The principle of buffering is the same as used for the DAC, except the data widths and clock rates from the buffer to the ADC. See Fig.23 for an overview.

As the transfer of data from the FIFO to the buffer during RAM read is only triggered by the position of the pointer reading out the data from the buffer, the clock signals for the NPI can be completely independent to the DAC clock. The only restriction is the maximum clock frequency to ensure the reload process is finished before the dedicated buffer is accessed again. The same applies for the analog to digital converter.

As there were three clock lines implemented in the custom IP (one for each ADC and one for the DAC) even an external clock can be used to clock the data output. Minor modifications would be necessary in the VHDL code to change one of the two ADC clock outputs to an input and provide the clock for both external ADCs by one single output pin.

Fig.23: Buffer concept at input of data

In the following section I will take a closer look at the maximum clock rates: The clock rates used in this setting, their interrelation and possible maximum configurations are critical for successful data transfer. Therefore the individual limitations observed within the prototype shall be outlined here in detail.