http://www.ub.tuwien.ac.at/eng

FAKULTÄT FÜR !NFORMATIK Faculty of Informatics

# Self-Stabilizing Byzantine Fault-Tolerant Clock Distribution in Grids

## DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

## **Technische Informatik**

eingereicht von

## **Martin Perner**

Matrikelnummer 0725782

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Univ.-Prof. Dr. Ulrich Schmid

Wien, 28.08.2013

(Unterschrift Verfasser)

(Unterschrift Betreuung)

# Self-Stabilizing Byzantine **Fault-Tolerant Clock Distribution** in Grids

## MASTER'S THESIS

submitted in partial fulfillment of the requirements for the degree of

## **Master of Science**

in

## **Computer Engineering**

by

## **Martin Perner**

Registration Number 0725782

to the Faculty of Informatics at the Vienna University of Technology

Advisor: Univ.-Prof. Dr. Ulrich Schmid

Vienna, 28.08.2013

(Signature of Author)

(Signature of Advisor)

# Erklärung zur Verfassung der Arbeit

Martin Perner Oldtimerweg 1, 2353 Guntramsdorf

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit - einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

# Acknowledgements

I would like to thank my family and friends for their support over the years that made the thesis possible. Special thanks go to Christoph Lenzen for his guidance with the proofs. Finally, I would like to thank my advisor for his feedback, suggestions and effort put into my thesis.

The work on this Master thesis was supported by the Austrian Science Foundation (FWF) under the project FATAL (P21694).

# Abstract

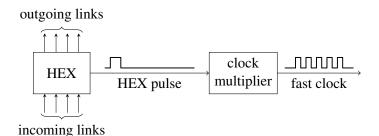

This thesis presents design and analysis of a self-stabilizing Byzantine fault-tolerant clock distribution scheme HEX, which allows to distribute a clock signal in a hexagonal grid topology. Typical application domains are VLSI circuits, multi-core processors and other parallel/networked system architectures that require accurately synchronized clocks at neighbor nodes, e.g., for synchronous communication.

In sharp contrast to clock trees, which are commonly used for this purpose, HEX tolerates both persistent and transient faults of intermediate nodes and wires and supports multiple synchronized clock sources, as, e.g., used in the multi-synchronous GALS (globally asynchronous locally synchronous) approach. To achieve this, every node in the HEX grid is running a very simple distributed algorithm that forwards clock ticks and also provides the synchronized clock signal locally.

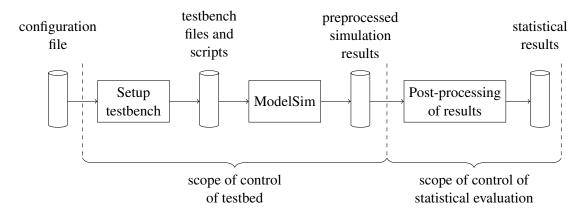

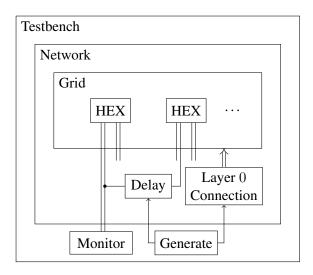

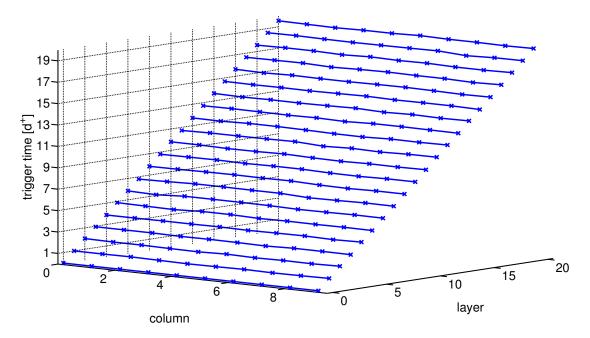

A VHDL implementation of the entire HEX algorithm is presented, which also incorporates a digitally controlled clock multiplier. By means of a comprehensive custom testbed, which also includes fault injection, HEX grids of variable size and with different delay parameters could be instantiated, simulated and post-processed. The entire design has been synthesized with the UMC 90 nm ASIC standard cell library, thereby generating a model that could be simulated using Mentor Graphics'<sup>®</sup> ModelSim.

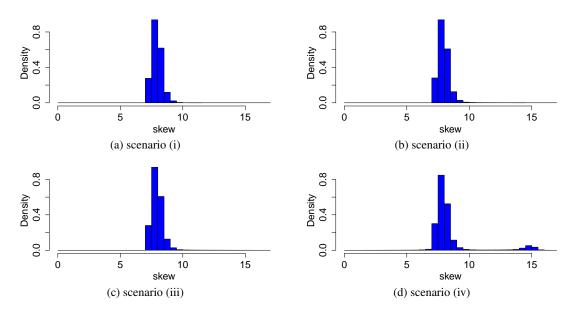

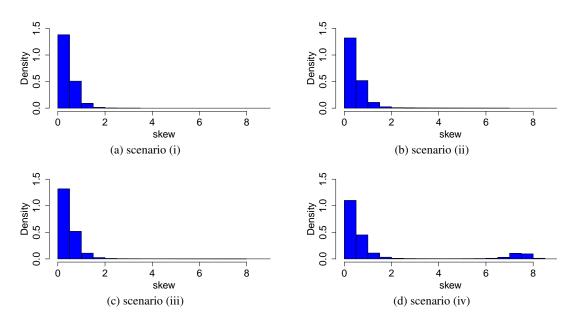

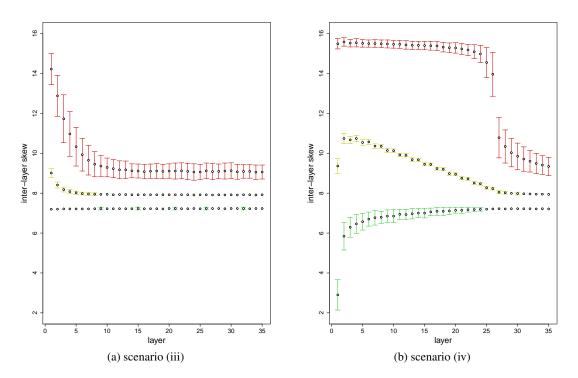

Comprehensive experiments have been conducted to verify and complement the results of the theoretical worst-case analysis of the achievable synchronization accuracy (clock skew) and the stabilization time, which are also documented in this thesis. In particular, a suite of experiments revealed that the quite exotic worst-case scenarios are extremely unlikely to occur in practice, such that the typical average clock skew is much better than the worst-case. Experiments involving faulty nodes allowed us to also shed light on the excellent properties of HEX in the presence of a substantial number of failures, where analytic results are not available.

The results of this work, which has been supported by the Austrian Science Fund (FWF) project FATAL (P21694), have also been published at the 6<sup>th</sup> International Conference on Dependability (DEPEND'13) and the 25<sup>th</sup> ACM Symposium on Parallelism in Algorithms and Architectures (SPAA'13); a comprehensive journal version is currently under review.

# Kurzfassung

Diese Diplomarbeit präsentiert Design und Analyse eines selbststabilisierenden, Byzantinisch fehlertoleranten Verfahrens (HEX) zur Taktverteilung in einer hexagonalen Grid-Topologie. Typische Anwendungsgebiete sind VLSI-Schaltungen, multi-core Prozessoren und andere parallele/netzwerkgekoppelte Systemarchitekturen, die, z.B. zu Kommunikationszwecken, genau synchronisierte Taktsignale in benachbarten Knoten benötigen.

Im Gegensatz zur Taktverteilung mittels einer Baumtopologie, die normalerweise hierfür verwendet wird, toleriert HEX sowohl persistente als auch transiente Fehler von Zwischenknoten und Verbindungsleitungen und unterstützt mehrfache synchronisierte Taktquellen, wie sie etwa in multisynchronen GALS (global asynchronen lokal synchronen) Architekturen verwendet werden. Um das zu bewerkstelligen, läuft auf jedem Knoten im HEX-Grid ein sehr einfacher verteilter Algorithmus, der Takte weiterleitet und auch lokal zur Verfügung stellt.

Zentraler Gegenstand der Arbeit ist eine VHDL-Implementierung des HEX-Algorithmus, die auch einen digital kontrollierten Taktmultiplizierer beinhaltet. Ein speziell entwickeltes Testbed, das auch Mechanismen zur Fehlerinjektion bereitstellt, erlaubt die Instantiierung, Simulation und das Post-Processing von HEX-Grids mit unterschiedlicher Größe und Zeitparametern. Das gesamte Design wurde mittels der UMC 90 nm ASIC-Standardzellen-Bibliothek synthetisiert, um ein für die Simulation mittels Mentor Graphics's<sup>®</sup> ModelSim geeignetes Modell zu generieren.

Umfassende Experimente wurden durchgeführt, um die Resultate der ebenfalls in dieser Arbeit dokumentierten theoretischen Worst-Case-Analyse der Synchronisationsgenauigkeit (Skew) und der Stabilisierungszeit zu verifizieren und, insbesondere, zu ergänzen. Diese bestätigten, dass die ziemlich exotischen Worst-Case Szenarien in der Praxis extrem unwahrscheinlich sind, sodass der typische mittlere Skew viel geringer als der Worst-Case ist. Experimente mit fehlerhaften Knoten, wo analytische Resultate nicht verfügbar sind, zeigten, dass HEX auch mit einer großen Anzahl fehlerhafter Knoten im Grid hervorragende Eigenschaften aufweist.

Die Resultate dieser Arbeit, die vom Österreichischen Fonds zur Förderung der wissenschaftlichen Forschung (FWF) im Rahmen des Projekts FATAL (P21694) unterstützt wurde, konnten auch in den Proceedings der 6<sup>th</sup> International Conference on Dependability (DEPEND'13) und des 25<sup>th</sup> ACM Symposium on Parallelism in Algorithms and Architectures (SPAA'13) publiziert werden; eine umfassende Journal-Version ist mittlerweile in Begutachtung.

# Contents

| 1  | Intro                          | oduction                                      | 1  |  |  |  |

|----|--------------------------------|-----------------------------------------------|----|--|--|--|

|    | 1.1                            | Computational Models in Distributed Computing | 3  |  |  |  |

|    | 1.2                            | Design Methodologies in VLSI                  | 7  |  |  |  |

|    | 1.3                            | The Clock Distribution Problem                | 12 |  |  |  |

|    | 1.4                            | Related Work                                  | 14 |  |  |  |

| 2  | HEX 17                         |                                               |    |  |  |  |

|    | 2.1                            | Topology                                      | 17 |  |  |  |

|    | 2.2                            | Algorithm                                     | 18 |  |  |  |

|    | 2.3                            | Skew Analysis                                 | 19 |  |  |  |

|    | 2.4                            | Fault Models                                  | 29 |  |  |  |

|    | 2.5                            | Pulse Separation                              | 31 |  |  |  |

| 3  | HEX                            | <b>X – Implementation and Results</b>         | 35 |  |  |  |

|    | 3.1                            | VHDL Implementation                           | 35 |  |  |  |

|    | 3.2                            | Simulation Environments                       | 41 |  |  |  |

|    | 3.3                            | Simulation Results                            | 46 |  |  |  |

| 4  | High-Frequency Clock67         |                                               |    |  |  |  |

|    | 4.1                            | Design Challenges                             | 67 |  |  |  |

|    | 4.2                            | Design Requirements                           | 68 |  |  |  |

|    | 4.3                            | Design Selection                              | 68 |  |  |  |

|    | 4.4                            | Implementation                                | 70 |  |  |  |

|    | 4.5                            | Analysis                                      | 71 |  |  |  |

| 5  | Conclusions and Future Work 77 |                                               |    |  |  |  |

|    | 5.1                            | Summary of Accomplishments                    | 77 |  |  |  |

|    | 5.2                            | Critical Reflection and Future Work           | 78 |  |  |  |

|    | 5.3                            | Applications                                  | 80 |  |  |  |

| Bi | bliogr                         | aphy                                          | 81 |  |  |  |

## CHAPTER

# Introduction

Every digital system, except purely asynchronous ones, needs a clock signal at some level to operate correctly. In the extreme case of synchronous circuits, all components (flip-flops) in the circuit are driven by the same perfectly synchronous clock signal. The *globally asynchronous locally synchronous* (GALS) [9] approach opened the door to a new way of circuit design, which allows a variety of different clock domains on the same chip. The clock sources of the clock domains may be completely independent (standard GALS) or keep some synchrony relation with each other (multi-synchronous or mesochronous GALS [47,60,70]).

The GALS approach basically allows different parts of a chip to run independently of each other. Since a complete independence is a rare scenario in real applications, however, some sort of communication between these independent parts is needed. In a standard GALS system, this can only be achieved by means of handshake-based approaches. Unfortunately, besides performance issues and metastability concerns, such solutions easily suffer from deadlocks in the presence of faults. To avoid this, some sort of synchronous communication must be resorted to. The effort to accomplish this depend primarily on the properties of the sender and receiver clocks.

If, as in mesochronous clocking, in particular, those clocks are guaranteed to be at most a bounded number of clock ticks apart, at any time, metastability-free high-speed communication can be designed with little effort using FIFO buffers [55]. Since the ability to communicate correctly, and hence the proper operation of any higher-level application, depends crucially on the bounded synchrony of the clocks, however, critical multi-synchronous GALS systems require a highly fault-tolerant clocking system: Besides non-fault-tolerant distributed clock generation approaches like [32, 36, 42], there are also Byzantine fault-tolerant solutions like DARTS [29] that guarantee bounded synchronized clocks at all correct source nodes, despite of up to f source nodes that can behave arbitrarily faulty. However, as an instance of Byzantine agreement [38], it requires a total number of source nodes  $n \ge 3f + 1$ .

Since transient errors, e.g., due to ionizing particle hits, are the dominant cause of failures in modern *very-large-scale integration* (VLSI) circuits, however, exceeding  $f \leq \frac{n-1}{3}$  faults is not an unlikely event. Unfortunately, classic Byzantine fault-tolerant solutions like DARTS cannot be

guaranteed to resume correct operation after such an event, even when all nodes operate correctly subsequently.

Self-stabilizing algorithms have been invented to cope with this problem [13]: They guarantee that the system will resume, within some finite stabilization time, correct operation even when started from an arbitrarily erroneous initial state. Byzantine fault-tolerant self-stabilizing clock generation methods like FATAL<sup>+</sup> [17, 18] achieve this even in the presence of up to  $f \leq \frac{n-1}{3}$  permanent Byzantine faulty nodes. However, clock generation approaches like FATAL<sup>+</sup> are expensive in terms of required hardware and interconnections between the nodes, and hence do not scale well with the number of clock sources.

A simple way to mitigate this problem is to use a clock generation approach like FATAL<sup>+</sup> only to synchronize a small number of "primary" clock sources, and to distribute their clock signals to the remaining "secondary" clock sources, by means of a suitable clock distribution approach. Obviously, unlike ordinary clock-trees, the latter shall be Byzantine fault-tolerant and also self-stabilizing, but still use a sparsely connected topology.

This thesis presents design and analysis of a self-stabilizing Byzantine fault-tolerant clock distribution scheme HEX, which allows to distribute a clock signal in a hexagonal grid topology. Typical application domains are VLSI circuits, multi-core processors and other parallel/networked system architectures that require accurately synchronized clocks at neighbor nodes. In sharp contrast to clock trees, HEX tolerates both persistent and transient faults of intermediate nodes and wires and supports multiple synchronized clock sources, as, e.g., provided by primary nodes executing the FATAL<sup>+</sup> clock generation algorithm [17].

To achieve this, every non-primary node in the HEX grid is running a very simple distributed algorithm that forwards clock ticks and also provides the synchronized clock signal locally. A VHDL implementation of the entire HEX algorithm will be presented, which also incorporates a digitally controlled clock multiplier. By means of a comprehensive custom testbed, which also includes fault injection, HEX grids of variable size and with different delay parameters will be instantiated, simulated and post-processed. The entire design is synthesized with the UMC 90 nm ASIC standard cell library, thereby generating a model that can be simulated using Mentor Graphics<sup>'®</sup> ModelSim.

Comprehensive experiments will be conducted to verify and complement the results of the theoretical worst-case analysis of the achievable synchronization accuracy (clock skew) and the stabilization time, which are also documented<sup>1</sup> in this thesis. In particular, a suite of experiments will reveal that the quite exotic worst-case scenarios are extremely unlikely to occur in practice, such that the typical average clock skew is much better than the worst-case. Experiments involving faulty nodes will also shed light on the excellent properties of HEX in the presence of a substantial number of failures, where analytic results are not available.

The results of this work, which has been supported by the Austrian Science Fund (FWF) project FATAL (P21694), have also been published at the 6<sup>th</sup> International Conference on Dependability (DEPEND'13) [54] and the 25<sup>th</sup> ACM Symposium on Parallelism in Algorithms and Architectures (SPAA'13) [16]; a comprehensive journal version [15] is currently under review.

<sup>&</sup>lt;sup>1</sup>I acknowledge, though, that the core analytic results have primarily been obtained by my collaborators, in particular, by Christoph Lenzen (MIT).

This thesis is structured into 5 chapters: (The remainder of) Chapter 1 provides a short introduction to the basics of both fault-tolerant distributed computing and digital design. It also contains the definitions of some key terms, and briefly summarizes the (very few) existing related research. Chapter 2 is devoted to the theoretical analysis of HEX in the fault-free case taken from [16]. Chapter 3 describes the VHDL implementation of the HEX algorithm and the testbed used for our simulation evaluation, the results of which are presented subsequently. Chapter 4 is devoted to the design and analysis of the digitally controlled clock multiplier used to implement the synchronized fast clocks. Some conclusions and directions of future work in Chapter 5 round-off the thesis.

#### 1.1 Computational Models in Distributed Computing

In this section, we will provide a short introduction to distributed computing based on the terms and notions used in [3].

Distributed computing is a field that focuses on the interaction between a set of independent *computing devices*, called *processes* or *nodes*, which try to achieve a common goal. This definition is widespread and covers many application domains, ranging from a VLSI chip to a cluster of computers to the Internet. Due to the spatial distribution of such systems, the processes need to communicate with each other, which is usually done via message-passing over dedicated links (on which we will focus here) or via shared memory.

Every process experiences *computation events* and *communication events*, where each such event is atomic and happens in zero time. A computation event causes the process to execute a computing step, which changes the state of the process performing it, based on received messages and the current internal state. Depending on the algorithm executed by the process, such a step can also include the sending of (multiple) messages. A communication event causes the delivery of a message, which was sent by another process, to the process performing the event. An *adversary* selects which process performs an event and thus determines the *execution* performed by the system. Usually, there are many possible executions that differ in the ordering of events, as the only dependency between two applicable events is that a message cannot be received before it is sent, i.e., the communication between two non-faulty processes is always causal.

Since no non-trivial distributed computing problem can be solved if the adversary never performs events on some processes, it is necessary to restrict the power of the adversary by a model of computation. These restrictions (called admissibility conditions) can include, e.g., the type and number of faults in the system, the general properties of the communication between the processes, or the maximal time between two events at the same process. There are many ways to define different models, yet there are two "extreme" models, that delimit the possible spectrum.

#### 1.1.1 Asynchronous Model

This is the weakest and most general model. There are neither constraints on the time between two computation events at the same process nor on the time between the sending and receiving of a message, except that they must be finite and  $\geq 0$ . Note that there are also no constraints on the time between two events on different processes. Since this puts almost no constraints

on the adversary (except that it must not starve a process forever and may not drop messages), many problems cannot be solved within the asynchronous model. For example, since a slow process cannot be distinguished from a crashed one, it is not possible to implement reliable failure detection.

#### 1.1.2 Lock-Step Synchronous Model

This is the simplest model to analyze, albeit it is only applicable if all processes are equipped with synchronized clocks. The executions in this model are partitioned into a sequence of rounds. Every round consists of the sending of messages, the reception of all sent messages, and a computation event on every process. All processes execute their computation event simultaneously, in zero time, and all messages are sent immediately after the respective computation event has been executed. Hence, every round is perfectly aligned at all processes, which makes it easy to solve distributed computing problems. In particular, since every process must participate in every round, it is easy to reliably detect process crashes.

Assuming lock-step rounds is of course unrealistic in real systems, but models can be constructed that allow to simulate lock-step rounds. For this to achieve, the communication delays need to be bounded, the maximal time between consecutive computation event must be known, and every process must have a clock with bounded drift. Then, synchronized local clocks with some specific synchronization accuracy can be implemented, which in turn allow to build rounds that are in lock-step w.r.t. clock time.

#### 1.1.3 Fault Models

As mentioned above, computational models must also define the types and maximum number of faults that can occur in the system. Doing this properly is not only of theoretical importance, but is also very relevant in practice. E.g., modern VLSI circuits are vulnerable to manufacturing defects and effects of radiation due to the miniaturization of the structures [5, 10]. There are certain applications, however, where a crash or a malfunction of the system is not tolerable, e.g., medical devices, power grids or aircraft. Properly designed fault-tolerant solutions, i.e., systems that do not fail despite a certain number of faults, are mandatory here.

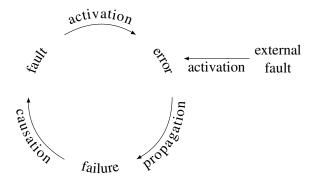

Up to now, we only talked about faults, but never how they affect a process or the system at a conceptual level. Conceptually, there is a distinction between a fault, an error and a failure [4]. They interact in a chain, starting with the initial fault, as depicted in Figure 1.1. The initial fault can be an external fault, or an internal fault originating from a failure of a faulty process. A fault activates an error, which may causes a failure when it propagates. A failure in turn can cause a fault of another process.

Fault models only define the faults the system can experience, as the prevention of the activation of an error is in the scope of the specific algorithm. Faults are classified according to their temporal duration and their behavior toward the other processes of the system. First, we will look at the possible temporal behaviors:

**Permanent Faults:** These types of faults render a process erroneous from the time on when the fault occurs. This can be caused, e.g., by a non-recoverable corruption of the internal state

Figure 1.1: This figure shows the relationship between fault, error and failure. An initial external fault activates an error, which can propagates into a failure of a component, which in turn can cause a fault in another component, which then can activate an error.

due to an external fault or a hardware defect. Note carefully, though, that the erroneous state need not lead to a failure continuously.

**Transient Faults:** As the name suggests, these types of faults create erroneous states that last only for a limited timespan. Typically, transient faults are introduced by external effects, e.g.,  $\alpha$ -particles hitting a transistor or a power outage.

After the primary effect of the fault has ceased, the affected process works normally again, although its state may be contaminated and needs to be recovered so that the process can be considered non-faulty again (cf. Section 1.1.4). If the algorithm employed is not able to reintegrate such a process in the system, a transient fault has the same effect as a permanent fault.

With respect to the behavior of faulty processes towards other processes, we will briefly introduce the two most commonly assumed types of faults:

- **Fail-Silent Faults:** Often referred to as crash fault, this type of fault is the simplest possible: A faulty process just stops sending messages. Difficulties may arise, though, when a process crashes in the middle of a broadcast.

- **Byzantine Faults:** This type of fault is the least restricted, as a process can perform arbitrary actions. A Byzantine faulty process can behave differently to each of its neighbors, can cause timing violations of its messages, and even send incorrect messages.

Fault-tolerant computing has developed solutions that transparently mask failures caused by such faults. Conceptually, this is done by employing fault containment regions, which prohibit the activation of an error or at least its propagation across their boundaries. Some types of faults can be handled, to some degree, at the hardware level and are thus transparently masked w.r.t. the algorithm. For example, a corrupted memory bit can be handled by the hardware when the data is accessed by using an error-correcting code. This is an instance of information

redundancy (and also resource redundancy). A very popular form of fault masking by resource redundancy is replication in conjunction with some form of voting, as, e.g., used in *triple modular redundancy* (TMR). Replicated processes are the dominant approach in fault-tolerant distributed computing and can even deal with Byzantine faults [38]. Finally, time redundancy techniques, i.e., repeating a computation that has failed, are often used as a less costly alternative in cases where short response times are less important. For example, retransmitting a lost message is heavily used in network protocols.

#### 1.1.4 Self-Stabilization

As fault masking techniques completely hide faults from becoming visible, they provide the best fault-tolerance one can hope for. Unfortunately, however, they can usually handle a limited number of faults only. For example, Byzantine distributed agreement [38] can be solved (in synchronous systems) only if at most f out of  $n \ge 3f + 1$  processes can fail. If it ever happens that more than f processes behave faulty, the state of correct processes may be contaminated and hence erroneous. The system will not be able to recover from such a state, even when all n processes would work correctly afterwards, as it is the case for transient faults. Thus, a transient fault has the same effect on the system as a permanent fault, and a process struck by such a fault has to be considered faulty from that time on. Due to the increasing miniaturization in VLSI design, the rate of transient faults has increased [10], which negatively affects the overall fault-tolerance of such systems.

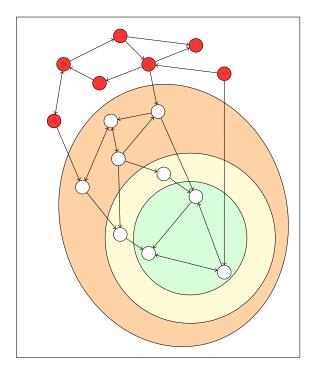

Another popular fault-tolerance technique is *failure detection, isolation and recovery* (FDIR), which cannot transparently mask failures, but guarantees that correct operation will eventually be resumed. The most powerful FDIR approach is a self-stabilizing algorithm. The term self-stabilization was introduced in [13] and specifies a system that, when started from any initial state, will reach a valid state in finite time, provided there is no fault during this stabilization time. The concept of self-stabilization has been extended later to also allow a limited number of permanent (Byzantine) faults [19]. To visualize the concept, consider the complete state space of a system as shown in Figure 1.2. Note that the states used here cover all processes in the system, not just the states of a single process, i.e., a state in the state space is the union of all states of the processes in the system here. This space can be subdivided into several state sets: Moving from the innermost set outwards, we first have the set of legal states, i.e., states in which the system operates correctly. This state set is enclosed by the set of safe states. These states have the property that every transition originating in them leads directly into the set of legal states. The last set is the set of pseudo-legal states, from which an execution exists that reaches a legal state. All states not covered by these sets are the remaining (erroneous) arbitrary states.

If the system is in a legal state and a "massive" fault occurs, then the next state can be outside of the legal state set. When the algorithm employed is self-stabilizing (and the allowed number of permanent faults is no longer exceeded) then the system will eventually reach a legal state again. This is called *convergence* and will happen within the stabilization time. When the system has converged, it will stay within the set of legal states (until another "massive" fault occurs), which is called *closure*.

As there are no restrictions on the states that can be reached due to a fault, this implies that the system can be started in an arbitrary state and will eventually converge to a legal state.

Figure 1.2: This figure shows the complete state space, which is a superset of multiple partial sets. The red nodes symbolize states which are arbitrary. The nodes in the orange area are pseudo-legal states, the nodes in the yellow area are safe states and the green area is the set of legal states.

#### 1.2 Design Methodologies in VLSI

The design of hardware is nowadays primarily done using *very-large-scale integration* (VLSI), which is the integration of millions of transistors on a single die. In this section we will introduce relevant basics of digital circuit design and the design process. Further details may be found in [6, 65, 72], for example.

Digital circuits are designed at a reasonably high-level through *hardware description languages* (HDLs), where the two most common ones are Verilog and VHDL. They allow, at different abstraction levels, to combine different types of boolean logic gates to create combinatorial logic. This combinatorial logic is then processed by a design tool, where also a technology mapping for the intended target device is done. The technology mapping converts generic constructs of the design into specific elements available in the target device, which can be an FPGA or an ASIC. After the technology mapping is finished, a netlist is produced, which describes the final layout of the circuit on the target chip.

Yet, boolean logic gates can only implement stateless operations. As soon as some internal state must be maintained as well, which inevitably involves feedback loops, methods must be employed to ensure the correctness of the computational results. There are two fundamentally different approaches to achieve this:

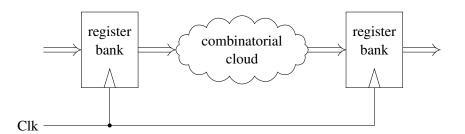

Figure 1.3: A section of a synchronous design. In the center there is the combinatorial cloud that consists of purely combinatorial logic. At every cycle of the clock, the results of the computation of the cloud is stored in the register bank on the right. The inputs for the computation stem from the left register bank. A possible feedback to the register bank on the left is not shown.

#### 1.2.1 Synchronous Model

In the synchronous model, the components of the design can be separated into two groups, namely, (i) the register banks and (ii) the combinatorial clouds connected by parallel data paths, as shown in Figure 1.3. The combinatorial cloud is purely combinatorial logic, which is located between two register banks. Each register bank consists of at least one register, which is typically made up of flip flops. A register has a parallel data and a clock input, as well as a parallel data output. Typically, on the rising edge of the clock signal, the register samples the data on the input and forwards it to the data output, which is then held until the next clock cycle occurs. The required time between two clock edges is defined by the time needed for a signal to propagate through the *critical path*, i.e., the path through the combinatorial cloud with the longest signal delay between any two registers on the chip. The critical path is also influenced by the operating temperature and supply voltage of the chip, which affect the processing delays of the gates, and the delays of the wires connecting the components.

#### 1.2.2 Asynchronous Model

Compared to the synchronous model, the asynchronous model is free of clocked components, i.e., registers. Results of the combinatorial cloud must hence be stored actively when they are available. Some form of handshaking is usually used for this purpose, but due to possibly different processing times of the different parallel paths, completion detection for a data path is a complex task. Completion detection can be done in the value domain, e.g., with encoding techniques like [12, 23, 46]. With these techniques, the data is encoded in a specific way to detect the completion of a computation via valid code words. Such techniques require 2 bits to encode 1 data bit, however, and thus suffer from increased hardware complexity.

Alternatively, completion detection can also be done in the time domain. Simple delayed handshake solutions can be employed in this case, if timing information for the critical path is available. Contrary to the synchronous model, in this scenario, one needs the individual critical path delays (per combinatorial cloud) here, and not the worst-case for the whole circuit. A very elegant approach introduced in [68] utilizes Muller C-Gates (see below) to capture the results of the computations. Nonetheless, delayed handshake solutions suffer from the same problems as

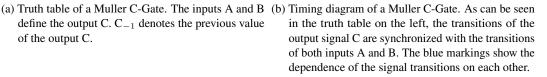

| А | В | С        |

|---|---|----------|

| 0 | 0 | 0        |

| 0 | 1 | $C_{-1}$ |

| 1 | 0 | $C_{-1}$ |

| 1 | 1 | 1        |

define the output C.  $C_{-1}$  denotes the previous value of the output C.

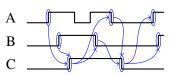

Figure 1.4: Truth table and timing diagram illustrating the behavior of a Muller C-Gate with the inputs A and B, and the output C.

Figure 1.5: Basic principle of metastability. The ball can either go to the stable state on the left or right side of the saddle. When this happens is unknown and cannot even be bounded.

synchronous ones, as the critical path delays also vary with the temperature and supply voltage.

#### 1.2.3 Muller C-Gate

A Muller C-Gate is a basic gate introduced in [49], which can be used for state-holding purposes in asynchronous circuits, like in [68]. In a nutshell, a Muller C-Gate can be seen as an AND-Gate for signal transitions.

The gate has two input ports and one output port. If the state of the input ports match, then their state is take as the new output state, cf. Figure 1.4a. I.e., a common state on the inputs is forwarded and held at the output. Therefore, the transitions at the output port are synchronized with the transitions at both input ports, as can be seen in Figure 1.4b.

#### 1.2.4 What is Metastability?

Metastability [44] describes an unstable state of a stateful discrete system, from which the system will reach, in finite yet unknown time, a stable state.

This can be visualized with the simple physical model shown in Figure 1.5. The ball on top of the saddle will roll down on one of the sides, but to which side, and when this is going to happen, is unknown. In digital logic, the problem is similar. The output voltage of a transistor is an analog value, which is separated into three regions: Two regions describing the discrete values '0' and '1', and the forbidden region separating them. This forbidden region has to be crossed while switching from one state to the other. Although this is a completely normal operation, it

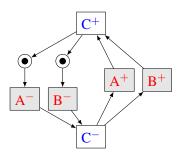

Figure 1.6: An example for a STG, which could be synthesized to a Muller C-Gate, with the inputs A and B and the output C. The nodes with *signal*<sup>+</sup> mark a rising transition of the signal, whereas *signal*<sup>-</sup> marks a falling edge of the respective signal. This is a correct STG, but does not describe the general behavior of a Muller C-Gate, as there are restrictions on the transitions of the input signals as well.

can cause an error if the signal is sampled by a memory element like a flip-flop whilst being in the forbidden region: The flip-flop can become metastable here and output an intermediate voltage for some unknown time (which, in turn, can cause the next downstream memory element to become metastable as well, i.e., metastability could spread in a system).

The same can happen within a flip-flop, due to the internal feedback loop, in case of a setup-/hold-violation. Flip-Flops require their input signal to be stable for a defined time before and after sampling, i.e., the clock transition, as the feedback loop needs some time to settle its state. In the synchronous model, metastability should not happen, as the time accounted for the critical path must incorporate these required time margins. However, input signals from outside the chip, or from other clock domains, can change their value at any time and thus induce metastability. Therefore, dedicated synchronizers, a couple of flip-flops connected in series, are employed for reducing the probability of metastability spreading to the real input of the circuit. Note that synchronizers increase the input signal propagation delay significantly (latency).

Metastability, in principle, can be avoided in asynchronous designs, as there are no clocked elements that have to make a decision in bounded time. Still, problems with external inputs remain, as they can behave arbitrarily anyway.

#### **1.2.5** Signal Transition Graphs

A *signal transition graph* (STG) is basically a labeled Petri Net, which is often used for an event-based description of an asynchronous circuit and its environment. More specifically, STGs define the possible transitions of the signals and can be used to model a speed-independent circuit [11,49,61,64]. A speed-independent circuits functionality is independent of the processing delays of the gates used for implementing the circuit. Note that the wire delays are assumed to be zero here, but as these delays can be abstracted into the processing delays of the gates, this is not a problematic restriction.

A STG like the one shown in Figure 1.6 is basically a Petri Net with implicit transitions, i.e., there are only places (nodes) and arcs (edges) but no transitions in a STG:

Nodes: The nodes represent a single transition of a specific signal, used as the label of the node,

which can be rising (+) or falling (-). Nodes with the same label and polarity in the STG must have a node with the same label and alternative polarity between them.

- **Edges:** The edges of a STG basically represent (some part of) the current state of the circuit. Due to this, and the alternation in polarity of the nodes, it is possible to infer the state of the system based on the currently active edges (see next item).

- **Token:** A token marks a currently *active edge* in the graph. The tokens drawn in a STG define the initial state of the circuit. Unlike Petri Nets, just having tokens on all the incoming edges of a node alone, i.e., all incoming edges active, cannot trigger a transition: the signal transition represented by the node itself is also needed. I.e., the incoming edges of a node are pre-conditions for the execution for the respective transition. During the transition, the tokens on the incoming edges are removed and all outgoing edges are provided with tokens, i.e., the outgoing edges represent the post-condition of a transition.

The possibility to use a STG for the specification of an asynchronous system is convenient, as it allows to (almost) automatically generate a design directly from the specification by means of tools like Petrify [11] and SIS [61]. Yet there are limits: the functionality of the design has to be cyclic, in the sense that all involved signals must make both rising and falling transitions in a strictly alternating fashion. Therefore, there is no way to directly embed a reset signal into a design specified by a STG, for example.

Moreover, tokens cannot appear or disappear on edges in the STG. This is the reason why a STG does not only model a circuit but also its environment, i.e., its input signals. Take for example the STG shown in Figure 1.6. This STG could be synthesized to a single Muller C-Gate, which would indeed implement the defined transition relation. However, the STG does not describe a general Muller C-Gate, with arbitrary inputs, as the STG specifies that the inputs A and B change their respective state exactly once after the output C changed its state.

#### 1.2.6 Functional and Timing Verification

Verifying the correctness of a circuit design is a very important part in the design process for VLSI chips, and usually requires high efforts and costs. By the rule of ten [73], there is an increase of one magnitude for the repair costs with each step in the manufacturing process, from the chip level to the board level to the system level and finally to system operation.

Compared to a software product, repairing a defect is usually not possible at a physical chip. Thus, also the verification process for a VLSI design is different from traditional software: As the production times and costs for a chip are high, it is unreasonable to depend solely on testing. The limited on-chip debugging possibilities also reduce the likelihood of reconstructing settings that caused faulty behavior, and support only limited test coverage as well. Thus, verifying the correctness of a circuit design relies heavily on simulation of the HDL code. These simulations are orders of magnitude slower than the execution of the same behavior in a physical chip, depending on the level of the simulation, but allow complete control over the *unit under test* (UUT). Note that this also allows to simulate the effects of faults, e.g., a broken wire, which are hard or impossible to analyze on a physical chip.

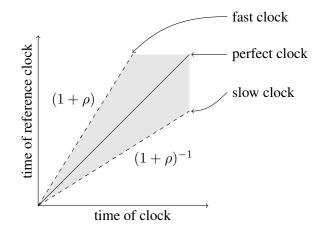

Figure 1.7: Visualization of the effect of the clock drift. The center line represents the perfect clock with no drift, the two outer line represent the minimal resp. maximal drift boundaries. These drift boundaries are reset after a resynchronization of the clock, as can be seen in the point of origin. A typical clock will be inside the gray envelope spanned by the slow and the fast clock.

A simulation environment simulates not only the UUT, but also the testbench that envelops the UUT. The testbench applies stimuli, corresponding to test cases, to the UUT and monitors the responses. Based on these responses, the testbench decides whether the results, provided by the design, are the correct results for the respective test cases. A testbench is called a testbed, when the simulation environment does not run the entire testbench. This includes cases where the testbench only provides the stimuli for the circuit and monitors the results, but applies these to a physical circuit (hardware-in-the-loop).

The abstraction level of simulations can range from a high-level structural simulation, which is rather fast, to the pre-layout simulation, where the design has already been mapped to specific hardware components of the target technology, and finally to the post-layout simulation, which is basically a simulation of the complete physical chip.

#### **1.3 The Clock Distribution Problem**

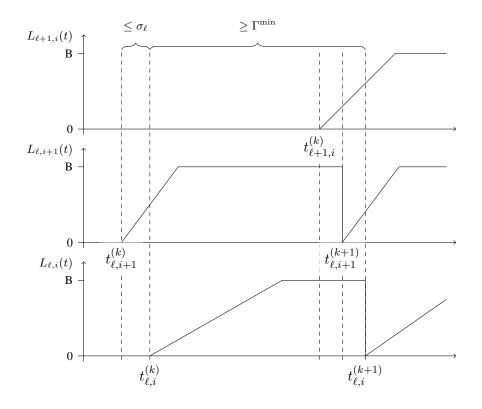

A clock is a device for measuring time and therefore produces ticks with a specific, fixed periodicity, the so called *granularity*. Yet, no clock is perfect, which means that the time between ticks may vary (although the granularity stays constant). These variations depend on many factors, from technological limitations to environmental influences, and can change over time. To specify a real clock, the derivation from an idealized, perfect, clock that displays real-time are used. We will now define the properties of the clocks used in this thesis.

**Drift:** The drift rate  $\rho_i$  is a multiplicative factor, which defines the minimal respectively maximal rate by which clock *i* (of process *i*) runs slower respectively faster than the perfect clock, cf. Figure 1.7. We denote with  $t_i^{(k)}$  the real-time when clock *i* generates its  $k^{\text{th}}$  tick; note that the perfect clock reads  $t_i^{(k)}$  at this time. The (short-term) drift rate is defined as the maximum

difference in time between two ticks of clock i measured with the perfect clock, divided by the granule  $n_i$  of the clock i.

$$\rho_i = \sup_{k \ge 1} \left| \frac{t_i^{(k+1)} - t_i^{(k)}}{n_i} - 1 \right|$$

**Tick separation time:** The tick separation time is the time between two ticks of a clock.  $\Gamma_i^{\min}$  resp.  $\Gamma_i^{\max}$  define the minimal resp. maximal tick separation time of clock *i*:

$$\Gamma_i^{\min} = \inf_{k \ge 1} \left( t_i^{(k+1)} - t_i^{(k)} \right)$$

$$\Gamma_i^{\max} = \sup_{k \ge 1} \left( t_i^{(k+1)} - t_i^{(k)} \right).$$

Note that  $1/\Gamma_i^{\min}$  resp.  $1/\Gamma_i^{\max}$  gives the maximal resp. minimal instantaneous clock frequency of clock *i*.

#### 1.3.1 Synchronized Clocks

Due to the drift  $\rho_i$ , clock *i* deviates from the perfect clock, or another clock *j*, after some time. To keep clocks close to each other, it is necessary to resynchronize those. The largest possible deviation between two clocks is called *precision* if measured in clock time, and *skew* if measured according to the perfect clock.

**Precision:** The precision  $\pi$  is an upper bound on the difference in ticks between two correct clocks read at the same time. Let  $b_i(t)$  be defined as  $b_i(t) = \sup \left\{ k | t_i^{(k)} \le t \right\}$ , then

$$\forall t, i_{\text{correct}}, j_{\text{correct}} : |b_i(t) - b_j(t)| \le \pi$$

**Skew:** The skew is the difference in time between the same tick of two different clocks, i.e.,  $\left|t_{i}^{(k)} - t_{j}^{(k)}\right|$ . Therefore, like the precision, the skew gives a measure for the tightness of the synchronization between different clocks. The skew manifests itself as a phase shift between the generated clock ticks.

#### 1.3.2 Clock Generation

Instead of resynchronizing free-running clocks, a set of processes may also generate clock ticks in a synchronized fashion.

**Definition 1.3.1 (Clock Generation):** For a set of processes (called primary clock sources), a correct clock generation algorithm ensures that all correct clock sources generate clocks with a given maximal skew  $\sigma_0$  and given minimal and maximal tick separation time in  $[\Gamma^{\min}, \Gamma^{\max}]$ .

There are several algorithmic solutions for both problems (synchronization and generation), which differ in the assumptions made on the system and their fault-tolerance properties [2, 17, 18, 20, 24, 59, 76] (see Section 1.4). However, all solutions with reasonable fault-tolerance properties require fully-connected communication topologies.

#### 1.3.3 Clock Distribution

Clock distribution is a technique related to clock generation. As the name suggests, clock ticks, which are generated by one or more synchronized *clock sources*, are being distributed through a suitable *distribution network*. The clock source depends on the specific application domain but can, e.g., be a crystal oscillator or a clock generation algorithm running on a set of processes. We will refer to a clock tick as *pulse*, once it has entered the distribution network.

**Definition 1.3.2 (Clock Distribution):** Given a set of primary clock sources with skew  $\sigma_0$  and pulse separation time in  $[\Gamma^{\min}, \Gamma^{\max}]$ , a correct clock distribution algorithm for a set of nodes ensures that all correct nodes eventually generate pulses with a given maximal skew  $\sigma_{ij}$  between all correct nodes *i* and *j*.

The distribution network can range from a single wire, which transports a signal wave corresponding to the pulse, to highly complex distribution networks consisting of nodes which forward *trigger messages*. Byzantine fault-tolerant clock distribution networks require the reception of multiple trigger messages from different nodes before the local clock tick can be triggered at a node. Thus, every node must be able to distinguish between trigger messages corresponding to different pulses: If there would be no way of detecting the corresponding clock tick of a trigger message, old trigger messages could circulate in the network and spuriously trigger nodes and generate more such trigger messages.

Basically, there are two approaches for solving this problem: (i) using some kind of high-level message to label the trigger messages in some way, or (ii) ensuring that the pulse separation time is large enough so that it is not possible for two trigger messages, corresponding to different pulses, to be mixed up. The first approach is used in theoretical and practical work [27, 66], and is required if trigger messages can circulate in the network. The second approach is the simplest approach possible, as it works with anonymous messages / clock signal transitions. It may decrease the maximum clock frequency, however, as, due to multiple paths, trigger messages can be in transit for a long time.

#### 1.4 Related Work

We are not aware of any related work on Byzantine fault-tolerant clock distribution. We can hence survey some less-related research only.

The capability to distributed a clock to a large number of nodes in a synchronized fashion is essential in many areas, though without considerations for fault-tolerance. Examples are VLSI circuits and other hardware devices, which are the primary focus of this thesis, or a set of distributed nodes in a master-slave topology either on a wired [33,48] or wireless network [30,67]. In VLSI circuits, clock trees are used to provide a high-frequency clock to parts of a chip with synchrony requirements in the range of a fraction of the cycle time [69]. Especially in synchronous designs, skew and power consumption are major problems nowadays due to the rising clock frequencies, so much effort is put into the construction of networks which minimize the skew [25, 39, 40, 56, 57, 62, 77]. In the area of 3D clock distribution for chips fault-tolerance has become an issue, but up to now only benign (fail-silent) faults have been considered [41, 43].

Distributed clock synchronization is an old, well-known problem. It was an active research topic in the 1980s [37, 66, 76], primarily as a real-world application of the consensus problem. More recent research in this area focused primarily on wireless sensor networks [67], self-stabilization [20] and VLSI implementations [27, 28]. The need for distributed clock generation stems from the fact that traditional clock sources, e.g., quartz oscillators, are difficult to control and also highly susceptible to faults. This susceptibility is also a problem for the existing non-fault-tolerant approaches for distributed clock generation [21, 22, 31, 32, 35, 36, 42, 45, 58], which use distributed ring oscillators, *phase locked loops* (PLLs) or similar constructs. Besides Byzantine fault-tolerant solutions like DARTS [28, 29], there are also clock generation algorithms like FATAL<sup>+</sup> [17, 18], which are Byzantine fault-tolerant and self-stabilizing. Since they require a fully-connected network, however, they do not scale to the large number of nodes targeted by HEX.

For didactic reasons, related work on clock multiplication is presented in Section 4.3.

# CHAPTER 2

# HEX

"Kein Hirt und eine Herde! Jeder will das Gleiche, jeder ist gleich: wer anders fühlt, geht freiwillig ins Irrenhaus." — Friedrich Nietzsche, Also sprach Zarathustra

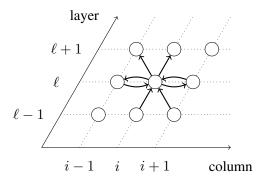

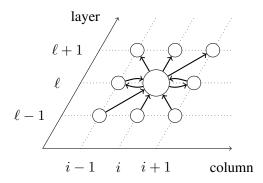

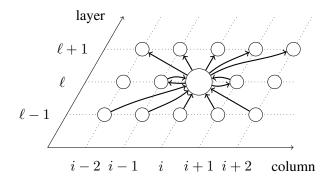

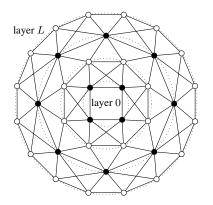

This chapter presents HEX, which is an abbreviation for *hexagonal grid*. HEX comprises an algorithm and a corresponding network structure, which together provide a fault-tolerant, self-stabilizing clock distribution scheme. The name arises from the structure of the neighbors of a node in a HEX grid, which resembles a hexagon, cf. Figure 2.1. This specific network structure was chosen as it is planar and regular. Furthermore, as the average node degree in a planar graph must be < 6,<sup>1</sup> the HEX grid has also the largest possible node degree for a planar graph while still being regular.

This chapter will first provide HEX-related definitions and the analysis of the achievable clock skew in the fault-free case. Subsequently it provides a discussion of possible fault models and their consequences for the skew. Finally, the pulse separation time, which is crucial for the self-stabilizing property, will be determined.

#### 2.1 Topology

HEX is based on a cylindric, directed graph G = (V, E), which is parameterized by  $L \in \mathbb{N}$ , the *layers* of the grid, and  $W \in \mathbb{N}$ , the *columns* of the grid. The node set V defines the vertices of the grid and is the set of tuples  $(\ell, i) \in [L + 1] \times [W]$ . The edge set E, for every node  $(\ell, i) \in V$ , consists of the following links, over which zero-length messages can be sent:<sup>2</sup>

•  $((\ell, i), (\ell, i + 1 \mod W))$  and vice versa to/from the right neighbor for  $\ell \neq 0$ .

<sup>&</sup>lt;sup>1</sup>This follows from Euler's formula. With  $3f \le 2e$ , which is a basic property of any graph, and  $\sum_{v \in V} (deg(v)) = kv$ , with k being the average node degree, this can be shown easily.

<sup>&</sup>lt;sup>2</sup>Note that, in an actual implementation, the timeouts calculated in Section 2.5 must be increased by the duration needed to transmit a message.

- Figure 2.1: The node  $(\ell, i)$  and its neighboring nodes. Column coordinates are modulo W, layer coordinates are between 0 and L. The structure of the connected neighbors form the name-giving hexagon.

- $((\ell, i), (\ell, i 1 \mod W))$  and vice versa to/from the left neighbor for  $\ell \neq 0$ .

- $((\ell 1, i), (\ell, i))$  from the lower-left neighbor iff  $\ell \ge 1$ , and  $((\ell, i), (\ell + 1, i))$  to the upper-right neighbor iff  $\ell \le L$ .

- $((\ell 1, i + 1 \mod W), (\ell, i))$  from the lower-right neighbor iff  $\ell \ge 1$ , and  $((\ell, i), (\ell + 1, i 1 \mod W))$  to the upper-left neighbor iff  $\ell \le L$ .

As it can be seen by the definition of the edges, HEX has the structure of a open cylinder. Thus all calculations on the grids columns are modulo W, without being mentioned explicitly.

Assumption 2.1.1: Each edge has a delay associated with it, which can vary between  $[d^-, d^+] \subset (0, \infty)$ . We assume that

$$\varepsilon = d^+ - d^- \le \frac{d^+}{2}.$$

### 2.2 Algorithm

| Alg       | <b>Algorithm 1:</b> Pulse forwarding algorithm for nodes in layer $\ell > 0$ .                                                                                                         |  |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1 forever |                                                                                                                                                                                        |  |  |  |  |  |  |

| 2         | <ul> <li>on received trigger message from (left and lower-left neighbor) or from (lower-left and lower-right neighbor) or from (lower-right and right neighbor)</li> <li>do</li> </ul> |  |  |  |  |  |  |

| 3         | broadcast trigger message; // local clock pulse                                                                                                                                        |  |  |  |  |  |  |

| 4         | sleep for some time within $[T^-, T^+]$ ;                                                                                                                                              |  |  |  |  |  |  |

| 5         | forget previously received trigger messages;                                                                                                                                           |  |  |  |  |  |  |

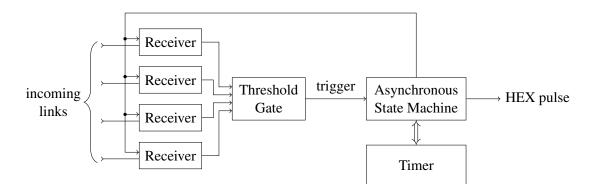

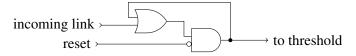

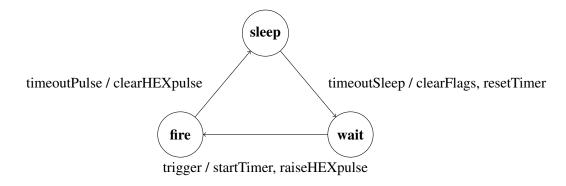

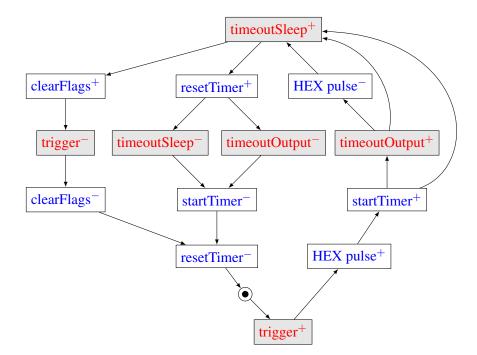

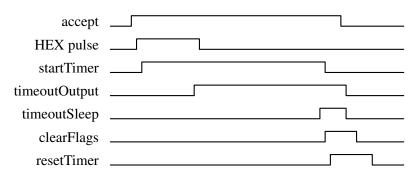

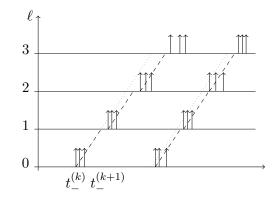

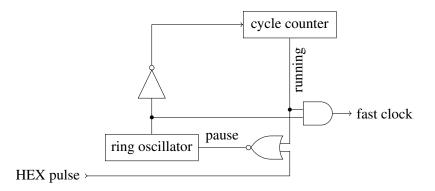

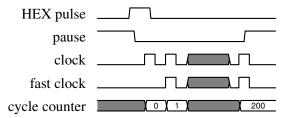

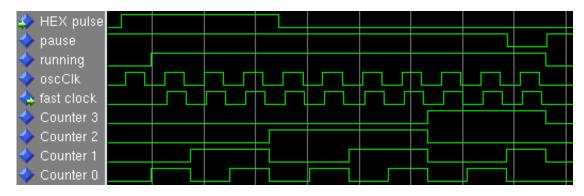

Every node in the HEX grid executes the algorithm shown in Algorithm 1. The node is constantly checking if a trigger condition becomes true, i.e., if the node received trigger messages from one of the three defined node pairs. If the node has been triggered, it broadcasts a trigger message to its outgoing neighbors and then goes to sleep. After the node wakes up, it deletes all trigger messages which were received since the last clearance and repeats checking the trigger conditions.

#### 2.3 Skew Analysis

**Definition 2.3.1 (causal links, neighbors and paths):** A link is a *causal link* for some node if the trigger message received over this link contributed to its triggering, i.e., enabled the guard in Line 2 of Algorithm 1. Note that in Algorithm 1 there are always (at least) two causal links. Furthermore, we say that a node is *left triggered* if the link to the left neighbor is causal, *right triggered* is defined analogously. If a nodes is neither left nor right triggered, it is called *bottom triggered*.

A neighbor is a *causal neighbor* if the link from this neighbor is a causal link. According to Assumption 2.1.1, if a causal neighbor  $(\ell', i')$  of a node  $(\ell, i)$  is triggered at time  $t_{\ell',i'}$ , then the node cannot be triggered before time  $t_{\ell',i'} + d^-$ , i.e.,  $t_{\ell,i} \ge t_{\ell',i'} + d^-$ . A *causal path* consists of causal links.

Note that in the theoretical analysis we assume that the processing time of a HEX node is zero, i.e., a link delay must incorporate the edge delay and the processing delay of the node.

#### 2.3.1 The Fault-Free Case

In the fault-free case, we can restrict our attention to the propagation of a single pulse through the network, i.e., one tick of the underlying clock generation system.

**Definition 2.3.2 (Left Zig-Zag Path):** Informally, a left zig-zag path is a causal path consisting only of links from left and lower-right neighbors.

Given  $\ell \in [L+1]$ ,  $\ell > 0$  and  $i, i' \in [W]$ , i < i', the causal path  $p_{\text{left}}^{i' \to (\ell,i)}$  is constructed starting from node  $(\ell, i)$  as follows: Assume the current starting node of  $p_{\text{left}}^{i' \to (\ell,i)}$  is  $(\ell'', i'')$ . If the left neighbor is causal, then its rightward link  $((\ell'', i'' - 1), (\ell'', i''))$  is prepended to  $p_{\text{left}}^{i' \to (\ell,i)}$ and thus  $(\ell'', i'' - 1)$  is the new starting node of the left zig-zag path. Otherwise, the lower-right neighbor must be causal, so its upward-left link  $((\ell'' - 1, i'' + 1), (\ell'', i''))$  is prepended to  $p_{\text{left}}^{i' \to (\ell,i)}$ . If i'' + 1 = i' and  $p_{\text{left}}^{i' \to (\ell,i)}$  contains more upward-left links than rightward links, the construction is terminated. If  $\ell'' - 1 = 0$ , with arbitrary i'' + 1, the construction is also terminated.

Note that the left zig-zag path depends on the current execution of the grid, as the causal links are determined by the link delays. Furthermore,  $p_{\text{left}}^{i' \rightarrow (\ell,i)}$  does not necessarily start in column i', i.e., when the construction has been terminated due to  $\ell'' - 1 = 0$ , the column may not be i'. Due to the fact that causal paths are acyclic,  $p_{\text{left}}^{i' \rightarrow (\ell,i)}$  will descend to a lower layer after at

Due to the fact that causal paths are acyclic,  $p_{\text{left}}^{i' \to (\ell, i)}$  will descend to a lower layer after at most |W| - 1 added rightward links. This also shows that causal paths are finite and thus their construction terminates in finite time.

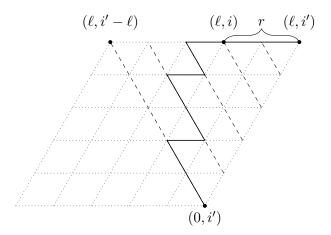

Figure 2.2: Visualization of the "spanning" triangle containing all left zig-zag paths in the proof of Lemma 2.3.5. The dashed lines are the diagonals.

**Definition 2.3.3 (Relative Width of a Left Zig-Zag Path):** The relative width r of a left zigzag path is the number of upward-left links in  $p_{\text{left}}^{i' \to (\ell,i)}$  minus the number of rightward links.

**Lemma 2.3.4** If a left zig-zag path  $p_{left}^{i' \to (\ell,i)}$  has r > 0 and starts in  $(\ell', i')$  then the same holds for every prefix.

PROOF Suppose that the prefix  $\pi$  violates this, then it must end with a node  $(\ell'', i'')$  with  $i'' \ge i'$ . But then the suffix must have more up-left than rightward edges and thus must have crossed i'. As a crossing of i' terminates the construction of a left zig-zag path, such a left zig-zag path cannot exist.

**Lemma 2.3.5** Consider a prefix  $\pi$  of  $p_{left}^{i' \to (\ell'', i'')}$ , starting at node  $(\ell', i')$  and ending at  $(\ell, i)$ , for which  $\ell > 0$  and r > 0 holds. Then, the triggering time of node  $(\ell, i')$  satisfies

$$t_{\ell,i'} \le t_{\ell,i} + rd^- + (\ell - \ell')\varepsilon.$$

**PROOF** W.1.o.g. we shift  $\ell'$  to 0 and update  $\ell$  accordingly to  $\ell = \ell - \ell'$ .

Thus  $p_{\text{left}}^{i' \to (\ell,i)}$  is limited by the triangle spanned by the nodes (0,i'),  $(\ell,i'-\ell)$  and  $(\ell,i')$ , cf. Figure 2.2. Note that  $(\ell,i)$  is between  $(\ell,i'-\ell)$  and  $(\ell,i')$  as  $i'-\ell \le i < i'$ . Furthermore note that  $p_{\text{left}}^{i' \to (\ell,i)}$  will, as shown in Lemma 2.3.4, not cross column i' and thus r > 0 also holds for every prefix of  $\pi$ . Also note that in cases where  $\ell > W$  the triangle would contain some nodes more than once; nonetheless the left zig-zag paths in such cases are still bounded by this lemma, only the timebound given is an overapproximation.

We define diagonal k as the set of nodes  $0 \le k \le \ell$ , on the line between the nodes (k, i') and  $(\ell, i' - \ell + k)$ .

To prove the lemma, we will first show that every node p on diagonal k, which is on or to the right of  $\pi$ , will be triggered by time  $t_p \leq t_{\ell,i} - (\ell - r)d^- + kd^+$ . Note that  $(\ell, i)$  resp.  $(\ell, i')$  are on diagonal  $\ell - r$  resp.  $\ell$ .

First we show that the statement holds for every node p on  $\pi$ . The predecessor q of p on  $\pi$  was triggered at least  $d^-$  before p, i.e.,  $t_q \leq t_p - d^-$ , as  $\pi$  is a causal path. This argument can be extended to every predecessor of p. So u, the  $h^{\text{th}}$  predecessor of p, which is h hops away from p, was triggered at least at  $t_u \leq t_p - hd^-$ . We now relate the diagonal to the hop count: The minimal diagonal reachable is the number of rightward links minus the hop count:  $k \geq (\ell - r) - h$ . Thus, we can conclude that  $t_u \leq t_p - hd^- \leq t_p - (\ell - r)d^- + kd^- \leq t_p - (\ell - r)d^- + kd^+$ , and have thereby shown that the statement holds for all nodes on  $\pi$ .

We will now prove by induction that our statement holds on every diagonal. Observe that every node on diagonal 0 is either on  $\pi$  or left of  $\pi$ . Thus, the base case h = 0 case has already been shown.

Assume now that statement holds for diagonal k and observe diagonal k + 1. We only need to consider nodes which are to the right of  $\pi$ . Observe that the left and lower-left neighbor of every node on diagonal k + 1 are on diagonal k. So every node p on diagonal k + 1 will be triggered at most  $d^+$  after its neighbors on diagonal k were triggered:  $t_p \leq t_{\ell,i} - (\ell - r)d^- + kd^+ + d^+ = t_{\ell,i} - (\ell - r)d^- + (k + 1)d^+$ , which proves our statement.

To prove our lemma, we just have to plug-in: Since  $(\ell, i')$  is on diagonal  $\ell$ , which is actually  $(\ell - \ell')$  due to our initial shifting, we obtain  $t_{\ell,i'} \leq t_{\ell,i} - ((\ell - \ell') - r)d^- + (\ell - \ell')d^+ = t_{\ell,i} + rd^- + (\ell - \ell')\varepsilon$  as asserted.

**Definition 2.3.6 (Distance and Skew Potential):** For two nodes  $i, j \in [W]$ , we define their distance as  $|i - j|_W = \min(d, W - d)$ , where  $d = i - j \mod W$ . For  $\ell \in [L + 1]$ , the skew potential on layer  $\ell$  is  $\Delta_{\ell} = \max(\max_{i,j \in [W]}(t_{\ell,i} - t_{\ell,j} - |i - j|_W d^-), 0)$ .

The skew potential is thus the difference between the trigger time of nodes i and j, at the same layer compensated by the time a trigger message would need, in the best case, to propagate between them.

The following Lemma 2.3.7 reveals an important property of HEX, namely, that the skew at layer 0 does not affect the skew at layer W - 2 and above.

**Lemma 2.3.7** For all  $\ell \in \{W - 2, \dots, L\}$  we have that  $\Delta_{\ell} \leq 2(W - 2)\varepsilon$ .

**PROOF** We will derive a bound on  $\Delta_{\ell}$  by subtraction the earliest from the latest triggering time of any node on layer  $\ell$ .

W.l.o.g. we assume that  $\ell = W - 2$ . Further, we pick two nodes  $i, i' \in [W]$ , i < i', for which  $i' - i = |i - i'|_W$  holds. Cases where the wrap-around distance is shorter can be handled by swapping the nodes, which is symmetrical anyway. We distinguish two cases.

Case 1:

$$p_{\text{left}}^{i' \to (\ell,i)}$$

starts at node  $(\ell',i')$  for some  $\ell' \in \{1, ..., \ell-1\}$ . Then, by Lemma 2.3.5,

$t_{\ell,i'} \le t_{\ell,i} + (i'-i)d^- + (\ell - \ell')\varepsilon \le t_{\ell,i} + (i'-i)d^- + \ell\varepsilon \le t_{\ell,i} + (i'-i)d^- + (W-2)\varepsilon$ .

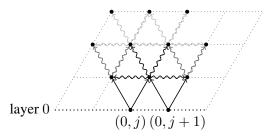

Figure 2.3: Illustration of the induction proof Lemma 2.3.7 at time  $d^+$ , considering all link delays are  $d^+$ . The solid lines mark the trigger messages which where received at  $d^+$ , the wiggly black lines symbolize the trigger messages which will be sent at  $d^+$ . The dark gray wiggly lines are the trigger messages which will be sent at  $2d^+$ , and the light gray are those sent at  $3d^+$ .

**Case 2:**  $p_{\text{left}}^{i' \to (\ell,i)}$  starts at node (0,j),  $j \in [W]$ . The path from (0,j) to  $(\ell,i)$  contains  $\ell$  upward-left links and at least  $(\ell - (i' - i))$  rightward links.

Denote by  $t_0$  the first time two adjacent nodes on layer 0 trigger. Then the earliest time node  $(\ell, i)$  will be triggered is:

$$t_{\ell,i} \ge t_0 + \ell d^- + (\ell - (i' - i))d^- = t_0 + (2(W - 2) - (i' - i))d^-$$

(2.1)

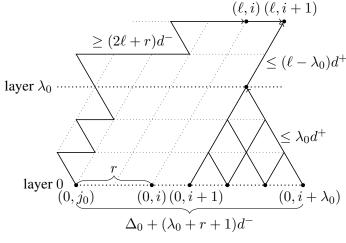

We will now show that every node in layer  $\ell = W - 2$  will be triggered at latest by  $t_0 + 2(W-2)d^+$ . Therefore, assume that (0, j) is the node such that  $\max(t_{0,j}, t_{0,j+1}) = t_0$ . We will prove by induction on  $\lambda$  that, for every layer  $\lambda$ , the nodes  $(\lambda, j - \lambda), (\lambda, j - \lambda + 1), \dots, (\lambda, j + 1)$  will be triggered no later than  $t_0 + 2\lambda d^+$ . An illustration of the first few layers is shown in Figure 2.3.

For the base case  $\lambda = 0$  consider layer 0: As the nodes (0, j) and (0, j + 1) were used to define  $t_0$ , the hypothesis holds.

Assume that the hypothesis held in layer  $\lambda$ , then the nodes  $(\lambda, j-\lambda), (\lambda, j-\lambda+1), \ldots, (\lambda, j+1)$  triggered at latest by  $t_0 + 2\lambda d^+$ . The nodes  $(\lambda + 1, j - \lambda), (\lambda, j - \lambda + 1), \ldots, (\lambda, j)$  all have two neighbors in layer  $\lambda$  which triggered no later than  $t_0 + 2\lambda d^+$ , thus those nodes will trigger no later than  $t_0 + (2\lambda + 1)d^+$ . Hence, no later than  $t_0 + (2\lambda + 2)d^+ = t_0 + 2(\lambda + 1)d^+$  the nodes  $(\lambda + 1, j - \lambda + 1)$  and  $(\lambda + 1, j + 1)$  will also trigger and thereby establish the hypothesis for  $\lambda + 1$ .

We can now use Equation (2.1) to calculate the worst-case skew between the nodes i and i':

$$t_{\ell,i} \ge t_0 + (2(W-2) - (i'-i))d^-$$

$$t_{\ell,i'} \le t_0 + 2(W-2)d^+$$

$$t_{\ell,i'} - t_{\ell,i} \le t_0 + 2(W-2)d^+ - t_0 - (2(W-2) - (i'-i))d^-$$

$$\le 2(W-2)\varepsilon + (i'-i)d^-$$

As all cases of (i' - i) can be covered by symmetry, as stated in the beginning, we can replace the term with the node distance, and conclude that

$$\Delta_{\ell} = \max_{i,i' \in [W]} (t_{\ell,i'} - t_{\ell,i} - |i' - i|_W d^-) \le 2(W - 2)\varepsilon$$

22

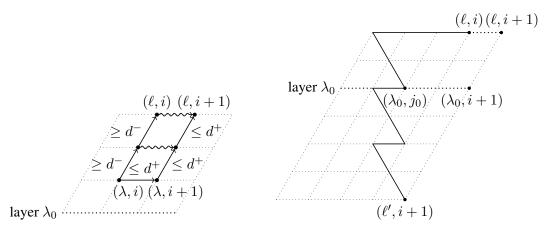

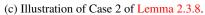

(a) Illustration of Case 1 of Lemma 2.3.8.

(b) Illustration of Case 3 of Lemma 2.3.8.

Figure 2.4: Illustration of the three cases used to proof Lemma 2.3.8.

holds as claimed in both cases.

**Lemma 2.3.8** For all layers  $\ell_0 \in [L]$  and  $\ell \in \{\ell_0 + 1, \dots, L\}$ , it holds for each  $i \in [W]$  that

$$|t_{\ell,i} - t_{\ell,i+1}| \le d^+ + \left\lfloor \frac{(\ell - \ell_0)\varepsilon}{d^+} \right\rfloor \varepsilon + \Delta_{\ell_0}.$$

PROOF We define  $\lambda_0 = \left\lfloor \frac{\ell d^-}{d^+} \right\rfloor$ , which marks the last layer where the longest possible  $p_{\text{left}}^{i' \to (\ell,i)}$ , under Assumption 2.1.1 with delay  $d^-$ , from a node (0,i) is slower than the direct path from

(0, i) to  $(\lambda_0, i)$  with delay  $d^+$ . Furthermore it holds that

$$\ell - \left\lfloor \frac{\ell d^-}{d^+} \right\rfloor = \left\lceil \frac{\ell \varepsilon}{d^+} \right\rceil.$$

(2.2)

Case 1:  $t_{\lambda,i+1} \leq t_{\lambda,i} + d^+$  for the smallest  $\lambda > \lambda_0$  such that for all  $\lambda' \in \{\lambda + 1, \dots, \ell\}$ :  $t_{\lambda',i+1} > t_{\lambda',i} + d^+$  holds true, cf. Figure 2.4a. This implies that the nodes  $(\lambda', i)$  cannot be triggered by their right neighbor, and therefore the links from  $(\lambda' - 1, i)$  must be causal. From this it follows that  $t_{\lambda'-1,i} + d^- \leq t_{\lambda',i}$ . As this property holds for all nodes, by induction, we get  $t_{\ell,i} \geq t_{\lambda,i} + (\ell - \lambda)d^-$ .

By the required property on  $\lambda$  we can also be sure that the trigger message from  $(\lambda', i)$  will arrive at node  $(\lambda', i + 1)$  before  $t_{\lambda',i+1}$ . Hence, the node will trigger when the message from its lower-left neighbor  $(\lambda' - 1, i + 1)$  arrives, if the node has not already done so. Consequently,  $d^+$ is the upper bound for the skew between two nodes in column i + 1 starting from layer  $\lambda$ , and we can, by induction, conclude that

$$t_{\ell,i+1} \le t_{\lambda,i+1} + (\ell - \lambda)d^+.$$

(2.3)

As we know, by our assumption, the difference between the two nodes  $(\lambda, i)$  and  $(\lambda, i + 1)$ , we can extend the former inequality to  $t_{\ell,i+1} \leq t_{\lambda,i} + (\ell - \lambda)d^+ + d^+$ . The skew between the two neighbors  $(\ell, i)$  and  $(\ell, i + 1)$  on layer  $\ell$  hence follows from

$$-t_{\ell,i} \leq -t_{\lambda,i} - (\ell - \lambda)d^{-}$$

$$t_{\ell,i+1} - t_{\ell,i} \leq t_{\lambda,i} + (\ell - \lambda)d^{+} + d^{+} - t_{\lambda,i} - (\ell - \lambda)d^{-} = (\ell - \lambda)\varepsilon + d^{+}$$

$$t_{\lambda',i+1} > t_{\lambda',i} + d^{+} \Rightarrow t_{\ell,i+1} - t_{\ell,i} > 0$$

$$t_{\ell,i+1} - t_{\ell,i} = |t_{\ell,i} - t_{\ell,i+1}| \leq (\ell - \lambda)\varepsilon + d^{+}$$

(2.4)

Case 2: Case 1 does not apply and  $p_{\text{left}}^{i' \to (\ell,i)}$  starts at some node  $(0, j_0)$ , for  $j_0 \neq i + 1$ . We can also conclude that  $r \ge 0$  (recall Definition 2.3.3), as otherwise the end would be in node (0, i + 1), which is excluded, or the left zig-zag path would have crossed column i + 1, in which case r > 0 would have been true and thus the left zig-zag path would have terminated there. Hence,  $p_{\text{left}}^{i' \to (\ell,i)}$  has length  $2\ell + r$  and  $j_0 = i - r \mod W$  and thereby we can infer that  $t_{\ell,i} \ge t_{0,j_0} + (2\ell + r)d^-$ .

Observe that a  $d^+$  path from node (0, i+1) to  $(\lambda_0, i+1)$  spans a triangle with node  $(0, i+\lambda_0+1)$  as the third corner, as can be seen in Figure 2.4c. For each  $j \in \{i+1, i+2, \ldots, i+\lambda_0+1\}$  it holds that  $|j - j_0|_W \le j - j_0 = j - i + r$ . From that, and using the definition of the skew potential, we obtain

$$t_{\ell,i} \ge t_{0,j_0} + (2\ell + r)d^-$$

$$\ge t_{0,j} - |j - j_0|_W d^- - \Delta_0 + (2\ell + r)d^-$$

$$\ge t_{0,j} - (j - i)d^- - \Delta_0 + 2\ell d^-$$

$$\ge t_{0,j} - \Delta_0 + (2\ell - \lambda_0 - 1)d^-.$$

By induction, we can show that for each  $\lambda \in \{0, ..., \lambda_0\}$  every node  $(\lambda, i + 1), (\lambda, i + 2), ..., (\lambda, i + \lambda_0 + 1 - \lambda)$  will trigger no later than

$$\max_{i \in \{i+1,\dots,i+\lambda_0+1-\lambda\}} (t_{0,j}) + \lambda d^+ \le t_{\ell,i} + \Delta_0 - (2\ell - \lambda_0 - 1)d^- + \lambda d^+$$

By using the definition of  $\lambda_0$ , as the maximal value for  $\lambda$ , we get

$$\begin{split} t_{\lambda_0,i+1} &\leq t_{\ell,i} + \Delta_0 - (2\ell - \lambda_0 - 1)d^- + \lambda d^+ \\ &\leq t_{\ell,i} + \Delta_0 - (2\ell - \lambda_0 - 1)d^- + \frac{\ell d^-}{d^+}d^+ = t_{\ell,i} + \Delta_0 - (\ell - \lambda_0 - 1)d^-. \end{split}$$

Case 1 does not apply, thus  $t_{\lambda,i+1} > t_{\lambda,i} + d^+$  holds for all  $\lambda \ge \lambda_0$ , which allows us to use similar arguments as we used to derive Equation (2.3): Every node  $(\lambda, i + 1)$  is left triggered and thus its triggering time can be obtained, by induction, starting from node  $(\lambda_0, i + 1)$ , which leads to

$$t_{\ell,i+1} \le t_{\lambda_0,i+1} + (\ell - \lambda_0)d^+.$$

(2.5)

Therefore, it follows that

$$\begin{split} t_{\ell,i+1} - (\ell - \lambda_0)d^+ &\leq t_{\lambda_0,i+1} \leq t_{\ell,i} + \Delta_0 - (\ell - \lambda_0 - 1)d^- \\ t_{\ell,i+1} &\leq t_{\ell,i} + \Delta_0 - (\ell - \lambda_0 - 1)d^- + (\ell - \lambda_0)d^+ \\ &= t_{\ell,i} + \Delta_0 + (\ell - \lambda_0)\varepsilon + d^- = t_{\ell,i} + \Delta_0 + \left(\ell - \left\lfloor \frac{\ell d^-}{d^+} \right\rfloor\right)\varepsilon + d^- \\ &= t_{\ell,i} + \Delta_0 + \left\lceil \frac{\ell \varepsilon}{d^+} \right\rceil \varepsilon + d^-, \end{split}$$

from which we arrive at

$$t_{\ell,i+1} - t_{\ell,i} = |t_{\ell,i} - t_{\ell,i+1}| \le \Delta_0 + \left\lceil \frac{\ell\varepsilon}{d^+} \right\rceil \varepsilon + d^-$$

**Case 3: Neither Case 1 nor Case 2 apply.** In this case,  $p_{\text{left}}^{i' \to (\ell,i)}$  starts at some node  $(\ell', i + 1)$  for some  $\ell' < \ell$ , and  $t_{\lambda,i+1} > t_{\lambda,i} + d^+$  holds for all  $\lambda \ge \lambda_0$ . Therefore, the first link of  $p_{\text{left}}^{i' \to (\ell,i)}$  is  $((\ell', i + 1), (\ell' + 1, i))$ , as shown in Figure 2.4b. As Case 1 does not apply,  $p_{\text{left}}^{i' \to (\ell,i)}$  must start on a layer  $\ell' < \lambda_0 - 1$ : Otherwise, e.g., for  $\ell' = \lambda_0 - 1$ ,  $(\lambda_0, i + 1)$  would be triggered no later than  $\max(t_{\ell',i+1} + d^+, t_{\lambda_0,i} + d^+)$ . Hence  $t_{\lambda_0,i+1} \le t_{\lambda_0,i} + d^+$  would hold, which contradicts the assumption that Case 1 does not hold.

Let  $(\lambda_0, j_0)$  be the last node of  $p_{\text{left}}^{i' \to (\ell,i)}$  on layer  $\lambda_0$ . Observe that  $j_0 = i + 1 - r$  holds and thus Lemma 2.3.5 can be applied on a prefix  $\pi$  of  $p_{\text{left}}^{i' \to (\ell,i)}$  ending at node  $(\lambda_0, j_0)$ , thus yielding  $t_{\lambda_0,i+1} \leq t_{\lambda_0,j_0} + rd^- + (\lambda_0 - \ell')\varepsilon = t_{\lambda_0,j_0} + (i + 1 - j_0)d^- + (\lambda_0 - \ell')\varepsilon$ . As Case 1 does not hold, we can use Equation (2.5) and obtain

$$t_{\ell,i+1} \le t_{\lambda_0,j_0} + (i+1-j_0)d^- + (\lambda_0 - \ell')\varepsilon + (\ell - \lambda_0)d^+.$$

By construction,  $p_{\text{left}}^{i' \to (\ell,i)}$  has length  $2(\ell - \ell') - 1$  and the prefix  $\pi$  has length  $2(\lambda_0 - \ell') - (i+1-j_0)$ , thus the suffix starting at node  $(\lambda_0, j_0)$  has length  $2(\ell - \lambda_0) + (i - j_0)$ . As the suffix is also a causal path, we can infer that

$$t_{\ell,i} \ge t_{\lambda_0,j_0} + (2(\ell - \lambda_0) + (i - j_0)) d^-.$$

Thus, we arrive at

$$\begin{split} t_{\ell,i+1} - t_{\ell,i} &\leq (1+i-j_0)d^- + (\lambda_0 - \ell')\varepsilon + (\ell - \lambda_0)d^+ - (2(\ell - \lambda_0) + (i-j_0))d^- \\ &= d^- + (\lambda_0 - \ell')\varepsilon + (\ell - \lambda_0)d^+ - 2(\ell - \lambda_0)d^- \\ &= d^- + (\ell - \ell')\varepsilon - (\ell - \lambda_0)d^- = (\ell - \ell')\varepsilon - (\ell - \lambda_0 - 1)d^- \\ &\underbrace{\leq}_{\ell'=0} \ell\varepsilon - \left(\ell - \frac{\ell d^-}{d^+} - 1\right)d^- = \ell\varepsilon - \left(\frac{\ell\varepsilon}{d^+} - 1\right)d^- = \ell\varepsilon - \frac{\ell\varepsilon d^-}{d^+} + d^- \\ &\leq \left\lceil \frac{\ell\varepsilon}{d^+} \right\rceil \varepsilon + d^-. \end{split}$$

Since these three cases where exhaustive and for each the claimed bound holds, this concludes the proof.  $\Box$

**Corollary 2.3.9** Set  $\delta = d^{-}/2 - \varepsilon$ . For each layer  $\ell \in \{W, \ldots, L\}$  and  $i \in [W]$  it holds that

$$|t_{\ell,i} - t_{\ell,i+1}| \le \max\left\{d^+ + \left\lceil \frac{W\varepsilon}{d^+} \right\rceil \varepsilon, \ \Delta_{\ell-W} + d^+ - W\delta\right\}.$$

(2.6)

PROOF The proof is, for great parts, analogous to Lemma 2.3.8 and thus will follow the same patterns. W.l.o.g. we assume that  $\ell_0 = \ell - W$ .

**Case 1:**  $t_{\lambda,i+1} \leq t_{\lambda,i} + d^+$  for the smallest  $\lambda > \lambda_0$  such that for all  $\lambda' \in \{\lambda + 1, \dots, \ell\}$ :  $t_{\lambda',i+1} > t_{\lambda',i} + d^+$  holds true. As there are no assumptions on the layer in Lemma 2.3.8, we can directly take Equation (2.4) from said lemma:

$$|t_{\ell,i} - t_{\ell,i+1}| \le (\ell - \lambda)\varepsilon + d^+ \le \left\lceil \frac{(\ell - \ell_0)\varepsilon}{d^+} \right\rceil \varepsilon + d^+.$$

Due to the assumption about  $\ell_0$ , the equation simplifies to

$$|t_{\ell,i} - t_{\ell,i+1}| \le d^+ + \left\lceil \frac{W\varepsilon}{d^+} \right\rceil \varepsilon,$$

which proves this case.

**Case 2: Case 1 does not apply and**  $p_{\text{left}}^{i' \to (\ell,i)}$  **starts at some node**  $(0, j_0)$ , for  $j_0 \neq i + 1$ . This case needs some additional refinements to show the bound. The beginning is equal to Case 2 of Lemma 2.3.8, but w.l.o.g. we now assume that  $\ell = W$ .

For each  $j \in \{i + 1, i + 2, ..., i + \lambda_0 + 1\}$  it holds that  $|j - j_0|_W \le j - j_0 \le W/2 = \ell/2$ , which is different from what has been used in Lemma 2.3.8. From that, and using the definition of the skew potential, we obtain

$$t_{\ell,i} \ge t_{0,j_0} + (2\ell + r)d^- \ge t_{0,j} - |j - j_0|_W d^- - \Delta_0 + (2\ell + \underbrace{r}_{\ge 0})d^- \ge t_{0,j} - \frac{\ell d^-}{2} - \Delta_0 + 2\ell d^- = t_{0,j} - \Delta_0 + \frac{3\ell d^-}{2}.$$

The proof now proceeds as in Case 2 of Lemma 2.3.8. By induction, we can show that

$$t_{\lambda_0,i+1} \le t_{\ell,i} + \Delta_0 - \frac{\ell d^-}{2}.$$

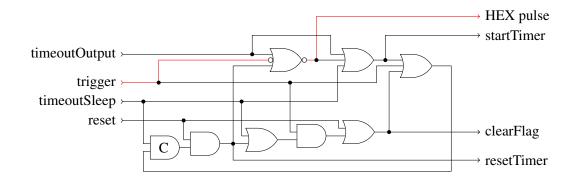

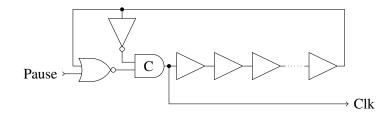

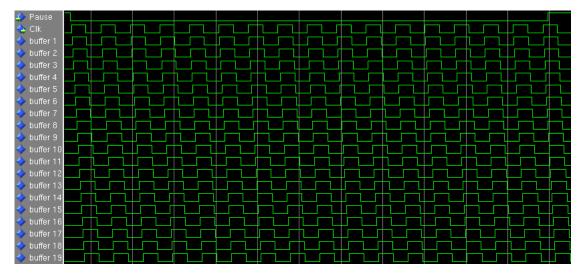

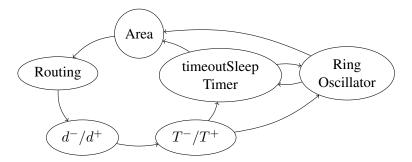

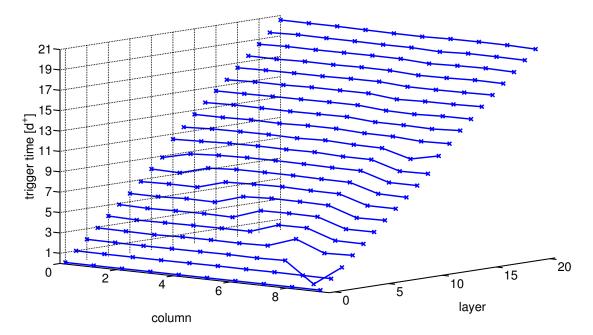

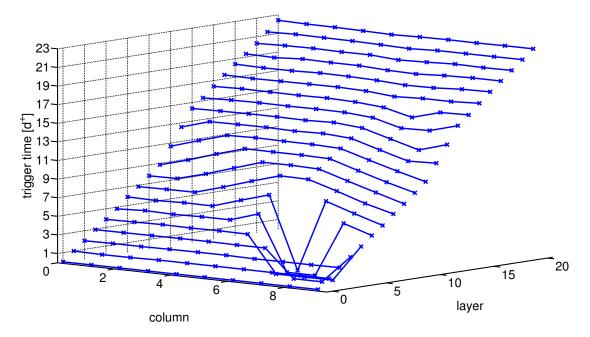

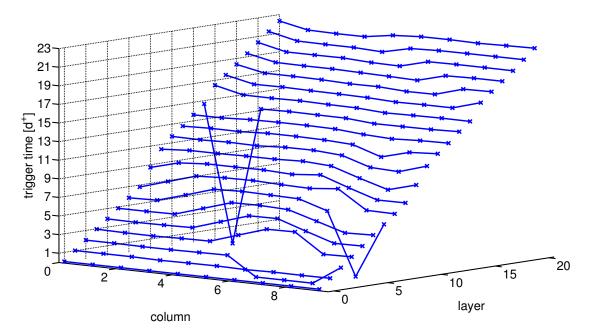

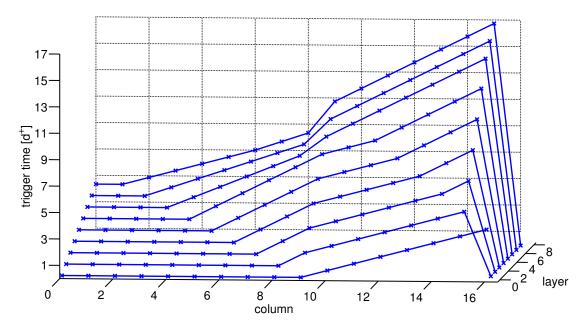

Plugging this into Equation (2.5) finally leads to