The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology. http://www.ub.tuwien.ac.at/eng

Hypervisor Based Composable Systems for the Automotive Industry

## Making a Secure Platform Safe

## DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Master of Science**

im Rahmen des Studiums

## Technische Informatik

eingereicht von

## Andreas Platschek

Matrikelnummer 0425291

an der

Fakultät für Informatik der Technischen Universität Wien

Betreuung: o.Univ.Prof. Dipl.-Ing. Dr. Dietmar Dietrich Mitwirkung: Dipl.-Ing. (FH) Dr.techn. Heimo Zeilinger Prof. Nicholas Mc Guire

Wien, 15.07.2013

(Unterschrift Verfasser)

(Unterschrift Betreuung)

# Hypervisor Based Composable Systems for the Automotive Industry

## Making a Secure Platform Safe

## MASTER'S THESIS

submitted in partial fulfillment of the requirements for the degree of

## **Master of Science**

in

### **Computer Engineering**

by

## **Andreas Platschek**

Registration Number 0425291

to the Faculty of Informatics

at the Vienna University of Technology

Advisor: o.Univ.Prof. Dipl.-Ing. Dr. Dietmar Dietrich Assistance: Dipl.-Ing. (FH) Dr.techn. Heimo Zeilinger Prof. Nicholas Mc Guire

Vienna, 15.07.2013

(Signature of Author)

(Signature of Advisor)

# Erklärung zur Verfassung der Arbeit

Andreas Platschek Theresiengasse 25-27, A-1180 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

# Acknowledgements

Thanks to all who gave me inspiration and guidance to write this thesis (knowingly or otherwise). Of course this includes everyone at OpenTech, OSADL and the whole FLOSS community - thanks for all I was able to learn from you and the guidance I got from you guys.

Special thanks to Prof. Nicholas Mc Guire, for all your guidance, patience and insight, as well as for kicking my butt at appropriate times.

Last but not least: thanks to my family and friends!

## Abstract

Following the trend already set by the avionics industry, the automotive industry is reconsidering its current approach towards on-board electronics as well and starts to integrate multiple ECUs (Error Containment Units) into one hardware node. Following this approach it is vital to ensure the independence of residing applications, which often require different levels of safety and security. Independence is achieved by partitioning, that means temporal and spatial isolation, supplemented by communication mechanisms that must not violate the isolation properties. This approach allows the construction of composable systems that simplify the reuse of (legacy) software modules based on temporal and spatial isolation. Furthermore the preservation of dependability, safety and security properties of the individual modules is ensured, enabling modular validation and certification.

This thesis approaches the safety aspects of utilizing free/libre open source software (FLOSS) components, taking the constraints of the automotive industry into account. The approach taken is to use the XtratuM2 hypervisor, and to execute multiple instances of a FLOSS implementation of an OSEK (Offene Systeme und deren Schnittstellen für die Elektronik im Kraftfahrzeug) compliant operating system – each instance running one automotive application – on top of it. The resulting implementation is able to run several independent automotive applications in parallel on the same processor, rather than requiring a single hardware node for each of them. This approach reduces the number of ECUs in the car, leading to a decrease of power consumption and weight, allowing a higher utilization of the hardware nodes and simplifying inter-node communication.

## Kurzfassung

Genau wie die Luftfahrt Industrie ist derzeit auch die Automobil Industrie im Umbruch, und beginnt mehrere ECUs (Error Containment Units) in einen Hardware Knoten zu integrieren. Bei diesem Ansatz ist es jedoch äußerst wichtig, dass die Unabhängigkeit der Applikationen – die meist auch unterschiedliche Sicherheitsanforderungen (sowohl Safety als auch Security) haben – erhalten bleibt. Die Unabhängigkeit wird durch Isolation, das heißt zeitliche sowie räumliche Trennung erreicht und wird durch geeignete Kommunikationsmechanismen, die keines dieser Isolationskriterien stören dürfen, ergänzt. Der Ansatz erlaubt, durch die Isolation die Safetyund Security-Eigenschaften zu erhalten und ermöglicht so die modulare Validierung sowie die modulare Zertifizierung von Software.

Die Arbeit versucht, die Safety-Kriterien, die von der Automobil Industrie gefordert werden, mit Hilfe von FLOSS (free/libre open source software) zu erfüllen. Die gewählte Vorgehensweise ist, basierend auf dem XtratuM2 Hypervisor mehrere unabhängige Instanzen einer FLOSS-Implementierung der OSEK-Spezifikation (Offene Systeme und deren Schnittstellen für die Elektronik im Kraftfahrzeug) laufen zu lassen, wobei jede dieser Instanzen eine typische Applikation aus dem Automobil Bereich ausführt. Die resultierende Plattform erlaubt es, mehrere unabhängige Applikationen parallel laufen zu lassen, anstatt einen Hardware Knoten für jede der Applikationen zu verwenden. Dieser Ansatz reduziert die Anzahl der Knoten im Fahrzeug und führt so zu einer Reduktion des Gewichtes sowie des Stromverbrauchs. Weiters wird die Ausnutzung der Ressourcen, die moderne CPUs zur Verfügung stellen, verbessert und die Kommunikation zwischen Applikationen vereinfacht.

# Contents

| 1 | Intr                      | Introduction 1                                   |  |  |  |

|---|---------------------------|--------------------------------------------------|--|--|--|

|   | 1.1                       | Motivation                                       |  |  |  |

|   | 1.2                       | Goals                                            |  |  |  |

|   | 1.3                       | Methodical Approach                              |  |  |  |

|   | 1.4                       | Structure of the Thesis                          |  |  |  |

| 2 | Concepts and Technologies |                                                  |  |  |  |

|   | 2.1                       | Operating Systems Classification                 |  |  |  |

|   | 2.2                       | Virtualization                                   |  |  |  |

|   | 2.3                       | Virtualization in the Safety Domain              |  |  |  |

|   | 2.4                       | Integrated Modular Avionics                      |  |  |  |

|   | 2.5                       | Toolchain - used tools                           |  |  |  |

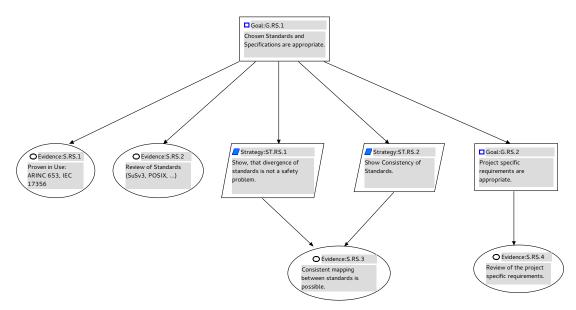

|   | 2.6                       | Goal Structured Notation    28                   |  |  |  |

|   | 2.7                       | Real-Time Structured Analysis and Design         |  |  |  |

| 3 | Rele                      | evant Standards 35                               |  |  |  |

|   | 3.1                       | ARINC 653                                        |  |  |  |

|   | 3.2                       | Interpartition Communication in ARINC 653        |  |  |  |

|   | 3.3                       | OSEK/VDX                                         |  |  |  |

|   | 3.4                       | Establishing a Mapping between ARINC653 and OSEK |  |  |  |

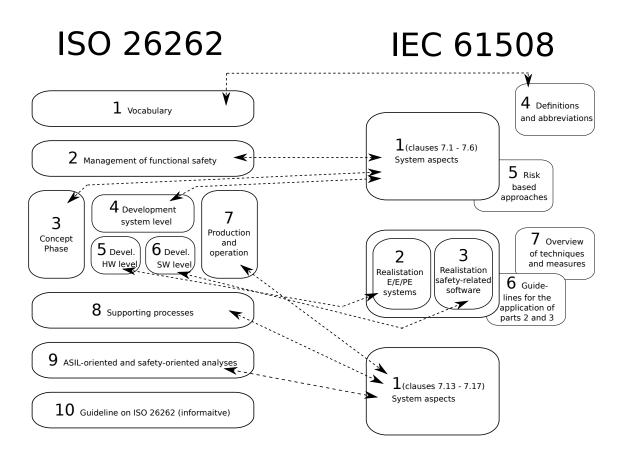

|   | 3.5                       | IEC 61508                                        |  |  |  |

|   | 3.6                       | ISO 26262 Road vehicles – Functional safety      |  |  |  |

|   | 3.7                       | EN 50128                                         |  |  |  |

|   | 3.8                       | MISRA-C                                          |  |  |  |

| 4 | Safety Case 53            |                                                  |  |  |  |

|   | 4.1                       | Introduction to Safety Cases                     |  |  |  |

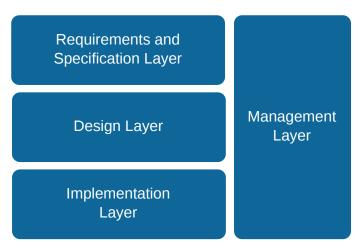

|   | 4.2                       | Implementing a Layered Safety Case               |  |  |  |

|   | 4.3                       | High-Level Safety Case    56                     |  |  |  |

| 5 | Implementation Details 69 |                                                  |  |  |  |

|   | 5.1                       | Assessment                                       |  |  |  |

|   | 5.2                       | Adaptation of the Build System                   |  |  |  |

|     | 5.3                              | Task Management                                | 76  |  |

|-----|----------------------------------|------------------------------------------------|-----|--|

|     | 5.4                              | Interpartition Communication                   | 78  |  |

|     | 5.5                              | Implementation Summary                         | 82  |  |

| 6   | Design of an Example Application |                                                | 83  |  |

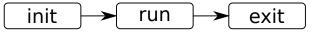

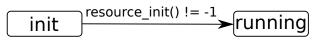

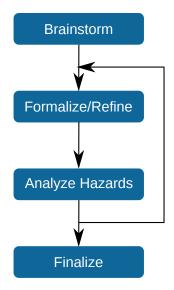

|     | 6.1                              | The Lifecycle of a Safety Critical Application | 83  |  |

|     | 6.2                              | Requirements Analysis                          | 86  |  |

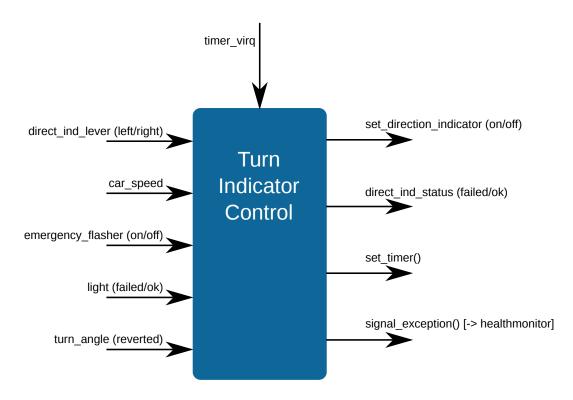

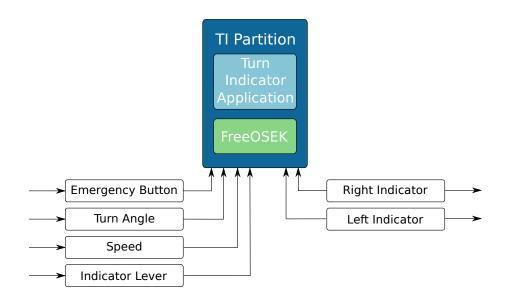

|     | 6.3                              | High Level Design                              | 87  |  |

|     | 6.4                              | High Level Hazard and Operability Study        | 91  |  |

|     | 6.5                              | Refinement of the High-Level Design            | 95  |  |

|     | 6.6                              | Detailed Design                                | 98  |  |

|     | 6.7                              | Risk Assessment of the Detailed Design         | 101 |  |

|     | 6.8                              | Design Summary                                 | 107 |  |

| 7   | Conclusion                       |                                                | 109 |  |

|     | 7.1                              | Summary                                        | 109 |  |

|     | 7.2                              | Conclusion                                     | 111 |  |

|     | 7.3                              | Future Work                                    | 112 |  |

| A   | Deta                             | iled Design                                    | 113 |  |

| В   | Cod                              | e Examples                                     | 115 |  |

| D   | B.1                              | xm hello                                       | 115 |  |

|     | В.1<br>В.2                       | xm_timer                                       | 115 |  |

|     | <b>D</b> .2                      | xin_umer                                       | 119 |  |

| С   | Pape                             | ers in the Context of this Thesis              | 123 |  |

| Bil | Bibliography                     |                                                |     |  |

| Int | Internet References              |                                                |     |  |

## CHAPTER

## Introduction

Modern cars already integrate applications of the same safety integrity level into one hardware node. The following chapter explains why it will be necessary to integrate applications of different integrity level into one hardware node in the future, and gives an outline of the goals and chapters of this thesis.

### **1.1 Motivation**

Today, the automotive industry strongly relies on software [1]. This need for more and more features stems on one side from the customer who expects a modern car to be equipped with certain features that improve comfort (e.g. navigation system, infotainment system with internet connection) and safety (e.g. ABS, ESP) and on the other side from the automotive industry which is on a journey to build autonomous driver-less cars [2] that are fully interconnected to each other (vehicle to vehicle communication - V2V) and to road side units (vehicle to infrastructure communication - V2I) via radio networks.

All of these features require a serious amount of computing power and a huge amount of program code. Currently, new features are added into vehicles by just adding another hardware node into the cars internal network. This led to the current situation were modern cars are basically highly distributed computer networks on wheels. To give a rough number, a modern higher class model contains about 70-80 hardware nodes [1].

A similar situation can be observed in the avionics industry, but there a trend to reduce the number of hardware nodes has already set in. As various articles in aviation magazines [Spi05,Ram07,Ada03,Mar06] suggest, there is a strong trend away from federated architectures towards integrated architectures (Integrated Modular Avionics - IMA), in the aviation community. Although this thesis is not targeting avionics, but automotive systems, most of the reasons why IMA is used in airplanes, are also advantageous for automotive systems. This similarity on an architectural level - not too surprisingly - can also be observed when looking at the proposed AUTOSAR architecture which correlates with the ARINC 653 IMA architecture. Furthermore, the avionics industry started to think about IMA a long time ago<sup>1</sup> and is designing and implementing IMA systems for quite some time now. Therefore a lot more information on integrated systems is available from the avionics industry than from the automotive industry.

The above mentioned advantages of IMA include - amongst others: significant weight reduction, a reduced power consumption, decreased hardware costs, reduced heat generation (and therefore simpler cooling), better utilization of modern CPUs, better scalability and higher flexibility. Additionally an IMA architecture allows better reuse of software modules and makes the software highly portable. This is especially important for safety-relevant software as it lends itself towards modular certification allowing the reuse of already certified components without the need of re-certification. In the past, those certification issues were not relevant for the automotive industry, but with the introduction of ISO 26262 [STA11a] this will become one of the major issues in the automotive industry.

The above mentioned applications that are using networks like V2V, V2I or an internet connection introduce a new set of security issues that are not immanent in the current closed networks of vehicles, although there are security issues in current implementations as well. The security aspects of OVERSEE are a very important step for the automotive industry. Security already is a big issue for today's vehicles, but it has to be considered even more stringent for future vehicles.

Recent shocking news on the deficits of security in the automotive sector have been the TPMS (Tire Pressure Monitoring System) [RMM<sup>+</sup>10] which is mandatory in the US since 2008 and became mandatory in the EU in 2012 for all new cars. This system incorporates embedded systems that are located on the inside of each tire and measure the tire's pressure. The measured value is then transmitted into the car using a radio transmitter, which according to [RMM<sup>+</sup>10] can be read and spoofed from entities outside of the vehicle very easily and thus be misused to track vehicles and/or communicate non-existent problems with the tire pressure to the inside of the vehicle.

A second example showing us how stringent security is needed in the automotive sector, is a paper of a group of researchers at the University of Washington, Seattle [KCR<sup>+</sup>10]. This paper explains how the authors were able to hack a car via the On-Board Diagnostics (OBD) interface - which is conveniently located somewhere (depending on the manufacturer and model of the car) under the dash-board or the console. Via this interface the authors were not only able to write messages onto the digital dashboard, but also to do harm, like e.g. deactivate the breaks during driving or flash the motor control, while the engine was running.

Integrated systems allow the implementation of better security mechanisms that are able to monitor the access point(s) into the car more efficiently. As already mentioned above, there is a number of advantages that is gained by the shift from federated towards integrated systems:

**Significant weight reduction** - due to the fact that the on-board systems network consists of fewer nodes and needs less wiring a significant weight reduction can be expected.

<sup>&</sup>lt;sup>1</sup>IMA has been used in jet fighters such as the F-22 or F-35 since the beginning of the 90's.

- **Reduced power consumption** a smaller number of CPUs that is better utilized should consume less power than a higher number of CPUs that is idle.

- **Decreased hardware costs** as the price difference between small microcontroller based systems and modern high performance hardware is not that big, a decrease in hardware costs can be expected.

- **Reduced heat generation/simpler cooling** a smaller number of hardware node does not require to pack them as densely and thus the heat generation will be reduced and cooling will be simpler.

- **Better utilization of modern CPUs** the performance of a modern CPU hardly justifies the use for one small application, leaving the CPU bored with a maximum utilization of few percent of its capabilities. Integrating several applications into one hardware nodes obviously leads to better utilization of the CPU.

- **Better scalability and higher flexibility** Using a virtualized environment, it is easier to add new applications in spare partitions and the abstraction of the network (form the view of the applications) allows to re-locate applications without any impact on the application itself, only the configuration files have to be adapted.

- Easy reuse / high portability of software modules as the software does only interact with the underlying layers via a well defined interfaces (examples could be ARINC 653, OS-EK/VDX, POSIX, etc.) the software can be reused easily in new platforms, as long as the needed interfaces are available. That means, the result is a highly composeable system.

- **Modular certification allowing** the reuse of already certified components without the need of re-certification is one of the main issues discussed in this thesis, and will be discussed later. Obviously a huge reduction in time and costs can be gained if is possible to avoid the time- and money-consuming process of re-certification.

- **Maintainability** maintenance can reach up to 90% of the total cost for a safety application, spending time and money in designing a system for maintainability will pay off in the long term.

While most of these advantages are inherent properties of an integrated system (e. g. reduction of weight) these advantages are of no value, if it cannot be shown that the integration of applications of a different safety integrity level does not impact safety of each individual application as well as the overall safety of the system. This of course cannot be shown generally and has to be part of the design and implementation of such a system.

Probably the biggest advantage of integrated systems, is the reusability of legacy code. Federated architectures make it hard to reuse legacy code, since very often the code was written for some old hardware platform which is not in use any more or for a legacy operating system that offered some weird non standardized interface to the application. All these problems are not existent for IMA systems using a standardized interface. An example for such an interface would be the one defined in the OSEK/VDX (Offene Schnittstellen für Elektronik in Kraftfahrzeugen/Vehicle Distributed eXecutive) specification. Being compliant to a standardized interface allows to run the application on every other operating system which is compliant to this API (Application Programming Interface), and of course it gets very easy to run legacy code on the newest version of the operating system, or on another OS that offers the same standardized API. The advantage is not only the easy reusability of the code, but code that has already been certified does not have to be certified again (as long as it is not changed).

The obvious downside of strong partitioning in time (achieved by static cyclic scheduling) is, that it obviously leads to a sparse timing which limits interaction with physical endpoints/devices. This results in the change of timing properties compared to physically concurrent distributed systems which may change the system behavior even if the components are unchanged. Depending on the application this change of behaviour may not be tolerable. Consider for example the control of the interior lights, an additional latency of 100ms to adopt new settings will not be relevant. On the other hand, an additional latency of 1ms will make a huge difference for the engine control where even few  $\mu$ s matter.

The major part of this thesis deals with the modular certification of software. In most available publications this is limited to the VMM (Virtual Machine Monitor) that assures the independence of the applications. Of course this thesis also discusses this part of the problem, but the focus is also set on how an application has to be designed and implemented to allow modular certification and really end up with an application that can be used over a long period.

### **1.2 Goals**

This thesis is tightly coupled with the OVERSEE project [3], a FP7 project funded by the European Commission. In short the goals of the OVERSEE project are to

- provide a single secure access point into the car,

- and allow the deployment of several independent partitions of different security levels on the same hardware node.

While safety has been descoped for the OVERSEE project, this thesis will look the safety aspects of the OVERSEE architecture. So the question this thesis is about to answer is, whether the hypervisor approach implemented in the OVERSEE platform is also suitable to fulfill the safety-requirements of the automotive industry.

This thesis also intends to make the industry aware of the advantages of open-source software and show that there is software around that is ready to be employed in safety-relevant software. While free/libre open source software (FLOSS) is entering more and more areas of computer science, (thanks to well known projects, like the Linux Kernel, the Apache Web server, the Firefox web browser or the OpenOffice.org office software suite) and is gaining more and more acceptance [PA08], there are still industries in which it is not seen as very attractive.<sup>2</sup>

One of these areas are safety critical systems, because companies still think that opening their source code will result in a huge disadvantage over rival companies. While this might be true for applications and some special libraries, this is definitely not true for "infrastructural" software, like the operating systems and common libraries. The effort to develop a modern operating system is a task which can only be solved by very few, huge corporations, and even for those the benefits of doing so are not existent.

There have already been several safety critical projects employing FLOSS software (e.g. a fire detection system by Siemens Building Technologies, using the Linux kernel [Ism08], a railway signaling system [PS08] as well as a railway signaling platform [AGS08]), and there is a growing demand for FLOSS software by the safety community, and in the air and space sector. Proof for this are e.g. that NASA is doing more and more open source projects [4], and also other space programs use FLOSS software (e.g. the DLR - Deutsches Zentrum für Luft- und Raumfahrt in their MAPHEUS-1 rocket).

### **1.3** Methodical Approach

To show that it is in fact realistic to design and implement a system with an integrated architecture, that fulfills these safety requirements, this thesis takes a look at the problem from two different angles.

First of all a high-level safety case for the system is constructed. This safety case is structured in layers to improve maintainability and allow reusability of the high level safety case without an impact on the applications.

Secondly the design and implementation of an application is considered. To show how a design for such a safety critical application, a real-world automotive application (an indicator control) is designed with modular certification in mind.

Apart from these more theoretical problems of integrated architectures and modular certification, on a more practical level it has to be shown that it is in fact feasible to run a current automotive application in such an environment. To do so an OSEK/VDX compliant <sup>3</sup> operating system is ported on top of the OVERSEE platform providing a well designed interface that is commonly used in the automotive industry. On top of that runtime environment an indicator control example is implemented.

<sup>&</sup>lt;sup>2</sup>The main problem still is the *Safety by secrecy* thinking that has to be abandoned. This paradigm has already been thrown over board by the security community a while ago, and is wrong for the same reasons for safety.

<sup>&</sup>lt;sup>3</sup>The chosen OSEK implementation has been reviewed by me, and not deviations from the specification could be found, e.g. all parts that have been implemented are likely to be fully OSEK/VDX compliant.

### **1.4** Structure of the Thesis

Chapter 1 already explained why safety is such a hot topic in the automotive industry, and why there is such a desperate need for a platform that is capable of satisfying the safety as well as the security needs of the industry.

Chapter 2 is going to summarize some of the important concepts and technologies this project is based on. Furthermore it not only compares them to other concepts not suitable but also states why those other concepts are not applicable to an application like this.

Chapter 3 gives an introduction the relevant standards one has to know if he wants to build a safety-relevant system for the automotive industry.

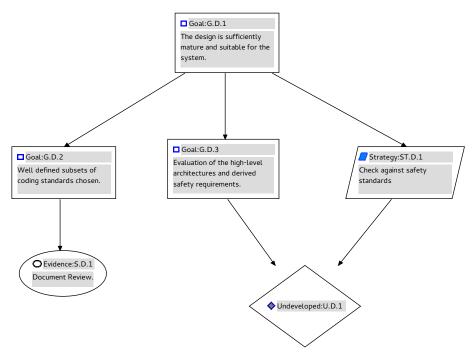

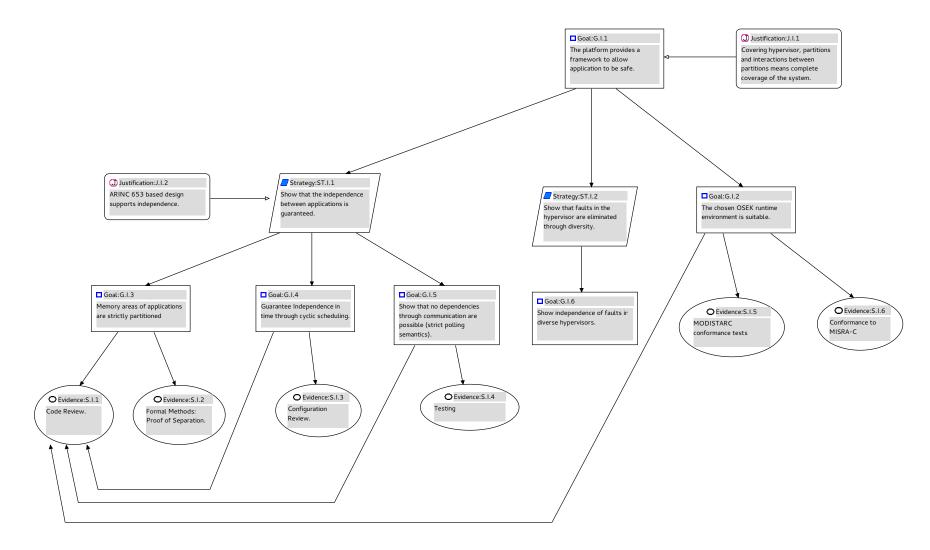

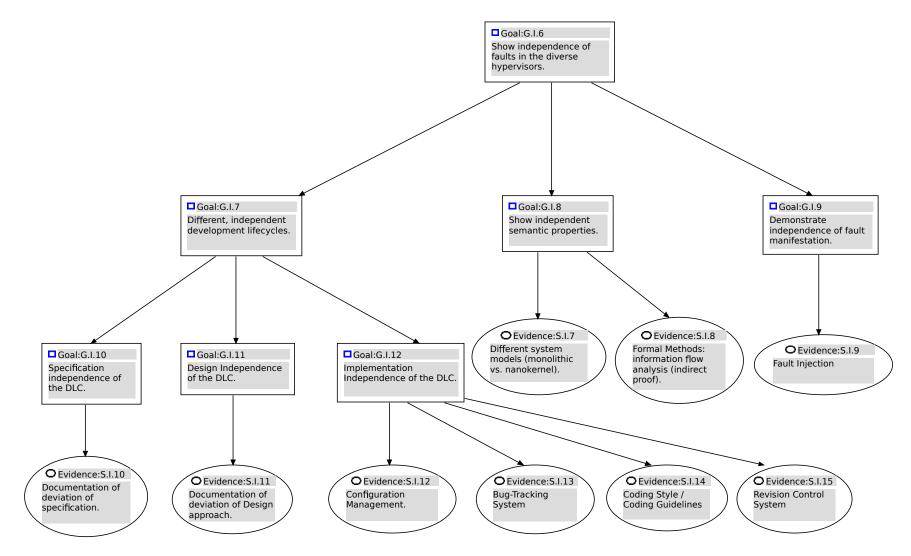

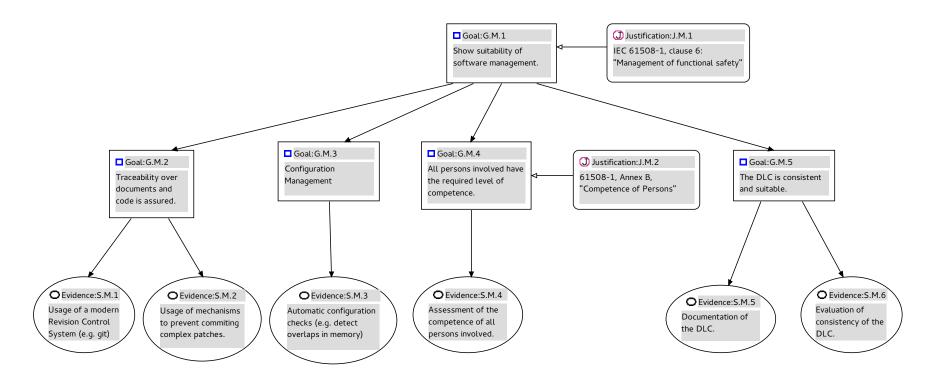

Safety Cases are used to argue the safety of a system in a structured way. In Chapter 4 a safety case for the OVERSEE platform is given. The safety case is structured using the well established goal structuring notation (GSN) and has additionally been layered to get an even better understandable, maintainable and re-usable argument.

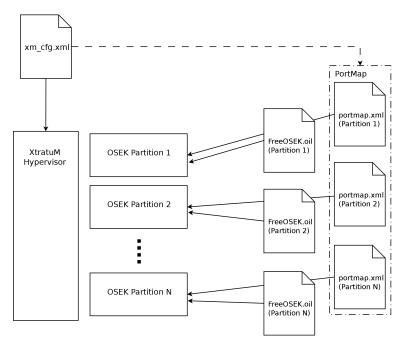

Chapter 5 starts of with the assessment of existing FLOSS implementations of the OS-EK/VDX specification and checks the feasibility of executing them in a XtratuM runtime environment. While the reuse of components is emphasized in the above introduction, no 100% fit may ever be expected. Some adaptations to the OSEK variant used was required as well as adaptations of the toolchain to integrate it into XtratuM. The steps for transforming FreeOSEK to a para-virtualized RTE on top of XtratuM is elaborated on in this chapter.

The design of applications to allow their reuse still is a major issue in the industry. In Chapter 6 a way how a simple indicator control application can be designed to assure reusability is shown.

The main part of this thesis is concluded in Chapter 7 where a summary is given, conclusions are drawn and a outlook to future work is given.

Furthermore, Appendix A contains the code defining the interface of the turn indicator example designed in Chapter6, Appendix B presents some simple OSEK compliant example applications runnable in the runtime environment and Appendix C contains a list of papers, that have been published in the course of this thesis.

# CHAPTER 2

# Concepts and Technologies

This chapter gives a short introduction to the concepts and technologies that form the basis for this thesis. These concepts and technologies range from operating system principles (Section 2.1) over virtualization principles in general (Section 2.2) to virtualization in safety critical systems (Section 2.3) to the difference between federated and integrated architectures in Section 2.4.

This is followed by a description of the tool-chain used for the practical part of the thesis as well as some thoughts on code quality and coding standards in Section 2.5. Last the notations used for the safety case (Section 2.6) and the design (Section 2.7) are introduced.

### 2.1 Operating Systems Classification

The following section gives an overview of the most important kernel architectures that are in use nowadays, and compares the properties of the different approaches that are relevant for this thesis.

### 2.1.1 Metrics of Classification

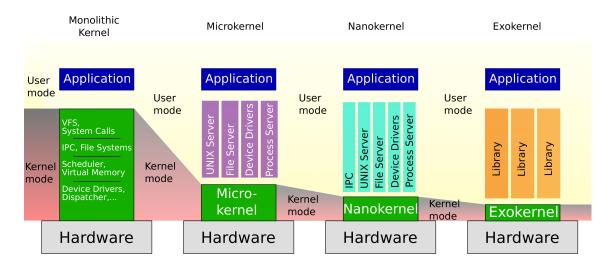

The three concepts (which are described in more detail in the remainder of this section) are compared in Figure 2.1. The order in which they are presented, is from left to right:

Size of the Kernel (in decreasing order) - One discussion coming up every time when two or more operating systems programmers come together, is the question of the size of the kernel - just think about the famous discussion on monolithic vs. microkernel between Linus Torvalds and Andrew S. Tanenbaum [5] - and what part should be in the core of the OS and what part should not. When safety comes into play as an additional factor, we also have to think about the implications that a larger code base makes for certification. While a smaller code base lends itself towards certification, there are strategies to handle big code bases as well.

- Level of Hardware Abstraction (in decreasing order) While hardware abstraction is one of the main duties in a monolithic architecture, the further right we move in figure 2.1, the less abstraction is provided by the OS core, and the more knowledge about hardware specifics is required of the application and library developers.

- **Size of Code Run in Kernel Mode** (in decreasing order) Modern CPU architectures can be operated in privileged and unprivileged modes (e.g. Ring0/Ring3 in the x86 family [6]). The different modes differ in the memory areas they are allowed to read/write from and the instruction set that is available. Generally, while in an unprivileged mode the instruction set is limited to a subset of the instruction set, and some privileged instructions cannot be used. Most OS only distinguish between kernel (privileged) mode and user (unprivileged) mode, meaning, that there are certain things that can only be done in kernel mode.

Obviously these three properties are either linked together very tightly, or exclude each other. The art is to find a way where the trade offs made in favor of one or the other approach are compensated by either technological means that allow to assure that safety properties are met, while still providing the convenient architectural properties (e.g. hardware abstraction) to the application developer.

While it is widely established that hypervisors for safety-relevant systems are small mirco- or even nanokernels, with a small code base is easier and cheaper to verify and certify, in the future also full featured operating systems could be used for hypervisors in the safety domain. In order to find out whether a monolithic approach like the one taken in the Linux kernel could be suitable for a safety-relevant system, the differences between those approaches have to be pointed out, in order to build the basis to understand the advantages/disadvantages of the properties, when it comes to safety assurance and certification.

Figure 2.1 gives a rough overview on the internals of the kernel architectures which is sufficient to illustrate the ratio between code executed in kernel mode and user mode in the four architectures.

As mentioned above, nowadays OS in the safety domain tend to be small (i.e. micro- or nanokernel approaches, often they still use no OS at all), since the verification, validation and certification of a smaller code base is already very expensive in effort, time and money, the use of huge monolithic OS seems to be not feasible - at least not with the safety assurance strategies that are used currently. Due to the high expenses in OS development, the question arises, whether an already existing OS could be used for the safety domain as well. This question is nothing new, we already experienced the same trend in the hardware area, where - back in the good old days - they had military grade (MIL) certified hardware that consisted only of expensive, high quality elements, operable in huge temperature ranges, under the harshest of environmental influences. Nowadays, this MIL certified hardware has vanished, and almost every domain is using COTS hardware even for applications where it has been unthinkable a decade a ago. The same might

Figure 2.1: Comparison of Kernel Architectures

happen to specialized software - at least a trend of companies pushing into this direction can be recognized, viewing some recent publications [AGS08, PS08].

### 2.1.2 Monolithic

As the name suggests, a monolithic kernel consists of one single piece. But rather than the kernel itself being one piece - usually it is possible to dynamically load/unload kernel modules at runtime, therefore the kernel itself is not really *"one single piece (mono) of stone (lithic)"*, but rather, in a monolithic kernel all parts of the operating system run in a single address space and as a single process (multi-threading is used in all modern monolithic operating systems though). This includes not only basic functionality, but also resource allocation and management systems (e.g. memory management, file systems, network stack), power management, interprocess communication (e.g. message queues, shared memory), and so on.

This design approach of running the whole OS in one address space, requires less encapsulation than would be needed in a microkernel approach, and therefore leads to a significant reduction of system calls and context switches leading to a performance increase.

In order to being able to handle a complex, monolithic OS that consists of millions of lines of code, rigorous logical and physical de-coupling of OS subsystems is needed. This is the reason, why object-oriented design patterns can be found in modern monolithic operating systems [7,8]. If such modular design patterns, assuring the independence of subsystems are not followed, the single address space approach can easily be misused and lead to unmaintainable systems. One negative example is Windows Vista, which can be called a very large software project without hesitation with its approximately 50 million lines of code. An Ex-Microsoft employee states in his blog [9], that:

"Windows code is too complicated. It's not the components themselves, it's their interdependencies. An architectural diagram of Windows would suggest there are more than 50 dependency layers (never mind that there also exist circular dependencies). After working in Windows for five years, you understand only, say, two of them. Add to this the fact that building Windows on a dual-proc dev box takes nearly 24 hours, and you'll be slow enough to drive Miss Daisy." [9]

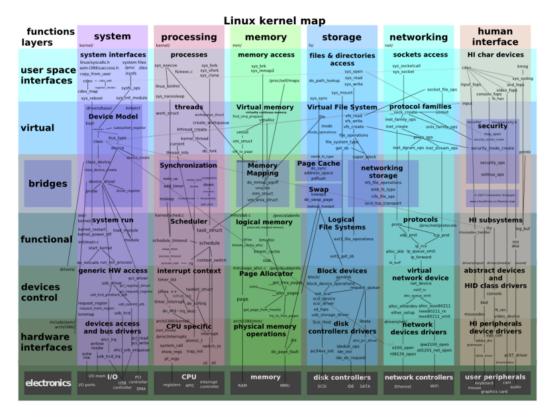

Since this statement is not verifiable and the example is a very bad one, we will now turn away from Microsoft and proprietary software and look at another monolithic operating system where the principle of de-coupling and cohesion works very well: the Linux kernel. Figure 2.2 shows an architectural map of the Linux operating system, with all its inter-dependencies. As you can see, there are only 8 dependency layers, and the inter-dependencies between the layers, as well as the inter-dependencies between the functions are not too many. Nevertheless, as this is a monolithic kernel, un-intended interference, outside of the intended interfaces is possible, but chances that someone contributing a patch that is calling around like crazy is getting away with that are very low, a very good explanation why it has to be done this way from the author would be necessary to convince the other developers.

At the moment, the Linux kernel consists of approximately 14.3 million lines of code (2.6.38). This sounds like a lot, but with Linux polymorphic configuration, this already includes the architecture specific code for all supported architectures (as of 2.6.38 there are 23 CPU architectures supported by the mainline kernel) as well as the device drivers that are part of the mainline kernel. Although this seems a lot, for a well configured, effective deployed kernel, this reduces to well under 1 million lines of code (a configuration with 2-3 file-systems, 5-10 drivers, networking and the common infrastructure will sum up to about 600k lines of code).

So how does this polymorphic configuration scheme work? At compile time you cannot only choose, which processor architecture you want the kernel to run on (and there are plenty of architectures Linux is running on, e.g. x86, x86\_64, arm, ppc, mips, sparc, alpha, blackfin), but you can also decide on many other things to be built into the kernel or not. You can in example decide on the scheduler (preemptive or not), memory model being used (flat or sparse), whether to use power management or not and which function of power management you want to use, you can decide on about 20 different file-systems, or if you need any tools to debug the kernel (e.g. tracers, profilers). You can also decide to build parts of the kernel as modules instead of directly linking them into the kernel. Theses modules can be loaded and unloaded dynamically at runtime, making the kernel highly modular. This configuration system is the key element, that allows to run Linux on basically everything from embedded devices like mobile phones [10, 11], over desktop systems [12, 13] up to supercomputers [14].

If you are interested in more detail, on how much lines of code are included between two releases, how many people are involved, which companies are involved, etc. in the development of the Linux operating system, then have a look at [GKH09].

Figure 2.2: Automatically generated architectural map of the Linux operating system. This image was published under a CC-BY-3.0 license, for details see http://commons.wikimedia.org/wiki/File:Linux\_kernel\_map.png

### 2.1.3 Microkernel

In a microkernel architecture, the amount of code executed in kernel space is minimized. This means, that the kernel itself only contains the most essential functionality, while the rest of the operating system is shifted into separate processes (ideally into user space), where it is handled by servers (sometimes also called translators [15]). For example, while memory allocation and protection would be handled in kernel space, memory management is already a task that is shifted into user space and has to be handled by a memory management server, in a microkernel architecture.

Since the opinions about what really is essential, diverge, there are several definitions about what a microkernel contains and how big a microkernel really is, but one element has been established over all definitions, namely that the Inter Process Communication (IPC) is part of the kernel, and that the key of a successful microkernel design is the IPC performance [Lie93, Lie94, Lie96].

But even the fastest of those IPC mechanisms pose a huge penalty on latencies, due to the

overhead introduced by the need for constant switching between user- and kernel-space. For this reason, most microkernel architectures do not run their servers in user-space, but in separate processes in kernel space. This approach makes you loose more or less all advantages gained from an microkernel architecture, and therefore is not desirable. Nevertheless, this approach has been implemented in several operating systems (e.g. Windows NT/Vista/7, Mach).

Microkernels are very popular in high security applications, where a Trusted Code Base (TCB) that is as small as possible is needed. A very well known example for this is the fully verified seL4 microkernel [16]. In comparison to the Linux kernel with about 600k lines of code in a actual deployable kernel, the seL4 kernel only consists of about 8700 lines of C-code and 600 lines of assembler code. Of course at this stage, the seL4 kernel is not of much use, and all the servers needed to get a system with similar functionality as the Linux kernel would result in a comparable amount of lines of code.

### 2.1.4 Nanokernel

The term nanokernel was first used in [BHF<sup>+</sup>92], but the intention there was a sarcastic side blow at the Mach kernel which calls itself a Microkernel while (due to some performance enhancing opitmizations) actually being more monolithic. In contrast to a microkernel, a nanokernel is more a HAL (Hardware Abstraction Layer) than an operating system, essentially resulting in a small layer that is able to monitor and control the applications running on top of it. Often these applications tend to be full grown operating systems, making the nanokernel a VMM (Virtual Machine Monitor), that provides only hardware abstraction, monitoring, and protection from other applications to the guest OS. Since the definition of a microkernel is that *i*t includes everything that is really essential, we could say that a nanokernel contains even less [17]. This in fact is true, but this does not mean that a nanokernel is in any way incomplete, but the concept is a totally different one.

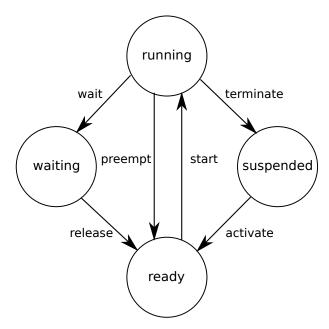

A nanokernel contains everything that is necessary to multiplex multiple runtime environments. Basically this is just memory protection, scheduling of the runtime Environments (RTEs) and interrupt virtualization. Everything else - including IPC - is shifted into one or multiple RTEs. While the this definition of a nanokernel is the one most widely in use, there are also other uses for it, e.g. [MK00] uses the term nanokernel for a kernel that supports timers with a nanosecond resolution.

Others call their operating systems nano-, pico-, atto-, ... kernel to emphasize the small code base, but most of them are not exceptional small, and from the functional point of view they clearly should be called microkernel.

### 2.1.5 Exokernel

The idea of exokernels [Eng98, ?] was developed at the MIT (Massachusetts Institute of Technology) around 1994. The main design principles of this operating system architecture, are to keep the kernel itself very small and to force as few abstractions as possible on the application developer.

While previously discussed operating system architectures try to abstract the hardware as much as possible (e.g. file systems, sockets for network communication), making it as transparent to the application developer as possible (e.g. "Everything is a file" in Unix), in the exokernel architecture, as few hardware abstractions as possible are introduced. This of course makes it harder to write an application, since the application developer is forced to do much of the low-level programming himself. Of course this approach avoids the layering introduced in all the other architectures, resulting in a better performance (note that scenarios with this performance gain are very unrealistic on modern multi-core systems).

The exokernel itself is, as mentioned above, very small and in principle only checks if a hardware resource is allocatable to an application (i.e. that it is free and the application has the permissions to allocate it), but there are no abstractions forced on the application programmer. An example would be an application that reads and writes to an hard disk. The exokernel only checks if the application has the permissions to read/write that part of the disk, but it does not force the structure of the data on the application (i.e. no file system). This principle of not abstracting resources allows different applications to use their own drivers. In example, it would be possible for two processes to use two different implementations of the TCP/IP stack to send messages via the network. Libraries are used to implement the different drivers and abstraction layers, and make them accessible to the applications. This is possible because the exokernel only provides rrawinterfaces, that can be used by the libraries to provide more abstract interfaces for the application.

Until now, two exokernel operating systems have been developed at MIT: Aegis and XOK. Both of them are explained in detail in [Eng98]. While Aegis is a proof of concept with limited support for storage, the exokernel principle is applied more thoroughly in XOK.

### 2.1.6 No Kernel at All

The classic approach of having no OS at all, and running the application directly on the CPU, managing the resources on its own can still be found (actually more often than one would guess), but eventually it is going to die out. The reasons for the extinction of this ancient species are simply the ever increasing complexity of modern CPUs, making it harder and harder to handle them without a full grown OS, the demand for more and more features provided by the applications that can often not be satisfied by running everything in a single while(1) loop and of course the portability issues of applications that are interacting with the hardware directly. Operating systems give us the abstraction needed by application developers to write portable code. If there is no OS, porting the application to a new platform is somewhere between hard and not possible at all.

### 2.1.7 Conclusion - Which is the Best Architecture

The question of "Which architecture is the best?" actually has a very simple answer: this really depends on your needs of your application. From a performance point of view, monolithic kernels are definitely the winner, the difference in the overhead of just doing a function call over invoking a microkernel's complicated IPC mechanisms and switching between user- and

kernel-space is too big to get comparable performance on a Microkernel architecture. The only way to get a microkernel based design close to the performance of an monolithic approach, is by *cheating* and running the server processes in kernel-space as well and thereby invalidating the microkernel paradigm of minimizing the code run in kernel-space.

For modern multi-core and multi-processor systems, the performance advantage of monolithic operating systems over microkernel based operating systems has proven to be even greater, but with the growing number of CPUs new problems arise and to scaling current operating systems to higher numbers of cores new approaches will have to emerge. One such approach might be to have a small operating system (micro- or nanokernel) that is doing few things well, and the RTEs running on top of that small kernel are full-featured monolithic operating systems pinned to different cores loosely coupled to each other, communicating through inter-domain communication mechanisms (e.g. for safety-critical and safety-relevant systems, such mechanisms could follow the design principles of the ARINC 653 interpartition communication - see section 3.2 for details).

From a safety point of view, the approach taken by many operating systems, is to have a small kernel (the nanokernel approach) that is easy verify-able due to its size, but contains merely a HAL as protection of the runtime environments in time and memory (see 2.4 IMA - Integrated Modular Avionics). Since the purpose of theses systems is to integrate multiple applications, that were running on multiple CPUs before, into one hardware node, the communication between those RTEs is loose and with relatively small throughput (since in an federated architecture it has probably been running over a CAN bus or something similar) even a relatively slow IPC mechanism is faster than the network connection used in an federated implementation before.

### 2.2 Virtualization

Virtualization is a technique that has already been in use since the 1960s [18], but which got very popular over the last years. The maybe most important example where virtualization is in use is server hosting. Since most web-, mail-, ... servers do not need the resources provided by a modern computer system<sup>1</sup>, server hosting companies tend to run several servers on one computer system. Since each of them is rented to another costumer, it is necessary to make sure the administrators of the servers do not bother each other, and it is also essential, that if one server is hacked, the others are still secure. This basically is what virtualization systems do: they allow to run several guest systems on one hardware node and assure, that these guest systems are separated from each other appropriately. For the users inside of the virtualized environment it looks like they are working on a real hardware node.

From this short summary of main employment scenarios it becomes obvious, that the main goal of virtualization is *separation*, to accomplish *independence* between runtime environments. For applications in the server market, this *separation* has to provide mainly independence in memory, to protect the data in one runtime environment from the users of the other runtime environment. Independence in time and a communication system that discourages the impact of

<sup>&</sup>lt;sup>1</sup>At least not all the time.

one runtime environment on the other one play a secondary role. Even if it is considered, this done on a quality of service level and not a strict separation level.

### 2.2.1 Full Virtualization

The big advantage of full virtualization is, that you can run the operating system of your choice without any further modifications, and the guest CPU architecture does not necessarily have to be the same as the host CPU architecture. QEMU as an example supports x86, x86\_64, ARM, SPARC, PPC, MIPS, MIPS64, m68k(Coldfire),... as target platforms (running x86 as host plaform).

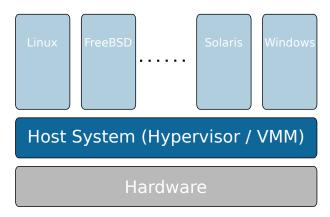

Since full virtualization allows to run unmodified operating systems, also proprietary systems can be installed as guest systems. An example how such an system could look like is given in figure 2.3, where the host operating system works as an VMM (Virtual Machine Monitor), sometimes also called hypervisor to run several guest systems. As you can see in figure 2.3, full virtualization allows us to run different operating systems like Linux, BSD, Windows, Solaris in parallel on the same computer system. The number of guest systems depends on the available hardware resources and can be up to hundreds of guest systems.

Figure 2.3: Full Virtualization

Full virtualization operates on the instruction level, and provides a specific CPU architecture to the guest operating system, by interpreting the single instruction. You can visualize this as a big switch-case statement with one case for each instruction of the CPU architecture. What the virtualization system does, is to fetch the next instruction, search the switch-case statement for the according function, which emulates the behavior of the respective guest.

Well known examples for a full virtualization FLOSS solutions are Virtualbox [19] and QEMU [20].

### 2.2.2 Paravirtualization

In contrast to a full virtualization system, a paravirtualized system does not operate on the instruction level, and the guest operating system has to be modified. This means, that the guest operating system is aware, that it is not running on real hardware and the boot process as well as the hardware specific functions are replaced by so called paravirtualized operations. Obviously, paravirtualization is restricted to guest operating systems, where the source code is available<sup>2</sup>.

Furthermore, the system is usually aware on which hardware architecture it is executed on, which is the same one as the hypervisor itself. <sup>3</sup> Examples for paravirtualized systems are KVM [21], XEN [22] and XtratuM [23].

### 2.2.3 XtratuM2 and its Hypercall interface

The remainder of this section is going to explain paravirtualization in greater detail, using XtratuM2 [23] as an example. The reasons why XtratuM2 was used in this thesis, is that it is the hypervisor chosen by the OVERSEE consortium. The main reasons why it was chosen as basis for the OVERSEE platform are that it is very small, accessible to everyone (it will be released under an open-source license) and it is staying close to an operating system specification that is very well known in the safety community (ARINC 653 - see section 3.1 for details).

XtratuM is a type I (bare metal) hypervisor targeting safety related composable systems. The main guidelines for design come from one of the key IMA standards, ARINC 653 [Com03]. XtratuM is an active FLOSS project being developed at Instituto de Informatica Industrial, Universidad Politecnica de Valencia. While the OVERSEE project is focused on security aspects the goal is to provide a platform that in principle can also satisfy safety requirements. There is a strong sharing of core demands on the lowest OS layer with respect to safety and security, and while safety and security have sometimes conflicting demands at higher levels these differences are not present at the lowest level of a hypervisor [Rus99]. The key to unify the requirements at the lowest level of safety and security is to provide a sound:

- Temporal isolation

- Spatial isolation

allowing to build high-level services on top that only allows explicitly permitted sharing of resources as well as communication. XtratuM thus is intentionally reduced close to the bare minimum that is needed to allow high-level services to operate in there respective OS environments and still give strong guarantees with respect to independence.

XtratuM offers a relatively narrow interface of Hypercalls to its partitions. This simplified things a lot for our porting efforts. In this section we will only briefly outline hypercalls that were used in this porting effort, for a full list of available hypercalls we refer you to the XtratuM

<sup>&</sup>lt;sup>2</sup>Of course the owner of a proprietary OS could paravirtualize it.

<sup>&</sup>lt;sup>3</sup>At least the author would see little sense in paravirtualization if the architectures are different.

Reference Manual [MRC11]. The intention of this section is to show the interface size used in the XtratuM guest management for a actual example.

- **Time services:** XtratuM provides an independent virtual time to each domain on which the guest-OS then can implement high-level timing services. In this sense the low-level services can be seen as mimicking hardware timing services.

- XM\_get\_time: Time entities in XtratuM are of microsecond granularity, and are maintained relative to the last system reset. There are two basic clocks in the system. Clocks in XtratuM are strictly monotonic. Clocks are maintained for the system (XM\_HW\_CLOCK) as well as for the partitions execution (XM\_EXEC\_CCLOCK)

- XM\_set\_timer: Interval timer service (providing one-shot behavior by setting the interval to 0). The expire time is an absolute time with respect to either hardware clock or execution clock. To a partition the expired timer is signaled as a virtual timer interrupt (emulating a hardware timer).

- **Interrupt services:** Signaling to partitions is provided via virtual interrupts, it is up to the guest-OS to then assign suitable meaning and response to the events. Note the absence of a interrupt request hypercall - as all resources are allocated statically in XtratuM there is no need for a request\_irq.

- XM\_enable\_irqs: globally disable interrupt delivery to this partition

- XM\_disable\_irqs: globally enable interrupt delivery

- XM\_set\_irqmask: used for masking (blocking) and unmasking of interrupts

- **Basic partition management functions:** Much of the partition management is related to the initialization and shutdown phase of a partition. The essence of the interface is that it minimizes the state information that needs to be handled by the hypervisor leaving more or less all state related work to the partition.

- XM\_suspend\_partition: This is a basic function that is only used in supervisor mode to manage a partition. It is used to block a partition (waiting on a resource) or temporarily stop a partition if errors are detected.

- XM\_resume\_partition: Simply the opposite to the above partition suspension.

- XM\_shutdown\_partition: As the hypervisor does not have information about the internal state of a partition shutdown is provided as an asynchronous notification. Basically a partition is sent a request to shut down via a dedicated interrupt and after cleaning up any internal state will then terminate it self.

- XM\_reset\_partition: Conversely to the XM\_shutdown\_partition, the XM\_reset\_partition is a forced shutdown of a partition whereby a warm and cold reset is differentiated, a warm reset preserves some of the partitions initialized resources (i.e. open ports and memory areas) while a cold reset clears this all and thus can have side-effects on other partitions via communication channels no longer being served.

- XM\_halt\_partition: A halted partition is set into an inactive state but no reclamation of resources (spatial or temporal) are done (that is left to the partition reset) in this state the partition is simply no longer scheduled by the hypervisor. The XM\_halt\_partition called by non-supervisor partitions can only pass self as the target of the halt.

- XM\_idle\_self: This allows a partition to suspend itself within its time slot. The partition will only be re-woken on its next time-slot or if a NMI is received within its current time slot. This can be used to implement donation schemes for system partitions.

- **Basic system management functions:** Note that these are not directly related to the guest-OS as these calls are related to privileged domains they are listed here for completeness.

- XM\_halt\_system: The halt partition call (also described above) is used by system partitions to manage the system as a whole as well as individual partitions. Only supervisor partitions can halt other partitions. This is used to prepare a partition reset as well as mode switching.

- XM\_reset\_system: Brute force system halt of the entire board after this only a hardware reset can reboot the system. No precautions are taken to put any partition into a sane state thus this is only the last step in a system shutdown as well as in extreme emergency situations.

- Low level Communication related functions: In practical implementations one does not actually use the low level object class functions but uses the wrappers provided to the commonly used objects (sampling and queuing ports as specified in ARINC 653). These wrappers thus are the actual hypercalls that will be issued though they are rarely used in guest-OS code.

- XM\_read\_object: read the object, verifying access permissions and other low-level properties. Usage in all reading functions like XM\_receive\_queuing\_message, XM\_read\_sampling\_message, etc.

- XM\_write\_object: write the object. This is used i.e. in XM\_write\_sampling / queuing\_message, XM\_send\_queuing\_message.

- XM\_ctrl\_object: is used to create and manage objects with specific properties as well as query these objects (i.e. retrieve the id of the object). This hypercall is used in object management functions like XM\_create\_sampling / queuing\_port, XM\_get\_sampling / queuing\_port\_status, etc.

While the overall hypercall set is a bit more elaborate than listed here, the essential calls used to implement the OSEK guest-OS are listed showing how small such a guest-OS interface actually can be constructed if the abstraction level is pulled down far enough.

### 2.2.4 A Formal Approach to Virtualization

So far only very practical approaches to virtualization have been mentioned. Of course there is also a theoretical approach to this topic. Especially when it comes to safety critical systems a mathematical approach to proving key properties of a system is desired. In [Rus82] John Rushby gives a *Proof of Separability*, for secure operating system kernels. Although his focus is on security, the separation properties discussed are key for safety as well.

Rushby begins by defining an abstract model of a computer:

$$M = (S, I, O, NEXTSTATE, INPUT, OUTPUT)$$

(2.1)

where M models a machine using the 6-tuple of S, the finite non-empty set of states this machine is able to take, I is the set of inputs, and O is the set of Outputs. While O is available continuously at every point in time, it can only be set once in the beginning. NEXTSTATE is a function that defines the transition between states, i.e.  $NEXTSTATE : S \rightarrow S$ , and  $INPUT : I \rightarrow S$  and  $OUTPUT : O \rightarrow S$  are functions to process input and generate output.

Furthermore, we have to consider a system shared by multiple users (otherwise there would be no need for security), this is done by defining C as a set of colors representing multiple users. Each of this users has his own input and output, which shall be secure and must not be leaked to other users in C. To indicate that, superscripts are used to indicate the user while subscripts are used to indicate the value at a point in time of S, I and O.

Next, Rushby gives a formal definition for security, the conclusion of which is:

"... each user of a C-shared machine must be unaware of the activity, or even the existence, of any other user: it must appear to him that he has the machine to himself." [Rus82, p.9]

Building on these basic definitions, Rushby then proofs that:

- **Theorem 1** A C-shared machine M is secure, if for each  $c \in C$ , there exists an M-compatible private machine for c.

- **Theorem 2** If M = (S, I, O, NEXTSTATE, INPUT, OUTPUT) is a C-shared machine and  $COLOUR : S \rightarrow C$  is a total function, then a private machine  $M^c = (S^c, I^c, O^c, NEXTSTATE^c, INPUT^c, OUTPUT^c)$  is M-compatible. (that is, the user c does not recognise the difference).

Theorem 3 Such an M-compatible machine exists for user c.

From those three theorems, Rushby derives six conditions for his security verification technique *Proof of Separability*:

" Using 'RED' as a more vivid name for the quantified colour c, these conditions may be expressed informally as follows:

- When an operation is executed on behalf of the RED user, the effects which that user perceives must be capable of complete description in terms of the objects known to him.

- When an operation is executed on behalf of the RED user, other users should perceive no effects at all.

- Only RED I/O devices may affect the state perceived by the RED user.

- *I/O devices must not be able to cause dissimilar behaviour to be exhibited by states which the RED user perceives as identical.*

- *RED I/O devices must not be able to perceive differences between states which the RED user perceives as identical.*

- The selection of the next operation to be executed on behalf of the RED user must only depend on the state of his regime." [Rus82, p.15]

The restrictions made by this list of conditions is, that it requires total isolation between the runtime environments (or regimes, as Rushby calls them). In a real-world application some form of communication between runtime environments will be required.

### 2.3 Virtualization in the Safety Domain

Although most virtualization solutions focus on Server applications, virtualization is also interesting for embedded and safety applications. The reasons for this are, that if you have a hypervisor or VMM (virtual machine monitor), that is very small (few lines of code), chances are good that it is relatively easy to assess. If you have such an hypervisor that has been approved by the authorities, it makes it very easy to build your system on top of it, since the application partitions are independent of the hypervisor and of each other, assessing them becomes easier too. The other big advantage is, that the reuse of legacy code becomes much easier and at the same time the development and integration of new applications can be done faster.

In this section, the different levels of virtualization are introduced, and some examples for each level are given. There are various reasons why virtualization is becoming more and more popular:

- Better utilization of hardware resources is achieved, if more applications run on one big computer, instead of several smaller ones.

- To secure a computer system. This technique is called sandboxing [24].

- Software development if you write a new piece of software you can first test it on a virtual machine, the advantage is, that you don't crash your real hardware, and some of the virtualization systems allow you to debug the guest systems (e.g. QEMU provides a gdbserver).

- NooM (e.g. TMR) systems can be done in a virtualized way, to prevent CCF's in the application

- In safety critical systems, virtualization is used to keep independent applications from influencing each other.

This last point the above list, is exactly what an IMA (integrated modular avionics) does, and it is the reason why different virtualization approaches are explained, and examples of virtualization software are given. The IMA approach and its advantages will be discussed in more detail in section 2.4.

### 2.4 Integrated Modular Avionics

At the moment, most safety-critical and safety-relevant software is based on a federated architecture, but in recent years there was a shift towards integrated architectures, and there are some examples - most out of the avionics industry - that use such an integrated architecture. This section explains the difference between a federated and an integrated architecture and lists some real world examples which use an IMA software architecture. After that a short rational why the integrated approach is also interesting for applications other than avionics is given.

### 2.4.1 Federated Architecture

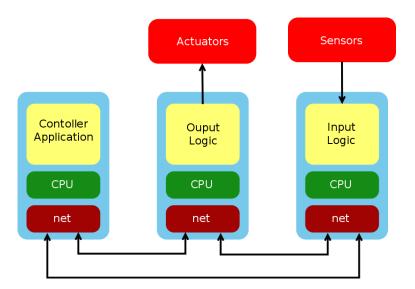

Today, most automotive systems in operation follow a federated approach. This means, that they have one node for each software module. This makes many things easier. E.g. the FCU's (fault containment units) can be identified easily - usually an FCU is one node. The downside is, that a federated approach leads to a highly distributed system very fast, and even relatively simple applications need many processors. One simple example - originating in [Wat06b, Wat06a, CBW07] - of a federated system is shown in figure 2.4. This example could be a simple control application, where one node is reading data from some senors, based on this data a new set value is calculated by a controller located on a second node, and the new set value is applied to the effectors by a third node. In order to get data required by the nodes out of one and into the other, a communication network is needed. To get a fast responding controller with a tight control loop, it is necessary to have a high speed communication network

As you can see, this very simple example already needs three CPU's. One CPU to read the sensors, one to calculate the set value, and one to operate the effectors. Running this application on three modern CPU's would be a waste since none of the three tasks uses even 1% of the CPU power of a modern CPU. So it would be nice to find a way to integrate the three parts of the system into one CPU, and not only achieve a better utilization of the CPU, but also save hardware and reduce the power consumption.

Figure 2.4: Simple example of a Federated System

### 2.4.2 Integrated Architecture

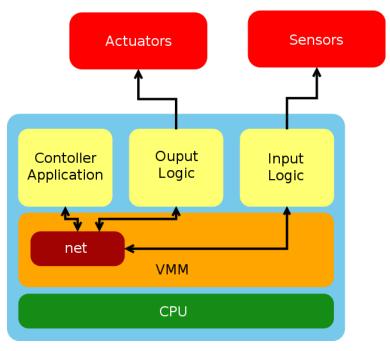

In contrast to a federated architecture, the integrated approach allows several independent parts of the software to reside in one hardware node. Figure 2.5 shows our simple controller application designed in an integrated manner, running input logic, controller and output logic on one common CPU. So instead of three bored CPU's we were able to reduce our hardware to one bored CPU. Furthermore the network connecting the three nodes is replaced by a virtualized network, increasing the savings even further.

Of course it would now be possible - depending on the application - to take further advantage of our integrated approach. Let's for example assume, that our controller is controlling the motor of a CNC mill, then our CNC mill would have 3 such controllers (one for each axis), meaning that a federated approach would require 9 hardware nodes to get the job done. With our integrated approach, all 3 controllers could be located on the same node, thus allowing a massive saving in hardware. But these savings in hardware are only the most obvious advantages here is a list of the most important advantages of integrated architectures:

- Weight reduction: Reducing might not be the biggest problem in the automotive industry (unless you are designing sports cars), but a weight reduction of course is also of advantage when it comes to fuel consumption

- **Reduced power consumption:** Inherent to the reduction of nodes is a reduction of power consumption.

- **Decreased hardware costs:** Modern COTS CPUs already are in the same price-range as special purpose microcontrollers. Sparing CPUs therefore will reduce the hardware costs.

Figure 2.5: Example of an integrated architecture.

- **Reduced heat generation:** In some industries (notably avionics) cooling can get an issue when lots of nodes are packed in a very tight space. Reducing the number of nodes in that space simplifies cooling, or might even eliminate some of those problems.

- **Better utilization of modern CPUs:** With the availability of very chip high performant CPUs, many nodes in a modern vehicle are utilized at few percent of their capabilities. Integrating applications into the same HW node will increase the utilization of the individual node.

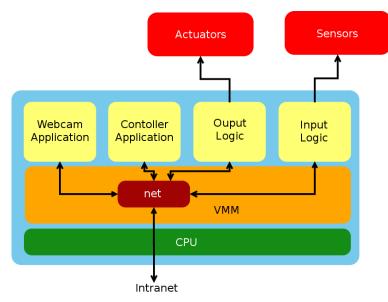

- **Better scalability / higher flexibility:** It is questionable if the increase in applications will come to an end any time soon. Having platforms that support the integration of new platforms are the key to increase the flexibility and get systems that scale well even if applications that we cannot even think of today have to be integrated into future systems. In example, consider the above discussed example. At some point a costumer could require to add a webcam to visually monitor the system. In a federated architecture, this would require you to introduce a new hardware node into the system, despite the fact that the available nodes have the resources (e.g. CPU time left, USB ports for the camera etc.) available. If an integrated approach had been taken from the very beginning, the system in figure 2.5 can easily be extended by a new application container and extended by the webcam application, depicted in figure 2.6

- **Better reuse of software modules:** The development of applications for the automotive industry is very expensive, thus a the desire to reuse applications is very high. Having an

integrated architecture with well defined interfaces that eliminates the hardware dependencies of the application itself helps to increase the reusability of newly developed as well as legacy applications.

**Increase of application portability:** In order to increase the reusability portability is a cructial pre-requisite. Of course writing highly portable code is a lot more initial effort,

but it will pay off in the long term.

- **Communication capabilities:** Integrated architectures not only allow to dynamically add applications, but also to add communication channels as desired.

- **Security:** Although security is often neglected in safety critical systems, it will become very important in the future. That said, virtualized (interpartition) communication is easier to protect than wired internode communication.

Figure 2.6: Example of an integrated architecture with an additional application

## 2.4.3 Related Work

In the following a short list of operating systems and applications that follow the IMA approach is given.

#### 2.4.3.1 Integrated Modular Avionics Operating Systems

The following list of OS that are following the IMA paradigm shows, how diverse the implementations can be, and how various approaches for the OS can be ranging over all the classes in 2.1.

- **POK:** the *partitioned operating system* [25] is an ARINC-653 compliant microkernel, that focuses on safety and security. POK has emerged from teaching activities at different schools and universities and is licensed under a BSD license.

- **XtratuM:** is a mostly ARINC 653 [23] compliant <sup>4</sup> hypervisor based on an nanokernel architecture. While the first version was strongly dependent on the Linux kernel (initialization of the hardware), XtratuM2 is already standalone and can be used without Linux, although Linux can be run as a guest inside of one or multiple partitions.

According to the homepage XtratuM is licensed under the GPL, but only version 1 can be downloaded directly at the moment.

- **VxWorks:** WindRiver's VxWorks [26] is a proprietary real-time operating system. It is widely used in smaller electronic devices (e.g. digital cameras), and there is also a ARINC 653 extension available, which has been used in many air- and space applications (e.g. Mars pathfinder mission) as well as in other mission critical and safety related applications.

- **Integrity:** Greenhill offers another ARINC 653 compliant operating system named Integrity [27].

#### 2.4.3.2 Applications

The IMA approach has first been used in avionics in the fourth generation of jet fighters. Examples are the Lockheed Martin F-22 and F-35, as well as Dassault Aviation's *Rafale*. More recently, IMA has found its way into civil aviation. Two very well known modern airplanes using IMA technology are the Airbus A380 and the Boeing 787. Although they both use IMA, the approach taken is very different [Ram07], as we will see in the following.

While the A380 integrates only few applications into one LRU, the approach taken in the 787 is a lot more radical, and uses a Common Core System (CCS), which integrates over 100 LRUs into one hardware node.

#### 2.4.4 The Integrated Approach Outside of Avionics

This thesis uses a lot of examples from the avionic sector, since the concept of integrating several software modules into one hardware module is already accepted in avionics, while other industries currently have not concept comparable to IMA. Although it can only be speculated on the reasons for this, it is obvious that integrated architectures would make a lot of sense in many applications. For example railway signaling, where lots of ECUs could be merged into one big TMR server, or machine controlling where e.g. all axis of CNC mill could be controlled by a single ECU.

With AUTOSAR [28], the automotive industry already started using the integrated approach, and the trend can be expected to go towards integrated components inside of vehicles very quickly. Of course one example for the research into the suitablity of integrated architectures in automotive is the OVERSEE project [3], and as we will see later in chapter 4, also ISO 26262

<sup>&</sup>lt;sup>4</sup>Actually its ARINC 653 with extensions.

mentions the concept of integrated architectures, allows the usage of multiple applications of different integrity levels if separation is guaranteed and suggests runtime environments that are compatible to ARINC 653.

# 2.5 Toolchain - used tools

One of the first things to do in the development phase of a safety critical software project, is to select the (subset of a) programming language(s) that shall be used as well as the used tools. Furthermore the suitability of the selected languages and tools for the given application has to be shown. A very short summary of the selection used in this thesis is giving in the following.

#### 2.5.1 Language Selection

In order to being able to select the toolchain, first a language has to be selected. In this case a long language selection process and discussion of the same can be skipped, since the language is inherent, due to preexisting code. From the XtratuM nanokernel itself to all OSEK OS implementations that were investigated in this thesis, the C programming language is used. Furthermore, C is in wide usage in the automotive industry, but to meet the high quality demands of the industry some restrictions are made. These restrictions are standardized and published in the MISRA-C:2004 [MIS04] coding guidelines.

In the practical part of this thesis not only MISRA-C compliant code will be written, since in some parts, this would not make sense. E.g. potential necessary changes (if any) in the XtratuM2 nanokernel will not be MISRA-C compliant. For the OSEK RTE as well as the example applications MISRA-C compliance is the goal, but lacking a MISRA checker it will not be possible to prove the compliance. The code in the OSEK RTE on the other hand will be MISRA-C compliant, as the current standalone implementations are MISRA-C compliant as well current standalone implementations are MISRA-C compliant as well.

The restrictions in MISRA-C are mostly dedicated to the avoidance of uncertainties in the C programming language itself. Such uncertainties, also called *undefined behavior* [29, 30], are differences in compilers that arise due to inaccurate specifications in the C programming language itself, and many experts in the safety domain criticise C as unsuitable for safety applications due to this undefined behaviour. The reasons why C is still a valid and good choice for safety critical and safety relevant software are:

- **High Availability** Compilers for the C programming language are available for almost all computer architectures and platforms on the market. Therefore, porting the system to a new architecture is a lot easier.

- **High Performance** Modern C compiler optimize the code, making it faster and more efficient than an human written assembler code could be.

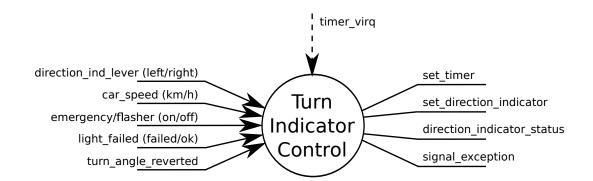

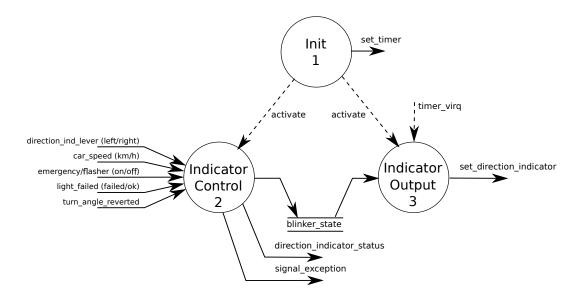

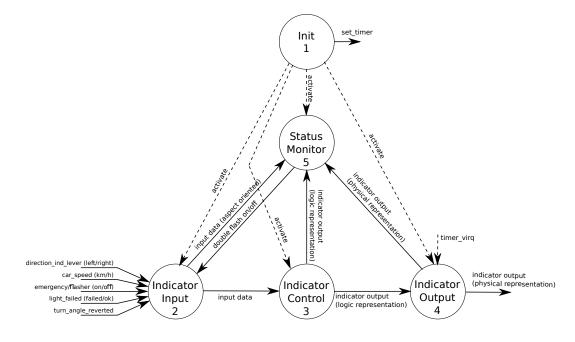

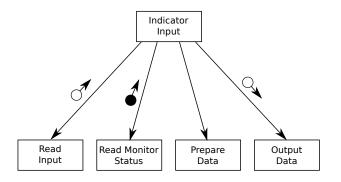

- Low Complexity The C programming language allows structuring of the Code, making it better readable and therefore better maintainable. Of course it is always possible to write