an der

# Online Test Vector Insertion – A Concurrent Built-In Self-Testing (CBIST) Approach for Asynchronous Logic

#### **DIPLOMARBEIT**

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

#### **Technische Informatik**

eingereicht von

## Jürgen Maier

Matrikelnummer 0825749

| Fakultät für Informatik der Te                                 | echnischen Universität Wien |                                         |  |  |  |  |  |

|----------------------------------------------------------------|-----------------------------|-----------------------------------------|--|--|--|--|--|

| Betreuung: ao.Univ.Prof. DiplIng. Dr.techn. Andreas Steininger |                             |                                         |  |  |  |  |  |

|                                                                |                             |                                         |  |  |  |  |  |

|                                                                |                             |                                         |  |  |  |  |  |

| Wien, 12.08.2014                                               | (Unterschrift Verfasser)    | (Unterschrift Betreuung)                |  |  |  |  |  |

|                                                                | (                           | (====================================== |  |  |  |  |  |

# Online Test Vector Insertion – A Concurrent Built-In Self-Testing (CBIST) Approach for Asynchronous Logic

## MASTER'S THESIS

submitted in partial fulfillment of the requirements for the degree of

#### **Master of Science**

in

## **Computer Engineering**

by

## Jürgen Maier

Registration Number 0825749

| to the Faculty o<br>at the Vienna l | of Informatics<br>University of Technology         |                        |

|-------------------------------------|----------------------------------------------------|------------------------|

| Advisor: ao                         | o.Univ.Prof. DiplIng. Dr.techn. Andreas Steininger |                        |

|                                     |                                                    |                        |

| Vienna, 12.08.                      | 2014                                               |                        |

| Violina, 12.00.                     | (Signature of Author)                              | (Signature of Advisor) |

# Erklärung zur Verfassung der Arbeit

| Jürgen Maier                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Eschenweg 1, 2223 Martinsdorf                                                                                                                                                             |

|                                                                                                                                                                                           |

|                                                                                                                                                                                           |

|                                                                                                                                                                                           |

| Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwende<br>ten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit |

| einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet in                                                                                                |

| Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als En                                                                                                 |

| lehnung kenntlich gemacht habe.                                                                                                                                                           |

|                                                                                                                                                                                           |

|                                                                                                                                                                                           |

|                                                                                                                                                                                           |

|                                                                                                                                                                                           |

|                                                                                                                                                                                           |

|                                                                                                                                                                                           |

|                                                                                                                                                                                           |

(Ort, Datum)

(Unterschrift Verfasser)

# Acknowledgements

First of all I want to thank my advisor professor Andreas Steininger for introducing me to that very interesting and thrilling field of application and his guidance while working on this thesis. I also want to thank my dear colleague Stefan Mödlhamer, who helped to improve the quality of this thesis with his indispensable input. Last but not least I would like to thank Sandra Burin for her patience while checking the thesis for grammar flaws as well as my parents for their never ending support throughout my studies.

## **Abstract**

Testing electronic circuits during their operation in the field is mandatory to ensure correct functionality over a long period of time. To avoid fault accumulation test vectors have to be applied actively to the circuit under test, without disturbing the normal operation. In synchronous circuits this topic has been investigated thoroughly, however for asynchronous ones, a more and more emerging design paradigm due to its superior properties, only few test approaches are available. In this thesis a novel concurrent Built-In Self-Testing (CBIST) approach is presented, that is capable of testing asynchronous logic without interrupting the normal operation at any point in time. For that purpose the rather unproductive NULL-phase of a 4-phase communication protocol is replaced by dedicated TEST values, which are generated and analysed on chip. In detail two 4-phase input streams (user and test data) are combined to a 2-phase one, which is afterwards processed by the circuit under test and then split up into two 4-phase streams again. The units responsible for merging and splitting had to be implemented from scratch due to missing references in literature, both for the bundled data and completion detection communication style and in several versions, differing by their complexity and level of concurrency. The proposed test procedure has the advantage that the test data are independent of the user data and can therefore be defined already at design time. This yields several advantages, for example the possibility to test rather complex structures like cyclic pipelines. As our assessment shows, the price for the test approach in terms of increased hardware effort and additional delay is very moderate, especially for large circuits. For those reasons the proposed test approach is a good alternative if data processing must not be interrupted at all.

# Kurzfassung

Um zu gewährleisten, dass eine elektronische Schaltung auch über längere Zeit gemäß ihrer Spezifikation arbeitet, ist es zwingend notwendig, diese im laufenden Betrieb zu testen. Zur Verhinderung von Fehlerakkumulation innerhalb der Schaltung müssen Testvektoren aktiv an die zu testende Einheit weitergegeben werden, ohne natürlich die normale Funktionsweise einzuschränken. Für synchrone Schaltungen wurde dieses Thema schon zur genüge erforscht. Für asynchrone Implementierungen, die sich aufgrund ihrer zahlreichen Vorteile immer stärker verbreiten, sind jedoch relativ wenig Testmethoden vorhanden. In dieser Arbeit wird deshalb ein völlig neuartiges Testverfahren präsentiert, das es ermöglicht, asynchrone Schaltungen zu testen, ohne die normale Funktion auch nur ein einziges Mal zu unterbrechen. Zu diesem Zweck wird die eher unproduktive NULL Phase eines 4-Phasen Kommunikationsprotokolls durch dezidierte Testvektoren ersetzt, die direkt am Chip erzeugt und analysiert werden. Im Detail werden zwei 4-Phasen Eingänge zu einem 2-Phasen Ausgang kombiniert, der anschließend von der zu testenden Schaltung verarbeitet und am Ende wieder in zwei 4-Phasen Ausgänge aufgespalten wird. Die Schaltungen, die das Verschmelzen bzw. Aufspalten übernehmen, mussten komplett neu entwickelt werden, da in der Literatur nichts Vergleichbares gefunden werden konnte. Diese Einheiten wurden für die bundled data als auch für die completion detection Kommunikationsmethode in unterschiedlichen Versionen implementiert, welche sich durch ihre Komplexität und den Grad der Parallelität unterscheiden. Die vorgestellte Testmethode hat den Vorteil, dass die Testdaten komplett unabhängig von den Nutzdaten gewählt werden können, was es möglich macht, diese bereits im Zuge der Entwicklung zu bestimmen. Dies hat etliche Vorteile, so gewährt es zum Beispiel die Möglichkeit, sehr komplexe Strukturen, wie etwa zyklische Pipelines, zu testen. Wie unsere Analysen zeigen, fällt der Preis dieser Testmethode, ausgedrückt in zusätzlicher Hardware und Verzögerungszeit, sehr moderat aus, besonders bei großen Schaltungen. Aus diesem Grund stellt die hier präsentierte Methode eine gute Alternative dar, wenn die laufende Datenverarbeitung auf keinen Fall unterbrochen werden darf.

# **Contents**

| 1 | Introduction                                               | 1               |

|---|------------------------------------------------------------|-----------------|

| 2 | State-of-the-Art                                           | 3               |

| 3 | Background on Asynchronous Logic 3.1 Asynchronous Circuits | <b>9</b><br>. 9 |

|   | •                                                          |                 |

|   | ,                                                          |                 |

|   |                                                            |                 |

|   | r r                                                        |                 |

|   | $\mathcal{E}$                                              |                 |

|   | 7                                                          | -               |

|   | 3.7 Signal Transition Graph                                |                 |

|   | 3.8 Petrify                                                |                 |

|   | 3.9 Circuit Drawings                                       |                 |

|   | 3.10 Fault Types                                           |                 |

|   | 3.11 Circuit Characteristics                               | . 16            |

| 4 | Methodology                                                | 17              |

| 5 | Proposed Solution - Overview                               | 19              |

|   | 5.1 Introduction                                           | . 19            |

|   | 5.2 Approach                                               | . 20            |

|   | 5.3 Complete CUT Testing                                   |                 |

|   | 5.4 Single Stage Testing                                   | . 23            |

|   | 5.5 Transformation Blocks                                  | . 24            |

|   | 5.6 Implementation Styles                                  | . 26            |

|   | 5.7 Test Vector Generation and Response Analysis           | . 29            |

| 6 | Proposed Solution - Bundled Data                           | 31              |

|   | 6.1 4-to-2 Phase Merge                                     | . 31            |

|   | 6.2 Implementations of 4-to-2 Phase Merge                  | . 34            |

|   | 6.3 Enhancements                                           |                 |

|   | 6.4 2-to-4 Phase Split                                     |                 |

|   | 6.5 Implementations of 2-to-4 Phase Split                  |                 |

|   |                                                            |                 |

| 7   | Prop   | oosed Solution - Completion Detection | 49  |

|-----|--------|---------------------------------------|-----|

|     | 7.1    | 4-to-2 Phase Merge                    | 49  |

|     | 7.2    | Implementations of 4-to-2 Phase Merge | 52  |

|     | 7.3    | 2-to-4 Phase Split                    | 58  |

|     | 7.4    | Implementations of 2-to-4 Phase Split | 61  |

| 8   | Prop   | oosed Solution - Extensions           | 69  |

|     | 8.1    | Cyclic Pipeline                       | 69  |

|     | 8.2    | Storage Elements                      | 74  |

| 9   | Proo   | of-of-concept                         | 77  |

|     | 9.1    | Introduction                          | 77  |

|     | 9.2    | Implementation                        | 79  |

|     | 9.3    | Fault Detection                       | 80  |

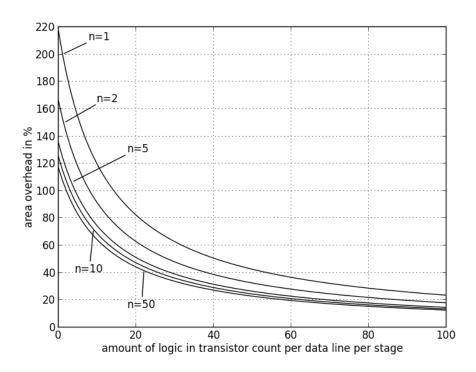

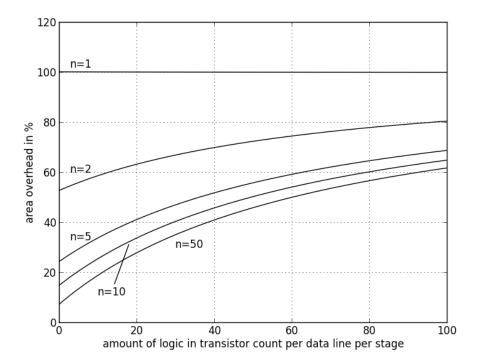

|     | 9.4    | Area Overhead                         | 81  |

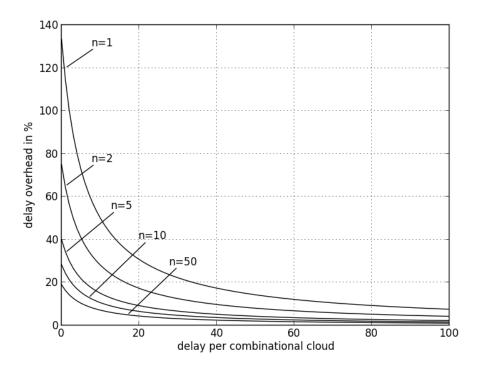

|     | 9.5    | Additional Delay                      | 89  |

| 10  | Criti  | ical Reflection                       | 95  |

|     | 10.1   | Analysis                              | 95  |

|     | 10.2   | Circuit Characteristics               | 98  |

| 11  | Cone   | clusion                               | 103 |

| A   | Glos   | sary                                  | 107 |

| В   | Code   | e                                     | 109 |

|     | B.1    | Petrify Library                       | 109 |

|     |        |                                       | 113 |

| C   | Pape   | er                                    | 121 |

| Bil | oliogr | ranhy                                 | 129 |

CHAPTER 1

## Introduction

Over the last few decades a tremendous shrinking of the feature size of electronic circuits has been observed, making it possible to implement more and more logic on the same die size. Together with the trends to higher speed and lower supply voltages [29] this leads to an increased sensitivity to disturbances, making it unreasonable to assume the correct functionality of a unit, once tested after fabrication, throughout its whole lifetime. The fact that more and more critical tasks, i.e. those where an unintended behaviour has severe consequence, are handled by integrated circuits drives the need to assure, that a unit is working along its specification. Some approaches, for example triple modular redundancy (TMR), are designed to tolerate a certain amount of faults. However, especially for long operation times, this yields several disadvantages, because it is commonly known that a TMR exhibits lower reliability compared to a normal approach, as soon as one replicate encounters a permanent fault [14]. For that reason test approaches are required that examine circuits and detect existing faults. A straight forward approach is to monitor input and output values of the circuit under test (CUT) and determine, if the output generated based on the inputs is valid or not. The big disadvantage of these methods is, that the test vectors are determined by the input data making it possible, that some parts of the circuit are not tested for a very long period, enabling fault accumulation [20, 29]. If all of these faults are activated later at once they may exceed the capabilities of the used fault-tolerance approach, which in general utilise the single fault model, i.e. they are able to handle one fault at a time. To prevent fault accumulation actively applying test values to the CUT during its normal operation becomes mandatory.

Asynchronous circuits are receiving increasing attention due to their superior properties compared to their synchronous counterparts [11, 12, 23]. In contrast to the latter ones no central clock is required to control the circuit, but instead the units inside communicate with each other by using handshake protocols. These are used to indicate the succeeding unit that new data are available or to tell the preceding one that the data have been processed and are not required any more. This mechanism makes the asynchronous design style event driven and timing much

more flexible, yielding an improved tolerance to process,voltage and temperature (PVT) variations. The main advantages, however, are that it naturally tackles the current problems with synchronous circuits, namely low skew clock networks and high power dissipation, due to its absence of a clock and the event driven working procedure. One important reason why asynchronous circuits, introduced already several decades ago, are not spread widely is their bad testability which results from the high level of concurrency. The fact that the single components of the CUT coordinate themselves results in a huge amount of possible states the system may be in, yielding a very high test effort.

The goal of this thesis is to tackle the bad testability of asynchronous circuits by implementing a novel online test approach, i.e. one that actively applies test vectors to the circuit under test during its normal operation. To achieve real concurrency the rather unproductive NULL-phase of a 4-phase handshake protocol<sup>1</sup> is utilised for testing. For that purpose the NULL values are replaced at the input of the CUT by dedicated TEST values and the resulting data stream is then processed. At the end the TEST values are removed again and checked for correctness, resulting in a unit, that uses the 4-phase protocol at its interfaces but the 2-phase one inside. In this thesis it is analysed what infrastructure is necessary to implement this test approach for the bundled data and completion detection design style together with a critical reflection on its properties.

Unfortunately the units inserting and removing the TEST values had to be designed from scratch due to missing references in literature. Several designs are presented in this thesis for these units, differing in complexity and level of concurrency. The circuit implementations are derived by designing the desired behaviour in a state transition graph (STG) and afterwards converting it automatically to a net list. To show the correct functionality of the approach a proof-of-concept implementation is used, which also states the basis for overhead considerations in the value and time domain.

This thesis is structured in the following way: In chapter 2 one will find a State-of-the-Art analysis of currently available implementations. In chapter 3 concepts as well as definitions used throughout the thesis are shortly described, followed by an overview of the used methodology in chapter 4. The chapters 5, 6, 7 and 8 then show the concrete implementation in theory, a proof-of-concept implementation, including an area and delay overhead analysis, is presented in chapter 9. Finally a critical reflection on and characterisation of the proposed test approach is carried out in chapter 10 followed by a final conclusion (chapter 11).

<sup>&</sup>lt;sup>1</sup>An explanation as well as additional information on these topics follow in section 3.

CHAPTER 2

## State-of-the-Art

Verifying that an electronic circuit is working according to its specifications is a well researched field in dependable computing. In this chapter existing approaches are presented, whereat two fundamental test methods are distinguished: concurrent checking and (online) testing. If the circuit under test has to be tested in the field it is crucial that no external units are required for testing, meaning that all necessary parts of the test approach have to be integrated on chip, also known as Built-In Self-Test (BIST). As one can imagine these approaches are of growing interest due to the increasing application of electronic devices in mobile applications. It would be unimaginable, if such a unit has to be connected to a separate test device to ensure its correct functionality. Many of the approaches shown in this section can be integrated as BIST approach, yielding more or less hardware overhead.

#### **Concurrent Checking**

Test approaches in this group observe the output and input of the CUT during its normal operation and determine, if the calculated result based on the input values is correct. To determine the correctness of the output values some kind of redundancy has to be introduced which however differs from approach to approach. One very favourable property of this procedure is, that it can be carried out completely concurrent to the normal operation, due to the fact that the input and output lines are only observed. In addition the results are available (nearly) in real time, yielding fantastic response times. This properties make these approaches very well suited to detect transient and intermittent faults (see section 3.10), however not for permanent ones. The reason is, that the test values, i.e. the input values, are not controllable, making it possible that certain parts of the circuit are not tested for a long time, implying the possibility of fault accumulation [20,29].

The above mentioned redundancy can be introduced in many different ways, for example in the space domain. For that purpose either the CUT gets duplicated or a unit carrying out the same functionality is implemented and connected to the same inputs. For error detection the outputs of both units are compared and if they differ an error has appeared [31]. Careful design of both implementations is advised to assure, that a fault is not present in both units, which would yield it undetectable. A very simple implementation for the additional unit is for example a lookup table realised by a storage element. This method works fine as long as both implementations do not produce identical errors, as outlined in [16], requires however a huge hardware overhead. In addition it is vulnerable to faults on shared resources like the clock signal. Researches have also discovered several shortcomings when used with asynchronous logic [41]. An even simpler approach also presented in [16] uses the additional unit solely to predict the parity of the output lines. This method however relies on the single fault assumption, i.e. that at a time only one fault exists. If a linear system, i.e. one having a linear relationship between input and output, has to be tested, the additional unit can be used to calculate the output analytically, as shown in [32].

A quite different approach uses codes for error detection. In detail the input lines are encoded leading to encoded output lines [20,26]. A fault is detected if the output value is not a valid code word, requiring additional data lines and therefore increased area. In addition the code has to be designed thoroughly, such that it is capable of detecting all modelled faults, which is a very challenging task. However it is possible that certain faults are only detectable by non-code words, making the approach incapable of detecting all faults, since non-code words will never be processed [18].

In addition to checking the logic values on the lines, [20] mentions the possibility to observe reliability indicators such as electric current, temperature, intermediate voltage, output activity and total dose to predict correct behaviour. By checking e.g. the power consumption it is possible to detect faults, that do not alter the output results, but for example increases the drained current [39], which may be a severe failure in modern low power applications. In addition it is possible to implement protocol checkers with this approach, assuring the correct temporal behaviour of a unit, due to the fact that CMOS circuits only consume power when they switch. A necessity for this approach however are current measurement units that are fast and precise enough for the given problem.

#### (Online) Testing

As mentioned before concurrent checking approaches allow fault accumulation. If even faults in rarely used parts of the CUT have to be detected reliably, as it is the case for units with long operation times, actively applying test vectors becomes mandatory. To detect a fault the output, like with concurrent checking, is investigated, with the difference, that the expected result can be precalculated. This makes it, at least in theory, possible, to check the semantic of the output signal and not just its syntax. Online testing, however, requires to interrupt the normal operation, implying a degradation of the delivered service. Therefore a proper integration of the test procedure yields a very big challenge. To assure efficient and fast error detection online test approaches are measured on the following quality criteria [14]:

- low performance penalty for the application

- high test coverage for a given fault model, determined by the quality and amount of test vectors

- low error detection latency, determined by the period required to apply the whole set of test vectors

Two fundamental properties have to be fulfilled by an online test approach:

**non-interference in time domain** The normal operation must not be delayed beyond the point that deadlines are missed. This can be assured by either including the test procedure into the schedule, which decreases the response time, or by making the test process preemptive [29]. For example is it imaginable to start the test procedure when the circuit is idle or at fixed points in time, independent of the current workload.

non-interference in value domain The internal state of the circuit must not be altered during the test. More specifically the first user data value that is processed after the test has finished must see the same environment as if it was processed right before the test. For that reason so called "transparent" test approaches are required, which restore the system state after they have been executed. [19] shows such a test approach for RAMs, where several operations are carried out on the data, eventually leading back to the original values (for example two times XOR). Another transparent approach is described in [1], where reconfigurable blocks in an FPGA are tested before configuration.

Most online test approaches use two distinct operation modes: In the normal mode the circuit processes user data and forwards the achieved results, whereas the test circuitry sleeps. Only after the circuit switches to the test mode, in most cases realised by an input line, the inputs of the CUT are redirected (for example by MUXes) to the test vector generator and the outputs to the test response analyser. The purpose of the latter is to compare the received results to the expected ones and indicate an error if they differ. It would of course require lots of memory to store the response to each single test vector, therefore so called compactors are used that generate unique values based on the received results [23,25,27]. Concrete implementations can be found for example in [17,21], which mainly differ in the way the test vectors are generated and analysed. Please note, that for certain approaches the test response analyser, i.e. the compactor, can be replaced by a checker [12]. As mentioned testing is only carried out when the circuit is in the test mode. When and how long it enters that state largely depends on the specific application and has to be determined at design time.

A different approach, called scan chain test, uses the internal storage elements to set the CUT to a specific state. Therefore all internal storage elements are connected to a linear chain, making it possible to shift the desired setting into the circuit under test. After the state was set, normal operation is started, but only for a very short amount of time. Afterwards the connected

storage elements are read out in the same fashion as before and the received state is compared to a reference value. This approach makes it possible to test each imaginable system configuration making it a very extensive test method. The downside is, as one can imagine, that it takes quite some time to shift in a new state and afterwards shift out the result. This implies that the normal operation also has to be interrupted for a long time. Furthermore in general additional devices are required to compare the resulting state to the intended one, making it not well suited for online testing. For synchronous circuits the amount of steps the test approach carries out can be controlled very well by the clock signal, which however is not available in asynchronous ones. Therefore the integration in these is a lot harder, but has already been achieved in several approaches [2, 23, 37].

Due to the dramatic shrinking of transistor sizes more and more logic can be placed on a single chip, making it possible to implement general purpose processors in embedded applications. This yields the possibility to shift testing to a higher level of abstraction, i.e. into the software domain, also called Software Based Self Test (SBST) [22]. In this domain complementary test methods are possible: A test procedure especially designed to activate every part of the chip is run from time to time and the generated results are analysed. The main difficulty in this case is the development of that specific test procedure. Of course also non-interference in the time domain has to be assured, which however can be implemented by using the scheduler of the processor [3]. Redundancy can also be introduced in the time domain, for example by double execution. In that case the calculations are carried out twice and the results of both runs are afterwards compared [10]. This makes it possible to detect transient faults that only effect a single computations however permanent ones, altering both, can not be detected. Even more elaborate mechanisms, exploiting the possibilities of processors, are realisable. The approach in [7], for example, uses the debug port to observe the control flow inside the processor. In detail the checker controls which branches are taken and generates checksums on the executed commands to assure the correct functionality.

Unfortunately no completely concurrent test approach, actively applying test vectors, could be found in literature. A very interesting approach, combining properties from concurrent checking and online testing, is called input vector monitoring Concurrent BIST [46]. This method determines a subset of all possible input vectors as test set. As soon as a new input vector is applied to the CUT it is checked if that value is part of the test set and if it has not been processed in the current cycle. If that is the case the output of CUT is compressed in a compactor. After all vectors of the test set have shown up the computed signature is compared to a precalculated value. Due to the fact that the input values are not controllable it might happen, that the set is never received completely, yielding the test procedure unfinished and stuck. To prevent this, the circuit switches to a special test mode if testing was not finished within a certain time interval and the still missing vectors are actively applied to the input. The earliest implementation of this approach has been proposed in [28] and was afterwards extended several times in w-MCBIST [46], SWiM-BIST [44], MICSET [48], R-CBIST [49], exploiting "X" values [43], NEMO [45] and w-CBIST [47], just to name a few. These differ mainly in the way the input vectors are detected as member of the test set. In the first version the input value is compared

to a value generated by a generator unit. Only when that value is detected the next one is generated. In future implementations this mechanism has been improved for example by window based approaches, capable of comparing more vectors at the same time, or by utilising RAMs.

#### **Asynchronous Circuits**

Most of the available test procedures were developed for synchronous circuits and afterwards adapted to asynchronous ones. Due to the fact that the two implementations may differ significantly (e.g. handshake lines, dual rail) not all possible faults are detectable by these approaches. For example is it a common mistake to assume that faults on the control lines cause a circuit to halt automatically; in fact that is only true for stuck-at faults under various constraints as pointed out in [30]. Others may for example introduce additional transitions, causing severe malfunctions of the CUT. Therefore protocol checkers have been developed [30, 52], which check the control lines not only in the value but also in the time domain. In the latter case the correct temporal order of the signals is assured, for example that a new value is only indicated after the old one has been acknowledged or that an acknowledge signal is only sent after new data values have been received.

Asynchronous circuits are in general harder to test due to the missing clock signal and the therefore increased concurrency of the single components of a chip. This makes it (nearly) impossible to verify each possible system state in an offline test. Therefore online test approaches, like the one proposed in this thesis, become even more valuable, because they are capable of testing the unit during its normal operation.

# **Background on Asynchronous Logic**

The purpose of this chapter is to give a short overview of the concepts and definitions applied in the thesis. For more detailed information on each topic follow the references stated in the text.

#### 3.1 Asynchronous Circuits

Only a small percentage of today's circuits are asynchronous, despite the fact that they have been invented a long time ago. However nowadays the number of implementations is rising due to their advantages compared to synchronous logic. The following listing gives a short overview over the most important properties of asynchronous logic and the main differences to the synchronous one.

Asynchronous circuits ...

- possess no central clock. The units coordinate themselves using handshake signals, indicating that data are available or have been processed. This mechanism also renders time consuming timing analysis unnecessary.

- are more robust against additional delays introduced for example by environmental changes,

e.g. temperature or voltage. They simply lower their working speed but will continue to

deliver results, not fail completely as synchronous ones do, when timing violations occur.

- consume less power compared to synchronous circuits because they only work when new data are available. In the synchronous case the clock drives the circuit always, even if nothing has to be done. In addition the clock network itself consumes a lot of power too 1.

<sup>&</sup>lt;sup>1</sup>Please note that power saving mechanisms like clock gating were introduced in synchronous designs to tackle those problems.

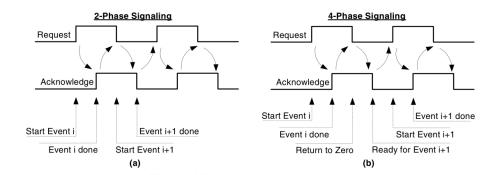

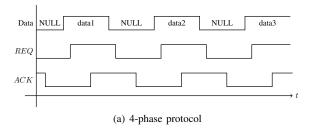

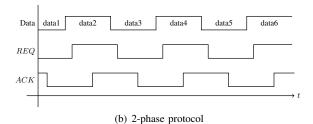

Figure 3.1: (a) 2-Phase and (b) 4-phase Signalling [41]

- have a high level of concurrency making development and testing very difficult. In addition they have to be designed very thoroughly to prevent glitches and spikes.

- lack design tool support because they are not used widely, making development even harder.

#### 3.2 Handshake Styles

The process used to coordinate the data exchange, i.e. the temporal order of sending and receiving data between two units, in asynchronous logic is called handshaking. Two fundamental styles (see also figure 3.1) are used for this purpose:

#### 4-phase

The name yields from the fact that there are four distinct phases in a complete transmission cycle. In the first one the sender indicates new data to the receiver which the latter acknowledges in the second phase. In the third one the sender returns to its base state which is again acknowledged by the receiver in the fourth phase. This method is also called Return To Zero (RTZ) or level signalling.

The 4-phase communication style uses two differing phases <sup>2</sup>, i.e. the DATA-phase holding the actual value and the NULL-phase used to separate two consecutive DATA values.

Due to the fact that efficient and simple robust function blocks are harder to build using the 2-phase style, combinational gates are in general realised using the 4-phase communication style [15].

<sup>&</sup>lt;sup>2</sup>These are not connected to the phases the expression 4-phase refers to.

#### 2-phase

As the name indicates this style needs only two phases for a single transmission. The sender indicates new data in the first phase and the receiver acknowledges it in the second one. This method is also called Non Return to Zero (NRZ) or transition signalling.

When using 2-phase communication DATA values are sent consecutively without any separating value in between. To recognise the end of the old value and the beginning of a new one the data are sent in two alternating phases, which are recognisable by the receiver, similar to the NULL-phase and DATA-phase of the 4-phase protocol.

The fact that only half of the phases are required to send the DATA values makes this style faster than the 4-phase one and also more power efficient. However in general the implementation of efficient function blocks is very difficult [15], which is the reason why it is mainly used for long communication lines connecting two units that internally use the 4-phase style.

#### 3.3 Bundled Data Approach

A configuration is called bundled data if in addition to the data lines separate request and acknowledge line are installed, which are used to indicate that valid data are ready to be processed or that the data have been read, more specifically to carry out the handshake protocol. A detailed description on bundled data is stated in [34, pp. 9-11].

A very important property of bundled data used in this thesis is the necessary delay on the request line, which is required to assure, that the request signal reaches the next storage element only after all input lines to that unit already got stable. The appropriate delay has to be determined at design time by thorough timing analyses and simulations.

The bundled data approach can be seen as an intermediate step between synchronous and DI<sup>3</sup> asynchronous logic. On the one hand it is possible to remove the clock signal however on the other hand thorough timing analysis, which are very time consuming and hard to execute, are still mandatory.

The handshake styles described in section 3.2 can be realised by a differing handling of the request line. In the 2-phase style each transition either from high to low or from low to high indicates new data whereas with the 4-phase style only a high value on the request line has that meaning. Due to the fact that no new data are sent in the NULL-phase, a delay of the request line is not necessary in that particular case. Therefore an asymmetric delay line, that only delays the high value of the request line, may be used in the 4-phase style. Please note that the same logic cloud can be used for both styles; only the pipeline nodes have to be changed due to the differing meanings of the transitions (single edge versus double edge) on the control lines.

<sup>&</sup>lt;sup>3</sup>More information on that follow in section 3.5

#### 3.4 Completion Detection Approach

The completion detection approach [34, pp. 11-13] uses for each data bit multiple wires, in the following called rails, for transmission. This enables the data themselves to indicate when they are ready to be processed instead of using a separate line for that purpose, which not only renders timing analysis unnecessary but also increases the stability.

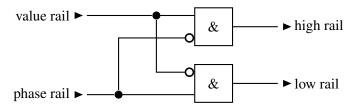

Using a 4-phase protocol in conjunction with completion detection yields the dual rail NULL convention logic (NCL), where one rail is named high rail and one low rail. A high value on the high rail indicates that the sent signal is logic high, and a high value on the low rail stands for a logic low value. Both wires carrying a high value is not allowed and never appears if every unit is working correctly. The NULL-phase used to separate two consecutive DATA values is identified by a low value on both rails.

Level encoded dual rail (LEDR), the 2-phase protocol chosen in this thesis, transmits two consecutive DATA values without any value in between. To clearly distinguish between old and new data, two phases are introduced, one where the parity of the two rails is even and one where it is odd. To signal the receiver a new value only the phase has to change, which can be done by changing a single rail. When looking at both rails one can see that one of the lines holds the actual value and the other one is responsible to generate the correct phase. If the DATA value between two succeeding phases is the same just the phase rail has to toggle to signal a new value. If the value changes the value rail itself toggles automatically generating a different phase and therefore indicating a new value.

Besides size and complexity another very important criterion has to be investigated when using the completion detection approach, namely timing assumptions. A detailed explanation follows in section 3.5.

### 3.5 Timing Assumptions

Timing assumptions express what timings have to be fulfilled to make the circuit work as specified. The fewer the assumptions that have to be made, the more robust the concrete implementation gets. A short summary of already specified assumptions shall be given here, a more detailed description can be found in [34, pp. 9-28].

**DI** Delay Insensitivity is the least restrictive class allowing arbitrary but finite delays. Only very few circuits are really DI because in general only inverters and Muller-C elements are allowed [11]. In special configuration also other gates may be used without loosing DI characteristics.

A clear sign that DI is not fulfilled is the violation of the *indication principle* ([34, pp. 14-16]) which states, that every change at the input of a gate has to be recognisable also at its output. If, for example, an OR-gate forwards a low value it can be said that both

inputs are low, however if the output is high, it is not possible to distinguish if both of just a single input lines holds a high value.

- **QDI** Quasi Delay Insensitivity is very similar to DI with just one additional restriction. If a signal line forks, i.e. is split up and directed to two different units, the signals on both lines of the fork have to have the same delay, also called *isochronic-fork*. This implies that a signal sent reaches both receiving units at the same time, which may be a very challenging task, as pointed out in [11]. Furthermore the *isochronic-fork* property may be violated during operation due to environmental properties such as a local temperature deviation.

- SI A circuit in general consists of several gates that are interconnected and together compute the desired result. However different paths through these logic gates might have a longer delay than others, causing gates to switch at different times, producing glitches or simply incorrect results. A circuit is called Speed Independent if no unintended behaviour is possible as a consequence of gates switching at different points in time. Due to the fact that the tool *Petrify* (section 3.8), used to develop the implementations in this thesis, only generates SI circuits, this timing assumption is fulfilled by all implementations. In addition [11] claims, that QDI and SI are identical for practical purposes, making it possible to assume all designed circuits QDI as well.

Please note that there exist additional, more restrictive, timing assumptions which are however neglected in this listing, because in this thesis only DI, or if that is not possible QDI, circuits are presented.

### 3.6 Data-Validity Schemes and Channel Types

When using the bundled data design style a separate line, more specifically the request line, indicates that new data are available, however there are different possibilities when the data really are available at the input of the next unit. Furthermore two different channel types can be distinguished, more specifically the push and the pull channel. In the first case the sender starts a transmission by indicating that new data is available, in the latter case the receiver indicates that it is ready to receive new data which causes the sender to transmit them if available. All these approaches are shown and described in detail in [34, pp. 116-117]

In this thesis the early data-validity scheme on a push channel is used. In detail the data lines hold valid data as soon as the request signal reaches the receiver and get invalid as soon as the acknowledge signal is received at the sender. This implies that the receiver has to read and process or store the DATA values before the acknowledge signal is sent.

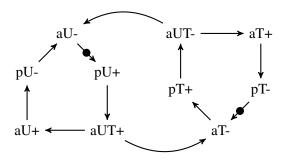

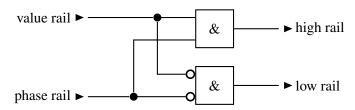

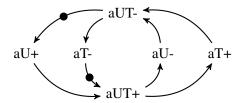

#### 3.7 Signal Transition Graph

Signal Transition Graphs [11], or short STGs, are a special form of a Petri Net [34, pp. 86-113], which specify the temporal order of transitions on input and output lines of a component. In this thesis these graphs are used to generate concrete circuit implementations using the tool *Petrify* (section 3.8).

In general an STG consists of places, arcs and special nodes, which are used to split or combine paths. Due to the fact that the latter are not used in this thesis they won't be described in more detail.

place Places in an STG represent a transition either at an input or output line. The transition is only allowed to occur, in the following also called to fire, if all its input arcs hold a token. After the place fired the tokens of the incoming arcs are removed and each outgoing arc receives a single token.

**arc** An arc connects two places and is able to hold one or more tokens. At the beginning an initial marking has to be introduced to start the data processing at the intended position.

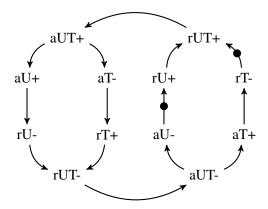

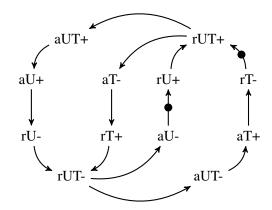

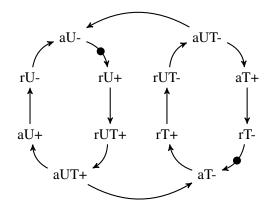

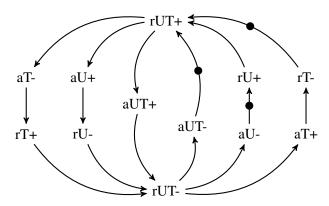

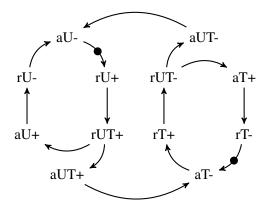

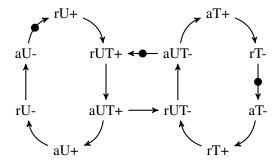

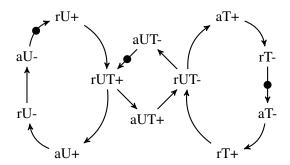

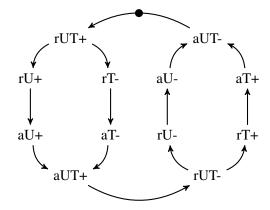

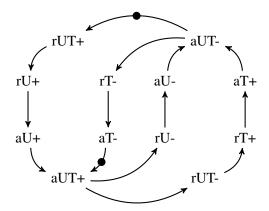

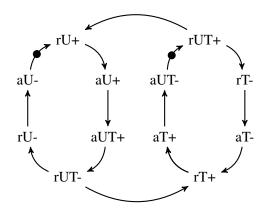

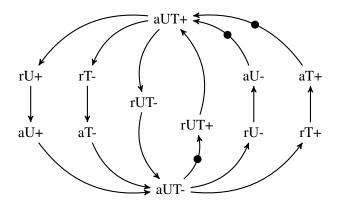

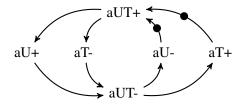

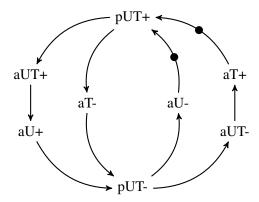

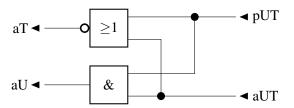

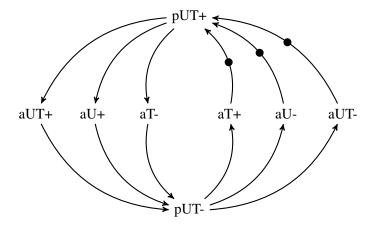

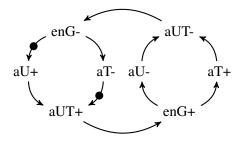

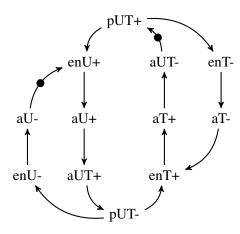

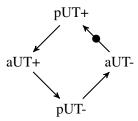

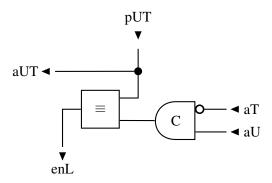

The STGs shown in this thesis encode the signals using the naming scheme xYs whereas  $x \in \{a,r,p\}$ ;  $Y \in \{U,T,UT\}$  and  $s \in \{+,-\}$ . The first letter specifies the type of the line, which is either an acknowledge (a), request (r) or a phase detector (p). The letters afterwards determine which data are delivered on the line, i.e. either the 4-phase types Test Data (T), User Data (U) or the combined 2-phase version User/Test Data (UT). Finally a '+' sign at the end indicates a rising edge and a '-' a falling one.

### 3.8 Petrify

"Petrify is a tool for synthesis of Petri nets and asynchronous controllers." [24] In this thesis it is used to convert STGs to netlists, i.e. into specific circuit implementations. For this thesis version 4.2 compiled 13-Oct-03 at 3:06 PM was used, which can be downloaded at [24]. The used gate library can be found in section B.1.

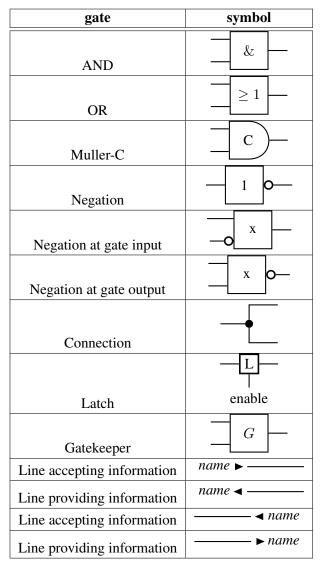

## 3.9 Circuit Drawings

Some of the developed circuits were also drawn using the gates shown in table 3.1. In the figures the inputs (labels aXX or rXX) are always displayed at the left side, the outputs (labels aXX or rXX) at the right and signals produced and consumed inside the unit (denoted by everything except aXX or rXX) at any side. Please note that the term input or output declares the data signals, the acknowledge line and, if used, the request line as a whole where an input is recognised by an incoming flow on the data lines and an output by an outgoing one, as it is also used when describing the overall functionality of a unit. The fact that all signals are

Table 3.1: logic elements and the corresponding symbols used in graphical circuit representations

referred to by a single term however implies that the acknowledge signal of an input is actually a line providing information to the outside and the acknowledge signal of an output is actually receiving information from the outside. For that reason the signal direction is indicated on the single lines by arrows, as they are shown in the last few lines of table 3.1.

#### 3.10 Fault Types

To classify fault sources it first of all has to be stated what the difference between fault, error and failure is. A failure appears, if the behaviour of a unit deviates from its intended one. The cause of a failure is an error, i.e. an incorrect system state which has been caused by a fault, an unexpected environmental property [13]. Based on these definitions the following classes of faults are distinguished [5]:

- 1. *permanent faults*: Faults in this category are first of all reproducible meaning that a vector that activates this fault will do this every time. This implies that the fault does not vanish by itself but it has to be removed actively. An example for this class are hardware defects like a broken wire.

- 2. transient faults: Transient faults are only introduced once and for a short time. Due to the increasing miniaturisation of circuits and the steady improvements in speed the importance of this class grows bigger and bigger. The typical example is cosmic radiation which causes voltage spikes on signal lines.

- 3. *intermittent faults:* Faults in this class are in general present all the time, however they only introduce an error if a specific trigger condition is showing up. Despite the fact that these faults are reproducible, they are in general very hard to detect and may be easily confused with transient ones. A typical example for this class is a software fault, that only produces a wrong result if a specific input value is received.

#### 3.11 Circuit Characteristics

To describe the capabilities of a test circuit, [31] proposes three properties which are also used for analysing the characteristics of the test scheme proposed in this paper in chapter 10.

- 1. Latency of Test Completion (LTC): This property describes how long it takes the test circuit to completely test the circuit during its normal operation, i.e. that all test vectors have been applied to the CUT.

- 2. Latency of Fault Detection (LFD): This attribute represents the time it takes the test circuit to detect a fault after it has occurred. Again it is calculated under the assumption that the CUT is working normally while testing is carried out.

- 3. *Error Latency* (EL): This indicator determines how long, in average, incorrect values are possible until the corresponding fault is detected. It is calculated as the difference between the *LFD* and the latency of fault manifestation (*LFM*) which indicates how long it takes until a fault generates a failure. The smaller the EL is the better the test circuit works. Please note that it is also possible for the EL to become negative indicating that faults are detected before they generate failures.

CHAPTER 4

## **Methodology**

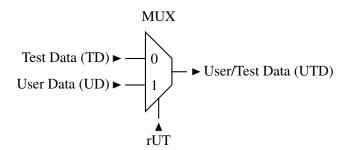

In a 4-phase protocol the exclusive task of the NULL-phase is to clearly separate two consecutive DATA values. More specifically the circuit does not process any data during that time but literally halts until the next DATA-phase starts. This behaviour introduced the question if it is possible to use the circuit during the NULL-phase for other useful purposes, like in this thesis to test the circuit without actually interfering with the original computations.

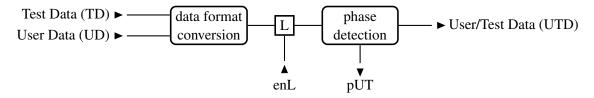

The easiest way to accomplish this assignment is to replace the NULL values by additional TEST values, used to actually test the CUT. The communication protocol is converted to a 2-phase type by carrying out this step, because afterwards a TEST value immediately follows a DATA value. For this purpose additional units are required that are capable of merging DATA values and TEST values into a single 2-phase output and another one that splits a single 2-phase input into DATA values and TEST values. At first an extensive literature research was started to find out if units having that particular behaviour already exist. Unfortunately this was not the case because no application could be found that propagates two input values one after the other to the output. The applications that were found always wait for both inputs to hold a DATA value and then both of them are sent at the same time.

For that reason the appropriate units had to be designed completely new, which was carried out by modelling state transition graphs (STGs) of the expected behaviour. These were then transformed into concrete circuit implementations using *Petrify* and finally checked for further simplifications. The top priority in this thesis was to identify the easiest and smallest ways to carry out the above described functionality. It turned out, that it reduces the size of the resulting circuits a lot, if the TEST values are delivered in the same way as the DATA values, i.e. by using a 4-phase communication protocol. This leads to the following desired functionality of the additional units:

**Merge** This unit only propagates the DATA values of the inputs in an alternating fashion to the output, the NULL values are dropped. If necessary a format conversion <sup>1</sup> is carried out on the data to assure a valid 2-phase communication at the output.

**Split** This unit propagates the DATA values of the 2-phase input in an alternating fashion to the two 4-phase outputs with optional necessary format conversions. Between any two consecutive DATA values a NULL value has to be inserted to create a valid 4-phase communication protocol.

While developing an efficient implementation of these two units several versions were discovered, differing mainly in their level of concurrency and their hardware requirements. Due to the fact that each of them has its pros and cons no "best" solution could be determined and therefore several versions are described and analysed in this thesis.

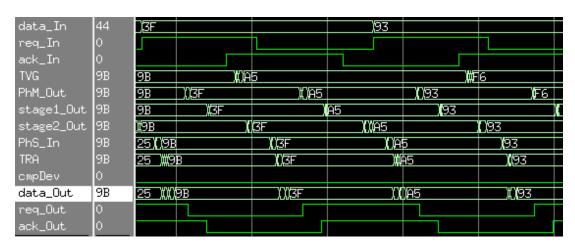

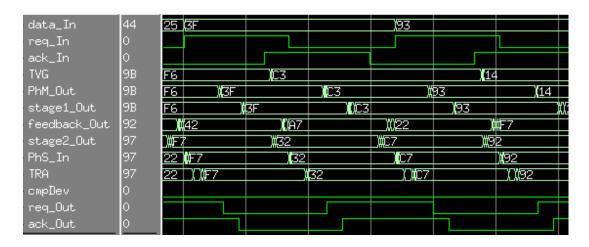

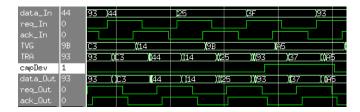

After all theoretical preparations were finished, an actual implementation using the proposed test approach was created. A simple three stage pipeline, was chosen as the CUT, which was afterwards extended by the proposed test approach. To verify the correct functionality the implementation was simulated and it was checked, if the output was according to the results achieved with the original pipeline. The internal test procedure was verified by introducing a stuck-at fault and it was observed, if it is detected correctly, i.e. if an error is reported to the outside world.

In addition the area overhead and introduced delay were estimated analytically to achieve generic formulae for an arbitrary amount of computational logic. The received results were then used to calculate characteristic values for the proposed test approach, which were afterwards analysed to determine the properties of the proposed test approach.

<sup>&</sup>lt;sup>1</sup>If more than one rail per bit is used a conversion is mandatory.

# **Proposed Solution - Overview**

This chapter gives a first introduction to the proposed test approach. At first the concept is developed step by step and afterwards the necessary components are presented as block diagrams. Furthermore the idea of different implementation styles is presented however without showing concrete circuit designs, which is the topic of the following two chapters.

#### 5.1 Introduction

As it was shown in section 3.2 the NULL-phase in a 4-phase protocol has solely the purpose to separate two DATA values, implying that it does not contribute to a computation at all. This fact begs the question, if that particular phase may be used for additional tasks, rather than just separating DATA values. In this thesis it is therefore investigated, if it is possible to implement a self-testing circuit that uses the time available in the NULL-phase to test the actual circuit and to develop appropriate implementations, if there are any.

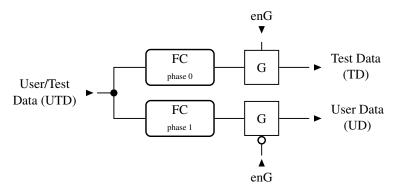

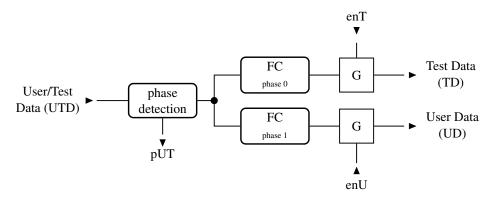

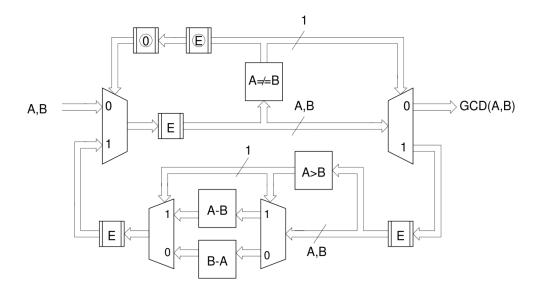

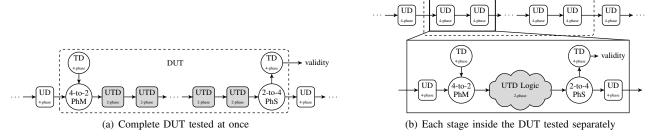

To test a circuit, the TEST values have to use the same path as the DATA values. To achieve this, the data input has to be blocked while the test vector is processed, because otherwise both may interfere. Due to that fact the core idea of the proposed approach is to replace the NULL values by TEST values, and afterwards feed the modified input stream into the circuit under test (CUT). At the output of the CUT the test vectors are replaced again by NULL values to achieve a correct 4-phase protocol. In parallel the processed test vectors, which were replaced by NULL values, are checked against precalculated ones. If no differences are detected one may assume that the application related calculations in the CUT were carried out without failures as well and the results can be assumed to be correct, however if the test result was not identical with the stored value a failure occurred and the circuit indicates this to the outside world.

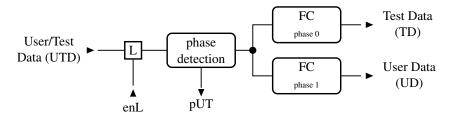

By replacing the NULL-phase of a 4-phase protocol with another DATA-phase the protocol is converted to a 2-phase one because in that case DATA values succeed one another without

any value in between. For the purpose of *merging* User Data and Test Data a unit has to be developed, that has two separate inputs, one for User Data and one for Test Data, and one output for the combination of both, using the 2-phase communication protocol. In a similar fashion also another unit is needed that *splits* the 2-phase User/Test Data stream up into Test Data and User Data, at which the User Data output has to use a valid 4-phase protocol, to assure correct functionality at the output of the CUT.

#### 5.2 Approach

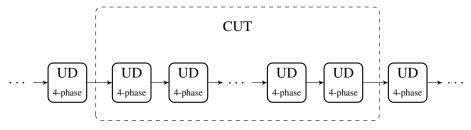

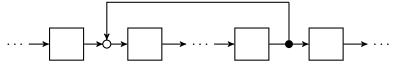

As starting point of all considerations a linear asynchronous Muller pipeline (i.e. without loops) using a 4-phase protocol like in figure 5.1 is chosen. Within that structure no registers are allowed, that store values from the previous computation for the next one, like the status register in an arithmetic logic unit (ALU). Altogether no interactions between different computation stages or succeeding values are allowed, as it is the case in state machines calculating their actual output based on their internal state and the input or when loops in the data path are used. This very restrictive model will be used to develop and exploit the fundamentals of the approach, however in chapter 8 it is investigated if some of the stated restrictions may be lifted under certain conditions.

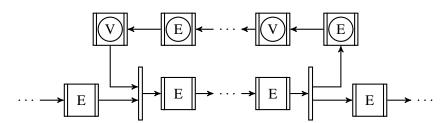

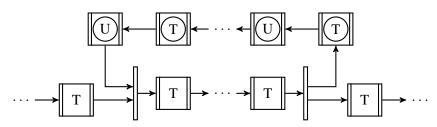

Figure 5.1: original Muller pipeline structure used as basis of considerations, multi-stage possible, 4-phase communication protocol

The nodes in the picture represent a controller with integrated latches, i.e. a complete pipeline unit. A subset of these, namely the ones that have to be tested, are then chosen, forming the Circuit Under Test (CUT) (figure 5.2<sup>1</sup>). After the CUT was formed it is transformed to a self-testing circuit, by integrating additional units<sup>2</sup>. Please note that it does not matter if the additional units are placed before or after the logic cloud. The only difference, of course, is that the logic will be tested if it is placed inside the CUT and not if it is outside.

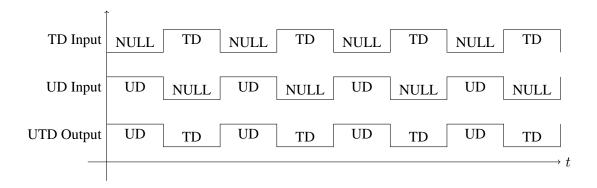

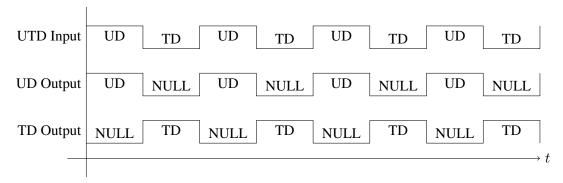

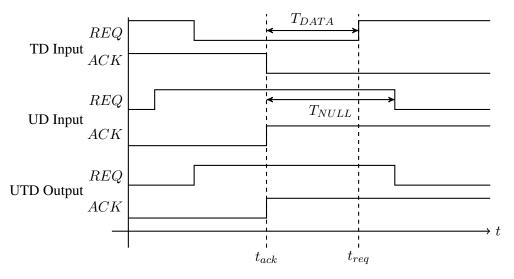

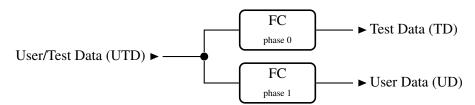

One of the additional units, as already mentioned, is responsible for merging the inputs. Figure 5.3 shows its inputs and output over time. Please note that the Test Data input was also chosen as 4-phase input, resulting in simpler circuits. Due to the fact that this building block converts two 4-phase inputs into one 2-phase output it is named 4-to-2 phase merge and gets described in detail in section 5.5.

<sup>&</sup>lt;sup>1</sup>In this figure the logic clouds are not shown for better readability.

<sup>&</sup>lt;sup>2</sup>Details on this procedure follow in section 5.3 and 5.4

Figure 5.2: original Muller pipeline structure used as basis of considerations, CUT already determined, logic clouds are dropped for better readability

Figure 5.3: Input and Output of the 4-to-2 Phase Merge unit over time

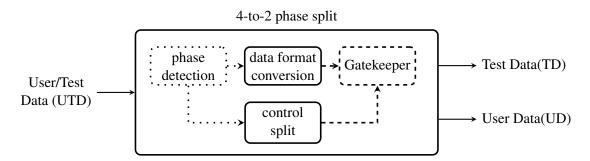

To remove the TEST values from the data stream at the end of the CUT, more specifically to split User Data and Test Data, another additional unit has to be integrated. It is exactly the opposite of the one before, i.e. taking a 2-phase User/Test Data input and splitting it up into a 4-phase Test Data output and a 4-phase User Data output. The latter one has to use the 4-phase protocol, whereas this property is not mandatory for the Test Data output, however as before the 4-phase style was chosen to simplify the resulting circuit implementation. Figure 5.4 shows the temporal progress of the input and the outputs of this particular unit. Due to the fact that it splits a 2-phase input up into two 4-phase outputs this building block is named 2-to-4 phase split and gets described in detail in section 5.5.

The test vectors fed to the 4-to-2 phase merge unit are produced by a test vector generator and the ones delivered from the 2-to-4 phase split unit are analysed by a test response analyser. Due to the fact that these units can be implemented in many different ways they are described in detail in section 5.7, where also the selection and generation of appropriate test vectors is discussed.

Two implementation styles, describing how the conversion from the Muller pipeline to a self-testing circuit is carried out, have been developed, namely *Complete CUT Testing* (CCUTT) and *Single Stage Testing* (SST). These will be described in more detail in the following sections.

Figure 5.4: Input and Output of the 2-to-4 Phase Split unit over time

#### **5.3** Complete CUT Testing

This design method is the most straight forward approach. The NULL values of the User Data input are replaced by TEST values at the beginning of the CUT and removed at the end. On the processed Test Data error checking is carried out to determine if failures have occurred.

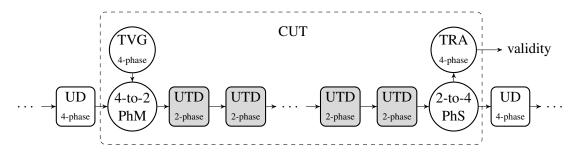

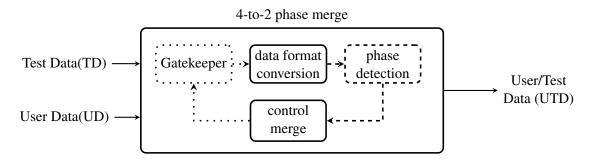

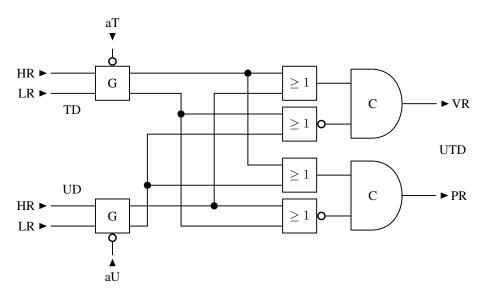

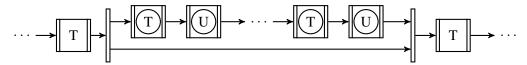

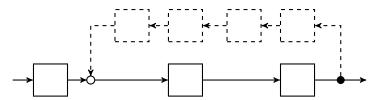

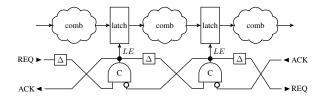

In detail the 4-to-2 phase merge unit is placed right at the entry of the CUT, or more specifically in front of the first pipeline node inside the CUT. The resulting 2-phase data flow is then injected into the original pipeline structure, which has to be adopted to the 2-phase communication protocol first. If the bundled data method is used this adaption only concerns the controller nodes, if completion detection is used solely the logic in between has to be adapted. At the end of the CUT Test Data and User Data are finally split up again in the 2-to-4 phase split unit. The split up Test Data are afterwards checked (details see section 5.7) and the outside world is informed through a signal line if the received result matched the expected result.

Figure 5.5: complete CUT Testing Approach, Schematic View

Figure 5.5 shows the approach, which is very similar to the original pipeline structure (Figure 5.2). Altered nodes, i.e. those transformed from 4-phase to 2-phase, are represented as coloured nodes, newly introduced ones, in detail the 4-to-2 phase merge (PhM) and 2-to-4 phase split (PhS) unit as well as the test vector generator (TVG) and test response analyser (TRA) are

displayed as nodes with a circular shape. As mentioned before, also the logic clouds, that are not shown in this figure, may have to be converted, depending on the used communication protocol.

When comparing the data interfaces of the CUT to the ones in the original pipeline (figure 5.2) one can see, that they are the same. This means that the test procedure is carried out transparent to the outside application, which is a necessary condition to test only parts of a longer pipeline. Furthermore this property implies that one can not tell if testing is carried out inside the unit by just looking at the data interface.

## 5.4 Single Stage Testing

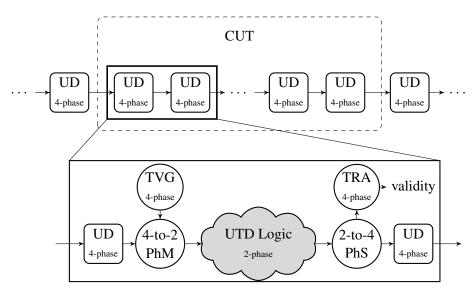

Another possibility to verify the correct behaviour of the CUT is to test each pipeline stage individually. In contrast to the Complete CUT Testing style described before only the logic clouds between the pipeline nodes are tested in this approach.

Figure 5.6: Single Stage Testing Approach, Schematic View, only shown for first stage, in real implementation test circuit has to be integrated between every two consecutive pipeline nodes

For that purpose all parts of the test circuit (test vector generator, test response analyser, 4-to-2 phase merge, 2-to-4 phase split) have to be implemented between every two consecutive pipeline nodes inside the CUT. Figure 5.6 shows this at the example of the first stage, using again a circular shape for newly integrated nodes. The logic cloud in between is coloured because it has to be converted from 4-phase to 2-phase when the completion detection design style is used, whereas no conversion at all has to be carried out when bundled data is chosen. Test Data and User Data are merged right after one pipeline controller, sent through the logic, which was adopted to 2-phase, and split up in front of the following controller node. The split up Test Data are checked for errors and the result is presented on an output line, in the figure named validity,

which is afterwards connected to the validity lines of all other stages in a way, that a mismatch is indicated to the outside application as soon as a single stage failed.

#### Advantages:

- The testing works transparent to the pipeline nodes i.e. they do not have to be modified, because the conversion to a 2-phase protocol is carried out after the output of the first node and the conversion back to a 4-phase one before the input of the next one. Therefore only the logic has to be converted to 2-phase. If the bundled data approach is used even this task can be dropped because in that case the logic for 2-phase and 4-phase is the same. The only task that might remain is to replace asymmetric delay lines by symmetric ones.

- By introducing a test circuit into each single pipeline stage, it is possible to test every one

of them separately. Therefore the specific properties of each stage can be tested individually and not combined with others as in the previous case. This will in general reduce

the effort of finding the right test vectors and may also reduce the effort of designing and

implementing the TVG and TRA.

### Disadvantages:

- The TVG and TRA design might get easier, however for each single stage one is needed. With an increasing stage count the effort may raise to a level that the overall design and implementation time exceeds that of a complex one.

- Errors in the stage controllers themselves are not detectable by this approach. That is the reason why an additional test procedure is necessary, for example a parity check.

#### 5.5 Transformation Blocks

While searching for literature for this thesis many different transformation circuits were found; some convert a 2-phase into a 4-phase protocol and others transform between protocols of the same phase type [15]. Even conversions between bundled data protocols and completion detection ones have already been introduced [8,9]. However no publications could be found describing an approach for combining two 4-phase inputs to one 2-phase output or reverse. That is the reason why these building blocks had to be designed completely new in this thesis.

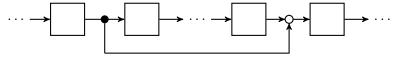

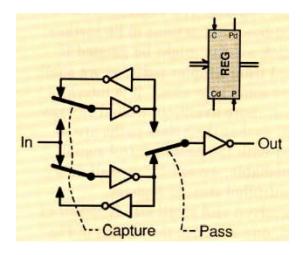

The 4-to-2 phase merge as well as the 2-to-4 phase split block can be integrated as a switch or as a pipeline node. The first method forwards either the User Data or the Test Data input but does not store any data, yielding the advantage, that very small implementations are possible. If the latter method is used an improved decoupling of in- and output can be achieved, resulting in an increased working speed at still very little circuit complexity. The big disadvantage of this

method is the additional latch, which can be seen as another failure source, making it more probable for an error to occur. At least these additional failures are detectable by the test procedure proposed in this thesis, as long as the latch is placed at the combined User/Test Data line.

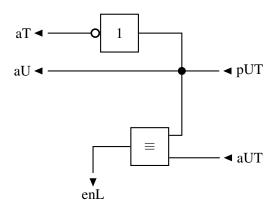

All latches introduced are defined to become transparent, i.e. propagate the value at their input to their output, whenever the enable input is high and store their actual value if the enable input is low. In the first case the latch is also called open, in the latter one closed throughout the thesis.

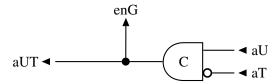

As it was described in the sections 3.2, 3.3 and 3.4 the 2-phase protocol sends the DATA values in two alternating phases. The fact that always exactly one 2-phase channel and two 4-phase channels, served in an alternating fashion, are integrated in one transformation block, makes it possible to assign each 4-phase channel to a specific DATA-phase of the User/Test Data line. This yields the advantage, in contrast to other approaches like in [8], that phase relations can be integrated hard wired and need not be calculated dynamically. This reduces the complexity of the circuit and also increases the speed. In this thesis the User Data channel is assigned to phase 1 i.e. when the request signal is high using the bundled data approach and odd parity when using the completion detection approach. In contrast the Test Data channel is assigned to phase 0, i.e. low request signal respectively even parity. Of course all following considerations are still correct when this assignment is interchanged i.e. User Data to phase 0 and Test Data to phase 1 however then some of the presented circuits have to be altered as well.

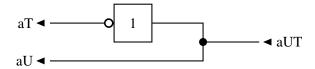

Due to the fact that the implementations for the bundled data and the completion detection approach differ a lot, detailed implementations are described in the chapters 6 (BD) and 7 (CD). The implementations are designed using STGs at which the starting configuration of User Data, Test Data and User/Test Data signals are defined as:

- The first action to come is a rising transition on the input (either User Data or User/Test Data)

- The Test Data Input/Output has already delivered its NULL-phase / acknowledged its DATA-phase at startup.

The main guideline when designing the test circuit was to keep it as simple and small as possible. One of the reasons for this choice was to keep the amount of necessary, additional hardware very low. Furthermore this thesis is supposed to investigate if such an approach is possible at all, so the driving force was to find any, not the best or fastest, implementation. That is the reason why additional complexity for increased speed was avoided.

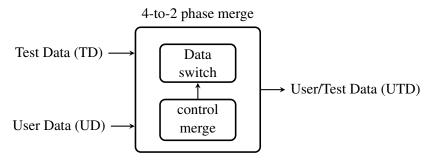

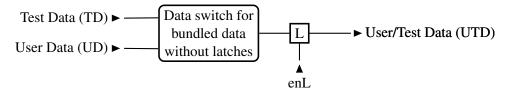

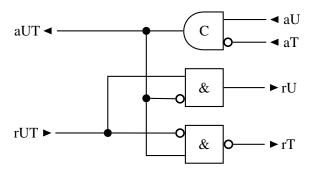

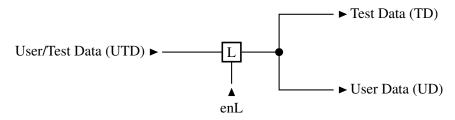

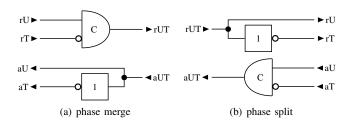

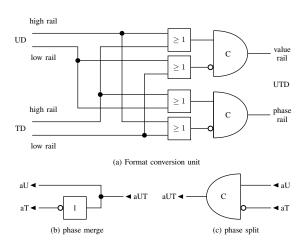

## 4-to-2 Phase Merge Unit

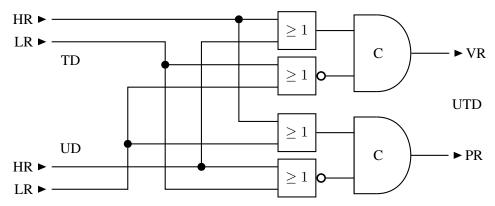

As mentioned in section 5.2 the 4-to-2 phase merge unit combines two 4-phase inputs, i.e. User Data (UD) and Test Data (TD), to a single 2-phase output, i.e. User/Test Data (UTD). This

is achieved by replacing the NULL-phase of one input signal by the DATA-phase of the other one and only propagating the combined data stream. The User Data values are thereby always assigned to phase 1 and the Test Data ones to phase 0. A time diagram of this process was already shown in figure 5.3. In reality the input signals naturally will not be aligned as perfectly as it is shown in that picture, but with a specific offset to each other. The point in time when the signals are propagated to the output in these cases depends on the design of the merge unit. Several different implementations are possible, differing in complexity and their level of concurrency. More details on these follow in section 6.2 for the bundled data approach and in section 7.2 for the completion detection approach.

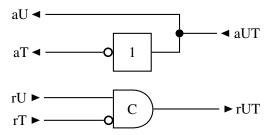

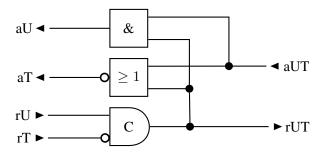

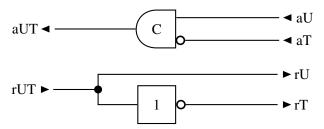

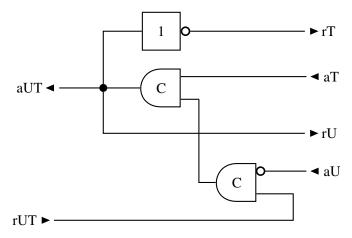

In the STGs describing the behaviour of the single implementations the request and acknowledge line of the User Data input are named aU respectively rU, those for the Test Data input aT and rT and the ones for the output User/Test Data aUT and rUT, according to the naming guidelines presented in section 3.7.

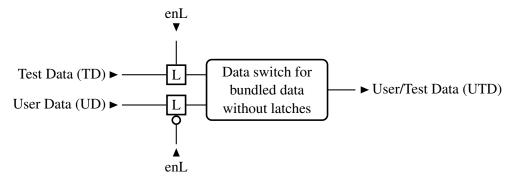

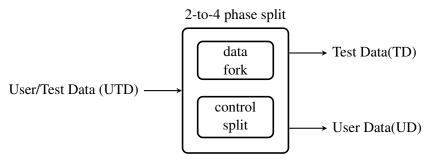

## 2-to-4 Phase Split Unit

As already described in section 5.2 the 2-to-4 phase split unit splits one 2-phase input, i.e. User/Test Data (UTD), into two 4-phase outputs, i.e. User Data (UD) and Test Data (TD). Therefore this block propagates all the values of phase 1 to the User Data output and the values of phase 0 to the Test Data output. In addition the unit has to insert NULL values between two consecutive DATA values on each output to create a valid 4-phase protocol. A time diagram of this process was already shown in figure 5.4.

As with the 4-to-2 phase merge unit the output behaviour of the 2-to-4 phase split unit is determined by the used implementations. Again several differing designs are possible, which are explained in detail in section 6.5 for the bundled data approach and in section 7.4 for the completion detection approach.

The nomenclature used for the signals is the same as with the 4-to-2 phase merge unit, with the only difference that input and output are interchanged, i.e. that User Data and Test Data are in this case output signals and User/Test Data the input signal.

## 5.6 Implementation Styles

Specific solutions are presented for the bundled data (see Section 6) and completion detection (see Section 7) protocol. The separate study of these two is reasonable, because the circuit implementations differ significantly. Nevertheless both have in common that the solutions are working in the same manner and that optimisations are possible in a similar way. For each approach different implementations are presented and shall be listed shortly here. For more details head to the above mentioned sections. Please note that this listing is by far not complete, i.e. there exist several additional implementations, however for this thesis only the simplest solutions were chosen.

**Basic Implementation:** A tight coupling between User Data and Test Data is introduced, forcing both 4-phase channels to be in differing phases (one in its DATA-phase and one in its NULL-phase) before the data value is propagated. In addition both 4-phase channels are requested/acknowledged at the same time, i.e. as the signal of the 2-phase one arrives. These couplings result in area efficient implementations with very little complexity. When used in the 4-to-2 phase merge unit it can be compared to the Join unit presented in [34, pp. 31-32, 58-60], with the difference that both inputs have to have diverse phases for the data to be propagated. Furthermore it has to be noted that unlike the Join unit this implementation only propagates values from one input at a time to the output and not from both. The 2-to-4 phase split unit is very much alike the Fork unit introduced in [34, pp. 31-32, 58-60], just differing by the fact that the request line of one output is negated and of course the implicit conversion from 2-phase to 4-phase.

The fact that the operation halts until both 4-phase lines have changed their state also implies, that the faster phase has to wait for the slower one. To tackle this problem some enhancements can be applied to increase the speed for certain timing constellation, presented in the following paragraphs.

**Early NULL-phase:** The considerations of this method are based on the fact, that the NULL-phase is a pure spacer, so no information is acquired by receiving it or required to create it. Therefore it is possible to acknowledge/start the NULL-phase much earlier than the DATA-phase.

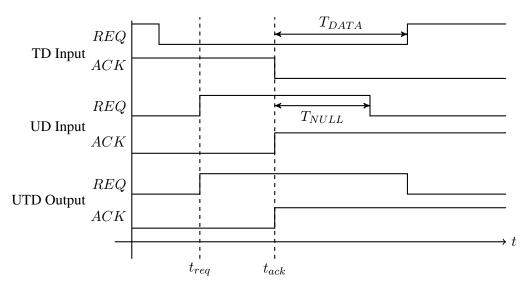

Figure 5.7 shows the concept on the 4-to-2 phase merge unit (bundled data implementation) with its two 4-phase inputs at the top and the 2-phase output at the bottom. One can observe that the DATA-phase arrives later than the NULL-phase, i.e.  $T_{DATA} > T_{NULL}$ . This situation can be improved by acknowledging the NULL-phase already at time  $t_{req}$ , giving the following DATA values more time to reach the 4-to-2 phase merge unit. In bundled data systems the constellation that DATA values are slower than NULL values is very probable if asymmetric delay lines are used, i.e. ones that only delay the request signal. In all other protocols it is less probable and the differences are not that big however it can not be precluded.

In the 2-to-4 phase split unit the implementation is very similar. In detail the NULL-phase at the appropriate output gets initiated (request signal sent) at the same instant the input is acknowledged. In contrast to the 4-to-2 phase merge unit in this case the NULL values get additional time. As a consequence this implementation just yields an improvement if the DATA-phase is faster than the NULL-phase, which however is far less probable than the reverse case.

**Early DATA-phase:** Another possibility to increase the speed is to focus on the DATA-phase of the 4-phase inputs/outputs. Due to the fact that this phase holds all the information required it is not necessary to also wait for NULL values, because they are dropped anyway. Therefore in this method the units continue their operation as soon as new data are available.

Figure 5.8 shows the concept on the 4-to-2 phase merge unit (bundled data implementation).

Figure 5.7: Early NULL-phase shown for the 4-to-2 phase merge unit in bundled data implementation

In this case the DATA values show up before the NULL values ( $T_{DATA} < T_{NULL}$ ), however the output is not requested until both of them have shown up, unnecessarily, because the NULL values are dropped anyway. Therefore it is possible to forward the new data, i.e. to request the output, already at time  $t_{req}$ .

Figure 5.8: Early DATA-phase shown for the 4-to-2 phase merge unit in bundled data implementation

When used in the 2-to-4 phase split unit this design style is realised by acknowledging the

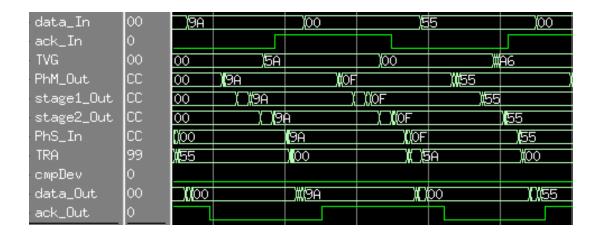

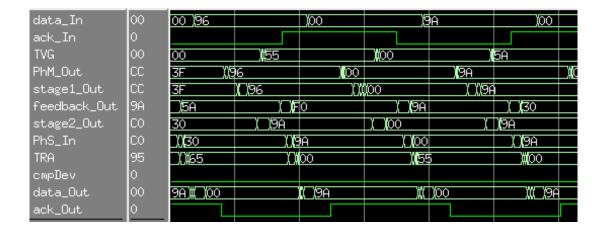

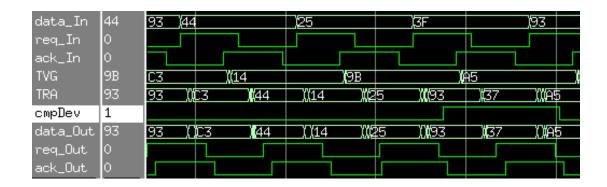

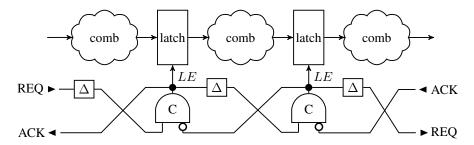

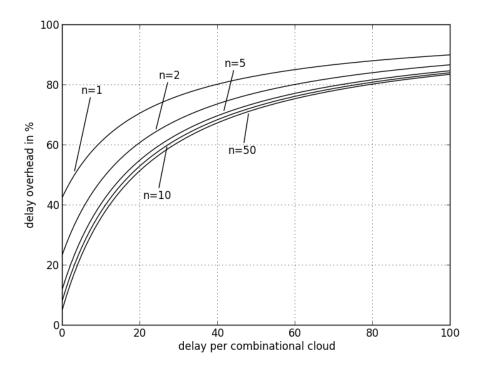

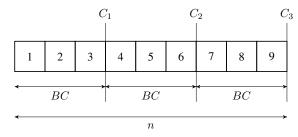

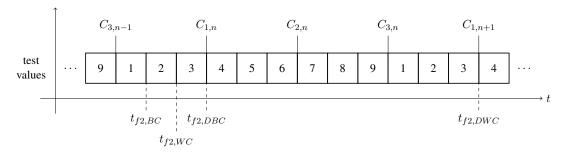

input as soon as the output that received the data has sent the acknowledge signal, even if the other one has not sent the acknowledge signal for its NULL-phase. As before this just yields an advantage if the DATA-phase is faster than the NULL-phase. Otherwise this design style falls back to the speed of the Basic Implementation.