# Implementing a Global Register Allocator for TCC

# **DIPLOMARBEIT**

zur Erlangung des akademischen Grades

# **Diplom-Ingenieur**

im Rahmen des Studiums

#### **Technische Informatik**

eingereicht von

#### Sebastian Falbesoner

Matrikelnummer 0725433

| an der<br>Fakultät für Informatik der | r Technischen Universität Wien |                         |

|---------------------------------------|--------------------------------|-------------------------|

| Betreuung: Ao.Univ.Prof.              | DiplIng. Dr.techn. Martin Ertl |                         |

|                                       |                                |                         |

|                                       |                                |                         |

| Wien, 22.08.2014                      | (Unterschrift Verfasser)       | (Unterschrift Betreuer) |

|                                       |                                |                         |

|                                       |                                |                         |

# Erklärung zur Verfassung der Arbeit

Sebastian Falbesoner Pachmüllergasse 1/14, 1120 Wien

| Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwen-   |

|----------------------------------------------------------------------------------------------|

| deten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit |

| - einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet    |

| im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als    |

| Entlehnung kenntlich gemacht habe.                                                           |

|                                                                                              |

| (Ort, Datum) | (Unterschrift Verfasser) |

|--------------|--------------------------|

In Dankbarkeit gewidmet meinen Eltern Lotte und Josef

#### **Abstract**

Register allocation is a long-standing research topic of computer science that has been studied extensively over the last decades. Its goal is to map a theoretically infinite number of program variables onto a finite, small set of CPU registers during compilation. Even though caches try to bridge the gap between register and memory access time, keeping as many values in registers as long as possible is crucial for good performance. Hence register allocation is still considered to be one of the most important compiler optimizations.

The present diploma thesis describes the process of implementing a register allocator for TCC, a small single-pass C compiler written in  $C^1$ . While TCC is very fast (up to a magnitude faster than gcc -00 for the x86 architecture), it produces code that is quite inefficient – some naive kind of register allocation is done only on the basis of statements. Our goal of implementing register allocation done on the basis of whole functions, that is, global register allocation, should hence result in a notable performance increase.

As prerequesite for register allocation in TCC, a proper IR (*Intermediate Representation*) needs to be generated in a first pass. On top of this internal representation, live variable analysis, register allocation and finally the code generation is then performed. We determine the variable live intervals with an extraordinarily simple approach that avoids the usual costly data-flow analysis techniques – it trades off the accuracy of the calculated intervals for higher execution speed. For the register allocation we use *Linear Scan*, a strategy that doesn't abstract the problem to graph coloring, but rather takes a simple approach involving the linear traversal of variable live intervals. While linear scan is very fast, it is stated that the generated code is almost as efficient as with graph coloring, making it a popular choice for JIT compilers.

As target machine, ARM, a classical RISC architecture, now widespread especially in mobile phones and in many other embedded systems, is chosen. Since data processing operands must not reside in memory in this *Load/Store architecture*, register allocation is even more important.

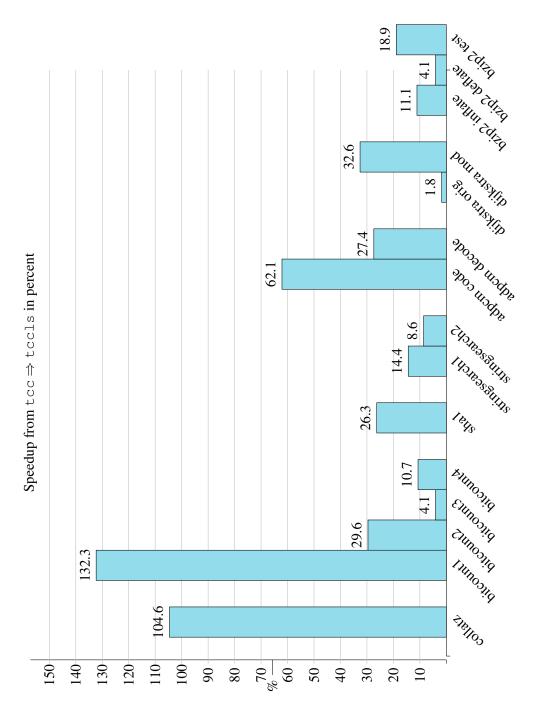

We determine the performance gain with various test applications, predominantly from the benchmark suite *MiBench*. Additionally, we compare compile-time as well as run-time performance with the widespread compiler gcc.

The execution time speedup of code generated by our implementation is about 32% on average (compared to the original TCC), while the compile-time is increased only marginally and is still an order of magnitude lower than for gcc without any optimization. Consequently, our register allocator implementation is an attractive trade-off for dynamic code generation with TCC.

<sup>&</sup>lt;sup>1</sup>of course, TCC itself can also be compiled with TCC

#### Kurzfassung

Registerzuteilung (engl. register allocation) ist eines der ältesten Forschungsthemen in der Informatik, welches im Laufe der letzten Jahrzehnte ausgiebig untersucht wurde. Das Ziel besteht darin, bei der Übersetzung von Programmen eine theoretisch unendliche Anzahl an Programmvariablen einer endlichen, kleinen Menge an verfügbaren Prozessor-Registern zuzuordnen. Auch wenn mit Hilfe von Caches die Kluft zwischen Register- und Speicherzugriffszeit überbrückt wird, so ist es doch wichtig, so viele Werte wie möglich so lange wie möglich in Registern zu halten, um eine gute Leistung zu erzielen. Somit wird Registerzuteilung nach wie vor als eine der wichtigsten Compileroptimierungen angesehen.

Die vorliegende Diplomarbeit beschreibt den Vorgang der Implementierung eines Registerallokators für TCC, einem kleinen Ein-Pass C-Compiler, der selbst auch in C geschrieben ist<sup>2</sup>. TCC ist sehr schnell (bis zu zehnmal schneller als gcc -00 für die x86-Architektur), erzeugt jedoch sehr ineffizienten Code – eine sehr einfache Art der Registerzuteilung wird nur auf Basis von Anweisungen gemacht. Unser Ziel, Registerzuweisung auf Basis von ganzen Funktionen zu implementieren (d.h. einen *globalen Registerallokator*), sollte somit einen deutlichen Geschwindigkeitszuwachs bringen.

Als Voraussetzung für einen Registerallokator in TCC muss ein passender Zwischencode (engl. IR, *Intermediate Representation*) in einem ersten Durchlauf erzeugt werden. Auf Basis dieser internen Repräsentation können dann die Lebensdaueranalyse der Variablen, Registerzuteilung und letztendlich die Codeerzeugung durchgeführt werden. Wir bestimmen die Lebensdauerintervalle der Variablen mit einem außergewöhnlich einfachen Algorithmus, der die üblichen Techniken der Datenflussanalyse vermeidet – die Genauigkeit der ermittelten Intervalle wird zugunsten einer höheren Ausführungsgeschwindigkeit geopfert. Für die Registerzuteilung benutzen wir *Linear Scan*, eine Strategie welche das Problem nicht auf Graphenfärbung reduziert, sondern mit einer sehr einfachen Vorgangsweise arbeitet, welche lediglich einen sequentiellen Durchlauf von den aktiven Intervallen (engl. *live intervals*) der Variablen benötigt. Obwohl die Strategie sehr schnell ist, wird angegeben dass der erzeugte Code beinahe so effizient ist wie jener von Graphenfärbungs-Algorithmen. Aufgrund dieser Tatsache ist Linear Scan sehr beliebt für JIT Compiler.

Als Zielarchitektur wird ARM gewählt, eine klassische RISC-Architektur, die mittlerweile weitverbreitet in Mobiltelefonen als auch in vielen anderen eingebetteten Systemen ist. Da in dieser *Load/Store-Architektur* die Operanden bei Datenverarbeitungsoperationen nicht im Speicher liegen dürfen, ist Registerzuteilung hier besonders wichtig.

Wir ermitteln den Geschwindigkeitszuwachs der Implementierung mit verschiedensten Testprogrammen, die vorwiegend von der Benchmark-Sammlung *MiBench* stammen. Zusätzlich vergleichen wir sowohl die Übersetzungs-Zeit- als auch die Laufzeit-Leistung mit dem weitverbreiteten Compiler gcc.

Unsere Implementierung erzeugt Code der im Durchschnitt um ca. 32% schneller ist (verglichen mit dem originalen TCC), wobei sich die Übersetzungs-Zeit nur marginal erhöht und immer noch über zehn Mal niedriger ist als für gcc ohne jegliche Optimierung. Somit ist unsere Implementierung des Registerallokators ein guter Kompromiss für dynamische Codeerzeugung mit TCC.

<sup>&</sup>lt;sup>2</sup>natürlich lässt sich TCC auch mit TCC kompilieren

# **Contents**

| Al | Abstract |                                                  |    |  |

|----|----------|--------------------------------------------------|----|--|

| Κι | urzfas   | ssung                                            | iv |  |

| 1  | Intr     | oduction                                         | 1  |  |

|    | 1.1      | Register Allocation                              | 1  |  |

|    | 1.2      | TCC – The Tiny C Compiler                        | 2  |  |

|    | 1.3      | ARM Architecture                                 | 3  |  |

|    | 1.4      | Goal                                             | 3  |  |

|    | 1.5      | Source Code                                      | 3  |  |

|    | 1.6      | Outline                                          | 3  |  |

| 2  | Regi     | ister Allocation and Related Work                | 5  |  |

|    | 2.1      | Motivation                                       | 5  |  |

|    | 2.2      | Subproblems of Register Allocation               | 6  |  |

|    | 2.3      | Register Allocation Scope                        | 6  |  |

|    | 2.4      | Liveness Analysis – Preliminary                  | 7  |  |

|    | 2.5      | Graph Coloring                                   | 7  |  |

|    | 2.6      | Recent Research involving SSA and Chordal Graphs | 10 |  |

|    | 2.7      | Linear Scan                                      | 11 |  |

|    | 2.8      | Other Approaches                                 | 15 |  |

| 3  | TCC      | C Internals                                      | 17 |  |

|    | 3.1      | Overview and Features                            | 17 |  |

|    | 3.2      | Overview of Modules and Phases                   | 18 |  |

|    | 3.3      | Lexical Analysis                                 | 19 |  |

|    | 3.4      | Syntax Analysis                                  | 20 |  |

|    | 3.5      | Syntax-Directed Translation                      | 21 |  |

|    | 3.6      | Simple Optimizations                             | 22 |  |

|    | 3.7      | Backpatching                                     | 22 |  |

|    | 3.8      | Register Usage and Code Quality                  | 23 |  |

*CONTENTS* vi

| 4  | Impl | ementation Considerations for the Proof-of-Concept         | 25 |

|----|------|------------------------------------------------------------|----|

|    | 4.1  | Choice of the Global Register Allocation Strategy          | 25 |

|    | 4.2  | Choice of the Target Architecture                          | 26 |

|    | 4.3  | Language support restrictions                              | 26 |

|    | 4.4  | The Big Picture                                            | 27 |

| 5  | Step | 1 - Implementing an Intermediate Representation            | 28 |

|    | 5.1  | Implementing the Additional Pass                           | 28 |

|    | 5.2  | Abstracting Variables with Virtual Registers               | 29 |

|    | 5.3  | IR Instruction Set                                         | 30 |

|    | 5.4  | Simple Expressions                                         | 34 |

|    | 5.5  | Boolean Expressions and Control-Flow Statements            | 36 |

|    | 5.6  | Function Calls                                             | 37 |

| 6  | Step | 2 – Calculating Variable Live Intervals                    | 39 |

|    | 6.1  | Simple Approach                                            | 39 |

|    | 6.2  | Restriction                                                | 41 |

|    | 6.3  | Interface to next phase                                    | 41 |

| 7  | Step | 3 – Performing Global Register Allocation with Linear Scan | 42 |

|    | 7.1  | Register Set Mapping                                       | 42 |

|    | 7.2  | Relevant Data Structures                                   | 43 |

|    | 7.3  | Algorithm                                                  | 44 |

|    | 7.4  | Interface to next phase                                    | 45 |

| 8  | Step | 4 – Generate Target Code                                   | 46 |

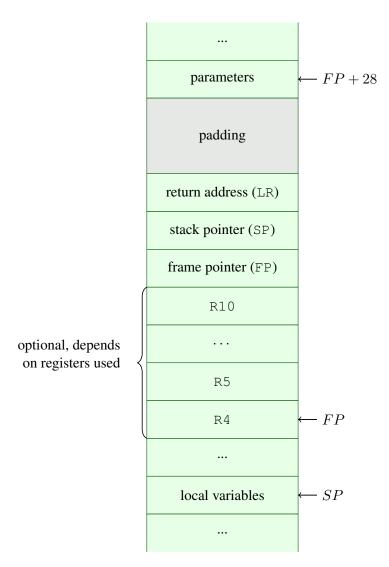

|    | 8.1  | Prologue and Epilogue                                      | 46 |

|    | 8.2  | Data-Processing Instructions                               | 48 |

|    | 8.3  | Generation of Spilling Code                                | 49 |

|    | 8.4  | Jumps and Branches                                         | 51 |

|    | 8.5  | Function Calls                                             | 51 |

| 9  | Resu |                                                            | 53 |

|    | 9.1  | Test Environment and Methods                               | 53 |

|    | 9.2  | Simple Showcase Example: The Collatz Conjecture            | 54 |

|    | 9.3  | MiBench Benchmarks                                         | 56 |

|    | 9.4  | Complex Benchmark                                          | 59 |

|    | 9.5  | Run-Time Evaluation                                        | 59 |

|    | 9.6  | Compile-Time Evaluation                                    | 63 |

|    | 9.7  | Implementation Effort                                      | 63 |

| 10 | Cone | clusions and Future Work                                   | 64 |

|    | 10.1 | Further Implementation                                     | 64 |

|    | 10.2 | Future Projects                                            | 65 |

| C  | ONTE              | NTS                                       | vii                  |

|----|-------------------|-------------------------------------------|----------------------|

| A  | A.1<br>A.2<br>A.3 | ARM Architecture History and Overview     | 66<br>66<br>67<br>67 |

| В  | The               | Raspberry Pi                              | 73                   |

| C  | Imp               | lementation Code Snippets                 | 75                   |

|    | C.1               | IR Generation (tccgen.c/tccir.c)          | 75                   |

|    | C.2               | Liveness Analysis (tccir.c)               | 82                   |

|    | C.3               | Linear Scan Register Allocation (tccls.c) | 85                   |

|    | C.4               | Code Generation (tccir.c)                 | 87                   |

| Bi | bliogr            | aphy                                      | 91                   |

CHAPTER 1

# Introduction

Compilers usually have the two main goals of generating *correct* and *fast* code. For dynamic code generators however, compile-time speed can be even an more important factor than runtime speed. *TCC* is a C-compiler which is very fast and well-suited for dynamic code generation, but it creates fairly inefficient code. By extending TCC with a *register allocation* phase, the code quality can be increased significantly with only a marginal loss of the high compilation speed.

# 1.1 Register Allocation

Due to the gap between register and memory access time in computers, one of the fundamental, obvious rules for writing efficient programs is to take advantage of the register set as much as possible. Processing data in main memory can be up to three magnitudes slower than directly on the CPU-near register set. The advent of data caches sped up operations on memory on average, but the rule still holds and bad register utilization can make drastic differences in program performance.

However, nowadays programs are rarely written in assembly language anymore, but higher-level languages are used where the programmer doesn't have control about the register set. Hence this is now the task of the compiler, called *register allocation*. That optimization phase is responsible for assigning a theoretically unbounded number of program variables to a bounded number of physical registers. If the number of active variables exceeds the available registers, registers need to be *spilled*, i.e. stored to a dedicated memory location, usually the stack.

Register allocation is considered to be a very central optimization, and virtually every widespread compiler nowadays implements it. Hennessy and Patterson state in their famous standard work about computer architecture the following:

"Because of the central role that register allocation plays, both in speeding up the code and in making other optimizations useful, it is one of the most important – if not the most important – optimizations."

<sup>&</sup>lt;sup>1</sup>[HP90]

Register allocation strategies are divided into *local* and *global*, where local algorithms see basic blocks as the basic unit, and global ones aim at performing register allocation over whole functions.

The traditional solution of globally approaching the register allocation problem is to reduce it to a graph coloring problem, but alternative strategies also exist. This is described in more detail in the next chapter.

# 1.2 TCC – The Tiny C Compiler

*TCC*, short for *Tiny C Compiler* (also called *TinyCC*) is a small C compiler written by Fabrice Bellard<sup>2</sup>. While the first versions targeted only the x86 architecture, support for x86-64, ARM and TMS320C67 was added over the years by various contributors.

TCC has a number of interesting properties that distinguish it from other C compilers:

- **Speed**: TCC is a single-pass compiler that directly generates binary code "on the fly", without relying on any external tools, not even an assembler. This makes it obviously very fast a compilation speed test for the *Links Browser* project<sup>3</sup> found that TCC is about nine times faster than gcc on the x86 architecture, where the time includes assembly and linking. For the ARM architecture, we observed a speedup factor of even 12 and above (see chapter 9).

- **Size**: TCC is very small. For example, the x86 TCC executable needs about 100kB. This, together with the speed factor, makes it an interesting option to use it on systems with limited resources, e.g. rescue disks or embedded systems.

- Scripting support: Provided with the -run switch on the command line, TCC directly compiles, assembles and links the given C files into memory and executes it. This enables the creation of command line scripts in C.

- Dynamic code generation: With libtcc, the core library of the compiler, TCC can be used as backend for dynamic code generation. By simply passing C code strings to a library function, it can be compiled and then run at runtime. There also exist bindings to enable scripting languages to access libtcc, for example Luatcc for Lua<sup>4</sup>.

TCC implements all of the ANSI C (C89/C90) standard and supports, apart from complex and imaginary numbers and variable length arrays, also the newer C99 standard<sup>5</sup>. Additionally, it also supports some GNU extensions and provides inline assembly support for x86.

The project is distributed under the GNU Lesser General Public License (LGPL). Currently it is maintained with the version-control system git; the repository can be received via the command git clone git://repo.or.cz/tinycc.git. An online version of it, including instructions on how to supply patches, is found on http://repo.or.cz/w/tinycc.git.

<sup>&</sup>lt;sup>2</sup>see http://bellard.org/tcc/

<sup>3</sup>see http://links.twibright.com/

<sup>&</sup>lt;sup>4</sup>see http://piratery.net/luatcc/

<sup>&</sup>lt;sup>5</sup>see the TCC reference documentation http://bellard.org/tcc/tcc-doc.html

#### 1.3 ARM Architecture

ARM is a popular 32-bit RISC architecture that is mostly known for its use in mobile phones. The simple instruction set with fixed-size encoding, the relatively large uniform register set (15 general purpose registers) and simple addressing modes (Load/Store architecture) make it a pleasant choice for code generation.

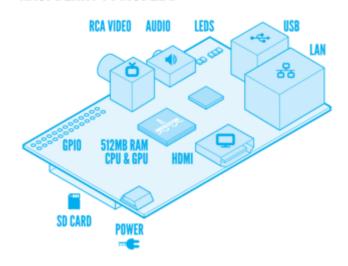

Since ARM is especially widespread in use in embedded domains, our hope is to make TCC an attractive option for those systems. We develop the implementation on the Raspberry Pi (see Appendix B), a credit-card sized home computer that surely could profit from having an improved TCC, as fast alternative to qcc that still generates efficient code.

#### 1.4 Goal

The obvious drawback of TCC is that with the current code generation method, it is unable to generate optimized code. Hence an additional pass must be generated that allows the manipulation of *intermediate code* for global register allocation. On top of this IR, data-flow analysis, register allocation and finally code generation can then be implemented.

We have two conflicting goals on the implementation: While the quality of the generated code in terms of speed should clearly increase, TCC should still retain its notable property of high-speed compilation.

#### 1.5 Source Code

The source code of the implementation is version-controlled with Git and can be found on Bit-Bucket ( $\Rightarrow$  https://bitbucket.org/theStack/tccls\_poc.git). It was started with the latest official version 0.9.26 of TCC as basis, and we also applied all changes from the "mob" branch <sup>6</sup> up to July 24th, 2013.

#### 1.6 Outline

Chapter 2 gives an overview of register allocation strategies, predominantly graph coloring algorithms and linear scan. New research work in this field that has been done within the last decade, like register allocation for SSA-programs is also covered shortly.

Chapter 3 describes how the implementation of TCC works, with a focus on those parts that we need to modify for our register allocator. Several important decisions (choice of register allocation algorithm and target architecture) and simplifying restrictions are established in chapter 4. It also contains a short introduction on the development environment, the Raspberry Pi, and gives an outline on the implementation plan.

The base of our implementation, the generation of an IR (intermediate representation) that abstracts variable accesses with virtual registers, is described in chapter 5. The next step, the

$<sup>^6</sup>$ mob branches have the special property that everyone can push changes to it without authentication, similar to the concept of Wikipedia; see http://repo.or.cz/h/mob.html for more informations

variable live interval calculation, is covered in chapter 6. Chapter 7 describes the mapping of virtual registers to physical registers, that is, the global register allocation with linear scan. Finally, chapter 8 covers the important aspect of generating the target code out of the register-allocated IR. This includes generating spill code.

Measurements of compile-time and run-time efficiency, compared to other compilers, are presented in chapter 9.

Chapter 10 concludes the thesis and gives some ideas on how the implementation could be further improved in the future.

Appendix A covers the ARM architecture, including the *Procedure Call Standard* (ARM EABI) that plays an important role for the register allocation. Appendix B lists details about our target machine, the Raspberry Pi. Appendix C contains relevant code snippets of our implementation.

# **Register Allocation and Related Work**

#### 2.1 Motivation

An important criterion for the code generating part of an optimizing compiler is *where* the instruction operands (this is, predominantly, program variables and temporary values) should be stored: in memory or in registers? Obviously, due to the nature of the memory hierarchy [HP90], register access is much faster than memory access.

Even if we assumed that all instructions take the same amount of time, keeping values in registers can be beneficial in terms of instruction count. On typical Load/Store architectures like ARM, all instruction operands for ALU operations must be registers. Hence for every modification of a variable that is stored in memory (that is, *spilled*), an extra load and store instruction pair is needed.<sup>1</sup> If we take as example a simple increment of a variable on a RISC machine, this needs three instruction if the variable in memory versus one if it is kept in a register, as shown in Table 2.1.

| operand in memory location $n$            | operand in register r |

|-------------------------------------------|-----------------------|

| $t \leftarrow \mathtt{mem} [n] \; (load)$ |                       |

| t ← t + 1                                 | r ← r + 1             |

| $t \rightarrow mem[n]$ (store)            |                       |

Table 2.1: Instructions for the simple assignment x := x + 1 depending on the storage

The register file on common architectures is still quite limited: ARM has 15 general purpose registers available (see Appendix A), while the dominating architecture for desktop computers, x86, even only has as few as eight register available. A subset of the register set is usually reserved for special purposes (e.g. stack pointer, frame pointer, return address) and can't be used for holding values of variables or temporaries. Hence the decision on which program value

<sup>&</sup>lt;sup>1</sup>note that there exist architectures like x86 where memory operands are possible at least in some instructions

resides in a register is even more crucial for improving the performance by minimizing the spilling instructions.

# 2.2 Subproblems of Register Allocation

The problem of register allocation actually implies three subproblems:

- What values in a program should reside in registers, what values should be stored in memory? (spilling)<sup>2</sup>

- In which register should each value reside? (register assignment)

- Given two non-interfering variables A and B that are related by an assignment (A = B), should we map them to the same register? (**coalescing**)

For optimal register allocation all of those subproblems have to be taken into account efficiently, which is still an open problem. For example, most early approaches were concentrated too much on assigning and spilling, ignoring the influence of a good coalescing strategy.

# 2.3 Register Allocation Scope

There are generally different approaches to register allocation, depending on the scope of the variables it is applied on. The original TCC uses some simple register allocation only based on *expressions*, which is very ineffective, as we will show in section 3.8. Usually the allocation is performed on a larger variable scope to minimize the amount of spilling instructions, with the following two main approaches:

- Local register allocation: based on the scope of basic blocks (that is, instruction sequences with only one entry and exit points each)

- **Global register allocation**: based on the scope of whole procedures, therefore also called *intraprocedural register allocation*

As third category there also exists *interprocedural register allocation*, which aims to find a register mapping over the "whole program" scope. To the knowledge of the author, though various research papers have appeared about this within the last two decades [WG92, KF96], no common compiler exists that implements this strategy.

This thesis is focussed solely on global register allocation, which is nowadays the most widespread approach in industrial compilers.

<sup>&</sup>lt;sup>2</sup>in early research prior to graph coloring approaches, the term *register allocation* addressed only this subproblem [ASU86]

# 2.4 Liveness Analysis – Preliminary

As a preliminary step for any register allocation algorithm, the compiler needs to find out which variables are live at the same time. This process called *liveness analysis* is essential, because then the values are not allowed to be assigned to the same register. Research papers about register allocation usually don't discuss liveness analysis, but rather assume that this information is already given. A simplified liveness analysis for our implementation, suitable as input for the linear scan algorithm, is described in chapter 6.

The following algorithms described are all independent of any platform and only assume that we have K uniform physical registers available that can be used.

# 2.5 Graph Coloring

One fundamental discovery for an efficient solution to global register allocation was its connection to the mathematical problem of graph coloring. This has first been recognized by John Cocke<sup>3</sup> in the early 70s [AC71], but the first implementation was not until ten years later by Chaitin (see below).

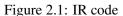

With the information gathered by liveness analysis, the compiler can construct an undirected graph in which every vertex represents a unique variable, and edges between vertices mean that the lifespan of the two variables overlap.

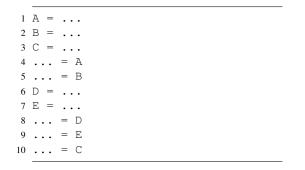

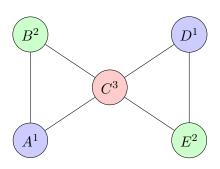

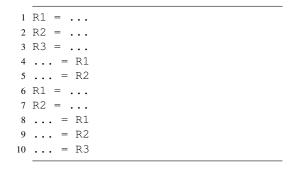

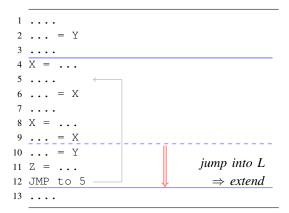

Consider the intermediate code skeleton in Figure 2.1, involving five variables A to E.

Figure 2.2: Interference Graph

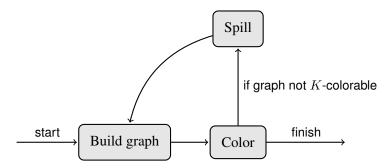

Figure 2.2 shows the so-called *interference graph* corresponding to the IR code to its left. The problem of register allocation can now be approached by K-coloring this graph, where each color represents one physical register. Two vertices sharing an edge may not not be assigned the same color. Figure 2.3 shows a possible coloring for our example, assuming we have three registers available (K = 3). The substitued IR code is shown in Figure 2.4.

There are situations where a coloring is not possible, because the number of variables that are live at the same time is larger than K (theoretically it can be unbounded). In this case, some registers need to be spilled, that is, moved to memory. As the intermediate code changes by the

<sup>&</sup>lt;sup>3</sup>often called "the father of RISC architecture"

Figure 2.3: Colored Interference Graph (K = 3)

Figure 2.4: IR code with virtual registers substituted by physical registers

insertion of spill code, the graph needs to be rebuilt and the process repeats, until the graph is K-colorable (in other words: its chromatic number is  $\leq K$ ) and no more spills are needed.

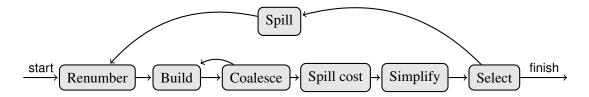

The general scheme for graph-coloring-based register allocation is shown in Figure 2.5.

Figure 2.5: Steps in register allocation based on graph coloring

Since the problem of determining whether an arbitrary graph G is n-colorable is NP-complete (for n > 2), so is register allocation<sup>4</sup>, and heuristic techniques have to be used to search for a coloring.

#### Chaitin

The first global register allocator based on graph coloring was designed by G.J. Chaitin [CAC<sup>+</sup>81] in the course of implementing a PL/I compiler for the IBM System/370. It is commonly called the "Yorktown allocator", as the working place was in Yorktown Heights.

In Chaitin's first approach, the spilling was done randomly when the graph was not K-colorable. In a later paper from 1982 [Cha82], smarter heuristics were introduced (a *spill cost*

<sup>&</sup>lt;sup>4</sup>Proof sketch

Chaitin showed that given an arbitrary graph, a program can be created with this exact interference graph  $[CAC^{+}81]$ . Hence, if we could solve register allocation, we could also color any graph (polynomial reduction). As a result, register allocation is NP-complete.

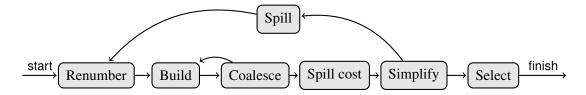

phase), when the allocator was implemented in the PL.8 compiler for the IBM 801 RISC system. The register allocation scheme is shown in figure 2.6.

Figure 2.6: Register allocation scheme of Chaitin's Yorktown allocator

The coloring procedure was based on *Kempe's algorithm* (from 1879). The idea is that given a graph G that contains a vertex v with degree < K, the graph is K-colorable if G without the node v is K-colorable. Knowing that, we can iterately remove nodes with a degree < K and push them on a stack (this is the *simplify* stage). If this doesn't work (e.g. there are no nodes with degree < K), a node has to be removed, actual spill code is inserted and we start again over with the graph building stage. If the empty graph is reached in the *simplify* stage we know that the graph can be K-colored and are finished: each vertex is popped again from the stack and colored (this is the *select* stage).

Between building and coloring the graph, nodes are coalesced whenever possible. This aggessive coalescing policy turned out to be a problem later, when the SSA-form arrived and the large number of temporaries that got coalesced led to huge live ranges. Those would often interfere with too many variables, introducing many spills.

#### Chaitin/Briggs

Preston Briggs improved on the Yorktown allocator in 1992 in the course of his PhD thesis [Bri92]. The main contribution was a better graph coloring heuristic that could produce more efficient code by saving many spills.

The register allocation scheme for the optimistic "Chaitin/Briggs" approach is shown in figure 2.7. This looks quite similar to the original approach, with the only difference that the

Figure 2.7: Register allocation scheme of Brigg's improved allocator

back-edge representing the spill code insertion occurs one step later, namely at the *select* phase

instead of the *simplify* phase. Instead of failing as soon as a node has degree  $\geq K$ , it is just left and the allocator continues with the hope to color it later, when it is popped back from the stack. Then only in the *select* phase, if a node can't be colored, it is spilled and the graph is rebuilt.

It turned out that the method can color more graphs. Briggs also introduced the *conservative* coalescing strategy which should solve the problem of the too aggressive coalescing used in the original allocator. However, this was again too conservative.

#### **Iterated Register Coalescing**

While earlier papers on register allocation algorithms based on graph coloring were primarily focused on coloring heuristics, the research community started to notice that good coalescing strategies are equally important. Too aggressive coalescing strategies (like Chaitin's) can make graphs uncolorable, introducing spills which could be avoided, while too conservative strategies (like Brigg's) leave too many move instructions in the code.

Appel and George's "Iterated Register Coalescing" algorithm [GA96] published in 1996 extends Brigg's allocation scheme with a coalescing strategy that is safe but still aggressive. By interleaving Chaitin's simplification steps and Brigg's conservatice coalescing, much more move instructions can be eliminated, without introducing too many spills.

It is a standard algorithm for implementing new register allocations, especially in the research community, and every new register allocation scheme is compared to it.

# 2.6 Recent Research involving SSA and Chordal Graphs

Recent research on graph-coloring-based register allocation has been published that targets on programs internally stored in SSA (*static single assignment*) form, which is the standard representation for modern compilers.

In SSA form, each variable is assigned only once. For variables that depend on program flow, special so called  $\phi$ -nodes are created. Before register allocation, those abstract nodes are substituted by concrete move instructions. Note that this leads to a large number of temporary variables, making a good coalescing strategy even more important.

Around 2005, different research groups showed that interference graphs of programs in SSA form are always *chordal* [HG06]. A graph is said to be chordal if every cycle of a length at least 4 has a cycle chord, which is an edge that connects two non-adjacent vertices of the cycle.<sup>5</sup>

Chordal graphs have many interesting properties, the most important one concerning register allocation being that chordal graphs can be colored optimally in linear time. An obvious idea is to transform programs into SSA form (in polynomial time), applying register allocation on it, and then applying the classical SSA elimination to do register allocation in overall polynomial time. However, this approach doesn't work since this elimination breaks the coloring and there is no possibility to make use of the SSA form to get polynomial coloring, as shown by Pereira [PP06]. Hence, register allocation after classical SSA elimination is also NP-complete.

Pereira and Palsberg proposed a simple algorithm which takes advantage of the useful properties of chordal graphs [PP05]. The technique is not relying on SSA form, but is based on the

<sup>&</sup>lt;sup>5</sup>see http://mathworld.wolfram.com/ChordalGraph.html for examples

observation that a very high percentage of functions have chordal interference graphs (95% of the methods for the Java 1.5 standard library). The idea is to perform optimally if the function has a chordal graph with a greedy coloring, and perform well otherwise. Contrary to other graph coloring algorithms, it is non-iterative. The authors claim that the algorithm is competitive to iterated register coalescing, and can even outperform it for settings with few registers.

#### 2.7 Linear Scan

A completely different approach to register allocation called *Linear Scan* was presented in the late nineties by Poletto and Sarkar [PS99].<sup>6</sup> It doesn't use graph coloring, but rather tackles the problem by using a greedy algorithm for assigning colors to an ordered sequence of intervals, in linear-time.

This approach was actually not entirely new, but is closely related to the *bin packing* register allocation that evolved during the work of the production quality compiler-compiler project (PQCC) at Carnegie Mellon University [LCH<sup>+</sup>80], led by William Wulf. His Bliss/11 compiler implements the register allocation phase in the *TNBIND* module which treats registers as bins with one valid value at any point [WJW<sup>+</sup>75]. The constraint is that overlapping live ranges can not be assigned to the same bin. If there is no bin left for a register allocation candidate, the one with the lowest cost (determined by a special heuristic based on lifetime – candidates distributed over a large span are generally less important) is decided to be spilled. This method was also used later in the GEM optimizing compiler (see the "second-chance binpacking" refinement below).

Linear Scan got very popular within the last decades and is used many real world compilers such as LLVM<sup>7</sup> or the Java HotSpot client compiler.

#### **Description with Example**

#### Prerequisites: instruction numbering and live intervals

Linear scan assumes all instruction in the intermediate representation to be numbered according to some order. In the original paper they assume depth-first ordering, while the possibility of numbering the instruction simply as how they appear in the IR is also mentioned<sup>8</sup>.

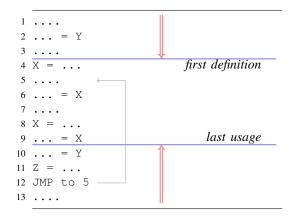

A central notion for linear scan is the *live interval*: [i,j] is said to be a live interval for variable/value v if there is no instruction with number j' > j such that v is live at j', and there is no instruction with number i' < i such that v is live at i'. Note that this is a conservative approximation of the usual live ranges, since there could be intervals within [i,j] in which v is not live.

<sup>&</sup>lt;sup>6</sup>The term "linear scan" was originally coined in an earlier paper about a dynamic code generation called *tcc* [PEK97] which implements the "Tick-C" programming language. Note that while also named "tcc", this a different compiler than the one covered in this thesis.

<sup>&</sup>lt;sup>7</sup>since the release of version 3.0 of LLVM in 2011, the default allocator is a new greedy register allocator (see http://blog.llvm.org/2011/09/greedy-register-allocation-in-llvm-30. html), but linear scan can still be enabled

<sup>&</sup>lt;sup>8</sup>this approach is used in our implementation, see chapter 5

passed interval is spilled

```

Algorithm 1 Linear Scan Register Allocation

1: procedure LSRA(Intervals) \triangleright Intervals is sorted in order of increasing starting points

2:

Active \leftarrow \{\}

for LI \in Intervals do

b traverse list of live intervals

3:

EXPIREOLDINTERVALS(LI)

4:

if |Active| = K then

▶ all registers are used, we have to spill

5:

SPILLATINTERVAL(LI)

6:

else

> still registers available, register can be assigned

7:

LI_{register} \leftarrow \texttt{RegisterPoolGet}()

8:

Active \leftarrow Active \cup LI

9:

10:

end if

11:

end for

12: end procedure

13: procedure ExpireOldIntervals(CurrentInterval)

for LI \in Active do

> traverse list of active intervals

14:

15:

if LI_{endpoint} \geq CurrentInterval_{startpoint} then

return

⊳ no old intervals anymore

16:

end if

17:

⊳ expire old interval and release register

Active \leftarrow Active \setminus LI

18:

19:

REGISTERPOOLADD(LI_{register})

20:

end for

21: end procedure

22: procedure SPILLATINTERVAL(Interval)

Spill \leftarrow Active_{last}

▷ spilling heuristic: widest distance of endpoint

23:

if Spill_{endpoint} > Interval_{endpoint} then

\triangleright interval Spill is spilled

24:

25:

Interval_{register} \leftarrow Spill_{register}

Spill_{location} \leftarrow NewStackLocation()

26:

Active \leftarrow (Active \setminus Spill) \cup Interval

27:

else

28:

```

#### Algorithm

end if

31: end procedure

29:

30:

In a first step, with the information from liveness analysis, live intervals are computed. Those are stored in a list that is sorted in order of increasing starting points. The linear traversal of this list is the outer skeleton of the linear scan method, as shown in Algorithm 1.

$Interval_{location} \leftarrow NewStackLocation()$

The central data structure is the *active list*, which contains the live intervals that overlap at the current point. The list is kept sorted in order of increasing end points and is empty at the beginning of the algorithm.

At each iteration of the live intervals, the following simple steps happen (lines 4–10):

- 1. Expiring of old live intervals (ExpireOldIntervals ()):

The list of active intervals is scanned. All active intervals where the endpoints precede the current interval's starting point are not overlapping and thus not relevant anymore, they are "expired". This leads to their removal from the active list and the corresponding register is marked as free again. Note that the traversal of the active list can be aborted as soon as an endpoint is behind the current interval's starting point, since the active list is sorted in order of increasing end points.

- 2. Register assignment (else-branch):

If no spilling is needed (see step below), we can choose a register from the pool and assign it to the current interval. It is added to the active list as well.

- 3. Spilling (if-branch, SpillAtInterval()):

The length of the active list shows how many registers are already used. If it is already as large as the number of available registers K, we don't have a register left for the current interval, and one interval must be spilled. While there are several heuristics for choosing a live interval to spill, the one in the paper is simple: it takes the interval that ends last, furthest away from the current point.

#### **Example**

Consider again the IR code example from Figure 2.1. Liveness analysis (which is trivial for this straight-code example) yields the following live intervals:

$$A \leftarrow [1, 4], B \leftarrow [2, 5], C \leftarrow [3, 10], D \leftarrow [6, 8], E \leftarrow [7, 9]$$

To show how linear scan handles spilling, we assume that the number of available physical registers K=2. Note that the intervals are already listed in order of increasing starting points. The following steps happen in each iteration of the linear scan traversal loop:

- 1. Interval A: no intervals expired,  $A_{reg} \leftarrow R1$ ,  $Active \leftarrow \{A\}$

- 2. Interval B: no intervals expired,  $B_{reg} \leftarrow R2$ ,  $Active \leftarrow \{A, B\}$

- 3. <u>Interval C</u>: no intervals expired, spilling needed since |Active| = |K|**C** is spilled since its endpoint is larger than the endpoints of A and B; Active unchanged

- 4. <u>Interval D</u>: A and B are expired and get removed from the Active set, registers R1 and R2 are available again,  $D_{reg} \leftarrow R1$ ,  $Active \leftarrow \{D\}$

- 5. Interval E: no intervals expired,  $E_{reg} \leftarrow R2$ ,  $Active \leftarrow \{D, E\}$

#### Conclusion

If V denotes the number of canditates for register allocation (that is, variables or temporary values, respectively live intervals), the algorithm takes O(V) time – K is bounded and assumed to be constant and hence doesn't influence the complexity.

There are two obvious advantages of linear scan over graph coloring approaches that make it an attractive choice: its simplicity, leading to comparatively low implementation effort, and the high compile-time speed (see also section 4.1). The latter is especially important for JIT compilers and dynamic compilation systems.

The drawback of linear scan is the quality of the generated code. Since live ranges are approximated and lifetime holes are not recognized, often many spills are unnecessarily generated.

The original paper argues that while linear scan is significantly faster than graph coloring (which even holds for fast graph coloring allocators that don't perform coalescing), the generated code is still efficient and only about 10% worse [PS99]. To our knowledge, there is no up to date research study that compares linear scan to other register allocation algorithms to verify this for state-of-the-art implementations and architectures.

#### Refinements

#### Second-chance binpacking

An improved, more complex variant of linear scan is called *second-chance binpacking* [THS98]. It is based on the bin packing approach used in the GEM optimizing compiler by the Digital Equipment Corporation [BCD<sup>+</sup>92]. By keeping track of the register allocation candidate's *live range holes* (e.g. intervals during which no useful values are maintained) the register file can be better used and hence less spills are needed. Another notable difference to linear scan is that the algorithm performs register allocation and instruction rewriting in a single pass. This enables spilled allocation candidates to have multiple chance to reside in registers during their lifetimes, hence the name.

The improvements result in a notable increase of compile-time. The original paper on linear scan compares to second-chance binpacking and suggests that there is only a marginal increase in performance of the produced code, while the allocation time almost doubles up for the presented benchmarks [PS99].

#### **Extended Linear Scan**

In 2007, Sarkar and Barik proposed two alternative algorithms based on linear scan called " $Extended\ Linear\ Scan$ " [SB07]. As motivation, the authors show that graph coloring, the defacto standard foundation for global register allocation, introduces unnecessary constraints and has some theoretical limitations. The basic extended linear scan algorithm (called  $ELS_0$ ) overcomes those limitations and based on that, a further extension of the basic algorithm (called  $ELS_1$ ) is presented. The former solves the problem for spill free register allocation (SFRA), while the latter covers register allocation with total spills (RATS), meaning that whole lifetime intervals are spilled.

Experimental results for a number of SPECint2000 benchmarks compare graph coloring with  $ELS_1$  and show that the compile-time speedups were significant (like for the original linear scan), while the resulting execution time also improved by 2.3% on average.

#### Linear scan for SSA form

Using linear scan on an IR which is in SSA form has several benefits, as pointed out by Wimmer and Franz [WF10]: first, for the calculation of the liveness intervals, no iterative data flow analysis is needed, since SSA form implies that there is only one definition for each variable. Secondly, tests on intersecting intervals during compilation can be omitted because non-intersection is already guaranteed by SSA form as well. Thirdly, the obligatory SSA deconstruction after register allocation can be integrated into the resolution phase.

Those advantages lead to both a lower compilation time as well as to a simpler implementation. The algorithm was implemented for the Java HotSpot client compiler, with the result that the compile-time time was decreased by 4% to 8% while the run-time was about equal, in one case even slightly better.

# 2.8 Other Approaches

Apart from the two major register allocation strategies, that is, graph coloring and linear scan, there have been proposed various other interesting and promising approaches within the last two decades [Pro09, Per08]:

• **Integer Linear Programming**: At this approach, the register allocation problem is modeled as constraints in a system of integer linear equations. Those equations, representing the interactions between registers and variables, can then be solved with well-known, optimized ILP solvers<sup>9</sup>.

The idea was first brought up in 1996 by Goodwin and Wilken [GW96], where they used 0-1-integer programming (a subclass of the integer linear programming model) for the formulation of the problem. While this solution produced very efficient code, it was too slow for practical use – it could take hours to find an optimal solution. The reason for this is the fact that integer linear programming is NP-complete, leading to a worst-case exponential running time.

To improve the ILP-based register allocation, Appel and George separated the phases between spilling and register assignment [AG01]. In a first step, the ILP solver finds the optimal solution to the question which variables should be kept in registers and which variables are spilled. For the remaining subproblems of coloring and coalescing, various solutions have been proposed so far, since the "optimal coalescing challenge" has been published in 2000.

$<sup>^9</sup> for \ example, \ lp\_solve, see \ http://sourceforge.net/projects/lpsolve/$

$<sup>^{10}{</sup>m see}$  http://www.cs.princeton.edu/~appel/coalesce

Shortly after this, George and Appel themselves had found a solution called *optimal coalescing*, where they again use integer linear programming to model coloring and coalescing. The reasearch was heavily focussed on architectures with few registers, predominantly the x86 architecture, where only six registers can be used for variables and temporaries. In practice the solution is, despite its name, not optimal and still too slow.

In 2006, Hack and Grund found a solution giving optimal results using a cutting-plane algorithm [GH07], which in turn again uses integer linear programming. It is faster than the approach from George and Appel – in cases where register allocation takes too long, the authors suggest to halt the computation and fall back to a more usual solver that doesn't take forever.

Though ILP-based register allocation is a very interesting approach with some advantages, it is still much slower than traditional approaches and is not implemented in industrial compilers yet.

• **PBQP**: The Partitioned Boolean Quadratic Problem (PBQP) belongs to the class of Quadratic Assignment Problems (QAP) and is a generalization of the graph coloring problem. PBQP is NP-complete, but a subclass of these problems can be solved in polynomial time.

The goal is to find a function of minimal cost, which is controlled by two sets of terms: the cost of assigning one variable x to another variable y (measured by a *local* cost function l(x,y)), and the cost given by the interactions between two variables, that is, assigning x to y and z to a (measured by a *related* cost function r(x,z,y,a)).

The algorithm by Scholz and Eckstein [SE02] solves in  $O(nm^3)$ , where n is the number of variables and m is the maximum size of any domain. The complexity of PBQP in regards of register allocation is  $O(|V|K^3)$ , where |V| is the number of variables in the source program.

• Puzzle-solving: The problem of register assignment is analogous to solving a collection of puzzles, as shown by Pereira in 2008 [QaPP08]. The register file is modeled as a puzzle board and the program variables as puzzle pieces. This approach takes linear time for a large number of architectures (including x86, PowerPC and StrongARM) and can match with widespread register allocators (e.g. the extended version of linear scan used by LLVM) both in regards of compile-time and run-time of the generated code.

# **TCC Internals**

The following sections describes the inner workings of TCC, with emphasis on the parts that are relevant for our extension. The informations apply to TCC version 0.9.26, the latest stable release (released in February 2013) at the time of writing.

#### 3.1 Overview and Features

Most modern compilers are constructed with the aid of generators for certain well-defined stages that can be described with appropriate formal languages, e.g. regular expressions for lexical analysis, context-free grammars for syntax analysis (examples of such generators include the prominent lex/yacc<sup>1</sup> duet). TCC goes the classical way in form of a single-pass compiler and implements all the stages "by hand".

TCC also doesn't rely on any external tools during run-time. Preprocessing is interweaved with lexical analysis (whereas gcc relies on cpp, the C preprocessor tool), an assembler is not needed since target code is output directly in binary format (whereas gcc relies on as, the GNU assembler), and even linking (whereas gcc relies on 1d, the GNU linker).

Hence, TCC is purely self-contained. This property as well as the obvious speed gain makes it an interesting option for interpreting C code. <sup>2</sup>

#### **Scripting support**

When started with the <code>-run</code> switch, TCC compiles the program into memory and directly starts it from there. In this way, C scripts can be easily provided in Linux systems similar to shell scripts by simply preceding the file with the she-bang "#!/usr/local/bin/tcc -run" and setting the executable bit.

<sup>1</sup>called flex/bison by now

<sup>&</sup>lt;sup>2</sup>since the whole code snippet is compiled at once before execution, it is in a strict sense not an interpreter, but rather a *load-run* compiler

With this mechanism, simple tasks can even be formulated as one-liners in the shell. Sometimes it would be comfortable to quickly try out how some small code snippets, e.g. calls to library functions, behave without the obligatory "save, compile and execute" cycle. This is possible with TCC by providing the -run switch and reading from *stdin* by putting the dash as "input file", for example:

```

$ echo 'int main() { printf("%d", time(0)); }' | tcc -run -

1397324291

```

#### **Dynamic code generation**

With the library libtcc, C code can be dynamically compiled and executed at runtime. The idea is to pass a single string containing the code to the library which compiles the code and stores it to the desired location, either memory or file system.

The following listing shows a minimum, pretty self-explanatory example of how to achieve this for a single trivial function adding two numbers (passed in line 13):

```

#include <stdlib.h>

#include "libtcc.h"

2

3

int main(int argc, char *argv[])

4

5

TCCState *s;

6

int size;

7

8

void* mem;

int (*func)(int, int);

9

10

s = tcc_new();

11

tcc_set_output_type(s, TCC_OUTPUT_MEMORY);

12

tcc_compile_string(s, "int foo(int x, int y) { return x+y; }");

13

14

size = tcc_relocate(s, NULL);

mem = malloc(size);

15

tcc_relocate(s, mem);

16

func = tcc_get_symbol(s, "foo");

17

18

printf("23 + 42 = %d\n", func(23, 42));

19

20

}

```

#### 3.2 Overview of Modules and Phases

TCC consists of the following modules:

- tcc.c: entry point, evaluates command-line arguments

- libtcc.c: directs the compilation process, provides interface for dynamic code generation

| category   | lexeme | token                       | notes                                    |

|------------|--------|-----------------------------|------------------------------------------|

| literal    | 1423   | TOK_CINT                    | literal value in tokc.i                  |

| operator   | ++     | TOK_INC                     |                                          |

| keyword    | for    | TOK_FOR                     |                                          |

| operator   | (      | ′ (′                        |                                          |

| identifier | foo    | $n \geq \text{TOK\_UIDENT}$ | every identifier has unique token number |

| keyword    | if     | TOK_IF                      |                                          |

| literal    | "bar"  | TOK_STR                     | literal value in tokc.cstr               |

| operator   | ->     | TOK_ARROW                   |                                          |

Table 3.1: Examples of some tokens in TCC

- <u>tccgen.c</u>: the core of the compiler, implements the top-down parser which directs the translation process

- tccpp.c: implements preprocessor and lexer

- [Arch.]—gen.c: low-level code generator for the specific architecture (arm-gen.c for ARM architecture)

- tccelf.c: routines for generating ELF files (object files, executable files or dynamic libraries)

- tccrun.c: support for the -run switch

TCC is a single-pass compiler, meaning that it doesn't create any form of intermediate representation of the code. In most compilers nowadays the parser usually emits either an AST (abstract syntax tree) or some intermediate language that is passed as input to the next phase. The TCC parser however directly emits object code when parsing expressions by calling the low level code generations functions, hence there is no separate code generation phase. This is the main reason why TCC compiles so extraordinarily fast.

# 3.3 Lexical Analysis

The lexer is implemented in tccpp.c. It is accessed repeatedly by the parser through the procedure next(), which places the next token into the integer variable tok. For some tokens, toke contains additional infos, e.g. values for literals.

Basic token values are defined in the header file tcc.h. Table 3.1 lists some examples of tokens returned by the lexer for certain lexemes. Note that in case of single character lexems (such as parantheses, commas or basic math operations), the token value equals this exact character value. Identifiers get unique token numbers greater or equal than TOK\_UIDENT.

# 3.4 Syntax Analysis

Syntax analysis in TCC is performed with *recursive-descent* parsing, a special form of top-down parsing where no backtracking is needed [ASU86]. Every non-terminal is associated with a recursive procedure that recognizes exactly that non-terminal in the input by implementing the corresponding production rule. Terminal symbols are directly matched and for non-terminals, the associated procedure is called.

This very simple approach is surprisingly effective and has been proposed and consistently used by compiler construction pioneer Niklaus Wirth [Wir96, BGP00], e.g. for the languages Pascal and Oberon.

The parser is started by fetching the first token and calling the procedure that is associated with the start symbol. In TCC, this is done in the function libtcc.c:tcc\_compile() via the next() and decl(VT\_CONST) calls. All the non-terminal procedures are implemented in tccgen.c.

Table 3.2 lists the EBNF-grammar non-terminals for C expressions (as stated in Appendix A13 of "The C Programming Language" (2nd edition) [KR88]) and the associated TCC parser procedures.

| EBNF non-terminal          | TCC parser function |

|----------------------------|---------------------|

| expression:                | gexpr()             |

| assignment-expression:     | expr_eq()           |

| conditional-expression:    | expr_cond()         |

| logical-OR-expression:     | expr_lor()          |

| logical-AND-expression:    | expr_land()         |

| inclusive-OR-expression:   | expr_or()           |

| exclusive-OR-expression:   | expr_xor()          |

| AND-expression:            | expr_and()          |

| equality-expression:       | expr_cmpeq()        |

| relational-expression:     | expr_cmp()          |

| shift-expression:          | expr_shift()        |

| additive-expression:       | expr_sum()          |

| multiplicative-expression: | expr_prod()         |

| cast-expression:           | unary()             |

| unary-expression:          | unary()             |

Table 3.2: C expression non-terminals and the corresponding parser functions in TCC

As an illustrative example, the implementation of expr\_or () is shown in Listing 3.1. Note that left-recursion can cause top-down parser to go into an infinite loop, hence the rules were not directly applied, but the list was rather implemented through a loop.

#### Listing 3.1 Implementation of the inclusive-OR-expression non-terminal

```

static void expr_or(void)

{

expr_xor();

while (tok == '|') {

next();

expr_xor();

gen_op('|');

}

}

```

The non-terminal procedures also contain the code generation calls ( $\Rightarrow$  gen\_op('|') in this example) – the concept where source language translation is completely driven by the parser is called *syntax-directed translation*.

# 3.5 Syntax-Directed Translation

The central data structure for the syntax-directed code generation is the *value stack*. Whenever operands of expressions are recognized by the parser, they are put on this stack, as elements of the structure type SValue (defined in tcc.h). The value stack primarily contains information on *where* the operands are located from the perspective of the generated code. It's field SValue.r contains the location value, together with some special flags in the upper bits.

Table 3.3 shows a subset of possible values and flags on elements on the value stack (shortly called *svalues*).

| Location values of r                                                                     | Meaning                                                                            |  |

|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| REG_R <b>X</b>                                                                           | value is stored in register RX                                                     |  |

| VT_CONST value is a constant, stored in SValue.c                                         |                                                                                    |  |

| VT_LOCAL value is stored on the stack (i.e. a local variable) with the offset SValue.c.i |                                                                                    |  |

| VT_CMP                                                                                   | value is stored in the processor's flags (meaning it is the consequence of a test) |  |

| VT_JMP/VT_JMPI                                                                           | VT_JMP/VT_JMPI value is the consequence of a conditional jump                      |  |

| Flags in r                                                                               | Meaning                                                                            |  |

| VT_LVAL                                                                                  | value is an <i>lvalue</i> , meaning that it is a pointer to the wanted value       |  |

| VT_SYM                                                                                   | value is a global variable — it's symbol SValue.sym must be added to the constant  |  |

Table 3.3: Some values and flags for svalues and their meanings

Whenever an *operator* is parsed, values are popped from the stack as operands, code is generated and the result is again pushed on the stack.

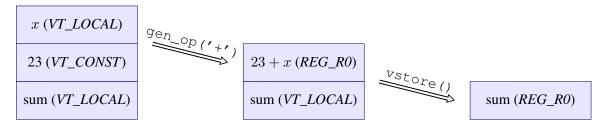

Consider the following assignment expression:  $\boxed{\text{sum} = 23 + \text{x}}$  where sum and x are both local variables. Figure 3.1 shows how the code generating functions for binary addition and for assignment change the value stack for this expression.

Figure 3.1: Value stack example for expression sum = 23 + x

An important part for the code generation is the function gv() which evaluates the top element on the value stack (vtop) into a register.

# 3.6 Simple Optimizations

Though most sophisticated types of optimizations like loop optimizations (e.g. loop unrolling, loop interchange) or data-flow optimizations (e.g. common subexpression elimination, constant propagation) are not possible in TCC as they require the presence of some form of intermediate representation, it still performs some basic optimizations:

- Multiplications/divisions by powers of two are substituted by shifts

- Optimization of comparison operators by maintaining a special cache for the processor flags

# 3.7 Backpatching

TCC has to solve a classical problem that one-pass compilers have to tackle: whenever control-flow statements (that is, conditionals or loops) are translated, the target address of forward branches is not known yet at the point of time when they are generated.

With the technique of *backpatching*, the instruction is generated with the address operand left empty (put to zero). The address of the instruction is saved (into a *symbol* variable) and is patched later when the code generator knows the target address.

<sup>&</sup>lt;sup>3</sup>see http://bellard.org/tcc/tcc-doc.html#SEC35

In some cases, there can be multiple forward branches with the same target address. For example, in a loop there can be an arbitrary number of break; statements that all target the address of the first instruction after the loop body. To avoid saving a list of symbols, TCC creates a linked list with the address operators of the jump instructions. The symbol always points to latest jump instruction, and this instruction has as operand the address of the preceding jump instruction, and so on. The first jump instruction always has zero as operand – this is the recognition that the linked list ends. The backpatching process then simply involves the traversal of the linked list, substituting every element with the actual target address. The backpatching is implemented in arm-gen.c:gsym\_addr().

We later adapt this technique to be used for the IR generation as well, see section 3.7.

# 3.8 Register Usage and Code Quality

The code generator only uses the subset of caller-saved registers (e.g. R0–R3 and R12 for the ARM architecture; EAX, ECX and EDX for x86) for evaluating expressions, the others remain completely unused. If there are more registers needed, one registers is chosen to be "spilled" onto the stack as temporary variable.

As TCC lacks local or global register allocation, the generated code never saves variable values in registers for the long term. Hence every assignment statements involves *load* instructions for all source operands in memory and a *store* instruction for the assignment. This naturally leads to fairly inefficient code, similar to that generated by qcc -00.

Figure 3.3 shows an example for code generated by TCC. The input, shown in Figure 3.2, is bit counting function which primarily consists of short assignment statements (this function is later used as benchmark, see bitcount1 in section 9.3). Note the large amount of instructions which only have the purpose of reloading the registers with values from memory and vice-versa. From the 12 loop instructions (spanning from addresses c8 to f4), 5 instruction belong to the load/store category, this is more than 40%. With global register allocation, all those expensive instructions can be eliminiated, yielding a significant run-time speedup.

```

int bit_count(long x)

{

int n = 0;

if (x) do

n++;

while (0 != (x = x&(x-1)));

return(n);

}

```

Figure 3.2: A simple bit counting function in C

```

000000a0 <bit_count>:

... [ Prologue ]

b4: mov r0, #0

b8: str r0, [fp, #-4]

bc: ldr r0, [fp, #12]

c0: teq r0, #0

c4: beq f8 <bit_count+0x58>

c8: ldr r0, [fp, #-4]

cc: mov r1, r0

d0: add r0, r0, #1

d4: str r0, [fp, #-4]

d8: ldr r0, [fp, #12]

dc: sub r0, r0, #1

ldr r1, [fp, #12]

e0:

e4: and r0, r1, r0

str r0, [fp, #12]

e8:

mov r1, #0

ec:

f0: cmp r1, r0

f4: bne c8 <bit_count+0x28>

f8: ldr r0, [fp, #-4]

... [ Epiloque ]

```

Figure 3.3: TCC-generated ARM object code for the function bit\_count()

# Implementation Considerations for the Proof-of-Concept

This chapter substantiates the rough idea of "implementing a global register allocator for TCC" by specifying several important choices about the proof-of-concept, predominantly the register allocation strategy used and the supported target architecture.

# 4.1 Choice of the Global Register Allocation Strategy

By thinking about how we should either use some form of classical graph coloring algorithm or linear scan as allocation strategy, the answer is quite obvious if we keep the main feature of TCC in mind: speed. Since TCC is so fast in compilation – which is especially pleasant for the unique feature of interpreting C code – and we don't want to sacrifice too much of that for global register allocation,  $\Rightarrow$  **Linear Scan** seems to be the perfect choice, with similar reasons as for JIT compilers. It only traverses once linearly over the live ranges and doesn't take multiple rounds like graph coloring approaches, if spill code is inserted.

Another decisive advantage of linear scan over graph coloring is *simplicity*. This is, apart from the very short and straightforward algorithm, also reflected in the data structures needed: linear scan only works with arrays and lists, and the latter can be easily represented as fixed-sized arrays if we are willing to reserve the space statically large enough and don't extend memory on demand. Hence no dynamic data structures are needed, as explained more in detail in chapter 7. Whereas for graph coloring approaches, usually the graph is represented both as matrix and adjacency list format. We also would have to support the insertion of spill code into the IR – in our solution, operands are simply marked and spill code insertion is done by code generator in the final phase. Our guess is that even a simple graph coloring implementation would take several times the effort than for linear scan.

With its two main advantages, linear scan matches perfectly the spirit of TCC: simple and fast.

The drawback of this choice is the lower quality of the generated object code. This is the tradeoff for the speed. Compared to the original TCC, the runtime efficiency will still increase noticably.

# 4.2 Choice of the Target Architecture

For the proof-of-concept it would be way too costly to implement the register allocator for all architectures supported by the original TCC (that is: x86, x86\_64, ARMv4, TMS320C67). While the target architecture is a matter of taste, it is advantageous to choose an architecture where code generation is simple.

We saw several benefits in choosing  $\Rightarrow$  **ARM** over Intel x86(\_64) as target architecture:

- RISC machine: few instructions, few addressing modes, simple instruction encoding

- fixed-size instructions (32 bits)

- uniform register file x86 would be register-constrained and had only 8 registers

The drawback of this choice is that special hardware is needed, as ARM is not common for desktop environments. With the *Raspberry Pi* (see Appendix B we found an easy and reasonable way to develop the TCC register allocation extension for the ARM architecture.

# 4.3 Language support restrictions

For the proof-of-concept, we restrict the supported input language for TCC to the following C subset:

- no float/double data type support: the support for more than one *register class* would increase the complexity of the implementation drastically; a fairly large part of the TCC code generation for the ARM architecture deals with floating points (type conversion, special calling conventions for so-called float aggregates etc.)

- no long long data type support: this data type would be stored in register pairs and hence complicates the register allocation process

- no GNU extension support

- no support for bitfields

- no support for passing/returning struct data types by value: the ARM calling conventions are quite complex for data types larger than four bytes this is reflected in arm-gen.c:gfunc\_call(), the function generating code for function calls, contains more than 300 lines; for comparison, i386-gen.c:gfunc\_call() is less than 100 lines.

In short, it supports ANSI C (C89) without floating points, bitfields and struct parameter/return value passing.

# 4.4 The Big Picture

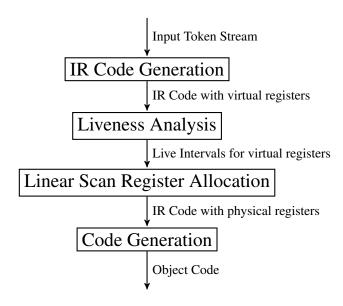

Figure 4.1 shows the steps of the implementation that are traversed for every function of the input source:

Figure 4.1: Overview of the Linear Scan extension for TCC

- 1. **IR Generation**: The first phase is driven by the top-down parser of TCC. It gets a token stream of a C source code function as input and outputs a corresponding IR listing in quadruple format. For all register allocation candidates (local and temporary variables) virtual register (*vreg*) numbers are assigned which are used as operands for the IR instructions, in order to abstract the concrete target destination. [⇒ see chapter 5]

- 2. **Liveness Analysis**: This phase determines the live intervals for all occuring virtual registers in the IR listing. It uses a simple approach that avoids data-flow analysis techniques but iteratively searches for backward jumps and extends the live interval if necessary. [⇒ see chapter 6]

- 3. **Linear Scan Register Allocation**: The actual register allocation with linear scan is performed in this phase: with the list of virtual registers and its corresponding live intervals as input, each *vreg* is mapped to either a concrete physical register or a spilling destination on the stack. [⇒ see chapter 7]

- 4. **Code Generation**: Finally, this phase generates the target code out of the IR listing and the mapping of virtual registers to concrete target locations which was the result of the previous phase. [⇒ see chapter 8]

# Step 1 – Implementing an Intermediate Representation

# 5.1 Implementing the Additional Pass

Since the basic translation unit for global register allocation is a function, we take the function parsing procedure gen\_function() in tccgen.c as starting point for our implementation. Listing 5.1 shows the essential parts of the original TCC.

Listing 5.1 Function parsing / code generation procedure in original TCC

```

static void gen_function(Sym *sym)

{

[ ... ]

gfunc_prolog(&sym->type);

rsym = 0;

block(NULL, NULL, NULL, NULL, 0, 0);

gsym(rsym);

gfunc_epilog();

[ ... ]

}

```

Our implementation is shown in Listing 5.2. In a first step, the IR code listing is cleared. In the original implementation, the parsing of the function parameters and the prolog code generation are tied together in <code>gfunc\_prolog()</code>. This doesn't work for our approach, since code generation is only done in the last step. For this reason we have an own function <code>IR\_AddFuncParams()</code> which parses the parameters without generating code. The <code>block()</code> call, representing the top-down parsing non-terminal symbol for the whole function block, remains unchanged. Within this call, the IR code is generated by invoking functions to the <code>tccir.c</code> module. The remaining calls are pretty self-explanatory.

# Listing 5.2 Function parsing / code generation procedure in our extended TCC

```

static void gen_function(Sym *sym)

1

2

3

[ ... ]

IR_Clear();

// Phase 1: IR code generation

4

IR_AddFuncParams(&sym->type);

5

block (NULL, NULL, NULL, NULL, 0, 0);

IR_LivenessAnalysis();

// Phase 2: Liveness Analysis

// Phase 3: LSRA

8

LS_RegisterAllocation();

IR_RegisterAllocationParams();

9

// Phase 4: Code generation

10

IR_GenCode();

11

[ ... ]

12

}

```

# 5.2 Abstracting Variables with Virtual Registers

As the original TCC doesn't know any intermediate representation and hence also provides no abstraction for values that could possibly be kept in registers, we have to implement the concept of *virtual registers* first. We use only two types of register allocation candidates: local variables and (compiler-generated) temporaries.

#### Local variables

As soon as a local variable is declared, a unique virtual register identifier should be assigned to it. First, the data structure for the symbol table (struct Sym in tcc.h) is extended by the vreq variable:

```

typedef struct Sym {

...

unsigned int vreg; /* associated virtual register */

}

```