Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

FAKULTÄT FÜR INFORMATIK

**Faculty of Informatics**

# Instruction Set Extensions for Time-Predictable Code Execution

## DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

#### Technische Informatik

eingereicht von

#### **Clemens Bernhard Geyer**

Matrikelnummer 0427482

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Peter Puschner

Wien, 9. Mai 2012

(Unterschrift Verfasser)

(Unterschrift Betreuung)

# Instruction Set Extensions for Time-Predictable Code Execution

## MASTER'S THESIS

submitted in partial fulfillment of the requirements for the degree of

## **Diplom-Ingenieur**

in

#### **Computer engineering**

by

#### **Clemens Bernhard Geyer**

Registration Number 0427482

to the Faculty of Informatics at the Vienna University of Technology

Advisor: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Peter Puschner

Vienna, 9. Mai 2012

(Signature of Author)

(Signature of Advisor)

## Erklärung zur Verfassung der Arbeit

Clemens Bernhard Geyer Ohligsgasse 6, 1110 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

## Abstract

Nowadays, highly dependable real-time systems are part of many applications in the aerospace and automotive industries. The requirements of real-time applications do not only include the correctness of results, but also the instant of time, when a result is available. In case of a so-called *hard real-time system*, the whole system may crash if a task does not finish within a given period of time. Thus, knowing worst-case execution times of programs in advance is of utmost importance.

*Worst-case execution time analysis* (WCET analysis) calculates the longest possible duration an application may take to finish. To do so, all external and internal influences have to be considered, for example, processor and memory load, the implemented caching strategy, etc. In order to simplify the analysis of assembler code, Puschner and Burns presented the so-called *single-path transformation* of algorithms in [PB02, Pus03]. It is based on the idea to eliminate conditional branches such that just one possible execution path remains which is trivial to analyze. Nevertheless, this is only possible if the processor provides certain kinds of instructions.

Within the current thesis, the instruction set of the SPARC V8 processor has been extended so that the analysis of assembler code is simplified. Additional goals included that it should be easy to implement these instructions in hardware and adapt existing code generators to support the instruction set extension. Moreover, the resulting worst-case performance should be improved. In order to evaluate the feasibility of the additional instructions, new code generating passes have been added to an existing compiler and an instruction set simulator has been implemented. Based on the results of numerous simulated benchmark algorithms, the most promising instruction set extensions have been identified and suggested to be part of future processors used in real-time systems.

## Kurzfassung

Hochzuverlässige Echtzeitsysteme sind heutzutage Teil vieler Anwendungen im Bereich der Luft- und Raumfahrt, sowie der Automobilindustrie. Die Anforderungen betreffen dabei nicht nur die Korrektheit der gelieferten Ergebnisse, sondern auch den konkreten Zeitpunkt, wann diese der Anwendung zur Verfügung stehen. Im Falle eines so genannten *harten Echtzeitsystems* kann es zur Katastrophe, zum Beispiel einem Flugzeugabsturz, kommen, wenn eine Anwendung zu lange für ihre Berechnungen benötigt. Deshalb ist es wichtig, schon im Vorhinein die maximalen Ausführungszeiten eines Programms zu kennen.

Die *Worst-case execution time Analysis* (WCET analysis) befasst sich mit der Berechnung der längst möglichen Ausführungszeiten eines Programms. Dabei müssen theoretisch alle Aspekte eines Prozessors, wie aktueller Speicherzustand, das zu Grunde liegende Caching Modell etc., berücksichtigt werden. Um die Analyse des Assembler-Codes zu vereinfachen, wurde von Puschner und Burns in [PB02, Pus03] eine Transformation vorhandener Algorithmen vorgeschlagen, sodass nur mehr ein möglicher Ausführungspfad existiert. Allerdings unterstützen nicht alle Prozessoren die dazu nötigen Instruktionen.

Im Rahmen dieser Diplomarbeit wurde das Instruction Set des SPARC V8 um Befehle erweitert, die die Analysierbarkeit des resultierenden Assembler-Codes vereinfachen sollen. Weitere Ziele waren eine einfache Umsetzung der zusätzlichen Befehle in Hardware, eine möglichst leichte Integration in vorhandene Codegeneratoren, sowie eine Verbesserung der Worst-case Performance. Um ein möglichst unverfälschtes Ergebnis zu erhalten, wurde ein vorhandener Compiler so angepasst, dass die vorgeschlagenen Erweiterungen bei der Übersetzung berücksichtigt werden. Außerdem wurde ein Simulator entwickelt, sodass die Performance der zusätzlichen Befehle anhand mehrerer Benchmark-Algorithmen erhoben werden konnte. Auf Grund der Messergebnisse war es möglich, die vielversprechendsten Kombinationen der Befehlserweiterungen zu identifizieren und sie als Grundlage für zukünftige Prozessoren im Echtzeitbereich vorzuschlagen.

## Contents

| Li                                      | st of A | Abbreviations                                           | xiii |

|-----------------------------------------|---------|---------------------------------------------------------|------|

| 1                                       | Intro   | oduction                                                | 1    |

|                                         | 1.1     | Problem Statement                                       | 1    |

|                                         | 1.2     | Overview of WCET Analysis                               | 2    |

|                                         | 1.3     | Outline                                                 | 3    |

| 2                                       | Instr   | ruction Set Analysis                                    | 5    |

|                                         | 2.1     | Analog Devices Blackfin Microprocessor                  | 5    |

|                                         | 2.2     | ARM Processors                                          | 10   |

|                                         | 2.3     | Atmel AVR Microcontrollers                              | 14   |

|                                         | 2.4     | Infineon TriCore Processors                             | 16   |

|                                         | 2.5     | Tensilica Xtensa                                        | 19   |

|                                         | 2.6     | Conclusion                                              | 21   |

| <b>3</b> Time Predictable Architectures |         |                                                         | 23   |

|                                         | 3.1     | The Necessity of Time Predictable Processors            | 23   |

|                                         | 3.2     | The Spring Architecture                                 | 25   |

|                                         | 3.3     | MACS                                                    | 26   |

|                                         | 3.4     | SPEAR                                                   | 28   |

|                                         | 3.5     | VISA                                                    | 29   |

|                                         | 3.6     | JOP                                                     | 30   |

|                                         | 3.7     | MCGREP                                                  | 32   |

|                                         | 3.8     | PRET                                                    | 34   |

|                                         | 3.9     | Time-Predictable VLIW Processors                        | 35   |

|                                         | 3.10    | Conclusion                                              | 37   |

| 4                                       | Exte    | nsions and Modifications of an Existing Instruction Set | 39   |

|                                         | 4.1     | Problem Statement                                       | 39   |

|                                         | 4.2     | The SPARC V8 Architecture                               | 41   |

|                                         | 4.3     | Instruction Set Extensions for the SPARC V8 Processor   | 43   |

| 5                                       | Impa    | acts on Code Generators                                 | 57   |

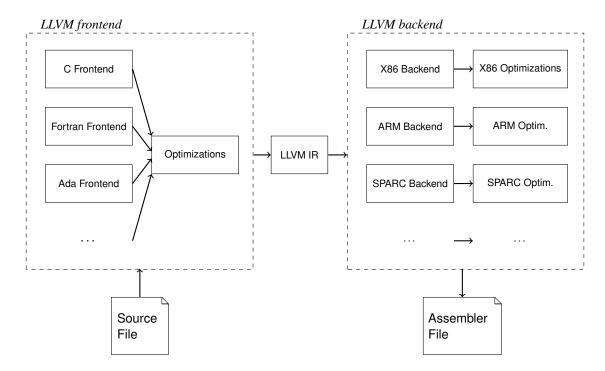

|                                         | 5.1     | The LLVM Compiler Framework                             | 57   |

|    | 5.2                   | Implementing Code Generation for Conditional Move and Conditional Select .     | 60         |  |  |  |

|----|-----------------------|--------------------------------------------------------------------------------|------------|--|--|--|

|    | 5.3                   | Implementing Code Generation for Predicated Instructions and Predicated Blocks | 61         |  |  |  |

|    | 5.4                   | Implementing Code Generation for Hardware Loops                                | 67         |  |  |  |

| 6  | Eval                  | Evaluation of Instruction Set Extensions 6                                     |            |  |  |  |

|    | 6.1                   | Manual Evaluation of Small Examples                                            | 70         |  |  |  |

|    | 6.2                   | Evaluation of Selected Algorithms                                              | 79         |  |  |  |

|    | 6.3                   | Towards a Time Predictable Instruction Set                                     | 92         |  |  |  |

| 7  | Conc                  | elusion 1                                                                      | .03        |  |  |  |

|    | 7.1                   | Final Review on the Presented Instruction Set Extensions                       | 03         |  |  |  |

|    | 7.2                   | Suggestions for Further Research                                               | 04         |  |  |  |

|    | 7.3                   | Summary                                                                        | 04         |  |  |  |

| Ap | opendi                | ices 1                                                                         | .07        |  |  |  |

| A  | Perfo                 | ormance Evaluation of Selected Algorithms                                      | .09        |  |  |  |

|    | A.1                   | 8                                                                              | 09         |  |  |  |

|    | A.2                   |                                                                                | 12         |  |  |  |

|    | A.3                   |                                                                                | 14         |  |  |  |

|    |                       | -                                                                              | 16         |  |  |  |

| в  | Benchmark Results 117 |                                                                                |            |  |  |  |

|    | B.1                   |                                                                                | 18         |  |  |  |

|    | B.2                   |                                                                                | 21         |  |  |  |

|    | B.3                   |                                                                                | 23         |  |  |  |

|    | B.4                   | •                                                                              | 25         |  |  |  |

|    | B.5                   |                                                                                | 27         |  |  |  |

|    | B.6                   |                                                                                | 29         |  |  |  |

|    | B.7                   |                                                                                | 31         |  |  |  |

|    | B.8                   |                                                                                | 33         |  |  |  |

|    | B.9                   | 5 6                                                                            | 35         |  |  |  |

|    |                       | 5 6 6                                                                          | 37         |  |  |  |

|    |                       |                                                                                | 39         |  |  |  |

|    |                       |                                                                                | 41         |  |  |  |

|    |                       | 1                                                                              | 43         |  |  |  |

|    |                       | · · · · · · · · · · · · · · · · · · ·                                          | 45         |  |  |  |

|    |                       |                                                                                | 47         |  |  |  |

|    |                       |                                                                                | 49         |  |  |  |

|    |                       | 6                                                                              | 51         |  |  |  |

|    |                       |                                                                                | 53         |  |  |  |

|    |                       |                                                                                | .33<br>.55 |  |  |  |

|    |                       | e                                                                              | .55<br>.57 |  |  |  |

|    |                       | I I I I I I I I I I I I I I I I I I I                                          |            |  |  |  |

|    | В.21                  | Software Division – Shift Implementation                                       | 59         |  |  |  |

| B.24 Threshold – Single-Path | 165 |

|------------------------------|-----|

| Bibliography                 | 167 |

| Index                        | 173 |

# List of Figures

| 4.1  | Opcode formats of SPARC V8                                         |

|------|--------------------------------------------------------------------|

| 4.2  | Conditional move instruction                                       |

| 4.3  | Opcode proposal for the conditional move instruction               |

| 4.4  | Possible block layout of the conditional move instruction          |

| 4.5  | Conditional select instruction                                     |

| 4.6  | Opcode proposal for the conditional select instruction             |

| 4.7  | Predicated blocks based on integer condition codes                 |

| 4.8  | Possible block layout of predicated blocks                         |

| 4.9  | Opcode proposal for predicated blocks based on condition codes     |

| 4.10 | Predicated blocks based on predicate registers                     |

| 4.11 | Opcode proposal for predicated blocks based on predicate registers |

| 4.12 | Instruction proposal for hardware loops                            |

| 4.13 | Opcode proposal for hardware loop instructions                     |

| 4.14 | Possible block layout of a hardware loop module                    |

| 5.1  | Overview of the LLVM workflow                                      |

| 5.2  | If-then-else-translation                                           |

| 5.3  | Branch elimination                                                 |

| 5.4  | Nested if-then-else elimination                                    |

| 6.1  | Performance evaluation of bubble sort                              |

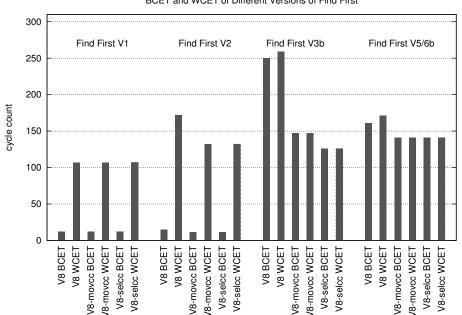

| 6.2  | Performance evaluation of find first                               |

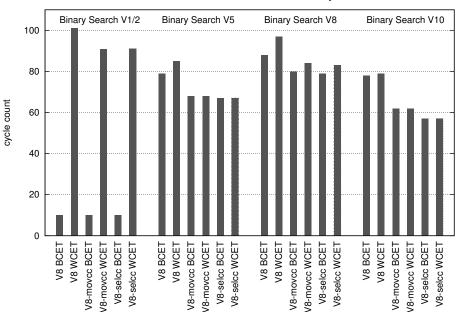

| 6.3  | Performance evaluation of binary search                            |

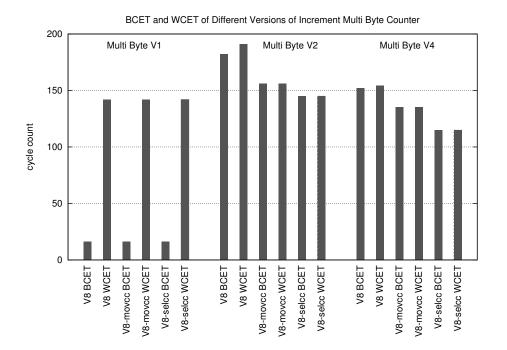

| 6.4  | Performance evaluation of multi-byte counter                       |

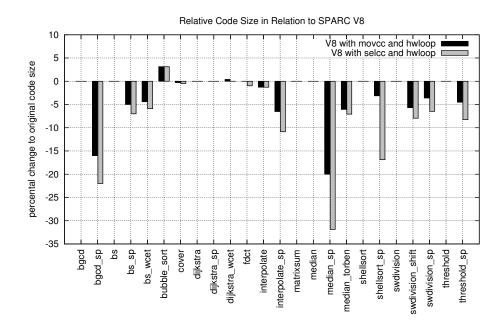

| 6.5  | Code size in comparison with SPARC V8                              |

| 6.6  | Deviation on SPARC V8 and v8-selcc 100                             |

| 6.7  | Number of branches in comparison with SPARC V8                     |

| 6.8  | Measured cycles in comparison with SPARC V8 102                    |

## **List of Tables**

| 2.1 | Feature overview of different processor architectures       | 22  |

|-----|-------------------------------------------------------------|-----|

| A.1 | Code size evaluation of bubble sort.                        | 110 |

| A.2 | Performance evaluation of bubble sort                       | 111 |

| A.3 | Code size evaluation of find first.                         | 112 |

| A.4 | Performance evaluation of find first.                       | 113 |

| A.5 | Code size evaluation of binary search.                      | 114 |

| A.6 | Performance evaluation of binary search.                    | 115 |

| A.7 | Code size evaluation of incrementing a multi-byte counter.  | 116 |

| A.8 | Performance evaluation of incrementing a multi-byte counter | 116 |

## **List of Algorithms**

| 5.1 | Swapping algorithm for conditional select instructions. | 61 |

|-----|---------------------------------------------------------|----|

| 5.2 | Algorithm for if-then-else elimination.                 | 63 |

| 5.3 | Algorithm for nested if-then-else elimination.          | 65 |

| 5.4 | Optimization algorithm for predicated blocks.           | 66 |

| 5.5 | Generating assembler code for hardware loops.           | 68 |

## **List of Code Examples**

| 2.2  | Two possible realizations of hardware-supported loops on the Blackfin processor. | 9  |

|------|----------------------------------------------------------------------------------|----|

| 2.3  | Storing and loading of multiple registers on ARM processors                      | 11 |

| 2.4  | Predicated instructions on ARM processors                                        | 12 |

| 2.5  | Conditional execution of Thumb instructions on ARM processors                    | 13 |

| 4.1  | Translation of if-then-else structure using conditional moves                    | 45 |

| 4.2  | Translation of if-then-else structure using conditional selects                  | 47 |

| 4.3  | Translation of if-then-else structure using predicated instructions              | 49 |

| 4.4  | Translation of if-then-else structure using predicated blocks.                   | 53 |

| 4.5  | Translation of a for-loop using hardware loop instructions.                      | 54 |

| 5.1  | LLVM table description definition of the conditional move instruction            | 60 |

| 5.2  | Transformation of nested if-then-else structures to predicated blocks            | 65 |

| 6.1  | Code generation for a simple branch test.                                        | 71 |

| 6.2  | Code generation for a complex branch test.                                       | 73 |

| 6.3  | Code generation for an adapted version of the complex branch test                | 74 |

| 6.4  | Code generation for a simple loop test                                           | 76 |

| 6.5  | Code generation for a simple loop test containing branches                       | 78 |

| 6.6  | Traditional implementation of the bubble sort algorithm.                         | 80 |

| 6.7  | Single-path implementation of the bubble sort algorithm                          | 81 |

| 6.8  | Alternative single-path implementation of the bubble sort algorithm              | 81 |

| 6.9  | Traditional implementation of the find first algorithm.                          | 83 |

| 6.10 | Single-path implementation of the find first algorithm                           | 84 |

| 6.11 | Simple backward loop implementation of the find first algorithm                  | 84 |

| 6.12 | Traditional implementation of the binary search algorithm                        | 86 |

| 6.13 | Single-path implementation of the binary search algorithm                        | 87 |

| 6.14 | Improved single-path implementation of the binary search algorithm               | 88 |

| 6.15 | Traditional implementation of incrementing a multi-byte counter                  | 89 |

| 6.16 | Single-path implementation of incrementing a multi-byte counter                  | 90 |

| 6.17 | Improved single-path implementation of incrementing a multi-byte counter         | 90 |

## **List of Abbreviations**

- ADC Analog to Digital Converter

- ALU Arithmetic Logic Unit

- ASIC Application Specific Integrated Circuits

- BCET Best Case Execution Time

- CFG Control Flow Graph

- CPI Cycles per Instruction

- CPU Central Processing Unit

- DES Data Encryption Standard

- DMA Direct Memory Access

- DSP Digital Signal Processor

- FIFO First In First Out

- FIR Finite Impulse Response

- FPGA Field Programmable Gate Array

- I<sup>2</sup>C Inter-Integrated Circuit

- ISA Instruction Set Architecture

- JPEG Joint Photographic Experts Group

- JVM Java Virtual Machine

- LRU Least Recently Used

- LSB Least Significant Bit/Byte

- MAC Multiply And Accumulate

- MBB Machine Basic Block

- MCU Microcontroller Unit

- MSB Most Significant Bit/Byte

- NOP No Operation

- PWM Pulse Width Modulation

- RAM Random Access Memory

- RISC Reduced Instruction Set Computer

- SIMD Single Instruction Multiple Data

- SPI Serial Peripheral Interface

- SRAM Static Random Access Memory

- SSA Single Static Assignment

- UART Universal Asynchronous Receiver Transmitter

- VGA Video Graphics Array

- VHDL Very High Speed Intagrated Circuits Hardware Description Language

- VLIW Very Large Instruction Word

- WCET Worst-Case Execution Time

## CHAPTER

## Introduction

#### **1.1 Problem Statement**

Real-time systems have become more and more important over the past decades: In the 1980's, the automotive and aerospace industries started to use digital controllers for several non-critical tasks. Nowadays, nearly all regulating operations of an airplane or a car are executed by embedded systems. For normal computer programs, the main requirement is that they deliver correct results. Time-critical controlling tasks have the additional requirement to deliver correct results until a specified instant of time, which is called a *deadline*. If the whole system may collapse in case the deadline cannot be met, it is called a *hard real-time system*. Examples are controlling tasks in an airplane or a nuclear power plant. If the system is only affected for a short period of time in case the deadline is missed, the system is denoted as a *soft real-time system*, confer [Kop97, p. 2f]. These include, for example, digital telecommunication systems.

One important aspect when dealing with real-time systems is the predictability of the implemented algorithms. If a task may take an arbitrary long time to finish, it could miss a deadline, causing the whole system to crash. Hence, it is of utmost importance to identify *worst-case scenarios* such that the timing constraints are known in advance. Unfortunately, modern processors are not designed to behave predictably, but to speed-up the average case performance. They make use of caches, static and dynamic branch prediction, pipelining, etc. All of these features have to be taken into account for a *Worst-case execution time* (WCET) Analysis. However, it is not always possible to reliably identify the worst-case scenario when all external influences are considered. This is the reason why WCET analysis often uses simplified models of processors, delivering pessimistic results.

For the current thesis, we restrict the focus of WCET analysis only to the influence of the instruction set provided by the processor: Conditional branches as well as instructions with variable execution times increase the number of scenarios to be analyzed. Moreover, the assembler output of the compiler highly depends on the available instructions: If, for example, an algorithm involves a division which is not provided by the instruction set, it has to be emulated by software. Of course, this solution has a much worse performance in comparison with an in-

struction provided by hardware. Thus, the resulting code quality of the assembler output may be improved by supporting additional instructions.

Although there are several approaches defining time predictable processor architectures, none of them analyzes the impact of the underlying instruction set architecture (ISA) on the resulting assembler code. This thesis tries to identify instructions which should be part of such architectures in order to get predictable and easy to analyze assembler code. These instructions should (1) easily be implemented in hardware, (2) easily be added to an existing instruction set, (3) be used by code generating passes and (4) improve the predictability and performance of the resulting assembler code.

In a first step, instruction sets and uncommon features of existing processors have been analyzed. Moreover, an evaluation of various approaches of time predictable processors has been done. In a second step, the SPARC V8 instruction set has been extended by several instructions which meet the previously described requirements. These additional instructions have been added to the code generating pass of the LLVM compiler framework. Hence, the impacts of the instruction set extensions on the assembler output could be verified. To analyze the effect of the newly introduced instructions on the worst-case performance, an instruction set simulator of the SPARC V8 has been implemented. Finally, a big variety of algorithms has been translated to assembler code. By enabling different combinations of the instruction set extensions in the code generating phase, the most feasible solutions in terms of code size and worst-case performance could be identified. The additional instructions which had the most positive influence on performance and WCET analysis have been proposed to be part of instruction sets of future time predictable processors.

#### **1.2 Overview of WCET Analysis**

In [PB00], Puschner and Burns define the targets of WCET analysis:

- WCET Analysis calculates *safe upper* bounds of task execution times. This means that the actual worst-case scenario may indeed have a lower execution time.

- WCET Analysis should deliver *tight* bounds of task execution times. Hence, the calculated results should be safe, but not too pessimistic as they otherwise would be useless.

Calculating the worst-case execution time of a given program is not possible for the general case, because it is an instance of the famous *Halting Problem* as indicated by Kirner and Puschner in [KP05]. This is the reason why most WCET analysis techniques try to simplify the problem: By providing additional information such as *flow facts*,<sup>1</sup> an analysis tool is able to identify the worst-case scenario more easily. Another possibility is to ignore the underlying hardware in a first step and to extract flow facts from the control flow graph (CFG) of the high-level code. This information is used later to calculate the exact worst-case cycle count on assembler code level.

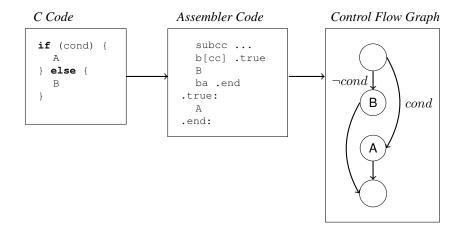

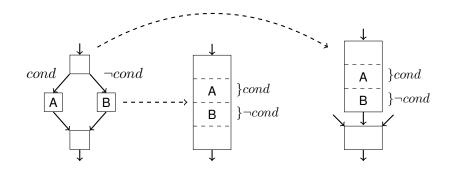

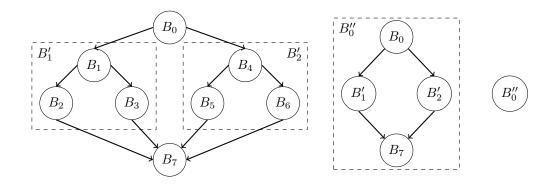

As WCET analysis including cache and pipeline models becomes more and more complex, Puschner and Burns introduced the so-called *single-path transformation* in [PB02]. It is based

<sup>&</sup>lt;sup>1</sup>*Flow facts* are presented in [KP05] and denote descriptions which paths within the control flow graph of a program are to be taken more likely.

on the idea that nearly all algorithms used in real-time systems can be implemented with fixed loop bounds and no complex loop exiting conditions. The minimal precondition, an instruction set has to provide in order to do a single-path transformation, is a conditional move instruction with constant execution time. In case conditional or predicated instructions are supported by the instruction set of the processor (see, e.g., Section 2.2.4), it is simpler to apply the single-path transformation. The main idea is to execute both, the if- and else-branch, and to decide afterwards which result will be used. It is also possible to transform nested if-then-else structures and loops with fixed bounds as presented in [PB02, Pus03]. Thus, the analysis of the corresponding control flow graph is trivial because only one possible path exists. Nevertheless, the resulting code usually shows worse performance, not only in the average, but also in the worst case.

#### 1.3 Outline

Chapter 2 gives an overview of existing state-of-the-art processors used in embedded systems. The main focus lies on the provided instruction set and tries to evaluate whether it fully supports the single-path transformation. Nearly each of the presented processors features special instructions. It will be evaluated whether these instructions are useful in order to simplify WCET analysis. Chapter 3 presents the most interesting scientific approaches which try to define a time predictable architecture. Some of them have really been implemented in hardware, whereas others only enumerate basic concepts.

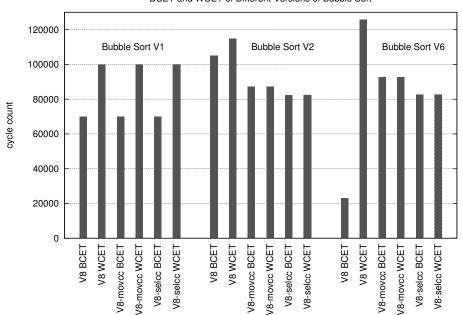

The main part of the thesis can be found in Chapters 4 to 6. First, the SPARC V8 processor and suggestions for instruction set extensions are presented. The chapter also includes opcode considerations and possibilities of how the extensions might be implemented in hardware. Chapter 5 gives an overview of the LLVM compiler framework and how it has been extended to support code generation for the additional instructions. The performance evaluation of the instruction set extensions is done in Chapter 6. It is based on a number of benchmark algorithms, which have been translated into multiple assembler codes: One implements the original SPARC V8 instruction set, others provide different combinations of the proposed instruction set extensions. Based on the resulting code sizes and worst-case performance, two combinations of additional instructions have been decided to be most feasible for processors being predictable and easy to analyze.

# CHAPTER 2

## **Instruction Set Analysis**

This chapter gives an overview of common state-of-the-art embedded processors/microcontrollers<sup>1</sup>. The focus lies on the instruction sets they provide, but additional information about important hardware features is also presented. The evaluation of the processors is mainly based on the impacts on WCET analysis, i.e., whether the ISA and properties of the individual processors provide useful functionality in the domain of real-time systems.

All presented microprocessors are used in different types of embedded applications, most of them related to real time systems such as controllers in the automotive industry or mobile devices in the field of telecommunications. Of course, the selection may not cover all available processors, e.g., the commonly used PowerPC is not part of the current analysis because it does not have any features which are specific to real-time systems or which are not covered by the other presented processors.

The aim of the current chapter is to present instructions or hardware features which are unique for a single processor and may be useful extensions for a time-predictable architecture. Consequently, only features which have not been described so far are explained in full detail. The order of presentation is alphabetical, based on the name of the manufacturer, and is no indication of the quality or importance of the individual processors.

#### 2.1 Analog Devices Blackfin Microprocessor

#### **2.1.1** General Features<sup>2</sup>

According to [Ana11], Blackfin processors are widely in use for embedded audio and video applications, voice and image processing, in the field of real time security, and in other applications. As the Blackfin is mainly used in signal processing, it combines features of a typical DSP with the possibilities and flexibility of microcontrollers. This may be the reason why Analog

<sup>&</sup>lt;sup>1</sup>Although these terms usually carry different meanings, there is no generally valid definition. Thus, *processor* and *microcontroller* are often used equivalently, depending on the specific definition of the manufacturer.

<sup>&</sup>lt;sup>2</sup>Confer[GK07, p. 163-167], [Ana08, p. 1.1-1.6] and [Ana10, p. 1.1-1.10].

Devices declares the Blackfin an *embedded processor*. It is based on a RISC architecture with an instruction size of 32 bits. However, frequently used instructions are encoded with 16 bits.

The Blackfin processor allows to address up to 4 GByte of internal and external memory, which are used for caches, internal RAMs and I/O registers. 4 KByte of the internal L1 memory may be used as a scratchpad such that time-critical applications get guaranteed access times to requested data. The processor has eight 32-bit registers R0 to R7, which may also be used as sixteen 16-bit registers (e.g., by separately accessing the lower and upper 16 bits of the corresponding registers R0. L and R0. H). There are six 32 bit pointer registers which are used for address calculations. Moreover, the Blackfin has two independent 40-bit accumulators, which support multiple computational operations<sup>3</sup> for a single instruction (see Section 2.1.3 for details). Of course, there are several more registers, but they are mostly for internal usage or special instructions.

As already mentioned, the Blackfin processor is not mainly designed for applications in hard real-time systems. Nevertheless, it offers some instructions supporting the WCET analysis of algorithms commonly in use in such kind of systems. In the following sections, these instructions are presented, together with instructions which are rather uncommon and specific to the Blackfin processor.

#### 2.1.2 Instructions for Calculating Minimum and Maximum Value<sup>4</sup>

The Blackfin processor offers the programmer hardware instructions to determine the minimum and maximum of two given integers. The given input numbers are interpreted as signed 16- or 32-bit values, depending on the instruction type. A number is said to be negative if the MSB is set. It is also possible to evaluate both operations independently on two 16 bit registers (see Section 2.1.3).

The application of these instructions is mainly to provide a hardware implementation of the MIN() and MAX() functions, which are used in nearly all high-level programming languages<sup>5</sup>. It may help to find the smallest/greatest element of an unsorted array in shorter time because the integer comparison is done in hardware and saving the smaller/greater value does not require additional conditional branches. Consequently, the control flow graph of the program gets simpler and WCET analysis is much easier.

#### 2.1.3 Single Instruction Multiple Data (SIMD)<sup>6</sup>

The Blackfin processor offers several possibilities to perform multiple operations with just one instruction. In principle, there are two possibilities:

<sup>&</sup>lt;sup>3</sup>In the current thesis, the term *instruction* refers to an assembly or high level language instruction whereas *operation* is equivalent to a basic mathematical function implemented in hardware. Thus, an instruction may unite multiple operations; the opposite is usually not true. In some cases the terms may be used interchangeably, e.g., in context of arithmetic instructions or operations.

<sup>&</sup>lt;sup>4</sup>Confer [Ana08, p. 15.31-15.35].

<sup>&</sup>lt;sup>5</sup>Usually, in the C programming language a macro like #define MAX(a,b) ((a)>(b))?(a):(b); is defined for this purpose.

<sup>&</sup>lt;sup>6</sup>Confer [GK07, p. 167-173] and [Ana08, p. 19.1-20.10]

- (1) An instruction performs two or more operations on one 32-bit register, but the lower and upper 16 bits are treated separately. Analog Devices calls this type of instruction a *vector operation*.

- (2) There are certain instructions which can be performed in parallel, beginning with one 32bit instruction followed by two 16-bit instructions. These three are treated as one 64-bit instruction. Analog Devices calls this type a *parallel instruction*.

Additionally, the Blackfin processor offers so-called MAC instructions (Multiply And Accumulate). They allow to add or subtract the result of a multiplication to or from the currently saved value in one of the accumulators. Although this single instruction performs multiple operations, it is a quite common feature of processors implementing an accumulator architecture. Moreover, it is a typical feature of DSPs, which allows the implementation of efficient matrix-matrix multiplications, which are needed for Fourier transformations. See [Ana08, p. 15.56-15.70] for a detailed description.

Vector operations usually work on 16-bit registers. However, two 32-bit registers may also serve as vector input for arithmetic instructions. Code example 2.1 shows different possibilities for this kind of operations: The first line subtracts the upper 16 bits of r3 from the upper 16 bits of r2, while at the same time the lower 16 bits of each register are added. The next example shows how two 32-bit registers are simultaneously added and subtracted while the results of both operations are saved to different destination registers. The last code line performs four arithmetic instructions with eight 16-bit input registers.<sup>7</sup> The four results of these operations are saved in the upper and lower 16 bits of registers r0 and r1, respectively. Note that each *real* instruction is closed with a semicolon, whereas two instructions belonging together are separated by a comma.

Code Example 2.1 Examples for arithmetic vector operations of the Blackfin processor.

r0 = r2 - | + r3; r3 = r6 + r7, r4 = r6 - r7; r0 = r2 + | - r3, r1 = r4 - | - r5;

There also exist vector operations for the simultaneous calculation of the minimum and maximum of two 16-bit values. In contrast to arithmetic instructions, only one of the two operations may be performed on both registers. Moreover, vector multiplications as well as vector MAC instructions are supported. They will not be discussed here as the principle is the same as for the instructions just presented.

Parallel instructions have a special syntax as it is only possible to execute certain operations concurrently. The first instruction has to be a 32-bit instruction and may also be a NOP. Supported are arithmetic, move, bit operation and vector operation instructions. It is followed by two 16-bit instructions which are subject to certain restrictions. For example, it is not possible to access registers used by the first 32 bit instruction. Nevertheless, it is possible to perform a MAC

<sup>&</sup>lt;sup>7</sup>The involved source operands are the upper 16 bits of r2 and r3, the lower 16 bits of r2 and r3 as well as the lower and upper 16 bits of r4 and r5.

operation and execute two read or write instructions in the same instant of time. The so-called *Instruction Alignment Unit* of the Blackfin processor always accesses eight bytes from the instruction memory to ensure that all instructions are aligned properly. This is necessary because there are 16-, 32- and 64-bit instructions. The last format is used for parallel operations. Consequently, the instruction fetch operation always takes the same amount of time, regardless of the current bit width. In case of a parallel instruction, the execution duration of each of the three instructions is equal. See [Ana08, p. 4.7-4.9] for further details about the pipelining concept of the Blackfin processor.

Beside the functions presented in the current section, there are so-called *video pixel operations*. They are also typical for DSPs and allow for the simultaneous calculation of the pairwise average of eight bytes. This feature may be useful when calculating a transition image of two given pictures. See [Ana08, p. 18.1-18.40] for more details about this kind of instructions.

#### 2.1.4 Instructions for Cache Control<sup>8</sup>

As already mentioned in Section 2.1.2, the Blackfin processor allows the programmer to define the usage of its L1 memory. This is done by writing configuration bits into the DMEM\_CONTROL register, indicating whether some parts of the memory should be used as an instruction cache, a data cache, as usual SRAM or as a scratchpad. Although the presented instructions are not very powerful on their own, it is a quite uncommon feature to let the user perform cache-related operations, which are usually only implemented by a hardware controller.

When L1 is defined as a data cache, the programmer has the possibility to perform some actions to manipulate the content of the cache. This may help to provide an easier analysis of execution time or to guarantee worst-case timings. The prefetch instruction allows the user to load a memory region into the internal data cache. The address of that region is provided by a pointer register. The flush and invflush operations provide the possibility to explicitly perform a read from or write to higher memory levels if the cache line has been marked as *dirty*.

#### 2.1.5 Hardware Loops<sup>9</sup>

The Blackfin processor allows the programmer to make use of a loop implemented in hardware. This is done by saving all necessary information for the loop bounds in special registers: LCx holds the value of the *loop counter*, LTx holds the address of the first instruction within the loop, and LBx holds the address of the first instruction after the loop. As the processor also supports nested loops for one inner and one outer loop, the registers with suffix "1" (e.g., LC1) have higher priority and should be used for the inner loop, whereas registers with suffix "0" can be used either for a single or for the outer loop. The instructions within the hardware loop may be of any kind, but must not be conditional branch, jump or call instructions. Otherwise, the execution behavior of the loop is undefined.

The assembler language definition of the Blackfin processor gives the user three possibilities for implementing the loop: The first five lines of Code Example 2.2 make use of the loop - begin\_loop - end\_loop construction, which is the most readable form. Note that the three

<sup>&</sup>lt;sup>8</sup>Confer [Ana08, p. 17.1-17.10] and [Ana10, p. 2.1-2.6]

<sup>&</sup>lt;sup>9</sup>Confer [GK07, p. 178-182] and [Ana08, p. 7.13-7.19]

instructions in line four are executed in parallel, as indicated by the two vertical bars (|+|) which conjunct parallel instructions presented in Section 2.1.3. The second possibility is also shown in Code Example 2.2 and is semantically equivalent to the upper assembler code: In both cases, the loop counter LC0 is initialized to "32", LT0 is set to the address of the first instruction within the loop, and LB0 to the address of the first instruction after the loop or lsetup instruction, which is the reason why the user explicitly has to state the starting address of the loop. LTx and LBx are set automatically by the two instructions. The end address label is encoded with 11 bits by the instruction, meaning that the end address may be 2046 bytes away from the current program counter at maximum. Consequently, the address range of a loop is quite limited. Nevertheless, it is also possible to manually initialize all needed loop registers such that the address range includes the whole memory of 4 GBytes.

**Code Example 2.2** Two possible realizations of hardware-supported loops implemented with the instruction set of the Blackfin processor. The code is based on Example 5.15 in [GK07, p. 181].

```

p5 = 0x20;

loop MYLOOP lc0 = p5;

loop_begin MYLOOP

r2 = r0 + r1 || r3 = [p1++] || r4 = [i1++];

loop_end MYLOOP

r2 = r3 + r4;

p5 = 0x20;

lsetup (loop_start, loop_end) lc0 = p5;

loop_start:

r2 = r0 + r1 || r3 = [p1++] || r4 = [i1++];

loop_end:

r2 = r3 + r4;

```

#### 2.1.6 Conclusion

Although the Blackfin processor is not primarily designed for hard real-time tasks, its instruction set offers quite good possibilities to design WCET-aware applications. The analysis of the CFG can be dramatically simplified by using features like hardware loops, which guarantee predictable timings also in case of nested loops. Moreover, it is possible to influence the cache semantics or even to turn off the cache and use the available memory as a normal RAM. As a cache is always a source of unpredictability, these features also help to improve the correctness of WCET analysis.

Nevertheless, the Blackfin does not provide any conditional instructions like predicated instructions or conditional moves. Thus, it is not possible to apply the single-path approach as described in Section 1.2 to programs optimized for the Blackfin processor. Moreover, due to the 10-stage pipelining concept paired with numerous possibilities of combining multiple instructions (vector operations and parallel instructions) with different bit widths, the timing analysis of scenarios with multiple possibilities for branch prediction may be very complex or even impossible. Consequently, the Blackfin processor may be an applicable choice for soft real-time systems, but it is not ideal for hard real-time systems with complex timing constraints.

#### 2.2 ARM Processors

#### **2.2.1** General Features<sup>10</sup>

The ARM company was originally formed as a joint venture between Acorn Computers, Apple Computers and VLSI Technology in 1990, but is an autonomous business today. It specializes in designing processors and embedded processors for all types of applications, including smartphones and mobile devices, automotive braking systems and smart sensors, as well as many others.<sup>11</sup> The main goals of the first ARM processors, which were designed as RISC processors, included high performance, high code density, low power consumption, and small die area.

The ARM instruction set uses a constant width of 32 bits, but it is also possible to change to the so-called *Thumb instruction set* (see Section 2.2.5), which only uses 16 bits. This provides an even higher code density, resulting in less power consumption because fewer memory fetching operations for instructions are necessary. In the latest version of the ARM instruction set, it is also possible to switch between the two instruction sets quite easily. Over the years, the ARM instruction set has been extended to include DSP operations and management instructions for handling multi-threaded operations.

ARM processors provide different modes (user, supervisor, system, etc.) with individual register sets. In each mode, there are 17 32-bit registers available (including the program counter and the processor state register), but up to eight registers may be dedicated to a certain mode. This kind of registers are called *banked registers*, whereas the registers which are visible to all processor modes are called *unbanked*.

Current ARM processors make use of the ARMv7 instruction set, although ARMv6 and ARMv5 are still in use. Moreover, the newer versions try to provide backward compatibility so that most ARMv5 instructions are also supported by ARMv6 and ARMv7. In the following subsections, the special features of the ARM instruction set are presented. They include predicated instructions, SIMD instructions, which are partially identical to the Blackfin instruction set, and special operations on floating point numbers. Note that the particular versions of the instruction sets will not be considered because the main focus lies on architectural principles and supported features.

#### 2.2.2 Single Instruction Multiple Data (SIMD)

Like the Blackfin processor, the ARM instruction set provides some features which are quite typical for DSPs. There are instructions allowing the programmer to split two 32-bit registers into four independent 16-bit registers and calculate the sum or difference of them. The simultaneous calculation of two different operations (i.e., add and subtract) on the 16-bit registers is

<sup>&</sup>lt;sup>10</sup>Confer [GS05] and [ARM05, p. A2.1-A2.15].

<sup>&</sup>lt;sup>11</sup>Confer [ARM11a] for further information.

also possible. Moreover, the user may split a 32-bit register into four 8-bit registers. In this case, only one arithmetic instruction may be executed simultaneously on all registers.<sup>12</sup>

Besides these types of simple arithmetic functions, it is also possible to multiply two 16-bit values, add or subtract a third register and save the result in a destination register. Alternatively, there are instructions dealing with four 16-bit registers, which are multiplied (separate multiplication of high halfword and low halfword of each 32-bit register). The results of both multiplications are summed up and added to the value of another register. The result of the whole operation is saved to the specified destination register.<sup>13</sup>

So far, the SIMD instructions of the ARM processor nearly provide the same functionality as the instruction set of the Blackfin processor. Nevertheless, there are special load and store instructions allowing to get or save multiple registers from or to memory. The user has access to all visible general-purpose registers of the current mode, including the program counter.<sup>14</sup> Code Example 2.3 shows how concurrently storing and loading multiple registers is done: The first part is the instruction itself, STM, which stands for *store multiple*. It is followed by the addressing mode *decrement after*, DA, and the base address register R1. The optional exclamation mark indicates that the value of R1 should be updated after the instruction. This might be useful when using R1 as the base address register of a stack. The last part of the instruction is a list of registers which shall be transferred to the memory. The LDMIB (*load multiple with increment before*) instruction in the last line of the example restores the state of the previously saved registers.

**Code Example 2.3** Storing and loading of multiple registers with a single 32 bit instruction. The example is based on [ARM05, p. A3.26].

STMDA R1!, {R2, R5, R7 - R9, R11} ... LDMIB R1!, {R2, R5, R7 - R9, R11}

#### **2.2.3** Floating Point Instructions<sup>15</sup>

Some ARM processors provide operations on floating point vectors, which are executed on a coprocessor. This extension is called the *vector floating-point architecture*, abbreviated VFP. The format of the numbers is based on the IEEE 754 standard and offers single and double precision operations. Besides the usual arithmetic operations (addition, subtraction, multiplication and division), the VFP module also provides a *multiply and accumulate* instruction on floating point registers. One special arithmetic instruction is the *square root* operation, which allows the calculation of the square root of a single or double precision floating point register.

<sup>&</sup>lt;sup>12</sup>Confer [ARM05, p. A3.14f].

<sup>&</sup>lt;sup>13</sup>Confer [ARM05, p. A3.10ff].

<sup>&</sup>lt;sup>14</sup>Confer [ARM05, p. A3.26f, A4.36-A4.42].

<sup>&</sup>lt;sup>15</sup>Confer [ARM05, p. C1.1-C4.126]

#### 2.2.4 Predicated Instructions<sup>16</sup>

One of the main features of the ARM processors are the so-called *predicated* or *conditional* instructions. This means that the programmer can, for nearly every instruction, specify a condition on which it shall be executed. If the condition is not met, the instruction behaves like a NOP. The condition flags for each instruction are evaluated (e.g., equal or less than) and compared with the CPSR (Current Program Status Register). This mechanism implies that all instructions which might change the flags of the CPRS should also only be able to write them when specified. Otherwise, the condition for all following instructions might become invalid.

The advantage of this technique is that small blocks of if-then-else code can be translated easily. The condition is used as a predicate for all instructions of the then-block, whereas the negated condition serves as predicate for the else-branch. Of course, it is not easy to translate complex nested if-then-else-statements without any conditional branch, but the CFG of the resulting assembler code may be much simpler for the WCET analysis. Moreover, predicated instructions allow the user to convert the CFG of a given program to a single-path variant as explained in Section 1.2.

Code example 2.4 shows a possible translation of a simple if-then-else statement: In the first line, R3 is subtracted from R2 and the result saved to R1. The suffix S after the SUB instruction indicates that the flags in the CPSR should be updated. The next instruction, which adds R6 to R5 and saves the result in R4, will only be executed if R2 and R3 are equal, meaning that R1 is zero. The last ADD instruction is only executed when R2 and R3 are not equal. It is also possible to use any other condition for the instructions, they do not have to be mutually exclusive.

**Code Example 2.4** Example for conditional execution of the ADD instruction: depending on the result of the first subtraction, either the second or the third line is executed. Confer [ARM11b, p. A8.24f, p. A8.422f].

| SUBS  | R1, | R2, | R3 |

|-------|-----|-----|----|

| ADDEQ | R4, | R5, | R6 |

| ADDNE | R4, | R5, | R7 |

#### 2.2.5 Thumb Instruction Set

"The Thumb instruction set was developed as a 16-bit instruction set with a subset of the functionality of the ARM instruction set. It provides significantly improved code density, at a cost of some reduction in performance."<sup>17</sup>

This quotation shows the original intention of the Thumb instruction set, namely to provide a reduction of the quite powerful ARM instruction set in order to achieve a higher code density. As most ARM processors support both types of instruction sets, it is possible to switch between them at runtime. There are two instructions providing this switching functionality:<sup>18</sup>

<sup>&</sup>lt;sup>16</sup>Confer [ARM11b, p. A4.3, p. A8.8].

<sup>&</sup>lt;sup>17</sup>See [ARM11b, p. A1.3]

<sup>&</sup>lt;sup>18</sup>Confer [ARM05, p. A4.16-A4.20].

- BX The so-called *branch and exchange* instruction conditionally performs a jump to the address given in the specified register. The LSB of the address register indicates whether the instruction at the destination address is a normal ARM instruction or a Thumb instruction.

- BLX The *branch, link and exchange* instruction is one of the few instructions which have no conditional field and are always executed. The semantics are quite similar to the BX instruction, but the address of the following instruction is saved in R14. The instruction can be used for a function call to a subroutine provided in the Thumb instruction set. Returning from the subroutine may be done using the BX instruction with R14 as address register.

Version 2 of the Thumb instruction set was introduced with the sixth version of the ARM instruction set (ARMv6). It provides additional features and also makes use of 32-bit instructions. One major advantage of the Thumb instruction set version 2 is that it supports nearly the full functionality of the ARM instruction set, while still offering a higher code density. Although one of the key features of the ARM instruction set, namely the conditional execution of instructions as presented in Section 2.2.4, is not supported, it is possible to conditionally execute a block of four instructions: Code example 2.5 shows the syntax and semantics of the IT instruction, which is an acronym for *if-then*. The single argument of the instruction is the condition for the the subsequent instruction. This is "not equal" (NE) in our case. The mask TTE after the instruction stands for "then", "then" and "else", meaning that the second and third instruction will also be executed if the condition is met, whereas the fourth instruction is only executed if the condition is not fulfilled. Of course, it is possible to specify any other execution mask. By regularly making use of this instruction, it is possible to provide predicated instructions for the Thumb instruction set, too. One disadvantage is that none except the last instruction may be a jump or similar instruction, because it could provoke undefined behavior according to the manual.

**Code Example 2.5** Conditional execution of Thumb instructions by making use of the IT instruction. See [ARM10, p. A7.277f] for more details.

ITTTE NE STR R2, [SP] ADDC R1,R1,#1 LDR R2, R1 SUB R1,R1,#1

#### 2.2.6 Conclusion

ARM processors are currently among of the most widely used processors in embedded applications and provide low power consumption, high code density and a powerful instruction set. Moreover, with the powerful features of floating point operations (e.g. square root implemented in hardware) and predicated instructions, WCET analysis of programs may be easier, especially when the algorithms involve floating point operations presented in Section 2.2.3. Additionally, ARM processors offer a considerable range of SIMD instructions, which are useful for finding an efficient solution for DSP applications.

Nevertheless, a compiler trying to find an assembler translation feasible for WCET analysis (e.g., a single-path transformation) of a given program requires sophisticated and complex techniques. That is the reason why the programmer has to be aware of the specific challenges and problems of an algorithm and may have to support the compiler.

Another problem regarding WCET analysis is to find the exact timing of instructions: As most ARM processors make use of static and dynamic branch prediction, but only within certain bounds, the calculation of the exact duration of a jump or conditional branch is nearly impossible. Although most operations take one or two clock cycles to finish, there are some instructions, like multiplications and coprocessor instructions, which may take up to five clock cycles, but may finish earlier, depending on the instruction length and whether they are conditional. Consequently, WCET analysis of a concrete single-path translation of a given code may also be very complex, even if the timing model does not include caches, which are also part of most ARM processors.<sup>19</sup>

#### 2.3 Atmel AVR Microcontrollers

#### 2.3.1 General Features

Atmel offers two different types of microcontrollers: One for small embedded applications such as automotive and peripheral controllers, and the other one for general-purpose applications including DSPs. The first type is the 8-bit variant of AVR microcontrollers, the second the newer 32-bit variant. Because the instruction set of the 32-bit AVR was developed completely from scratch, there are not many similarities to the 8-bit version. The naming "8-bit" and "32-bit" only relates to the bit-width of the general-purpose registers and has nothing to do with the instruction length of the instruction sets. In the following subsections, both types of instruction sets and the main features of the corresponding microcontrollers are presented.

#### **2.3.2 8-Bit AVR Instruction Set**<sup>20</sup>

Atmel's 8-bit microcontrollers are mainly used for embedded controlling tasks, including distributed systems, and provide programmers with a small, but powerful instruction set. They were introduced by Atmel in 1996 and have been quite successful since then.<sup>21</sup> Nearly all 8bit AVR microcontrollers provide numerous features for digital and analog input and output. These include analog comparators, ADCs, various timer functions (PWM, input capture, etc.), interrupt-triggered input pins and hardware implementations of different communication interfaces (e.g., UART, SPI, I<sup>2</sup>C).

One of the main advantages of the 8-bit AVR instruction set is its simplicity, which makes it quite easy for beginners to get in touch with assembler and microcontroller programming.

<sup>&</sup>lt;sup>19</sup>Confer [ARM09, p. 16.1-16.34].

<sup>&</sup>lt;sup>20</sup>Based on [Atm10].

<sup>&</sup>lt;sup>21</sup>Confer [Atm11, p. 2]

Moreover, most of the microcontrollers are very cheap and affordable for private persons. These are the reasons why they are a common solution for hobby engineers. Nearly all instructions have a length of 16 bits, with the exception of calling, jumping, loading and storing functions with absolute addresses. As all registers have a width of 8 bits, it is possible to initialize a register just with one instruction, which is usually not the case for most instruction sets. The 8-bit AVR instruction set provides all arithmetic functions except for integer division. Moreover, bit manipulating instructions like setting or clearing a bit of a register, data transfer functions like loading from and storing to memory, and control flow instructions like conditional branches are supported. Naturally, all arithmetic functions are also available for integers with more than 8 bits (add with carry bit etc.).

The 8-bit AVR instruction set does not provide any sophisticated SIMD instructions like Blackfin or ARM processors, and there is no possibility of conditional execution of any instruction.<sup>22</sup> Nevertheless, some devices offer a hardware implementation of DES having nearly constant execution times of one encryption or decryption operation. This can make WCET analysis of applications involving DES quite easy, although this is a rather uncommon scenario.

As 8-bit AVR processors do not have any caches or complex pipelines and only use static branch prediction, the timing of all instructions is nearly independent of any constraints. This makes the 8-bit AVR instruction set very convenient for WCET analysis. Nevertheless, there are no features for single-path conversion. Consequently, the WCET analysis is highly dependent on the complexity of the CFG of a given program.

#### 2.3.3 32-Bit AVR Instruction Set<sup>23</sup>

Like the Thumb version 2 instruction set of ARM processors (see Section 2.2.5), commonly used instructions have a length of 16 bits whereas more powerful, but rare instructions are encoded with 32 bits. Like nearly all modern processors, 32-bit AVR microcontrollers offer several processor modes for exception and interrupt handling. Moreover, there are several pipeline stages which allow to execute an instruction nearly every clock cycle. Some 32-bit AVR processors also offer hardware support for the Java virtual machine so that Java byte code can be executed directly, without retranslating the program.

Like ARM and Blackfin processors, 32-bit AVR microcontrollers provide a range of different SIMD instructions, including *multiply accumulate* and parallel adding and subtracting on two halfwords of a 32-bit register (see Section 2.1.3 for further details). Additionally, it is possible to load and store multiple registers from and to memory. Refer to the architecture manual ([Atm11]) for a detailed description of all SIMD instructions.

In contrast to ARM processors, it is not possible to execute all instructions conditionally. Nevertheless, the most common operations may be predicated so that they are only executed when a given condition is met. These operations include conditional add, subtract, return, load and store instructions, which allow single-path conversion of any given code.

Like the Blackfin processor, 32-bit AVR microcontrollers allow to control the cache explicitly: There are instructions in the supervisor mode for prefetching data and instructions and for

<sup>&</sup>lt;sup>22</sup>One exception are the sbrc and sbrs (skip next instruction if bit in register is cleared, resp. set). <sup>23</sup>Based on [Atm11]

setting control bits in the page table of the memory. Thus, an operating system can implement a custom replacement strategy for pages and caches.

Another interesting feature is the possibility to evaluate the current performance. The hardware mechanism to do that works as following: There is one counter register which is incremented every clock cycle. Additionally, there are two so-called *performance counters* which are incremented when a specified event occurs. By monitoring certain events, like the completion of an instruction execution or a cache miss, it is possible to calculate performance statistics during operation, with only minimal additional delay.

#### 2.3.4 Conclusion

Although the 8- and 32-bit versions of the AVR instruction set are very different, they both offer some interesting features which could help making WCET analysis easier: On one hand, the timing analysis of 8-bit AVR instructions is easy because there are nearly no internal or external dependencies such as pipeline stalling, cache misses or data dependencies. On the other hand, 32-bit AVR microcontrollers offer some conditional instructions which make single-path conversion possible. Moreover, calculated theoretical results of WCET analysis may be verified by evaluating the performance counter registers.

Unfortunately, the 8-bit AVR instruction set does not provide any predicated instructions, which can make WCET analysis quite complicated when analyzing translated assembler code. The 32-bit AVR is not 100 percent suitable for hard real-time tasks, either: Although a single-path conversion is theoretically possible, the resulting code might be useless for real-time systems due to the increased runtime. Moreover, the provided performance-enhancing features like caches and pipelining prohibit a completely correct WCET analysis.

#### 2.4 Infineon TriCore Processors

#### **2.4.1** General Features<sup>24</sup>

The Infineon TriCore processor was designed with the intention to unite the features of three different types of processors:

- CPUs provide hardware mechanisms which are useful for operating systems. Moreover, CPUs usually have the ability to deal with floating point numbers and support memory management.

- MCUs are efficient when dealing with interrupts and bit manipulations.

- DSPs are designed to provide typical arithmetic instructions for signal processing applications, including multiplication and accumulation.

The TriCore tries to unite the advantages of all three types of processors in a single core, which is the reason for its name *TriCore*. It is mainly in use in automotive applications for control and communication tasks. Although Infineon states in the manual that the instruction set of the

<sup>&</sup>lt;sup>24</sup>Confer [Inf03a, p. 15-27]

processor is rather large, all instructions are encoded with 16 or 32 bits, which is a common technique for 32-bit processors.

The processor provides 16 data and 16 address registers with 32 bits length. That consequently means that a specific register may only be used by a subset of the instruction set. Nevertheless, operations dealing with address registers are optimized for address calculation, whereas instructions on data registers provide DSP and bit manipulating features.

#### 2.4.2 SIMD Instructions

Like all presented 32-bit processors, the TriCore supports multiply add, multiply subtract and multiply accumulate instructions. Additionally, it also supports the execution of so-called *packed* multiply add and subtract instructions: The lower and upper 16 bits of two registers are multiplied and the 32-bit result of each multiplication is added (subtracted) to (from) a 64-bit register. The concurrent execution of a multiply add and a multiply subtract instruction is also possible.<sup>25</sup>

Nearly all arithmetic instructions (except for division) are also available as *packed* instructions, which means that the operation on a 32-bit register behaves like an operation on two 16-bit or four 8-bit registers. In contrast to the Blackfin processor, simultaneous adding and subtracting of two 16-bit values is not possible. Nevertheless, the TriCore provides packed versions of a minimum and maximum instruction, which allow the calculation of the minimum/maximum of up to four bytes in one instruction.<sup>26</sup>

#### 2.4.3 Conditional Instructions and Branches<sup>27</sup>

Like the 32-bit AVR, the TriCore is not fully predicated, but provides some instructions which are only executed on a provided condition. The condition is saved in a register which may only be tested for equality or non-equality to zero. The TriCore has a 32-bit *select* and a 16-bit *conditional move* instruction. The *select* instruction saves the value of the first register to the destination register if the condition register is zero, otherwise, the value of the second register is saved to the destination register. This behavior can be compared to a hardware multiplexer which selects one of two input signals depending on a control signal. The *conditional move* is a restricted version of the *select* instruction and is only capable of taking data register 15 as conditional register. Moreover, depending on the value of d15, either the value of a specified register is saved to the destination register or the destination register remains untouched.

Beside the instructions just presented, there are also conditional *add* and *subtract* instructions. Depending on the value of the conditional register, which is only tested for non-equality to zero, the sum or difference of two registers is saved to a destination register. If the condition register is zero, the value of the destination register remains untouched. There is also a 16-bit version of these instructions: Data register 15 is implicitly used as condition register, and the destination register has to be equal to the second source register of the addition or subtraction.

The Infineon TriCore, like the Blackfin, provides a hardware support for loops: There is one instruction which increments or decrements a register, checks the value, and performs a jump to

<sup>&</sup>lt;sup>25</sup>Confer [Inf03a, p. 203-215 and p. 232-242]

<sup>&</sup>lt;sup>26</sup>Confer [Inf03a, p. 30-39 and p. 52f]

<sup>&</sup>lt;sup>27</sup>Confer [Inf03a, p. 68ff and p. 168ff]

a specified address if the result is equal to zero. Its assembler acronyms are JNEI and JNED, which stands for jump if not equal and increment or decrement, respectively. An improved variant is the loop instruction, which has a similar syntax, but is only executed the first time the loop is entered. The counting register is automatically decremented when the end of the loop is reached, and a check for zero is performed. According to the manual, using the loop instruction results in a much better performance than using the JNED instruction. Although there is no information about nested loops, it is stated in [Inf03b, p. 26] that the loop cache only comprises two levels. Consequently, having more than one inner loop does not enhance the performance.

#### 2.4.4 Timing Analysis<sup>28</sup>

The TriCore processor consists of two computational units; the integer processing (IP) and the load/store (LS) unit. The former is responsible for nearly all arithmetic instructions, whereas the latter is mainly responsible for address calculations and memory accesses. Disregarding conditional branches, pipeline hazards or multi-cycle instructions, all instructions take one clock cycle to finish. Moreover, it is also possible to execute one IP and one LS instruction – which do not depend on each other – in one clock cycle.

Pipeline stalls may occur when dealing with multiply accumulate instructions where one instruction uses the destination register of a preceding SIMD instruction as source register. In all other cases, the cycle duration is highly dependent on the type of instruction that follows. Infineon gives some recommendations for sophisticated instruction scheduling strategies. For example, a simple idea is to alternately use LS and IP instructions. The interested reader is referred to the manual and the guide for compiler writers for additional information.

#### 2.4.5 Conclusion

Although the TriCore unites nearly all presented *special features* of the Blackfin, ARM and 32bit AVR processors, analyzing the exact execution time of a given program is a quite challenging task. Firstly, one has to take into account the instruction scheduling; changing the order of only two instructions may cause a completely different result in the cycle count. Secondly, the static branch prediction model is very sophisticated and the exact number of cycles depends on the jump type (forward or backward jump).

Moreover, the possibilities when dealing with conditional instructions are very limited – in comparison with the ARM instruction set, as well as with the 32-bit AVR: Applying a single-path conversion to a given algorithm surely reduces the complexity of the CFG, but may have a tremendous effect on the WCET, which will certainly increase. Nevertheless, the Infineon TriCore processor provides some very interesting and useful instructions for WCET analysis, although the complex hardware implementation may cancel out the advantages of these features.

<sup>&</sup>lt;sup>28</sup>Confer [Inf03a, p. 264-275] and [Inf03b, p. 30-43].

#### 2.5 Tensilica Xtensa

#### **2.5.1** General Features<sup>29</sup>

In contrast to all other presented processors of the current chapter, the Tensilica Xtensa is no offthe-shelf ASIC, but provides the developer a basic set of features which may be fully adapted to personal needs. This ranges from the individual scaling of the size of cache, RAM and ROM to the implementation of custom instructions. In contrast to other FPGA-based processors<sup>30</sup> like Altera's NIOS II, the Xtensa is delivered with a complete toolchain allowing the customer to adapt hardware, compiler, and software individually. Additionally, the processor may be optimized for different characteristics like small die area or low power consumption.

The main application field of the Xtensa processor lies in hardware-software codesign: When there is an application-specific problem to be solved, which requires high performance of a single task and the general-purpose instruction set of an average processor, the Xtensa processor may be an adequate choice. Section 2.5.4 gives some practical examples of how to increase the performance of an application with the help of additional instructions implemented in hardware. The following sections give an overview of the Xtensa architecture and instruction set. At the end, the predictability of the processor is evaluated.

#### 2.5.2 Architecture Overview

As already mentioned, the Xtensa architecture is not fixed and may be configured and extended. In principle, it consists of five different types of modules/features:<sup>31</sup>

- **Base ISA Features** These modules are the only fixed parts of the Xtensa. They implement the basic instruction set, basic processor control features, memory access, and the processing pipeline, which consists of five stages (see below).

- **Configurable Functions** Like the base ISA features, these modules are part of every Xtensa implementation, but their parameters can be set to user-defined values. They include the register file, the instruction memory and the data memory. The memory size of each module may be chosen from a given list of options.

- **Optional Functions** In contrast to the configurable functions, optional modules may or may not be added to the current processor design. They include a JTAG controller, a debugging interface and several ALU features like multiply-accumulate, DSP and floating point operations.

- **Optional and Configurable Functions** These modules may or may not be added to the current processor design. They include data and instruction caches, data and instruction RAMs, timers, and an extension for exceptions and interrupts. Moreover, the user can specify several characteristics, such as cache size and cache replacement strategy.

<sup>&</sup>lt;sup>29</sup>Confer [Gon00].

<sup>&</sup>lt;sup>30</sup>Such processors are usually denoted *soft cores*.

<sup>&</sup>lt;sup>31</sup>Confer [Ten02, p. 1ff] and [Ten10, p. 6].

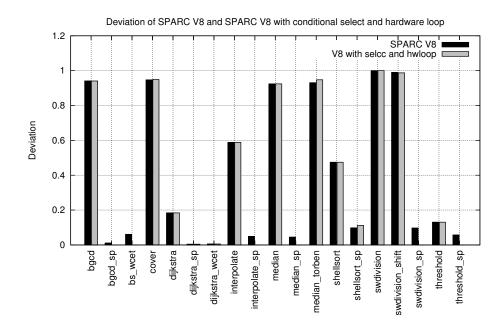

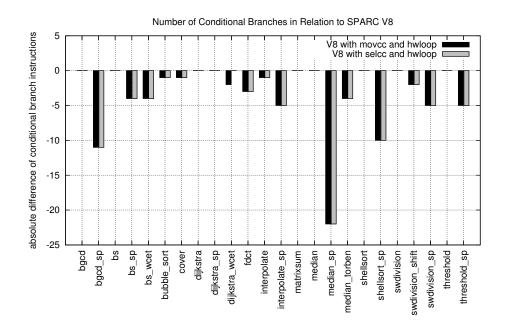

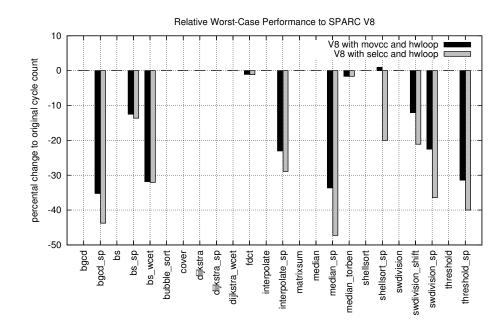

**Designer-Defined Features** These modules provide the highest freedom for the designer. With the help of a description language, the user may add individual modules for the ALU, thus providing application-specific instructions. Moreover, it is also possible to implement a user-defined load/store unit or to adapt the pipeline to support SIMD instructions.