FAKULTÄT FÜR INFORMATIK

**Faculty of Informatics**

# The Transient Tolerant Time-Triggered System-on-Chip (4TSoC)

### DISSERTATION

zur Erlangung des akademischen Grades

### Doktor/in der technischen Wissenschaften

eingereicht von

### Mikel Azkarate-askasua Blazquez

Matrikelnummer 0928311

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Priv.Doz. Dipl.-Ing. Dr.techn. Roman Obermaisser

Diese Dissertation haben begutachtet:

Die approbierte Originalversion dieser Dissertation ist an der Hauptbibliothek

The approved original version of this thesis is available at the main library of

the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

de

Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

(Priv.Doz. Dipl.-Ing. Dr.techn. Roman Obermaisser) (Prof. Dr. Kees G.W. Goossens)

Wien, 15.10.2012

(Mikel Azkarate-askasua Blazquez)

FAKULTÄT FÜR INFORMATIK

**Faculty of Informatics**

# The Transient Tolerant Time-Triggered System-on-Chip (4TSoC)

### DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

### Doktor/in der technischen Wissenschaften

by

### Mikel Azkarate-askasua Blazquez

Registration Number 0928311

to the Faculty of Informatics at the Vienna University of Technology

Advisor: Priv.Doz. Dipl.-Ing. Dr.techn. Roman Obermaisser

The dissertation has been reviewed by:

(Priv.Doz. Dipl.-Ing. Dr.techn. Roman Obermaisser) (Prof. Dr. Kees G.W. Goossens)

Wien, 15.10.2012

(Mikel Azkarate-askasua Blazquez)

## Erklärung zur Verfassung der Arbeit

Mikel Azkarate-askasua Blazquez Arizmendiarrieta 2, 20500 Arrasate (Baskenland)

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

## The Transient Tolerant Time-Triggered System-on-Chip (4TSoC)

Embedded systems of different application domains (offshore windmills, railway, avionic, etc.) can benefit from integrated architectures. The functionality that required several chips in the past can now be integrated in a single chip due to the recent advances on silicon technology miniaturization. This approach carries interesting economical benefits due to the reduction on cost of electronic components and interconnection.

Most of the current integrated architectures have been implemented using a software approach (e.g., a hypervisor) in order to build the illusion of having several execution environments on monolithic processor chips. However, building integrated architectures using a hardware approach, upon a Multi-Processor System-on-Chip (MPSoC), the system not only achieves a better performance, but also increased power efficiency, and significantly higher reliability. In fact, high integration enables small transistor technologies, but causes more sensitivity w.r.t. energy variations which requires new fault tolerance measures to overcome the transient fault rates (e.g., soft-errors) that have significantly increased.

This dissertation presents a Transient Tolerant Time-Triggered Systemon-Chip (4TSoC), an integrated architecture for safety-related embedded systems. The 4TSoC architecture introduces fault-tolerance mechanisms for application components, communication interfaces and the Time-Triggered Network-on-Chip. As a prerequisite for replication we introduce on-chip fault-containment mechanisms along with design methods to address fault containment during synthesis.

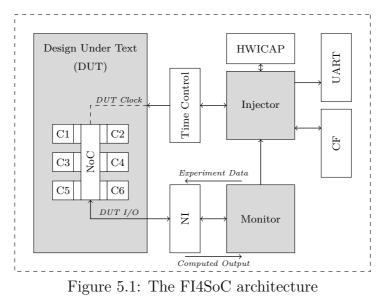

A Fault Injection for System-on-Chip (FI4SoC) has been developed to test state-of-the-art integrated architectures (e.g., XtratuM, TTSoC) and validate 4TSoC hardening configurations. The experiments have provided experimental evidence for reliability of the 4TSoC architecture in the presence of soft-errors.

## The Transient Tolerant Time-Triggered System-on-Chip (4TSoC)

Integrierte Architekturen stellen einen signifikanten Nutzen für eingebettete Systeme aus verschiedenen Anwendungsdomänen (z. B. Windenergie, Eisenbahn, Luftfahrtelektronik, etc.). Die Funktionalität, die bisher durch mehrere Einzelchips erreicht wurde, kann nun durch die Fortschritte der Silikonindustrie in einen einzigen Chip integriert werden. Dieser neue Ansatz bringt Kostenreduktion sowohl bezüglich der Anzahl der Komponenten als auch deren Verkabelung.

Viele gängige integrierten Systeme benutzen einen Softwareansatz (i.e. einen Hypervisor), um mehrere virtuelle Ausführungsumgebungen auf einem Chip zu emulieren. Im Gegensatz dazu basiert die vorliegende Arbeit auf einem Hardwareansatz, genauer einem "Multi-Processor System-on-Chip (MPSoC)". Diese Hardwarelösung bietet Vorteile hinsichtlich Performanz, Energieeffizienz und Zuverlässigkeit gegenüber dem Softwareansatz.

Diese Dissertation behandelt eine "Flüchtige Fehler tolerierende zeitgesteuerte System-on-Chip Architektur", die als integrierte Architektur für sicherheitskritische eingebettete Systeme konzipiert ist. Als Teil der Architektur wird eine Replikation der Applikationskomponenten und die dazugehörige Systemkomponente vorgestellt. Im Weiteren wird ein Fehlermodell für MPSoCs erarbeitet, das die Architektur durch Gliederung in Fehlerbegrenzungen ("Fault Containment Regions (FCR)") und deren Replikation beherrscht. Zum Testen der Architektur wurde ein Fehlereinstreuungssystem ("Fault Injection for System-on-Chip (FI4SoC)") entwickelt, um aktuelle integrierte Architekturen zu testen (z.B. XtratuM, TTSoC) und MaSSnahmen zur Härtung zu validieren.

Die Arbeit schlieSSt mit einer Betrachtung verschiedener MaSSnahmen zur Verbesserung der Fehlertoleranz in einem zeitgesteuerten System-on-Chip und deren Anwendbarkeit in verschiedenen Anwendungsdomänen.

## The Transient Tolerant Time-Triggered System-on-Chip (4TSoC)

Aplikazio domeinu ezberdinetako sistema txertatuak (itsasoko haizerrotak, trengintza, hegazkingintza, etab.) txip bakarrean integratutako arkitekturez profita daitezke. Aurrez txip anitzetan inplementatutako funtzionalitateak txip bakar batean sar daitezke orain azken urteotan silizio teknologiak jazo duen izugarrizko miniaturizazioari esker. Honek ekonomikoki oso interesgarria den txip eta interkonexio murrizketa dakar.

Sistema txertatuentzako integratutako arkitekturek software mekanismoak erabili dituzte prozesadore bakarreko txipetan exekuzio ingurune ezberdinen ilusioak sortzeko (adb., hiperbisoreak). Aldiz, integratutako arkitektura berberak hardware mekanismoak erabiliz eraikiz gero, txipean txertatutako prozesadore anitzeko sistema (ingelesez MPSoC) bat erabilita, errendimendu hobea lortzeaz gain, energetikoki, eta batez ere, segurtasunari dagokioenean abantail ugari lor litezke. Izan ere, aipatutako integrazioa ahalbidetzen duen transistore teknologia nimiñoak, energia bariazioetara sentikorragoak diren txipak ekarri ditu, eta honek mekanismo berriak eskatzen ditu falta iragankorren maiztasun igoera nabarmenari (soft-error deitutakoak bereziki) aurre egiteko.

Tesi honek falta iragankorrekiko indartutako MPSoC bat (4TSoC) aurkezten du, segurtasunarekin lotutako sistema txertatuentzako integratutako arkitektura bat. Txip barnean erreplikatutako konponenteen erabilera proposatzen du horretarako, bai aplikazioaren menpe dauden konponenteak inplementatzeko, baita arkitekturako sistema-konponenteak berak indartzeko ere. Konfigurazio guztiekin MPSoCak fidagarriago egiteko aukeren modelo bat sortu da. Gainera, erreplikazio hauek baliagarri suertatzeko beharrezkoa den falta-kontentzioa aurkezten du eta berau nola bermatu hardwarea sintetizatzeko orduan.

Txipean txertatutako sistemak frogatzeko falta injekzio erraminta bat (FI4SoC) garatu da, eta akademiak aurkeztutako beste integratutako arkitektura batzuk (XtratuM, TTSoC) ikertzeaz gain proposatutako 4TSoC konfigurazioen liburutegia baliozkotzat eman da. Azkenik, konfigurazio interesgarrienak aplikazio domeinu ezberdinetan duten balioa neurtu da.

## Acknowledgments

This dissertation has been developed in collaboration among the *Electronics* division of Ikerlan Research Center (Basque Country, Spain), the *Real-Time* System group of Vienna University of Technology (TU Wien, Austria) and the *Embedded Systems* group of the University of Siegen (Germany).

I would like to give very special thanks to six extraordinary professionals. First, to Prof. Roman Obermaisser for his full support in these 3 years, his great ideas and our passionate discussions in Vienna and Siegen. To Prof. Hermann Kopetz and Antonio Perez for giving me the opportunity to do this work between TU Wien and Ikerlan. To Prof. Kees Goossens for his reviews and contribution from Eindhoven as co-examiner of this thesis. And to Dr. Imanol Martinez and Dr. Jon Perez for their support from Ikerlan Research Center.

I would like to mention my colleges in Ikerlan (Iban, Niko and Xabi), TU Wien (Albrecht, Armin, Bekim, Benedikt, Christian E. S., Christian P., Ekarin, Harald, Michael, Roland, Oliver, Sven, Vaçlav and Wolfgang), Siegen (Rubaiyat and Zaher), all with whom I have discussed several points of my thesis and, of course, the rest of the friends and staff within the three institutions.

Finally, to all the people I crossed and enjoyed (I hope for long time) during these last years in Arrasate (Ander, Imanol, Jon and Vero), Vienna (Aaron, Ainhoa, Eirini, Iñaki, Irene, Jarek, Jonathan, Ju, Mikel G., Rocio, Sara and Virginia) and Siegen (Imad and Mohan).

## Contents

| Abs                   | stra | t                                                       |      |       |   | i    |

|-----------------------|------|---------------------------------------------------------|------|-------|---|------|

| Con                   | nten | s                                                       |      |       |   | ix   |

| $\operatorname{List}$ | of   | Figures                                                 |      |       |   | xiii |

| $\operatorname{List}$ | of   | Acronyms                                                |      |       | - | xvii |

| 1 I                   | Intr | duction                                                 |      |       |   | 1    |

| 1                     | .1   | Problem Statement                                       | <br> |       |   | 2    |

| 1                     | .2   | Proposed Solution                                       | <br> |       |   | 2    |

| 1                     | .3   | Contributions                                           | <br> |       | • | 3    |

| 1                     | .4   | Thesis Organization                                     | <br> | <br>• | • | 3    |

| 2 I                   | Bac  | ground and Basic Concepts                               |      |       |   | 7    |

| 2                     | 2.1  | The Notion of Time                                      | <br> |       |   | 7    |

|                       |      | 2.1.1 Time Flow and Models .                            | <br> |       |   | 7    |

|                       |      | 2.1.2 State                                             | <br> |       |   | 10   |

|                       |      | 2.1.3 Determinism                                       | <br> |       |   | 10   |

|                       |      | 2.1.4 Behavior and Service                              | <br> |       | • | 11   |

| 2                     | 2.2  | Job, Partition and Component .                          | <br> | <br>• | • | 11   |

|                       |      | 2.2.1 Job                                               | <br> | <br>• | • | 11   |

|                       |      | $2.2.2  \text{Partition} \dots \dots \dots \dots \dots$ | <br> |       | • | 11   |

|                       |      | 2.2.3 Component                                         | <br> |       |   | 12   |

| 2                     | 2.3  | Integrated Architectures                                | <br> |       |   | 13   |

|                       |      | 2.3.1 Implementation                                    | <br> |       | • | 13   |

|                       |      | 2.3.2 Technologies                                      | <br> |       |   | 16   |

| 2                     | 2.4  | Dependability Concepts                                  | <br> |       |   | 18   |

|   |     | 2.4.1    | Physical Faults in Semiconductors                      | 19 |

|---|-----|----------|--------------------------------------------------------|----|

|   |     | 2.4.2    | Fault Containment Regions (FCRs)                       | 21 |

|   |     | 2.4.3    | Fault Tolerance                                        | 21 |

|   |     | 2.4.4    | Fault Injection                                        | 22 |

|   | 2.5 | Cogni    | tive Complexity                                        | 24 |

| 3 | Ana | alysis d | of the State-of-the-Art                                | 27 |

|   | 3.1 | Xtrati   | uM Hypervisor                                          | 27 |

|   |     | 3.1.1    | Communications and Timeliness                          | 28 |

|   |     | 3.1.2    | Fault Handling                                         | 29 |

|   | 3.2 | Cell M   | Aulti-Processor                                        | 29 |

|   |     | 3.2.1    | Communications and Timeliness                          | 30 |

|   |     | 3.2.2    | Fault Handling                                         | 30 |

|   | 3.3 | CoMF     | $PS_0C$                                                | 30 |

|   |     | 3.3.1    | Communications and Timeliness                          | 31 |

|   |     | 3.3.2    | Fault Handling                                         | 31 |

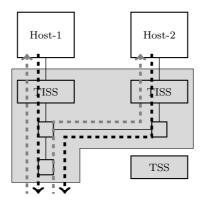

|   | 3.4 | TTSo     | C                                                      | 31 |

|   |     | 3.4.1    | Communications and Timeliness                          | 32 |

|   |     | 3.4.2    | Fault Handling                                         | 33 |

|   | 3.5 | IEC 6    | 1508 On-Chip Replication                               | 33 |

|   |     | 3.5.1    | Fault Handling                                         | 34 |

|   | 3.6 | Analy    | rsis                                                   | 35 |

|   |     | 3.6.1    | Timeliness                                             | 35 |

|   |     | 3.6.2    | On-Chip Design Fault Containment                       | 36 |

|   |     | 3.6.3    | On-Chip Physical Fault Containment and Fault Tolerance | 37 |

|   | 3.7 | Concl    | usion                                                  | 37 |

| 4 | The | e 4TSo   | C                                                      | 41 |

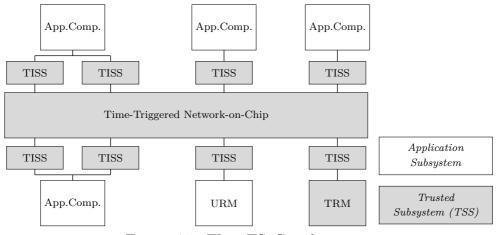

|   | 4.1 | Descri   | iption                                                 | 42 |

|   |     | 4.1.1    | Application-Specific Subsystem                         | 42 |

|   |     | 4.1.2    | Trusted Subsystem                                      | 43 |

|   | 4.2 | Fault    | Hypothesis                                             | 43 |

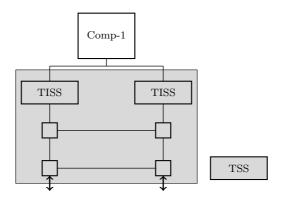

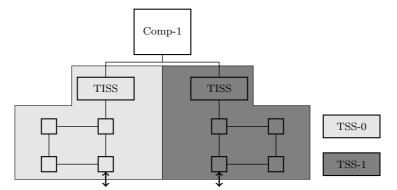

|   |     | 4.2.1    | Fault Containment Regions                              | 44 |

|   |     | 4.2.2    | Failure Modes and Rates Assumptions                    | 44 |

|   | 4.3 | 4T Co    | pre Services                                           | 45 |

|   |     | 4.3.1    |                                                        | 45 |

|          |     | 4.3.2  | 4T Communication Services                                                                  | 47 |

|----------|-----|--------|--------------------------------------------------------------------------------------------|----|

|          |     | 4.3.3  | 4T Configuration Services                                                                  | 49 |

|          |     | 4.3.4  | 4T Execution Services                                                                      | 52 |

|          | 4.4 | 4TSo   | C Fault Tolerance Model                                                                    | 52 |

|          |     | 4.4.1  | On-chip TMR                                                                                | 53 |

|          |     | 4.4.2  | On-chip TMR Upon Replicated Channels                                                       | 54 |

|          |     | 4.4.3  | Recovery upon TMR                                                                          | 54 |

|          | 4.5 | 4TSo   | C Synthesis Model                                                                          | 55 |

|          |     | 4.5.1  | ASIC and FPGA End-Devices                                                                  | 55 |

|          |     | 4.5.2  | Xilinx Implementation Patterns                                                             | 58 |

|          |     | 4.5.3  | An IEC-61508 Compliant FPGA                                                                | 60 |

| <b>5</b> | Eva | luatio | n Tools                                                                                    | 63 |

|          | 5.1 | FI4So  | C: Fault Injection Framework                                                               | 63 |

|          |     | 5.1.1  | Fault Injector Requirements                                                                | 63 |

|          |     | 5.1.2  | FI4SoC Description                                                                         | 65 |

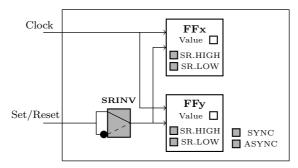

|          |     | 5.1.3  | Injection of Supported Faults                                                              | 67 |

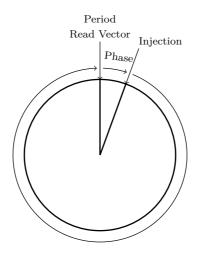

|          |     | 5.1.4  | Injection Process                                                                          | 69 |

|          |     | 5.1.5  | Framework Tools                                                                            | 70 |

|          |     | 5.1.6  | Discussion                                                                                 | 71 |

|          | 5.2 | The N  | Aöbius Tool                                                                                | 74 |

|          |     | 5.2.1  | The Möbius Tool and FI4SoC Framework                                                       | 74 |

|          | 5.3 | Evalu  | ated Architectures                                                                         | 75 |

|          |     | 5.3.1  | XtratuM LEON3 Implementation                                                               | 75 |

|          |     | 5.3.2  | TTSoC Implementation                                                                       | 75 |

|          |     | 5.3.3  | 4TSoC Implementation                                                                       | 76 |

| 6        | Exp | oerime | nt Campaigns                                                                               | 79 |

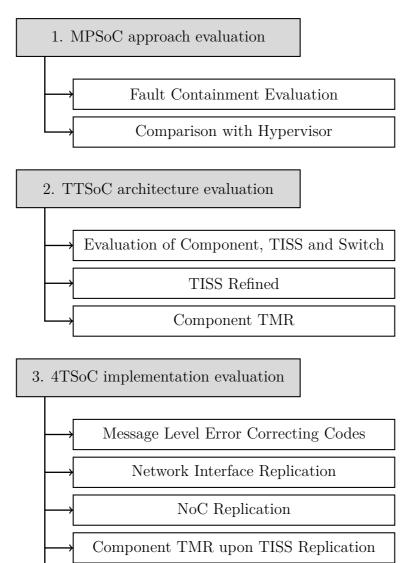

|          | 6.1 | MPSc   | C approach evaluation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                | 81 |

|          |     | 6.1.1  | Fault Containment Evaluation                                                               | 81 |

|          |     | 6.1.2  | Comparison with Hypervisor                                                                 | 82 |

|          | 6.2 | TTSo   | C architecture evaluation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 83 |

|          |     | 6.2.1  | Evaluation of Component, TISS and Switch Reliability $% \mathcal{T}_{\mathrm{r}}$ .        | 84 |

|          |     | 6.2.2  | TISS Refined                                                                               | 85 |

|          |     | 6.2.3  | Component TMR                                                                              | 87 |

|          | 6.3 | 4TSo   | C implementation evaluation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$      | 88 |

|              |                      | 6.3.1   | Message Level Error Correcting Codes                                                                                             | 89  |

|--------------|----------------------|---------|----------------------------------------------------------------------------------------------------------------------------------|-----|

|              |                      | 6.3.2   | Network Interface Replication                                                                                                    | 91  |

|              |                      | 6.3.3   | NoC Replication                                                                                                                  | 93  |

|              |                      | 6.3.4   | Component TMR upon TISS Replication                                                                                              | 93  |

|              |                      | 6.3.5   | Recovery                                                                                                                         | 95  |

| 7            | Res                  | ults    |                                                                                                                                  | 99  |

|              | 7.1                  | MPSo    | C vs. Hypervisor                                                                                                                 | 99  |

|              |                      | 7.1.1   | Fault Containment Evaluation                                                                                                     | 99  |

|              |                      | 7.1.2   | Comparison to a Hypervisor Approach                                                                                              | 100 |

|              | 7.2                  | TTSo    | C Evaluation $\ldots$                           | 100 |

|              |                      | 7.2.1   | Component, TISS and Switch Evaluation                                                                                            | 101 |

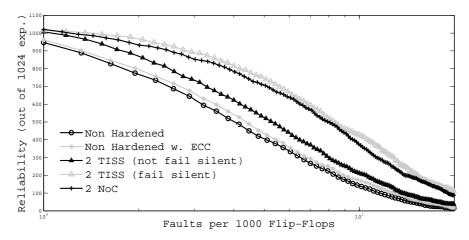

|              |                      | 7.2.2   | TISS Refinement                                                                                                                  | 101 |

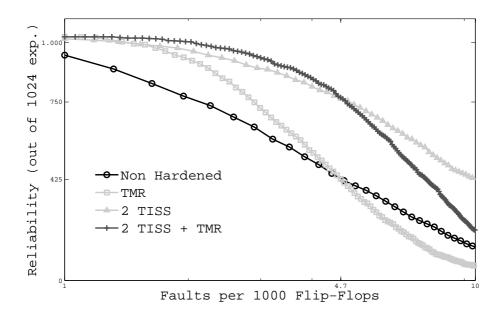

|              |                      | 7.2.3   | Component TMR                                                                                                                    | 103 |

|              | 7.3                  | 4TSo    | $C Evaluation \dots \dots$ | 103 |

|              |                      | 7.3.1   | Message Level Error Correcting Codes                                                                                             | 103 |

|              |                      | 7.3.2   | 4T Communication Services                                                                                                        | 104 |

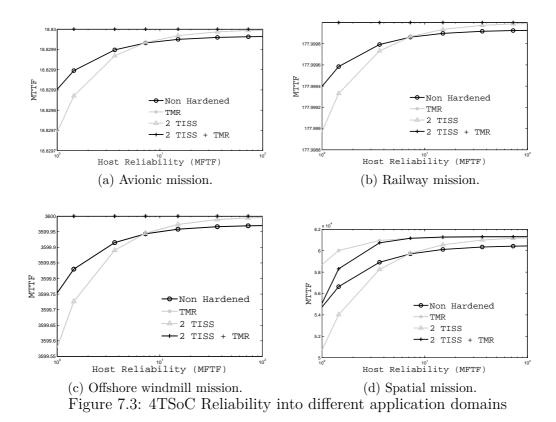

|              |                      | 7.3.3   | Component Replication                                                                                                            | 105 |

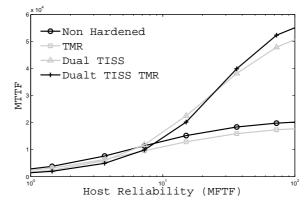

|              |                      | 7.3.4   | Recovery                                                                                                                         | 109 |

|              | 7.4                  | Summ    | nary of the Results                                                                                                              | 112 |

| 8            | Cor                  | nclusio | n                                                                                                                                | 115 |

|              | 8.1                  | Summ    | nary                                                                                                                             | 115 |

|              | 8.2                  | Futur   | e Research                                                                                                                       | 116 |

| Bi           | ibliog               | graphy  |                                                                                                                                  | 119 |

| P            | ublic                | ations  |                                                                                                                                  | 131 |

| $\mathbf{C}$ | Curriculum Vitae 133 |         |                                                                                                                                  | 133 |

# List of Figures

| 1.1  | Thesis Organization                                                   | 5  |

|------|-----------------------------------------------------------------------|----|

| 2.1  | Time representation                                                   | 7  |

| 2.2  | The dense and discrete models of time                                 | 8  |

| 2.3  | Distributed models of time.                                           | 8  |

| 2.4  | Cyclic representation of an embedded control system process           | 9  |

| 2.5  | Interfaces of a component                                             | 12 |

| 2.6  | (Bare-metal) Embedded hypervisor architecture $\ldots \ldots \ldots$  | 14 |

| 2.7  | A NoC based MPSoC                                                     | 16 |

| 2.8  | Actel antifuze technology cross section                               | 18 |

| 2.9  | Memory cells technologies                                             | 18 |

| 2.10 | Fundamental chain of dependability threats                            | 18 |

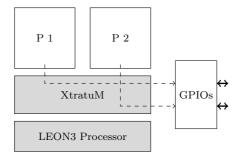

| 3.1  | XtratuM architecture                                                  | 28 |

| 3.2  | The Cell processor                                                    | 29 |

| 3.3  | The CoMPSoC architecture                                              | 31 |

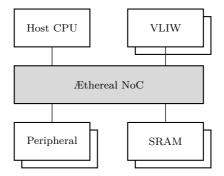

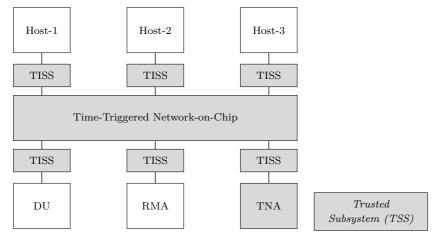

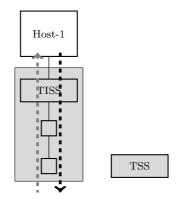

| 3.4  | The TTSoC architecture. The gray area denotes the TSS                 | 32 |

| 3.5  | IEC 61508 on-chip block replication                                   | 33 |

| 3.6  | Applying IEC 61508 boundaries for integrated architecture $\ . \ .$ . | 38 |

| 3.7  | Solutions mapped on physical and design fault containment axes        | 39 |

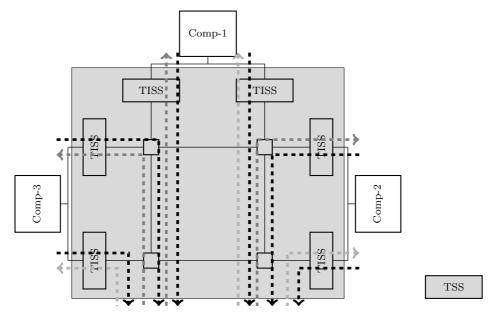

| 4.1  | The 4TSoC architecture                                                | 41 |

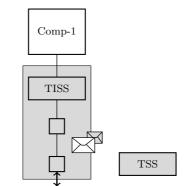

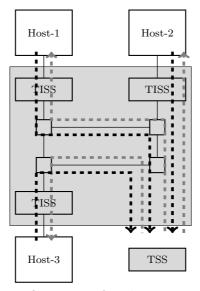

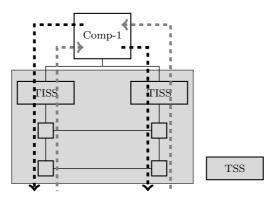

| 4.2  | TISS Replication for 4TSoC                                            | 48 |

| 4.3  | NoC Replication for 4TSoC                                             | 49 |

| 4.4  | Error Correcting Codes for 4TSoC                                      | 50 |

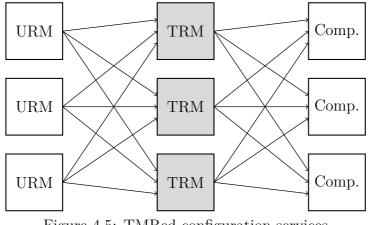

| 4.5  | TMRed configuration services                                          | 51 |

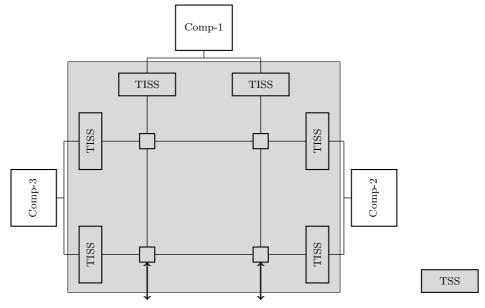

| 4.6  | Application component TMR                                             | 54 |

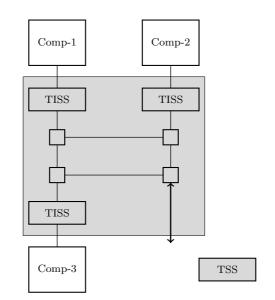

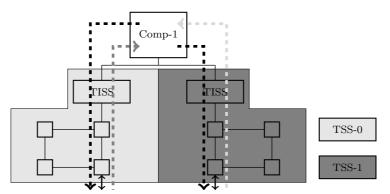

| 4.7  | TMR configuration with two TISSes                                     | 55 |

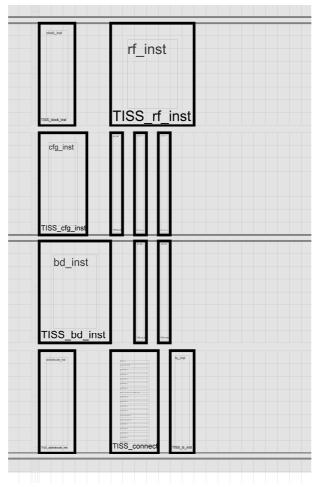

| 4.8  | 4TSoC layout on a Virtex-4 LX160 FPGA (FPGA Editor) $\ldots$      | 59  |

|------|-------------------------------------------------------------------|-----|

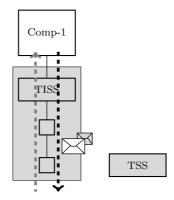

| 5.1  | The FI4SoC architecture                                           | 66  |

| 5.2  | Simplified representation of a Virtex-4 CLB slice                 | 68  |

| 5.3  | Fault injection period                                            | 70  |

| 5.4  | Tool work-flow in the framework                                   | 71  |

| 6.1  | Experiment campaings                                              | 80  |

| 6.2  | A two component MPSoC for fault containment assessment            | 81  |

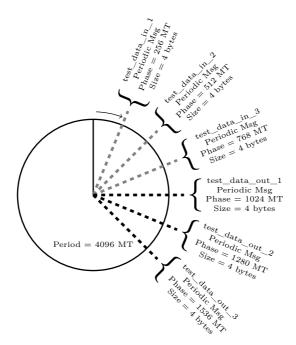

| 6.3  | NoC scheduling for fault containment evaluation                   | 82  |

| 6.4  | Hypervisor assessment setup                                       | 83  |

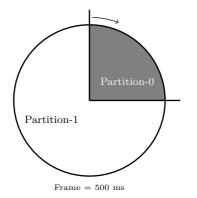

| 6.5  | Uneven partition durations on the processor frame                 | 84  |

| 6.6  | Experiment configuration for the TTSoC assessment $\ldots \ldots$ | 85  |

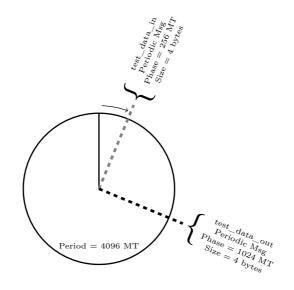

| 6.7  | Experiment schedule for the TTSoC assessment                      | 86  |

| 6.8  | Mapping of the TISS entities on the FPGA layout                   | 88  |

| 6.9  | Experiment configuration for the TMR configuration assessment     | 89  |

| 6.10 | Experiment schedule for TMR assessment                            | 89  |

| 6.11 | Experiment configuration for the message-level ECC assessment     | 90  |

| 6.12 | Experiment schedule for ECC assessment                            | 91  |

| 6.13 | Experiment configuration for the TISS replication assessment      | 91  |

| 6.14 | Experiment schedule for dual TISS                                 | 92  |

| 6.15 | Experiment configuration for the NoC replication assessment       | 93  |

| 6.16 | Experiment schedule for dual NoC assessment                       | 94  |

| 6.17 | Experiment configuration for the TMR-dual TISS assessment         | 95  |

| 6.18 | Experiment schedule for Dual TMR assessment                       | 96  |

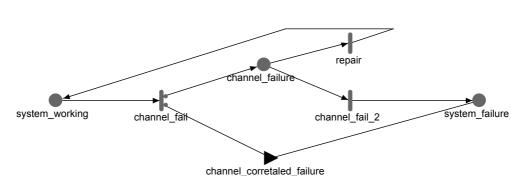

| 6.19 | Möbius model of component TMR                                     | 96  |

| 7.1  | Trusted system component hardening results                        | 104 |

| 7.2  | Application components hardening results                          | 105 |

| 7.3  | 4TSoC Reliability into different application domains              | 108 |

| 7.4  | Mission where dual TISS configurations are clearly more reliable  | 109 |

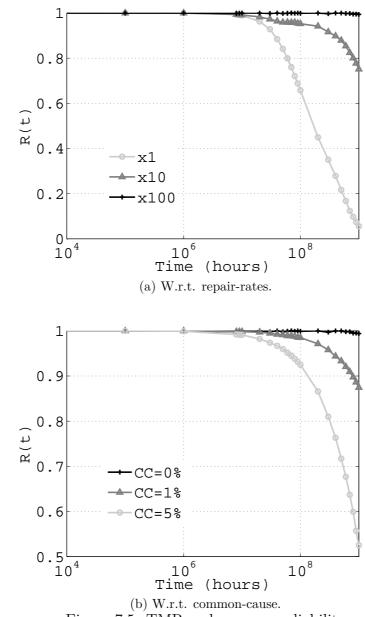

| 7.5  | TMR and recovery reliability                                      | 110 |

## List of Tables

| 2.1  | ITRS prediction for soft errors and MBUs                                        | 20  |

|------|---------------------------------------------------------------------------------|-----|

| 3.1  | Techniques that increase and decrease the $\beta$ -factor                       | 35  |

| 3.2  | Comparison of integrated architecture implementation features .                 | 40  |

| 4.1  | Comparison for end-device candidates                                            | 58  |

| 5.1  | Information of a fault vector                                                   | 69  |

| 5.2  | LEON3 resources on Xilinx Virtex-4                                              | 75  |

| 5.3  | 4TSoC IP resource on Xilinx Virtex-4                                            | 76  |

| 7.1  | Common-independent failures in XtratuM Hypervisor                               | 100 |

| 7.2  | Mean Fault to Fail and number of partitions                                     |     |

| 7.3  | Results for the TTSoCA blocks                                                   | 101 |

| 7.4  | TISS reliability for different cycle length                                     | 101 |

| 7.5  | TISS reliability per building instance                                          | 102 |

| 7.6  | Normal TISS, internally TMRed TISS, and dual TISS reliability                   | 102 |

| 7.7  | Results for the TMR experiment                                                  | 103 |

| 7.8  | ECC contribution in the different blocks $\ldots \ldots \ldots \ldots \ldots$   | 104 |

| 7.9  | Mission times by application domain $\ldots \ldots \ldots \ldots \ldots \ldots$ | 108 |

| 7.10 | Results for 4TSoC hardening mechanism                                           | 111 |

| 7.11 | Summary of MPSoC Apporach Evaluation                                            | 112 |

| 7.12 | Summary of the TTSoC Evaluation                                                 | 113 |

| 7.13 | Summary of the 4TSoC Evaluation                                                 | 114 |

|      |                                                                                 |     |

## List of Acronyms

**4TSoC** Transient Tolerant Time-Triggered System-on-Chip **ASIC** Application Specific Integrated Circuit **AUTOSAR** Automotive Open System Architecture **CF** Compact Flash **COTS** Commercial Off-The-Shelf **CPS** Cyber-Physical System **CRCR** Capture-Readback-Controlled Reset **DAS** Distributed Application Subsystem **DMA** Direct Memory Access **ECC** Error Correcting Codes **EDC** Error Detection Code **EMI** Electromagnetic Interference FCR Fault Containment Region FI4SoC Fault Injection for System-on-Chip **FIT** Failure in Time **FPGA** Field Programmable Gate Array **GPIO** General Purpose Input Output **HWIFI** Hardware Implemented Fault Injection **IMA** Integrated Modular Avionics

- **IP** Intellectual Property

- **LI** Local Interface

- **LIF** Linking Interface

- **LRM** Local Resource Manager

- **NoC** Network-on-Chip

- **MBD** Model Based Design

- **MBU** Multiple Bit Upset

- **MFTF** Mean Faults To Failure

- **MMU** Memory Management Unit

- **MTTF** Mean Time To Failure

- MTTR Mean Time To Recover

- MPSoC Multi-Processor System-on-Chip

- **NoTA** Network on Terminal Architecture

- **NI** Network Interface

- **OS** Operating System

- **RTL** Register Transfer Level

- **RTOS** Real-Time Operating System

- **PLB** Peripheral Local Bus

- **PIM** Platform Independent Model

- **PSM** Platform Specific Model

- **SEE** Single Event Effect

- **SET** Single Event Transient

- **SEU** Single Event Upset

- **SOI** Silicon On Insulator

- SWIFI Software Implemented Fault Injection

- **TDI** Technology-Dependant Interface

- **TDM** Time Division Multiplexing

- **TID** Total Ionizing Dose

- **TII** Technology-Independent Interface

- **TISS** Trusted Interface Subsystem

- **TMR** Triple Modular Redundancy

- **TRM** Trusted Resource Manager

**TSS** Trusted Subsystem

**TTNoC** Time-Triggered Network-on-Chip

**TTSoC** Time-Triggered System-on-Chip

**URM** Untrusted Resource Manager

**VDSM** Very Deep Sub-Micron

**VMM** Virtual Machine Monitor

### List of Abbreviations

a.k.a. also known as

e.g. exempli gratia (for example)

i.e. id est (that is)

vs. versus (against)

w.r.t. with respect to

Ama, aitxa, arreba zein betiko lagunei urrin ta hurbil dien honei maitasunakin

The quotes at the beginning of each chapter are traditional Basque sayings, property of the Basque people for hundreds of years.

"Eroa da hasten düana ürrent ez dirokean lana", It is crazy the one who begins the work that cannot finish

## Chapter 1

## Introduction

The tremendous advances of the semiconductor technology enables more powerful chips with more transistors using less silicon area. Current chips can integrate more than one billion 28 nanometer transistors switching faster than 1 GHz. Multi-core chips offer an interesting abstraction that eases the understanding of such complex and highly integrated chips, by partitioning the chip in several cores. They also offer a way to overcome the performance limits of monolithic processors [Gel01] and they are shown to be more energy efficient [PPB<sup>+</sup>07]. Furthermore, the parallel computation of multi-core chips offers means to deal with concurrency.

These interesting features have already penetrated the embedded market with the name of Multi-Processor System-on-Chips (MPSoCs) where, depending on the application, the energy efficiency or dealing with concurrency are usually mandatory requirements. According to predictions, by the year 2015 the use of MPSoCs in multimedia (e.g., smart-phones [K.11]) and mixed-criticality [Ern10] embedded systems will share between 30% and 90% of the embedded market.

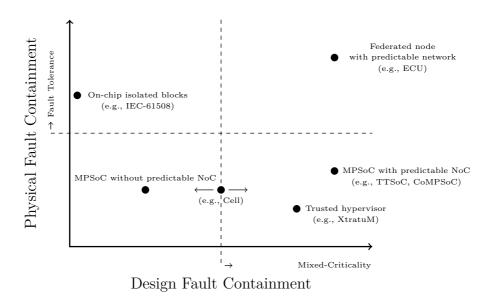

Focusing on mixed-criticality embedded systems, where the safety of the implemented functions and the reliability of the integrated chips play a crucial role, MPSoCs can also provide interesting features [KOESH07]. The integration of several functions of different application systems and criticalities has typically been done using a software approach where a monolithic processor was partitioned by hypervisors and other virtualization mechanisms. However, a hardware approach using MPSoCs provides intrinsic design fault containment by dedicated processors with some containment coverage for physical faults that cannot be achieved by software approaches. Due to the spatial separation of the hardware resources within the MPSoC, physical faults can damage some processing elements but not all of them in some degree or coverage.

### **1.1** Problem Statement

Highly integrated silicon technologies show increasing rates of transient physical fault due to process variations, shrinking geometries, and lower power voltages [Con02]. These physical faults require rigorous function isolation (e.g., specified by the IEC-61508 safety standard [IEC09]) if a reliability increase is obtained by the replication of on-chip components. This rigorous on-chip replication cannot be achieved on any software approach upon monolithic processors due to the resource sharing of the software replicas. In contrast, the computation blocks of an MPSoC can provide certain fault containment coverage to host the replicas. Anyway, even in an MPSoC hardware approach, independent chips are necessary if safety-critical reliability is pursued by the replication of components and those component should communicate using distributed networks.

The reliability of the critical infrastructure is another technical problem of hardware-based integrated architectures at the chip-level compared to distributed systems. The shared resources and core services of the MPSoC (the communication service, the clock, etc.) could lead to single points of failures within the chip because the rest of the on-chip components rely on them.

### 1.2 Proposed Solution

This dissertation introduces the Transient Tolerant Time-Triggered Systemon-Chip (4TSoC), an MPSoC based integrated architecture at the chip-level with system-level fault tolerance mechanism against soft-errors. These softerrors are spontaneous bit-flips in flip-flops and memory elements and they are considered the most common type of transient fault. The MPSoC approach provides superior physical fault-containment coverage compared to software approaches and fault tolerance is provided not only for the application subsystem, but also for the critical infrastructure (e.g., NoC and core services) of the architecture.

In contrast to other low-level approaches such as redundancy [Gai06] [Xil06], Error Correcting Codes (ECCs) [PKCC06] or circuit level hardening [MSZ<sup>+</sup>05], reliability increase for chip against transient fault can benefit from system-level management of an MPSoC based integrated architecture. This architecture offers fault containment features that enable the incorporation of system-level fault tolerance mechanism from distributed systems (component TMR, communication channel duplication, etc.) by analogy. System-level mechanisms enable a higher abstraction level, higher resilience against proximity faults and ease the chip development (e.g., ability to use standard libraries, reduce the complexity, early validation).

### **1.3** Contributions

The contribution or partial objectives of this dissertation consists of:

- The 4TSoC model: an MPSoC model with support for fault containment and fault masking based in a transient fault hypothesis for mixedcriticality systems, an extension of the TTSoC architecture. A synthesis model for such an MPSoC is also introduced inspired by the isolation requirements of the IEC-61508 standard.

- Fault tolerance mechanisms library for MPSoCs: an adaptation of fault tolerance mechanisms from distributed systems for on-chip multiprocessors, i.e., component TMR, network interface replication, the use of multiple NoCs and message-level ECCs.

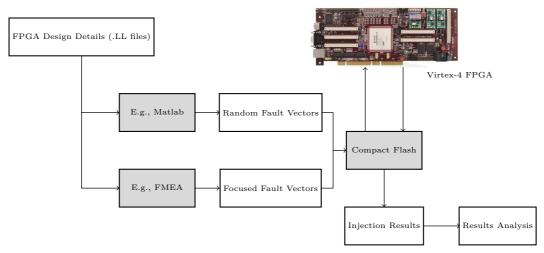

- The FI4SoC fault injection framework: an FPGA based fault injection framework for integrated architectures supporting transient fault emulation at RTL level using dynamic partial reconfiguration.

- Reliability Assessment of the TTSoC: an evaluation of the reliability of the TTSoC components (network interfaces, NoC, etc.) and the effectiveness of its fault containment and on-chip replication mechanisms.

- Comparison of fault tolerance mechanisms: a comparison of the previously introduced fault tolerance mechanisms using a specificic softerror (Single Event Transients, SETs) transient fault model.

### 1.4 Thesis Organization

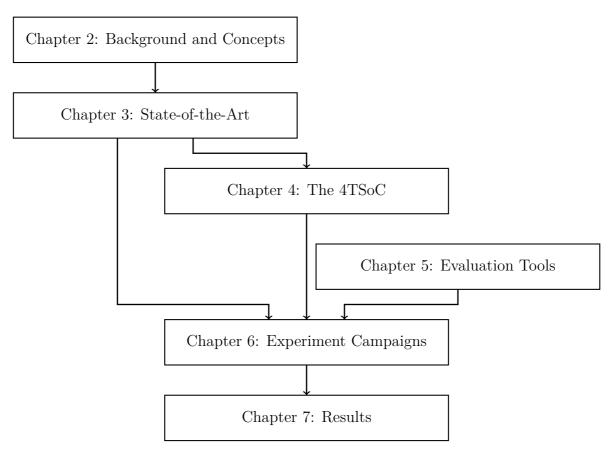

This thesis is organized as described below:

- Chapter 2 describes the background and basic concepts on which the work of this thesis is based. It follows three main paths: the notion of time, integrated architectures and dependability.

- Chapter 3 analyzes state-of-the-art of integrated architectures with respect to timeliness, design fault containment and physical fault handling.

The scope of the analysis covers the XtratuM hypervisor, the Cell multiprocessor, the CoMPoC MPSoC template and the TTSoC architecture. The on-chip replication recommended by the IEC-61508 standard is also studied. The reasons for the selection are described in the chapter.

- Chapter 4 introduces the 4TSoC architecture, an MPSoC model to increase the reliability of single chips against the transient faults within the fault hypothesis. It offers a fault containment model and a collection fault tolerance mechanisms.

- Chapter 5 describes the evaluation platform for the validation of the 4TSoC approach.

- Chapter 6 describes the experiments assessing the MPSoC approach for on-chip fault-containment, the TTSoC architecture and the new features of the 4TSoC model.

- Chapter 7 reviews the evaluation results and provides a comparative overview of the different integrated architecture approaches and fault tolerance mechanisms.

- Finally, Chapter 8 shows the conclusion and future work.

Figure 1.1: Thesis Organization

1.4 Thesis Organization

$1 \ Introduction$

"Zaldirik seguruena, nork bere zangoak", The safest horse, one's own legs

## Chapter 2

## **Background and Basic Concepts**

This chapter gives the background and the basic concepts on which this thesis is based.

#### 2.1 The Notion of Time

Incorporating the notion of time into embedded systems is a key requirement [Per11]. In fact, embedded systems are also known as *Cyber-Physical Systems* (CPSs) to emphasize this integration with time and physical environment. The notion of time generically used in embedded systems is the Newtonian physics concept of time, dismissing relativistic effects.

#### 2.1.1 Time Flow and Models

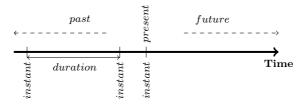

Figure 2.1: Time representation

The flow of time is represented as a straight line going from the past (on the left) to the future (on the right) as shown in Figure 2.1. A cut on this line is an instant and the present instant, now, decouples the past from the future. A relevant happening occurring on a particular instant is an event and the interval between two instants is named a duration [Kop06].

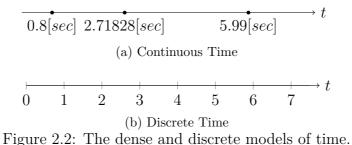

A suitable model for time in the real world is a continuous or dense time-line (Figure 2.2), whereas in digital systems a discretized model of time is used. In a dense model, time advances continuously with infinitesimal steps. A discrete model consists of time steps of a fixed duration adapting the dense model to the computational environment.

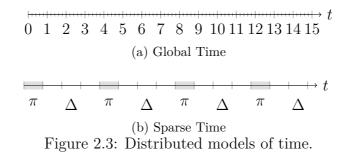

In distributed systems (Figure 2.3), a discrete global time (with a sparse time model) is established to provide a consistent temporal order of events based on

model) is established to provide a consistent temporal order of events based on their time-stamps. This global time is approximated by generating a macrotick clock using the local microtick clock of the distributed computers and a clock synchronization algorithm [Kop11]. Through this approach a maximal divergence of one tick is achieved among the local microtick clocks, which is known as the reasonableness condition.

A sparse time model [Kop07] restricts the occurrence of events (e.g., the sending of a message) that are in the sphere of control of the computer system to the activity intervals of a sparse-time base and the distributed parts share the same global time using a clock synchronization algorithm. Real-time is partitioned into a sequence of alternating intervals of activity of duration  $\pi$  and silence of duration  $\Delta$ . All the events that happen within the same activity interval are considered simultaneous.

The global time as well as the sparse time model can be applied at chip-level and distributed systems [KOESH07]. Focusing at chip level, the global time can be used to synchronize multiple clock domains and avoid undesired effects. These effects include:

- Clock skew: it is the maximum delay from the clock input of one flipflop to the clock input of another flip-flop. It is also knows as phase noise. The skew is mainly caused by the differences among clock sources and the clock distribution network.

- Clock jitter: it refers to differences between actual output position and the ideal output position of the clock edge. There are two contributions, fixed and random, to the total clock jitter. The fixed jitter has more timing offset and it is caused by specific sources such as crosstalk, signal noise, etc. The random jitter is derived from environmental factors (temperature, radiation, etc.).

The time margin for the synthesis of a chip is too narrow for future on-chip distributed systems with a single clock source at a negligible skew [BDM02], therefore, the chip must use several clock domains. In these cases, a global time is an option to overcome skew effects due to the technology constrains and to provide synchronization of multiple clocks within the reasonableness condition. This on-chip global time can be implemented using a slow clock line distributed along the chip or using clock synchronization algorithms analogously to classic off-chip distributed networks (e.g., TTP).

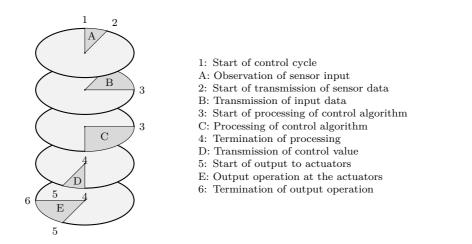

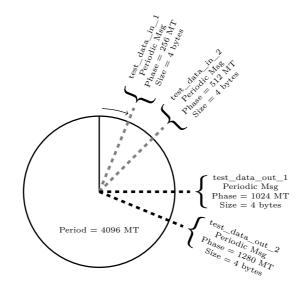

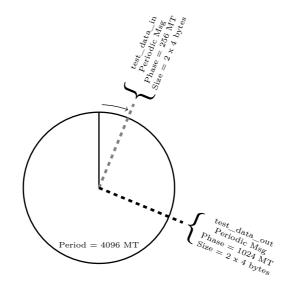

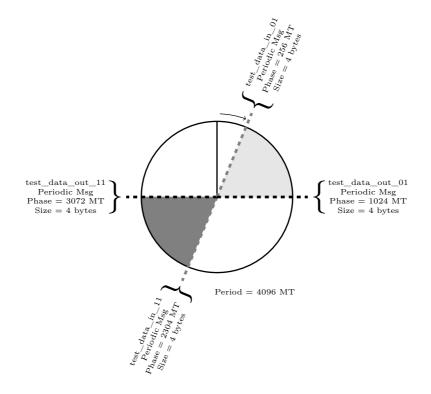

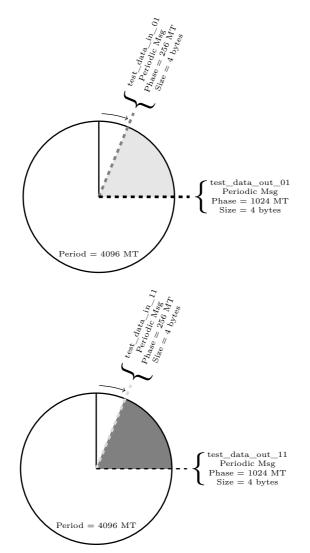

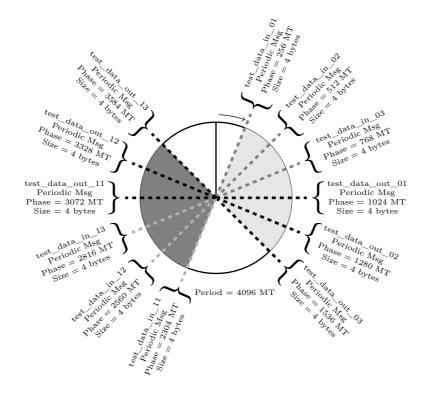

Despite the linear representation of time models, embedded control systems typically exhibit a cyclic temporal structure with a set of steps that are repeated each cycle (Figure 2.4) [OSHK08]. This cyclic description fits better the human cognitive nature of time [Win01]. The time-diagrams of this thesis prefer this circular representation.

Figure 2.4: Cyclic representation of an embedded control system process.

#### 2.1.2 State

Once a precise concept of time is introduced in a system a precise concept of state can be established. State decouples past from the future, in such a way that in a deterministic system, a future output can be determined by the future inputs and this system state [Mes89].

One can distinguish three types of system states, the initialization-state (i-state), the history-state (h-state) and the ground-state (g-state) [Kop11]:

- *i-state*: this is the state that can be loaded off-line, the static data structures (e.g., application program code, initialization data).

- *h-state*: it comprises the information required to start an "empty" composed function task at a given point in time. It is defined by the dynamic data structures at given instant that contain information about the current and past computations.

- *g-state*: it is the minimal h-state, when tasks are inactive and the channels are flushed. This g-state is ideally periodic.

A consistent notion of state is a prerequisite for fault masking through voting where the replicated subsystems must be replica determinate. This condition is only full-filled if each of the replicated nodes contains the same externally visible h-state at its ground state, and produces the same output messages at points in time at bounded time intervals [Pol95].

The instant when a system reaches the ground state is also called reintegration point. This minimal h-state is the optimal point in time for a subsystem to recover from a faulty-state by recreating it or copying [XR96] the g-state from a replicated node.

#### 2.1.3 Determinism

A given item (e.g, property, output) is deterministic if it is completely predictable and does not depend on randomness for a given set of conditions [Kop08b]. For instance, an output is deterministic for a given set of relevant conditions, if given the same set of initial conditions then the system always generates the same outputs at the same time when given the same inputs at the same time.

As time is part of the definition of determinism, it must be consistent (w.r.t. an external observer) at the system level of the design. For instance, in the case of a distributed embedded system the notion of time should be based on the sparse time.

#### 2.1.4 Behavior and Service

The behavior of a system can be defined as its activity (e.g., message sequence) during the progression of time. A system's service is the behavior according to the specification, whereas a failure is the opposite, a deviation of the system behavior from the specification.

# 2.2 Job, Partition and Component

In *Model Based Design* (MBD) the system services are first designed in a *Plat-form Independent Model* (PIM) and then mapped to a given platform using a *Platform Specific Model* (PSM). Job, partition and component concepts are introduced during this PIM to PSM refinement process.

#### 2.2.1 Job

A job is the basic unit of work [KOESH07] which provides a service to other jobs across the linking interfaces and to the environment via the local interfaces into a PIM. A distributed application consist on more than one *Distributed Application Subsystem* (DAS). A DAS is a nearly autonomous application system that performs a composite of services. For example, a train has up to dozens of DASes, such as, traction control, signaling, infotainment, etc. On its behalf, each DAS comprises several jobs, the unit of distribution. Therefore, a DAS is a composition of jobs and services.

#### 2.2.2 Partition

A partition is the physical execution environment for a job. Originally, the term partition referred to the allocation on time domain of a monolithic processor to multiple operating systems [Rus99], but in this dissertation it also refers to the spatial and physical decoupling of the execution environment. A partition can be a classical node (e.g., an ECU in the automotive domain), a virtual processor (e.g., in an hypervisor), a dedicated processor of a multi-core chip or a silicon fabric (e.g., an FPGA implementing a finite state-machine). The purpose of partitioning is fault containment: a failure in one partition must not propagate to cause failure in another partition. A partition should provide spatial and temporal partitioning with respect to other partitions [Rus99]:

• *Spatial Partitioning*: a partition ensures that the job in one partition cannot change the software or private data of another job, nor command the private devices of another partition.

• *Temporal Partitioning*: ensures that the service received from shared resources by a job in one partition cannot be affected by a job in another partition, including performance, rate, latency or jitter.

Partitioning is a prerequisite for the composability of jobs from different sources and criticalities.

#### 2.2.3 Component

The mapping of a job into a partition results in a component. These hardwaresoftware components, which are self contained subsystems, can be used as building blocks in the design of a larger system [KOESH07] [RE06] of a componentbased design. A large proportion of complex systems in nature evolve from the hierarchical composition of simple components [Sim62]. The building of complex embedded systems can benefit from the easier understanding of hierarchical component-based design.

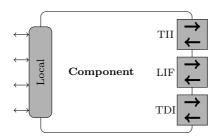

The definition of component interfaces is of utmost importance in order to avoid undesired interactions and facilitate the desired ones. Components interact using four basic types of interfaces (Figure 2.5) [OKP10]:

- *Local Interface* (LI): it establishes a connection between a component and its local environment.

- *Linking Interface* (LIF): the services of a component are offered to other components through this interface.

- *Technology-Independent Interface* (TII): this interface is used by the system to perform operations without the involvement of the application.

- *Technology-Dependant Interface* (TDI): it provides the means to look inside a component and to observe internal variables.

Figure 2.5: Interfaces of a component.

From the point of view of service provision, there are two types of components: system components and application components. System components provide an architectural service and they conform to the "style" of an architecture (the services and constraints that condition the implementation of a system). Application components implement the specified application functionality, the application service, and use the services of the available system components to reduce the effort required to implement the application functionality. Hence, an integrated architecture provides system components to integrate several application components that map jobs of multiple DASes on a single node.

# 2.3 Integrated Architectures

An architecture is a framework for the construction of systems for a chosen application domain that provides generic architectural services and imposes and architectural style for constraining an implementation in such a way that the ensuing system is understandable, maintainable, extensible, and can be built cost effectively [OK09]. The architectural style describes the principles, accepted statements about some fundamental insight in a domain, and structuring rules that characterize an architecture [Kop11].

An integrated architecture [OK09] provides multiple partitions for the mapping of jobs of different DASes into a single node. Whereas in federated architectures [KOPS04] each node provided a single partition for a single job, the high integration of transistors in semiconductors makes possible to integrate several jobs in a single chip. This integration enables the reduction of hardware and connection wires and the subsequent decrease of the amount of power used, weight, space and the number of computation chips. Several integrated architectures were created for specific application domains, for example: *Automotive Open System Architecture* (AUTOSAR) [GbR06], *Integrated Modular Avionics* (IMA) [ARI91] or *Network on Terminal Architecture* (NoTA) [KKOE07].

#### 2.3.1 Implementation

The implementation of an integrated architecture can be done following two main approaches: a software approach or a hardware approach. On the first approach, the communication services are implemented in software (e.g., hypervisor queues) offering virtual processors as partitions for the execution of jobs. In the second option, the communication is implemented in hardware (e.g., a *Network-on-Chip* (NoC)) and dedicated processors or silicon fabric (e.g., FPGA) are provided as a partition for each job.

#### Software Approach

Several software architectures address temporal and spatial partitioning on a monolithic processor approach, from which the most populars are microkernels [Lie95] and hypervisors [CRM<sup>+</sup>09]. Whereas hypervisors provide partitions for operating systems (e.g., jobs), microkernels perform a context switch per thread where the system software itself acts as an operating system. Hence, the microkernel approach is not the most suitable for the integration of distributed jobs (with potentially heterogenous operating systems), but for non-distributed homogeneous threads. In this section the scope of the software approach will be put on embedded hypervisors.

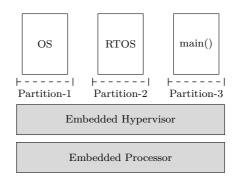

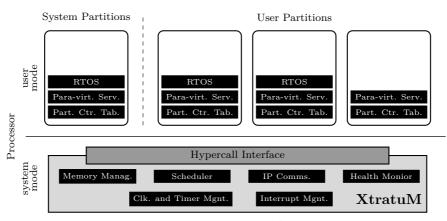

Hypervisors, also known as *Virtual Machine Monitors* (VMMs), are programs that run on hardware or a host *Operating System* (OS) using the highest privilege level, governing and separating multiple partitions (Figure 2.6). They enable the software implementation of jobs that can be assisted by a generalpurpose OS or a *Real-Time Operating System* (RTOS).

Figure 2.6: (Bare-metal) Embedded hypervisor architecture

Hypervisors are classified by the layer that executes them and the virtualization level. In the first category, type-1 hypervisors (also named bare-metal) run directly on the native hardware, whereas type-2 lay upon a host OS. The bare-metal approach reduces the virtualization overhead making it more efficient for embedded systems. Anyway, this approach can require specific hardware features of the processor, such as: additional privileged modes for each partition, direct interrupts or extended page table for the memories of each partition [Neu06]. In the second category, full-virtualized and para-virtualized architectures are distinguished. Full-virtualization offers a virtual image of all the resources and therefore support any kind of program or OS in the partitions. Para-virtualization replaces the critical or conflicting instructions that may break the isolation by hypervisor services or hypercalls. It minimizes hypervisor overhead, but it requires customization of the guest program or OS in order to support those hypercalls. The source code of the OS is frequently available in embedded system and, as it requires less overhead, the para-virtualized approach is often preferred.

The implementation of partitioning in hypervisors requires the following features: (1) spatial partitioning, achieved by a hardware mediation (e.g., a *Memory Management Unit* (MMU)) that prevents any job to write in the memory locations of other jobs or the hypervisor.(2) A fixed cyclic scheduling of the partitions, providing temporal partitioning for the integrated jobs.

#### Hardware Approach

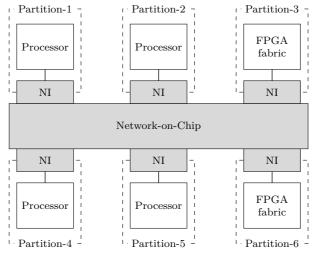

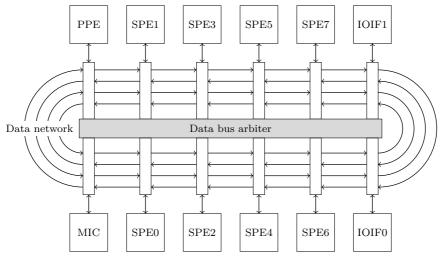

The hardware approach aims at providing dedicated cores of a *Multi-Processor* System-on-Chip (MPSoC) as partitions for jobs. MPSoC architectures differ at the way the on-chip cores communicate among themselves, e.g., shared memories (e.g., caches [CS99], FIFOs [NTS<sup>+</sup>08]), buses, or through NoCs [HGBH09] [OSHK08]. The explicit timing of message based communication is preferred in order to enhance temporal partitioning for integrated architectures (e.g., using a deterministic schedule). Among message based communication options, NoCs scale better than buses when the number of cores increases [BDM02].

A NoC based integrated architecture approach provides message-based services to a set of hardware partitions (Figure 2.7) that constitute the MPSoC. These hardware partitions permit the heterogeneous (software or hardware) implementation of jobs. The software implementation of a job executes upon a dedicated core that can be assisted by an OS. The hardware implementation of a job upon a silicon fabric (e.g., FPGA) is also called an *Intellectual Property* (IP) core. Anyway, this term is controversial because many of these cores are not claimed for intelectual property and they are publicly available (e.g., opencores.org). This dissertation uses the term *core* to refer to the hardware implementation of jobs.

First of all, the NoC and *Network Interfaces* (NIs) are responsible for the information exchange among components, but also for the spatial and temporal partitioning of the chip. Spatial partitioning is ensured by limiting the interaction of components to the exchange of messages. The NIs of each partition (e.g., a time-triggered NoC) can contain the predefined points in time that each job can transmits messages and this information can not modified by the job. Hence, the temporal behavior of a job cannot be interfered (e.g, message collision) by other jobs.

#### Mixed Approach

There are multiple solutions using a software partitioning approach (e.g., hypervisor) upon a multi-core chip [RTS10]. Anyway, these works do not con-

Figure 2.7: A NoC based MPSoC

sider both, the hardware and the software, in a single architectural style. The hardware is a predefined multiple-purpose multi-processor chip and the partitioning software must adapt to those limited resources that do not match all the requirements (e.g., memory independence) and constraints (e.g., physical fault containment coverage) of the integrated architecture style. Moreover, this mixed approach often address data-server applications more than embedded systems.

There are new projects such as the European FP-7 MULTI-PARTES project [Mul11] targeting a mixed integrated architecture approach addressing embedded systems and their use in safety-related applications.

#### 2.3.2 Technologies

Integrated architectures are synthesized into a final end-device technology. Both the single processor behind the software approach and the MPSoC for the hardware approach can be implemented using ASIC or FPGA technology.

#### Application Specific Integrated Circuit (ASIC)

Application Specific Integrated Circuit (ASIC) devices are integrated circuits for a particular application that consist of a large number of primitive logic elements (e.g., NAND, NOR, AND), Flip Flops and interconnections. Current shrinking technology allows the integration of over 100 million gates on a single chip. Nowadays, it is also possible to mix analog primitives in digital ASIC fabric. Moreover, ASICs offer different levels of customization, like standard cell, structured, full custom, etc. ASIC technologies are usually programmed using photo-lithographic masks which are too expensive (e.g., 1 billion dollars) to produce for low production volumes. Nevertheless, the largest number of embedded systems make use of generic processors chips built in this technology because they are produced in large volumes that make this approach economically profitable.

#### Field Programmable Gate Array (FPGA)

An FPGA is a device that can be reconfigured after manufacturing by storing a circuit diagram synthesized from a hardware description language (HDL) into its configuration memory. It is considered an alternative to ASICs for smaller design and lower production volumes. The configuration memory holds the setup of the FPGA configurable structures after a synthesis, placement and routing process.

Logic is implemented using Look Up Tables (LUTs) which store truth tables in the configuration memory. Sequential functions are implemented thanks to flip-flops and routing is performed using switching matrix structures and multiplexers. The LUTs, flip-flops and routing elements compose the programmable elements or Configurable Logic Blocks (CLBs). Custom clock frequencies and noise reduction are obtained with Digital Clock Managers (DCMs) and PLLs. The resulting clock signals are distributed by dedicated clock nets. Memories, buffers and registers can be implemented using the aforementioned LUT or flip-flop structures or with dedicated embedded block memories (e.g., Block RAMs). New application oriented FPGAs include DSP blocks or even silicon implemented processors (hard cores).

FPGAs can be classified by the memory technology used to store the circuit information: antifuze, flash (e.g., EPROM, EEPROM) and Static-RAM (SRAM) FPGAs.

- Antifuze FPGAs: the antifuze technology is based in the following principle: in the open stage there is an insulator between two hardly doped semiconductors (Figure 2.8b) and the close stage is obtained by applying an important voltage (e.g., 16V) which causes the break of the insulator and makes the antifuze conducting (Figure 2.8a). This technology is programmable only once.

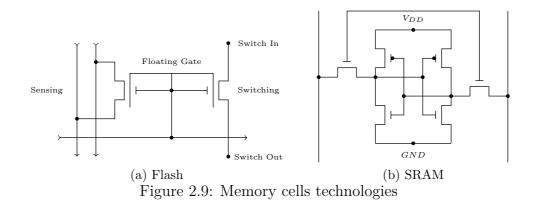

- *Flash FPGAs*: the flash FPGA configuration memory is based on a non volatile memory where two MOS transistors are used per bit cell (Figure 2.9a), similarly to other EPROM/EEPROM memories. It is the cheapest technology as it only uses two transistors per bit cell.

(a) Programmed (b) Unprogrammed Figure 2.8: Actel antifuze technology cross section

• SRAM FPGAs: Nowadays, most of scommercial FPGAs are manufactured in SRAM technology. It is based on the well know six transistor (6T) SRAM technology (Figure 2.9b). It provides the highest integration capacity (e.g., 45nm) compare with previous technologies and it is the most extended technology.

# 2.4 Dependability Concepts

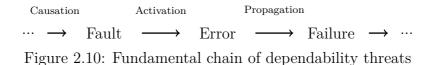

A fault is the first link of the fundamental chain of dependability threats (Figure 2.10) [ALR01]. A fault is defined as the hypothesized cause of an error, which consists on an incorrect state. Subsequently, an error can cause a failure, a deviation not only of the state but of the actual behavior with respect to the service specification.

The notion of dependability covers several meta-functional attributes of a computer system that relate to the quality of service (e.g., occurrence of failures) a system delivers to its users during an interval of time [Kop11] [ALR01]. From those attributes we explain three that will be extensively used in this dissertation:

• Availability: it is a measure of the delivery of correct service with respect to the alternation of correct (*Mean Time To Failure* (MTTF)) and incorrect service (*Mean Time To Recover* (MTTR)). It is measured by the fraction of time that the system is ready to provide the service (Equation 2.1).

$$Availability = \frac{MTTF}{MTTF + MTTR}$$

(2.1)

• Reliability: the Reliability R(t) of a system is the probability that a system will provide the specified service until time t, given that the system was operational at the beginning, i.e.,  $t = t_0$ . When the failure rate  $(\lambda)$  of a system has an exponential distribution reliability at any mission time follows Equation 2.2. This reliability can be modeled within several configurations using mathematics [DS01a]. The standard measure for reliability is the *Failure in Time* (FIT) which provides the expected failures that a hardware component will suffer during  $10^9$  hours of operation (about 115000 years).

$$R(t) = e^{-\lambda t} \tag{2.2}$$

• Safety: it is the reliability regarding critical failure modes. In case of a detection of a fail safe system, it is possible to perform some corrective action, or to bring the system to a safe state, where the outputs of the local interfaces are set to a non dangerous value (e.g., the barriers are set down in a level crossing of a train).

#### 2.4.1 Physical Faults in Semiconductors

There are several works on the taxonomy of faults [ALRL04] [ALR01]. In the scope of the physical faults experienced by integrated semiconductor devices, faults are basically classified as permanent or transient based on their persistence in the system [Con02].

Physical permanent faults are originated by underlying hardware irreversible damages [MSK<sup>+</sup>08] [GAM<sup>+</sup>02] (development imperfections, wear-out, etc.). For instance, cosmic rays can also cause permanent faults in few cases, i.e., with high ionizing doses, but they will be treated later as transient fault causes

due to the higher probability. The dependability means of the last decades have addressed permanent faults, but during the last years the research attention have switched to transient faults. Whereas permanent fault rates remain stable with technological improvements, the increasing sensitivity to voltage, frequency and energy variations due to transistor shrinking has resulted in higher transient fault rates [Con02]. Besides the well known *Electromagnetic* Interferences (EMIs) that remain in the system for limited periods (e.g., a maximal duration of 50 ms was tolerated in automotive applications [HT98]) and then disappear, new transient faults in the form of Single Event Effects (SEEs) have emerged.

These SEEs are spontaneous events of electronic systems caused when energized particles (cosmic neutrons, alpha particles, etc.) collide with integrated devices. Contrary to the aforementioned permanent faults and EMIs, SEEs do not affect nodes or integrated chips as a whole. The cross section of a single event is about hundreds of micrometers [CMFC<sup>+</sup>98] which is just a small fraction of current integrated chips that have silicon fabrics of some dozens of millimeters.

SEEs are classified based on the induced effect and severity as listed below:

- Single Event Upset (SEU): a bit-flip induced in a memory cell by a single energetic particle.

- Multiple Bit Upset (MBU): an event induced by a single energetic particle that causes multiple upsets (SEUs) during its passage through an electronic device. They are also called MCU (Multiple Cell Upset) when affecting bits of different memory words.

- Single Event Transient (SET): one or more voltage pulses (e.g., glitches) caused by a single event which propagate through the circuit.

The associated fault rate is expected to grow according to the International Technology Road-map for Semiconductors (ITRS) shown in Table 2.1. It must be also considered that the particle flux causing SEEs increases with altitude and is not equal at different longitudes and latitudes of the world.

| Table 2.1: ITRS prediction for soft errors and MBUs |      |      |      |      |  |  |

|-----------------------------------------------------|------|------|------|------|--|--|

|                                                     | 2010 | 2013 | 2016 | 2019 |  |  |

| Soft Error Rate (FIT/Mb)                            | 1200 | 1250 | 1300 | 1350 |  |  |

| Percentage of MBU                                   | 32%  | 64%  | 100% | 100% |  |  |

TUDO 0.1

#### 2.4.2 Fault Containment Regions (FCRs)

A Fault Containment Region (FCR) is a set of subsystems that share one or more common resources that one single fault may affect [Kop11]. To form a fault containment boundary around a collection of hardware elements, one must provide independent power and clock sources and additionally electrical isolation and spatial separation [LH94]. These requirements make it impractical to provide more than one FCR within a single semiconductor chip at a safetycritical rigor (at a probability of failure of  $10^{-9}$  failures per hours).

If one distinguishes design and physical faults [Obe08], integrated architectures can provide FCRs for design faults. The spatial and temporal partitioning techniques [Rus99] for the components of an integrated architecture can provide design fault containment. For physical faults, the hardware approach can provide certain containment coverage by providing spatial separation of the partitions and multiple clock domains and pin-out (e.g., grounding) on the chip layout (e.g., for SEEs [CMFC<sup>+</sup>98]). These on-chip FCRs for physical faults work only at single chip failure probabilities (e.g., around  $10^{-5}$  to  $10^{-6}$  failures per hours [PMH98]).

Physical fault containment and design fault containment are orthogonal properties. Physical fault containment does not assure design fault containment and vice-versa. For instance, one may use two separated chip processors (two FCRs for physical faults) to implement a function but both can fail simultaneously due to a single design fault on the software. In the same way, a hypervisor can assure design fault containment for two independent operating systems within the same chip and a single physical fault can make both fail.

#### 2.4.3 Fault Tolerance

Fault tolerance is a mechanism to deliver a correct service despite the occurrence of faults [Kop11]. The masking of a fault in order to hide it from the application, is always based on redundancy. One can distinguish temporal, information and hardware redundancies.

- *Temporal Redundancy*: it involves the repetition (rollback) of instructions, segments of jobs or entire jobs. The re-execution of these pieces of software must consider the duration of the fault and the handling of the state. For instance, temporal redundancy is not valid for permanent faults or transient faults of longer duration than the execution time.

- Information Redundancy: digital systems process, transmit and store data in the form of groups of bits and to avoid that any of these bits could

flip due to physical factors during processing, transmission or storage. Detection (*Error Detection Code* (EDC)) or correction (*Error Correcting Codes* (ECC)) codes are appended to the original binary bits by encoding part of the original information in order to detect or recover from those bit-flips.

• Hardware Redundancy: It is based on the replication of blocks (e.g., a component). These blocks perform the same job and faults can be detected (two replicas) or even tolerated (three or more replicas) by comparing the outputs of the replicas. Each of the replicated components must be an FCR in order to avoid common cause failures that would undermine the reliability increase, and they must be replica determinate to support exact voting [Pol95]. Triple Modular Redundancy (TMR) is one of the most used hardware redundancy mechanism where faults are masked based on a majority voting. The duplication of components is also an option when the replicated components show fail-silent behavior [Kop11].

#### 2.4.4 Fault Injection

Fault injection can be defined as the artificial insertion of faults for the acceleration of their occurrence (normally) at the development phase of a system [Kop11]. This deliberate insertion of upsets (fault or errors) in computer systems is used for the evaluation of its behavior in the presence of faults or the validation of specific fault tolerance mechanisms [Ade03].

Injection techniques are classified by the mechanism used to insert the fault into hardware, software or simulator based fault injection.

- *Hardware Implemented Fault Injection* (HWIFI): is performed in a hardware model of the system (e.g., an early prototype of the final product) by inserting different physical perturbations, such as, electro-magnetic, thermal or radiation. One can identify two HWIFI categories: with contact (e.g., pin-level injection) and without contact (e.g., radiation beams).

- Software Implemented Fault Injection (SWIFI): it consists of reproducing at software level the errors that would have been produced upon faults occurring in the hardware or the software.

- Simulator Based Fault Injection: it allows to experimentally evaluate the dependability by using a model of the system before its final conception (e.g., design phase). Usually, this type of faults are performed by CAD tools at different abstraction layers (electrical level, gate level, RTL level, etc.) and using *Field Programmable Gate Array* (FPGA) emulation.

When emulating faults using FPGAs, two abstraction levels can be distinguished: (1) gate level (also called physical) and (2) *Register Transfer Level* (RTL) (also called logical).

- At gate level: the fault injection emulates a technology-dependent fault model. For instance, authors of [ACD<sup>+</sup>07][SATGM08] directly inject bit-flips (SEUs) at any position of the FPGA configuration memory. The results of such an injection campaign are only valid for a concrete FPGA technology, but an accurate measurement of the actual reliability is performed. One can correlate the SEU sensitivity of a specific FPGA technology (e.g., from vendor reliability data [Xil11]) with the fault injection results and give an approximate reliability in FIT of the tested FPGA design.

- At RTL level: one can raise the abstraction to a level where the end technology is still unknown. At this level, the previous configuration memory bit-flip fault model is not directly applicable. Therefore, one injects faults specifically in those flip-flops and registers of the FPGA that are also defined at the RTL level. Physical faults affecting other elements (e.g., configuration memory) are modeled indirectly through the failure rates and failure modes at the RTL level. For example, similarly to bit-flips in the configuration memory of an FPGA, transient pulses (e.g., SETs [ATM<sup>+</sup>07]) on the combinatory hardware of a VLSI chip can provoke register level changes (e.g., bit flips in registers or memory elements). One injects only those logical faults (i.e., bit-flip on actual RTL registers and memories) in the FPGA design. Although, the probability of a SET or a SEU to leak to RTL is unknown, one can compare fault tolerance mechanisms and give relative figures about which of them accomplishes its function better. In addition, the fault injection can already be performed earlier in the development process, because RTL models are available at an earlier development stage.

Fault injection at RTL using FPGAs has been mainly implemented using the simulation of modified HDL code. For instance, one can find fault simulation tools for system models designed in Verilog at RTL level addressing permanent (e.g., stuck-at) faults [MG96] or in VHDL addressing wider fault models (e.g., transient faults) [BGB<sup>+</sup>08]. Other approaches, like FT-UNSHADES [ATM<sup>+</sup>07], use other fault injection technologies, such as partial reconfiguration on Xilinx Virtex II FPGA technology to inject bit-flips in flip-flops and latches to emulate the effects of SETs at RTL level. The use of actual FPGAs for the emulation of faults significantly accelerates the injection compared to the use of simulation platforms. However, the above fault injection frameworks do not

target MPSoCs or integrated architectures. Aside from fault injection at RTL, there is only few work addressing NoCs, i.e., with a focus on on-chip routers and switches [FCCK06]. Other approaches include an additional wrapper to stimulate the IPs of the DUT at a higher abstraction level (i.e., the IEEE-1500 standard [IEE05]).

# 2.5 Cognitive Complexity

Integrated architectures must deal with the current complexity of embedded systems. Such architectures should not penalize the human comprehension, on the contrary, they should use representations and techniques fitting the human cognition and ease the work of integrated system engineers. In previous works, authors have identified three main simplification strategies tackling with this cognitive complexity that can be applied to embedded system architectures [Kop08b] [Per11]: