Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

#### DIPLOMARBEIT

## Data Acquisition Software for a Silicon Strip Detector Readout System

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Diplom-Ingenieurs

> unter der Leitung von Ao.Univ.-Prof. Dipl.-Ing. Dr.techn. Karl Riedling Institut für Sensor- und Aktuatorsysteme

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

> von Thomas-Benjamin Obermayer, BSc Gusenleithnergasse 5/1/11 1140 Wien

Wien, im November 2012

#### IN ERINNERUNG AN MEINEN GROSSVATER, DER MIR BEIBRACHTE, WIE MAN DEN COMMODORE 128 PROGRAMMIERT.

In memory of my grandfather: For teaching me how to program the Commodore 128.

## Kurzfassung

In der Hochenergiephysik werden zur Reproduktion von Teilchen-Trajektorien Siliziumstreifendetektoren eingesetzt. Zur Erfassung entsprechender Detektordaten werden speziell dafür vorgesehene Readout-Chips und Auslesesysteme verwendet.

Das Institut für Hochenergiephysik der Österreichischen Akademie der Wissenschaften (HEPHY) hat einen Prototyp für das Auslesesystem des Belle II Silicon Vertex Detectors vorgestellt, welches Readout-Chips des Typs APV25 initialisiert, steuert und ausliest. Dieses Auslesesystem wird im Rahmen des Belle II Experiments im japanischen Forschungszentrum für Hochenergiephysik (KEK) zum Einsatz kommen. In Ergänzung zum genannten Prototyp wurde eine Windows-Applikation zur Datenerfassung mittels Personal Computer entwickelt. Mängel im Software-Design und in der Dokumentation verursachten Probleme bei der Wartung und Weiterentwicklung dieses Programms.

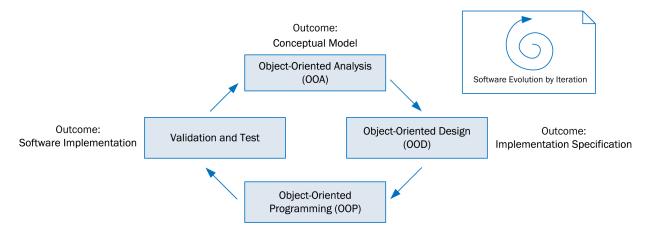

Diese Arbeit beschreibt den Entwicklungsprozess, das daraus resultierende Design und die Implementierung einer neuen, auf Linux basierenden Applikation zur Erfassung von Daten mit dem genannten Auslesesystem. Eine Anforderungsspezifikation, welche vor der Softwareentwicklung erstellt wurde, wird präsentiert. Ferner werden eine reproduzierbare Vorgehensweise für die objektorientierte Analyse (OOA) und die Einhaltung allgemein anerkannter Grundsätze im objektorientierten Design (OOD) beschrieben. Es wird gezeigt, dass etablierte Entwurfsmuster und Softwareentwicklungstechniken mit dem Ziel verfolgt wurden, ein wartbares C++ Programm zu erstellen, welches einfach zu lesen und testen ist und entsprechend neuer Anforderungen angepasst werden kann. Außerdem beschreibt die Arbeit, wie ein wiederverwendbares Framework aus Softwarekomponenten für das Belle II Experiment erstellt wurde. Die Struktur und das Verhalten der Software werden mit einer geeigneten Teilmenge der Unified Modeling Language (UML) beschrieben.

In ihrer Gesamtheit stellt diese Arbeit einen Ansatz vor, wie etablierte Softwareentwicklungstechniken eingesetzt werden können, um einen vernünftigen Kompromiss zwischen zeitlichem und technischem Aufwand auf der einen Seite und Softwarequalität auf der anderen Seite zu erreichen.

## Abstract

It the area of high energy physics, Silicon Strip Detectors (SSDs) are used to reproduce the trajectories of particles traversing a particle detector. The readout of SSDs is accomplished by dedicated readout chips and readout systems intended for Data Acquisition (DAQ).

The Institute of High Energy Physics of the Austrian Academy of Sciences (HEPHY) developed a prototype of the Belle II Silicon Vertex Detector readout system, designed for initialising, controlling and reading out front-end chips of the APV25 type. It will be used for the Belle II Experiment conducted at the KEK research laboratory in Japan. An appropriate Windows-based DAQ software application supporting this prototype was also developed at HEPHY.

However, shortcomings in the design and documentation of this DAQ application caused issues in maintenance and further development.

This thesis describes the development process, the resulting design and the implementation of a new, Linuxbased, DAQ application supporting the prototype readout system mentioned above. The thesis also presents a requirements specification, which was finalised ahead of further software development. Furthermore, a reproducible strategy for Object-Oriented Analysis (OOA) and the compliance with generally accepted principles of Object-Oriented Design (OOD) are described. It is shown how established design patterns and software engineering techniques were followed with the aim to create a maintainable C++ program that is easy to read, test and debug, and can be adapted to changing requirements. In addition to this, the extraction of a stable, state-of-the-art framework of components reusable for the Belle II Experiment is illustrated. An appropriate subset of the Unified Modeling Language (UML) is used to describe software structure and behaviour in brief.

As a whole, this thesis presents an approach as to how established software engineering techniques can be utilised to reach a reasonable tradeoff between temporal and technical development effort on the one hand and software quality on the other hand.

## Danksagungen

Meine Danksagungen gelten zunächst Herrn Prof. Dr. Karl Riedling, unter dessen engagierter wissenschaftlicher Betreuung diese Arbeit geschrieben wurde. Für ein lehrreiches Jahr danke ich Herrn Dr. Markus Friedl und Herrn Dipl.-Ing. Christian Irmler vom Institut für Hochenergiephysik der Österreichischen Akademie der Wissenschaften. Meinen KollegInnen Annekathrin, Maria, Helmut, Immanuel und Paul danke ich für die gute gemeinsame Zeit während meiner Tätigkeit an diesem Institut. Verpflichtet bin ich Frau MMag. Veronica Peintinger, die in einer für sie bewegten Zeit den Text in mühevoller Arbeit gelesen, korrigiert und damit maßgeblich aufgewertet hat.

Meinen aufrichtigen Dank spreche ich meinen Eltern aus, die mir einen Zugang zu Wissenschaft und Technik ermöglicht und mich während meiner gesamten Studienzeit vertrauensvoll unterstützt haben. Meiner Freundin Marion möchte ich für die mir gegenüber aufgebrachte Geduld danken, aber auch für die liebevolle Unterstützung während der Erstellung dieser Arbeit. Andreas, Gabriela und Mario Marschall bin ich für ihre freundschaftliche Hilfestellung verbunden. Schließlich möchte ich Herrn Mag. Günter Wildmann für zahlreiche Anregungen und Diskussionen danken, welche meine Vorgehensweise nachhaltig bereichert haben.

## Contents

| K | urz                   | fassung                           | iv          |  |  |

|---|-----------------------|-----------------------------------|-------------|--|--|

| A | Abstract              |                                   |             |  |  |

| D | ank                   | sagungen                          | vi          |  |  |

| 1 | Int                   | roduction                         | 1           |  |  |

|   | 1.1<br>1.2<br>1.3     | Issues Addressed in This Thesis   | 2<br>2<br>2 |  |  |

| 2 | Th                    | e Belle II SVD Readout System     | 3           |  |  |

|   | 2.1<br>2.2            | The Hardware Setup                | 4<br>13     |  |  |

| 3 | Software Requirements |                                   | 19          |  |  |

|   | 3.1                   | Purpose                           | 20          |  |  |

|   | 3.2                   | Scope                             | 20          |  |  |

|   | 3.3                   | Requirements Format and Numbering | 21          |  |  |

|   | 3.4<br>2.5            | User Requirements Definition      | 21          |  |  |

|   | 3.5                   | System Requirements Specification | - 30        |  |  |

| v | l | l | l |

|---|---|---|---|

|   |   |   |   |

| 4 | Software Development Methodology                  | 31 |

|---|---------------------------------------------------|----|

|   | 4.1 Object-Oriented Analysis                      | 33 |

|   | 4.2 Object-Oriented Design                        | 35 |

|   | 4.3 Object-Oriented Programming                   | 41 |

| 5 | Software Design and Implementation                | 45 |

|   | 5.1 Documentation                                 | 46 |

|   | 5.2 Reuse-Oriented Architecture                   | 46 |

|   | 5.3 Third Party Standard Components               | 46 |

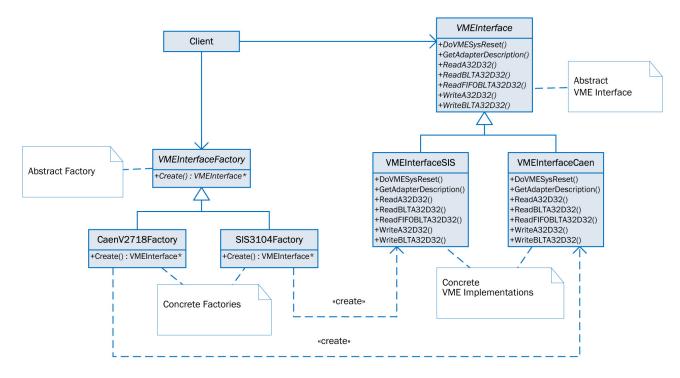

|   | 5.4 VME Interface Abstraction                     | 49 |

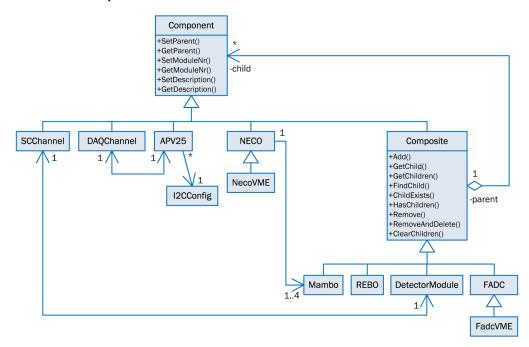

|   | 5.5 Readout System Abstraction                    | 53 |

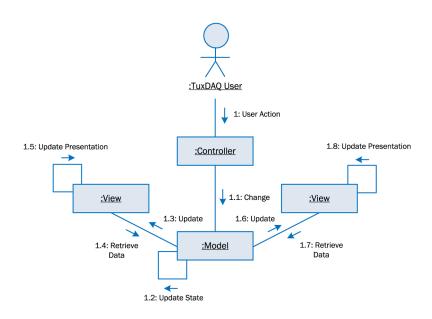

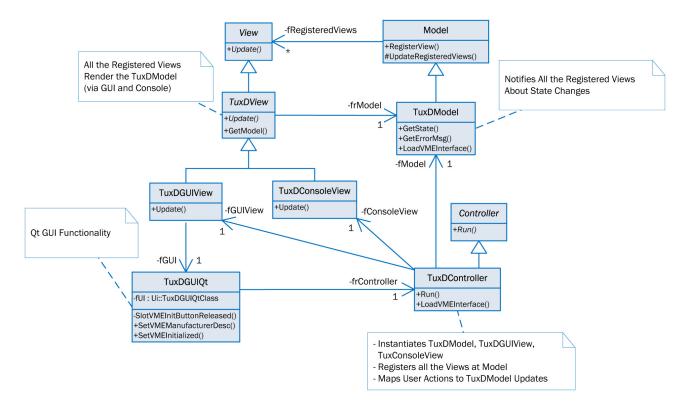

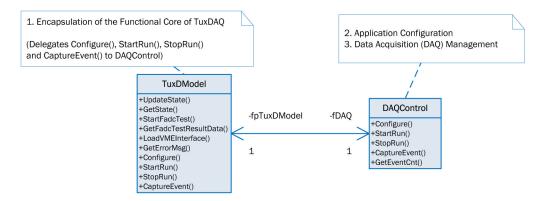

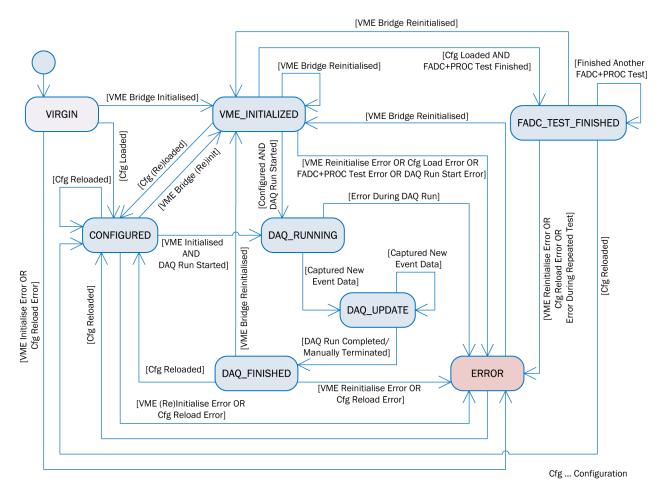

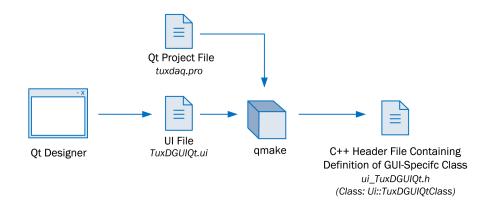

|   | 5.6 Model-View-Controller                         | 56 |

|   | 5.7 Interaction between TuxDAQ and TuxOA          | 64 |

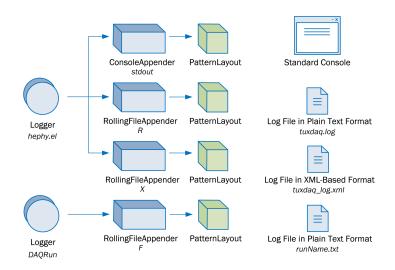

|   | 5.8 Logging                                       | 65 |

| 6 | Application Overview for Users                    | 69 |

|   | 6.1 Starting TuxDAQ                               | 69 |

|   | 6.2 Different Graphical User Interface (GUI) Tabs | 70 |

|   | 6.3 Performing a DAQ Run                          | 71 |

|   | 6.4 VME Bridge Initialisation                     | 73 |

|   | 6.5 FADC+PROC Test                                | 73 |

|   | 6.6 Error Treatment                               |    |

|   | 6.7 The Configuration File                        |    |

|   | 6.8 Data Output Files                             | 74 |

| 7 | ' Software Environment                            | 75 |

|   | 7.1 Operating Systems and VME Libraries           |    |

|   | 7.2 Development Tools                             |    |

|   | 7.3 Prerequisites for TuxDAQ Operation            | 76 |

| 8 | 3 Conclusion                                      | 77 |

| A | A Traceability                                    | 79 |

|   | A.1 Source Traceability                           | 79 |

| <ul><li>A.2 Requirements Traceability</li></ul> |    |

|-------------------------------------------------|----|

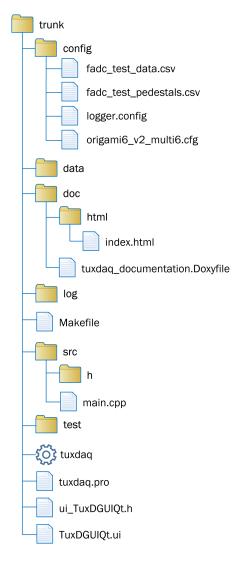

| B The TuxDAQ Repository                         | 87 |

| Acronyms                                        | 89 |

| Bibliography                                    | 91 |

ix

# Introduction

In recent years, a lot of research in the field of high energy physics has focused on readout systems for Silicon Strip Detectors (SSDs) and associated Data Acquisition (DAQ) software. SSDs are used to reproduce the trajectories of particles traversing a particle detector. In the related research area, DAQ systems are products and processes used to collect data produced by a sizeable number of front-end chips. These are attached to the SSDs. Data acquired in this way is stored and provides a basis for further analysis of physical phenomena.

In regards to these systems, the Institute of High Energy Physics of the Austrian Academy of Sciences (HEPHY) has made noteworthy contributions to the Belle Experiment<sup>1</sup> [2] as well as to the proposed follow-up experiment Belle II [3] at the KEK Research Laboratory<sup>2</sup> in Japan.

In 2009, Friedl et al. presented an early prototype readout system for the future Belle II Silicon Vertex Detector (SVD) [4]. This system provides appropriate hardware components for initialising, controlling and reading out front-end chips of type APV25 [5].

Supporting this prototype, a DAQ software application was developed. It was designed to set up all components involved on basis of a configuration file to control the readout system properly, to acquire respective data, to run a limited online analysis<sup>3</sup> on this data and to store it for further offline analysis.

Based on National Instruments (NI) LabWindows/CVI, the program is a proprietary solution. It is tied to Microsoft Windows operating systems. Moreover, its 'monolithic' software architecture, which has gradually grown, and the implementation in ANSI C<sup>4</sup> show suboptimal levels of maintainability and portability<sup>5</sup>.

Hardware and software have proven successful during experimental research at HEPHY, CERN and at other research facilities [3]. Nevertheless, the aforementioned facts and shortcomings in documentation make the present DAQ program an impractical option for both long-term usage in a developing experimental environment and for reuse in the Belle II Experiment.

<sup>&</sup>lt;sup>1</sup>The Belle Experiment was explicitly honoured in the statement of the Nobel Prize in Physics 2008 for the experimental verification of the CP violation theory [1].

<sup>&</sup>lt;sup>2</sup>High Energy Accelerator Research Organisation, Tsukuba

<sup>&</sup>lt;sup>3</sup>The term 'online' is to be understood as 'during operation' in this context.

<sup>&</sup>lt;sup>4</sup>Defined by ANSI X3.159-1989, also referred to as C89

<sup>&</sup>lt;sup>5</sup>Quality measures as defined in ISO/IEC 9126-1

#### 1.1 Issues Addressed in This Thesis

This thesis describes the development process, the resulting design and the implementation of a new DAQ application for the prototype Belle II SVD readout system.

The new program will be based on the existing solution as far as function is concerned. Nevertheless, an elaborated object-oriented architecture as well as the usage of field-proven principles and patterns will improve the quality measures mentioned above. With  $C++^6$ , a widely spread state-of-the-art programming language will be used for implementation. The application will be based on Linux - currently the favoured operating system in the scientific field at hand. Furthermore, the new system will support VME interface adapters by different manufacturers. The online analysis of acquired data will be extracted to a separate program. This will improve runtime flexibility and DAQ performance. Enhanced software modularity and a comprehensive documentation will allow for the reuse of components for the Belle II Experiment and for other projects in the area of high energy physics research. Porting the program to different operating systems in future will be easier, and design changes in the hardware will cause fewer software modifications than before.

In this thesis I am presenting an approach to how established software engineering techniques can be utilised to an extent that builds a reasonable tradeoff between development effort (temporal and technical) and software quality. An appropriate subset of the Unified Modeling Language (UML)<sup>7</sup> is used to describe the software structure and behaviour.

#### 1.2 Overview

In Chapter 2, the proposed Belle II readout system is described from a software developer's perspective. The requirements for the new DAQ application can be found in Chapter 3. A description of the software development methodology in Chapter 4 is followed by a detailed overview of the software design and implementation in Chapter 5. An application overview for users is presented in Chapter 6. Chapter 7 describes the software environment of the new DAQ program. Finally, Chapter 8 provides a comprehensive summary and describes what future work should include.

#### 1.3 Typographic Conventions

Text in *italic face* represents a term that is defined within this thesis. Subsequent instances of such a term are not in italic face. **Bold face** letters emphasise respective content and serve to improve readability.

Binary numbers are tagged with a subscript 'b', e.g.  $11110101_b$ . In contrast, hexadecimal numbers are tagged with a subscript 'h', e.g.  $F5_h$ . Numbers without any subscript are decimals, e.g. 245.

All-numeric calendar dates have the format of *dd/mm/yyyy*.

<sup>&</sup>lt;sup>6</sup>Defined by ISO/IEC 14882:2003

<sup>&</sup>lt;sup>7</sup>Defined by the UML Specification 2.0, 2006 (Object Management Group)

# 2

# The Belle II SVD Readout System

This chapter describes an early prototype of the Belle II SVD readout system, as available at HEPHY. The system was originally designed for an intermediate upgrade of the Belle SVD2, which was never implemented [3]. This prototype, however, contains all types of components of the planned new productive system albeit on a smaller scale. In the Belle II Experiment, the implementation of more SSDs will require a higher effort of readout hardware than provided by the present system. Thus, some design modifications will be necessary for the final design [6]. These modifications will potentially require adaptations of the software involved.

In the course of prototype development, an appropriate DAQ software application has evolved. Although this program has represented an elaborated and useful tool for several beam tests<sup>8</sup> and lab tests, it will only be suitable for future requirements to a limited extent (see Chapter 1).

Nevertheless, from a functional point of view, the existing program provides a state-of-the-art basis for further software development. Hence, a brief introduction to this software application will follow a description of the hardware setup.

<sup>&</sup>lt;sup>8</sup>These tests (typically conducted at CERN) are intended for the examination of SSD prototypes with a high-energy particle beam and all the equipment involved (e.g. readout electronics, cooling, software).

#### 2.1 The Hardware Setup

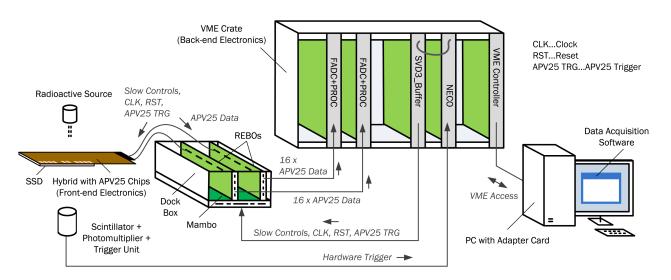

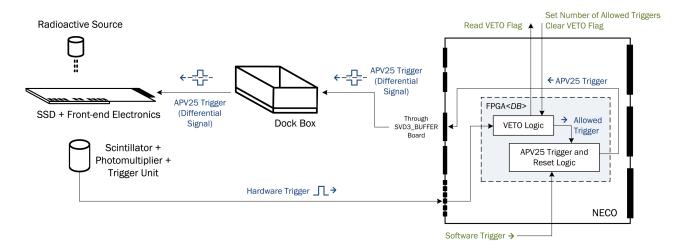

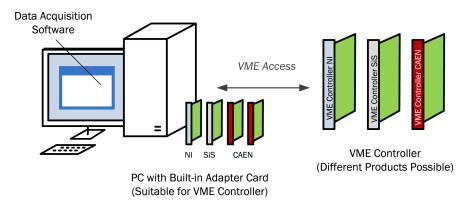

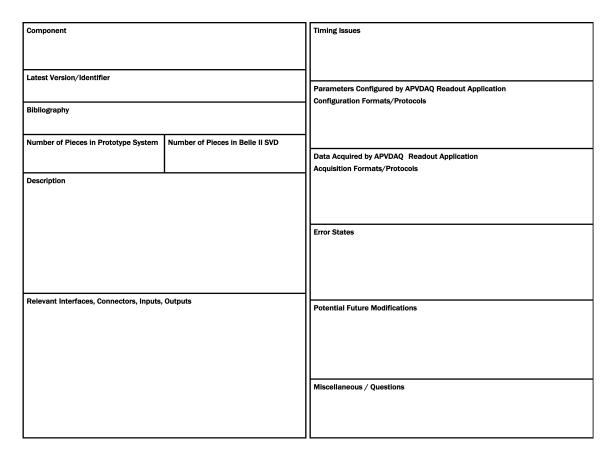

As shown in Fig. 2.1, the hardware setup at HEPHY consists of the following components<sup>9</sup>:

- A radioactive source (default: <sup>90</sup>Sr) emitting beta-particles (electrons) which are to be investigated. In contrast to a high energy beam, this source is available and suitable for lab tests at HEPHY.

- A *scintillator* with an attached *photomultiplier and trigger unit*, which in combination deliver a trigger pulse (referred to as *hardware trigger*) when a traversing particle is detected. Installed behind one or more detector modules, these devices indicate particles that have crossed all the sensors. Such an incident is also referred to as an *event*.

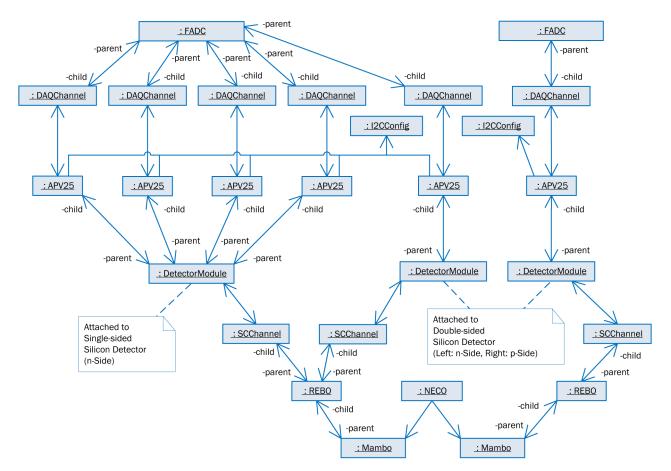

- Up to eight so-called *hybrids*, each of them attached to an SSD (single-sided or double-sided) for position measurements of traversing particles. Depending on the types of sensor and hybrid board, these *front-end electronics* usually contain four to ten *readout chips* of type APV25.

- One Dock box containing a motherboard (Mambo), which hosts two Repeater Boards (REBOs)

- A VMEbus<sup>10</sup> system (*VME crate*) containing *back-end electronics*. These contain one *VME controller*, one readout master controller (*NECO*<sup>11</sup>) along with a control distribution unit (*SVD3\_Buffer*<sup>12</sup>) and two *Flash Analogue-to-Digital Converter and Data Processing (FADC+PROC) boards*.

- A *Personal Computer (PC)* connected to the VME controller via an integrated *adapter card*. This PC runs an appropriate software application for the acquisition of data, referred to as *data acquisition software*.

Figure 2.1: Prototype of the Belle II SVD Readout System at HEPHY

<sup>&</sup>lt;sup>9</sup>Power supplies and respective cabling are not considered.

<sup>&</sup>lt;sup>10</sup>Defined by ANSI/IEEE 1014-1987

<sup>&</sup>lt;sup>11</sup>NECO is an acronym for New Controller.

<sup>&</sup>lt;sup>12</sup>SVD3 is an acronym for Silicon Vertex Detector 3, which was originally designed as an upgrade of the Belle SVD2.

On the following pages, the main electronic components of the readout chain will be explained from a software developer's perspective. Referring to Fig. 2.1, the readout chain will be described from left to right, starting with the SSDs.

#### 2.1.1 Silicon Strip Detectors

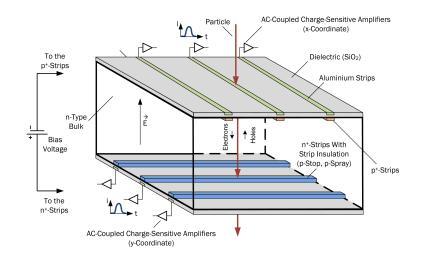

A Silicon Strip Detector (SSD) is a semiconductor device intended for the detection of traversing charged particles and photons, respectively. It is also referred to as *sensor* and comprises a number of doped narrow strip implants, which act as charge collecting electrodes. Placed on one side of a low-doped silicon bulk, these strips build a one-dimensional array of diodes. By connecting each strip to a charge-sensitive amplifier (readout chip), one-dimensional position measurements of traversing particles can be achieved. Respective detectors are referred to as Single-Sided Silicon Strip Detectors (SSSDs).

Two-dimensional position measurements can be achieved with so-called Double-Sided Silicon Strip Detectors (DSSDs). These detectors provide another set of doped narrow strips on the backside of the bulk.

Fig. 2.2 describes the function principle of an AC-coupled n-type bulk DSSD<sup>13</sup>. The strips, together with the bulk, provide a set of diodes, which are reverse-biased. That is, n<sup>+</sup>-strips are connected to a voltage more positive than the voltage of the p<sup>+</sup>-strips. The bias voltage causes an electric field  $\vec{E}$  within the semiconductor.

If a charged particle traverses the device, it produces electron-hole pairs (due to energy loss). Under the influence of the electric field, the carriers move towards respective electrodes (strips). The drifting carriers induce currents i(t) in the electrodes, which can be acquired by AC-coupled charge-sensitive amplifiers.

Figure 2.2: Function Principle of an n-Type Bulk Double-Sided Silicon Strip Detector (DSSD)

The original Belle II SVD design contains 187 n-type bulk DSSDs, each providing either 512 or 768 n<sup>+</sup>strips and 768 p<sup>+</sup>-strips [3]. These design parameters may change up until the completion of the final design. At HEPHY, both SSSDs and DSSDs with various strip configurations are used for experimental research.

<sup>&</sup>lt;sup>13</sup>This type of DSSD is used in the Belle II Experiment.

#### 2.1.2 APV25 Readout Chips

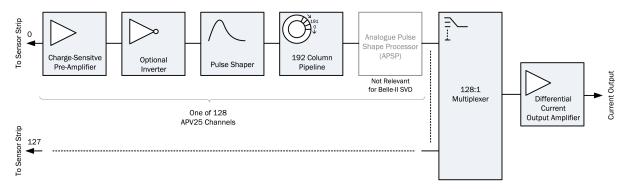

The APV25 readout chip is an analogue pipeline Application-Specific Integrated Circuit (ASIC) designed for the readout of 128 strips of an SSD. Fig. 2.3 presents a block diagram of the chip's internal structure.

Figure 2.3: APV25 Block Diagram, Based on Fig. 1 of [5]

The ASIC provides 128 channels, each dedicated to the readout of a specific sensor strip. Within a channel, the charge values obtained from the corresponding strip are amplified, optionally inverted, shaped and periodically written to a 192 column analogue ring buffer memory. This memory is referred to as *pipeline*, and it allows practically dead-time free measurements [4]. Depending on the operation mode, either one (*peak mode*) or more (*multi-peak mode*) consecutive samples of one pipeline column can be read out<sup>14</sup>.

These samples are obtained from the pipeline and output by a multiplexer stage once an appropriate trigger signal is given. From now on, this trigger signal will be referred to as *APV25 trigger* (in contrast to the hardware trigger signal introduced in Section 2.1). Two consecutive APV25 triggers must be separated by at least two clock cycles [7]. This constraint defines the *maximum rate of APV25 triggers*.

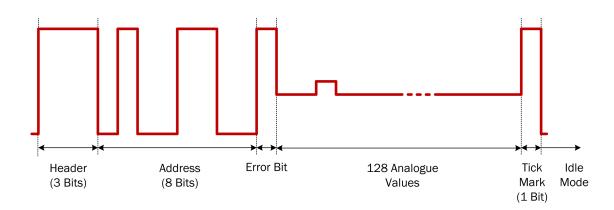

The APV25 has a differential analogue current output where the 128 multiplexed samples of analogue strip data are represented by current values<sup>15</sup>. Due to the internal multiplexer structure, the order of channels read out is non-consecutive [7]. In the output signal of one respective sample, the sequence of 128 analogue values is preceded by a digital header, a digital 8-bit address and an error bit. The address refers to the pipeline column containing the analogue values of when the chip was triggered. A synchronisation pulse (*tick mark*) is output periodically, regardless of whether an APV25 trigger has been given or not<sup>16</sup>. Fig. 2.4 shows the analogue output format of the APV25.

A slow control interface conforming to the  $I^2C$  standard<sup>17</sup> allows the control of certain circuit parameters and other general settings (e.g. the operation mode). The chip also provides an internal calibration feature, which is outlined in [8].

As per original plan, the implementation of 1902 APV25 chips into the future Belle II SVD is proposed [4]. However, a concrete number of instances will be defined when the detector design is frozen. The prototype at HEPHY was designed for 384 chips. Because of limitations in installed readout hardware, it can be used for the readout of 32 chips.

<sup>&</sup>lt;sup>14</sup>For *hit-time reconstruction* (implemented on FADC+PROC boards), typically six consecutive samples are taken [4].

$<sup>^{15}</sup>g_{AS} = 1 \text{ mA}/MIP$ ,  $g_{AS}$ ...APV25 Analogue Signal Gain, MIP...Minimum Ionisable Particle, see Fig. 5.4 of [8]

<sup>&</sup>lt;sup>16</sup>Subsequent to the sequence of 128 analogue values of the last sample output before the chip changes to idle mode. In idle mode, a tick mark is issued every 35 clock cycles.

<sup>&</sup>lt;sup>17</sup>Defined by the I<sup>2</sup>C-Bus Specification, Version 2.1, January 2000 (NXP Semiconductors)

Figure 2.4: APV25 Analogue Output Format (Abscissa: Time; Ordinate: Reconstructed Amplitude of Differential Output Current), see [7]

#### 2.1.3 Hybrids

The APV25 requires only a limited amount of external wiring. Among electrical measures, the chip's  $I^2C$  address is programmed by tying dedicated pins to ground or leaving them floating. Furthermore, the arrangement of multiple readout chips on one composite module means that the readout of entire sensors can be accomplished (typically containing 512 strips or more per side).

For that purpose, so-called hybrid boards have been developed. The future Belle II SVD design proposes two different types. In addition to *conventional hybrids* [8], *Origami chip-on-sensor modules* [9] will be implemented.

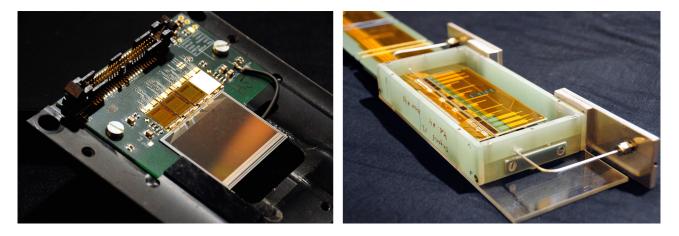

Fig.2.5 (left) shows a conventional hybrid board attached to a SSSD. It contains three of four possible readout chips serving 384 sensor strips. The readout of a Double-Sided Silicon Strip Detector (DSSD) would require two conventional hybrid boards. The photo on the right shows the Origami chip-on-sensor concept, where ten readout chips are mounted on top of a DSSD as part of a flexible electronic circuit . Electrically, four readout chips belong to one circuit serving the sensor's n-side (512 strips), whereas the other six chips belong to a separate circuit serving the p-side (768 strips).

For electrical reasons, one readout circuit can only serve one respective sensor side (either n-side or pside). Therefore, a DSSD requires at least two separate readout circuits. For the sake of simplicity, I will refer to an entire hardware readout module as *hybrid* (irrespective of its type). By contrast, I will refer to the electrical circuit serving one sensor side as *detector module*. In the case of Origami modules (serving DSSDs), one hybrid maps to two detector modules (one containing four readout chips and the other one containing six readout chips). However, a conventional hybrid maps to one detector module (containing four readout chips). Each detector module comprises a separate I<sup>2</sup>C control bus system<sup>18</sup>.

A design upgrade allowing for up to six readout chips per conventional hybrid board has been proposed. Considering this upgrade, the Belle II SVD design would require the implementation of 89 Origami modules and of 169 conventional hybrids [3]. This would map to 1902 APV25 chips spread over 347 detector modules. These numbers have to be considered as tentative up to the completion of the design process. The prototype at HEPHY can read out eight detector modules of four readout chips each.

Hybrids containing less than the maximum number of readout chips are also possible.

<sup>&</sup>lt;sup>18</sup>By default, I<sup>2</sup>C addresses 34, 36, 38, 40 (42, 44) are dedicated to the APV25S-1 chips of one respective detector module.

Figure 2.5: A Conventional Hybrid Board (left) in Contrast to a Prototype of the Origami Concept (right)

#### 2.1.4 Dock Box

The front-end detector modules have to be provided with clock, reset, APV25 trigger and I<sup>2</sup>C control signals (*slow controls*), all of which are generated and delivered by the NECO master controller / SVD3\_Buffer in the back-end (see Section 2.1.5). Moreover, analogue data obtained from detector modules is to be transferred to dedicated FADC+PROC boards (also located in the back-end, see Section 2.1.6).

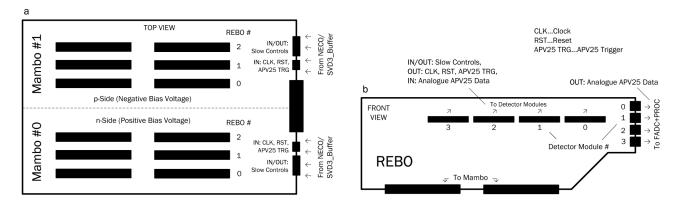

Not only do all of these signals have to be buffered, but in addition to that, floating low voltage signals of the front-end have to be translated to ground-bound signals of the back-end and vice versa [3]. These tasks are accomplished by repeater boxes (Dock boxes) located a few meters away from the front-end electronics. Electronically, each Dock box contains a motherboard (Mambo) hosting up to six Repeater Boards (REBOs).

Fig. 2.6 gives a schematic overview of both components: The motherboard is composed of two electrical subunits, Mambo #0 which hosts up to three REBOs dedicated to n-side detector modules and Mambo #1 hosting up to three REBOs dedicated to p-side detector modules<sup>19</sup>. Each REBO slot has a unique address within one Mambo subunit.

Actual signal buffering and level translation are implemented in the REBO units. In these units, clock, reset, APV25 trigger and slow controls obtained from the back-end are translated and subsequently delivered to respective detector modules. Furthermore, data read out from the front-end is translated and transported to the back-end.

The prototype readout chain at HEPHY was designed for the operation of up to four Dock boxes, altogether containing eight Mambo subunits and 24 REBOs. Every REBO can serve up to four detector modules, each of which contains a maximum of four readout chips.

Dock boxes will be replaced by *junction boxes* in the proposed final design. These junction boxes will only contain connectors, voltage regulators and passive components. Together with the FADC+PROC functionality, signal level translation will be implemented into a new composite back-end board, which will serve up to 24 readout-chips<sup>20</sup>. About 80 of these boards (spread over several VME crates) will be deployed [3].

<sup>&</sup>lt;sup>19</sup>These assignments are specific to the HEPHY lab; in any other setting Mambo #0 could also be dedicated to p-side modules and Mambo #1 to n-side modules.

<sup>&</sup>lt;sup>20</sup>Either six detector modules of four chips each or four detector modules of six chips each

Figure 2.6: Schematic Overview and Addressing Schemes of (a) Mambo and (b) REBO

#### 2.1.5 NECO Master Controller and SVD3\_Buffer

The New Controller (NECO) is a 9U VME board<sup>21</sup> located in the back-end. It can be controlled by software via the VMEbus interface. To achieve front-end configuration and flow-control, the NECO unit allows to address detector modules following the addressing schemes of Mambo and REBO (see Fig. 2.6). It delivers slow controls from the back-end to Dock boxes, where they are forwarded to connected detector modules. Within a detector module, readout-chips are addressed via a dedicated I<sup>2</sup>C bus (see Section 2.1.3). In addition to slow controls, the board generates and delivers clock, reset and APV25 trigger signals.

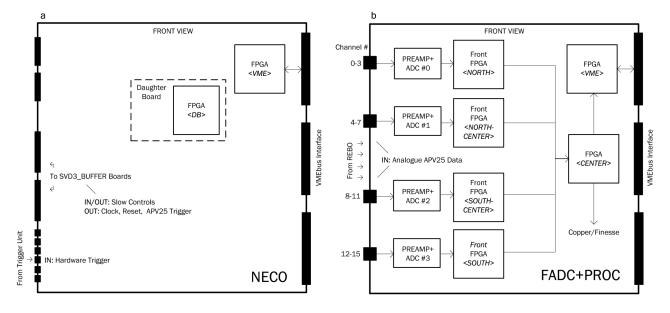

Fig. 2.7a gives an elementary overview of the NECO master controller. It contains two Field Programmable Gate Arrays (FPGAs). FPGA<DB>comprises several logical components, among them:

- · Several registers for enabling, resetting and configuring involved equipment

- A so-called *VETO logic*, which limits the rate of allowed hardware triggers to the maximum rate of APV25 triggers (see Section 2.1.2). In addition to that, it ensures that data processing and DAQ can be accomplished in real-time.

- An APV25 trigger and reset logic for the generation of appropriate APV25 trigger and reset signals

FPGA<VME> is intended for VMEbus communication. In addition, this FPGA comprises an  $I^2C$  master unit for the utilisation of I<sup>2</sup>C busses on NECO, on REBOs and in the detector modules.

The VETO logic blocks all hardware triggers exceeding a configurable number of *allowed triggers*<sup>22</sup>. A *VETO flag* is set when the number of allowed triggered has been reached. This flag can be read out and cleared by software.

Allowed triggers are passed to the APV25 trigger and reset logic. This unit generates APV25 triggers and APV25 reset signals conforming to the chip's specifications. In contrast to hardware triggers, that are allowed to pass through by the VETO logic, the generation of APV25 triggers<sup>23</sup> can be initiated by software. These *software triggers* are, however, asynchronous to actual events at the sensor. In Fig. 2.8, an overview is given. Different trigger types are marked blue, and software initiated actions are represented in green colour.

<sup>&</sup>lt;sup>21</sup>Default VME address of NECO prototype at HEPHY: 1A000000<sub>h</sub>

<sup>&</sup>lt;sup>22</sup>Typically one (configurable by configuration file)

<sup>&</sup>lt;sup>23</sup>And APV25 reset signals, respectively

Figure 2.7: Schematic Overview and Addressing Schemes of (a) NECO and (b) FADC+PROC

Figure 2.8: VETO Logic, APV25 Trigger and Reset Logic of NECO

Propagation delays of involved signals (mainly caused by cable lengths) are non-negligible. To achieve correct Analogue-To-Digital Converter (ADC) timing and synchronisation of clock and trigger signals, delay elements<sup>24</sup> are implemented on the NECO and FADC+PROC boards as well as in the REBO units. Providing an I<sup>2</sup>C interface, the delay elements of NECO and REBO can be configured by the NECO I<sup>2</sup>C master unit.

The design of the prototype readout chain would allow to spread back-end electronics over two VME crates. In this scenario, the NECO master controller, installed in one crate, would be supported by two SVD3\_Buffer distribution boards (each buffer board located in a separate VME crate). The task of these distribution boards is to buffer signals and to forward them to Dock boxes accordingly.

In the present prototype system the NECO master controller could be connected to two separate SVD3\_Buffer boards, each allowing the connection of two Dock boxes. For the final design, an upgrade, which conforms with the modified structure mentioned in Section 2.1.4, will be necessary.

#### 2.1.6 FADC+PROC Data Processing Boards

Like NECO, the Flash Analogue-to-Digital Converter and Data Processing (FADC+PROC) unit is a 9U VME board<sup>25</sup> in the back-end. A conceptual overview is given in Fig. 2.7b. The board provides 16 inputs for analogue APV25 data bundled to groups of four readout chips. These bundles correspond to specific detector modules and consequently to their dedicated REBO outputs. Data of all channels is processed and subsequently held available for data acquisition.

Each input is connected to an adjustable equaliser, which compensates for involved frequency-dependent cable loss. This unit is followed by a preamplifier and a 10-bit Flash Analogue-to-Digital Converter (FADC). In subsequent FPGAs (referred to as *front FPGAs*), groups of four channels have a dedicated pipelined processing unit which can perform channel reordering (to restore the physical strip order, see Section 2.1.2), pedestal subtraction, a two-pass common mode correction and zero suppression (sparsification). Following this, the data from all channels is collected, formatted and buffered in FPGA<CENTER>(referred to as *central FPGA*) [4]. The board can be operated in two different modes:

- Transparent mode All raw APV25 data can be acquired as it has been obtained from the front-end (in non-consecutive strip-order). This data is held available in First In, First Out (FIFO) memories<sup>26</sup>, each of which is assigned to an input channel of the board and implemented in the Front FPGAs.

- 2. *Hit mode* Different from transparent mode, a filtered subset solely containing significant data of particle hits can be acquired. This filtering is done by the hardware in real-time. The resulting hit data from all channels is collected, re-ordered and stored in a FIFO memory<sup>27</sup> of the central FPGA.

Data can be acquired via the VMEbus interface (implemented in FPGA<VME>). This option is the simplest, and therefore used at the HEPHY lab. Alternatively, a COPPER/FINESSE interface could be used. This is a "general purpose pipelined readout platform developed at KEK" [3]. It would allow data readout at a higher transfer rate but would come with additional hardware requirements.

<sup>&</sup>lt;sup>24</sup>Of type Delay25 [10]

<sup>&</sup>lt;sup>25</sup>Default VME addresses of prototype FADC+PROC boards at HEPHY: 1B000000h, 2B000000h

<sup>&</sup>lt;sup>26</sup>Namely *FIFO1*

<sup>&</sup>lt;sup>27</sup>Namely FIFO3

The prototype readout system was designed for the use of 32 FADC+PROC data processing boards. For the final design of the Belle II SVD readout system, the deliberations in Section 2.1.4 have to be taken into consideration.

#### 2.1.7 VME Controller and VME/PC Interface

The NECO master controller and the FADC+PROC data processing units in the back-end can be accessed via their VMEbus interface. For this purpose, a PC containing an adapter card is connected to a VME controller, which is installed in the VME crate. A PC software program can use this combination (referred to as *VME bridge*) to set up and control a DAQ process.

At HEPHY lab, an NI MXI-card for the conventional PCI<sup>28</sup> bus in combination with an appropriate NI VME-MXI-2 VME crate controller module has been used for several years. This solution has become outdated for the following reasons:

- In modern PC equipment, the conventional PCI bus interface has become deprecated. Sticking to a PCI-based adapter card would make the selection of new computer equipment difficult.

- Experience has shown that the stability of software drivers and according software programs is suboptimal.

Therefore, two alternative VME bridges were acquired:

- 1. CAEN A2818 PCI adapter [11] and A3818 PCIe<sup>29</sup> adapter [12] / V2718 VME controller [13]

- 2. Struck Innovative Systeme (SiS)1100e PCIe adapter / 3104 VME controller [14]

Both VME bridges are characterised by fibre-optic links and the availability of Linux-based software drivers. They promise improvements on the outdated NI solution and are the first choice for all future activities.

Fig. 2.9 shows the situation at HEPHY lab. In total, three different VME controllers with appropriate adapter cards are available.

Figure 2.9: VME Bridges at HEPHY Lab

<sup>&</sup>lt;sup>28</sup>Defined by the PCI Local Bus Specification, 2002 (PCI-SIG)

<sup>&</sup>lt;sup>29</sup>Defined by the PCI Express 1.0a Specification, 2003 (PCI-SIG)

#### 2.2 Data Acquisition Software

The readout system described in Section 2.1 is an enhancement of an APV25-based predecessor system named *APVDAQ* [15]. An appropriate DAQ software application [8] had been deployed with APVDAQ before both hardware and software were extended gradually in the course of time.

Therefore, the DAQ software program for the present prototype readout system provides many functions and algorithms of the original APVDAQ system. These are supplemented by extensions addressing new hardware (NECO, FADC+PROC, Mambo, REBO) and respective Graphical User Interface (GUI) elements. Taking this background into account, the evolved program is still referred to as *APVDAQ readout application*.

It was developed with NI LabWindows/CVI, an event-driven ANSI C Integrated Development Environment (IDE) that provides engineering-specific functionality for instrument control, DAQ, analysis and User Interface (UI) development [16]. As mentioned in Chapter 1, the application is Windows-based.

#### 2.2.1 Functional Overview

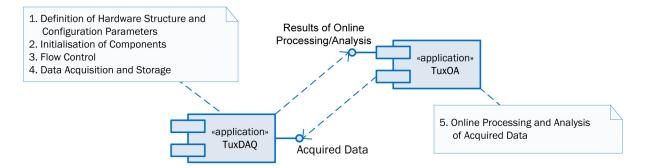

The APVDAQ readout application is used to manage DAQ runs by means of the prototype Belle II SVD readout system. In this context, a *DAQ run* can be understood as a process designed to obtain particle detector data from a set of front-end readout chips. Acquired data can be stored for further analysis by an offline analysis tool, which has also been developed at HEPHY (see Section 7.4 of [8]). The APVDAQ readout application fulfils five major tasks:

- 1. Definition of the hardware structure and setup of configuration parameters based on a *configuration file* (see Section 2.2.5)

- 2. Appropriate initialisation of all components involved

- Flow control management by proper delivery of VME messages to NECO and FADC+PROC boards and delivery of slow controls to the front-end (via NECO)

- 4. Data acquisition from FADC+PROC boards and storage of acquired data

- 5. Online processing and analysis of acquired data

#### 2.2.2 Run Types

The APVDAQ readout application provides several types of DAQ runs. Irrespective of the type, a given number of events<sup>30</sup> are always captured at the beginning of a run. For these events (referred to as *initial events* or *pedestal events*), software triggers are initiated periodically by the program in order to determine pedestals and signal noise of all sensor strips<sup>31</sup> observed. Resulting values are used for appropriate signal correction by means of hardware (FADC+PROC) and software.

<sup>&</sup>lt;sup>30</sup>Typically 600 (parameter in the configuration file)

<sup>&</sup>lt;sup>31</sup>Under the assumption that the random noise process at the sensor is time-invariant within the software trigger interval, periodical (deterministic) sampling and stochastic sampling provide same results. Therefore, the acquisition of pedestal events based on periodical trigger delivery can be considered as a random process.

Among others, the APVDAQ readout application provides the following DAQ run types:

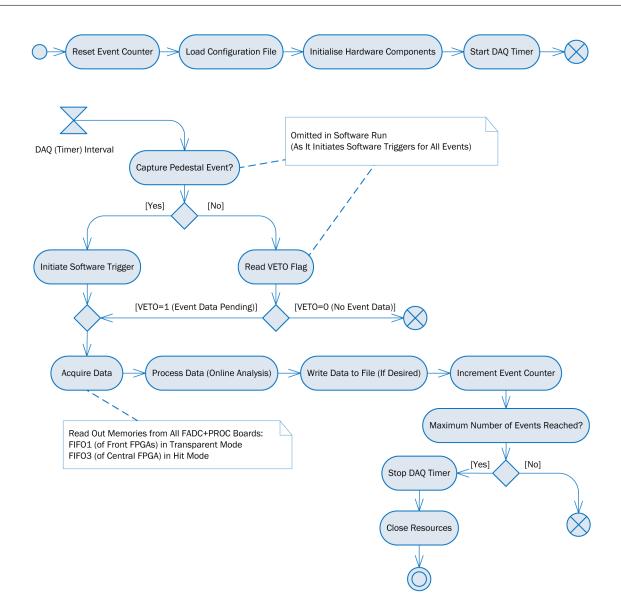

- *Hardware run* This is used for source measurements in the laboratory as well as for beam tests. At the beginning, all hardware components are initialised based on a given configuration file. In the next step, the acquisition of pedestal events is accomplished. Subsequently, the status of the VETO flag (see Section 2.1.5) is checked periodically at the pace of the DAQ timer. If the VETO flag is set, new event data is pending. Consequently, data acquisition, processing and storage (if desired) are accomplished before the program clears the VETO flag again. This procedure is repeated until the desired number of events have been captured. Fig. 2.10 visualises the hardware run in the form an UML activity diagram.

- *Software run* In contrast, this process is entirely based on software triggers. The VETO logic is disabled, and consequently any hardware triggers are ignored. In a software run, software triggers are initiated cyclically at the pace of the DAQ timer. As software triggers are asynchronous to particle hits, this run type is not suitable for the acquisition of relevant particle data. However, the advantage of a software run is that no radioactive source or beam is needed. Therefore, it can be used for development purposes and to test the proper functioning of the whole readout chain.

- *Run for internal calibration* This utilises the built-in calibration feature of the APV25 chip. It is used to check the peaking time and to obtain calibration constants for each strip channel. Further offline analysis tools require this data for converting ADC values into electron-based signals [8].

- *ADC delay scan* This allows the user to determine the best setting of the ADC delay, which is associated with each readout channel of the FADC+PROC board. The ADC delay value has an essential impact on the timing of respective FADC chips.

For a detailed description of both the calibration run and the ADC delay scan, see Section 6.6.1 of  $[8]^{32}$ .

#### 2.2.3 Performing a DAQ Run

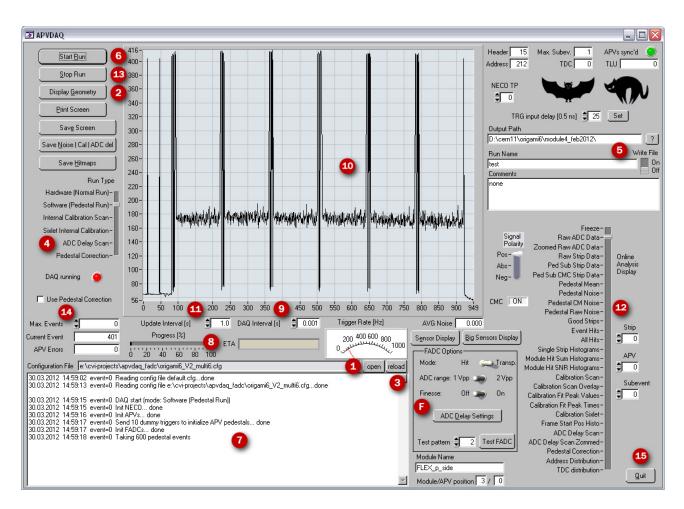

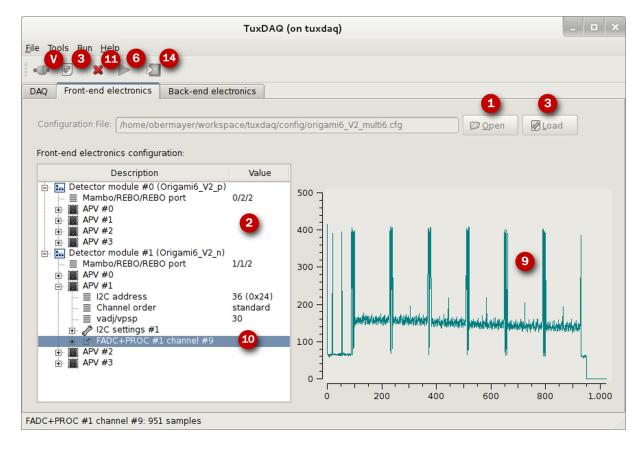

Fig. 2.11 shows the GUI of the APVDAQ readout application. Below, the typical scenario for performing a DAQ run<sup>33</sup> is described. The numbers and letters between parentheses refer to the respective labels in the figure.

After starting up the application, the GUI is loaded. Now the user can select a configuration file (1), which defines the structure of the readout hardware (front-end and back-end) as well as certain configuration parameters. Having selected an appropriate file, the arrangement of front-end electronics defined within it may be verified with a geometry display. This tool can be opened with (2). If the given configuration settings need to be varied, the configuration file can be edited during runtime with an external text editor. Then, the modified file can be reloaded (3) without a restart of the application.

In the next step, the user can select the type of DAQ run that is to be performed (4). Depending on whether or not acquired data should be written to a file, an output path, a run name and respective comments can be entered (5).

<sup>&</sup>lt;sup>32</sup>Explanations in [8] about a common clock delay for all readout channels do not apply. FADC+PROC boards allow to define this value for each particular channel.

<sup>&</sup>lt;sup>33</sup>Hardware run or software run

Figure 2.10: Hardware Run of the APVDAQ Readout Application (UML Activity Diagram, Reverse-Engineered)

Once an appropriate configuration file has been loaded, a run type selected and data output set up properly, a DAQ run can be initiated with the 'Start Run' button (6). Following this, the application performs an initialisation of all involved hardware components based on configuration file settings. For this purpose, it addresses NECO and FADC+PROC boards via the VME bridge. Slow controls, intended for the front-end, are handed over to the NECO controller, which distributes them to Dock boxes accordingly. They are forwarded to respective detector modules. This procedure can be traced in a console window (7), which is also used for error notifications and other status messages.

Once the setup of hardware components has finished, the acquisition of data from the FADC+PROC boards starts. In addition to the console window, several GUI widgets (8) monitor the ongoing DAQ run. Further to the actual APV25 trigger rate, the number of the currently captured event, the number of occurred APV errors and the Estimated Time of Arrival (ETA) (estimated completion time) are presented to the user.

Figure 2.11: GUI of the APVDAQ Readout Application

A timer-based architecture allows the user to interact with the GUI during a DAQ run. Therefore, a DAQ *interval*<sup>34</sup> can be defined (9), which corresponds to a period of time during which data is acquired cyclically. A plot widget (10) provides graphical information on the recently captured and processed data<sup>35</sup>. The plot is updated periodically at an interval<sup>36</sup> that can be adjusted separately (11). Here, a value of zero would lead to plot updates at the pace of data acquisition.

The user can choose among various plot types by means of a dedicated slider widget (12), and analysis results are presented in the plot widget <sup>37</sup>. The algorithms provided allow noise calculation, pedestal subtraction, common mode correction and hit finding.

Generally, a DAQ run concludes after the 'Stop Run' button (13) has been pressed. In addition to that, the user may define a maximum number of events to be captured (14). In this case, the DAQ run terminates

<sup>&</sup>lt;sup>34</sup>Typically (and at minimum) 1 ms

<sup>&</sup>lt;sup>35</sup>Extraction of raw strip data from data frames and reordering of sensor strips (see Section 2.1.2)

$<sup>^{36}\</sup>text{Typically}~1\,\text{s}$

<sup>&</sup>lt;sup>37</sup>In Fig. 2.11, the option 'Raw ADC Data' is selected (12): Raw FADC data currently read out from one specific APV25 front-end chip is visualised by the plot widget (abscissa: time in clock periods; ordinate: amplitude in ADC counts). The plot shows the data regarding one respective event, where six consecutive samples have been captured in consequence of one APV25 trigger signal (chip operated in multi-peak mode). As mentioned in Section 2.1.2, for each of the six samples a digital header is followed by 128 values of analogue strip data. In the example at hand, analogue values hint at channel-to-channel pedestal variations rather than a significant particle hit on the sensor. In contrast, Fig. 5.28 of [3] shows a comparable plot containing data of a captured particle hit.

automatically as soon as the desired set of events has been recorded. This setting can also be changed during an ongoing DAQ process. If the value is zero, the DAQ run does not conclude automatically. Instead, the user has to terminate the process manually.

All acquired data is written to disk, if desired (see Section 2.2.6). The APVDAQ readout application allows the execution of several successive DAQ runs without the need for a program restart. The user can quit the application by pressing the 'Quit' button (15).

#### 2.2.4 FADC+PROC Test

In addition to several run types, the APVDAQ readout application provides a test function for FADC+PROC boards (see Fig. 2.11, (F)).

Different *test patterns* (predefined test data) can be loaded into a dedicated test Random Access Memory (RAM) of an FADC+PROC unit. Then, the test function acquires this data from the board via VME bridge and plots both test data as well as acquired data on the screen. If both plots match, it can be assumed that the tested unit works properly.

By these means, FADC+PROC hardware and firmware, VME connectivity and applied settings can be tested. Note that for such a test the checked FADC+PROC board has to be configured for autonomous clock generation [17].

#### 2.2.5 The Configuration File

Ahead of a run, an appropriate configuration file has to be loaded. This configuration file contains:

- *Definition and configuration of front-end electronics* This implies different APV25 parameters, the definition of composite detector modules and their addressing within the given hardware structure.

- *Definition and configuration of back-end electronics* In addition to the addressing of all back-end boards, specific parameters for NECO and FADC+PROC boards can be defined.

- *DAQ parameters* These are hardware and software parameters, which are relevant for a data acquisition process.

- Sensors and zones configuration For online analysis purposes, sensors can be defined. In addition to the

definition of their physical parameters, sensors are associated with readout chips. Furthermore, they can

be partitioned into several zones<sup>38</sup>.

- Other parameters These imply parameters for calibration and hit recognition.

#### 2.2.6 Data Output Files

Depending on the type of a run, the APVDAQ readout application produces several output files. During a DAQ run, the following files are produced:

• A copy of the original configuration file (.cfg) As the used configuration file contains essential information on a specific run, a copy is created. This copy is used by offline analysis tools.

<sup>&</sup>lt;sup>38</sup>A sensor zone can be considered as a unique set of strips of a specific sensor.

- *A log file (.txt)* This is a plain text file, which contains the run type, the run name, respective comments, the number of events, a note on the original configuration file and logging output that has been produced during a run. The log file is also used by offline analysis tools.

- *Binary data files (.dat)* Data acquired from FADC+PROC during a DAQ run is stored in binary format. If a large amount of data is acquired, a new data file is spawned after every 2 GB. The generated files serve as a data basis for offline analysis.

The run for internal calibration produces a *calibration file* (*.cal*), which is described in Section 6.6.1 of [8]. The ADC delay scan does not produce any data output files [8].

3

## Software Requirements

Chapter 1 outlined the role of the APVDAQ readout application at HEPHY and the demand for a new concept to meet future requirements. In Chapter 2, the hardware environment and the APVDAQ readout application were described briefly.

This chapter presents the software requirements for a new DAQ application. The provided requirements were identified in a dedicated *requirements engineering process*, which included the following activities:

- *Requirements elicitation* Professional staff was accompanied and interviewed during everyday work with the APVDAQ readout application at HEPHY lab and during a beam test at CERN in October 2011. In so doing, typical *scenarios* were identified.

- *Requirements classification, organisation, prioritisation and negotiation* These activities were mainly performed in the context of *weekly meetings* with the staff of the HEPHY Department of Electronics.

- *Iterative requirements definition and specification* This was accomplished with the help of a *Wiki* system<sup>39</sup> [18] for documentation and communication.

The organisation of this chapter follows the recommendations of IEEE 830-1998 [19] and [20]. Sections 3.1 to 3.3 serve as a brief introduction. Section 3.4 provides a User Requirements Definition (URD) containing (*functional* and *non-functional*) *user requirements*, which describe the services provided by the new application from a user's point of view. As a comprehensive System Requirements Specification (SRS) would be out of scope of this thesis, an exemplary overview in Section 3.5 shows how formal *system requirements* can be defined. These build a solid basis for the design, implementation and test of the required application.

<sup>&</sup>lt;sup>39</sup>A web-based content management system which is characteristically easy to handle

All presented methods of requirements engineering have been chosen with the claim for a balance between effort and benefit. They are suitable for engineers of all disciplines, who develop software in an environment of non-computer scientists. Therefore, formal methods that can be learned easily were chosen over more difficult ones whenever their use was considered reasonable or inevitable.

#### 3.1 Purpose

This chapter describes the user requirements for a new DAQ program that is suitable for the prototype of the Belle II SVD readout system (see Chapter 2).

The intended audience is the staff of the institute's Department of Electronics and successional students, who will use and advance the system, the thesis advisor Dr. Karl Riedling and the developer.

#### 3.2 Scope

Section 2.2.1 described the main tasks of the APVDAQ readout application. The software product to be developed will be functionally based on this program, but it will assign the stated tasks to two separate Linux-based programs:

- Tasks 1 to 4 will be covered by a program named  $TuxDAQ^{40}$ . The present thesis deals with this program and gives a comprehensive overview on the requirements, design and implementation of TuxDAQ.

- Task 5 will be covered by another program, the *TuxOA*<sup>41</sup>. A detailed description of that program is beyond the scope of this thesis. However, many of the introduced components can be used for both TuxDAQ and TuxOA. An outlook on the interaction between both programs is presented in Section 5.7.

Both programs will exchange acquired data via a dedicated interface. The separation of tasks promises an increase of runtime flexibility and performance scalability. Fig. 3.1 shows the new configuration in a UML component diagram.

Figure 3.1: Separation of Tasks (UML Component Diagram)

<sup>&</sup>lt;sup>40</sup>The name TuxDAQ is a composition of *Tux* and *Data Acquisition (DAQ)*. Tux is the name of the offical Linux mascot [21].

<sup>&</sup>lt;sup>41</sup>The name TuxOA is a composition of *Tux* and *Online Analysis (OA)*.

#### 3.3 Requirements Format and Numbering

The verb *shall* is used whenever the described requirement is mandatory, *should* is used for desirable requirements. Sentences without any of these verbs are explanations. Text belonging to formal user requirements is in **bold** face to improve readability.

User requirements are identified by the section they belong to and also by an item number. This item number is unique within a particular section. For references to a specific requirement, a *user requirement identifier* is used, following the syntax rule below:

Requirement <section>/<number>, where

<section> is the number of the section to which the requirement belongs to <number> is the item number used with each instance of <section>.

If a requirement is referenced within a particular section, the section number and the separating slash are omitted.

#### 3.4 User Requirements Definition

This section characterises the typical TuxDAQ user and describes the services which TuxDAQ offers for them. In addition to user requirements (sentences containing 'shall' or 'should'), explanations are provided.

As a framework of maintainable components for the Belle II Experiment will be extracted, special attention has been given to several kinds of *traceability* [20]:

- *Source traceability* User requirements are linked to the people who proposed them (see Appendix A.1) and supported by their rationales. In so doing, system developers can understand requirements better, and qualified people can be consulted in case of a requirements change.

- *Requirements traceability* By documenting dependencies between requirements, it is possible to evaluate the number of affected requirements when one particular requirement changes. See Appendix A.2 for a detailed requirements traceability overview.

- *Design traceability* Links between requirements and design modules allow system developers to identify all design modules impacted by a proposed requirements change. For a design traceability table, see Appendix A.3.

It should be mentioned that the user requirements presented here were primarily formulated with a focus on the user perspective and readability. Although they have the characteristics of good requirements<sup>42</sup>, user requirements are neither specific enough to serve as a straight basis for programmers nor are they suitable for the identification of software test cases. For these scenarios, specific system requirements are needed (see Section 3.5).

<sup>&</sup>lt;sup>42</sup>Requirements should be correct, unambiguous, complete, consistent, ranked according to importance, verifiable, modifiable and traceable [19].

#### 3.4.1 User Characteristics

Fig. 3.2 gives an overview on the TuxDAQ user hierarchy.

Typically, a *TuxDAQ user* is a physicist or a an electronic engineer who is educated in the field of SSDs. They are interested in acquiring data and its according interpretation. The typical TuxDAQ user understands where to connect hybrid prototypes and how to operate the readout system and software application. Relevant configuration files are provided to the typical TuxDAQ user. In case of any error, the typical TuxDAQ user consults a specialist for troubleshooting.

A *specialised TuxDAQ user* is a developer, who has a sophisticated understanding of the readout system. In case of problems (in hardware or software), they are responsible for troubleshooting. This user type knows the implemented software procedures at least on a system level, and they are able to create configuration files for different hardware setups.

Specialised TuxDAQ User

Figure 3.2: TuxDAQ User Hierarchy (UML Actors and UML Generalisation Relationship)

#### 3.4.2 TuxDAQ Environment

The (hardware and software) environment of TuxDAQ can be described as follows:

1. Compatibility with the Belle II SVD Prototype Readout System:

### TuxDAQ shall be a DAQ application that is suitable for the prototype of the Belle II SVD readout system, which is described in Chapter 2.

2. Multiple VME Bridges:

Like the APVDAQ readout application, TuxDAQ will run on a PC that comprises an adapter card connected to a matching VME controller (installed in a VME crate). This so-called VME bridge represents a *low-level communication interface* between the back-end and the DAQ system. In contrast to the APVDAQ readout application, **TuxDAQ shall operate with different kinds of VME bridges (see Section 2.1.7) to communicate with the readout system.** Fig. 2.9 illustrates the existing VME environment at HEPHY.

3. Interoperability with HEPHY Offline Analysis Tool:

As a successor of the APVDAQ readout application, TuxDAQ is embedded in an environment of various established tools and processes. In particular, compatibility of TuxDAQ with the existing offline analysis

tool at HEPHY is important. To achieve this, **TuxDAQ shall produce the same set of data output files as the APVDAQ readout application (see Section 2.2.6)**. This refers to file types, names, sizes and formats.

4. Linux Compliance:

Due to the prevalence of Linux in the related scientific field, **TuxDAQ shall run on Linux-based oper**ating systems.

#### 3.4.3 Field of Application

1. Main Purpose of TuxDAQ:

TuxDAQ, together with the readout system, shall acquire data from SSD prototypes at the HEPHY laboratory in Vienna.

2. Usage at External Research Facilities:

In addition to lab tests, TuxDAQ shall serve as DAQ application for beam tests at different external research facilities. Typically, HEPHY staff organise periodical beam tests of new prototype equipment at CERN and KEK. For these beam tests, the readout system is installed at the external sites.

- 3. Reusability for the Belle II Experiment:

- a) The architecture and implementation of TuxDAQ shall allow software developers to extract a framework of maintainable components for the Belle II Experiment.

- b) These components shall cover tasks 1, 2 and 3 of Section 3.2. For task 4 (acquisition of data), a different dedicated DAQ system (including appropriate DAQ software) will be developed [3].

#### 3.4.4 Configuration

- 1. Configurability by Means of a Configuration File:

- a) **TuxDAQ shall allow for the definition of the hardware structure of the readout system by means of a configuration file that can be loaded by the user.** This does not include any settings specific to VME bridges.

- b) **TuxDAQ shall allow for the definition of parameters for the configuration of components by means of the same configuration file.** This does not include any settings specific to VME bridges.

- c) Referring to this configuration file, TuxDAQ should keep the legacy configuration file format of the APVDAQ readout application (see Section 2.2.5). Consequently, extra effort and expense for the re-creation of existing configuration files and staff training can be avoided.

- 2. No Sensors and Zones Necessary:

**TuxDAQ** shall not mandatorily require any configuration parameters for sensors and zones (as provided by legacy configuration files). This is because no online processing or analysis of the acquired data will be performed by TuxDAQ (see Requirement 3.4.5/2).

3. Selection of VME Bridge:

#### TuxDAQ shall allow the user to select a VME bridge for operation prior to program execution.

#### 3.4.5 Main Functions

TuxDAQ shall carry over functionality from the APVDAQ readout application as follows:

1. Exploration of Loaded Configuration:

**TuxDAQ shall allow exploration of a loaded configuration.** This could be achieved by the visualisation of both the hardware structure and the parameters defined in a configuration file. The exploration of a configuration by a skilled person prior to a run can prevent system malfunction.

- 2. No Online Data Processing and Analysis:

- a) Irrespective of the run type, TuxDAQ shall not perform any processing or analysis of the acquired data during operation.

- b) If data storage is desired, TuxDAQ shall store these data in its original format as acquired from the FADC+PROC boards.

This is because all online processing functionality will be extracted to TuxOA (see Section 3.2).

- 3. Hardware Run:

- a) TuxDAQ shall allow for a hardware run as described in Section 2.2.2.

- b) From a functional point of view, this run type shall be identical to the hardware run of the APVDAQ readout application except for the constraint mentioned above (see Requirement 2).

- 4. Software Run:

- a) TuxDAQ shall allow for a software run as described in Section 2.2.2.

- b) From a functional point of view, this run type shall be identical to the software run of the APVDAQ readout application except for the constraint mentioned above (see Requirement 2).

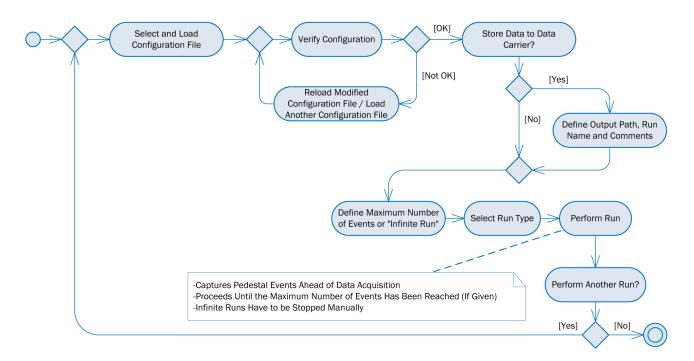

- 5. Typical Workflow:

- a) Based on the scenario described in Section 2.2.3, TuxDAQ shall allow the user to perform hardware and software runs according to the typical workflow outlined in Fig. 3.3.

- b) TuxDAQ shall allow activities prior to 'Perform Run' not only in the depicted sequence, but also in an arbitrary order (e.g. selecting a run type could be performed before a configuration file is loaded, etc.).

- c) TuxDAQ shall allow the user to request an 'infinite run', which captures events until they stop the run (or until the output data carrier is full).

- d) As an alternative, **TuxDAQ shall allow the user to define a maximum number of events to be captured (in this case, the program shall terminate the run automatically).**

Figure 3.3: *TuxDAQ Requirement: Typical Procedure of Performing a Hardware Run or a Software Run (UML Activity Diagram)*

- e) TuxDAQ shall allow the user to modify both settings, even during a run.

- f) If during a run a user sets the maximum number of events lower than the current number of events, TuxDAQ shall ignore the (invalid) user input.

- g) In addition to the activities depicted in Fig. 3.3, TuxDAQ shall allow the user to define a DAQ interval (see Section 2.2.3).

- 6. Run for Internal Calibration:

- a) TuxDAQ shall provide a run for internal calibration, as described in Section 2.2.2.

- b) The APVDAQ readout application stores data to a .cal file. This data has been processed after its acquisition. In contrast, **TuxDAQ shall store data to a .dat file that has been acquired directly from the FADC+PROC boards.** This is due to the fact that all online processing functionality will be extracted to TuxOA (see Section 3.2).

- 7. ADC Delay Scan: TuxDAQ shall provide an ADC delay scan, as described in Section 2.2.2.

- 8. FADC+PROC Test:

- a) TuxDAQ should provide an FADC+PROC test function, which is based on the test function of the APVDAQ readout application (see Section 2.2.4) as far as function is concerned.

- b) TuxDAQ should allow the user to test any channel of any configured FADC+PROC board.

- 9. Progress Monitoring of Active Run:

- a) TuxDAQ shall allow the user to follow the progress of an ongoing run, so that it is possible for the user to monitor the proper functioning of the readout system during operation.

- b) **TuxDAQ shall also provide additional information for specialised TuxDAQ users.** As a result, they can track the proper functioning of particular subprocesses (e.g. the initialisation of specific components).

- 10. Estimation of Run Conclusion:

**TuxDAQ shall allow the user to estimate when an ongoing run will conclude.** This enables staff to direct their attention to other tasks during long-term runs.

11. Offline Run Reproduction:

**TuxDAQ shall allow specialised TuxDAQ users to reproduce a successful run after conclusion and program termination.** On one hand, this helps staff to reproduce proper operation after long-term runs. On the other hand, it may facilitate understanding offline analysis results.

#### 3.4.6 Data Exchange with TuxOA

1. Stand-alone Operability:

If neither online processing nor online analysis of acquired data are necessary for operation, Tux-DAQ shall allow the user to operate it as a stand-alone application, without TuxOA running at the same time. This brings the benefits of runtime-flexibility and performance scalability.

- 2. Automatic TuxOA Invocation:

- a) If TuxDAQ requires results of online processing, it shall invoke TuxOA automatically.

- b) If this is the case, all data shall be exchanged between both applications automatically.

- 3. Collaboration with TuxOA:

- a) TuxDAQ shall allow the user to request the online analysis of acquired data prior to operation.

- b) In this scenario, TuxDAQ shall invoke TuxOA automatically and provide TuxOA with the data acquired. Online processing and analysis of acquired data are then performed automatically by TuxOA.

- c) TuxDAQ should also allow the user to request the online analysis of acquired data during operation.

#### 3.4.7 Error Treatment

- 1. Configuration File Validation:

- a) After a configuration file has been loaded by the user, TuxDAQ shall validate this file.

- b) If the file is invalid, TuxDAQ shall reject the configuration file.

c) In this case, TuxDAQ shall provide an error notification containing information about the fault for the user.

This prevents an undefined malfunction of the readout system due to configuration faults.

- 2. User Input Validation:

- a) If the information provided by the user prior to a run or FADC+PROC test is insufficient or invalid, TuxDAQ shall not start the run.

- b) Instead, TuxDAQ shall provide an error notification for the user.

- 3. Low-level Communication Link Error Handling:

- a) If the low-level communication link between TuxDAQ and the readout system cannot be established or used properly, TuxDAQ shall abort operation.

- b) In this case, TuxDAQ shall provide an error notification for the user.

These error notifications on communication link issues may simplify troubleshooting.

- 4. DAQ Error Handling:

- a) If, during operation, data cannot be acquired from the readout system properly, TuxDAQ shall abort operation. Due to the fact that the readout system could have run into an undefined error state, aborting operation is a safe coping strategy.

- b) In this case, TuxDAQ shall provide an error notification for the user.

- c) If available, TuxDAQ shall provide information on the fault as well. This may simplify troubleshooting.

- 5. Data Storage Error Handling:

- a) If, during operation, data cannot be written to the data carrier properly, TuxDAQ shall abort operation.

- b) In this case, TuxDAQ shall provide an error notification for the user.

- c) If available, TuxDAQ shall provide information on the fault as well.

See Requirement 4 for a rationale.

6. Recovery from Failures:

If any of the aforementioned problems (see Requirements 1, 2, 3, 4 and 5) have occurred, TuxDAQ shall recover in such a manner that the user can start over without a restart of the application. This improves usability and prevents an undefined malfunction during operation.

7. Error Notifications:

All possible error notifications issued by TuxDAQ shall be expressed in such a manner that specialised TuxDAQ users may identify a fault within a maximum duration of  $d_{IF,max} = 30 \text{ min.}$  As

TuxDAQ is not a consumer application, this requirement represents a reasonable tradeoff between development effort and user convenience.

8. Stack Trace on Error:

**For all possible error notifications, TuxDAQ shall present an according** *stack trace*<sup>43</sup>**.** This potentially simplifies troubleshooting.

9. Error Information on the Screen:

**TuxDAQ shall present error notifications and the according stack trace on the PC screen during operation.** This allows the user to react on problems immediately.

10. Offline Error Tracking:

**TuxDAQ shall archive error notifications and the according stack trace for an offline error analysis.** This is particularly useful when an error has occurred during a long-term run.

- 3.4.8 User Interface

- 1. Graphical User Interface (GUI):

TuxDAQ shall provide a Graphical User Interface (GUI). This is for user convenience.

2. GUI Tasks:

The TuxDAQ GUI (see Requirement 1) shall provide means to fulfil the following Requirements: 3.4.3/1, 3.4.4/1, 3.4.5/(1, 3, 4, 5, 6, 7, 8, 9, 10), 3.4.6/3 and 3.4.7/9.

- 3. Console Interface:

- a) As an alternative to a GUI, TuxDAQ should provide a console interface, which allows the user to operate the application on the standard console of the operating system. A console interface would allow operation without the need for a graphical desktop system. Additionally, it simplifies process automation. Moreover, some users prefer a console interface to a GUI.

- b) The console interface should fulfil the same requirements as the GUI does.

- c) Moreover, Requirement 3.4.7/8 should be considered.

- 4. GUI as Default User Interface:

- a) By default, TuxDAQ shall load the GUI at program start.

- b) TuxDAQ shall provide means that allow the user to declare at program start whether they want to use the console interface as an alternative to the GUI.

- c) TuxDAQ shall not provide both user interfaces at the same time.

<sup>&</sup>lt;sup>43</sup>A report on the sequence of nested active procedures at the point of time when an error occurred

# 3.4.9 System Properties and Constraints on the System Implementation

1. TuxDAQ as Open Source Project:

#### TuxDAQ shall be available as open source software.

2. Usage of Free Software Components:

Any programming libraries involved in TuxDAQ development shall be free software. That is, they shall permit combination and redistribution with TuxDAQ for scientific purposes at no cost.

3. Object-Oriented Design and Implementation:

**The TuxDAQ design and implementation shall be based on the object-oriented paradigm.** This is a state-of-the-art approach and improves maintainability (see Requirement 3.4.3/3).

4. C++ as Programming Language:

TuxDAQ shall be programmed in C++. This decision is based on the following reasons:

- C++ allows to follow the object-oriented paradigm.

- C++ is wide-spread in the related research area.

- Application Programming Interfaces (APIs) of the relevant VME bridges are available for C/C++.

- A variety of C++ tools (compiler, libraries, etc.) are available as free, Linux-based software.

- Legacy code of the APVDAQ readout application is available in C. Using C++ as programming language allows to carry over C code fragments with minimal effort.

- 5. Compatibility With the CERN ROOT Framework:

**TuxDAQ shall allow to integrate the CERN ROOT framework.** This free, C++ based framework provides a variety of functions related to particle physics and mathematics. Consequently, this requirement might become relevant in the future.

6. Minimum Performance:

Given that it has the same hardware setup and the same configuration parameters, TuxDAQ shall show at least the same DAQ performance as the APVDAQ readout application. In this context, DAQ performance can be measured in terms of the *effective event rate*<sup>44</sup>.

- 7. Maximum File Size:

- a) Any data output files produced by TuxDAQ shall not exceed a size of  $2\,\mathrm{GB}.$

- b) If more data is to be produced, several files of up to 2 GB shall be created (see Requirement 3.4.2/3).

- 8. System Evolution:

The software developer(s) of TuxDAQ shall take anticipated changes due to the evolution of the readout system into consideration. These changes are described in Sections 2.1.2 to 2.1.7.

<sup>&</sup>lt;sup>44</sup>Events captured per second

#### 3.4.10 Documentation

1. Application Programming Interface (API) Reference Manual:

In addition to this thesis, the developer(s) of TuxDAQ shall provide an API reference manual (with respect to Requirement 3.4.3/3), which serves as a detailed documentation of the TuxDAQ program source code. This improves maintainability.

2. Inline Source Code Comments:

The developer(s) of TuxDAQ shall document complex program artefacts with adequate inline source code comments. Consequently, successive programmers are provided with helpful information for maintenance or further development.

# 3.5 System Requirements Specification

System requirements build the baseline for system design, implementation and the creation of test cases. Compared to user requirements, they are "more detailed descriptions of the software system's functions, services and operational constraints" and "should define exactly what is to be implemented" [20].

A System Requirements Specification (SRS) would consist of a variety of system requirements. For the sake of compactness, only one example is presented. It demonstrates how a user requirement may expand to several verifiable system requirements. Fig 3.4 shows the system requirements derived from User Requirement 3.4.5/10.

#### System Requirements Specification

**Requirement 3.4.5/10-1:** During an active run, TuxDAQ shall present the consecutive number of the current event ( $n_{current\_event}$ ) on the PC screen within one DAQ interval after respective event data has been acquired from an FADC+PROC board and stored (if data storage was desired).

**Requirement 3.4.5/10-2:** If a maximum number of events  $(n_{max\_events})$  has been defined by the user and a run is currently active, TuxDAQ shall present the ratio  $n_{current\_event}/n_{max\_events}$  in measures of percent (accuracy: 1%) on the PC screen within one DAQ interval after the capture of the current event.

**Requirement 3.4.5/10-3:** If a maximum number of events  $(n_{max.events})$  has been defined by the user and a run is currently active, TuxDAQ shall provide an estimated time of run conclusion (system time, accuracy: 1 min) on the screen based on the consecutive number of the current event  $(n_{current.event})$ .

Figure 3.4: System Requirements Derived From User Requirement 3.4.5/10

Instead of a natural language specification of system requirements, other methods may be used, e.g. Requirements Diagrams and Tables of SysML<sup>45</sup>.

<sup>&</sup>lt;sup>45</sup>Defined by the Systems Modeling Language Specification 1.2, 2010 (Object Management Group)

# 4

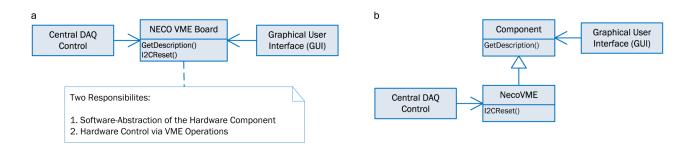

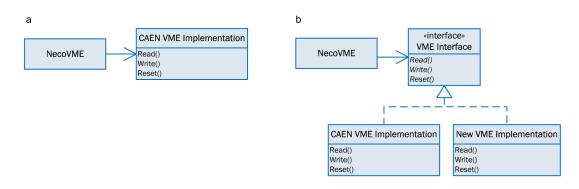

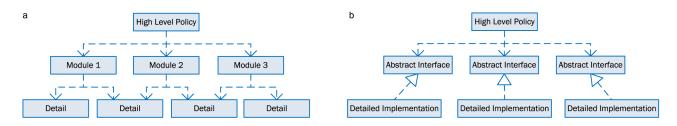

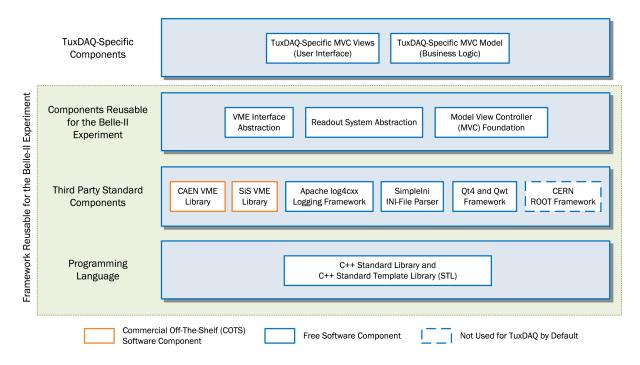

# Software Development Methodology