Die approbierte Originalversion dieser Dissertation ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

# DISSERTATION

# **Comprehensive Physical Modeling** of Hot-Carrier Induced Degradation

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik von

## Ivan Starkov

Quellenstrasse 171/27 A-1100 Wien, Österreich

Matrikelnummer 0828601 geboren am 30. März 1983 in Leningrad

Wien, im Januar 2013

# Kurzfassung

Transistoren fast aller Technologie-Knoten leiden unter Degradierung durch heiße Ladungsträger (HCD), die mit dem Aufbau von Defekten an oder nahe der Silizium/Siliziumdioxid-Grenzfläche verbunden ist. Dieses nachteilige Phänomen ist seit mehr als vier Jahrzehnten bekannt, seither sind zahlreiche Modellierungsversuche unternommen worden. Die Degradierung durch heiße Ladungsträger zu modellieren ist kompliziert, da diese drei verschiedene, aber stark verbundene Aspekte umfasst. Tatsächlich brechen die Ladungsträger, die mit der Si/SiO<sub>2</sub> Grenzfläche interagieren die Si-H Bindungen, wodurch Grenzflächendefekte generiert werden. Dementsprechend müssen die mikroskopischen Mechanismen für die Generierung von Defekten richtig beschrieben werden. Die Information darüber, wie effizient diese Ladungsträger den Bindungs-Dissoziations Prozess auslösen, erfolgt durch eine gründliche Ladungsträger-Transport-Behandlung. Weiters können jene generierten Defekte Ladungsträger einfangen, wodurch die Elektrostatik des Transistors verändert wird. Darüber hinaus wirken sie als zusätzliche Streuzentren und setzen die Ladungsträgerbeweglichkeit herab. Daher ist ein weiterer wichtiger Teilvorgang in dem heißen Ladungsträger-Degradierungs-Modellierungsparadigma die Simulation der Eigenschaften von degradierten Bauelementen. Aufgrund der komplizierten Natur fehlt noch immer ein umfassendes Physikalisches Modell, daher sind die meisten bestehenden Modelle empirisch.

Die Hauptaufgabe dieser Arbeit ist es, ein Physikalisches Modell für die Degradierung durch heiße Ladungsträger vorzuschlagen, welches in der Lage ist, diese Degradierung in Metall-Oxid-Halbleiter Feldeffekttransistoren (MOSFET) mit unterschiedlichen Kanallängen unter Verwendung eines einzigen Satzes von physikalischen Parametern zu beschreiben. Der entwickelte Ansatz berücksichtigt nicht nur die Schäden, die durch Kanal-Elektronen erzeugt werden, sondern auch die Schäden durch Stoßionisation sekundär produzierter Kanal-Löcher. Obwohl der Beitrag der Löcher zu der gesamten Defektgenerierung im Vergleich zu den Elektronen kleiner ist, ist ihr Einfluss auf den linearen Transistor-Strom vergleichbar mit dem der Elektronen. Der Grund für diesen Trend sind durch Löcher erzeugte Defekte nahe dem Drain-Anschluss, wodurch das elektrische Verhalten des Bauelementes stärker beeinflusst wird.

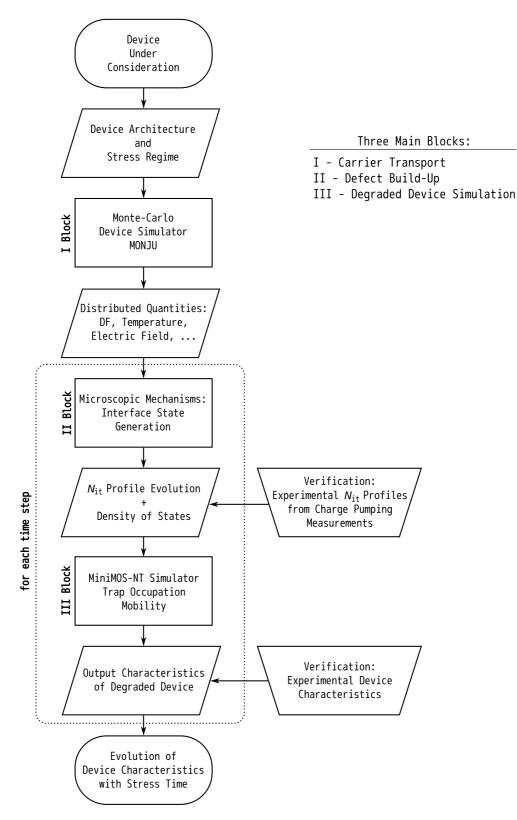

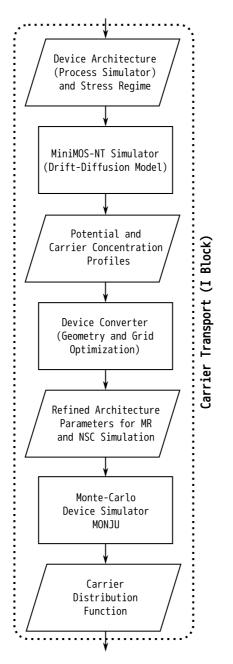

Das Modell umfasst drei Hauptkomponenten: ein Ladungsträger-Transport-Modul, ein Modul zur Modellierung der mikroskopischen Mechanismen der Defekt-Generierung und ein Modul für die Simulation der Eigenschaften degradierter Bauelemente. Das Ladungsträger-Transport-Modul berechnet eine Reihe von Ladungsträgerenergie Verteilungsfunktionen (DF) an einer beliebigen Position in dem MOSFET für eine bestimmte Bauelemente Architektur und für bestimmte Stress/Betriebsbedingungen. Für die Berechnung der DF wird der Vollband-Monte Carlo (MC) Bauelemente Simulator MONJU eingesetzt. Anschließend wird die Information über die Ladungsträger DF verwendet, um für jeden Stress Zeitpunkt Grenzflächenzustandsdichte-Lateral-Profile zu erzeugen. Diese Profile werden dann in den Schaltungs-und Bauelementsimulator MiniMOS-NT geladen, welcher die elektrischen Charakteristiken des degradierten Bauelementes berechnet. Da die MC Methode sehr zeitaufwendig ist, wird der Ansatz verfolgt, das genaue Ladungsträgertransport-Modul durch eine vereinfachte Behandlung zu ersetzen, welches bedeutet, dass ein Vergleich zwischen den verschiedenen Implementierungen des Ladungsträgertransport Moduls des Modells durchgeführt wird. Hierfür werden Monte-Carlo, Hydrodynamische (HD) und Drift-Diffusions (DD) Ansätze für die Lösung der Boltzmann Transportgleichung angewandt. Eine Diskrepanz zwischen experimentellen Ergebnissen und Simulationen, die unter Einsatz dieses vereinfachten Ansatzes eingetreten ist, wird aufgezeigt und erklärt.

Wie bereits erwähnt, umfasst das entwickelte Physikalische Modell für HCD drei Hauptmodule. Jedes Modul basiert auf bestimmten Annahmen, die als potenzielle Fehlerquellen fungieren, und beinhaltet eine bestimmte Anzahl von anzupassenden Parametern. Mit anderen Worten, aufgrund der komplizierten Struktur des Modells, sollten mögliche Fehler durch geeignete Auswertung der Schnittstellen zwischen den Modulen überprüft werden. Obwohl eine gute Darstellung der degradierten Bauelementeeigenschaften erreicht werden könnte, wird im folgenden versucht, das mikroskopische Modell des Defektaufbaus zu überprüfen, indem man die Technik des Ladungspumpen (CP) für eine bestimmte Bauelemente Architektur anwendet und mit dem Modell vergleicht. Es ist zu betonen, dass die Algorithmen für die Extraktion von den Grenzflächenzustandsprofilen, in Abhängigkeit von der Position entlang der Bauelemente Grenzfläche aus den CP Daten, auf bestimmten Annahmen basieren und somit auch potenziell ungenau sein können. Darüber hinaus werden eine umfassende Analyse und ein Vergleich der einzelnen Extraktionstechniken, mit deren Hilfe die räumliche Verteilung der durch heiße Ladungsträger induzierten Grenzflächen- und Oxiddefekte bestimmt wird, durchgeführt. Die Vorteile und Grenzen der Charakterisierungsalgorithmen, verbessert durch ein neues einfaches, kompaktes Modell für die lokale Oxidkapazität, werden diskutiert. Es wird gezeigt, dass durch Ignorieren der räumlichen Veränderung der Oxidkapazität ein falsches Ergebnis erzeugt wird, welches zu einer mehrdeutigen Interpretation von HCD führt. Daher wird eine behutsame Gewinnung des anfänglichen Grenzflächenzustandsdichte-Profils für einen vorgestressten MOSFET vorgenommen. Die Auswirkung der bereits vorhandenen Bauelemente Grenzflächenzustände auf die nachfolgenden Grenzflächen-Defektprofile wird im Rahmen der prädiktiven HCD Modellierung aufgezeigt. Ein gründlicher Vergleich zwischen simulierten Grenzflächenzustandsprofilen und solchen, die aus CP Daten extrahiert wurden, wird durchgeführt.

Basierend auf einer rigorosen TCAD Version eines Physikalische Modells für HCD wird ein analytisches Modell, das sich in geeigneter Weise dem Träger-Beschleunigungs-Integral (AI) nähert, entwickelt. Unter Verwendung eines solchen Ansatzes ist man in der Lage, die Degradierung des linearen Transistor-Stroms zu repräsentieren. Einer der wichtigsten Vorteile dieses analytischen Ansatzes ist, dass dieser auf einem Physikalische TCAD-Modell, anstatt auf einer empirischen Anpassung zu experimentellen Daten, beruht. Das Modell stellt auch die bei relativ langen Stresszeiten beobachtete Sättigung der HCD dar. Die Flexibilität des resultierenden Ausdrucks ermöglicht es, diesen Ansatz zu verwenden, während man die Auswirkungen von schwankenden Parametern der Bauelemente Topologie auf HCD berücksichtigt. In diesem Fall führt das zeitaufwendige MC basierte Transport-Modul zu extrem hohem Rechenaufwand.

# Abstract

Transistors of nearly all technology nodes suffer from hot-carrier degradation (HCD) which is associated with the buildup of defects at or near the silicon/silicon dioxide interface. This detrimental phenomenon has been known for more than four decades and numerous modeling attempts have been undertaken. However, hot-carrier degradation is rather complicated to model because it includes three different but strongly connected aspects. In fact, carriers interacting with the Si/SiO<sub>2</sub> interface break Si – H bonds, thereby generating traps and thus the microscopic mechanisms for defect creation must be properly described. The information on how efficiently these carriers trigger the bond dissociation process is provided by a thorough carrier transport treatment. Furthermore, these generated traps can capture carriers and thus distort the electrostatics of the transistor and degrade the carrier mobility. Due to the complicated nature, a comprehensive physics-based model is still missing and most existing HCD models are empirical.

The main task of this work is to design a physics-based model for hot-carrier degradation, which is able to represent HCD observed in metal-oxide-semiconductor field-effect-transistors (MOS-FETs) with different channel length using a single set of physical parameters. The developed approach considers not only the damage produced by channel electrons but also by secondary channel holes generated by impact ionization. Although the contribution of the holes to the total defect creation is smaller compared to that of electrons, their impact on the linear drain current is comparable with the electron one. The reason behind this trend is that hole-induced traps are shifted towards the source, thereby more severely affecting the device behavior.

The model includes three main modules: a carrier transport module, a module for modeling of microscopic mechanisms of defect creation and a module for the simulation of the characteristics of degraded devices. The carrier transport module calculates a set of carrier energy distribution functions (DFs) at any position in the MOSFET for a particular device architecture and stress/operating conditions. For DF calculation a full-band Monte Carlo (MC) device simulator MONJU is employed. Then the information regarding the carrier DF is used to generate interface state density profiles. These profiles are loaded into a circuit and device simulator MiniMOS-NT, which calculates the characteristics of the degraded device. Since the MC method is very time-consuming the precise carrier transport module is substituted by a simplified treatment, i.e. a comparison between different realizations of the model carrier transport module is carried out. Namely Monte Carlo, hydrodynamic (HD) and drift-diffusion (DD) schemes for the solution of the Boltzmann transport equation are employed. A discrepancy between experimental results and simulations, which occurred while employing this simplified approach, is shown and explained.

As previously stated, the developed physics-based model for HCD includes three main modules. Each module is based on some assumptions acting as potential sources of error and includes a certain number of fitting parameters. In other words, due to the complicated structure of the model, these errors should be screened by properly evaluating the interfaces between the modules. Therefore, although a good representation of the degraded device characteristics could be achieved, one attempts to verify the microscopic model for the defect build-up in the following by employing the charge pumping (CP) technique for a particular device architecture. It is worth emphasizing that the algorithms for the extraction of the interface state profiles versus position along the device interface from the CP data are based on some assumptions and thus could be potentially inaccurate as well. Therefore, an exhaustive analysis and comparison of extraction techniques of the hot-carrier induced interface and oxide trap spatial distributions is performed. The advantages and limitations of the characterization algorithms improved by a new simple compact model for local oxide capacitance are discussed. It is demonstrated that by ignoring the spatial variation of oxide capacitance, a spurious result is produced, leading to an ambiguous picture of HCD. Additionally, a careful extraction of the initial interface state density profile for a pre-stressed MOSFET is undertaken. The impact of pre-existing interface states on the subsequent interface trap profile evolution is demonstrated in the context of predictive HCD modeling. A thorough comparison between simulated interface state profiles and those extracted from CP data is carried out.

Based on a rigorous technology computer-aided design (TCAD) version of a physics-based model for HCD, an analytical model, which suitably approximates the carrier acceleration integrals (AIs), is developed. Using such an approach one is able to represent the linear drain current degradation. One of the main advantages of this analytical approach is that it is based on a physics-based TCAD model rather than on an empirical fit to experimental data. The model also represents the saturation of HCD observed at relatively long stress times. The flexibility of the resulting expression allows us to employ this approach while considering the impact of fluctuating parameters of device topology on HCD. In this case the time-consuming MC based transport module would otherwise lead to extremely high computational costs. Education is a weapon whose effects depend on who holds it in his hands and at whom it is aimed. Iosif Dzhugashvili, Interview with H. G. Wells (September 1937)

# Contents

| Kurzfassung ii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|

| Abstract iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |  |  |  |

| Contents vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ii                 |  |  |  |

| List of Figures is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | x                  |  |  |  |

| List of Tables xiv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | v                  |  |  |  |

| List of Abbreviations xv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | v                  |  |  |  |

| List of Symbols xv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | /i                 |  |  |  |

| 1.1       Historical Background       1         1.2       Main Physics-Based Concepts for HCD Modeling       2         1.3       Characteristic Features of HCD       2         1.3       Characteristic Features of HCD Mechanisms       2         1.3.1       Different Nature of HCD Mechanisms       2         1.3.2       HCD in High-Voltage Devices       2         1.3.3       HCD in Scaled Devices       2         1.3.4       Strong Localization       2         1.3.5       Interface, Border and Oxide Traps       2         1.3.6       Temperature Behavior       2         1.4       Analysis and Comparison of Existing Physics-Based HCD Models       2 | $3 \\ 6 \\ 7$      |  |  |  |

| 2       Carrier Transport       24         2.1       Boltzmann's Transport Equation       24         2.2       Hydrodynamic Transport Model       25         2.3       Drift-Diffusion Transport Model       26         2.4       Monte Carlo Method       27         2.4.1       Multiple Refresh       27                                                                                                                                                                                                                                                                                                                                                                | $4 \\ 5 \\ 6 \\ 7$ |  |  |  |

|                   | $2.5 \\ 2.6$ | 2.4.2       Non-Self-Consistent Simulation                                                                                    | 28<br>29<br>31 |  |

|-------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------|----------------|--|

| 3 Defect Creation |              |                                                                                                                               |                |  |

|                   | 3.1          | Microscopic Model for Interface State Creation                                                                                | 34             |  |

|                   | 3.2          | Secondary Generated Carriers as a Crucial Component for Modeling of HCD $$                                                    | 40             |  |

|                   | 3.3          | Analysis of Worst-Case HCD Conditions in the Case of n- and p-channel MOSFETs                                                 | 43             |  |

|                   |              | 3.3.1 WCC of Long-Channel Devices                                                                                             | 44             |  |

|                   |              | 3.3.2 WCC of High-Voltage Devices                                                                                             | 47             |  |

|                   | 3.4          | Impact of the Carrier Distribution Function on HCD Modeling                                                                   | 47             |  |

|                   |              | 3.4.1 Comparison of Different Transport Module Realizations                                                                   | 49             |  |

|                   |              | 3.4.2 Analysis of WCC within Simplified Transport Schemes                                                                     | 50             |  |

| 4                 | The          | Charge-Pumping Technique                                                                                                      | 53             |  |

|                   | 4.1          | Basic Principles of Charge Pumping Measurements                                                                               | 53             |  |

|                   |              | 4.1.1 Local Threshold and Flatband Voltages                                                                                   | 54             |  |

|                   |              | 4.1.2 Effective Channel Length                                                                                                | 56             |  |

|                   | 4.2          | Interface State Density Profile of Unstressed Device                                                                          | 57             |  |

|                   |              | 4.2.1 Verification of the Interface State Density Distribution Uniformity $\ldots$                                            | 57             |  |

|                   |              | 4.2.2 Interface State Profile of an Unstressed Device                                                                         | 60             |  |

|                   | 4.9          | 4.2.3 Impact of Pre-stressed Interface State Density Profile on HCD Modeling .                                                | 61             |  |

|                   | 4.3          | Charge-Pumping Extraction Techniques for the Hot-Carrier Induced Interface<br>and Oxide Trap Spatial Distributions in MOSFETs | 62             |  |

|                   |              | 4.3.1 Local Oxide Capacitance                                                                                                 | 65             |  |

|                   |              | 4.3.2 Comparison of Interface State Profiles Extracted with Different Capaci-                                                 |                |  |

|                   |              | tance Approaches                                                                                                              | 69             |  |

|                   | 4.4          | 4.3.3 Extraction Techniques Description                                                                                       | 70             |  |

|                   | 1.1          | Hot-Carrier Stress                                                                                                            | 74             |  |

|                   | 4.5          | HCD Caused Interface State Profile – Simulations vs. Experiment                                                               | 77             |  |

| 5                 | Ana          | lytic Modeling Approach for HCD                                                                                               | 82             |  |

|                   | 5.1          | An Analytical Approach for Physical Modeling of HC Induced Degradation $\ . \ .$                                              | 82             |  |

|                   | 5.2          | Impact of Gate Oxide Thickness Variations on HCD                                                                              | 88             |  |

| 6                 | Sum          | mary and Outlook                                                                                                              | 93             |  |

| Bil               | oliogr       | aphy                                                                                                                          | 96             |  |

| Ov                | vn Pı        | ublications                                                                                                                   | 111            |  |

# List of Figures

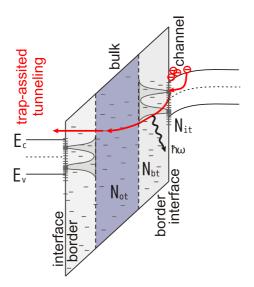

| 1.1  | Interface, border and oxide bulk traps. Trap-assisted tunneling is represented by                                   |    |

|------|---------------------------------------------------------------------------------------------------------------------|----|

|      | red arrows.                                                                                                         | 7  |

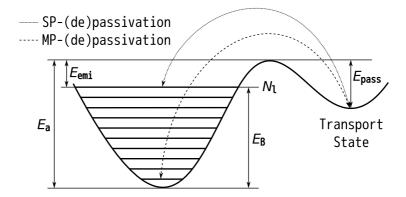

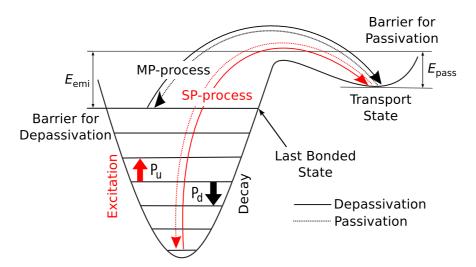

| 1.2  | Two competing processes of Si – H bond-breakage: the single- and multiple-                                          |    |

|      | carrier mechanisms. The bond is interpreted as a truncated harmonic oscillator.                                     | 9  |

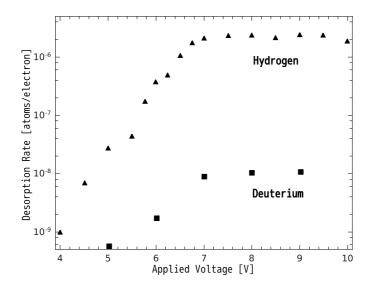

| 1.3  | Disparity between H and D desorption rates induced by electrons tunneling from                                      |    |

|      | the STM tip on the passivated Si surface (data from [140])                                                          | 10 |

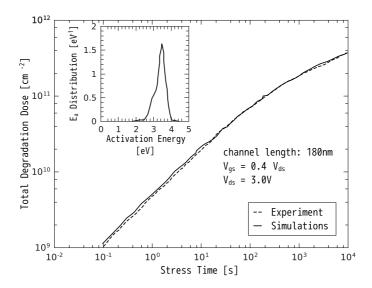

| 1.4  | The total degradation dose (cumulative $N_{\rm it}$ ) as a function of stress time: experi-                         |    |

|      | ment vs. theory obtained for a 180nm device under worst-case stress conditions,                                     |    |

|      | i.e. $V_{\rm gs} = 0.4 V_{\rm ds}$ . Inset: distribution of Si – H bond-breakage activation energy.                 |    |

|      | The data are borrowed from [24].                                                                                    | 12 |

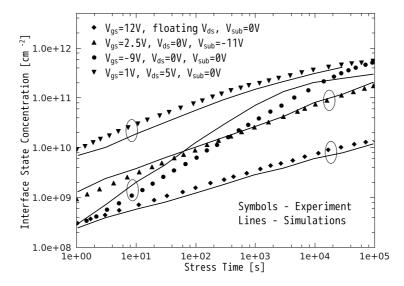

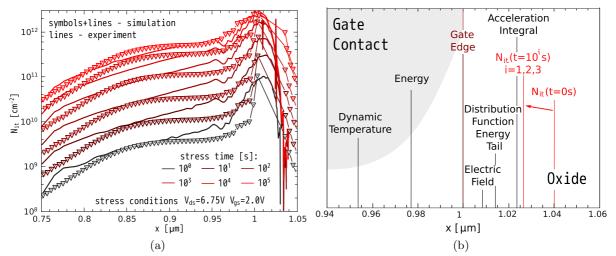

| 1.5  | The interface state concentration $N_{\rm it}$ , simulation vs. experiment. An n-MOSFET                             |    |

|      | with a gate length of $0.35\mu$ m and an oxide thickness of 6.5nm was subjected                                     |    |

|      | to hot-carrier stress at (1): $V_{\rm gs} = -9V$ , $V_{\rm ds} = V_{\rm sub} = 0V$ ( $V_{\rm sub}$ is the substrate |    |

|      | voltage); (2): $V_{gs} = 12V$ , $V_{sub} = 0V$ and floating source and drain; (3): $V_{gs} = 1V$ ,                  |    |

|      | $V_{\rm ds} = 0V, V_{\rm sub} = -11V;$ (4): $V_{\rm gs} = 2.5V, V_{\rm ds} = 5V, V_{\rm sub} = 0V.$ Data from [25]. | 14 |

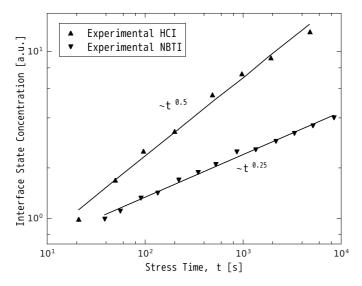

| 1.6  | Different time slopes of hot-carrier induced degradation and NBTI. The data are                                     |    |

|      | borrowed from [26]                                                                                                  | 15 |

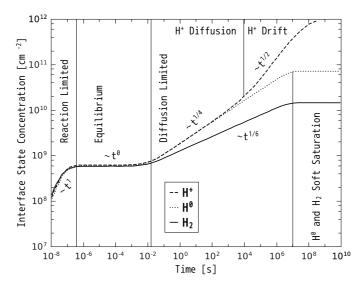

| 1.7  | The main phases of the reaction-diffusion model applied to NBTI with different                                      |    |

|      | time slopes being marked. Data from [150]                                                                           | 16 |

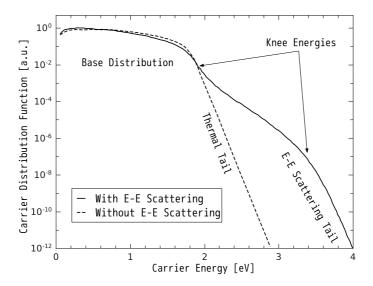

| 1.8  | The impact of electron-electron scattering on the shape of the carrier energy                                       |    |

|      | distribution function. In the former case an additional hump in the distribution                                    |    |

|      | function high-energy tail appears. Data from [29].                                                                  | 17 |

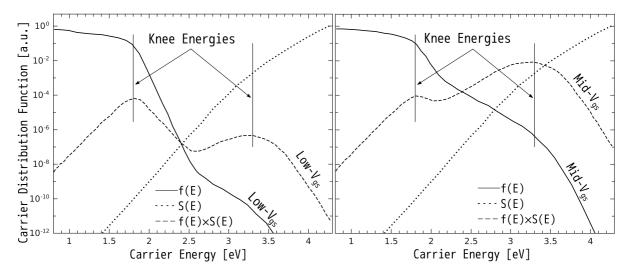

| 1.9  | Schematic representation of the energy-driven paradigm. Knee energies shift de-                                     |    |

|      | pending on the applied voltage (the data borrowed from [29])                                                        | 18 |

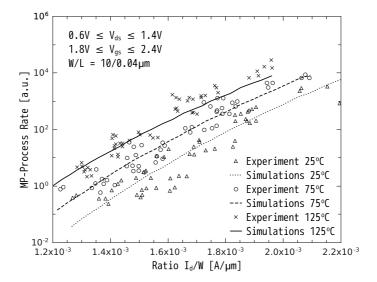

| 1.10 | Experimental bond dissociation rate for the multiple-particle process vs. the the-                                  |    |

|      | oretical one. The information about stress conditions is shown on the canvas.                                       |    |

|      | The data are borrowed from [31].                                                                                    | 20 |

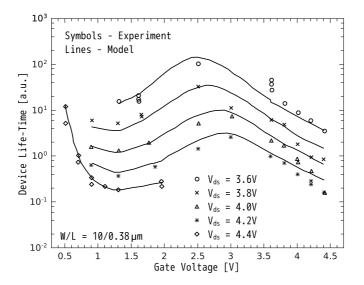

| 1.11 | Comparison between the experimental device life-time and that calculated within                                     |    |

|      | the Bravaix framework (for devices fabricated in a 65nm node). The data are                                         |    |

|      | taken from $[18]$ .                                                                                                 | 21 |

| 1.12 | The flowchart of the proposed model for hot-carrier degradation depicting three                                     |    |

|      | main modules: carrier transport module, module for microscopic mechanisms for                                       |    |

|      | defect creation, and module for simulations of the degraded devices                                                 | 22 |

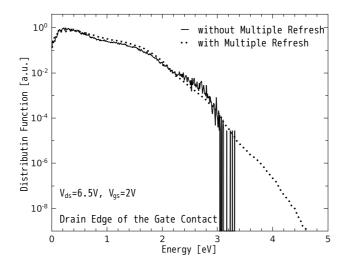

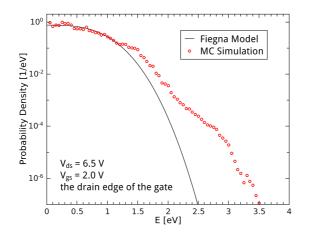

| 2.1          | The electron distribution function for n-type MOSFET at $V_{\rm ds} = 6.5$ V and $V_{\rm gs} = 2$ V simulated with and without Multiple Refresh for the same computational time.                                                                                                                                                                                   |    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|              | Graph is taken for room temperature and corresponds to the drain edge of the                                                                                                                                                                                                                                                                                       |    |

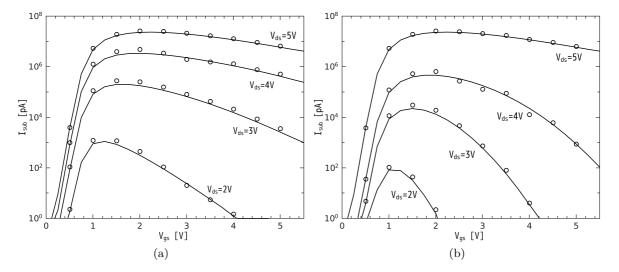

| 2.2          | gate contact                                                                                                                                                                                                                                                                                                                                                       | 28 |

|              | current of n-type MOSFET with a gate length $0.5\mu$ m (a) and $2.0\mu$ m (b) for<br>the series of the drain-source voltage $V_{\rm ds} = 2.0, 3.0, 4.0, 5.0$ V                                                                                                                                                                                                    | 29 |

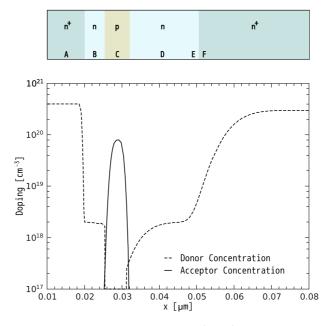

| 2.3          | Schematic representation of the considered $n^+ p n^+$ structure (above) and 1D doping profile (below).                                                                                                                                                                                                                                                            | 30 |

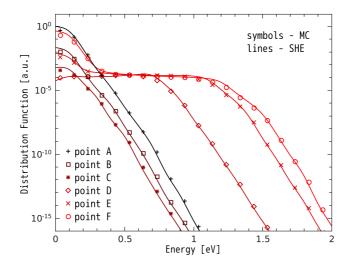

| 2.4          | doping profile (below)                                                                                                                                                                                                                                                                                                                                             | 30 |

|              | simulation schemes.                                                                                                                                                                                                                                                                                                                                                | 31 |

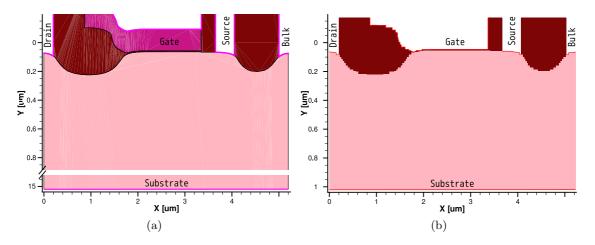

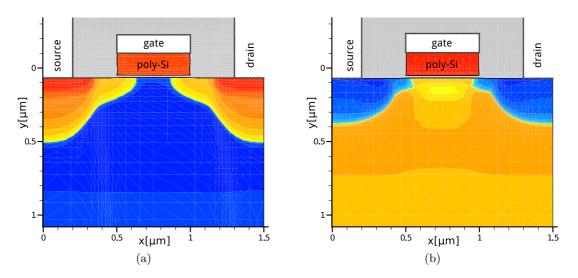

| $2.5 \\ 2.6$ | The simulation flowchart for the carrier transport block of developed HCD model.<br>The cross section of the high voltage n-type LDMOS transistor (a) before and (b)                                                                                                                                                                                               | 32 |

|              | after the conversion procedure                                                                                                                                                                                                                                                                                                                                     | 33 |

| 3.1          | Schematic representation of the SP- and MP-processes                                                                                                                                                                                                                                                                                                               | 35 |

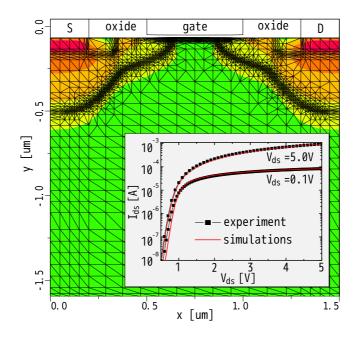

| 3.2          | The topology of an n-MOSFET with the donor doping profile represented by the color map. The origin of the lateral coordinate corresponds to the beginning of                                                                                                                                                                                                       |    |

|              | the source. Inset: experimental $I_{\rm ds}$ - $V_{\rm ds}$ curves vs. simulated ones                                                                                                                                                                                                                                                                              | 38 |

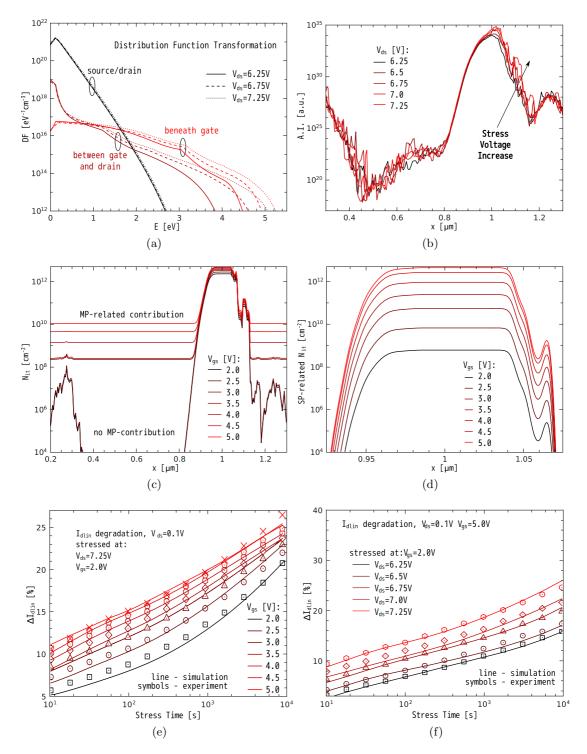

| 3.3          | Evolution of crucial characteristics of the degradation with the lateral coordinate:<br>(a) carrier distribution function along the interface; (b) the carrier acceleration<br>integral featuring a peak near the position of most prolonged high-energy tails of<br>the distribution function; (c) the total interface charge density $N_{\rm it}$ and (d) stored |    |

|              | on the SP-related traps $N_{\rm MP}$ in the region where the AI peaks. $I_{\rm dlin}$ degradation<br>for (e) different operation $V_{\rm gs}$ and fixed stress conditions $V_{\rm gs} = 2.0$ V, $V_{\rm ds} = 7.25$ V                                                                                                                                              |    |

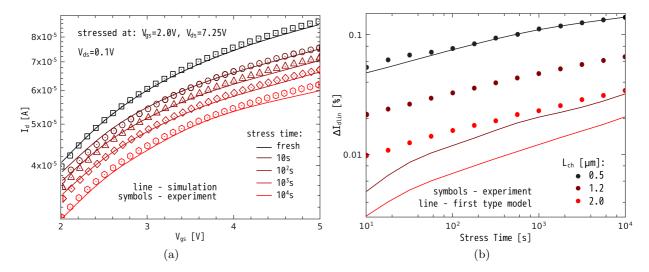

| 3.4          | and for (f) different stress $V_{\rm ds}$ and fixed operation $V_{\rm ds} = 0.1 \text{V}$ , $V_{\rm ds} = 1.26 \text{V}$<br>(a) The transformation of the transfer characteristics during stress: experiment                                                                                                                                                       | 39 |

| 0.4          | (symbols) vs. theory (lines). (b) The degradation of the $I_{\rm dlin}$ current predicted                                                                                                                                                                                                                                                                          | 10 |

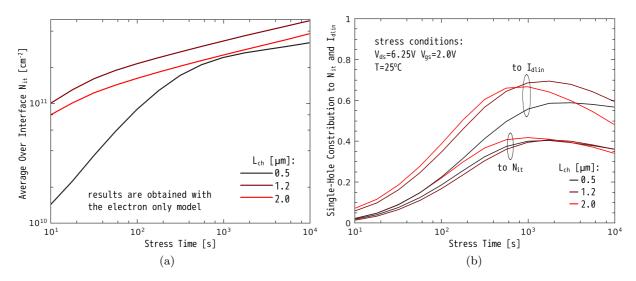

| 3.5          | by the electron-only HCD model for different channel lengths                                                                                                                                                                                                                                                                                                       | 40 |

|              | ponent into the total $I_{\text{dlin}}$ change and to the total $N_{\text{it}}$ .                                                                                                                                                                                                                                                                                  | 41 |

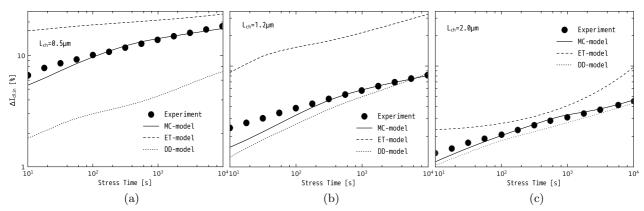

| 3.6          | The relative $I_{\text{dlin}}$ change vs. time: experiment, simulations and contributions of                                                                                                                                                                                                                                                                       |    |

|              | electrons and holes separately for channel lengths of (a) 0.5, (b) 1.2 and (c) $2.0\mu$ m.                                                                                                                                                                                                                                                                         | 42 |

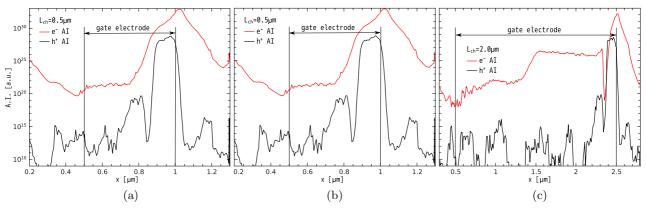

| 3.7          | The acceleration integrals for electrons and holes for the case of $L_{\rm ch}$ = 0.5, 1.2                                                                                                                                                                                                                                                                         |    |

| 9.0          | and $2.0 \mu\text{m}$ .                                                                                                                                                                                                                                                                                                                                            | 42 |

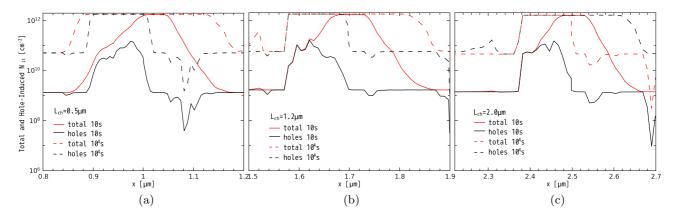

| 3.8          | The total $N_{it}$ profile and that induced only by holes for 10s and 10 <sup>4</sup> s and for three different channel lengths.                                                                                                                                                                                                                                   | 43 |

| 3.9          | The topology of 5V (a) n-MOSFET and (b) p-MOSFET with the net doping profile highlighted.                                                                                                                                                                                                                                                                          | 44 |

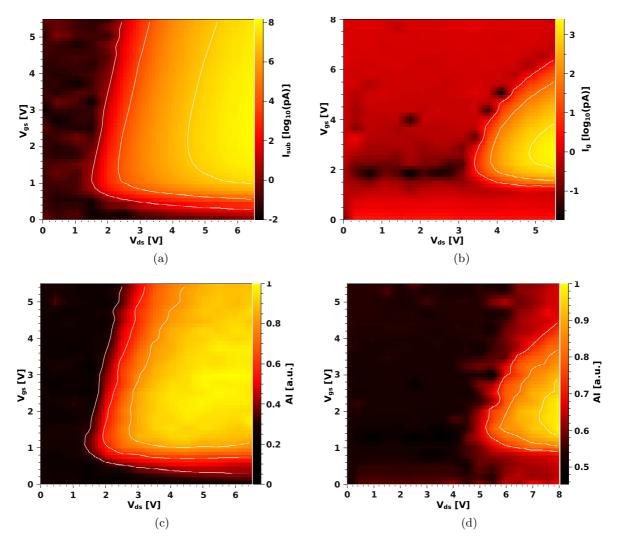

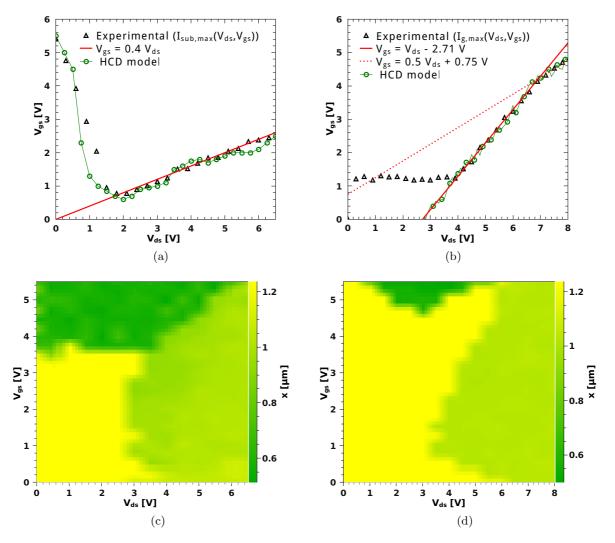

| 3.10                                                                                     | Experimental (a) $I_{sub}$ and (b) $I_{g}$ as a function of $V_{gs}$ and $V_{ds}$ for the n- and p-<br>MOSFET, respectively. Maximum value of the acceleration integral as a function                                                                                                                                                                                                                                            |                            |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|                                                                                          | of $V_{\rm gs}$ and $V_{\rm ds}$ for (c) n- and (d) p-MOSFET.                                                                                                                                                                                                                                                                                                                                                                    | 45                         |

| 3.11                                                                                     | The interrelation between $V_{\rm gs}$ and $V_{\rm ds}$ corresponding to the WCC of (a) n- and                                                                                                                                                                                                                                                                                                                                   |                            |

|                                                                                          | (b) p-MOSFET. The position of the maximum acceleration integral as a function                                                                                                                                                                                                                                                                                                                                                    |                            |

|                                                                                          | of $V_{\rm gs}$ and $V_{\rm ds}$ for (c) n- and (d) p-MOSFET.                                                                                                                                                                                                                                                                                                                                                                    | 46                         |

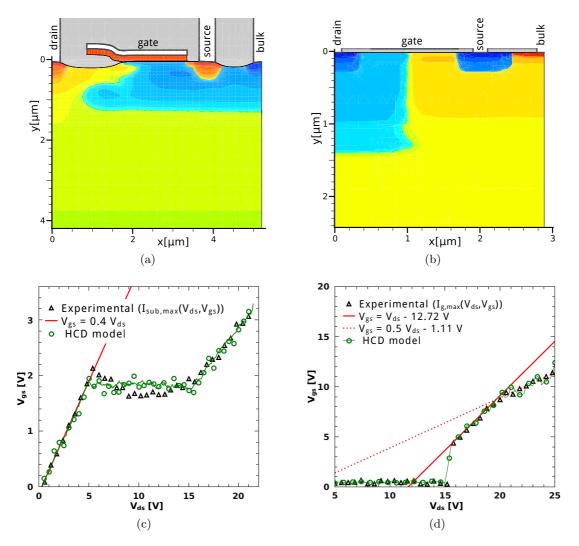

| 3.12                                                                                     | The topology of HV (a) n- and (b) p-LDMOS with the net doping profile high-                                                                                                                                                                                                                                                                                                                                                      |                            |

|                                                                                          | lighted. The interrelation between $V_{\rm gs}$ and $V_{\rm ds}$ corresponding to the WCC of (c)                                                                                                                                                                                                                                                                                                                                 |                            |

|                                                                                          | n-MOSFET and (d) p-MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                       | 48                         |

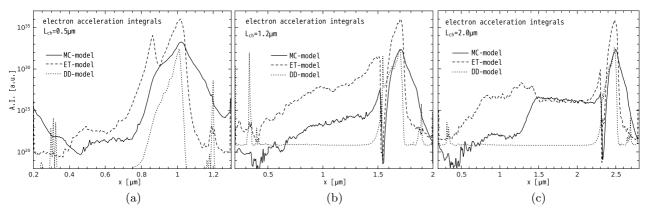

| 3.13                                                                                     | The electron acceleration integral calculated with with Monte Carlo, Hydrody-                                                                                                                                                                                                                                                                                                                                                    |                            |

|                                                                                          | namic, and Drift-Diffusion based versions of the HCD model for the case of (a)                                                                                                                                                                                                                                                                                                                                                   |                            |

|                                                                                          | $L_{\rm ch} = 0.5 \mu {\rm m}$ , (b) $L_{\rm ch} = 1.2 \mu {\rm m}$ and (c) $L_{\rm ch} = 2.0 \mu {\rm m}$ .                                                                                                                                                                                                                                                                                                                     | 49                         |

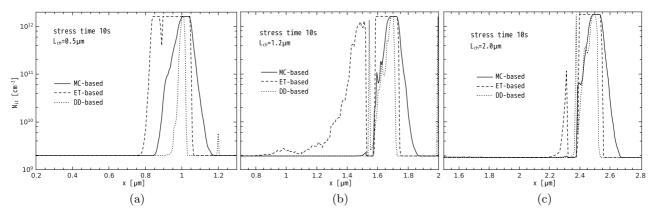

| 3.14                                                                                     | The simulated $N_{it}(x)$ profiles obtained with Monte Carlo, Hydrodynamic, and                                                                                                                                                                                                                                                                                                                                                  |                            |

|                                                                                          | Drift-Diffusion based versions of the proposed HCD model for the case of (a)                                                                                                                                                                                                                                                                                                                                                     |                            |

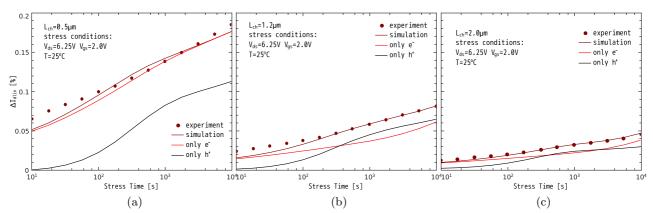

|                                                                                          | $L_{\rm ch} = 0.5 \mu {\rm m}$ , (b) $L_{\rm ch} = 1.2 \mu {\rm m}$ and (c) $L_{\rm ch} = 2.0 \mu {\rm m}$ .                                                                                                                                                                                                                                                                                                                     | 50                         |

| 3.15                                                                                     | The linear drain current degradation: experiment vs. simulations. The case of                                                                                                                                                                                                                                                                                                                                                    |                            |

|                                                                                          | (a) $L_{\rm ch} = 0.5 \mu {\rm m}$ , (b) $L_{\rm ch} = 1.2 \mu {\rm m}$ and (c) $L_{\rm ch} = 2.0 \mu {\rm m}$ .                                                                                                                                                                                                                                                                                                                 | 50                         |

| 3.16                                                                                     | The carrier distribution function: the result of Monte-Carlo simulations and its                                                                                                                                                                                                                                                                                                                                                 |                            |

|                                                                                          | fitting with the Fiegna model for a long-channel 5V n-type MOSFET                                                                                                                                                                                                                                                                                                                                                                | 51                         |

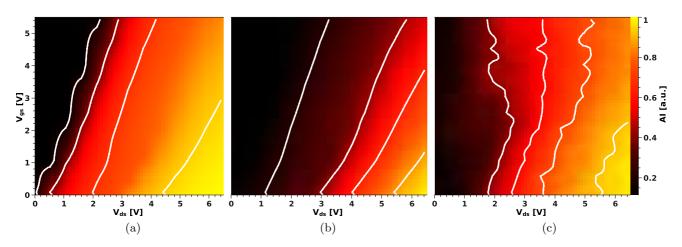

| 3.17                                                                                     | The maximum value of the acceleration integral as a function of $\{V_{\rm ds}, V_{\rm gs}\}$ calcu-                                                                                                                                                                                                                                                                                                                              |                            |

|                                                                                          | lated with the (a) Fiegna, (b) drift-diffusion and (c) hydrodynamic models                                                                                                                                                                                                                                                                                                                                                       | 52                         |

|                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |

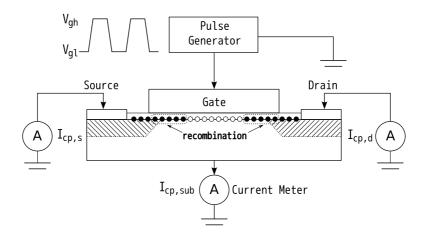

| 11                                                                                       | Basic experimental setup for charge-pumping measurements                                                                                                                                                                                                                                                                                                                                                                         | 54                         |

| 4.1                                                                                      | Basic experimental setup for charge-pumping measurements                                                                                                                                                                                                                                                                                                                                                                         | 54                         |

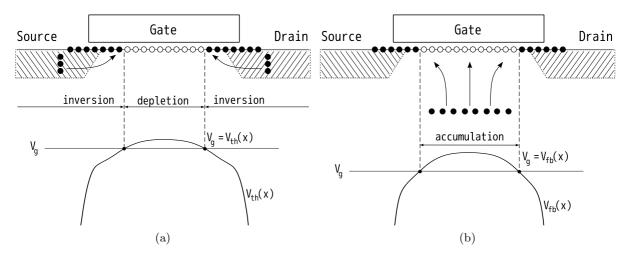

| 4.1<br>4.2                                                                               | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage                                                                                                                                                                                                                                                                                                                                         |                            |

| 4.2                                                                                      | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards                                                                                                                                                                                                                                                         | 54<br>54                   |

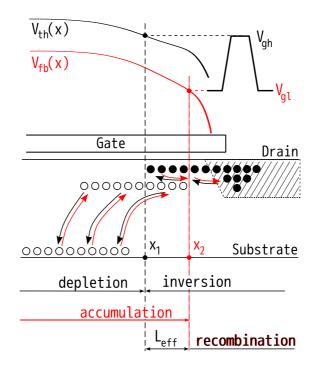

|                                                                                          | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$                                                                                                                                                       |                            |

| 4.2                                                                                      | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons                                                   | 54                         |

| 4.2<br>4.3                                                                               | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$    |                            |

| 4.2                                                                                      | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$    | 54                         |

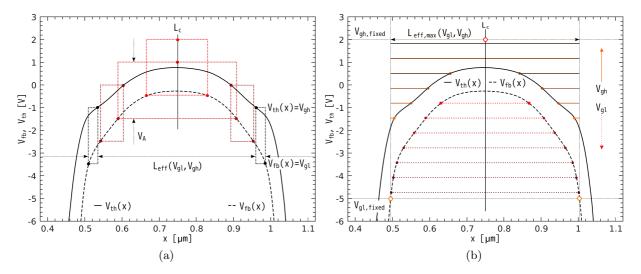

| 4.2<br>4.3                                                                               | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards<br>The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$ | 54<br>55                   |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                            | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$    | 54                         |

| 4.2<br>4.3                                                                               | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$    | 54<br>55<br>56             |

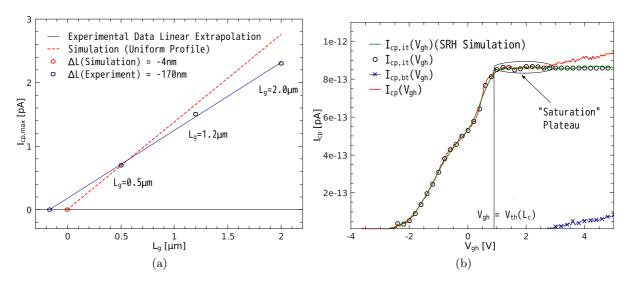

| <ul><li>4.2</li><li>4.3</li><li>4.4</li><li>4.5</li></ul>                                | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$    | 54<br>55                   |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                            | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$    | 54<br>55<br>56             |

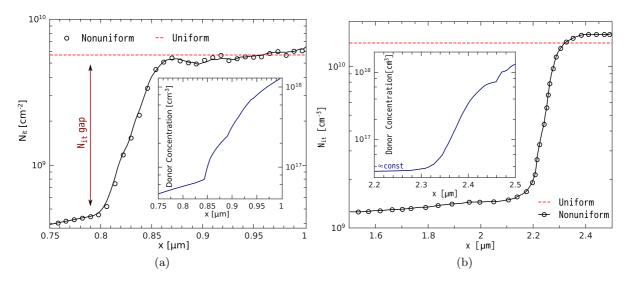

| <ul><li>4.2</li><li>4.3</li><li>4.4</li><li>4.5</li></ul>                                | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$    | 54<br>55<br>56<br>58       |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>              | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$    | 54<br>55<br>56             |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li><li>4.5</li></ul>                                | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$    | 54<br>55<br>56<br>58<br>59 |

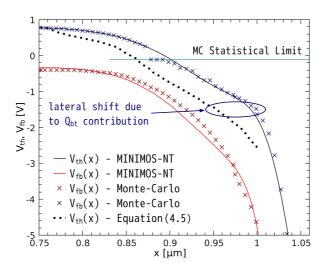

| <ol> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ol> | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$    | 54<br>55<br>56<br>58       |

| <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>              | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$    | 54<br>55<br>56<br>58<br>59 |

| <ol> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ol> | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$    | 54<br>55<br>56<br>58<br>59 |

| <ol> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ol> | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$    | 54<br>55<br>56<br>58<br>59 |

| <ol> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ol> | Definition of (a) local threshold voltage $V_{\rm th}(x)$ and (b) local flatband voltage $V_{\rm fb}(x)$ for nMOSFET. The positive direction of voltage points downwards The response of the free carriers to the applied periodic gate pulse. At $V_{\rm g} = V_{\rm gh}$ electrons flood into $x_1$ and holes return to the substrate. At $V_{\rm g} = V_{\rm gl}$ electrons return to the drain and holes flood into $x_2$    | 54<br>55<br>56<br>58<br>59 |

| 4.9  | (a) Interface state density profile evolution calculated with developed HCD model                                     |     |

|------|-----------------------------------------------------------------------------------------------------------------------|-----|

|      | under assumption of a uniform initial profile and employing $N_{\rm it}(x)$ extracted ac-                             |     |

|      | cording to the proposed scheme. (b) Comparison of the $I_{\rm dlin}$ degradation calcu-                               |     |

|      | lated with MiniMOS-NT using obtained $N_{\rm it}(x)$ profiles (a) as input degradation                                |     |

|      | characteristics.                                                                                                      | 62  |

| 4.10 | Time evolution of the measured charge-pumping current during hot-carrier stress                                       |     |

|      | using the varying high/low-level charge-pumping technique                                                             | 64  |

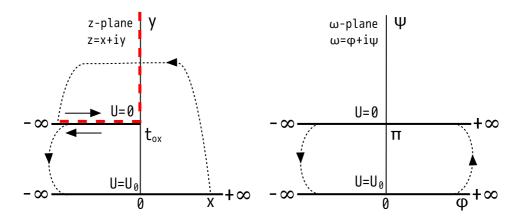

| 4.11 | The conformal transformation used to solve the gate/drain fringing problem. The                                       |     |

|      | complicated case of the corner gate form (red dashed line) is reduced to a ray. $\ .$                                 | 66  |

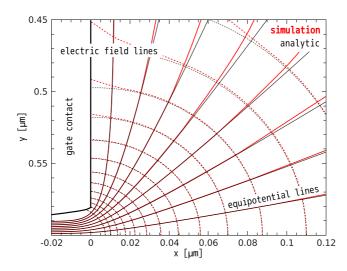

| 4.12 | The comparison of equipotential and field-lines in the oxide near the gate corner as                                  |     |

|      | the analytical solution and simulated by means of device simulator MiniMOS-NT.                                        | 66  |

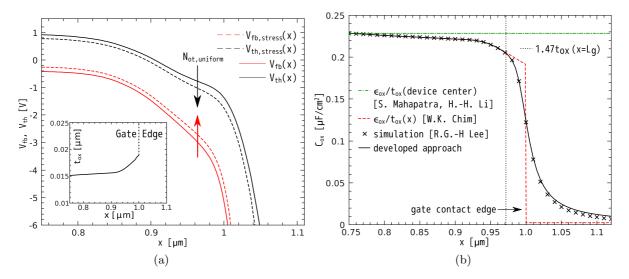

| 4.13 | (a) Local threshold and flatband voltage distributions with uniform oxide charge                                      |     |

|      | profiles. Inset: the dependence of the oxide thickness vs. the lateral coordinate.                                    |     |

|      | (b) The local oxide capacitance calculated using the approach of Lee <i>et al.</i> , com-                             |     |

|      | pared with the newly developed analytical model. Here $L_{\rm g}$ is the position of the                              |     |

|      | drain end of the gate.                                                                                                | 69  |

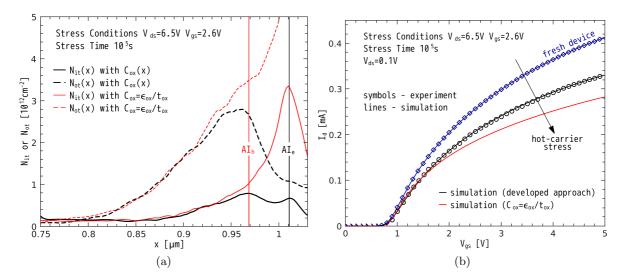

| 4.14 | (a) The lateral distributions of $N_{\rm it}(x)$ and $N_{\rm ot}(x)$ calculated using different $C_{\rm ox}(x)$       |     |

|      | approaches for 10 <sup>5</sup> s at $V_{\rm ds}$ =6.5V and $V_{\rm gs}$ =2.6V. Peaks of $N_{\rm it}(x)$ correspond to |     |

|      | the maxima of electron and hole acceleration integrals. (b) A comparison of                                           |     |

|      | experimental and simulated transfer characteristics for fresh and stressed devices.                                   | 70  |

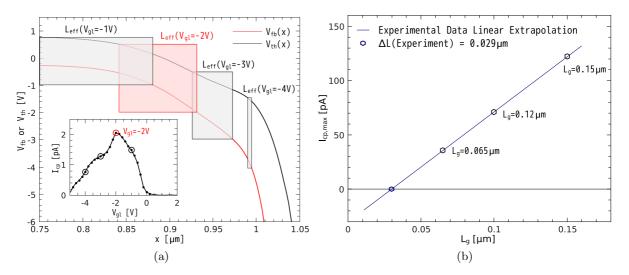

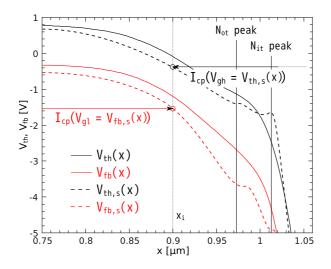

| 4.15 | Typical local threshold and flatband voltage profiles before $\{V_{\rm th}(x), V_{\rm fb}(x)\}$ and                   |     |

|      | after $\{V_{\text{th},s}(x), V_{\text{fb},s}(x)\}$ hot-carrier stress for n-type MOSFET                               | 71  |

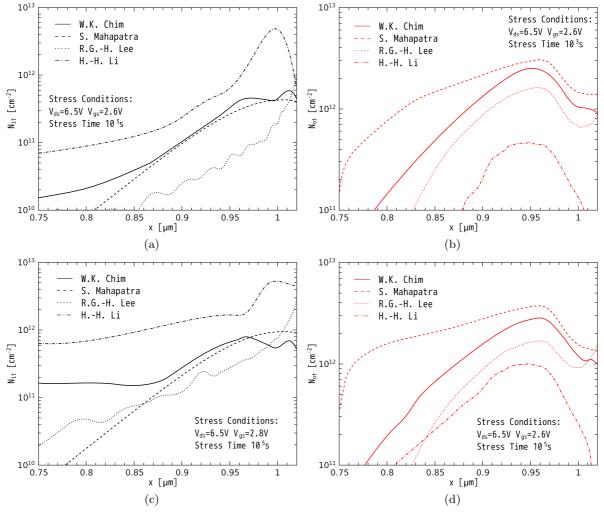

| 4.16 | The lateral distributions of (a),(c) $N_{\rm it}(x)$ and (b),(d) $N_{\rm ot}(x)$ calculated using                     |     |

|      | different extraction approaches for $10^3$ s and $10^5$ s at $V_{\rm ds}$ =6.5V and $V_{\rm gs}$ =2.6V                | 72  |

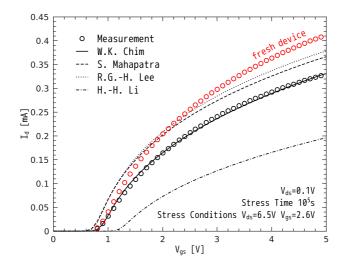

| 4.17 | The comparison of the experimental and simulated transfer characteristics for                                         |     |

|      | fresh and stressed devices                                                                                            | 73  |

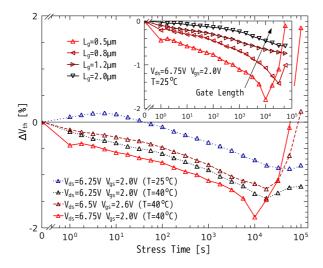

| 4.18 | The shift of $V_{\rm th}$ as a function of stress time at various voltages. Inset: $\Delta V_{\rm th}$                |     |

|      | measured for devices of the same architecture but different only in channel lengths                                   |     |

|      | stressed at $V_{\rm ds}$ =6.75V and $V_{\rm gs}$ =2.0V                                                                | 75  |

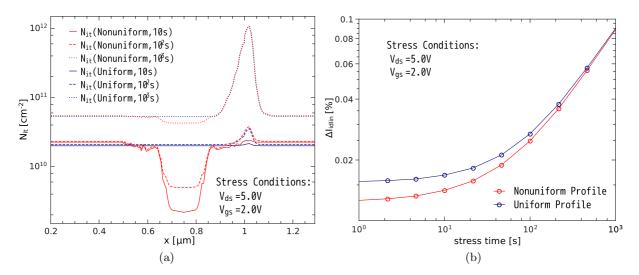

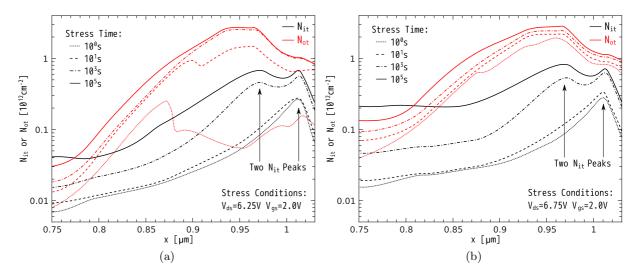

| 4.19 | The evolution of $N_{\rm it}(x)$ and $N_{\rm ot}(x)$ profiles with stress time for (a) $V_{\rm ds}=6.25{\rm V}$       |     |

|      | and (b) $V_{ds}=6.75V$ , the gate-source stress voltage was set to 2V                                                 | 76  |

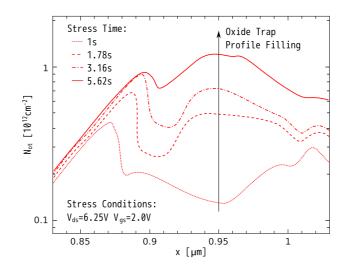

| 4.20 | Filling of the oxide traps revealed for small stress times at the stress regime with                                  |     |

|      | $V_{\rm ds}$ =6.5V and $V_{\rm gs}$ =2.6V.                                                                            | 77  |

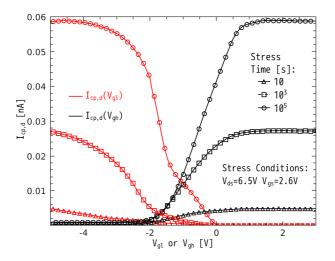

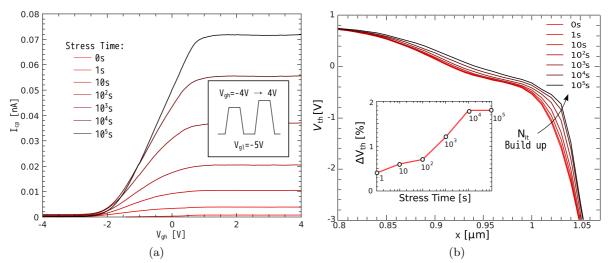

| 4.21 | (a) Time evolution of the measured $I_{\rm cp} - V_{\rm gh}$ relationship during hot-carrier stress                   |     |

|      | using the constant-base-level charge-pumping technique. Inset shows the gate                                          |     |

|      | pulse train. (b) Local threshold $V_{\rm th}(x)$ voltage distributions along the channel                              |     |

|      | before and after the stress. The shift of the threshold voltage $\Delta V_{\rm th}$ measured by                       |     |

|      | the maximum transconductance method is shown in inset                                                                 | 78  |

| 4.22 | (a) The interface state density vs. coordinate $x$ for several stress times: experiment                               |     |

|      | vs. theory. (b) The position of the maxima of main physical quantities: the electric                                  |     |

|      | field, average carrier energy, acceleration integral, position of the most extended                                   |     |

| 1.25 | tails of the, etc.                                                                                                    | 79  |

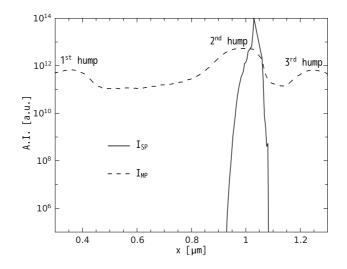

| 4.23 | The dependence of the acceleration integral for the SP- (solid line) and MP- (dash                                    | ~ ~ |

|      | line) processes. Integrals are given in arbitrary units                                                               | 80  |

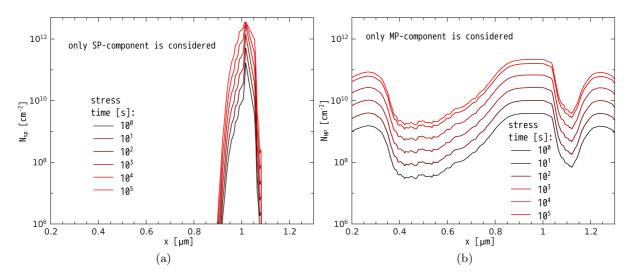

| 4.24 | Both (a) SP- and (b) MP-related components of the total interface state density plotted vs. the lateral coordinate                                                                                                                                                                | 81 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

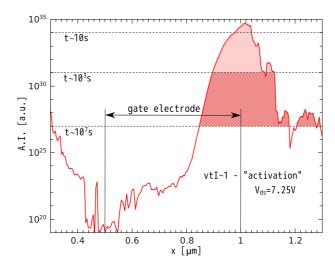

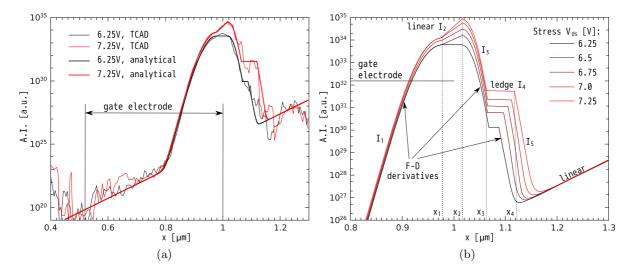

| 5.1  | An example of a TCAD result for the AI with characteristic activation times                                                                                                                                                                                                       |    |

| 5.2  | being sketched                                                                                                                                                                                                                                                                    | 83 |

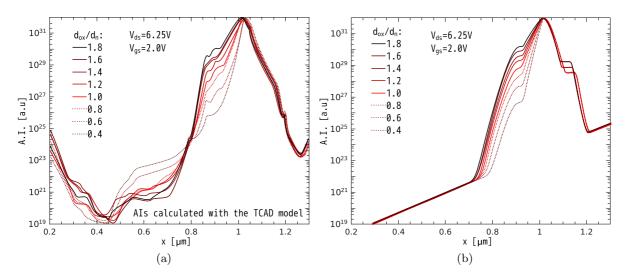

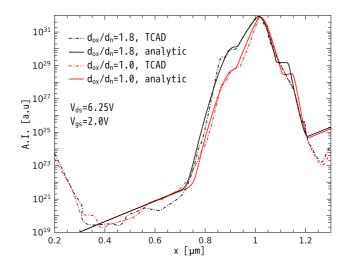

|      | with the TCAD model and the analytical expression                                                                                                                                                                                                                                 | 85 |

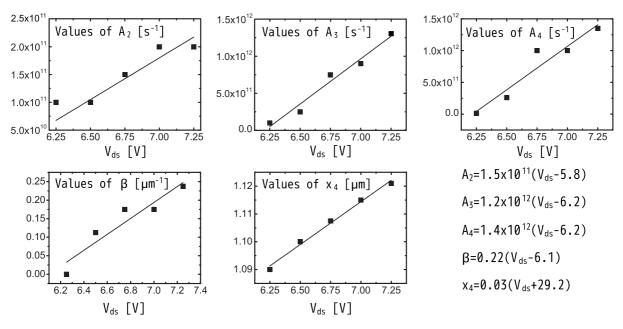

| 5.3  | The parameters $A_2$ , $A_3$ , $A_4$ , $\beta$ and $x_4$ vs. $V_{\rm ds}$ as well as their fitting by the linear                                                                                                                                                                  |    |

| 5.4  | dependence on $V_{ds}$                                                                                                                                                                                                                                                            | 86 |

|      | $V_{\rm ds} = 7.25$ V. (b) $I_{\rm dlin}$ degradation calculated by substituting one (or some) con-<br>tribution(s) $J_{\rm i}$ by the constant value ( $V_{\rm ds} = 7.25$ V)                                                                                                    | 87 |

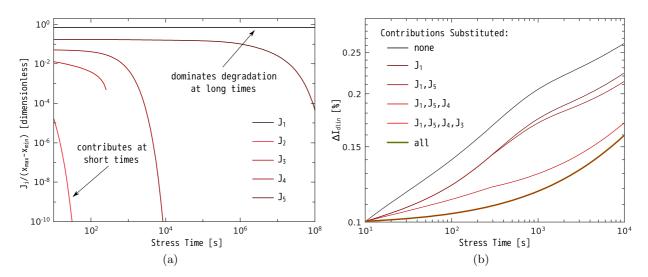

| 5.5  | (a) Comparison between the $\Delta I_{\text{dlin}}$ portion induced by the SP-component ob-                                                                                                                                                                                       | 01 |

|      | tained within the TCAD model and the analytical approach. (b) $I_{\rm dlin}$ degradation:                                                                                                                                                                                         |    |

|      | experiments vs. simulations. Very good agreement between the experimental data                                                                                                                                                                                                    |    |

|      | and the results of both TCAD and analytical model is obtained.                                                                                                                                                                                                                    | 88 |

| 5.6  | The AI profiles calculated with (a) the calibrated TCAD model and with (b) the analytical model for different oxide thicknesses (except $t_{ox}$ , the device topology is                                                                                                         |    |

|      | identical).                                                                                                                                                                                                                                                                       | 89 |

| 5.7  | Comparison between AIs calculated with the TCAD model and the analytical                                                                                                                                                                                                          |    |

| -    | expression for two different oxide thicknesses.                                                                                                                                                                                                                                   | 90 |

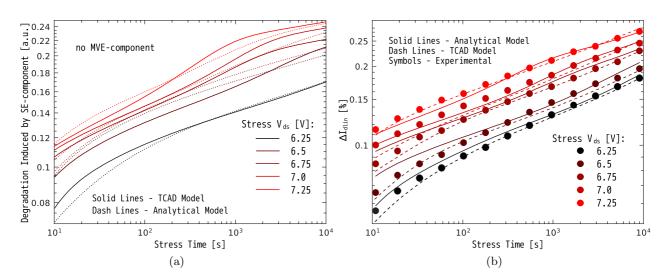

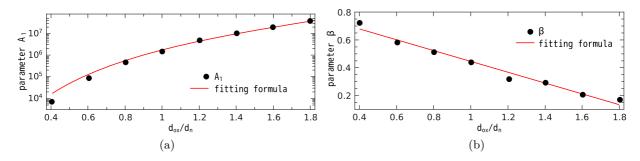

| 5.8  | Dependences of parameters $A_1$ (a) and $\beta$ (b) on the relative oxide thickness $t_{\rm ox}/t_{\rm n}$ .                                                                                                                                                                      | 90 |

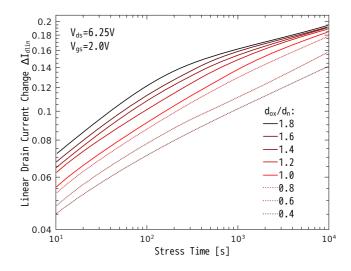

| 5.9  | Dependences $\Delta I_{\text{dlin}}(t)$ calculated for different values of $t_{\text{ox}}$                                                                                                                                                                                        | 91 |

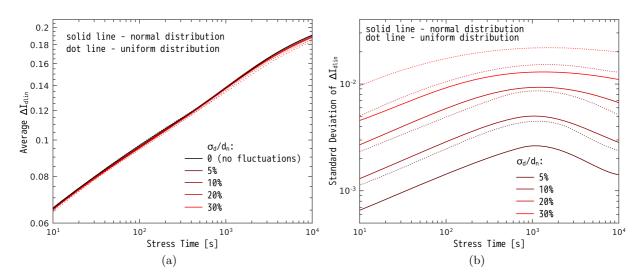

| 5.10 | (a) The mean value of $I_{\rm dlin}(t)$ vs. t calculated for different $\sigma_{\rm d}$ . (b) The standard deviation of $\Delta I_{\rm dlin}(t)$ calculated for different $\sigma_{\rm d}$ .                                                                                      | 02 |

|      | deviation of $\Delta I_{\text{dlin}}(t)$ calculated for different $\sigma_{\text{d}}$ .                                                                                                                                                                                           | 92 |

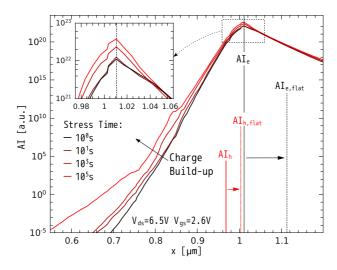

| 6.1  | The evolution of electron AI with stress time for $V_{\rm ds}=6.5$ V and $V_{\rm gs}=2.6$ V. The position of the $N_{\rm it}(x)$ peaks does not change with the stress time. The assumption of a constant oxide thickness results in a significant shift of the AI peak for holes |    |

|      | and electrons $(AI_{e(h)} \rightarrow AI_{e(h),flat})$ .                                                                                                                                                                                                                          | 94 |

# List of Tables

| 1.1 | The parameters of the stretching and bending vibrational modes of the $\mathrm{Si}-\mathrm{H}$ |    |

|-----|------------------------------------------------------------------------------------------------|----|

|     | bond [30]                                                                                      | 19 |

| 2.1 | Self-consistent and non-self-consistent simulation regimes - comparison of sub-                |    |

|     | strate current and computational time                                                          | 29 |

# List of Abbreviations

| $\mathbf{AC}$   | alternating current                               |  |  |  |

|-----------------|---------------------------------------------------|--|--|--|

| AI              | acceleration integral                             |  |  |  |

| $\mathbf{BTE}$  | Boltzmann's transport equation                    |  |  |  |

| $\mathbf{BTI}$  | bias temperature instability                      |  |  |  |

| $\mathbf{CMOS}$ | complementary metal-oxide- semiconductor          |  |  |  |

| $\mathbf{CP}$   | charge pumping                                    |  |  |  |

| DC              | direct current                                    |  |  |  |

| DD              | drift-diffusion                                   |  |  |  |

| DEMOS           | drain extended metal-oxide-semiconductor          |  |  |  |

| $\mathbf{DF}$   | distribution function                             |  |  |  |

| DOS             | density-of-states                                 |  |  |  |

| HC              | hot carrier                                       |  |  |  |

| HCD             | hot-carrier degradation                           |  |  |  |

| HD              | hydrodynamic                                      |  |  |  |

| $\mathbf{HV}$   | high voltage                                      |  |  |  |

| LDMOS           | lateral diffused metal-oxide-semiconductor        |  |  |  |

| $\mathbf{MC}$   | Monte Carlo                                       |  |  |  |

| MOS             | metal-oxide-semiconductor                         |  |  |  |

| MOSFET          | metal-oxide-semiconductor field-effect-transistor |  |  |  |

| $\mathbf{MP}$   | multiple particle                                 |  |  |  |

| $\mathbf{MR}$   | multiple refresh                                  |  |  |  |

| NBTI            | negative bias temperature instability             |  |  |  |

| $\mathbf{NSC}$  | non-self-consistent                               |  |  |  |

| $\mathbf{SC}$   | self-consistent                                   |  |  |  |