Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

FAKULTÄT FÜR INFORMATIK

Faculty of Informatics

# Teaching Multi-Core Programming

### DIPLOMARBEIT

zur Erlangung des akademischen Grades

### Magister

im Rahmen des Studiums

### Informatikmanagement

eingereicht von

### **DI Matthias Wenzl**

Matrikelnummer 0425388

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Ass.Prof. Dr. Monika DiAngelo

Wien, 12.11.2012

(Unterschrift Verfasser)

(Unterschrift Betreuung)

FAKULTÄT FÜR !NFORMATIK

Faculty of Informatics

# Teaching Multi-Core Programming

### MASTER'S THESIS

submitted in partial fulfillment of the requirements for the degree of

### Magister

in

#### **Computer Science Management**

by

### **DI Matthias Wenzl**

Registration Number 0425388

to the Faculty of Informatics at the Vienna University of Technology

Advisor: Ass.Prof. Dr. Monika DiAngelo

Vienna, 12.11.2012

(Signature of Author)

(Signature of Advisor)

### Erklärung zur Verfassung der Arbeit

DI Matthias Wenzl Elisabethallee 39/8, 1130 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit - einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

### Acknowledgements

First, I would like to thank Ass.Prof. Dr. Monika Di Angelo for her valuable feedback and remarks. Moreover, I would like to thank my wife for her cherished support and understanding.

This thesis has been partly supported by the City of Vienna, MA23 under the project grant number MA23-Projekt 10-09.

### Abstract

During the last decades processor manufactures mainly increased performance by shrinking their production size and increasing the processor's clock speed. However, due to physical limitations this approach is not efficient any more. As a consequence, the computer industry increased the number of processor cores on a single die, thus creating multi-core processors. Up to today multi-core processors are used in all kinds of computer systems ranging from super computers to mobile phones. However, programming multi-core systems is a challenging task, which requires software engineers to restructure the way they think about computer programs.

Therefore, this thesis presents a best practice based approach, introducing two course concepts on parallel programming. The first course is a more guided one, where all students are obliged to focus on the same assessment types within the course. Moreover, this course has a strong practical focus, thus being aimed at a university of applied science context. The second course offers more theory and a greater freedom to the students as they are free to choose a certain topic within the field of multi-core systems. This course is aimed at a university context.

The best-practice course concepts are obtained through a thorough analysis of numerous research articles with the following focus:

- The identification and proposition of solutions on the issues and pitfalls when teaching multi-core programming.

- The recommendation of suitable assessment methods when dealing with this challenging field.

- A set of related courses already teaching parallel programming in various aspects.

As a consequence two best-practice based course concepts tailored to the needs of a university and a university of applied sciences are derived. Based on these best-practice examples, two actual courses are designed. This includes a detailed course schedule, learning outcome, assessment concepts, and a set of recommended research articles on the theory of concurrent systems.

### Kurzfassung

Eine Kombination von Erhöhung der Taktrate und Verringerung der Strukturbreiten war in den letzten Jahrzehnten ein gängiges Mittel zur Geschwindigkeitssteigerung von Mikroporzessoren. Aufgrund physikalischer Beschränkungen ist derzeit mit diesem Ansatz jedoch kein nennenswerter Geschwindigkeitszuwachs mehr zu erzielen. Eine naheliegende Lösung war die Entwicklung sogenannter Mehrkernprozessorsysteme, welche mehrere Prozessorkerne auf einem Chip zur Verfügung stellen und somit wieder zu einer Rechenleistungssteigerung führten. Heute sind Mehrkernprozessorsysteme bereits allgegenwärtig und in diversen Computersystemen, vom Supercomputer bis zum Mobiltelefon, im Einsatz. Allerdings ist die Programmierung von Mehrkernprozessorsystemen eine herausfordernde Aufgabe, welche von angehenden Ingenieuren verlangt, ihre Betrachtungs- und Herangehensweise im Bereich der Softwareentwicklung grundlegend zu erweitern. Aus diesem Grund stellt diese Diplomarbeit zwei Lehrveranstaltungsdesigns basierend auf einer "Best-Practice"- Evaluierung vor. Der erste Kurs wird hierbei an die Anforderungen eines Universitätskurses angepasst, während der zweite Kurs für die Anforderungen an einer Fachhochschule optimiert ist. Die Vorgehensweise zur Erreichung dieser Ziele ist hierbei wie folgt:

- Die Identifikation von Herausforderungen und deren Lösungen im Unterrichten von parallelen Programmiertechniken und deren zugrunde liegender Theorie.

- Eine Analyse geeigneter Methoden zur Leistungsprüfung im Hinblick auf die unterschiedlichen Kursausprägungen.

- Eine Gegenüberstellung diverser Kurse im Bereich parallelen Rechnens auf Basis ihrer Lehrziele.

Aufbauend auf diesen Erkenntnisse und den daraus resultierenden "Best-Practcie"- Empfehlungen werden die tatsächlichen Lehrveranstaltungen für ein universitäres, sowie für ein Fachhochschulumfeld abgeleitet. Die praktischen Kursbeschreibungen beinhalten einen detaillierten Zeitplan, die entsprechend ihrem Unterrichtsumfeld angepassten Lehrziele, Konzepte zur Leistungsüberprüfung sowie eine Auswahl an empfohlenen wissenschaftlichen Artikeln zu den behandelten Themen.

### Contents

| Li | List of Figures vi                                 |                                                                      |    |  |  |  |  |

|----|----------------------------------------------------|----------------------------------------------------------------------|----|--|--|--|--|

| Li | List of Tables vii                                 |                                                                      |    |  |  |  |  |

| Li | List of Abbreviations viii                         |                                                                      |    |  |  |  |  |

| 1  | Intr                                               | oduction                                                             | 1  |  |  |  |  |

| 2  | Basi                                               | cs of Multi-Core Systems                                             | 4  |  |  |  |  |

|    | 2.1                                                | Categorizing Multi-Processor Systems                                 | 4  |  |  |  |  |

|    | 2.2                                                | Hardware Parallelism                                                 | 7  |  |  |  |  |

|    | 2.3                                                | Software Parallelism                                                 | 26 |  |  |  |  |

|    | 2.4                                                | Conclusion                                                           | 37 |  |  |  |  |

| 3  | Challenges in Teaching Concurrent Programming      |                                                                      |    |  |  |  |  |

|    | 3.1                                                | Qualification Profiles and Learning Outcomes                         | 40 |  |  |  |  |

|    | 3.2                                                | Issues and Pitfalls in Parallel Programming                          | 42 |  |  |  |  |

|    | 3.3                                                | Parallel programming courses                                         | 44 |  |  |  |  |

|    | 3.4                                                | Assessment Concepts                                                  | 51 |  |  |  |  |

|    | 3.5                                                | Evaluation Results                                                   | 53 |  |  |  |  |

|    | 3.6                                                | Best Practices                                                       | 55 |  |  |  |  |

|    | 3.7                                                | Summary                                                              | 58 |  |  |  |  |

| 4  | Two Approaches for Teaching Multi-Core Programming |                                                                      |    |  |  |  |  |

|    | 4.1                                                | Multi-Core Programming in a University Context                       | 61 |  |  |  |  |

|    | 4.2                                                | Multi-Core Programming in a University of Applied Sciences Context . | 79 |  |  |  |  |

|    | 4.3                                                | Summary                                                              | 87 |  |  |  |  |

| 5  | Con                                                | clusion                                                              | 89 |  |  |  |  |

### Bibliography

## **List of Figures**

| 2.1  | Flynn's Taxonomy [97]                                                           | 6  |  |

|------|---------------------------------------------------------------------------------|----|--|

| 2.2  | Filling and Emptying of a Three Stage Pipeline                                  | 8  |  |

| 2.3  | Processor Architecture Overview                                                 | 9  |  |

| 2.4  | Chip Multi-Processor Architecture                                               | 12 |  |

| 2.5  | Chip Multi-Threading Architecture                                               | 14 |  |

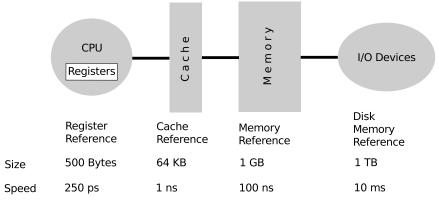

| 2.6  | Memory Hierarchy [40]                                                           | 15 |  |

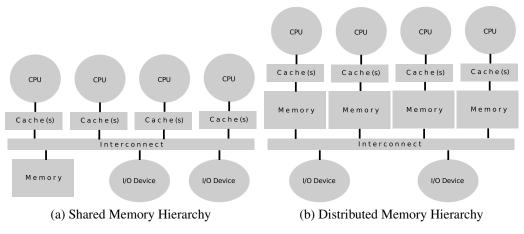

| 2.7  | Memory Hierarchies of Multi Processor Systems                                   | 16 |  |

| 2.8  | A 2-Way Set Associative Cache [3]                                               | 24 |  |

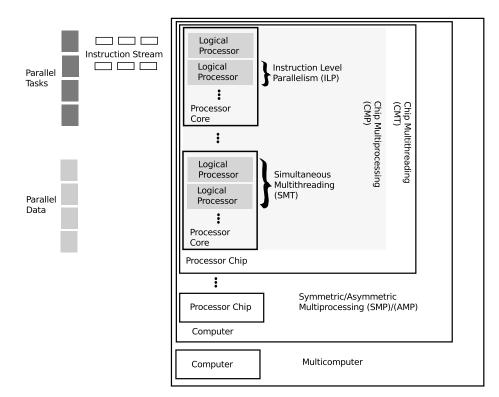

| 2.9  | Categorizing Hardware Parallelism [104]                                         | 25 |  |

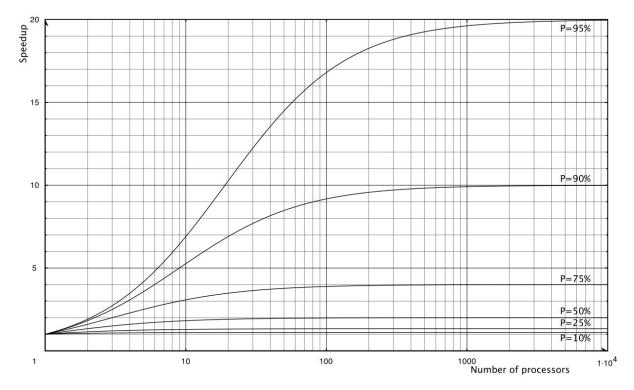

| 2.10 | Amdahl's Law: Speedup using a program with a parallel portion P [104] 27        |    |  |

| 2.11 | Special Issues in parallel programs                                             | 32 |  |

| 2.12 | False Sharing and its avoidance                                                 | 35 |  |

| 2.13 | Hour Glass of Concurrent Computing [104]                                        | 37 |  |

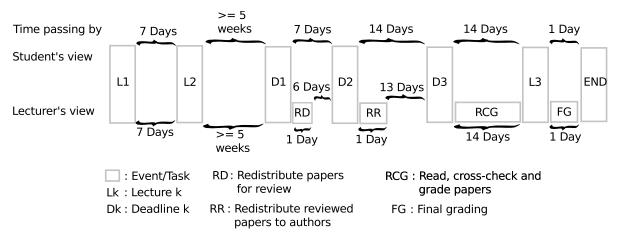

| 4.1  | Multi-Core programming in a university context - detailed course timeline .     | 71 |  |

| 4.2  | .2 Multi-Core prgramming in a university of applied sciences context - detailed |    |  |

|      | course timeline                                                                 | 81 |  |

### **List of Tables**

| 3.1 | Results of Mult-Core Programming Course Examintation         | 59 |

|-----|--------------------------------------------------------------|----|

| 3.2 | Abstract Course Overview                                     | 60 |

| 4.1 | University Course Key Facts                                  | 62 |

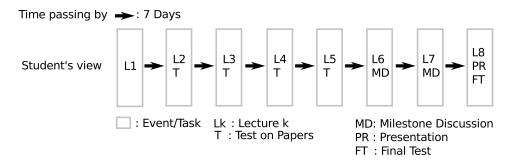

| 4.2 | University Course Time Table from a student's point of view  | 69 |

| 4.3 | University Course Time Table from a lecturer's point of view | 70 |

| 4.3 | University Course Time Table from a lecturer's point of view | 71 |

| 4.4 | Weighted grade components                                    | 72 |

| 4.5 | University of Applied Science Course Key Facts               | 81 |

| 4.6 | University of Applied Science Detailed Course Description    | 84 |

| 4.7 | Weighting of grade components                                | 85 |

### **List of Abbreviations**

- ALU Arithmetic Logic Unit

- AMP Asymmetric Multi-Processor

- CMP Chip Multi-Processor

- CMT Chip Multi-Threading

- **CPU** Central Processing Unit

- **EDA** Electronic Design Automation

- EU European Union

- FPGA Field Programmable Gate Array

- **FPU** Floating Point Unit

- GPU Graphic Processing Unit

- GUI Graphical User Interface

- HT Hyper Threading

- ILP Instruction Level Parallelism

- **IO** Input/Output

- **IPC** Inter Process Communication

- ISA Instruction Set Architecture

- LRU Least Recently Used

- MESI Modified Exclusive Shared Invalid

- MISD Multiple Instruction Single Data

MIMD Multiple Instruction Multiple Data

MPI Message Passing Interface

NUMA Non Uniform Memory Access

**OpenMP** Open Multi Programming

PC Personal Computer

SIMD Single Instruction Multiple Data

**SISD** Single Instruction Single Data

SMP Symmetric Multi-Processor

SMT Simultaneous Multithreading

TLP Thread Level Parallelism

UMA Uniform Memory Access

**UNESCO** United Nations Educational, Scientific and Cultural Organization

### CHAPTER

### Introduction

During the last decades processor manufactures mainly increased performance by shrinking their production size and increasing the processor's clock speed. However, due to physical limitations this approach is not efficient any more. As a consequence, the computer industry increased the number of processor cores on a single die, thus creating multi-core processors [104]. Up to today multi-core processors are used in all kinds of computer systems ranging from super computers to mobile phones. However, programming multi-core systems is a challenging task, which requires software engineers to restructure the way they think about computer programs [33, 59, 64].

Therefore, this thesis presents a best practice based approach, introducing two course concepts on parallel programming. The first course is a more guided one, where all students are obliged to focus on the same assessment types within the course. Moreover, this course has a strong practical focus, thus being aimed at a university of applied science context. The second course offers greater freedom to the students as they are free to choose a certain topic within the field of multi-core systems. As a consequence, this course is aimed at a university context. Nevertheless, the presented course concepts base on a thorough analysis of existing multi-core programming courses in order to derive best practices considering assessment, assignments, and general course structures with respect to desired learning outcomes. Eventually, both course designs will be applied in the summer term 2013 at the Vienna University of Applied Sciences and the Vienna University of Technology.

The remainder of this thesis is structured as follows: Chapter 2 provides a hardware and software oriented introduction on multi-core programming in general. The Chapter consists of a short overview on the history of parallel computing and a categorization of parallel computing systems according to Flynn [29]. Afterwards, hardware parallelism is examined, investigating processor architectures, memory consistency, and processor synchronization. Subsequently, Chapter 2 addresses software parallelism, introducing Amdahl's Law [6] and focusing on topics like categorizing software parallelism. Moreover, this Chapter investigates synchronization and communication issues and discusses software libraries aiding in developing parallel software.

The subsequent Chapter 3, is divided into 4 consecutive parts:

- 1. First, it is shown that the comparison of single courses within degree programs cannot be done on basis of the alumni qualification profile, but must be done with respect to the so called learning outcome.

- 2. Subsequently, numerous contributions identifying issues and challenges in teaching parallel programming in a more specific manner are reviewed.

- 3. Moreover, a set of dedicated parallel programming courses is evaluated with respect to their learning outcome definitions as well as their actual teaching content.

- 4. The result of this evaluation serves as a basis to derive two best practice courses. One is aimed at a university environment, the other one is designed to fit in a university of applied science context. These best practice course concepts will be used to design two courses in Chapter 4.

As a consequence, Chapter 4 presents the actual instances of the best practice course templates developed in the previous Chapter. The first course presented is composed for a university context. It is designed as a conference simulation which requires participants to write a seminar paper, perform a peer review, and do a final presentation with a subsequent discussion. The freedom of choice is implemented by letting students choose their general topic out of a topic pool. The second course is dedicated to a university of applied sciences context, thus offering more industry focused content. This includes covering dedicated programming libraries for all participants. Although students are required to read and understand certain research papers on the theory of parallel computing as well, the main focus of the course is the communication of the application of parallel programming techniques.

Finally, Chapter 5 concludes the thesis. Moreover, this Chapter presents the results of an evaluation on the university of applied science course that has been held in a somewhat related version in the summer term of 2013.

# CHAPTER 2

### **Basics of Multi-Core Systems**

The first computer featuring real hardware parallelism was built in 1968. At that time, Barnes et. al. [8] proposed the *ILLIAC IV* computer. It consists of 256 parallel computing elements, a unified address, and Input/Output (IO) space. The main purpose of this architecture was to aid in matrix calculations and the handling of large multi-dimensional data structures. Aside of this early attempt to increase computing power by adding extra hardware, it was not before November 2000, that chip multi-processors (CMP) were available to the public with the introduction of Intel's Pentium 4 Hyper Threading (HT) processor family [104]. By today, multi processor systems have also spread into the embedded market and are available to many people of the industrialized parts of the world. However, since 1968 numerous technologies and methods regarding parallel computing have been introduced. Therefore this chapter provides an overview of the used taxonomy in parallel computing.

#### 2.1 Categorizing Multi-Processor Systems

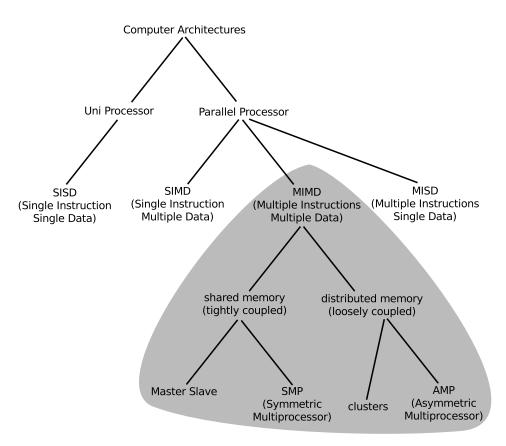

The first and still most common categorization of parallel processors has been proposed by Flynn in 1972 [29]. Flynn developed a hierarchical model to represent an architecture's structure from a macroscopic point of view. To allow an abstract categorization of computer systems, Flynn used the *stream* concept, which denotes a sequence of data or instructions [30]. His approach is known as Flynn's taxonomy today. It reveals the following processor architecture classes:

- **Single Instruction Single Data (SISD)** This kind of processor architecture consists of a single processing unit that operates with a single instruction stream on a single data stream. It does not provide any hardware parallelism at all, regarding truly parallel execution. This class refers to classic single processor architectures systems like older Personal Computers (PCs), or old main frames.

- **Single Instruction Multiple Data (SIMD)** Systems utilizing these architecture use a single instruction stream to operate on multiple data streams. This very common type of parallelism can be found in Graphic Processing Units (GPUs), or array processors, for example. The idea behind this concept is, that it is possible to operate on one large data structure consisting of several independent sub-structures concurrently. Thus being able to finish the task faster [48].

- **Multiple Instruction Single Data (MISD)** The third classification type by Flynn describes an architecture where multiple instruction streams, thus multiple processing units operate on a single data stream. An example for this kind of architecture is an application specific processor for pattern matching developed by Olaf René [11]. However, no commercially available processor using this kind of architecture has been built until today [40, 97].

- Multiple Instruction Multiple Data (MIMD) Modern general purpose multi processor systems implement this kind of architecture where multiple instruction streams operate on multiple data streams. Examples for such systems implementing the MIMD architecture in the field of embedded systems are: [31, 32, 75, 80, 88, 96, 100–102]. Moreover, all modern server and desktop processors from Intel<sup>1</sup> and AMD<sup>2</sup> belong to this category. Furthermore, this category features clusters and super computers as well.

In order to be more specific it is also possible to break down the MIMD architecture into two sub categories [97], loosely and tightly coupled systems.

<sup>1</sup>www.intel.com <sup>2</sup>www.amd.com

- The first sub category describes so-called *"loosely coupled"* MIMD systems. Such architectures describe systems, where the sum of available processing units does not share a common memory. They are also called *distributed memory* systems and are applied in super-computers as well as in embedded systems.

- The second disposition of systems implementing the MIMD architecture are socalled *"tightly coupled"* systems. In this case all processing units in a processor share a common accessible memory in general. Moreover, master/slave systems do also belong to this category. In a master/slave system a single master processor performs the required task scheduling, like starting and stopping jobs on a set of slave processors. Such architectures are mainly found in the field of embedded systems today. An example is the TI AM1710 platform from Texas Instruments [100].

Figure 2.1: Flynn's Taxonomy [97]

Furthermore, there exist another two ways to categorize parallel computing systems. On the one hand, it is possible to distinguish between Asymmetric Multi-Processor (AMP) and Symmetric Multi-Processor (SMP) systems. An SMP system implements a MIMD architecture, where all of the available processor cores utilize the same Instruction Set Architecture (ISA) [90]. A system consisting of several processors from at least two different ISAs are called AMP.

On the other hand, there exists a classification into homogeneous and heterogeneous systems. From a hardware point of view, these two terms can be used synonymously with the definition of SMP and AMP [90]. However, from a software perspective, the term heterogeneous describes a system executing at least two different operating systems on a given hardware platform, which may implement an AMP or a SMP. Considering homogeneous systems, only one operating system may be used on an AMP or SMP system from the software point of view [41,90,104]. In this thesis, the terms homogeneous and heterogeneous are used from a software point of view, if not stated otherwise. Figure 2.1 depicts the categorization introduced in order to provide an overview on the parallel computing taxonomy. Considering Figure 2.1, SMP and AMP are not bound to *tightly*, respectively *loosely-coupled* memory architectures, but these are their most common implementations [90]. Moreover, the sub-tree discussed in this thesis shown in Figure 2.1, as enclosed gray area. Furthermore, there exist different techniques implementing parallelism in computer systems. Therefore, the subsequent Sections 2.2 and 2.3 provide an introduction of hardware and software related techniques to realize parallel systems.

#### 2.2 Hardware Parallelism

This section discusses techniques to implement parallelism at a hardware level, thus supplying computing systems with the components necessary to work on at least two *tasks* simultaneously. The term *task* refers to a wide variety of granularity, reaching from parallel execution of instructions to parallel computation of whole programs.

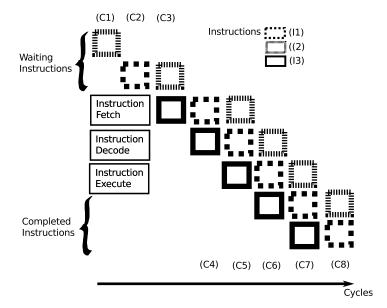

Figure 2.2: Filling and Emptying of a Three Stage Pipeline

#### **Instruction Level Parallelism**

The first method described to implement parallelism in a computer system is called Instruction Level Parallelism (ILP) [82]. In fact the processors pipeline realizes the parallel processing of data or instructions by interleaving. In Figure 2.2 a three stage pipeline<sup>3</sup> executing three independent instructions in parallel using ILP is shown. As it can be seen it takes three cycles (C3) - (C5) until the pipeline is full ((C5)). Subsequently, it takes another three cycles (C6) - (C8) until it is emptied again. However, in cycle (C5) the pipeline is executing three instructions (11) - (13) concurrently. In order to exploit ILP the following conditions must be fulfilled:

- (1) No data dependencies: A data dependency exists if the result of instruction i depends on a parameter of instruction j. Moreover, an instruction j is data dependent on instruction k, whereas instruction k is data dependent on instruction i [82].

- (2) No name dependencies: Name dependencies refer to a case when at least two instructions use the same register or memory location to operate on.

<sup>&</sup>lt;sup>3</sup>It consists of the three basic steps: Instruction *Fetch*, Instruction *Decode*, and Instruction *Execute*

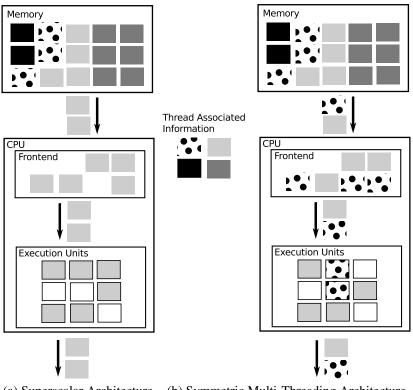

(a) Superscalar Architecture(b) Symmetric Multi-Threading ArchitectureFigure 2.3: Processor Architecture Overview

- (3) No data hazards: Data hazards denote two instructions that would alter the results of their operands when being executed in parallel. The distance between two instructions that are allowed to depend on each other is bound by the pipeline length [40].

- (4) No control dependencies: A control dependency occures when ordering of instructions are determined by a branch. Therefore, this condition states that the order of instructions determined by branches must not be changed [40].

Finally, ILP is used in all processors including a pipelined architecture. This is true for every processor since about the second half of the 1950's [93].

A generalization of the ILP approach is the so called *Superscalar* processor architecture [93]. Here, a processor is capable of processing two or more instructions in parallel. This is possible since the most important resources in the pipeline are accessing the processing t

sible separately, or are available multiple times (e.g. separate store/load units, separate but multiple available integer execution units). Nevertheless, a processor implementing this architecture can only execute instructions associated with a single thread/process in parallel. But, due to the fact that a series of instructions may be independent from each other, they can be executed concurrently because it is possible to utilize several of the available execution units at once. Examples of processors implementing a *Superscalar* architecture are the *MIPS R10000*, and the first *Pentium 4* processors [77]. Figure 2.3a gives an overview on this kind of architecture.

Therefore, to further exploit the parallel potential of certain software components, the next logical step was to increase the number of software threads being executed without the necessity of task switches by the operating system. This has been realized by the implementation of truly Multi-Threaded processor architectures.

#### Hardware Multi-Threading

Multi-Threading describes the concurrent execution of software components (threads, processes) on a given processor [94]. The first attempts of multi-threading were performed in software, where an operating systems scheduler has to issue context switches<sup>4</sup> to execute threads/processes in a pseudo parallel way. The term pseudo parallel refers to the fact that SISD architectures could only execute threads/processes by interleaving. This is also true for processor architectures implementing ILP, or the *Superscalar* architecture.

To further push the performance increase of *Superscalar* processor architectures a hardware support for task switching has been proposed by the introduction of Simultaneous Multithreading (SMT), which is also called HT by Intel [40]. The intended performance gained on multithreaded software is achieved by at least doubling the number of available processor registers, stack pointers, and program counters. Moreover, the processor provides resources for thread context sensitive pipeline flushes, subroutine return predictions and trapping [83]. The multiple availability of these resources causes the operating system to perform task switches in a faster way, since all that has to be done is to switch to the next thread context by changing to the next available regis-

<sup>&</sup>lt;sup>4</sup>Context switches oblige a lot of costly operations like saving processor registers, stack pointer, and the program status word to the stack.

ter bank. Nevertheless, threads and processes are still executed in a pseudo parallel scheme [40,94]. Figure 2.3b shows the operation principle of a processor implementing the SMT architecture.

However, the further increase of parallel execution units and mirrored registers sets does not scale linearly with the estimated performance [77]. This is merely caused by the fact that the administrative overhead considering queuing and multi-port register files results in a limit on the performance return of an SMT architecture [77]. For example, when upgrading a four issue<sup>5</sup> machine, to an eight issue machine, the performance increase will only be about 20% [77]. Therefore, the next step in the development of processors being able to execute threads and processes in a truly parallel way was the proposal of *Chip Multi-Processor* architectures.

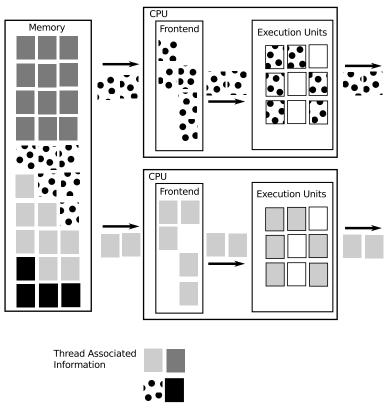

#### Chip Multi-Processor (CMP)

According to Olukotun et al. [77], the consequences of the limitations of *Superscalar* processors led to decentralized microprocessor designs in order to achieve anticipated performance gains. Moreover, the idea of implementing several comparatively small processor cores on a die, instead of one complex multi-issue design supports the processor's flexibility and scalability considering software execution [53]. This has been observed by Wall [107]. In his study, the author identified two general classes of programs executed on a processor.

• The first class describes programs with low to moderate inherent parallelism. These programs usually implement a large number of integer operations. However, they are not able to be fully exploited by a given multi-issue *Superscalar* architecture, due to their lack of larger amounts of independently executable code. Due to the fact that CMP processors implement independently operating processor cores on one chip, this class of programs can be executed in a more efficient way. This argument is also supported by [77], who showed that programs falling into this class scale worse on a four issue *Superscalar* processor than on a two

<sup>&</sup>lt;sup>5</sup>The term *issue* denotes the number of parallel execution units in a *Superscalar* or *Symmetric Multithreading* processor.

Figure 2.4: Chip Multi-Processor Architecture

issue *Superscalar* processor, both operating at the same clock frequency and implementing the same instruction set base.

• The second class represent programs containing a high amount of parallelism, while implementing floating point operations mostly. Although these kinds of programs would perform well on a *Superscalar* processor, they would not perform worse on a CMP, since several available processor cores could be used to exploit the available parallelism capability.

Therefore, CMP systems implement execution models being able to cope with both, low to moderate, and high parallelism capabilities [77]. Figure 2.4 shows a CMP system implementing two processor cores. Nevertheless, there exist three general types of application areas inducing architecture variants of CMP systems according to Kumar et al. [53].

- Server & High Performance Computing This group is generally used in business or scientific computing. Thus machines in this field have to process a high amount of independent data using commercially available software (e.g. database servers). In the field of high performance computing, highly specialized software components are used to exploit a processor's architecture in an effective way. Therefore, CMP systems housing a large number of simple, but yet powerful processor cores can be used for these scenarios. Due to cost effectiveness reasons computers featuring these processor architectures have to operate on a high workload most of the time.

- **Desktop Computing** In contrast to high performance computing systems, the average user has to master only a small number of tasks in parallel. However, in order to use software developed for SISD processors in a convenient way, it is highly desirable to have a smaller, but more powerful number of cores in a system belonging to this requirement group.

- **Embedded Computing** Embedded systems do not have unified performance requirements. Their concern is rather application specific. An example for opposing system requirements in the field of embedded systems is the modern cell phone. On the one hand, the phone is obliged to have a long operational and standby availability, thus consuming as few power as possible. On the other hand, a modern phone must service its user with a lot of additional features like a music player or 3D graphics support. These media features need a lot of processor power in contrast to a phone's main tasks. Therefore, a heterogeneous CMP solution can often be found in these cases.

#### **Chip Multi-Threading (CMT)**

Due to the ever decreasing feature size and the resulting increase of transistors on a chip it is possible to implement hardware SMT features in a CMP system, as it is shown in Figure 2.5 [94]. This so called *Chip-Multi-Threading* is implemented by the high end models of Intel's *Core I7* and *Core I5* processors, for example. The motivation for implementing such systems is located in the field of highly parallel software, such as data base applications. Usually, such kind of software serves several hundred of users, where

Figure 2.5: Chip Multi-Threading Architecture

each user is associated with a process, consisting of several threads in order to hide disk access latencies [94]. Therefore, a processor design implementing truly parallel execution of processes in combination with fast task switching capabilities is very well suited for an environment realizing a high rate of Thread Level Parallelism (TLP). However, the design of CMT capable processors is not done by simply instantiating whole processor cores multiple times on one chip. Instead there exist a lot of shared resources which are only available in a fraction of the physically available cores, such as Floating Point Units (FPUs), for example. Therefore, there exist special requirements when exploiting the capabilities of CMP and CMT systems, regarding interconnect technologies [94].

#### **Special Issues regarding truly Parallel Executing Processors**

Besides the fact that CMP and CMT processors provide solutions to the problems on how to deal with parallel programs in an efficient way, there still exist various challenges

Figure 2.6: Memory Hierarchy [40]

in exploiting these capabilities which are discussed in the following Subsections.

#### **Memory Hierarchies**

The design of memory hierarchies has to cope with two contradictory conditions. On the one hand, programmers want to have access to an infinite space of fast memory. On the other hand, the faster the memory, the more expensive it is. In order to find a balanced tradeoff between the costs and the performance constraints, a computer's memory is organized in a set of layers, as it can be seen in Figure 2.6. In the first layer, a set of registers expose a small amount of storage to the Central Processing Unit (CPU). This kind of memory is implemented inside the processor core and can be accessed within a few clock cycles. The next layer represents the so called cache memory. The cache can be seen as a memory, exploiting the principle of locality in an aggressive way. The adjacent layer is called main memory in general and is located off chip, thus it is necessary to let the processor communicate with a dedicated memory controller<sup>6</sup> to access the main memory, thus decreasing the access speed. The last layer includes mass storage devices, like a hard disk or a flash memory [40].

Furthermore, considering CMP and CMT systems it is possible to distinguish between *shared memory*<sup>7</sup> and *distributed memory*<sup>8</sup> architectures, as explained in Sec-

<sup>&</sup>lt;sup>6</sup>Sometimes, these memory controllers reside on-chip as well.

<sup>&</sup>lt;sup>7</sup>This architecture is also known as Uniform Memory Access (UMA)

<sup>&</sup>lt;sup>8</sup>This architecture is also known as Non Uniform Memory Access (NUMA)

Figure 2.7: Memory Hierarchies of Multi Processor Systems

tion 2.1. As shown in Figure 2.7, both memory hierarchy models consist of memories only local to a specific processor. Therefore, the necessity for memory synchronization and consistency arises [40].

Nevertheless, synchronization of concurrent processes was important in uni processor systems<sup>9</sup> as well, but could be realized without the need of additional hardware support apart from the common *Test & Set* instructions necessary for implementing synchronization primitives, such as semaphores or spin locks [22]. This was possible since concurrent processes in a uni processor systems were actually executed in a pseudo parallel way [94]. However, when dealing with multi processor systems there has to be additional hardware support for synchronizing the access to shared memory regions, as well as keeping them in a consistent state.

#### **Synchronization**

To gain synchronized access to a central resource, the mutual exclusion problem has to be solved [20]. Basically, the problem states, that when multiple processes compete over a single resource it must be assured that one process has exclusive access to that resource. Furthermore, it must be guaranteed that a process has only access to the resource for a finite amount of time. Moreover, it must be asserted that also other

<sup>&</sup>lt;sup>9</sup>Including Superscalar and SMT architectures

processes can enter the shared resource once the process possessing it has left.

Since synchronization is a common problem in both, uni processor and multi processor systems, there exist dedicated instructions to perform these tasks. They are usually subsumed under the term *Test & Set* instructions [22]. However, there exist major differences in the implementation of *Test & Set* instructions between uni processor and CMP systems. In order to illustrate these difference, the synchronization instructions of the ARMv5 and ARMv6 ISAs are compared [1]. Here, the ARMv5 ISA represents a uni processor instruction set, whereas the ARMv6 symbolizes a multi processor capable ISA.

Listing 2.1: ARMv5 compatible Spinlock Implementation [61]

```

static inline void __spin_lock_nds(nds_spinlock_t *lock)

1

2

{

3

unsigned long tmp;

4

__asm__ __volatile__(

5

6

"spin: ldr %[tmp], [%[lock]]\n"

7

" cmp %[tmp], 0\n"

8

" bne spin \n"

9

" ldr %[tmp], 1\n"

10

" swp %[tmp], %[tmp], [%[lock]]\n" /* atomic */

" cmp %[tmp], 0\n"

11

" bne spin\n"

12

13

: [lock] "r" (&lock ->lock), [tmp] "r" (tmp)

14

15

);

16

}

```

Synchronizing pseudo parallel executing processes using an ARMv5 ISA can be done with the help of a single instruction, called **swp**. This instruction performs a combined load and store operation, making it possible to exchange the value of a variable in an atomic way. This is necessary, since an occurring interrupt request would intercept a non atomic load and store operation, thus resulting in the possibility that two processes will access the shared resource, due to a context switch. The read back value of the atomic **swp** instruction is used to determine the actual state of a lock, guarding the entrance to a shared resource region, for example. A possible implementation of such a guarding routine can be seen in Listing 2.1. This procedure works as follows: The variable *lock* represents a guarding variable and is accessed by all processes that want to utilize the shared resource. In order to do so, the variable *lock* must be set to zero. As long as *lock* ist not set to zero, it is assumed that another process has access to the shared resource, thus a process wishing to use it as well has to wait. This is done in lines 6 to 8 of Listing 2.1, where the instruction **bne** denotes that the program flow shall branch to the label **spin**, if the preceding compare operation did not return *true*. Line 9 loads a value indicating an occupied resource in the variable **tmp**. Subsequently the instruction **swp** is executed performing the *Test & Set* operation. If the read back value is equal to zero, the shared resource has not been used by another process. Therefore the process attempting to occupy it succeeds (line 11). Otherwise, the CPU will branch back to the label **spin** in line 6).

Although the mentioned **swp** instructions are available in the ARMv6 ISA as well, they are not suited for synchronization in multi processor environments, since **swp** instructions do not perform write buffer<sup>10</sup> flushes [1,3]. Therefore, the instructions **ldrex**, and **strex** are available in processors implementing the ARMv6, and above architectures. These two instructions implement system wide exclusive load and store operations. This is done by marking an address accessed by using **ldrex** exclusively for a specific processor. Subsequently, **strex** can be used to store a date exclusively on the memory location marked by **ldrex**, thus making it possible to implement synchronization primitives in multi processor environments. In order to get a better overview on how synchronized access on a shared resource can be done in a multi processor environment, Listing 2.2 presents an example implementation of a Spinlock for an ARMv6 processor.

```

Listing 2.2: ARMv6 compatible Spinlock Implementation [61]

```

```

1 static inline void __spin_lock_nds(nds_spinlock_t *lock)

2 {

3     unsigned long tmp;

4

5     __asm__ __volatile__(

6     "spin: ldrex %0, [%1]\n"

7     " teq %0, #0\n"

```

<sup>&</sup>lt;sup>10</sup>Using write buffers is a common technique to bypass memory latencies [3].

```

8

" strexeq %0, %2, [%1]\n"

9

" teqeq %0, #0\n"

10

" bne spin"

11

: "=\&r" (tmp)

12

: "r" (&lock ->lock), "r" (1)

13

: "cc");

14

15

smp_mb();

16 }

```

In line 6 an exclusive load operation is performed, to retrieve the current state of the variable *lock*. Subsequently, the value is compared against zero (line 7). If the comparison **teq** returns true, the instruction **strex** is issued (line 8). The **eq** post-fix denotes that the instruction **ldrex** must only be executed if a preceding comparison evaluated to true. Otherwise, a *no-operation* instruction is executed. Eventually, the *lock* is occupied once **strex** was executed successfully<sup>11</sup>. Eventually, a system synchronization instruction encapsulated in the function *smp\_mb()* is called in line 15.

#### **Memory Consistency**

From a uni processor system's point of view memory consistency is not a big problem, since read and write operations affect memory in the order they were issued. This is also true for processors being able to perform memory operations in an out of order<sup>12</sup> manner if the following rules are obeyed.

- (1a) It must be assured that two instructions do not reference the same data.

- (2a) It must be guaranteed that one instruction does not control the execution of the other (e.g. an IF clause).

Once these two conditions are fulfilled it is possible to perform memory operations out of order. In essence these two conditions enable compiler optimizations like register allocation, code motion, loop transformations and several hardware optimizations such

<sup>&</sup>lt;sup>11</sup>This is indicated by writing a zero into the return register (First parameter of the instruction).

<sup>&</sup>lt;sup>12</sup>Out of order means that a certain processor can execute instruction k before instruction i, although i is located before k in the program flow, if both instructions are independent from each other. [40]

as ILP, for example [3]. Therefore, the topic of memory consistency describes models that allows the programmer to have a consistent view on all memory operations, such that they behave in the same way as the program execution order depicts it. Thus, one expects a read operation to return the value of the last recent write operation to the very same memory location.

However, when it comes to multi processor systems it is not sufficient to fulfill conditions (1a) and (2a) only in order to maintain memory consistency. In order to have a consistent memory view in a shared memory multi processor environment Lamport [54] proposed the *Sequential Consistency* model in 1979. The author identifies two major aspects in keeping memory operations sequentially consistent:

- (1b) Maintaining program order among operations from individual processors and

- (2b) maintaining a single sequential order among operations from all processors.

The second aspect results in a presentation of memory operations that appear to be *atomic* regarding memory operations from another processors point of view. Beside Lamport's conditions to retain sequential consistent memory operations in multi processor environments, Adve and Gharachorloo [3] examined numerous multi processor systems with focus on their memory hierarchies, and read/write operation implementations. Eventually, the authors derived the following constraints on sequential consistency:

- A processor must ensure that its previous memory operation completes before it issues a new one in program order. This requirement is called *Program Order*. Moreover, a write operation must generate invalidate or update messages for all cached copies.

- If a system utilizes caches it must assure that writes to the same location are serialized. Thus, the value of a write must not be returned by a read until all other processors have updated their caches. This requirement is called *Write Atomicity*.

Finally, due to the fact that the sequential consistent memory model introduces several bottle necks because of its firm requirements, several models relaxing the sequential consistency model have been proposed [3,40]. To categorize the relaxed memory order

models we use the formal definition of [40], which corresponds to the two requirements *Program Order* and *Write Atomicity* as proposed in [3]. A rule has the following syntax:  $X \rightarrow Y$ . Its semantic is, that operation X must complete before operation Y. The *sequentially consistent memory model* can be described with the following rules:  $R \rightarrow W$ ,  $R \rightarrow R$ ,  $W \rightarrow R$ ,  $W \rightarrow W$ . The following relaxing memory models are named after the rules they relax in the *sequentially consistent model*.

- A model known as *total store ordering* or *processor consistency* relaxes the W → R requirement. This model retains ordering during write operations. It is commonly used by programs operating under the sequential consistency model, without the need for additional synchronization.

- Relaxing requirement  $W \to W$  results in a model called *partial order store*, which is implemented in certain SPARC processors, for example.

- The third memory model relaxation omits the requirements R → W and R → R and realizes a variety of models known as *weak ordering*. This kind of model is used in the PowerPC consistency model, for example.

After introducing the theoretical background of memory consistency models in multi processors environments, the subsequent Subsection will present an overview on techniques realizing these models.

#### **Enforcing Consistency**

The two major methods to coerce memory consistency in shared memory multi processor systems are represented by cache coherency protocols and memory barriers [66]. As described in the Subsection "Memory Hierarchies" in Section 2.2, caches can be described as some kind of short term memory to a processor. Moreover, the presence of a cache results in a performance increase since the processors pipeline would have to be stalled each time the memory would have to be accessed without having a cache. Furthermore, when a multi processor system is deployed as shared memory architecture each processor might have its own private cache, as it has been presented in Figure 2.7a. Thus to compel a consistent view on memory, it is necessary to let the caches share their information by utilizing cache coherence protocols.

Nevertheless, in order to understand the operation of cache coherence protocols, the basic functionality of a cache is explained in these paragraphs. First, we will explain the terms of definitions used when dealing with caches. Subsequently, the functionality of the example cache shown in Figure 2.8 is explained.

The smallest accessible amount of memory that a cache can exchange with main memory is called *cache line*. These lines are typically between 16 and 256 bytes wide. In Figure 2.8, a cache line is represented by a cell in the table (E.g. The cell which states 0x12345000). In our case, the cache line is 256 bytes wide. Thus each cache line represents a 256 byte wide consecutive memory block. This makes our cache rather large. Caches of this size are usually organized as hash tables with fixed sized buckets, which are named *sets* from a hardware developer's point of view. A *set* of *lines* is called *way*. Because the location of the *line* in the cache is determined by a simple hash function looking at four address bits at the start address of the *line*, the cache can be referred to as *associative*. Therefore, the cache depicted in Figure 2.8 implements a *two way set associative cache*.

The cache operates in the following way. Once a CPU is reset, and the cache has been activated by software, all memory transfers using cache able memory regions must pass through the cache. Due to the fact that caches are initially empty, the first access to the cache results in a so called *miss*. Assume that this request aimed at a word stored at memory address 0x12345308. Since the requested word is located in the address range between 0x12345300 and 0x123453FF, the whole memory block starting at address 0x12345300 with a length of 256 bytes is transferred into the cache, and indexed at *way* 0, line  $0x12345300^{13}$ . The memory block index is returned by the cache's hash function. Therefore, it is also possible that two words from distinct address ranges evaluate to the same index position in the cache (See address index 0xE in Figure 2.8). Here, a memory block from the base address 0x42310E00 has been stored at *way* 1, because *way* 0 has already been occupied by another memory block belonging to the base address 0x12345E00. However, since caches have no infinite capacity, there exist replacement strategies, like Least Recently Used (LRU)<sup>14</sup> in order to exchange data

<sup>&</sup>lt;sup>13</sup>This makes sense because of the principle of locality, which states, that it is very likely that once data is accessed at a specific location, there will be more accesses to addresses nearby [40].

<sup>&</sup>lt;sup>14</sup>The cache replacement strategy LRU, drops the least common accessed memory block after a certain amount of cache hits. [40].

stored in the cache with data located in main memory when necessary [40, 66].

When it comes to SMP systems, the following question arises with the use of private processor caches. How does CPU 0 know about a change of a variable located in CPU 1's private cache?

The answer to this question are so called coherence protocols. Their key feature is to track the state of any shared data block, as well as keeping data up to date [40]. In general there exist two different classes of cache coherence protocols.

- **Directory based** This kind of protocols provides a central book keeping mechanism to track the state of shared data. Although directory based protocols have a higher implementation overhead they are better suited for large scale multi processor systems [40].

- **Snoop based** A distributed approach on keeping memory in a consistent state is followed by snoop based cache coherence protocols. Here, each cache controller listens on a shared bus in order to gain knowledge on which memory blocks must be synchronized in order to keep a system in a consistent state. This technique is widely used in today's desktop and server processors with few processing cores [40].

Basically, both protocol types consist of several states indicating the current condition of each cache *line*. Each of these states may send messages to each other if an appropriate action, like a write operation to a cached memory location that is also present in another processors cache, is induced by one of the CPUs participating in the SMP<sup>15</sup>.

Since modern processors are able to execute instructions out of order, or issue read operations before an earlier write due to the anticipation of write buffers, so called *memory barriers* were introduced to guarantee an in order access to memory and IO devices. *Memory barriers* are interventions that instruct the compiler to retain the order of instruction execution as implemented by the developer, thus avoiding to apply some kind of optimization techniques in order to execute the given code faster [66]. There exist several types of *memory barriers*:

<sup>&</sup>lt;sup>15</sup>Therefore, it is sometimes mentioned that shared memory systems base upon message passing system [66]

|     | Way 0      | Way 1      |

|-----|------------|------------|

| 0x0 | 0x12345000 |            |

| 0x1 | 0x12345100 |            |

| 0x2 | 0x12345200 |            |

| 0x3 | 0x12345300 |            |

| 0x4 | 0x12345400 |            |

| 0x5 | 0x12345500 |            |

| 0x6 | 0x12345600 |            |

| 0x7 | 0x12345700 |            |

| 0x8 | 0x12345800 |            |

| 0x9 | 0x12345900 |            |

| 0xA | 0x12345A00 |            |

| 0xB | 0x12345B00 |            |

| 0xC | 0x12345C00 |            |

| 0xD | 0x12345D00 |            |

| 0xE | 0x12345E00 | 0x42310E00 |

| 0xF | 0x12345F00 |            |

Figure 2.8: A 2-Way Set Associative Cache [3]

- **General Barriers** This kind of barrier enforces that both, memory read and memory write operations are finished, before any of the memory read, memory write operations after the barrier are executed.

- **Read Barriers** If this barrier is used it is guaranteed, that all read operations are located before the barrier are finished before any of the read operations after the barrier are executed. This does not apply for memory write operations.

- **Write Barriers** If this barrier is used it is guaranteed, that all write operations before the barrier are finished before any of the write operations, after the barrier are executed. This does not apply for memory read operations.

- **Data Dependency Barriers** This kind of barrier implements a weaker version of the read barrier. Its usage is restricted to data dependencies only, thus it could be applied if a second read operation directly depends upon a first read operation. This could be the case if the first read operation loads an address, which is used to load data within the second read operation.

Figure 2.9: Categorizing Hardware Parallelism [104]

Eventually, memory barriers in conjunction with cache coherency protocols realize a consistent and ordered view on memory transaction in multi-processor systems.

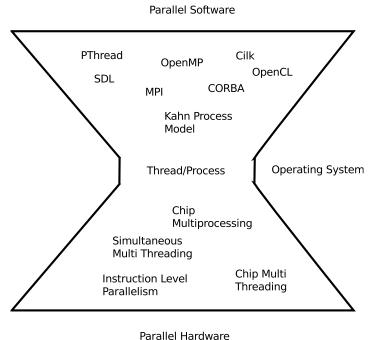

Section 2.2 gave an introduction on parallelism from a hardware point of view. First, several methods of hardware parallelism from instruction level parallelism to chip multithreading were discussed. Second, special issues regarding parallel executing hardware were introduced. This includes the discussion of memory hierarchies, memory consistency in general, as well as techniques to enforce a consistent view on memory transaction during the execution of truly parallel symmetric multi processor systems. Finally, Figure 2.9 presents a hierarchically structured overview on the introduced techniques to implement parallel computing systems. The figure is structured in the following way. The mangled data and instruction streams as described in Section 2.1 are depicted on the outer left side of Figure 2.9. The *Logical Processor* blocks represent a single issue pipeline, capable of implementing Instruction Level Parallelism (ILP). Since it is possible to have several components of such a pipeline available multiple times, the next hierarchical step represents Simultaneous Multithreading (SMT) architectures subsuming Superscalar systems as well. Systems implementing several processor cores of the just mentioned feature are usually called Chip Multi-Processor (CMP) systems. However, CMP architectures implement Superscalar processor cores only. Therefore the term Chip Multi-Threading (CMT) takes SMT capable Central Processing Units (CPUs) into account. From a hardware point of view, the use of the same Instruction Set Architectures (ISAs) on one chip, or on several chips realizing a parallel computing systems can be described as a Symmetric Multi-Processor (SMP) system. Despite, the use of several distinct ISAs would be called an Asymmetric Multi-Processor (AMP) system. This fact is shown in the third layer of Figure 2.9. Finally, a system consisting of several microcomputers is called a multicomputer. This kind of architectures represent distributed memory systems. However, also CMT systems can be realized as distributed memory architectures for example. The subsequent section will introduce software based approaches to exploit hardware provided parallelism.

#### 2.3 Software Parallelism

The previous Section presented numerous methods to potentially accelerate the execution of parallel software by increasing the number of hardware components computing on parallel tasks. Unfortunately, a linear increase of processors on a program with a given percentage of parallel executable code does not result in a linear performance gain. This circumstance is known as Amdahl's law [6], and can be calculated as seen in Equation 2.1, where S(N) is the achieved speedup by using N processors on a program consisting of a parallel portion of P. As shown in Figure 2.10, there exist speedup limits, even when using highly parallel code (P=95%) and more than 1000 processors trying to exploit the available parallelism. However, there exists a relaxation of Amdahl's law which has been proposed by Gustafson [38], stating that it is always possible to achieve speedup by choosing bigger problems. This essentially means that due to increasing computing power (using more and faster processors), it is possible to solve bigger problems in the same time as smaller ones, therefore leading to an overall computational speedup. Nevertheless, Amdahls and Gustafsons law are still applying to today's multi-core system according to Hill et al. [42].

Figure 2.10: Amdahl's Law: Speedup using a program with a parallel portion P [104]

$$S(N) = \frac{1}{(1-P) + \frac{P}{N}}$$

(2.1)

The remainder of this Section is structured as follows: First, a categorization of available approaches in supporting the development of parallel software is given. This categorization is twofold, and presents a tool and a model based taxonomy. Afterwards, the topics synchronization and communication are reviewed from a software point of view. Finally, this Section addresses special issues regarding the truly parallel execution of software. Finally, a short summary concludes Section 2.3.

#### **Categorizing Software Parallelization**

Before addressing special issues in truly parallel executing programs, it is necessary to introduce two techniques in parallel software categorization made by Tröger [104] and Skillicorn [92]. The first method presented by Tröger, will describe ways to develop

parallel software at different supportive levels regarding libraries, languages, or tools. The second categorization approach made by Skillicorn focuses on a model centric view of parallel programming languages. According to Tröger [104] and Popovici [95], there exist various techniques to support programmers in developing parallel software.

- **Compiler Optimization** In this approach, it is the compiler's responsibility to make use of the available processors in the appropriate way. However, it has been shown by Blume et al. [12] that this is very hard to achieve, since the compiler would have to take all possible side effects into account as well. Therefore, this kind of parallelism support is merely limited to loop parallelism, which describes an approach of mapping certain loop constructs to parallel threads, thus reducing the amount of required serial loop iterations.

- **Operating System** The basic concepts of exploiting parallel hardware are provided by operating systems and are known as processes and threads. Hereby, a process can be viewed as a program which is executed in a protected memory area within an operating system environment. Since operating systems are capable of executing several processes in parallel, there arises the need for inter-process communication. However, inter-process communication, as well as processes communicating with operating system components, such as hardware drivers for example, require a certain amount of waiting time, causing these processes to be suspended and woke up by the operating system on demand [97]. Nevertheless, suspending and rescheduling processes results in a throughput decrease of parallel software due to the rather expensive administrative actions<sup>16</sup> that must be performed by an operating system to reschedule a task, for example [92]. Therefore, the concept of threads has been introduced in operating systems [92]. A thread does not have its own operating system protected memory region. Thus context switches within threads associated with a process are faster, and the number one choice for parallel software implementation on operating systems [97]. This argument is supported by the fact that a large number of parallel programming libraries, virtualization environments, and languages, actually use threads in order to glue their concepts of parallelism to the operating system. Tröger [104] calls this the hour-glass of parallel software since a lot of parallel software solutions encompass threads to

<sup>&</sup>lt;sup>16</sup>Saving context of currently running process and restoring context of to be run process [97].

utilize a larger number of hardware components providing parallelization support (See Section 2.2).

Application Level The application level is formed by immanent parallel programming languages, extension to sequential languages, as well as domain specific languages encompassing parallelism in high-level language constructs [104]. However, since most of today's programs are written in C,C++ or Java, the most common parallel programs are actually implemented using language extension such as Open Multi Programming (OpenMP) [89], Message Passing Interface (MPI) [35], Cilk<sup>17</sup>, or rely directly on one of the available threading libraries such as PThread<sup>18</sup>, for example. Despite the large success of parallel extensions for sequential languages, languages implementing a parallel programming model by design are not very widespread. Instead, only few of the many parallel languages, which have been proposed remained. Amongst them are substitutes like High Performance Fotran [62], and OCCAM [71]. In contrast to general purpose languages like C or Java, domain specific languages focus on specific problem domains, like formal verification (Promela<sup>19</sup>) or database queries (SQL). Due to their high grade of abstraction for their specific problem field, some domain specific languages are not Turing complete [99].

Regardless of the used parallelism approach, software engineers have to decide on the degree of control they want to have when writing parallel software [104]. In order to be able to choose the right granularity of control for each task, Skillicorn et al. [92] identified five key concepts a programming model might hide before its developer, in order to aid her producing productive code. These concepts are:

- Concurrency or parallelism of the software,

- Decomposition of the software into parallel threads,

- Mapping of threads to processors,

<sup>&</sup>lt;sup>17</sup>http://supertech.csail.mit.edu/cilk/-Last visit: 04/12/2012

<sup>&</sup>lt;sup>18</sup>http://www.gnu.org/software/pth/ - Last visit: 04/12/2012

<sup>&</sup>lt;sup>19</sup>http://www.dai-arc.polito.it/dai-arc/manual/tools/jcat/main/ node168.html-Last visit: 04/13/2012

- Communication among threads,

- Synchronization among threads.

Constituitively, Skillicorn defined six abstraction levels on base of his five key concepts. These levels of abstraction are presented in reverse order of abstraction. Thus the last mentioned abstraction level provides the greatest degree of freedom, but leaves almost all parallel programming challenges to the programmer.

- 1. The most abstract parallel programs are formed by languages implementing models that abstract parallelism completely. Therefore, the programmer has only to consider the meaning of the program, rather than how their program will execute in parallel. An example for languages implementing this model is Crystal [18].

- 2. The second kind of programming models is implemented by languages in which parallelism is made explicit, but decompositions of programs into threads, communication and synchronization is not. Therefore, programmers must only be aware of the fact, that their algorithm will be executed in parallel, but not how this is done. Such models oblige programs to express the maximal amount of parallelism, however the amount of used parallelism depends on the architecture the programs eventually operates on. An example for languages implementing this model is OpenMP [89].

- 3. The third abstraction level describes models where it is necessary to cope with parallelism and decomposition explicitly. However, thread mapping, synchronization and communication are done by the language implementing the model. An example for languages implementing this model is the specification language SDL [15], which is used by the ITU-T to model telecommunication protocols.

- 4. This model demands that software developers have to consider parallelism, decomposition, and mapping explicitly. However, the tasks synchronization and communication is done by the language realizing the model. When using such languages, the developer is required to have knowledge on the underlying architecture, since his mapping decisions will inevitably influence the software's performance on this architecture. Therefore, it is a challenge to design software

using this model in a portable way. An example for languages implementing this model is CORBA [36].

- 5. The fifth level of abstraction demands that the programmer is able to deal with the tasks parallelism, decomposition, mapping, and communication explicitly. Synchronization is done implicit by the language. An example for languages implementing this model is the Kahn Process Language [50].

- 6. This model offers the greatest degree of freedom to the programmer, as he has to consider all five concepts explicitly. However, according to [92,95] it is "extremely difficult to build software using such models, because both correctness and performance can only be achieved by attention to vast numbers of details". An example for languages implementing this model is the specification language OpenMPI [35].

Beside the taxonomies of parallel software, there exist special issues that have to be taken into account when executing parallel programs on parallel hardware.

## Special Issues regarding Software executed on truly Parallel Executing Processors

Subsection "Special Issues regarding truly Parallel Executing Processors" on page 14 mentioned two issues regarding parallel hardware, namely, consistency, and synchronization. This Subsection will investigate these two points from a software point of view.

#### Synchronization & Communication

In Subsection "Special Issues regarding truly Parallel Executing Processors" on page 14 synchronization upon a central resource has been contemplated from a processor's instruction sets point of view. Usually, when developing parallel software on behalf of an operating system, none of these issues are of concern, except the issues arising when using the different types of synchronization primitives. The terms and techniques introduced in this thesis, apply for uni-core and multi-core systems. This is true since on uni-core systems it is also possible to execute processes in a parallel manner. Nevertheless,

Figure 2.11: Special Issues in parallel programs

one has to synchronize processes and threads when trying to access a mutual exclusive resource. Since this is a very common problem in software engineering so called Inter Process Communication (IPC) methods have been defined [97]. These methods are usually provided, and exported to the programmer by the operating system. Amongst them are Locks, Semaphores, Sockets, Signals and Message. However, these synchronization tools may lead to the following issues in a program when not used properly [97]:

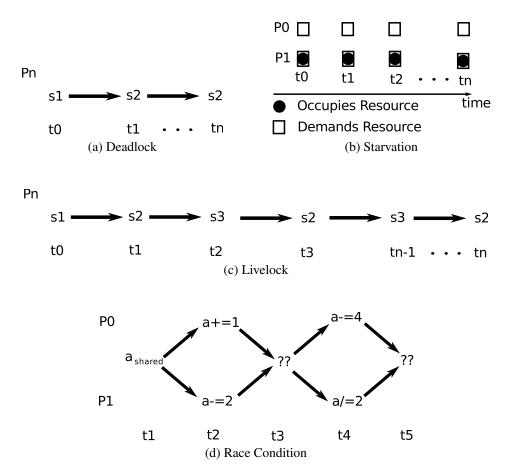

**Race Condition** This term describes a particular error occurring in parallel programs. It happens when the result of a concurrent program depends on the order the participating processes are scheduled. This kind of errors are usually hard to detect, since it is not easy to reproduce them in a deterministic way. However, race conditions result from synchronization errors. An example race condition is shown in Figure 2.11d. Here, two processes P0 and P operate on a shared variable a. However, P0 and P1 do not synchronize upon the access on a. Therefore, the outcome of the parallel executed equations at time t3 and t5 is arbitrary since the read and write order is not deterministic.

- **Deadlock** If the advance of at least two processes depend on each other in a circular way resulting in a state where none of the processes can make an advance, this is called a deadlock. The situation might occur when process 0 has occupied resource A, and needs to occupy resource B as well, thus waiting for B to be freed. However, process 1 has already occupied resource B and needs to occupy resource A as well, thus waiting for resource A. Therefore both processes wait for the release of their missing resource without releasing their already occupied one. Thus leads to the state where process 0 and process 1 will wait forever, thus forming a deadlock. This example can also be viewed from a state transition perspective, as it is done in Figure 2.11a. Here, the progress of a program is reflected by a state change from sx to sx+1, thus an ongoing state change from sx to sx would reflect a deadlock, since it would show now progress in the program execution. As a consequence, process Pn in Figure 2.11a shows a deadlock since from time t1 to time tn the process stays in state s2.

- **Livelock** Basically a livelock is the same as a deadlock, except for the fact that processors can still advance in circles inside a livelock, but cannot leave the circle, thus spinning there forever. This instant is reflected by Figure 2.11c, where a process Pn enters a loop from time t3 to time tn.

- **Starvation** When a set of processes want to access a mutual exclusive resource like, a network interface card for example, but at least on of these processes is never allowed to interact with the resource (e.g. because its priority is too low), then this process suffers from starvation. This parallel programming issue is depicted by Figure 2.11b. Here, the processes P0 and P1 compete for a mutual exclusive resource. However, although both processes demand that resource, only process P1 gets access granted to it, thus leading to a starvation of process P0.

- **Convoying** Assume a set of truly parallel executing processes operating on several mutual exclusive resource protected by a synchronization primitives like locks. If the order of access to these shared resource is of matter, it is possible that all processes competing for the resource end up accessing the mutual exclusive resource in a serial way. This is called convoying, like a convoy of trucks driving serially on a high-way [69].

- **Priority Inversion** This phenomenon can occur when a high priority process cannot access a shared resource, because a process with a lower priority has occupied the lock and is currently preempted. Therefore, the lower priority process causes the high priority one to wait, thus inverting the access priority. [69]

Finally, it is the programmer's responsibility to be aware of these side effects regarding parallel programming. The following subsection discusses memory consistency from a software point of view.

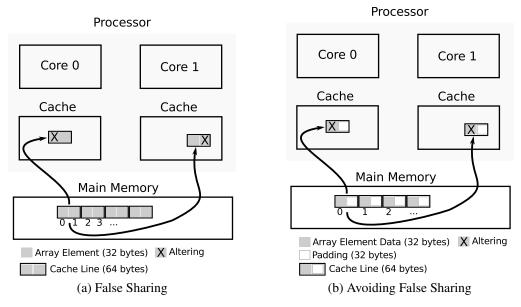

#### Consistency

From a software developer's point of view, memory consistency is guaranteed when she obeys the rules of synchronization and avoids race conditions. However, when developing parallel software on shared memory systems there exists certain potential to introduce performance bottle necks by ignoring the processor's cache architecture. Consider the code example depicted on Listing 2.3 with respect to a cache with a line size of 64 bytes. The used processor is a two core 32-bit CPU, with an integer size of 4 byte. In this example, an array *sh\_array* is used to house 128 elements of type *struct container*, whereas each element requires 32 bytes of storage. The two functions *thread\_operate\_on\_even* and *thread\_operate\_on\_odd* will be executed concurrently, where each thread is going to be placed on a dedicated core of the processor. As it can be seen there is no thread synchronization required since thread 1 will only operate on even array indices, and thread 2 will manipulate odd array elements only. Therefore, it may be assumed that this kind of task partitioning will result in a speedup of 100%. However, this assumption is shown to be incorrect due to false sharing [14].

Listing 2.3: Example code to evocate False Sharing

1 struct container {

Figure 2.12: False Sharing and its avoidance

```

2

unsigned int id;

3

unsigned char data [28];

4

};

5

6

struct container sh_array [128]; /* will be shared */

7

8

/*thread 1*/

9

void *thread_operate_on_even(void *arg) {

for (i = 0; i < 128; i = i+2)

10

11

sh_array[i] = calc_on_even(sh_array[i]);

12 }

13

/*thread 2*/

14

15

void *thread_operate_on_odd(void *arg) {

for (i = 1; i < 128; i = i+2)

16

17

sh_array[i] = calc_on_odd(sh_array[i]);

18

}

```

False sharing happens when the software developer does not consider the line size of its processors cache. In our case, a cache line is 64 bytes large. However, an item of the container array occupies 32 bytes only, therefore, two consecutive array elements are stored within a 64 byte long memory block. Since thread<sup>20</sup> 1, running on processor core 0, operates on even, and thread 2, running on processor core 1, manipulates odd array elements each processor core invalidates the whole cache line, once it writes to its memory location. As a consequence the cache coherence protocol is triggered to update the cache line in memory, thus leading to a response time increase due to memory latency implied by a forced cache miss. This results in crippling the performance of the two threads operating on mutual memory regions within a shared cache line. This instance is also reflected in Figure 2.12a.

A straight forward solution to avoid false sharing is the introduction of padding bytes as it can be seen in Listing 2.4, line 5. Here the array called *padding* has no productive purpose, it is just available to occupy another 32 bytes of memory to achieve cache line alignment. However, it is not guaranteed that the array will start at a 64 byte address boundary. Therefore it is necessary to align the beginning of the structure to the desired address boundary manually. This is done in line 6. The compiler attribute is dedicated to be used with the GNU C compiler<sup>21</sup> only. Nevertheless, on systems operating Microsoft Windows, one can use  $\_declspec(align(x))^{22}$  as prefix before the variable declaration to achieve an alignment on an address boundary of x bytes. As a result, the cache coherence protocol will not invalidate the cache line when parallel executed processes on mutual processors access two adjacent, but independent array elements.

#### Listing 2.4: Example code to avoid False Sharing

```

1 struct container {

2 unsigned int id;