The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

FAKULTÄT FÜR !NFORMATIK Faculty of Informatics

# Experimental Framework for Controller Area Network based on a Multi-Processor-System-on-a-Chip

# DIPLOMARBEIT

zur Erlangung des akademischen Grades

# Diplom-Ingenieur

im Rahmen des Studiums

# Technische Informatik

eingereicht von

# Walther Operenyi

Matrikelnummer 0407269

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung Betreuer/in: Prof. Dipl.-Ing. Dr.techn. Roman Obermaisser Mitwirkung: Univ.Ass. Dipl.-Ing. Roland Kammerer

Wien, 03.12.2012

(Unterschrift Verfasser)

(Unterschrift Betreuer/in)

"Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe."

Wien am 03.12.2012

#### Abstract

Controller Area Network (CAN) is used for sending and receiving short real-time messages up to 1 Mbit/s. CAN is mainly used in the car industry to interconnect Electronic Control Units (ECUs) so that the ECUs communicate via messages. Each message has a unique id and a payload. Furthermore, each message with a unique id is sent repeatedly on demand to transport control information via its payload. The control information is generated and accepted by control tasks. Each task fulfills a well-defined operation purpose and is executed by an ECU. Therefore the unique id of a message definitely tags the control information in order to address tasks and ECUs. In addition, the message id determines the priority of a message. Each CAN message that is ready for transmission starts to emit if no message is in transmission. As multiple messages start to emit simultaneously the priority of a message determines its transport so that the message with the highest priority transmits and the remaining messages stop to emit. The remaining messages are sent afterwards. Thus the transmission times (difference between message generation and reception) of each message with a unique id vary.

Typically, many tasks in a CAN system have to concurrently exchange data and control information in real-time. Low transmission latencies and a low variability of the transmission latencies are important to ensure high control performance. In this diploma thesis an experimental evaluation technique is presented to determine statistical data of the transmission behaviour in CAN such as the maximum, minimum and average transmission latencies. Therefore a hardware platform was developed that consists of processors that emulate ECUs. Furthermore, tasks are simulated on each processor which generates messages of the same unique id randomly but within limited time intervals. These messages are transmitted via CAN and the transmission times are measured to derive statistical data. In addition, auxiliary parameters are collected such as number of sent and received messages at each particular processor. Furthermore, a complete toolchain is presented to design test configurations and analyze statistical data.

CAN has a good average transmission time behaviour but the transmission times are sometimes extremely delayed. In general, the transmission times are reduced if the collision probability is decreased. The collision probability is determined by the number of messages and by the send frequency of each message with a unique id. Thus the collision probability determines the utilization of the transmission medium.

#### Kurzfassung

Controller Area Network (CAN) dient zum Senden und Empfangen von kurzen Echtzeitnachrichten bei einem Datendurchsatz von bis zu 1 Mbit/s. Die Automobilindustrie setzt CAN für die Vernetzung von Electronic Control Units (ECUs) ein. Die Vernetzung ist mittels Nachrichtenübertragung realisiert. Eine Nachricht besteht aus einer eindeutigen Kennung und Nutzdaten. Eine Nachricht wird bei Bedarf instanziert und übertragen um Kontrollinformation zu senden. Kontrollinformation wird von Prozessen generiert und entgegengenommen und dient zum Regeln und Steuern. Ein Prozess erfüllt einen eindeutig definierten Zweck und wird auf einer ECU ausgeführt. Hierbei bezeichnet die Kennung die Nutzdaten um Prozesse und ECUs zu adressieren. Darüber hinaus bestimmt die Kennung die Priorität einer Nachricht. Eine Nachrichtenübertragung beginnt falls keine Nachtrichtenübertragung stattfindet. Falls mehrere Nachrichtenübertragungen gleichzeitig starten wird ausschließlich die Nachricht mit der höchsten Priorität transportiert. Die restlichen Nachrichten werden anschließend versandt. Aus den oben genannten Gründen fluktuieren die Transportzeiten für den Nachrichtenversand. Die Transportzeit ist die Differenz zwischen der Nachrichteninstanzierung und dem Empfang.

Prozesse müssen teilweise innerhalb einer Zeitschranke terminieren und daher muss Kontrollinformation rechtzeitig zur Verfügung stehen. Darüber hinaus ist ein optimierter mittlerer Datendurchsatz erforderlich da die Leistungsfähigkeit vieler Prozesse von der mittleren Reaktionszeit abhängt. In dieser Diplomarbeit wird eine experimentelle Evaluierungsmethode vorgestellt, welche statistische Daten betreffend des Transportverhaltens ermittelt. Hierfür wurde eine Hardwareplattform entwickelt, welche aus Prozessor besteht um ECUs zu emulieren. Des weiteren werden auf jedem Prozessor Prozesse simuliert, welche jeweils Nachrichten mit einer eindeutigen Kennung während eines zufälligen und beschränkten Zeitintervalls generieren. Die instanzierten Nachrichten werden mittels CAN verschickt und mit Hilfe der ermittelten Transportzeiten statistische Daten berechnet. Darüber hinaus werden zusätzliche Parameter wie z.B. die Anzahl der versandten und empfangen Nachrichten bei jedem Prozessor bestimmt. Des weiteren wird eine komplette Toolchain vorgestellt, welche zum Entwurf von Testkonfigurationen und Auswertung von ermittelten statistischen Daten dient.

CAN weist akzeptable durchschnittliche Transportzeiten für die Nachrichtenübertragung auf. Jedoch treten sporadisch extremst verzögerte Transportzeiten auf. Die Transportzeiten sind bei einer geringeren Kollisionswahrscheinlichkeit reduziert. Die Kollisionswahrscheinlichkeit wird durch die Anzahl der Nachrichten sowie durch die Sendefrequenz jeder einzelnen Nachricht bestimmt. Die Kollisionswahrscheinlichkeit bestimmt die Auslastung des Transmissionsmedium.

#### Danksagung

Diese Arbeit entstand am Institut für Technische Informatik, Abteilung Echtzeitsystem, an der Technischen Universiät Wien.

Besonderen Dank richte ich an den Betreuer dieser Diplomarbeit, Prof. Dr. Roman Obermaisser, der mir die Möglichkeit geboten hat dieses ansprechende Projekt zu realisieren. Durch seine Denkanstöße und die Diskussion mit ihm entstanden zahlreiche elegante Lösungsansätze. Darüber hinaus möchte ich mich bei Univ.Ass. Dipl.-Ing. Roland Kammerer für die hilfreiche Unterstützung, Diskussionen und Gegenlesen meiner Diplomarbeit erkenntlich zeigen. Außerdem gilt mein Dank BSc Bernhard Frömel für die Unterstütung bei der Implementierung.

Mein herzlichster Dank gilt meinem Freund Dr. Daniel Ambort für das Kontrolllesen meiner Diplomarbeit und die aufheiternden Gespräche.

Außerdem bedanke ich mich für die konstruktiven Gespräche mit Prof. Dr. Herbert Grünbacher, Dr. Christian Paukovits und Dipl.-Ing. Jakob Lechner.

Ich danke des weitern Ing. Leo Mayerhofer für die technische Projektunterstützung und Maria Ochsenreiter für die administrative Hilfe.

Schließlich danke ich meiner Mutter, die mir dieses Studium ermöglicht hat.

# Contents

| Ab | stract                                                                                                                                                                                                              | iii                               |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Kı | rzfassung                                                                                                                                                                                                           | v                                 |

| Da | iksagung                                                                                                                                                                                                            | vii                               |

| Co | ntents                                                                                                                                                                                                              | ix                                |

| Li | t of Figures                                                                                                                                                                                                        | X                                 |

| Li | t of Tables                                                                                                                                                                                                         | xii                               |

| 1  | Introduction                                                                                                                                                                                                        | 1                                 |

| 2  | Related Work         2.1       Multilevel Inspection of Multiple CAN-Networks         2.2       Emulation of CAN Networks         2.3       Worst-Case Response Time Analysis         2.4       Stochastic Analysis | 5<br>5<br>7<br>9<br>12            |

| 3  | Basic Concepts         3.1 Controller Area Network         3.2 Star Network         3.3 Hardware in the Loop         3.4 System on Chip                                                                             | <b>17</b><br>17<br>30<br>36<br>39 |

| 4  | System Model4.1System Structure4.2Experimental Model                                                                                                                                                                | <b>47</b><br>47<br>54             |

| 5  | Prototype Setup and Experiments5.1Explanation of Structure5.2Explanation of Structure Elements5.3Experimental Process5.4Experiments                                                                                 | <b>57</b><br>57<br>59<br>66<br>68 |

| 6  | Res              | ults                            | 71  |  |

|----|------------------|---------------------------------|-----|--|

|    | 6.1              | 4 CSDs - No Ramp MCE            | 71  |  |

|    | 6.2              | 8 CSDs - No Ramp MCE            | 73  |  |

|    | 6.3              | 4 CSDs - High Priority Ramp MCE | 76  |  |

|    | 6.4              | 8 CSDs - High Priority Ramp MCE | 84  |  |

|    | 6.5              | 4 CSDs - Low Priority Ramp MCE  | 90  |  |

|    | 6.6              | 8 CSDs - Low Priority Ramp MCE  | 96  |  |

| 7  | Disc             | eussion                         | 101 |  |

|    | 7.1              | Test System                     | 101 |  |

|    | 7.2              | Interpretation of Data          | 103 |  |

|    | 7.3              | Collision Probability           | 106 |  |

|    | 7.4              | Errors and Overload Frames      | 107 |  |

|    | 7.5              | Emission Rate and Utilization   | 108 |  |

|    | 7.6              | Future Work                     | 109 |  |

|    | 7.7              | Conclusion                      | 110 |  |

| Li | List of Acronyms |                                 |     |  |

| Bi | Bibliography     |                                 |     |  |

# **List of Figures**

| 2.1 | OSI model                                                                                    | 5  |

|-----|----------------------------------------------------------------------------------------------|----|

| 2.2 | System architecture of Multilevel Inspection[Nov09]                                          | 7  |

| 2.3 | Convolution ( $\mathcal{W}_t^P \star f_{\mathcal{E}_i}$ ) and shrinking of $\mathcal{W}_t^P$ | 13 |

| 2.4 | Calculation of a PMF for a characteristic message                                            | 14 |

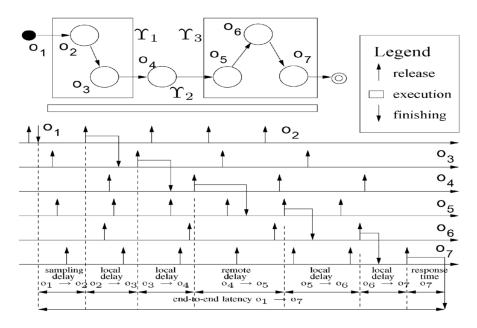

| 2.5 | End-to-end latency of a path $\Pi_{o_1,o_7}$ [ZNGSV09]                                       | 16 |

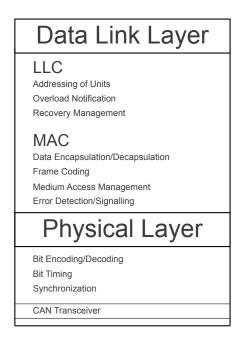

| 3.1 | CAN Layers                                                                                   | 17 |

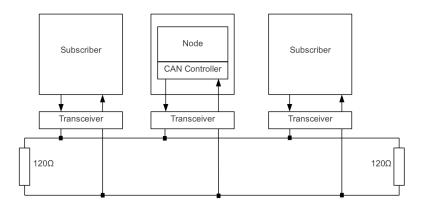

| 3.2 | CAN Bus with 3 attached subscribers                                                          | 19 |

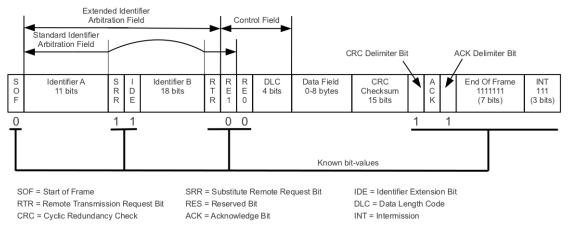

| 3.3 | Data/Remote Frame                                                                            | 21 |

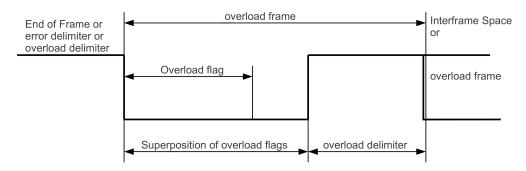

| 3.4 | Overload Frame                                                                               | 25 |

| 3.5 | CAN: bit time                                                                                | 28 |

| 3.6 | Principle layout of a CAN Transceiver                                                        | 29 |

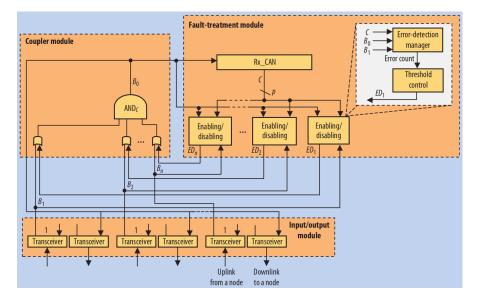

| 3.7 | CANcentrate architecture[BPA09]                                                              | 32 |

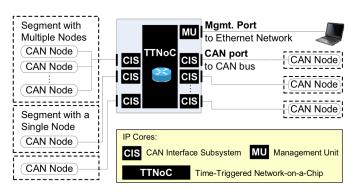

| 3.8 | Architecture of the CAN router[KOF12]                                                        | 35 |

| 3.9 | Real-time HIL testing                                                                        | 36 |

|     |                                                                                              |    |

| 3.10 | Flow of the SystemC scheduler[FYS10]                                                                                             | 37  |

|------|----------------------------------------------------------------------------------------------------------------------------------|-----|

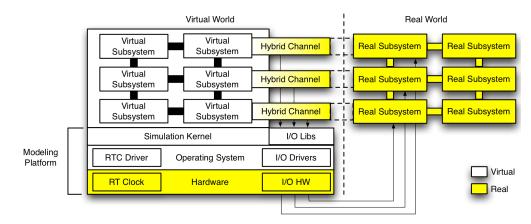

| 3.11 | Architecture of a HIL and HW/SW co-design for real-time embedded systems[FYS10]                                                  | 38  |

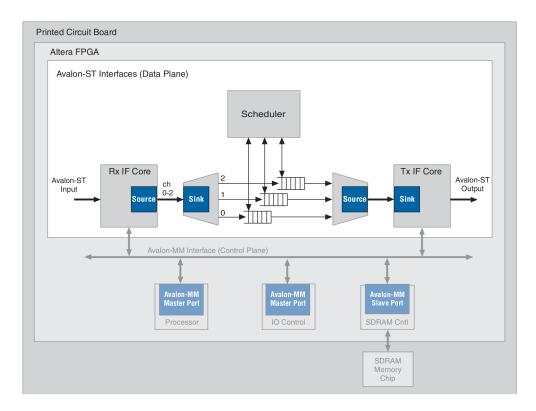

| 3.12 | Layout of Altera Streaming Interface[Alt11a]                                                                                     | 42  |

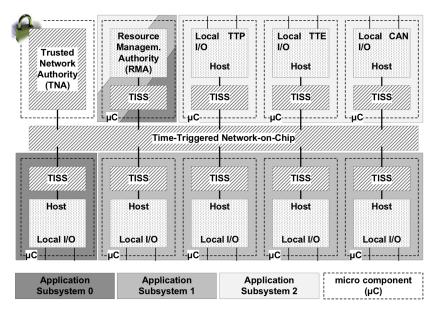

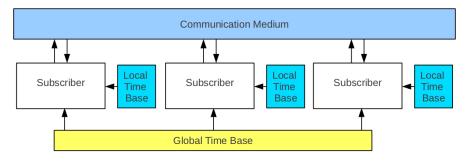

| 3.13 | Structure of the TTSoC architecture[Pau08]                                                                                       | 44  |

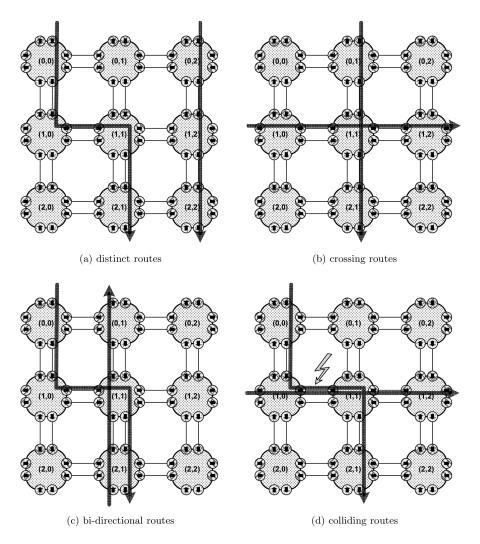

| 3.14 | Simultaneous routes in a network-on-chip[Pau08]                                                                                  | 45  |

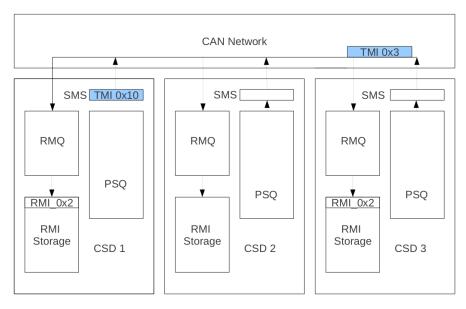

| 4.1  | Structure of the test platform                                                                                                   | 47  |

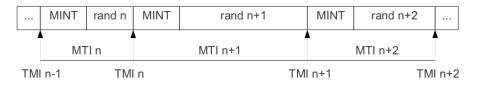

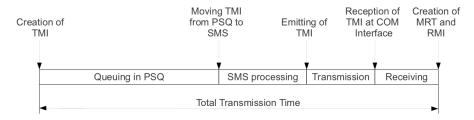

| 4.2  | Message Time Intervals of a Message (TMI)                                                                                        | 49  |

| 4.3  | Transmission and Transmission Time of a Message                                                                                  | 51  |

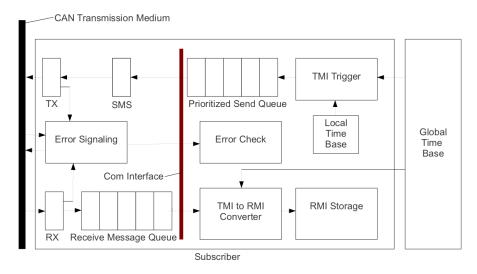

| 4.4  | Block Diagram of a CAN Simulation Device                                                                                         | 52  |

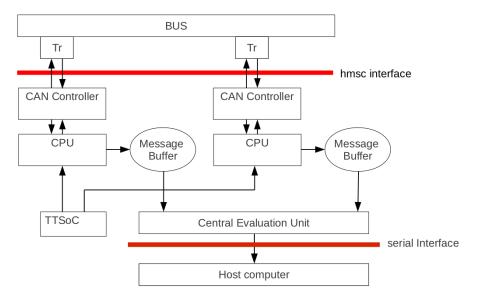

| 5.1  | Interfaces of the prototype                                                                                                      | 58  |

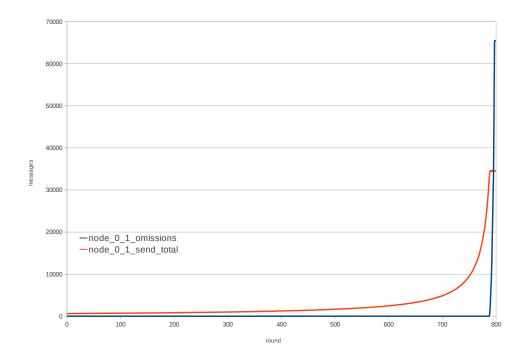

| 6.1  | Total sent TMIs and send omissions of MCE 0x1 in the test system with 4 CSDs and a high priority Ramp MCE                        | 78  |

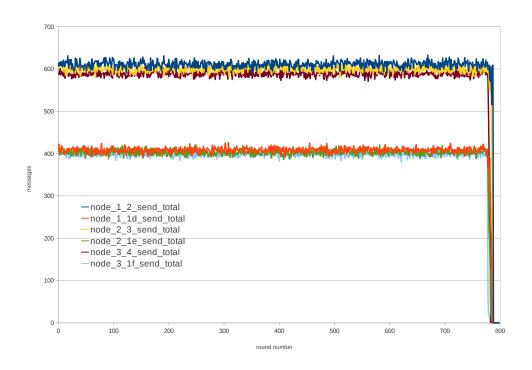

| 6.2  | Total sent TMIs of MCEs 0x2, 0x3, 0x4, 0x1d, 0x1e, 0x1f in the test system with 4 CSDs and a high priority Ramp MCE              | 79  |

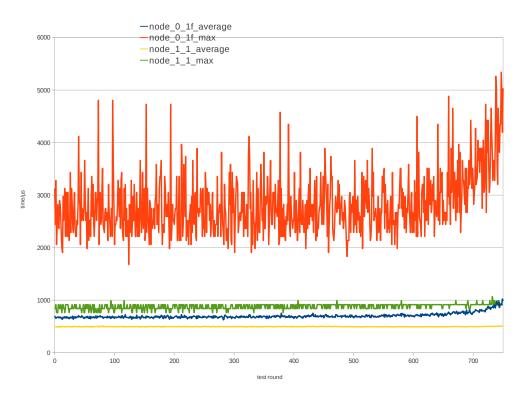

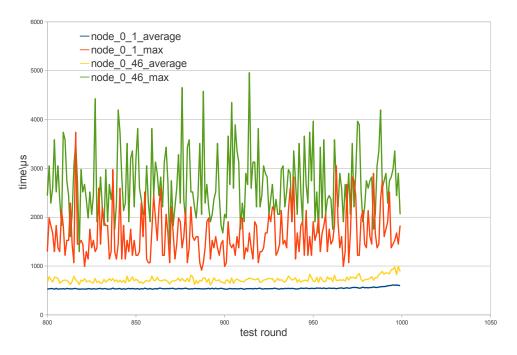

| 6.3  | Total maximum and average transmission times of MCE 0x1 and MCE 0x1f in the test system with 4 CSDs and a high priority Ramp MCE | 80  |

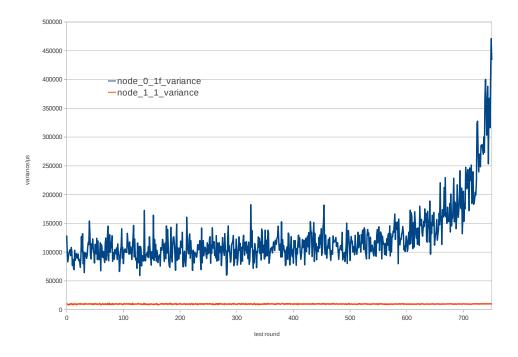

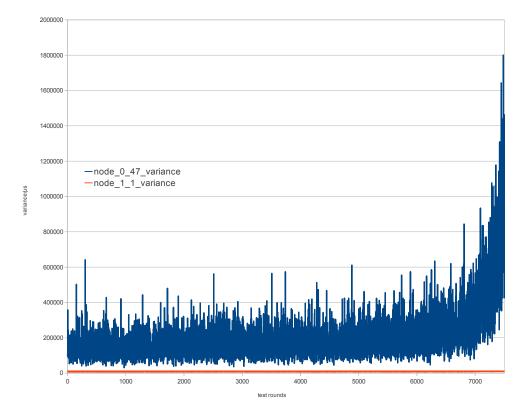

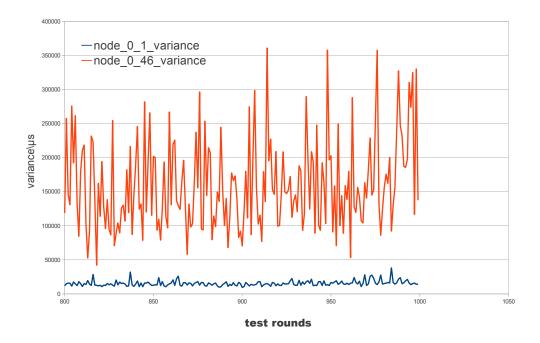

| 6.4  | Measured variances of MCEs 0x1 and 0x1f in the test system with 4 CSDs and a high priority Ramp MCE                              | 83  |

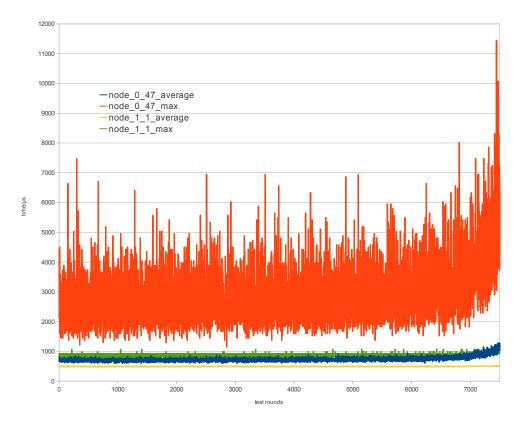

| 6.5  | Total maximum and average transmission times of MCE 0x1 and MCE 0x46 in the test system with 8 CSDs and a high priority Ramp MCE | 87  |

| 6.6  | Measured variances of MCEs 0x1 and 0x47 in the test system with 8 CSDs and a high priority Ramp MCE                              | 90  |

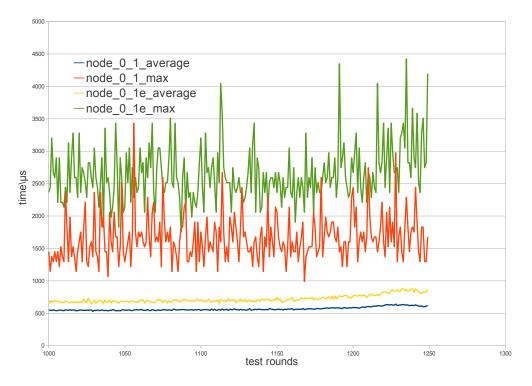

| 6.7  | Total maximum and average transmission times of MCE 0x1 and MCE 0x1e in the test system with 4 CSDs and a low priority Ramp MCE  | 93  |

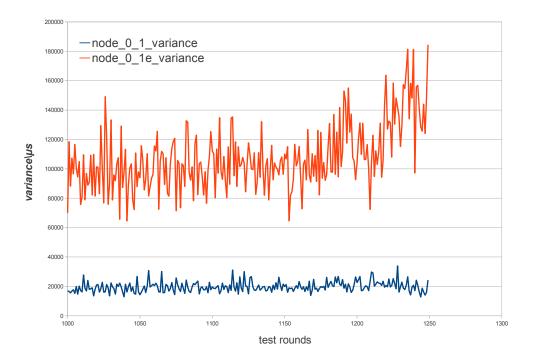

| 6.8  | Measured variances of MCEs 0x1 and 0x1e in the test system with 4 CSDs and a low priority Ramp MCE                               | 95  |

| 6.9  | Total maximum and average transmission times of MCE 0x1 and MCE 0x46 in the test system with 8 CSDs and a low priority Ramp MCE  | 97  |

| 6.10 | Measured variances of MCEs 0x1 and 0x46 in the test system with 4 CSDs and a low priority Ramp MCE                               | 99  |

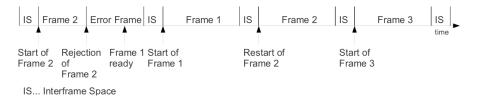

| 7.1  | Blocking of a triggered messages                                                                                                 | 106 |

| 7.2  | Delay of frames due to an erroneous frame                                                                                        | 108 |

|      |                                                                                                                                  |     |

# **List of Tables**

| 3.1        | Length of the payload (data field) denoted by the Data Length Code                                                           | 22       |

|------------|------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.2<br>3.3 | CAN: bit time                                                                                                                | 28<br>30 |

| 4.1        | Test run configurations                                                                                                      | 56       |

| 6.1        | Mean, minimum, maximum and standard deviation of the send behavior of a test system with 4 CSDs and a RSTEP of zero          | 72       |

| 6.2        | Mean and maximum statistics of the transmission times of a test system with 4 CSDs and a RSTEP of zero                       | 72       |

| 6.3        | Total maximum transmission times of each CSD of a test system with 4 CSDs and a RSTEP of zero                                | 73       |

| 6.4        | Variance statistics of the transmission times of a test system with 4 CSDs and a RSTEP of zero                               | 73       |

| 6.5        | Mean, minimum, maximum and standard deviation of the send behavior of a test system with 8 CSDs and a RSTEP of zero          | 74       |

| 6.6        | Mean and maximum statistics of the transmission times of a test system with 8 CSDs and a RSTEP of zero                       | 75       |

| 6.7        | Total maximum transmission times of each subscriber of a test system with 8 CSDs and a RSTEP of zero                         | 75       |

| 6.8        | Variance statistics of the transmission times of a test system with 8 CSDs and a RSTEP of zero                               | 76       |

| 6.9        | Mean, minimum, maximum and standard deviation of the send behavior of a test system with 4 CSDs and a high priority Ramp MCE | 70       |

| 6.10       | Mean and maximum statistics of the transmission times of a test system with 4 CSDs and a high priority MCE                   | 82       |

| 6.11       | Total maximum transmission times of each CSD of a test system with 4 CSDs and a high priority Ramp MCE                       | 82       |

| 6.12       | Variance statistics of the transmission times of a test system with 4 CSDs and a high priority Ramp MCE                      | 85       |

| 6.13       | Mean, minimum, maximum and standard deviation of the send behavior of a test system with 8 CSDs and a high priority Ramp MCE | 86       |

| 6.14       | Mean and maximum statistics of the transmission times of a test system with 8 CSDs and a high priority MCE                   | 88       |

| 6.15       | Total maximum transmission times of each CSD of a test system with 8 CSDs and a high priority Ramp MCE                       | 89       |

| 6.16       | Variance statistics of the transmission times of a test system with 8 CSDs and a high priority Ramp MCE                      | 91       |

| 6.17 | Mean, minimum, maximum and standard deviation of the send behavior of a test                                                     |     |

|------|----------------------------------------------------------------------------------------------------------------------------------|-----|

|      | system with 4 CSDs and a low priority Ramp MCE                                                                                   | 92  |

| 6.18 | Mean statistics of the transmission times of a test system with 4 CSDs and a low priority Ramp MCE                               | 94  |

| 6.19 | Total maximum transmission times of each CSD of a test system with 4 CSDs and a low priority Ramp MCE                            | 94  |

| 6.20 | Variance statistics of the transmission times of a test system with 4 CSDs and a low                                             | 71  |

|      | priority Ramp MCE                                                                                                                | 95  |

| 6.21 | Mean, minimum, maximum and standard deviation of the send behavior of a test system with 8 CSDs and with a low priority Ramp MCE | 96  |

| 6.22 | Mean and maximum statistics of the transmission times of a test system with 8 CSDs                                               |     |

|      | and with a low priority Ramp MCE                                                                                                 | 98  |

| 6.23 | Total maximum transmission times of each CSD of a test system with 8 CSDs and                                                    |     |

|      | a low priority Ramp MCE                                                                                                          | 98  |

| 6.24 | Variance statistics of the transmission times of a test system with 8 CSDs and a low                                             |     |

|      | priority Ramp MCE                                                                                                                | 100 |

xiii

# CHAPTER

# Introduction

A transmission is the transfer of structured information (data) over a distance. Transmissions are mediated by physical carriers (transmission media) and regulated by subscribers that receive or send transmissions. Furthermore, the transmission media and subscribers are interconnected either directly from subscriber to transmission medium or indirectly via transmission media themselves. One example of a direct interconnection is the Controller Area Network (CAN) bus where the transmission medium is accessed by the CAN standard. CAN bus is used for sending and receiving short real-time messages up to 1 Mbit/s[fS03]. Each message consists of an identifier (id) for tagging and a payload for user data. Furthermore, each message can only be sent if there is no message in transmission. Therefore an error-free message transmission cannot be interrupted. Moreover, messages are related to priorities so that the unique priority (id) of a message determines which message will be transmitted if multiple messages start to transmit simultaneously (prioritization of messages). The prioritization of messages is a main feature of CAN because collided messages (message collisions) will not cause the retransmission at arbitrary later time points. Each collision will be resolved (called arbitration) such that the message with the highest priority will be transmitted and the remaining messages will be transmitted afterwards. Therefore each subscriber has equal communication rights and hence CAN is a multimaster system. The complete CAN standard is explicitly explained in Subsection 3.1.

There are about 800 million CAN Controllers (controller chip that handles the CAN communication) sold per year and the sale volume is still increasing[Zel11]. Furthermore, CAN is mainly used in the car industry[MMTS11]. In addition, the Society of Automotive Engineers Vehicle Network Committee divided auto data transmission networks (a network consists of subscribers which exchange information via physical carriers) into 3 types (A, B and C) according to the SAE J2057 standard[LPL11]. Class A are low speed applications such as a power window actuator, class B are medium speed applications that require fast reaction times and class C are high speed applications. Applications based on CAN are in classes B and C. Furthermore, especially class C networks require predictable transmission times (time difference between message generation and reception at a receiver) because CAN is used for embedded systems such as a power-train control module. Such a power-train control module has to determine each result in time and therefore it requires information transmitted via CAN in time (time-critical). Therefore the longest transmission time is a main property in a communication system. Each communication system (communication network) consists of independent locations (called Electronic Control Unit (ECU) in an automotive system) that executes processes (processes form together applications) and the processes exchange information via messages. Furthermore, a communication system requires also a minimized average transmission time behaviour because many applications are not time-critical but the performance of the controls depend on the average response times[ZNGSV09]. Each response time is the difference between the time point of an action and the time point to react with such a corresponding action.

The determination of the time behaviour of CAN is difficult for multiple reasons (exemplarily)[PV03]:

- Messages can be generated at different locations (ECUs) without synchronization

- Message collisions

- An error management that is handled by the subscribers themselves (each CAN Controller is responsible for the reduction of its communication privileges if it acts erroneously). The error management influences the transmission behaviour of the erroneous CAN Controller

- Erroneously transmitted messages which delay all queued messages including the erroneous message due to retransmission and transmission of a part of the erroneous message

Furthermore, there are many techniques available to determine the time transmission behaviour of CAN. In Subsection 2.1 a hardware platform was developed to test CAN by explicit test cases so that messages are triggered in time or by events so that message transmissions are explicitly interrupted, etc. The advantages of such a test method are the following: 1) CAN will be tested in real-time and 2) test cases can be explicitly forced. The disadvantage of such a hardware platform is that test cases have to be defined. Therefore only defined test cases are considered and unintended behaviour will not be unaccounted for.

In Subsection 2.2 CAN networks were emulated via simulation software. The advantages of such methods are a fast implementation of a CAN network and that the simulation time advances faster than in real-time. The disadvantages of such methods are that its hard to model the complete CAN standard and that the test method is not fully adequate to a real CAN network.

There are formal methods available which are mainly base on a work from Tindell et al.[TBW95] to determine the longest possible transmission time (worst-case transmission time) for each CAN message (for each identifier). The worst-case transmission time is an important property for applications which must finish within a certain time interval[Kop97]. Such a method is exemplarily presented in Subsection 2.3. The advantages of such formal methods are that the transmission time behaviour is obtained for the assumed worst-case transmission time obtained rapidly. The disadvantage of such methods is that the worst-case transmission time appears with a very low possibility. Such a possibility of a worst-case transmission time can

be lower than a probability of a hardware failure[ZNGSV09]. Furthermore, it is not possible to fully design the CAN system properties. Therefore many decisions have to be made that will be detrimental or will not meet the bus properties due to of unintended behaviour. In addition, such methods can be determined with more optimistic assumptions that are non-trivial to design. One example of such an approach is presented in Subsection 2.3. Such methods produce more optimistic particular assumptions but may lead to the global misses of deadlines.

There exists also stochastic methods to simulate the transmission time behaviour of CAN which is exemplarily presented in Subsection 2.4. The advantage of such methods is that the CAN network will be simulated by random functions and therefore the average transmission time behaviour will be correctly determined. Furthermore, the simulation clock advances faster than in real-time. The disadvantage of such methods is that the longest transmission times and especially the worst-case transmission times are hard to detect. This is due to particular system components such as processes that trigger messages that are not totally independent from each other.

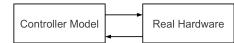

In general, the state-of-the-art works focus on an artificial approach so that CAN is not evaluated under runtime conditions. Therefore several decisions have to be made for the overall CAN network. Furthermore, A CAN system can be evaluated by simulating particular processes which trigger particular messages at the end of their simulated execution time. In addition, messages can be used to transfer time points which are obtained at the simulated creation time of the message. Moreover, a time point can be determined at the reception of such a message and thus the transmission time can be determined by calculating the difference between the creation time point and the reception time point. Furthermore, processors can be used to simulate the process execution times. Therefore a system consisting of several processors (a CAN Controller is attached to each processor) can be used to simulate a CAN network under runtime conditions. Therefore each processor simulates defined processes and each process is periodically executed. Furthermore, the execution times of a particular process can vary in time. Therefore the system properties vary and thus the transmission times of messages will vary. Furthermore, such a system can be evaluated for a defined period to calculate the average transmission times, variances of transmission times, the longest transmission time, etc. In addition, a particular run that was triggered in order to determine statistical data can be repeated to obtain more statistical data. Therefore repetitive runs that were undertaken in order to determine statistical data have a high significance for the description of the transmission time behaviour of CAN messages.

In a CAN bus system every message is broadcast to all subscribers except the sender (multicast reception). However there are abnormalities that cause an inconsistent reception of CAN messages at the receivers[PV03]. Therefore in such a test system the number of sent and received messages are determined at each subscriber. Furthermore, there are also proprietary star architectures available. A star architecture indirectly interconnects subscribers for message exchange. These prototypes (called CAN star) can be evaluated by the presented technique for their performance. Furthermore, it can also be checked if all subscribers except the sender receive all emitted messages in CAN star network.

This diploma thesis is organized into following chapters:

- Chapter 2: This chapter gives an exemplary overview of the state-of-the-art CAN performance evaluation techniques.

- Chapter 3: It describes the CAN standard as well as two proprietary CAN star architectures. Furthermore, the basic concepts for the prototype implementation to evaluate the performance of CAN are provided.

- Chapter 4: This chapter describes the architecture of the system structure and the experimental process of tests for a CAN based communication system evaluation.

- Chapter 5: Herein the structure of the prototype and the overall test system is described. Furthermore, the toolchains to create the prototype and the configuration data are explained. In addition, the data preparation to show the transmission time behaviour is described.

- Chapter 6: This chapter presents the results.

- Chapter 7: In this section the results and the properties of the prototype are discussed.

# CHAPTER 2

# **Related Work**

This chapter gives an overview of the state-of-the-art CAN performance evaluation techniques. Note that the CAN standard is explicit described in Subsection 3.1.

# 2.1 Multilevel Inspection of Multiple CAN-Networks

Novak[Nov09] presents a framework which consists of hardware blocks that evaluate transmission times, the behaviour in error cases, etc. This framework consists of a set of basic blocks that form a test system for multiple CAN networks. These basic blocks are implemented by reusable units of logic (Intellectual Property (IP) cores - see Subsection 3.4) in a reconfigurable integrated circuit called Field-Programmable Gate Array (FPGA). Each IP core of such a test system accesses and/or monitors CAN buses at the so called Open System Interconnection (OSI) layers 1 and 2. The OSI model divides the communication design into 7 layers such that each layer fulfills a well-defined part[fS96].

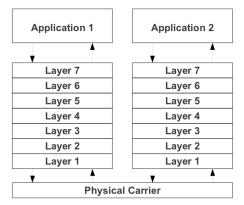

Layer 1 interacts with a physical information carrier. Moreover, a layer i is related to

layer i+1 but not layer 7 that provides a communication interface for an application such as a monitor function. All layers are stacked according to their numbers such that each result from a layer between layer 1 and 7 is processed by a related layer and forwarded. Therefore it is possible to replace each layer without modifying the remaining layers. Note that only layer 1 and 2 are required for the formation of a minimal communication architecture. Also note that layers may be merged.

In Figure 2.1 the principle layout of the OSI model is shown where two applications at different locations are connected by a physical carrier.

Layer 1 prepares bit sequences for the specific properties of a physical carrier (e.g. a physical carrier

Figure 2.1: OSI model

can be a copper line) and forwards them to the physi-

cal carrier. Layer 1 also receives bit sequences that are emitted at different locations and inverts the preparation for the physical carrier. Layer 2 stacks information (e.g. a message) into a frame (defined as a delimited sequence of sequential emitted bits) and addresses remote stations that are connected to the same physical carrier. In addition, layer 2 also transforms received frames into information suited for layer 3 (e.g. a message). Layer 2 also assures the correct transmission of these frames. The description of the other layers are not defined due to the lack of importance in this diploma thesis. The OSI model is standardized by the International Organization for Standardization (ISO).

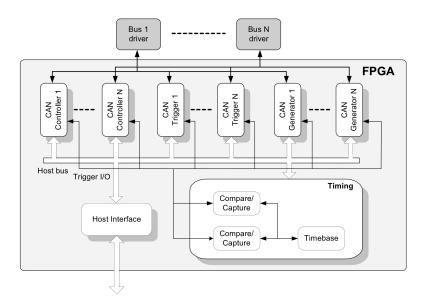

The IP cores are related to a global 32-bit time base with a resolution of 1  $\mu s$  that establishes a global time view as well as compares and captures registers to trigger events. A comparison register stores a number that is constantly compared to the global time base. If there is a match an event will be triggered. Furthermore, the time points of asynchronous events from external buses are stored in capture registers. There are three IP cores (also called IP function) that are used as follows:

- A CAN Controller IP Function that provides the standard functions of a CAN Controller and acts on OSI layer 2. In addition, it provides a transmission queue which stores ordered message objects (a message object is the body of a message i.e. id and payload) for transmission. In addition, each message from such a transmission queue is emitted upon an external request. This request is either hardware-triggered or by the transmission queue and can be described as follows: Each message located in the transmission queue is related to an absolute time point and triggers for sending if a compare register matches the time correlated to the message. Furthermore, received messages are related to their reception times. Upon receipt of a message an output signal is triggered. Moreover, it is possible to force the error state (the error state determines the communication privileges) of the CAN Controller.

- A CAN Trigger IP Function analyzes the traffic at the physical carrier (therefore it acts at OSI layer 1) to provide synchronization. In order to synchronize it is not adequate to detect an already received message due to the need of acting while a message (frame) is in transmission (e.g. to jam a frame that is in transmission). This unit analyzes the bit sequence of a frame and detects patterns within a frame. A detected bit sequence leads to the generation of a trigger signal.

- A CAN Generator IP Function emits predefined frames in such way that the emission of each frame is independent of the requirements of the CAN standard at OSI layer 1 (e.g. it is possible to transmit a complete frame that omitted the arbitration process). Frames are emitted by the description of program sequences. A program sequence defines the time point of the emission of a CAN frame, sequences of frames, build up of the events, etc. Furthermore, it is possible to vary the length of each bit within a frame that is in transmission.

In Figure 2.2 the test system architecture is shown. Furthermore, a test system can observe

## 2.2. Emulation of CAN Networks

Figure 2.2: System architecture of Multilevel Inspection[Nov09]

1 up to n CAN networks. Each CAN network is connected to at least one CAN Controller IP Function, one CAN Trigger IP Function and one CAN Generator IP Function. All IP cores are interconnected and therefore it is possible that e.g. the CAN Trigger IP Function detects a bit sequence of a CAN frame that is in transmission and triggers the CAN Generator IP Function to jam such a transmission. Furthermore, all IP cores are connected to a host interface that is accessed by an external host. An external host manages the configuration of the IP cores via the host interface.

# 2.2 Emulation of CAN Networks

Bago et al.[BMP07] evaluate simulation tools which emulate CAN networks for analysis of the utilization of the CAN bus, error detection (transmissions can be erroneous which is traced by the error management), etc. These simulation tools rely on the following parameters:

- Matrix Laboratory (MATLAB) is a mathematical software that can execute matrix operations, draw functions and data, implement algorithms, etc[HC10]. Algorithms are defined by textual description (programming language) placed in a so called m-file and/or higher programming languages such as C. Furthermore, MATLAB can also be extended by packages that provide symbolic computation to provide for example graphical multi-domain simulation.

- Simulink is an extension package for MATLAB that is an environment for multi-domain simulation as well as Model-Based Design for dynamic and embedded systems[Mat].

• Colored Petri Nets consist of place nodes (places), transition nodes (transitions) and directed arcs that connect places to transitions and therefore a Petri net is a graph[JKW07]. The places represent the state of the graph (system) and can be marked by one or more so called tokens. Each token has a data value (token color). Tokens at a certain place are allowed to have a set of token colors (color set of a place). Tokens move from places to connected transitions at other places. This is determined by arcs that connect the nodes. Input arcs of a transition define which token colors are required for a relocation whereas output arcs of a transition describe the modification of the token colors. Therefore a Colored Petri Net characterizes a finite automaton such as a communication system.

# TrueTime

TrueTime is a MATLAB/Simulink-based simulator for real-time control systems. TrueTime kernels model nodes that send and/or receive messages. In addition, the behaviour of each node is described by a code function. A code function is written in C++ or a MATLAB m-file and split into segments that are executed sequentially. Each segment consists of an execution code and an execution time that simulates the time consumption of the segment to compute (e.g. a segment simulates the emission of a message and conserves an execution time of 200  $\mu s$ . Therefore after 200  $\mu s$  the message is sent and the next code segment starts). Furthermore, TrueTime Network models a network and TrueTime kernels are connected to a TrueTime Network that is within the Simulink environment.

The following CAN bus properties were simulated by TrueTime: prioritization of messages, configuration flexibility (e.g. how easy can a new message be integrated in the system), multimaster and error detection. The test system consists of a single TrueTime kernel connected to a single TrueTime network. There exists sets of messages. Each set is defined by a number of messages with the same send period. Hence there is a code segment for every set and the messages within a set are ordered according to their priorities. In order to add a new node a new TrueTime kernel has to be instanced and a corresponding code function has to be written. Each TrueTime kernel has the same rights for bus access (multimaster). Errors can be simulated by a TrueTime kernel that owns the highest priority message (the highest priority message will simulate errors that cause delays).

TrueTime outputs the busy state of the bus relative to the simulation time and therefore the utilization of the bus can be calculated.

# **CPN Tools**

CPN Tools simulate and analyze Colored Petri Nets (CPN). The colors (properties) of a CPN are described by a textual description called CPN Markup Language. One property of such textual description is time. Each time property prevents one or even more transitions until the simulation time reaches a specific time point. Each transition can be used to e.g. create a single periodic message or to model transmission times.

The following CAN bus properties were simulated by CPN Tools: prioritization of messages, configuration flexibility, multimaster, error detection and automatic retransmission of erroneous transmitted messages as soon as the bus is idle. The simulation consists of a CPN that emulates the bus architecture and that connects via single places to other subnets that represent nodes. Furthermore, each subnetwork that represents a node links to an additional subnet that simulates the creation of messages. The bus simulation CPN models the prioritization of messages at the bus level. In addition, it also forces the prioritization of messages at the subnets and simulates the prioritization of messages at nodes. The bus simulation CPN has a single place where it stores received messages in conjunction with the reception times (communication log) and fulfills the multimaster property. In addition, errors are simulated by a place which blocks the message transition with a defined probability. Furthermore, in case of an error the respective message will be retransmitted. In order to add a new node a new subnet which represents the node as well as the subnet which composes the message set of the node have to be generated and attached to the bus simulation CPN.

From the above mentioned communication log it is possible to calculate the simulation time, message size and utilization of the CAN bus.

# 2.3 Worst-Case Response Time Analysis

Bit stuffing avoids the occurrence of five consecutive bits with same polarity by inserting bits with opposite polarity (stuff bit). Furthermore, bit stuffing is a CAN inherent system feature. Nolte et al.[NHN03] use a worst-case response time analysis and extend it with a probability distribution for stuff bits which determines the worst-case response time of CAN messages.

## **Traditional Schedulability Analysis of CAN Frames**

The maximum send frequencies of all messages in a network are assumed to determine the worst-case response time for message transmissions. The recurring generation of a particular message can be seen as a traffic stream and therefore the generation of all particular messages is defined as a set S of streams. In analogy to CPU scheduling the set S corresponds to the set of CPU tasks and each  $S_i \in S$  is a triple  $\langle P_i, T_i, C_i \rangle$ , where  $P_i$  is the priority (defined by the message identifier),  $T_i$  is the send period and  $C_i$  the worst-case transmission time of the frame of a message on the bus of stream  $S_i$ . As the minimum variation in queuing time relative to  $T_i$  is 0 the worst-case latency  $R_i$  for a message i of  $S_i$  can be defined by the following criteria:

$$R_i = J_i + q_i + C_i \tag{2.1}$$

where  $J_i$  is the maximum variation in the period  $T_i$  (relative to the start of  $T_i$ ) and  $q_i$  represents the effective queuing time. The effective queuing time  $q_i$  is defined as follows:

$$q_i^n = B_i + \sum_{j \in hp(i)} \left\lceil \frac{q_i^{n-1} + J_j + \tau_{bit}}{T_j} \right\rceil (C_j + 3\tau_{bit})$$

(2.2)

- $B_i$  is the worst-case transmission time of all CAN frames that have a lower priority (in CAN the priority of a frame that transports a message is determined by the priority of the message) than a frame which was sent on  $S_i$ . A frame which is in transmission is not interruptible. This implies that a frame that is in a transmission queue has to wait until the bus is idle.

- hp(i) is the set of streams with a higher priority than  $S_i$

- $\tau_{bit}$  is the bit time (duration of a single transmitted bit) on the bus that transmits a bit of a frame. The bit time has to be considered due to the different start times of nodes located at different locations reasoned by the propagation delay. The propagation delay is the required time to propagate a signal.

- $3\tau_{bit}$  represents the Intermission (also called Intermission space) defined as the minimum time between frames sent on a bus to transmit messages.

Note that equation 2.2 is a recursion where (n + 1)th value is calculated by the *n*th value and  $q_i^0$  is 0.

Equation 2.2 and 2.1 can be rewritten as:

$$R_i^n = J_i + B_i + C_i + \sum_{j \in hp(i)} I_j (R_i^{n-1} - J_i - C_i) (C_j + 3\tau_{bit})$$

(2.3)

$I_j(t)$  is the worst-case number of periodic message creations for a messages j in a time interval of t:

$$I_j(t) = \left\lceil \frac{t + J_j + \tau_{bit}}{T_j} \right\rceil$$

(2.4)

$J_j$  is the worst-case creation jitter (difference between shortest and longest delay) in the message period  $T_j$ .

# Schedulability Analysis of CAN Frames with a Probability Distributions for Stuff Bits

The worst-case transmission time  $C_i$  is based on the transmission speed of a bit at the bus, data size, the identifier bits (CAN support two identifier formats with different lengths), overhead bits and stuff bits. The number of stuff bits in the traditional schedulability analysis is assumed for the worst-case and depends on the data transported by the frame in bytes (0 to 8 bytes, denoted as  $L_i$ ). In addition, it also depends on the identifier format and a fixed number of overhead bits which are adapted for bit stuffing (34 for standard frame format and 54 for extended frame format, denoted as g). As 10 bits are not considered for bit stuffing and  $\tau_{bit}$  is the worst-case time for bit transport, the resulting worst-case time for a CAN frame transmission according to the traditional approach can be formulated as follows:

$$C_{i} = (8L_{i} + g + 10 + \left\lfloor \frac{g + 8L_{i} - 1}{4} \right\rfloor)\tau_{bit}$$

(2.5)

By using a probability distribution for stuff bits instead of the worst-case number a more accurate probability-based response time is yielded. The distribution of stuff bits can be denoted as follows:  $\Upsilon$  that is a set of pairs defined as  $(x, P(x) \in \Upsilon$  where x is the number of stuff bits and P(x) is the probability of x stuff bits. Furthermore, if multiple frames are sent sequentially and someone assumes that the frames are independent of each other, the resulting joint distribution

$\prod_{n} \Upsilon \text{ is the combination of n distributions of stuff bits } (\prod_{n} \Upsilon = \underbrace{\Upsilon \times \Upsilon \times \ldots \times \Upsilon}_{n}). \text{ Moreover, } \prod_{n}^{n}$  is the joint distribution of frames with the same length. The calculation of the joint distribution results in the combination of all probabilities e.g. (a, P(a)) \* (b, P(b)) = (a + b, P(a) \* P(b)) where  $a, b \in \{0, 1, \ldots\}$ .

Therefore the transmission time of a single frame on the bus can be expressed as follows:

$$C_i(p) = c_i + \Upsilon_{L_i}(p)\tau_{bit} \tag{2.6}$$

$\Upsilon_{L_i}$  is the distribution of stuff bits in the message and  $c_i$  the transmission time of the frame without stuff bits:

$$c_i = (8L_i + g + 10)\tau_{bit} \tag{2.7}$$

Hence the worst-case blocking time by a single frame i is as follows:

$$B_i(p) = b_i + \Upsilon_{\max_{k \in lp(i)}(L_k)}(p)\tau_{bit}$$

(2.8)

$\Upsilon_{\substack{k \in lp(i) \\ k \in lp(i)}}$  is the distribution of stuff bits of the blocking frame *i* and *b<sub>i</sub>* is the worst-case transmission time of the frame *i* without stuff bits i.e. the longest frame with a priority lower than *i*:

$$b_i = \max_{k \in lp(i)} (c_k) + 3\tau_{bit}$$

$$(2.9)$$

Thus the response time of a message from the creation time until reception composes as follows:

$$R_i^n(p) = J_i + b_i + c_i + \sum_{j \in hp(i)} I_j(R_i^{n-1}(p) - J_i - c_i)(c_j + 3\tau_{bit}) + \Psi_i(p)\tau_{bit}$$

(2.10)

The distribution of the total number of stuff bits  $\Psi_i$  is defined as follows:

$$\Psi_{i} = \Upsilon_{\max_{k \in lp(i)}(L_{k})} \times \Upsilon_{L_{i}} \times \prod_{j \in hp(i)} \prod_{I_{j}(R_{i}(p)-J_{i}-c_{i})} \Upsilon_{L_{i}}$$

(2.11)

$\Upsilon_{\substack{k \in lp(i)}}(L_k)$  is the distribution of stuff bits of the longest lower priority frame.

$\Upsilon_{L_i}$  is the distribution of stuff bits of the frame of the analyzed message.

$\prod_{j \in hp(i)} \prod_{I_j(R_i(p)-J_i-c_i)} \Upsilon_{L_i}$  is the distribution of stuff bits of all messages which have a higher priority than the analyzed message.

# 2.4 Stochastic Analysis

Zeng et al.[ZNGSV09] introduce a stochastic method that determines response times within a distributed system that consists of locally triggered ECUs that communicate with each other using CAN messages. Furthermore, each ECU uses processes (application tasks) to solve defined problems. Messages and application tasks (tasks for short) are mapped to a Directed Acyclic Graph (DAG), where vertexes correspond to tasks and messages and edges describe signals between vertexes. Furthermore, the computations in the DAG periodically proceed in discrete time steps. A time step simulates the behavior of tasks and message transmissions for a time quantum of a real system. Thus a sequence of computations characterizes message transmissions and task executions. Hence this stochastic method determines end-to-end transmission times in a distributed system with clock drifts (the ECUs are not synchronized) and offsets (the ECUs do not start simultaneously).

## **Basic Definitions**

Each ECU has a local clock that triggers computation steps in such a way that tasks are periodically activated, executed and scheduled by their priority. When activated a task reads its input signals and when completed it writes its results into shared variables. A task  $\tau_i$  can be described by a quintuple ( $\Upsilon_i, T_i, O_i, \mathcal{E}_i, P_i$ ), where  $\Upsilon_i$  is the ECU on that  $\tau_i$  executes,  $T_i$  its period,  $O_i$  its initial phase,  $\mathcal{E}_i$ , its execution time and  $P_i$  its priority. Each periodic activation of a task is an instance (job) and the *j*th instance of  $\tau_i$  is denoted as  $\Gamma_{i,j}$  with an arrival time  $A_{i,j} = O_i + (j-1)T_i$  which is the time  $\Gamma_{i,j}$  is ready for execution.

A middleware acts as the interface between tasks and the CAN bus and supports a special task for this purpose. This task, called transmit task (TxTask), assembles messages periodically from the shared variables and pushes them into a prioritized message queue that is ordered by the id of each message. Messages in a prioritized message queue are transmitted to other ECUs. A message  $m_i$  can be described by a sextuple  $(\Upsilon_i, \Upsilon_i^{SRC}, T_i, O_i, \mathcal{E}_i, P_i)$ , where  $\Upsilon_i$  is the CAN bus resource used to transmit  $m_i, \Upsilon_i^{SRC}$  the emitting ECU of  $m_i, T_i$  its send period,  $O_i$  its initial phase and  $\mathcal{E}_i$  its transmission time.  $P_i$  is the CAN id of the message  $m_i$  and therefore its priority. The *j*th instance (job) of  $m_i$  is denoted as  $M_{i,j}$  with a queuing time  $Q_{i,j} = O_i + (j-1)T_i$  which is the time  $M_{i,j}$  is ready for transmission.

$\mathcal{E}_i$  is a discrete random variable with a distribution  $f_{\mathcal{E}_i}$  that defines the probability for each value within an interval  $[E_i^{min}, E_i^{max}]$ . This probability distribution is called probability mass function (pmf). In a pmf each time value is a multiple of the granularity  $\tau$  that represents a time step in a discrete-time model and simulates the computations and communications in a real system. Such computations and communications run on a system resource  $\Upsilon_k$  where the hyperperiod  $H_k$  is the least common multiple (lcm) of periods of all objects executed on  $\Upsilon_k$ . Furthermore, the system resources (ECUs) have independent clocks and therefore the clock difference  $\mathcal{O}_{\Upsilon_k,\Upsilon_l}$  describes the clock difference between ECUs  $\Upsilon_k$  and  $\Upsilon_l$ .

A DAG consists of vertexes V and edges E. V represents the tasks and messages by a set of objects  $\{o_1, ..., o_n\}$  and an edge  $e_i \in E$  connects two vertexes in the DAG that denotes a data transfer. Furthermore, a path  $\Pi_{i,j}$  is a sequence of objects such that there is an edge between any two consecutive objects. Furthermore, the end-to-end latency  $\mathcal{L}_{i,j}$  of path  $\Pi_{i,j}$  is the difference between the activation of an instance at  $o_i$  and the results produced at  $o_j$ .

## **Task Response Time**

The response time of a job depends on the jobs that are queued before. Therefore the *P*-level backlog at time t  $W_t^P$  is a pmf and defined as the sum of the remaining execution times of all jobs that have a higher priority than *P* and are not completed until *t*. The *P*-level backlog at the beginning of a hyperperiod  $G_k^P = W_{(k-1)H}^P$  is a sequence of random variables  $\{\mathcal{G}_1^P, ... \mathcal{G}_k^P, ...\}$  and determined by a Markov chain. A Markov chain *M* is a triple (S, P, F) where *S* is a set of states, P is a set of transition function that links all states in *S* by probabilities such that  $\sum_{s' \in S} P(s, s') = 1$  and *F* is the set of final states in *S*[AHM05].

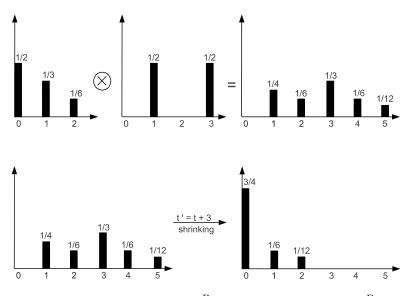

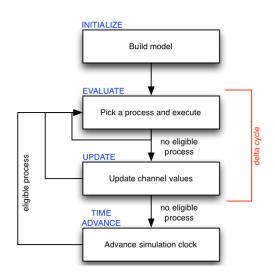

After the calculation of  $\mathcal{G}^P$ , the job releases in order of its release times and modifies iteratively the backlog within the hyperperiod. Right after the release of a job convolution of the backlog pmf with the job execution time pmf ( $\mathcal{W}_t^P \star f_{\mathcal{E}_i} = \sum_{1}^k \mathcal{W}_t^P[m]\mathcal{E}_i[n-m]$ ) obtains the remaining *P*-level backlog pmf. Shrinking advances the time from *t* to *t'* (time instant right before the next release of a task) by shifting the backlog pmf by t' - t units to the left and by summing up all probabilities defined for non-positive values at the origin. In Figure 2.3 an example for convolution and shrinking is shown.

Figure 2.3: Convolution  $(\mathcal{W}_t^P \star f_{\mathcal{E}_i})$  and shrinking of  $\mathcal{W}_t^P$

The convolution of the backlog pmf with the job response time pmf at the release time of the job yields to the pmf of the job response time. The response time of a job prolongates if a higher priority job arrives during its execution time. Hence the job response time pmf of a job  $\Gamma_{i,j}$  is

updated by a split up at the release time of the higher priority job. The convolution of the right hand side with the execution time pmf of the higher priority job generates the actual response time pmf. This is repeated iteratively for all higher priority jobs released after  $\Gamma_{i,j}$ .

## Message Response Times

The *P*-level backlog  $W_t^P$  is a pmf and defined as the sum of all remaining transmission times at time t from queued message instances that are higher in priority than the analyzed one. Furthermore, the pmf of the message instance response time in the approximate system results from its transmission time and the stationary distribution of the backlog at the beginning of the hyperperiod that is adapted for each release of a message instance. In addition, a possible uninterrupted transmission of lower priority job is considered to achieve the pmf of the total transmission time.

## **Characteristic Interference Message**

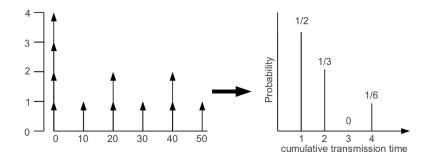

The interference of messages from remote stations to an inspected message are summarized by a characteristic interference message (characteristic message for short) for each remote station. Therefore the characteristic message represents the load from the remote ECUs. The characteristic message's period  $T_c$  is the greatest common divisor (gcd) of the periods of messages at a particular remote ECU that are higher in priority than the analyzed message. In order to obtain the pmf of the characteristic message the following example can be considered. Someone may assume three messages at a remote ECU that have a period that correlates to the transmission time denoted as (period, transmission time): (60,2),(10,1),(20,1). Therefore  $T_c$  is 10 and hence there are 6 time instants. At the beginning all messages are queued and so the transmission time is 4 and the transmission times of the following time instants are 1, 2, 1, 2, 1. Thus from a remote message  $m_i$  point of view the probability to obtain the interference of 4 transmission time units is 1/6 because there is only on possibility in 6 time instances to obtain this time inference, for 2 transmission time units it is 1/3 and for 1 transmission time units it is 1/2. This can be denoted as  $\mathbb{P}(1) = 1/2$ ,  $\mathbb{P}(2) = 1/3$ ,  $\mathbb{P}(4) = 1/6$ . This example is explained in Figure 2.4. Furthermore,

Figure 2.4: Calculation of a PMF for a characteristic message

the characteristic message has a fixed initial offset of  $-T_c/2$  and in each hyperperiod a random release jitter in  $[0, T_c)$  denoted as  $\mathcal{J}_c$ . Both are caused by  $\mathcal{O}_{\Upsilon_k, \Upsilon_l}$ . The higher priority mes-

sages that are located at the same ECU as the analyzed message  $m_i$  are not summarized by a characteristic message since they have known queuing instants.

#### **Stationary Backlog Within the Hyperperiod**

The backlog  $W_t^P$  at the start of the hyperperiod consists of local higher priority messages and characteristic messages. The backlog is adapted in time steps  $\tau$ . The computation of  $W_t^P$  at time t from  $t - \tau$  requires an intermediate step arbitrarily close to t and at this intermediate step shrinking advances the time. Furthermore, the possible activation of message instances is determined and the probability of a single activation can be easily computed by  $1/n_t$  where  $n_t$ is the number of steps from t to the latest possible queuing time. If no new message instance triggers the backlog remains the same and so the intermediate time step transforms to t without modification. Otherwise the transmission time  $\mathcal{E}_p$  extends the backlog and so the intermediate time step transforms to t.

#### **Initial Blocking Time**

A message that is in transmission can not be interrupted. Therefore even a low priority message can block a message instance  $M_{i,j}$ .  $M_{i,j}$  has a blocking delay  $\mathcal{B}_{i,j}$  (also denoted as b) and an instance of a lower priority message  $m_{k,l}$  causes a blocking time length b > 0 if  $m_{k,l}$  has a transmission time  $\mathcal{E}_k > b$  and its transmission starts exactly at  $\mathcal{E}_k - b$  units before the queuing instant  $M_{i,j}$ . The probability that such an instance transmission starts exactly at  $\mathcal{E}_k - b$  is  $\tau/T_k$ . Furthermore, by adding up all probabilities of all messages that have a lower priority than  $M_{i,j}$  $(lp(P_i)$  denotes the set of all messages with priority lower than  $m_i$ ) the following formula can be assumed:

$$\mathbb{P}(\mathcal{B}_{i,j} = b) = \sum_{m_k \in lp(P_i)} \frac{\mathbb{P}(\mathcal{E}_k > b)}{\frac{T_k}{\tau}}$$

(2.12)

The backlog time is added by convolution to the backlog at the message queuing time.

#### Message Response Time Calculation

The earliest possible start time for a message instance  $m_{i,j}$  is at its queuing time (arrival time)  $t_q$ . Furthermore, the backlog computes as described above. An analyzed message instance is queued as long as the backlog at t is not equal to zero. Someone may assume that it takes k steps to obtain a backlog at t of zero. Hence the total queuing time  $t_k$  for a message instance can be expressed as follows:

$$t_k = t_q + k\tau \tag{2.13}$$

The total transmission time of a message instance is the sum of the transmission time  $\mathcal{E}_i$  and the queuing time  $t_k$ .

## Stochastic Analysis of End-To-End Latency

In Figure 2.5 an example of an end-to-end delay  $(\mathcal{L}_{o_1,o_7})$  is shown. Someone may assume that

Figure 2.5: End-to-end latency of a path  $\Pi_{o_1,o_7}$ [ZNGSV09]

an external event (modeled as vertex  $o_1$ ) and a task  $\tau_i$  (modeled as vertex  $o_2$ ) that reads the data is generated by this event. Then the time between the occurrence of this event and the activation of the corresponding task that reads the data is called sampling delay. Furthermore,  $\tau_i$  converts the data from this event to a result and stores it at the middleware. The corresponding task response time is the difference between activation and response as explained in Subsection 2.4. The middleware provides this result to a task  $\tau_j$  (modeled as vertex  $o_3$ ) that generates data from the result  $\tau_i$  and stores them at the middleware. The time between activation of a task that produces a result for a following task and the activation of the following task that reads the result is called local delay. Note that not all results from task instances are part of the end-to-end propagation. The outcome from a job of a task  $\tau_i$  can be overwritten by the next job of  $\tau_i$  before recognition at a vertex that follows  $\tau_i$ . An overwritten value is not propagated and so the delay is not considered for the end-to-end latency.

The TxTask (denoted as  $o_4$ ) of the middleware assembles the result from  $\tau_j$  to a message object  $m_i$ . The transmission time of this message object is described in Subsection 2.4. Furthermore, a receive task  $\tau_r$  (denoted as  $o_5$ ) obtains  $m_{i,j}$  and  $\tau_r$  handles  $m_{i,j}$  via the middleware to task  $\tau_k$  (denoted as as  $o_6$ ). The time difference between the activation of the TxTask which produced a message instance  $m_{i,j}$  and the activation of the receive task that reads  $m_{i,j}$  is called remote delay. Furthermore,  $\tau_k$  computes a result and a task  $\tau_l$  (denoted as  $0_7$ ) receives it via the middleware. The task  $\tau_l$  stimulates an activator. The time difference between activation by an (external) event and completion (stimulation of an activator) is called response time. The path  $\Pi_{o_1,o_7}$  determines the end-to-end latency  $\mathcal{L}_{o_1,o_7}$  by summing up all latencies.

# CHAPTER 3

# **Basic Concepts**

This chapter provides the basic concepts for the implementation of the prototype and also describes the CAN standard as well as CAN star implementations.

# 3.1 Controller Area Network

This subsection describes the CAN Specification 2.0 which consists of Part A that uses a so called standard frame format and Part B that uses the standard and so called extended frame format[Rob91]. In this diploma thesis we will discuss only the CAN standard for Part B.

The subscribers in a CAN based communication system interact by frames to transport messages and each subscriber signals a frame in bits. Each bit that is sent to the bus is characterized by a low state (called recessive bit that represents a logical '1') or a high state (called dominant bit that represents a logical '0'). Furthermore, a dominant bit signalled at the bus is always read as '0' by all subscribers in the system even if a recessive bit is emitted simultaneously. Furthermore, each message that is ready for transmission is transformed into a frame and the transmission of a frame starts if the bus is not in use (bus idle denotes an unoccupied bus). Each subscriber starts the transmission of a frame by emitting a single dominant bit to indicate that the bus is in use and continues by emitting the priority of the frame that is the unique id of the corresponding message. Moreover, each emitting subscriber also determines the value at the bus for each bit that is in transmission. The transmission of the priority of the

Figure 3.1: CAN Layers

frame (a priority is higher if its number is lower) must

be read back as emitted. Otherwise the corresponding

subscriber may stops the transmission of the frame (an other subscriber sends a frame with a higher priority). The prioritization process that occurs at the emission to ensure the exclusive emission of a single frame is called arbitration. Furthermore, the access technique multiple subscribers apply to check for an idle bus followed by arbitration is called Carrier Sense Multiple Access/Collision Resolution (CSMA/CR).

Figure 3.1 shows the structure of the CAN standard by its layers. Furthermore, the CAN standard by Bosch defines parts of the physical layer (layer 1) as well as the Data Link Layer (DLL) (layer 2) of the OSI reference model. The DLL consists of Medium Access Control (MAC) and the Logical Link Control (LLC). The LLC provides the data transfer as well as remote data request to a node. Each node performs computations and communicates via CAN to other nodes. Moreover, the LLC also manages overload notifications (see Subsection 3.1) and recovery (see Subsection 3.1). Furthermore, the LLC also filters received messages and therefore the LLC is responsible for the addressing of units (see Subsection 3.1).

The MAC provides the data encapsulation/decapsulation (see Subsection 3.1), the frame coding (see Subsection 3.1), medium access management (see Subsection 3.1) and the error detection/signalling (see Subsection 3.1).

The sublayer Physical Signalling of the physical layer provides the bit encoding/decoding, bit timing and synchronization (see Subsection 3.1). The above presented services (DLL and Physical Layer) are provided by a independent unit called CAN Controller to a node.

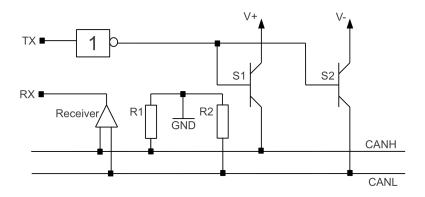

CAN is defined by ISO 11898[fS03]. The ISO 11898 completely specifies the DLL and the Physical Layer. The Physical Layer consists of the Physical Signalling sublayer, Physical Medium Attachment (PMA) and the Medium Dependent Interface (MDI). The services of the PMA and MDI are provided by a unit called CAN Transceiver. The CAN Transceivers are interconnected by wires and each CAN Transceiver is attached to a CAN Controller. The Subsection 3.1 describes the features of a CAN Transceiver.

The application field of CAN is the car industry but it is also often used in other areas like medical devices, non-industrial machines, marine electronics, factory automation, etc.[OAFAA06]. For example, a car consists of several ECUs such as engine control units, sensors, anti-skid-systems, etc. and such devices are connected via CAN.

## **Basic Definitions**

This Subsection provides some basic definitions for the CAN standard.

#### Bus and Bus Level - Recessive/ Dominant

A bus consists of 2 wires: CANH and CANL[Ric02] and these two lines are driven by a CAN Transceiver. Each subscriber that is part of the CAN network is connected to CANH and CANL via a CAN Transceiver. Each subscriber consists of the following parts:

- A node that performs algorithm described by an user.

- A CAN Controller that provide the communication services to the node. The CAN Controller manages the Data Link Layer as well as the Physical Layer.

Figure 3.2 shows the CAN bus with 3 attached subscribers (the two 120  $\Omega$  resistors are terminating resistors and their purpose is described in Subsection 3.1).

Figure 3.2: CAN Bus with 3 attached subscribers

CANH and CANL are driven by the CAN Transceivers to obtain two different bus levels. The bus level represents the actual physical state of the bus and the differential signalling of CANH and CANL determine the physical state:

- Dominant state (logic '0') if a threshold voltage between CANH and CANL exceeds a defined maximum level. At a dominant state the positive supply voltage drives CANH and the negative supply voltage drives CANL.

- Recessive state (logic '1') if a threshold voltage between CANH and CANL doesn't exceed a defined minimum level. At a recessive state CANH and CANL are driven over a pull-down resistor to ground.

This technique yields to a wired AND-conjunction and so a dominant bus level overwrites a recessive bus level. Furthermore, an idle bus has a permanent recessive state.

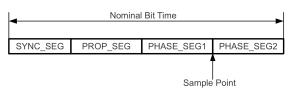

#### **Bit Times and Bit Rates**

A bit propagated at the bus is a dominant or recessive state kept for a defined time interval at the transmission of a frame and the duration of that time interval (called bit time) determines the bit rate. The bit rate is the number of bits per seconds transmitted and so the relationship between bit time (bit\_time) and bit rate (bit\_rate) is:

$$bit\_time = 1/bit\_rate$$

(3.1)

The bit rate of CAN is up to 1Mbit/s and at a bit rate of e.g. 1Mbit/s the duration of a single bit is 1  $\mu$ s.

#### Messages

A message transports information in a fixed format of different but limited length. A message consists of an identifier (id) to definitely tag a message as well as defining its priority (lower number has higher priority) and a payload to transport user data. In CAN there are two messages: Standard messages (to be compatible with Part A controllers) that have an id length of 11 bits and extended messages that have an id length of 29 bits. Both message formats provide a payload length of 0 to 8 bytes.

Each node exchanges information by messages and therefore a node access the CAN Controller and overhands the information to be transported in a message format. Vice versa received messages can be read from a node by accessing the corresponding CAN Controller.

## **Transmitter and Receiver**

A transmitter is a unit that currently emits a message. A receiver is a unit that is not a transmitter if the corresponding bus is not idle. Note that each Transmitter also listens to the bus for e.g. arbitration (see Subsection 3.1).

## Frames

CAN provides the following frames: Error frames (see Subsection 3.1), overload frames (see Subsection 3.1), data frames and remote frames (see Subsection 3.1). Data frames transport messages and remote frames request messages. Data and remote frames refers in Part B to a standard frame format and an extended frame format and therefore there exists standard data frames, standard remote frames, extended data frames and extended remote frames. Furthermore, in Part A there are only standard frame formats and CAN Controllers specified by Part B are compatible to Part A CAN Controllers and vice versa as long as only standard identifiers are used.

## **Data Frames, Remote Frames and Arbitration**

Data frames serve as carriers for messages to exchange information between nodes. Furthermore, remote frames are used to request data frames. Each data/remote frame consists of fields and bits and a single transmitted bit of a frame is propagated for a single bit time at the bus. Figure 3.3 shows the extended and standard frame format of a data/remote frame (the bits are emitted from left to right).

## **Start of Frame**

The transmission of a frame starts if the bus is idle and as the bus is idle the access by a subscriber to transmit a data/remote frame is indicated by the so called Start of Frame (SOF). The SOF

Figure 3.3: Data/Remote Frame

transforms the recessive state of the idle bus into a dominant state for a single bit time and therefore the bus is not idle any more.

#### **Arbitration Field and Arbitration**

After the SOF the emission of the Arbitration Field (denoted as Extended Identifier Arbitration Field/Standard Identifier Arbitration Field) continues. The Arbitration Field consists of following parts:

- Standard frames of Identifier A (the identifier of a standard message), the Remote Transmission Request Bit (RTR) and Identifier Extension Bit (IDE). The IDE is merged with the Reserved Bit 1 (RE1).

- Extended messages of Identifier A, the Substitute Remote Request Bit (SRR), IDE, Identifier B (the identifier of an extended identifier is split into Identifier A and Identifier B) and the RTR.

The IDE denotes the transport of a standard frame (dominant) or an extended frame (recessive). An extended frame has the advantage of possessing more identifiers whereas standard frames are compatible to communication devices relayed on Part A and the advantage of having faster transmission due to transport of less bits.

The difference between a remote frame and a data frame is the RTR. If it is set dominant the frame is a data frame and if it is set recessive it is a remote frame. Remote frames are used to request data frames of the same identifier. Moreover, the Substitute Remote Request Bit (SRR) guarantees that the IDE is always a single bit time after Identifier A.

The forwarding of a data/remote frame interrupts if an emitted recessive bit at the Arbitration Field is read back as dominant bit. This technique, called arbitration, prevents the simultaneous

emission of data/remote frames. Arbitration proceeds bitwise and therefore an emission stops directly at the detection of a lost arbitration. Thus an identifier with a lower number has a higher priority

#### **Control Field**

After the emission of the Arbitration Field a so called Control Field follows. The Control Field consists of two reserved bits (Reserved Bit 0 and Reserved Bit 1) and a Data Length Code (DLC) that specifies the length of the payload in bytes. The DLC consists of 4 bits (DLC3, DLC2, DLC1 and DLC0) used for numbering and a number greater than 8 specifies a payload of 8 bytes. Furthermore, for remote frames the DLC denotes the payload length of a requested data frame. Table 3.1 denotes the DLC coding for each byte length of the payload ('d' denotes dominant and 'r' denotes recessive).

| Number of data in bytes | DLC3 | DLC2 | DLC1 | DLC0 |

|-------------------------|------|------|------|------|

| 0                       | d    | d    | d    | d    |

| 1                       | d    | d    | d    | r    |

| 2                       | d    | d    | r    | d    |

| 3                       | d    | d    | r    | r    |

| 4                       | d    | r    | d    | d    |

| 5                       | d    | r    | d    | r    |

| 6                       | d    | r    | r    | d    |

| 7                       | d    | r    | r    | r    |

| 8                       | r    | d    | d    | d    |

Table 3.1: Length of the payload (data field) denoted by the Data Length Code

The reserved bits are used for further expansion and should be emitted as dominant bits but the receivers accepts them as dominant and recessive. Moreover, the bit Reserved Bit 1 for the standard frame format changed (from Part A) to IDE and therefore the IDE and Reserved Bit 1 are merged.

#### Data Field

User data are transported in the Data Field. The data field has a length of 0 to 8 bytes for data frames and zero length for remote frames.

#### **CRC** Checksum

The CRC (Cyclic Redundancy Check) Checksum is derived by the division of a polynomial. The coefficients of the polynomial are given by the bit stream of SOF, Arbitration Field, Control Field, Data Field (if present), and for the 15 lowest coefficients, by 0. The coefficients are calculated modulo-2 by the generator-polynomial:

$$x^{15} + x^{14} + x^{10} + x^8 + x^7 + x^4 + x^3 + 1$$

(3.2)

The following pseudo code shows the calculation of the CRC Checksum by a shift register (NEXT\_BIT denotes the next bit of the bit stream):

```

Listing 3.1: Algorithm to calculate CRC Checksum

CRC_REGISTER = 0;

REPEAT

CRC_NEXT = NEXT_BIT EXOR CRC_REGISTER(14);

CRC_REGISTER(14:1) = CRC_REGISTER(13:0);

CRC_REGISTER(0) = 0;

If CRC_NEXT then // Division fits at this step

CRC_REGISTER(14:0) =

CRC_REGISTER(14:0) =

CRC_REGISTER(14:0) EXOR 0x4599

ENDIF

UNTIL (CRC Checksum starts or there is an Error condition)

```

#### Acknowledge Bit, CRC Delimiter Bit and ACK Delimiter Bit