Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

# **Functional Safety in KNX**

## DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

## **Technische Informatik**

eingereicht von

## Marco Steffan

Matrikelnummer 0215884

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung Betreuer: Ao.Univ.Prof.Dr. Wolfgang Kastner Mitwirkung: Dr. Wolfgang Granzer

Wien, 24.11.2011

(Unterschrift Verfasser)

(Unterschrift Betreuer)

## Erklärung zur Verfassung der Arbeit

Marco Steffan Wiesenweg 13, 6170 Zirl

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

#### Abstract

Building automation systems aim at providing a comfortable environment while saving available resources. In case of using fire alarm systems (functional safety) or access-control systems (security) those systems are realized as separate, closed systems interacting with an existing building automation system via dedicated points of interaction. Integrated systems providing functional safety natively are currently hardly available.

This thesis targets an approach to extend the building automation technology KNX with functional safety. In compliance with IEC 61508 (Functional safety of electrical/electronic/programmable electronic safety-related systems) and ISO 13849 (Safety of machinery - Safety-related parts of control systems) an architecture satisfying safety integrity level 3 (SIL3) as defined by IEC 61508 is presented. Security is thereby left unconsidered. SIL3 compliance implies sufficient support on hardware level (fault-tolerance), a standard-conform documentation of all development steps as well as adequate software to detect errors in the hardware and the communication system.

The intention of the thesis is not the provision of a complete implementation of all requirements according to IEC 61508 but rather elaboration of an extension to existing approaches within this field. On that score and in compliance with IEC 61784-3 (Industrielle Kommunikationsnetze - Profile - Teil 3-1: Funktional sichere Übertragung bei Feldbussen) measures to detect errors in the communication system are discussed, architectures for a SIL3 compliant KNX-system are presented and resulting impacts on hard- and software are shown.

#### Kurzfassung

Gebäudeautomationssysteme dienen in erster Linie der Erzeugung eines komfortablen Raumklimas bei gleichzeitiger, ressourcenschonender Nutzung der zur Verfügung stehenden Energie. Geht man davon aus, dass funktionale Sicherheit (Safety) etwa für Brandmeldeanlagen oder Systemsicherheit (Security) für Zutrittskontrollen erforderlich sind, werden diese Anforderungen durch eigenständige Systeme realisiert, die (im besten Fall) über ausgewählte Schnittstellen mit einem vorhanden Gebäudeautomationssystem kommunizieren. Integrierte Systeme, die bereits "nativ" funktionale Sicherheit zur Verfügung stellen, sind derzeit kaum verfügbar.

Diese Arbeit versucht einen Ansatz zu schaffen, die Gebäudeautomationstechnologie KNX um funktionale Sicherheit zu erweitern. In Übereinstimmung mit den Standards IEC 61508 (Funktionale Sicherheit sicherheits-bezogener elektrischer / elektronischer / programmierbarer elektronischer Systeme) und ISO 13849 (Sicherheit von Maschinen - Sicherheitsbezogene Teile von Steuerungen) wird eine mögliche Architektur erarbeitet, um einen Sicherheitsintegritäts-Level 3 (SIL3) laut IEC 61508 zu erreichen. Systemsicherheit bleibt dabei unberücksichtigt. SIL3 impliziert eine ausreichende Unterstützung der zugrunde liegenden Hardware (Fehlertoleranz), eine Standard-konforme Dokumentation aller Entwicklungsschritte sowie Software, um Fehler in der Hardware und dem Kommunikationssystem zu erkennen.

Ziel dieser Arbeit ist nicht eine vollständige Ausarbeitung aller Erfordernisse gemäß IEC 61508, sondern eine Erweiterung zu bereits bestehenden Ansätzen in diesem Umfeld zu schaffen. Im Zuge dieser Arbeit werden Mechanismen, die Fehler im Kommunikationssystem erkennen, in Abstimmung mit IEC 61784-3 (Industrielle Kommunikationsnetze - Profile - Teil 3-1: Funktional sichere Übertragung bei Feldbussen) diskutiert, Architekturen für ein SIL3 konformes KNX-System vorgestellt und sich daraus ergebende Anforderungen an die Hard- und Software erarbeitet.

## Contents

| Al | ostrac  | t                                                                         | ii   |

|----|---------|---------------------------------------------------------------------------|------|

| Kı | ırzfas  | sung                                                                      | iii  |

| Co | ontent  | ts                                                                        | v    |

| Li | st of l | Figures                                                                   | vi   |

| Li | st of [ | <b>Fables</b>                                                             | viii |

| 1  | Intr    | oduction                                                                  | 3    |

|    | 1.1     | Motivation                                                                | 3    |

|    | 1.2     | Guide through this Thesis                                                 | 4    |

| 2  | Buil    | ding Automation Systems                                                   | 5    |

|    | 2.1     | Introduction                                                              | 5    |

|    | 2.2     | KNX                                                                       | 8    |

| 3  | Stat    | e-of-the-art Standards                                                    | 13   |

|    | 3.1     | ISO 13849 - Safety of machinery - Safety-related parts of control systems | 15   |

|    | 3.2     | IEC 61508 - Functional safety of E/E/PE safety-related systems            | 18   |

|    | 3.3     | Conclusions of ISO 13849 and IEC 61508                                    | 28   |

| 4  | Exis    | ting Safety Solutions in HBA Systems                                      | 31   |

|    | 4.1     | IEC61784-3 - Functional safety fieldbuses                                 | 32   |

|    | 4.2     | Industrial Automation solutions                                           | 36   |

|    | 4.3     | OpenSafety                                                                | 40   |

|    | 4.4     | SafetyLON                                                                 | 43   |

| 5  | KN      | X Safety                                                                  | 47   |

|    | 5.1     | Hardware Architectures for Safe KNX Nodes                                 | 48   |

|    | 5.2     | Synchronizing Safety Nodes                                                | 53   |

|    | 5.3     | Intercommunication - KNX Safety Protocol Extension                        | 59   |

|    | 5.4     | Software Architecture for a Safety Node                                   | 64   |

| Bi | bliogr | aphy                                                        | 93              |

|----|--------|-------------------------------------------------------------|-----------------|

| 6  | 0011   | clusion Outlook and further work                            | <b>91</b><br>92 |

|    | 5.9    | Building Safe Hardware                                      | 84              |

|    | 5.8    | Scheduling tasks on a Microprocessor                        | 81              |

|    | 5.7    | Hardware self tests                                         | 73              |

|    | 5.6    | KNX Safety Application                                      | 72              |

|    | 5.5    | Intracommunication - Communication between Safe Controllers | 67              |

# **List of Figures**

| 2.1 | Three-tier architecture                                              | 7  |

|-----|----------------------------------------------------------------------|----|

| 2.2 | Two-tier architecture                                                | 7  |

| 2.3 | KNX model [2]                                                        | 9  |

| 2.4 |                                                                      | 10 |

| 2.5 |                                                                      | 12 |

| 3.1 | Fault chain defined by [21]                                          | 13 |

| 3.2 | One-out-of-two architecture (1002)                                   | 14 |

| 3.3 | Simplified V-Model of the software lifecycle proposed by ISO 13849-1 | 17 |

| 3.4 | Requirements map for parts 1 to 7 of IEC 61508 [13]                  | 19 |

| 3.5 |                                                                      | 20 |

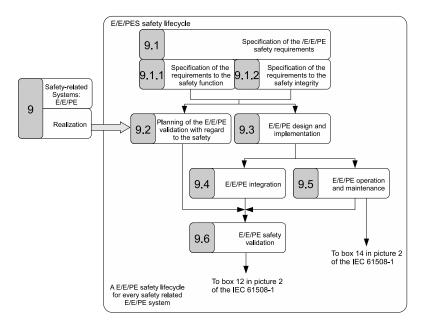

| 3.6 | E/E/PES safety lifecycle in the realization phase defined by [4]     | 22 |

| 3.7 | Relation between hardware and software architectures of PE [5]       | 23 |

| 4.1 | C-model for safety-relevant communication networks [17]              | 36 |

| 4.2 | Example for SRVT timing [17]                                         | 37 |

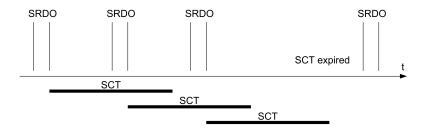

| 4.3 | Example for SCT timing [17]                                          | 37 |

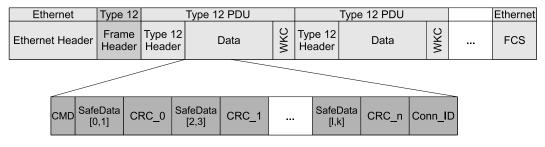

| 4.4 | Basic FSCP 12/1-System [14]                                          | 39 |

| 4.5 |                                                                      | 39 |

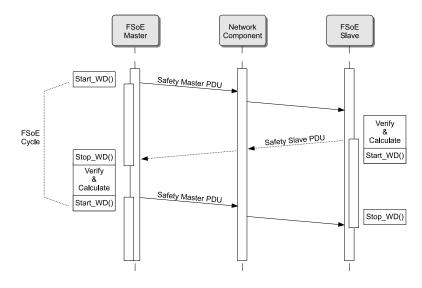

| 4.6 | FSoE Cycle [14]                                                      | 40 |

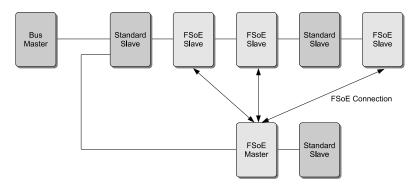

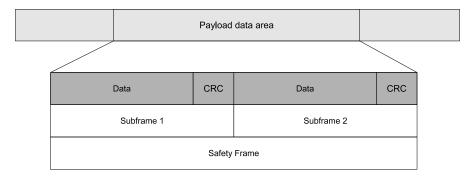

| 4.7 |                                                                      | 42 |

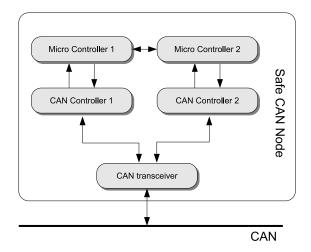

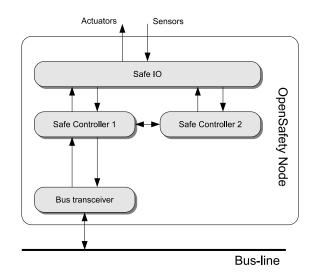

| 4.8 | Possible hardware architecture for an OpenSafety-Node                | 42 |

| 4.9 | SafetyLON protocol Extension                                         | 44 |

| 5.1 | System chain - From the sensor to the actuator                       | 47 |

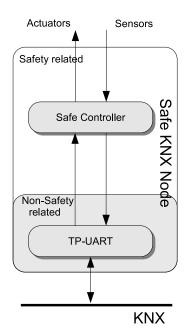

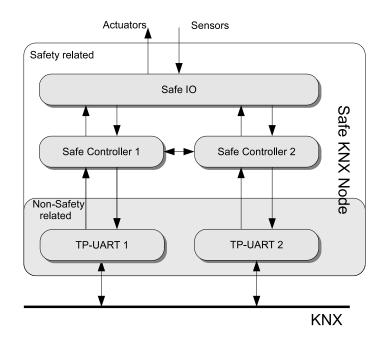

| 5.2  | One channel architecture                                                    | 49 |

|------|-----------------------------------------------------------------------------|----|

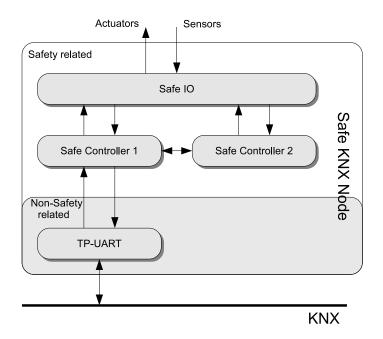

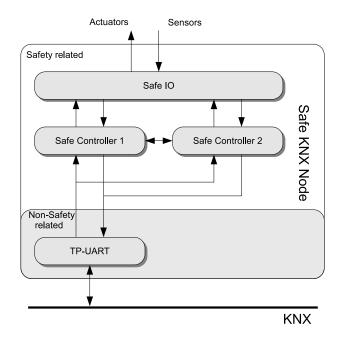

| 5.3  | Replicated Safe Controllers on a single bus-coupler                         | 50 |

| 5.4  | Replicated Safe Controllers on a single bus-coupler - Alternative           | 50 |

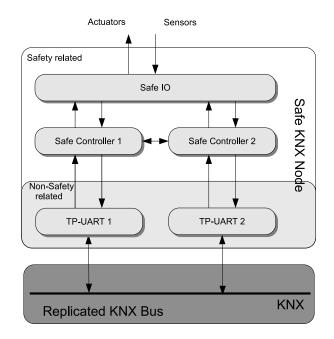

| 5.5  | Replicated Safe Controllers with replicated bus-couplers                    | 51 |

| 5.6  | Redundant Safe Nodes on a redundant Bus                                     | 52 |

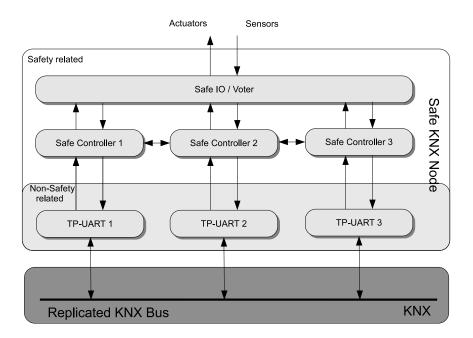

| 5.7  | Triple modular redundancy - TMR                                             | 53 |

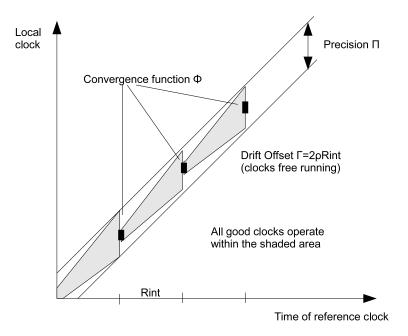

| 5.8  | Synchronization condition                                                   | 55 |

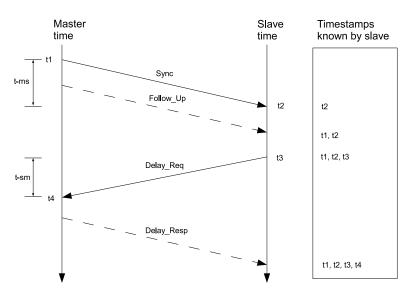

| 5.9  | Basic synchronization message exchange [15]                                 | 57 |

| 5.10 | Example execution of vector clocks                                          | 59 |

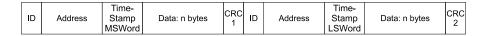

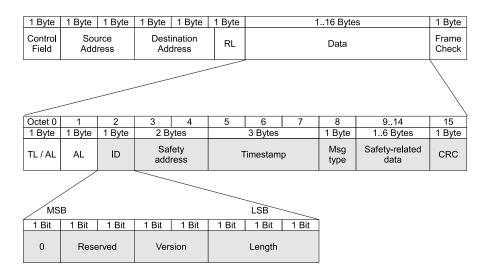

| 5.11 | Safety providing protocol extension for KNX                                 | 60 |

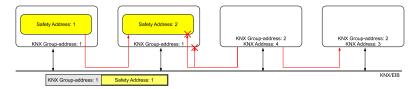

| 5.12 | Schematic addressing in KNX Safety                                          | 62 |

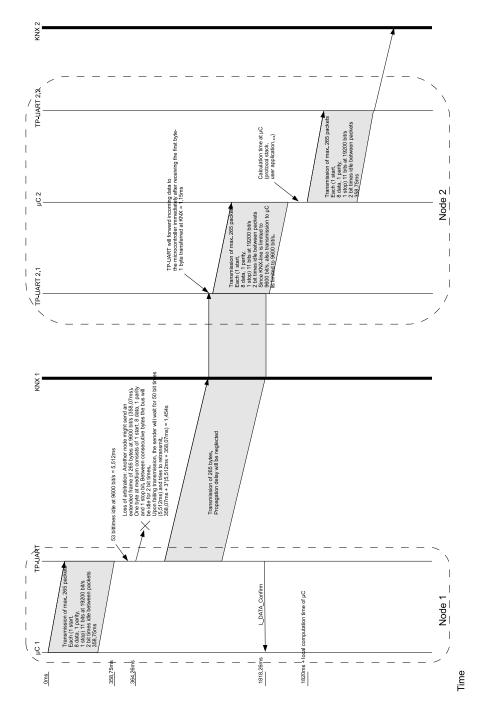

| 5.13 | Timing diagram of message exchange between KNX nodes                        | 65 |

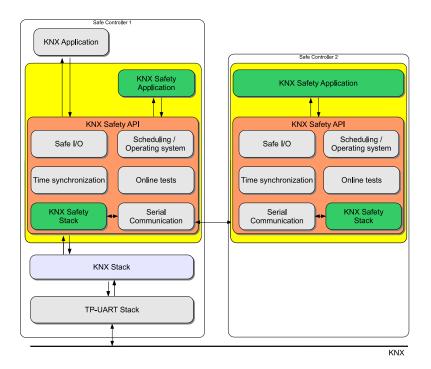

| 5.14 | Software architecture of a safe KNX node                                    | 66 |

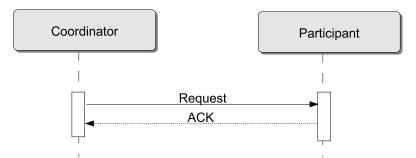

| 5.15 | Simple acknowledge transmission protocol                                    | 67 |

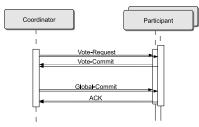

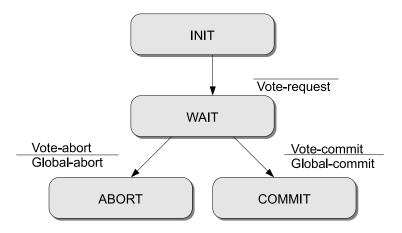

| 5.16 | Sequence diagram of a successful Two-Phase-Commit Protocol                  | 68 |

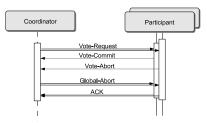

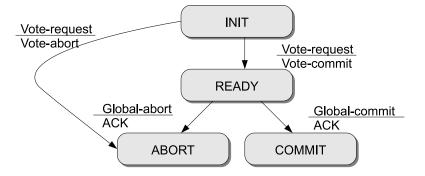

| 5.17 | Sequence diagram of a failed Two-Phase-Commit Protocol                      | 68 |

| 5.18 | State diagram of the coordinator in the Two-Phase-Commit Protocol           | 68 |

| 5.19 | State diagram of a participant in the Two-Phase-Commit Protocol             | 69 |

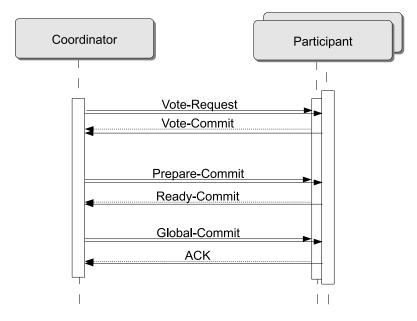

| 5.20 | Sequence diagram of the Three-Phase-Commit Protocol                         | 70 |

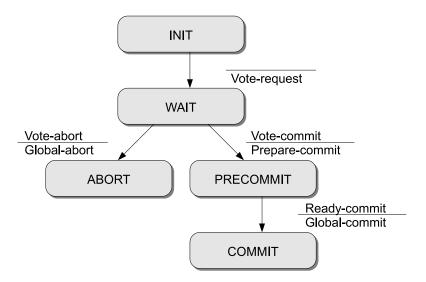

| 5.21 | State diagram of the coordinator in the Three-Phase-Commit Protocol         | 71 |

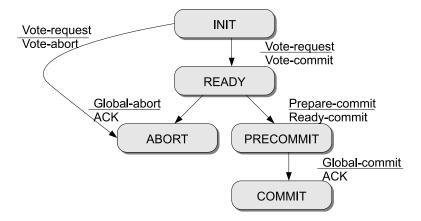

| 5.22 | State diagram of a participant in the Three-Phase-Commit Protocol           | 72 |

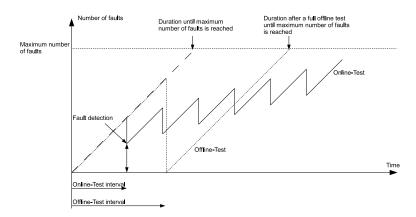

| 5.23 | Online and Offline test intervals. Slightly modified illustration from [28] | 73 |

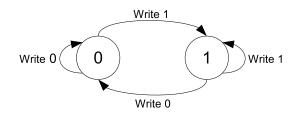

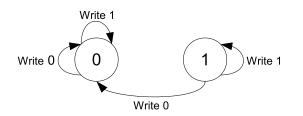

| 5.24 | State diagram of a correct working memory cell                              | 74 |

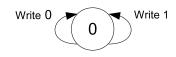

| 5.25 | State diagram of a stuck-at zero error in a memory cell                     | 75 |

| 5.26 | State diagram of a stuck-at one error in a memory cell                      | 75 |

| 5.27 | State diagram of a state transition error of memory cell                    | 75 |

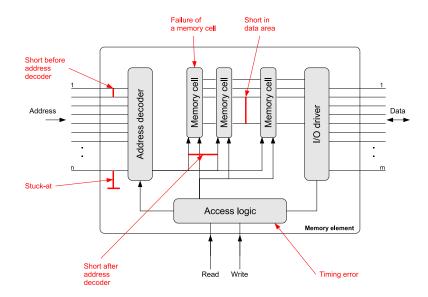

| 5.28 | Potential errors in a memory block                                          | 76 |

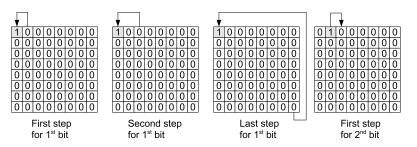

| 5.29 | Sample execution of Galpat-Pattern-Test                                     | 77 |

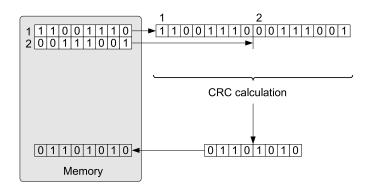

| 5.30 | Sample calculation of CRC                                                   | 78 |

| 5.31 | Structure of stack memory                                                   | 80 |

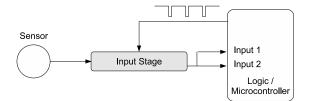

| 5.32 | Single sensor on replicated input stages                                    | 85 |

| 5.33 | Replicated sensors on replicated input stages                               | 85 |

| 5.34 | Example of connecting two switches in line                                  | 86 |

| 5.35 | Example of connecting two switches parallel                                 | 86 |

| 5.36 | Monitoring sensors using pulsed voltage                                     | 86 |

| 5.37 | Test in a closed circuit                                                    | 87 |

| 5.38 | Testable input stage in a closed circuit                                    | 87 |

| 5.39 | Serially connected switches with read-back switch state                     | 87 |

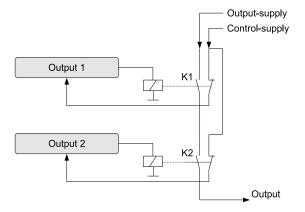

| 5.40 | Two-channel output using semiconductors                                     | 88 |

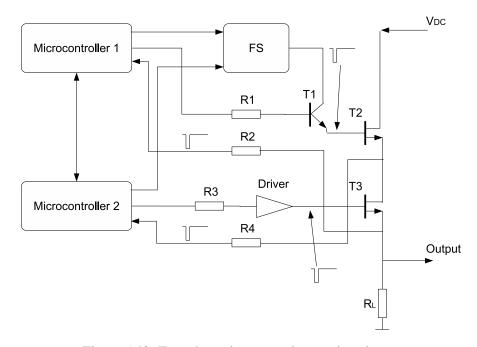

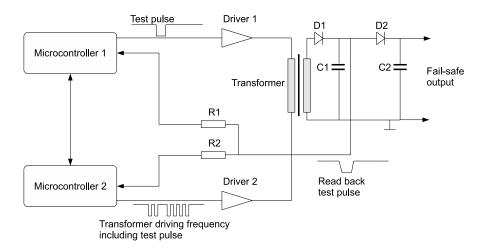

| 5.41 | Fail-safe unit                                                              | 89 |

## **List of Tables**

| 3.1 | Performance Levels (PL)                                                                             | 15 |

|-----|-----------------------------------------------------------------------------------------------------|----|

| 3.2 | Mean time to failure for a channel $MTTF_d$                                                         | 16 |

| 3.3 | Diagnostic coverage (DC)                                                                            | 16 |

| 3.4 | Safety integrity levels for devices with high performance rate [3]                                  | 21 |

| 3.5 | Safety integrity of hardware: Constraints to architectures for safety-related type A subsystems [4] | 24 |

| 3.6 | Safety integrity of hardware: Constraints to architectures for safety-related type B                | 24 |

| 0.0 | subsystems [4]                                                                                      | 25 |

| 3.7 | Relation between Performance Levels (PL) and Safety Integrity Levels (SIL) as de-                   |    |

|     | fined by [10]                                                                                       | 28 |

| 4.1 | Communication errors and detection measures by [9]                                                  | 35 |

| 4.2 | Relation between residual error rate and safety integrity level                                     | 35 |

| 4.3 | Communication errors and detection measures used by CANopen Safety                                  | 38 |

| 4.4 | Communication errors and detection measures used by Safety over EtherCAT                            | 41 |

| 4.5 | Communication errors and detection measures by OpenSafety                                           | 43 |

| 4.6 | Communication errors and detection measures used by Safety LON                                      | 45 |

| 5.1 | Communication errors and detection measures used in KNX safety                                      | 61 |

| 5.2 | Message types for KNX Safety                                                                        | 64 |

| 5.3 | RAM test methods and resulting DC                                                                   | 77 |

| 5.4 | ROM test methods and resulting DC                                                                   | 79 |

| 5.5 | Example round-robin scheduling                                                                      | 84 |

| FSoE    | Failsafe over CPF 12                                         |

|---------|--------------------------------------------------------------|

| CPF     | Communication Profile Family                                 |

| SFF     | Safe Failure Fraction                                        |

| SIL     | Safety Integrity Level                                       |

| PL      | Performance Level                                            |

| $PL_r$  | Required Performance Level                                   |

| E/E/PES | Electric/Electronic/Programmable Electronic System           |

| SRP     | Safety-Related Part                                          |

| EUC     | Equipment under Control                                      |

| MTTR    | Mean Time To Repair                                          |

| DC      | Diagnostic Coverage                                          |

| CCF     | Common Cause Failure                                         |

| SCL     | Safety Communication Layer                                   |

| PTP     | Precision Time Protocol                                      |

| CRC     | Cyclic Redundancy Check                                      |

| FCS     | Frame Checking Sequence                                      |

| SRDO    | Safe Communication Object                                    |

| SRVT    | Safety-relevant Object Validation Time                       |

| SA      | Safe Address                                                 |

| SPDU    | Safety Process Data Unit                                     |

| APDU    | Application Process Data Unit                                |

| GSPN    | Generalized Stochastic Petri Nets                            |

| ANubis  | Advanced Network for Unified Building Integration & Services |

| CPU     | Central Processing Unit                                      |

| OSSD    | Output Silicon Switched Device                               |

| WCET    | Worst Case Execution Time                                    |

| PES     | Programmable Electronic System                               |

| MTTF    | Mean Time To Failure                                         |

| FMEA    | Failure Mode and Effects Analysis                            |

| SCL     | Safety Communication Layer                                   |

| CRC     | Cyclical Redundancy Check                                    |

| CS      | Control System                                               |

| SRESW   | Safety-Related Embedded Software                             |

| SRASW   | Safety-Related Application Software                          |

| HVAC    | Heating Ventilation Air Conditioning                         |

| ROM     | Read Only Memory                                             |

| RAM     | Random Access Memory                                         |

| EPROM   | Electrical Erasable Read Only Memory                         |

| TMR     | Triple Modular Redundancy                                    |

| BCI     | BatiBus Club International                                   |

| EIBA    | European Installation Bus Association                        |

| EHSA    | European Home System Association                             |

| HBA     | Home and Building Automation                                 |

|         |                                                              |

- CSMA Carrier Sense Multiple Access

- TPCI Transport Layer Protocol Control Information

- APCI Application Layer Protocol Control Information

- PDU Process Data Unit

- CAFMS Computer Aided Facility Management System

- FSCP Functional Safety Communication Profile

- SCM Safety Configuration Manager

- CiA CAN in Automation

- SCT Safeguard Cycle Time

# CHAPTER 1

## Introduction

#### 1.1 Motivation

Traditionally, Building Automation Systems (BAS) provide basic services like Heating, Ventilation and Air Conditioning (HVAC), lighting and shading. Safety critical applications like fire detection and alarm systems are usually stand-alone units which interact with BAS using dedicated gateways. Increasing requests for BAS in safety-critical environments ask for advanced mechanisms to integrate safety-critical technology into BAS. Therefore, it is necessary to define what safety-critical properties are and what their meaning is - to detect hazardous events in an automation system. These can be failures in hardware, software or the underlying communication-system like a "wrong message" in any way. Such a message can be wrong in a sense of its value-domain or in its time-domain. Detection of the afore mentioned failures requires implementation of certain mechanisms in hardware and software.

The requirements for safety-critical systems are specified in two common standards - ISO 13849 (Safety of machinery - Safety-related parts of control systems) and IEC 61508 (Functional safety of electrical/electronic/programmable electronic safety-related systems). Especially, IEC 61508 presents a very general view on requirements and guidelines for the complete lifecycle of a safety-related device. Requirements to communication systems are presended in detail in IEC 61784-3 (Functional safety fieldbuses).

The thesis follows the approach presented in [20] and tries to extend the KNX protocol to fulfill requirements of SIL 3 as defined by IEC 61508. To achieve this, certain measures regarding hardware and software are required. From a hardware point of view a higher level of safety can be achieved by application of redundancy approaches. Furthermore, software is required which is capable of detecting failures in hardware and the communication system. On that score, the following chapters will give discussions on how to achieve functional safety in the KNX protocol in terms of hardware requirements and involved software.

#### **1.2** Guide through this Thesis

Chapter 2 will give an overview about automation systems and related terms and definitions. Furthermore, the target technology KNX will be described.

Chapter 3 will cover state-of-the-art standards IEC 61508 and ISO 13849 and show the main differences between them. Following IEC 61508, the achievement of specific Safety-Integrity-Levels (SIL) is of importance. SILs define requirements concerning electrical and programming-standards implying the failure rate of a safety-providing device depending on its frequency of use. In the context of this thesis, high demanding devices which allow a maximum of one hazardous failure in  $10^7$  hours will be of special interest (SIL3).

Existing solutions in BAS and industrial automation will be presented and compared in Chapter 4. Here, special attention is put on potential communication errors as defined by IEC 61784-3.

In Chapter 5, special aspects relevant for this thesis regarding safety will be presented in detail. This will include a discussion on possible hardware architectures, communication issues, clock synchronization, scheduling and hardware self tests.

The closing Chapter 6 will conclude gained knowledge and provides an outlook on further work.

# CHAPTER 2

## **Building Automation Systems**

Progress in technology mostly aims at making things more convenient for the user. Focusing on electronic devices, additionally energy efficiency comes into mind. That trend also affects buildings or their building automation systems. When talking about automation, mainly industrial automation comes into mind. Characterized by short reaction times, fast control loops, high precision and occasionally high dependability, an industrial automation system handles tasks where human power is not sufficient, too slow, or not possible due to dangerous environments. Building Automation Systems (BAS) are a special category of industrial automation. In contrast, timings are more relaxed due to long response times from the building. Additionally, a BAS has to take care of energy efficient house keeping and to do that in a most comfortable way.

#### 2.1 Introduction

BAS start at small homes with just a handful of devices and end at large, public buildings like airports or office buildings automatized by some thousand devices. Especially for large buildings the advantage of BAS is clear: A BAS provides central knowledge and control about all processes involved in a building which is also known as Computer Aided Facility Management System (CAFMS). In case of an error, the operator is enabled to gain information about the error and can initiate measures to maintain the system at a very early stage. Another advantage of BAS is the ability to dynamically reconfigure the behaviour of the system. If for example a light switch should control more than the initially installed lamps, it was necessary to re-wire certain parts of the installation in traditional electrical installations. Using a BAS, simply re-binding the switch to more lamps can be done from a PC in far less time. Having knowledge of multiple sensors also enables construction of intelligent buildings. For example, opening a window will turn off the heating or ventilation. Likewise, increasing temperatures in a room will activate sun shadings and climate control. Since the properties of a comfortable room climate are different for each person, smart room controllers in combination with knowledge about who is in the room could control HVAC according to the person's preferences (smart buildings). Against all

advantages, the main disadvantage is the tremendous cost for initial installation. Additionally, operators have to be trained thoroughly.

According to [19], typically the running costs of a building over its lifetime are seven times the initial cost for construction. Considering the whole life cycle of a building, the amount of saved energy during its lifetime makes the use of a BAS economically feasible.

Another topics in BAS are security and safety. These are two completely different concepts, although described by the same word in German language ("Sicherheit").

Security describes protection of a system against malicious attacks. For instance, considering a network, insertion of a malicious message or listening to the contents sent through the network have to be detected or prevented by certain security measures. At the beginning, BAS were designed and implemented as closed systems and missing knowledge of potential intruders on how to break the BAS was protection enough. Advances in wireless technology, networked automation devices in every room in combination with open standards give motivation for development of appropriate measures to close those vulnerabilities.

Safety describes the failure free operation of a system or at least the detection of an error and transferring the system to a safe state. Safety in automation is currently just available for industrial automation solutions (with some minor exceptions). That can be divided into requirements for operator safety and requirements for process safety. For example, an emergency stop information transferred through an automation network is required to be delivered and performed within predefined deadlines. If that requirement cannot be met, the operator working on the machine could sustain injury or the machine could take damage. That means, the information has to be transmitted correctly and in time - no matter what happens, the machine has to be transferred to a safe state. Safety in HBA has been an isolated topic so far, addressing primarily fire alarm systems. Until now, safety providing systems have been mainly constructed as closed systems communicating via dedicated gateways with other systems. The only HBA solution providing functional safety found so far is an extension to LON called SafetyLON.

#### **Automation Networks**

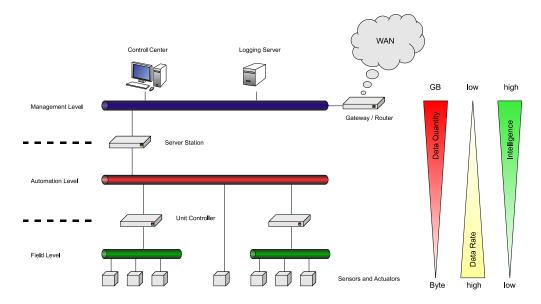

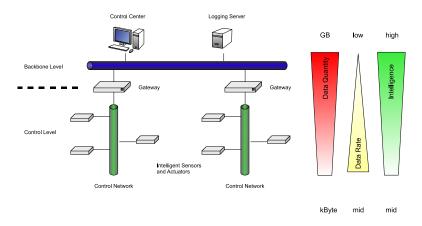

Communication in a traditional automation system can be visualized by the three-levelarchitecture as depicted in Figure 2.1.

The *field level* is responsible for direct interaction with the physical environment and collects data from simple sensors and activates actuators. Usually that level is equipped with lowbandwidth networks. The collected data is transferred to the *automation level* which processes and passes data to the management level (*vertical communication*) or issues other devices at field level to take action (*horizontal communication*). The topmost *management level* provides a global view of all data across the BAS. Therefore, control terminals and logging systems are placed on that level. Operators are enabled to (re-)configure the BAS through a control center and perform diagnostic measures on the BAS in case of an error. Typically, the management level is equipped with a high-bandwidth network caused by high amount of data collected by the lower levels. If communication with other automation systems is required, the management level networks are connected via gateways or routers.

As described, the previous approach assumes simple sensors with small processing power to prepare raw data in a very basic way. Development in the microprocessor sector increased

Figure 2.1: Three-tier architecture

processing power to admit advanced techniques to pre-process and transmit sensor values [18]. That simplifies the diagram in Figure 2.1 to the enhanced two-tier architecture depicted in Figure 2.2 by making use of *intelligent devices*.

Figure 2.2: Two-tier architecture

Increased intelligence on sensor/actuator level enables integration of communication protocols for direct communication between sensors and actuators through a *control network* what makes a separate automation level obsolete. Communication between different control networks is established via gateways through *backbone networks* providing sufficient bandwidth for intercontrol network communication as well as for management- and logging tasks.

### 2.2 KNX

In 1996, *BatiBus Club International* (BCI), *European Installation Bus Association* (EIBA) and *European Home System Association* (EHSA) started to develop a common standard for home and building automation. In 1999, leading manufacturers of electrical building equipment such as Siemens, Bosch and Merten, along with some more, founded Konnex Association (also known as KNX Association). The first KNX specification was published in 2002 which was adopted EN 50090 in 2005 and accepted as an international standard ISO/IEC 14543-3 later in 2006.

Basically, KNX defines runtime-characteristics, a toolkit of services as well as mechanisms to manage a network. The building automation system is defined by a distributed application implemented through standardized data-point types and "functional block" objects modelling logical device channels. KNX is platform independent enabling usage of any kind of microprocessor to implement a network device.

#### **Elements of KNX**

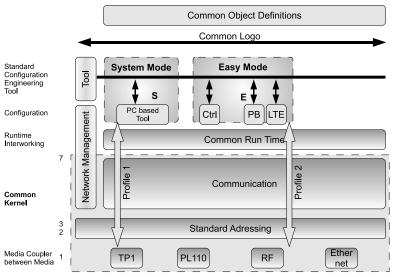

The KNX framework consists of the following parts:

- An inter-working and (distributed) application model which performs the actual HBA application (lighting, shading, HVAC,...).

- Configuration and management schemes for logical linking or binding of KNX devices. These schemes are structured in a set of configuration modes.

- A communication system which defines communication media, a message protocol and a communication stack. The communication system has to implement required mechanisms for configuration and management and hosts the distributed application. This is typified by the KNX Common Kernel [2].

- A set of device models is summarized in profiles.

An illustration of the afore mentioned components of KNX is depicted in Figure 2.3.

#### Supported communication media by KNX

KNX offers a wide variety of possible communication media suited to customer's needs and devices to enable interaction between different media.

• Twisted pair is the basic medium in KNX. Main characteristics are: energy and information are transported over the same pair of wires, an asynchronous, character oriented data transfer, half duplex, bi-directional communication. TP1 (9,6 kBit/s) is the basic medium inherited from EIB and allows free choice of topology. On top of TP1 the CSMA/CA protocol is implemented.

Ctrl = Controller approach LT = Logical Tag PB = Push Button approach LTE = Logical Tag extended

Figure 2.3: KNX model [2]

- Powerline (PL110, 1,2 kBits/s) allows data transmission over main wire. Its characteristics are a central frequency of 110 kHz, spread frequency shift keying signalling, asynchronous transmission of data packets and half duplex, bi-directional communication. PL110 implements CSMA and is EN 50065-1 compliant.

- RF is fully specified within KNX in the 868 MHz bandwidth. Characteristics are: frequency shift keying signalling, asynchronous, half duplex, bi- or unidirectional communication. The central frequency is set to 868,30 MHz using short range device frequency with a duty cycle limited to < 1% and a data rate of 32 kHz. Medium access is based on CSMA mechanisms [1].

- Furthermore, IP-enabled integration for IEEE 802.2 (LAN), 802.11 (WLAN), IEEE1394 (Firewire) is handled in KNXnet/IP.

The communication is implemented in compliance with the OSI layer model. As in most automation systems, not all seven layers are implemented. KNX uses the following four layers:

- The "Data Link Layer General" is implemented on top of the *Data Link Layer* and provides medium access control and logical link control.

- The *Network Layer* provides a segment wise acknowledge telegram and controls hop count of a frame.

- The *Transport Layer* enables communication relationships between communication points. Supported relations are 1 to N (multicast) connectionless, 1 to all (broadcast) connectionless, 1 to 1 connectionless and 1 to 1 connection-oriented.

- The Application Layer offers a toolkit to maintain and run the distributed application.

#### **Topologies**

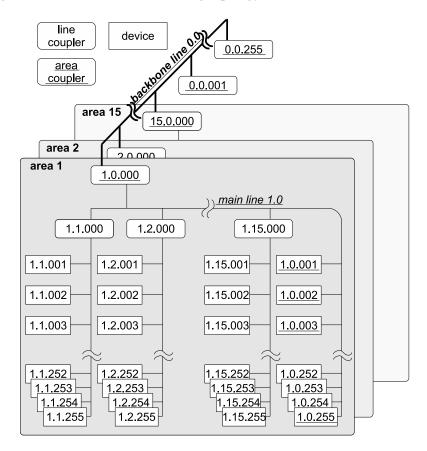

As shown later, a KNX frame supports 16-bit space for individual source and destination addresses. That results in a total of 65535 possible devices on a KNX network. The network can be grouped physically into *lines* of 256 devices each. These lines can be formed by a *main line* into an *area*. A *domain* is a combination of up to 15 areas connected through a *backbone line*. Figure 2.4 gives an illustration of the resulting topology.

Figure 2.4: KNX topology [2]

#### Addressing schemes

Central functionality of a network is to enable communication between nodes. Therefore, nodes need to be identified uniquely. In most cases, an installation will be wired and configured afterwards. KNX offers device identification by a unique device serial number or by the device's individual address. Unique serial device numbering is achieved through controlled allocation of number ranges to manufacturers by KNX Association. By knowledge of a devices identification (unique serial number or individual address) it is possible to communicate with that device.

KNX distinguishes system resources keeping configuration information (address-, lookup tables and parameters) and parameters which control the application.

Communication is distinguished between network resource management and run-time communication. Configuration and management tasks usually require direct communication with the related node (point-to-point connection) or require communication with all nodes (broadcast) nodes. In contrast, run-time communication mainly uses multicast communication with other nodes interested in changed values.

In order to achieve inter-working, the data-points have to implement "Standardized Datapoint Types", grouped into "Functional Blocks". Communication between nodes is established after "binding" or linking data-points located on different devices to common multicast group addresses. Binding of devices happens either through loose or strict binding rules or depending on semantic information contained in the address. Upon a successful binding process the distributed application is enabled. That is, if a local application on a node writes a data-point value the change notification will be sent across the network with the corresponding address of the sending node. Any node interested in the changed value from that node will receive that value and inform its local application about the new value. The local application on the receiving node will now react depending on its internal state machine and update its own data-points. The communication between nodes transferes multiple local applications into a single, distributed application.

KNX supports the following three binding schemes: free, structured or tagged. Basically, free and structured binding assume free addressing which means that the numerical value of addresses do not contain application semantics. The only assumption is, that all data-points communicating with each other are assigned to the same address. Contrarily, tagged binding assumes the numerical value of an address to contain a semantic (data-point) identifier. Therefore, the *logical tag* or *zoning* part of the address identifies a device's communication partners on a device level. By assigning data-points to the same zone, they form a group communicating via multicast.

To configure a KNX network, two main configuration modes are specified as depicted in Figure 2.3. Depending on the user's preferences and application environment these modes provide functionality to configure a device remotely from ETS tool or locally using the push button approach:

• E(asy)-Mode is applied for simple manipulations where devices are configured according to a structured binding without need for separate configuration tools. Controller mode (Ctrl) supports installation of a limited number of devices on one logical

segment of a physical medium. Such an installation will contain one dedicated node responsible for the configuration process.

Logical Tag (LT) and Logical Tag Extended (LTE) modes basically enable device configuration using DIP-switches or selectors.

Push Button mode (PB) is almost equal to Ctrl-mode configuration but without the need for a dedicated configuration device.

• S(ystem)-Mode enables central, free binding and configuration of the installation, typically carried out with the ETS tool.

#### **KNX Frame**

The frame of a KNX TP1 telegram is depicted in Figure 2.5. Depending on the communication medium, different preambles might be appended which will be left unconsidered here.

| Octet 0          | 1 | 2              | 3 | 4              | 5                                   | 6 |      | 7             | 8 |      | N-1 | N≤22           |

|------------------|---|----------------|---|----------------|-------------------------------------|---|------|---------------|---|------|-----|----------------|

| Control<br>Field |   | ource<br>dress |   | nation<br>ress | Address<br>Type;<br>NPCI;<br>Length |   | APCI | Data;<br>APCI |   | Data |     | Frame<br>Check |

Figure 2.5: KNX LPDU TP1 standard frame structure

The control field determines the priority and distinguishes between standard and extended frame format. The individual source address determines the address of the sending node. The individual (unicast) or group (multicast) destination address determines the address of the receiving node(s). The following byte contains hop-count and address-type-information. The Transport Layer Protocol Control Information (TPCI) controls the transport layer to manage end-to-end connection. The Application Layer Protocol Control Information (APCI) accesses application layer primitives (read, write, response,...). The standard frame ensures compatibility with KNX messages (up to 14 octets of data). Extended frames can contain up to 248 octets of data. The enclosing frame check sequence ensures data consistency.

#### **KNX line access**

To access contents sent on the KNX line, special hardware in form of a transceiver is required. Therefore, Siemens provides the TP-UART-IC (Twisted Pair - Universal Asynchronous Receive Transmit - IC).

This module supports every transmit- and receive - function and also the high ohmic decoupling of energy from bus line. It generates further a stabilized 3.3V or 5V supply to use by a host controller. Up to 256 subscribers can be connected to one bus line [25]

The TP-UART-IC consists of an analog part responsible for level converting on the KNX-line and a digital part providing serial access for communication with connected microcontrollers.

# CHAPTER 3

## **State-of-the-art Standards**

This section gives an overview of applicable standards for safety-related systems. First, ISO 13849 for a general approach regarding safety of machinery is presented. A more detailed description of safety-related development is specified by IEC 61508, a standard defining a complete lifecycle model for every development phase of an Electric/Electronic/Programmable Electronic System (E/E/PES). Here, a degree of safety is described by safety integrity levels (SIL) which are assigned depending to the probability of one hazardous failure per hour. In contrast, performance levels (PL) are defined by ISO 13849.

Prior to focusing on the standards, some important terms such as fault, error, failure, risk, hazard, dangerous failure and hazardous event are introduced:

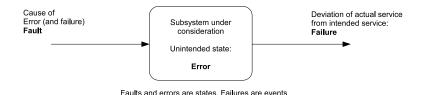

[21] describes faults, errors and failures as a chain depicted in Figure 3.1. A *fault* is the cause of an error and, thus, the indirect cause of failure. In [6], a fault is defined as an unusual condition which leads to loss of ability to perform a desired functionality. An *error* is both, the deviation of an expected result ([6]) or an incorrect internal state, like a corrupted element in the memory ([21]), whereas a *failure* is an event that denotes the deviation between the actual and the intended service, or the loss of ability to perform a demanded functionality, respectively.

Figure 3.1: Fault chain defined by [21]

Risk is defined as the combination of probability of error and the resulting harm [6].

A *hazard* is a potential source of harm and is specified to define the source (mechanical or electrical harm) or type (fire, cut or electrical shock) of harm [6]. Thus, a *hazardous event* is a situation where a hazard leads to a harm [6].

A *dangerous failure* describes a failure that potentially leads the safety-related system to a dangerous or non-functioning state [6].

In safety-related systems, redundancy is common practice which introduced multiple-channel architectures. Such an architecture can be, for example, a *loo2 architecture* (one out-of two) describing an approach where one output is chosen among two possible candidates (see Figure 3.2). The expression loo2 gives no information about the chosen criteria for either of the two input channels. It is clear, that such an architecture is optionally extendable by more inputs like a loo3 or loo4 architecture.

Figure 3.2: One-out-of-two architecture (1002)

A clear distinction has to be drawn between safety and security, although it is not always possible in every aspect. Security describes the protection of a system against malicious attacks. Contrarily, safety is defined as the ability of a system to perform its intended behaviour even in case of failure under predefined conditions.

The structure of standards in the domain of safety-related machinery as defined by ISO 12100-1 is as follows:

- Type-A-Standards cover definitions, design guidelines, and general aspects applicable to machinery.

- Type-B-Standards cover a specific safety-aspect or a type of safety equipment that is applicable for a wide range of machinery:

- Type-B1-Standards for specific safety-aspects like safety margins and temperature levels.

- Type-B2-Standards for safety equipment.

- Type-C-Standards cover detailed safety requirements for a specific machine or a group of machines.

In case different standards have to be applied, like a Type-A and a Type-C standard, the higher level standard (Type-C in that case) will have to be favoured. By means of that categorization, ISO 13849 is a Type-B1 standard.

# 3.1 ISO 13849 - Safety of machinery - Safety-related parts of control systems

This section explains some of the basic principles on how to achieve a certain level of safety as defined by ISO 13849-1 [10]. Performance levels (PL) are the base for the following development process. This standard specifies methods to fulfill the requirements for a PL through the terms diagnostic coverage, mean time to failure, common cause failure, and some more key words explained briefly in the following. Furthermore, ISO 13849 defines requirements to the lifecycle of safety-related software. The second part of the standard (ISO 13849-2 [11]) presents guidelines and techniques for the validation of the afore defined safety concept.

All parts of a machine control supplying safety functionality are called "safety-related parts of the control system" (SRP/CS). These parts may be realized in hard- or software. Additionally, such a machine may supply operational functionality. The ability of a device to provide safety-related functionality under predictable conditions is divided into five PLs as shown in Table 3.1. These PLs are defined in terms of probability of a dangerous failure per hour.

| Performance Level (PL) | Average probability of                |

|------------------------|---------------------------------------|

|                        | a hazardous failure per hour          |

|                        | [1/h]                                 |

| a                      | $\ge 10^{-5}$ until $< 10^{-4}$       |

| b                      | $\geq 3 * 10^{-6}$ until $< 10^{-5}$  |

| с                      | $\ge 10^{-6}$ until $< 3 * 10^{-6}$   |

| d                      | $\ge 10^{-7} \text{ until} < 10^{-6}$ |

| e                      | $\ge 10^{-8}$ until $< 10^{-7}$       |

Table 3.1: Performance Levels (PL)

Probability of a dangerous failure depends on certain parameters. ISO 13849 defines the following criteria which have to be considered:

- Hard- and software structure

- Fault detection mechanisms

- Degree of diagnostic coverage (DC)

- Dependability of used devices  $(MTTF_d)$

- Common cause failures (CCF)

- Behaviour at systematic failures

- Behaviour at faults

- Development process

- Load under operational conditions

- Environmental conditions

With regard to the evaluation process of PLs those aspects are grouped into quantifiable (MTTF, DC, CCF, structure) and non-quantifiable, qualitative (all others) principles. Quantifiable aspects of PLs can be estimated by usage of Markov models, generalized stochastic Petri Nets (GSPN)

or reliability block diagrams. In ISO 13849, the determination of PLs under quantifiable aspects is proposed by five different architectures fulfilling predefined characteristics in case of fault. If other architectures are used, detailed calculations on the achieved PLs need to be given. For a description of predefined architectures, please refer to [10].

To achieve a required PL, measures have to be taken to lower risk. These measures are the reduction of the probability of a fault on device level by usage of more reliable devices and by improvement of the structure of the SRP/CS to lower the effect of the fault. Depending on expectable faults, these measures can be applied separately or together, where common cause failures have to be taken into account.

#### Mean time to failure of a channel $MTTF_d$

Assuming a redundancy approach, a *channel* is defined to be one of the replicated paths. The value of the  $MTTF_d$  of each channel is divided into three steps as depicted in Table 3.2 and shall be calculated individually for each channel.

| Description for each channel | Range for each channel                |

|------------------------------|---------------------------------------|

| low                          | 3 years $\leq MTTF_d < 10$ years      |

| medium                       | 10 years $\leq MTTF_d < 30$ years     |

| high                         | 30 years $\leq MTTF_d \leq 100$ years |

Table 3.2: Mean time to failure for a channel  $MTTF_d$

$MTTF_d$  for each device has to be determined by gathering information from data-sheets provided by the manufacturer or other methods defined in appendices C and D of [10]. If neither is applicable, a duration of 10 years has to be taken.

#### **Diagnostic coverage DC**

In most cases an estimation of the DC will be done by a Failure Mode and Effects Analysis (FMEA) or a similar procedure. Therefore, all relevant faults and failures have to be considered, including a calculation if the PL of the SPR/CS fulfills the required performance level  $PL_r$ . ISO 13849 defines four levels of DC as shown in Table 3.3.

| Description | Range                |  |

|-------------|----------------------|--|

| none        | DC < 60%             |  |

| low         | $60\% \le DC < 90\%$ |  |

| medium      | $90\% \le DC < 99\%$ |  |

| high        | $99\% \le DC$        |  |

Table 3.3: Diagnostic coverage (DC)

#### **Requirements to safety-related software**

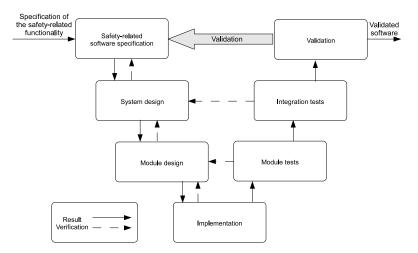

The aim of the software development process is to avoid faults introduced by the software lifecycle. ISO 13849 specifies certain criteria which have to be fulfilled depending on the required performance level. Basically, a consistent documentation of the whole development process falls into these conditions. The standard proposes to use the simplified V-Model for the software lifecycle as shown in Figure 3.3.

Figure 3.3: Simplified V-Model of the software lifecycle proposed by ISO 13849-1

This standard distinguishes between safety-related embedded software (SRESW) and safetyrelated application software (SRASW). A subset of the applicable methods for SRESW and SRASW up to the  $PL_r$  d is listed in the following:

- Software lifecycle with verification and validation

- Documentation and reasoning of the specification and the design

- Modular and structured development and implementation

- Handling of systematic failures

- Extended functional tests

- Change management including reasoning

- Quality management

Usage of SRASW is subjected to some more requirements depending on the type of programming language and the  $PL_r$ :

- Certified toolchain

- Validated libraries

- Criteria to performance (e.g. reaction times)

- Semi-formal methods to describe data and control flow

- Simulation of the implemented code

- Adequate testing

- A complete, consistent, readable, available and understandable documentation

- Verification

- Change management

For detailed requirements, please refer to points 4.6.2 and 4.6.3 in [10].

ISO 13849-1 proposes the parametrization of safety-related software as well. According to this, the inserted parameters need to be examined with respect to their validity. Further, safe data transmission from a configuration tool to the device has to be ensured and the effects of incomplete or incorrect transmitted parameters have to be known in advance. Additionally, the configuration tool needs to comply with the same requirements of SRP/CS as the configured device. Once again, for a detailed description of applicable criteria to parametrize safety-related devices, please refer to point 4.6.4. in [10].

#### ISO 13849-2 Validation

The standard's second part addresses validation of mechanical, pneumatical, hydraulic and electronic systems. The validation process assumes error lists containing all considered faults. These lists are processed by a predefined validation process and a validation plan. Furthermore, the whole validation process needs to be documented.

Finally, the most important part is the validation of safety-related functionality. In that step validation has to ensure correct operation of the device under different configurations and its reaction to different inputs. Additionally, where applicable, a combination of safety-related devices needs to be validated by analysis or by testing if required.

### 3.2 IEC 61508 - Functional safety of E/E/PE safety-related systems

IEC 61508 is the de-facto standard for anything concerning safety-related electric/electronic/programmable electronic (E/E/PE) systems. It covers every single step of the development process of safety-related systems starting from the very first concept up to the decommission of the system and provides requirements and methods in order to achieve a specified safety integrity level (SIL).

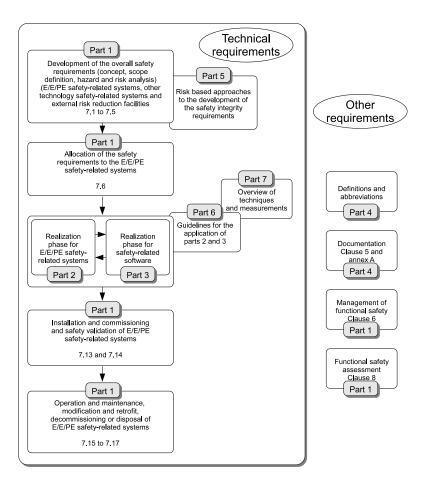

IEC 61508 is divided into seven technical parts and an additional guide part. The document structure and relation between them are shown in Figure 3.4. Part one covers basic terms, conditions and requirements for the entire safety lifecycle of the development process. The second part addresses special requirements for E/E/PE systems. In the third part, the development of safety-related software is examined in terms of lifecycle, parametrization, extension and upgrading, whereas definitions and abbreviations are defined in the fourth part. Methods for determining the achieved safety integrity level are laid down in part five. The sixth part presents guidelines for the application of parts two and three. Finally, the seventh part gives an overview of techniques and measures for the implementation and validation.

Before details regarding the development of a safety-related system are described, basic definitions of safety and functional safety need to be given. According to IEC 61508-0 [13] the definition of safety is as follows:

Figure 3.4: Requirements map for parts 1 to 7 of IEC 61508 [13]

This is the freedom from unacceptable risk of physical injury or of damage to the health of people, either directly, or indirectly as a result of damage to property or to the environment.

Opposite to that, functional safety is defined as:

Functional safety is part of the overall safety that depends on a system or equipment operating directly in response to its inputs.

Both terms can only be determined by considering the system as a whole together with the environment it is interacting with. The procedure of developing a safety-related device is as follows: First, a hazard analysis needs to be performed. According to this, the necessity of functional safety is determined. If so, adequate measures need to be taken into account during design.

Functional safety means, that it is required to perform a specific function to ensure that risks are kept below a certain level. Therefore, the *safety function requirements* (what the function

does) deriving from the hazard analysis and the *safety integrity requirements* (the probability that the safety function performs as defined) which again derive from the risk assessment need to be determined. The hazard analysis points out what needs to be done to prevent hazardous failures, whereas risk assessment defines the degree of certainty that the safety function will be performed.

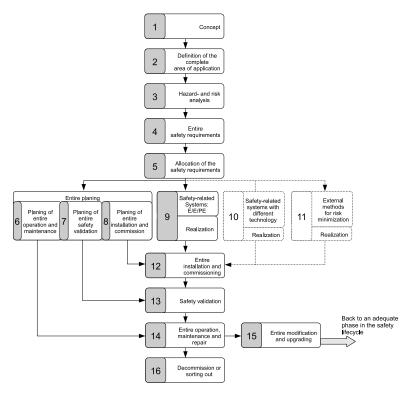

#### The entire safety lifecycle

In order to achieve the required safety integrity, the standard defines a lifecycle model (see Figure 3.5) which covers every step of the lifetime of a safety-related device starting at the first concept and ending by the decommission of the device.

Figure 3.5: Entire safety lifecycle as defined by [3]

To achieve and keep a defined SIL during the design and throughout the further operation, each step must to be documented scrupulously. Additionally, the generated documentation has to be versioned, revisioned and approved. Further, the standard requires defined authorities for the technical and management phases of each cycle in the model, referred to as *management of functional safety*.

A brief description of the single steps of the entire safety lifecycle seems to be helpful:

The concept phase is intended to get knowledge about the equipment under control (EUC) and its environment. This is the base for the consecutive steps, for which reason all possible

sources of hazards and information about them as well as any information from applicable standards have to be pointed out.

The aim of defining the complete area of application is to show the limits of the EUC and the application area for the following hazard and risk analysis, requiring specification of physical devices, external events and subsystems.

The hazard and risk analysis point out hazards, hazardous events and sequences leading to hazardous events. Probability of a hazardous event, its impact and necessary measures to reduce the risk have to be considered. Furthermore, any assumptions during the analysis have to be stated.

The entire safety requirements target the development of safety-related E/E/PES, focussed on the safety functionality and the safety integrity. Therefore, safety functions and necessary risk reduction for every hazardous event have to be defined. Requirements for safety integrity have to be determined for every safety function.

Assignment of safety requirements is intended to map the previously defined safety functions to the safety-related systems and E/E/PES and to assign a SIL to each of these functions. In case the assignment of the safety requirements shows that the required SIL cannot be achieved, the architecture has to be changed and the assignment needs to be re-done. Requirements to safety integrity have to be adequate in order to show that the mean probability of failure or the probability of a hazardous failure per hour is satisfied. Furthermore, common cause failures (CCF) have to be taken into account, unless the single subsystems can be shown to operate independently. Independence is given if

- the subsystems are functionally different,

- they are based on different technologies,

- they do not use common parts, services or supply systems,

- they have no common operational, maintenance or test measures, or

- they are physically separated.

In case one of these requirements cannot be satisfied the subsystems cannot be considered as independent in terms of safety integrity.

Once the mapping has been done, the safety integrity levels have to be assigned according to Table 3.4.

| Safety Integrity Level | Operational mode with continuous operation  |

|------------------------|---------------------------------------------|

|                        | (Probability of a hazardous fault per hour) |

| 4                      | $\geq 10^{-9} \text{ until } < 10^{-8}$     |

| 3                      | $\geq 10^{-8}$ until $< 10^{-7}$            |

| 2                      | $\geq 10^{-7} \text{ until } < 10^{-6}$     |

| 1                      | $\geq 10^{-6} \text{ until } < 10^{-5}$     |

Table 3.4: Safety integrity levels for devices with high performance rate [3]

For systems containing of multiple subsystems with different SILs, the whole system will have to be regarded as a system with the lowest SIL among its subsystems, unless it can be shown that sufficient independence between them is present.

#### The E/E/PES lifecycle model defined by IEC 61508-2

This section describes the lifecycle model for a E/E/PES as a part of the overall IEC 61508-1 lifecycle model in Figure 3.5. Therefore, the component 9 of the model is extracted into further steps as shown in Figure 3.6. The model is kept very general and can be used unchanged for hard- and software development. The sub-lifecycle is organized in six tasks which will be explained in the following.

Figure 3.6: E/E/PES safety lifecycle in the realization phase defined by [4]

#### Specification of the E/E/PES safety requirements

The specification of the requirements to the safety functionality needs to contain the following:

- A description of the provided safety functionality

- Performance requirements like throughput and response times

- Interfaces between the E/E/PES and user interfaces

- Any safety relevant information

- Operational modes like parametrization, automatic, semi-automatic, manual, shut down, maintenance

- All kinds of failure performance, i.e. the reaction of the system in case of failure (e.g. alarm or shut-down)

- The meaning of the hardware/software interaction

- Constraints and limits of the E/E/PE subsystems

- Requirements to the commission and restart of the E/E/PES

Furthermore, the specification of the E/E/PES safety integrity requires to define the SIL for every safety function, the operational mode for every safety function, limits to the environmental conditions and limits to electromagnetic compatibility.

#### Planning the validation of the safety-related E/E/PES regarding safety

#### E/E/PES design and implementation

This step presents the most complex part in the development process of a safety related device. For better understanding, it is subdivided into several smaller items:

**General requirements** The main requirement is that the design needs to fulfill the specification in all points. The design of a safety-related E/E/PES including hard- and software-architecture, sensors, actuators, programmable electronics, embedded- and application software as shown in Figure 3.7 has to be accomplished in order to satisfy all of the following conditions:

- Safety integrity requirements to hardware consisting of the requirements due to the probability of dangerous hardware failures and the constraints of the safety integrity caused by hardware architecture.

- Requirements to the systematic safety integrity consisting of the certificate of approved devices and the requirements to avoidance and handling of systematic failures.

- Requirements to the system behavior when detecting a fault.

| Architecture of the programmable electronic                                                                                 |                                                                                    |                                                                                                                              |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PE Hardware Architecture                                                                                                    | PE Hardware Architecture<br>(containing of embedded and application software)      |                                                                                                                              |  |  |  |  |

| General and application-                                                                                                    | PE Embedded software                                                               | PE Application software                                                                                                      |  |  |  |  |

| specific properties of the<br>PE hardware<br>Examples:<br>- Diagnostic tests<br>- Redundant processors<br>- Two-Channel I/O | Examples:<br>- Communication drivers<br>- Fault handling<br>- Application software | Examples:<br>- I/O functions<br>-Derived functionality like<br>sensor tests if not pro-<br>vided by the embedded<br>software |  |  |  |  |

Figure 3.7: Relation between hardware and software architectures of PE [5]

In case a safety-related E/E/PES supplies safety-relevant and non-safety-relevant functionality, the complete hardware and software have to be considered safety-relevant except a proof for the independence of safety and non-safety-related parts of the system can be provided. The arising SIL that has to be satisfied is the highest among all affected devices. That means, a system requiring SIL2 has to contain systems satisfying at least SIL2. If one subsystem just fulfills SIL1, the whole system is considered to have SIL1.

If independence between safety and non-safety functionality is required the methods for achieving the separation and the reasons therefore have to be disclosed.

The developer has to ensure the adequateness of the requirements for the safety-related E/E/PES hardware and software with focus on the safety-functionality, safety-integrity requirements, electrical equipment and user interfaces.

A further step requires documentation and reasoning of the applied procedures and measures in design as well as of hardware-software interaction.

The whole system has to be partitioned into subsystems whereby each of them requires a separate design and verification process. In case a subsystem has multiple outputs it is required to show that no possible combination of states leads to a hazardous failure of the E/E/PES. If possible, all components should be dimensioned for underload.

**Constraints to the hardware safety integrity due to architecture** The highest achievable SIL in the context of hardware is limited through the fault tolerance of the hardware and the fraction of safe failures in the subsystems. A fault tolerance of N means that the safety functionality will get lost by N+1 faults with the constraint that fault detection mechanisms like diagnosis must not be taken into consideration. Where a fault leads to another fault, these two faults are considered to be a single fault. If certain improbable faults can be excluded from the fault tolerance calculation it has to be reasoned and documented. The fraction of non-hazardous failures (SFF) of a subsystem is defined as the mean rate of non-hazardous faults plus hazardous detected faults divided by the overall failure rate of the subsystem:

$$SFF = \frac{Safe Faults + Detected Faults}{Overall Failure Rate of the Subsystem}$$

(3.1)

The standard defines subsystems of types A and B. Type A is required to be completely specified by means of fault performance of the components, the subsystem itself under a fault and reliable information about process experience. Even if only one requirement is not fulfilled, a subsystem is classified as type B. Depending on the subsystem type either Table 3.5 for type A or Table 3.6 for a type B subsystem have to be taken into consideration. These tables describe the achievable SIL depending on the fault tolerance of the hardware and the fraction of nonhazardous failures. For example, a subsystem of type A with more than 99% of non-hazardous failures can reach SIL4 with a fault tolerance of 1.

| Fraction of nonhazardous failures | Fault tolerance of the hardware |      |      |  |

|-----------------------------------|---------------------------------|------|------|--|

|                                   | 0                               | 1    | 2    |  |

| < 60%                             | SIL1                            | SIL2 | SIL3 |  |

| 60% - <90%                        | SIL2                            | SIL3 | SIL4 |  |

| 90% - <99%                        | SIL3                            | SIL4 | SIL4 |  |

| $\geq$ 99%                        | SIL3                            | SIL4 | SIL4 |  |

Table 3.5: Safety integrity of hardware: Constraints to architectures for safety-related type A subsystems [4]

**Requirements for the estimation of the failure probability of a safety function due to random hardware faults** The probability of loss of the safety functionality due to random hard-

| Fraction of nonhazardous failures | Fault tolerance of the hardware |      |      |  |

|-----------------------------------|---------------------------------|------|------|--|

|                                   | 0                               | 1    | 2    |  |

| < 60%                             | not allowed                     | SIL1 | SIL2 |  |

| 60% - <90%                        | SIL1                            | SIL2 | SIL3 |  |

| 90% - <99%                        | SIL2                            | SIL3 | SIL4 |  |

| ≥99%                              | SIL3                            | SIL4 | SIL4 |  |

Table 3.6: Safety integrity of hardware: Constraints to architectures for safety-related type B subsystems [4]

ware faults has to be less than the specified failure limit and has to be estimated considering the following:

- The architecture of the safety-related subsystem related to the safety function.

- The estimated failure rate/s of each subsystem in every operational mode which leads to a dangerous failure and can/cannot be detected through diagnostic mechanisms.

- The vulnerability to common cause failures.

- The diagnostic coverage of the diagnostic tests.

- The interval of online tests to detect dangerous faults which cannot be detected by diagnostic tests.

- The probability of an undetected failure of any data transmission process.

According to these criteria the diagnostic test-interval has to be set adequately. If for any design the required limits of failure rates cannot be fulfilled, critical components or parameters need to be identified and possibilities for improvements have to be located. Afterwards the improvements have to be applied and the probability of a hardware failure has to be determined again.

**Requirements to avoid failures** Therefore, appropriate procedures and measures have to be developed and applied. According to the required SIL, these procedures have to be modular and transparent. Furthermore, they have to give a clear and precise description of the provided functionality, the interfaces of the subsystems, the timely order of the information and parallel operation and synchronization. Additionally, a proper documentation as well as validation and verification have to be supported.

Maintenance schemes and integration tests have to be planned during the design phase to ensure that the required SIL can be obtained. If possible, automated tools and integrated development tools should be used.

**Requirements to handle systematic failures** Systematic failures should already be detected in the design phase. Therefore, the testability and maintainability as well as the human abilities to operate the system have to be taken into account. Thus, the design should ensure that all remaining design errors regarding the hardware, environmental conditions, human errors, all remaining software errors and communication issues are detected.

**Requirements to the system behavior at fault detection** If a fault has been detected the system either has to go into a safe state and inform the operator about it or, if that is not possible, the fault has to be isolated. If the fault cannot be fixed within the MTTR a predefined action has to take place.

**Requirements to E/E/PES implementation** The implementation of the safety-related E/E/PES has to be in agreement with the design of the E/E/PES. Every subsystem that is used by a safety function has to be identified and described as a safety-related subsystem. To every safety-related subsystem the following information has to be provided:

- The functional specification of functions and interfaces used by the safety-related subsystem.

- The estimated failure rate/s caused by random hardware errors in every mode leading to a dangerous failure and being detected or not by diagnostic measures.

- The environmental limits of the subsystem.

- The lifetime of the subsystem.

- Maintenance requirements and intervals.

- The diagnostic coverage and test interval.

- Any required information to determine the MTTR.

- Any information to determine the fraction of safe failures.

- Fault tolerance of the hardware.

- All remaining limits applicable to the subsystem to avoid systematic failures.

- The highest SIL that can be consumed by a safety function.

- Any information regarding configuration of the subsystem.

- A confirmation about the verification of the subsystem.

Estimated failure rates for a subsystem caused by random hardware errors can be determined by a failure mode and effects analysis (FMEA) or, if available, by performance information about the subsystem under similar conditions.

**Requirements to data communication** In case of data communication influencing the safety functionality, the probability of an undetected fault of the communication system has to be estimated. Therefore, transmission errors, repetition, loss, insertion, wrong sequence, corruption, delay and masquerade have to be taken into account. Especially the parameters residual error rate, rate of residual information loss, bitrate and message delay have to be considered for the estimation. The topic of data communication will be discussed in detail in the Section 4.1 describing the IEC 61784-3.

#### **E/E/PES** integration

The integration tests of an E/E/PES have to ensure that all modules interact in the specified way and fulfill the intended behaviour. For the execution of the tests, appropriate procedures and measures have to be applied. Furthermore, every modification needs to be evaluated and the tests themselves must be properly documented.

# E/E/PES operation and maintenance procedures

That point addresses the routinely procedures for maintenance purposes. It has to be ensured that an unsafe state does not occur during these tasks. Moreover, it requires that irregularities from the normal operation and online test results are documented. Procedures for maintenance have to be defined which are applied in case of failure including procedures for diagnosis, repair, logging and analysis of failures and revalidation. Routinely maintenance procedures have to fulfill systematic methods which have to detect non-detected failures resulting in reduction of the required safety integrity.

# Validation of the E/E/PES regarding safety

Validation of the E/E/PES has to be performed according to the previously defined validation plan. Each used measurement device has to be calibrated and verified for its correct functionality. During tests every safety function has to be evaluated according to its intended behaviour and results have to be documented in an adequate way.

# **E/E/PES modification**

If an existing E/E/PES has to be modified the following requirements have to be complied:

- An exact and complete specification of the modification.

- An analysis of the impact on the whole system.

- Approval for all modifications.

- Test-cases of the modified components including data gained by the revalidation process.

- Deviations from the normal operation.

- Required changes to the system behaviour and the documentation.

Once the system has been modified it has to be re-verified and re-validated.

# **E/E/PES** verification

The goal of the verification is to ensure the correctness and consistency of the device with the specification. Therefore, the verification already has to be planned during the development phase of the E/E/PES. That plan has to include strategies and procedures for verification, usage of measurement devices, documentation and analysis of the gained results. For each stage of the design phase it has to be shown that the safety integrity requirements are fulfilled.

# SIL 3 in detail

In the previous sections some of the basic requirements for the development of a safety-related E/E/PES have been presented. Basically, these requirements are applicable from SIL 1 to SIL 4. Part 3 of IEC 61508 [5] presents guidelines for every SIL with a special focus on the software of an E/E/PES.

As already mentioned the development of safety-related software has to be executed according to the lifecycle model in Figure 3.6. Besides, some more guidelines for the implementation of each step are given in Appendix A and B of [5]. For the software specification and design, computer-based specification tools and semi-formal methods are recommended. Appropriate, if possible certified, programming languages, toolchains, compilers, libraries and integrated development environments should be used. As this thesis does not target a fully developed device, not all of the recommendations can be met. For instance, the usage of interrupts and pointers should be avoided although they are some of the basic concepts in microcontroller programming.

According to Table 3.6, a SIL can be achieved by increasing the SFF or the fault tolerance of hardware. For SIL3 that is to detect more than 99% of hazards with a fault tolerance of 0 or to detect 90% to 99% of hazards with a fault tolerance of 1 or to detect 60% to 90% of hazards with a fault tolerance of 2. As shown later, a high SFF can only be gained through extensive online tests and thus high diagnostic coverage. The consequence is to increase hardware fault tolerance. A discussion on different hardware architectures will be given in Section 5.1.

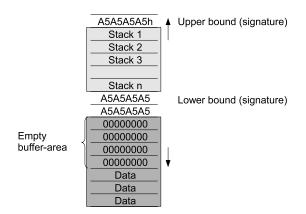

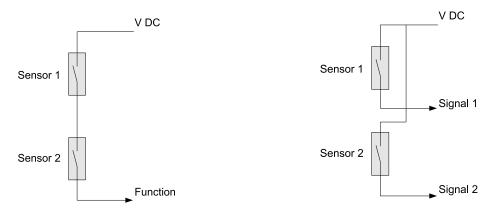

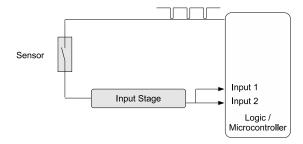

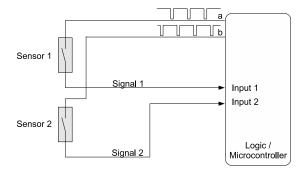

# 3.3 Conclusions of ISO 13849 and IEC 61508