# Effects and Mitigation of Transient Faults in Quasi Delay-Insensitive Logic

### DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

#### Doktor der technischen Wissenschaften

by

Dipl.-Ing.(FH) Werner Friesenbichler

Registration Number 0526423

to the Faculty of Informatics at the Vienna University of Technology Advisor: A.o.Univ.Prof. Dipl.-Ing. Dr. Andreas Steininger

The dissertation has been reviewed by:

A.o.Univ.Prof. Dipl.-Ing. Dr. Andreas Steininger

Prof. Dr.-Ing. Heinrich Theodor Vierhaus

Wien, im Dezember 2011

Dipl.-Ing.(FH) Werner Friesenbichler

#### Erklärung zur Verfassung der Arbeit

Dipl.-Ing.(FH) Werner Friesenbichler Rosengasse 10/7, 2700 Wiener Neustadt

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit - einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

#### Acknowledgements

I would like to thank Andreas Steininger for his advice, experience and patience in the often lengthy discussions. Of course I also would like to thank Heinrich Vierhaus from the Brandenburg University of Technology Cottbus for reviewing the thesis and giving fruitful feedback. Thank you RUAG Space Gmbh for granting sponsoring to attend conferences.

Thanks to my colleague Thomas Panhofer, for all the helpful suggestions, reviews, collaborations on papers, coffee break discussions and especially for the motivation during stressful periods.

Finally, my thanks go to my family, my friends and especially to Stephanie, for supporting my work and giving me the strength and endurance to get the job done.

## Abstract

Asynchronous *Quasi Delay-Insensitive* (QDI) logic offers an improved fault tolerance compared to common synchronous logic. Its delay-insensitive encoding makes QDI circuits not only robust to varying delays but also highly insensitive to transient faults, as such faults likely generate illegal data that is simply ignored.

To describe these fault effects in a quantitative manner, a model that includes all assumptions and boundary conditions has to be employed on. With existing models one has to make a trade-off between the level of detail they provide and their complexity. In this work, a new *trace based fault model* is developed. It covers both unprotected as well as hardened QDI circuits in the necessary level of detail, while still only moderate computational efforts are required to analyze real-world circuits. A *trace* is the sequence of all signal transitions a circuit receives and generates. As that sequence can be used to synthesize QDI circuits, it only seems to be natural to utilize traces for the description of QDI circuits in a faulty environment as well. Thereby the developed model is used to identify problematic fault scenarios and to derive their relative probability.

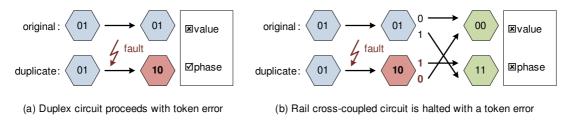

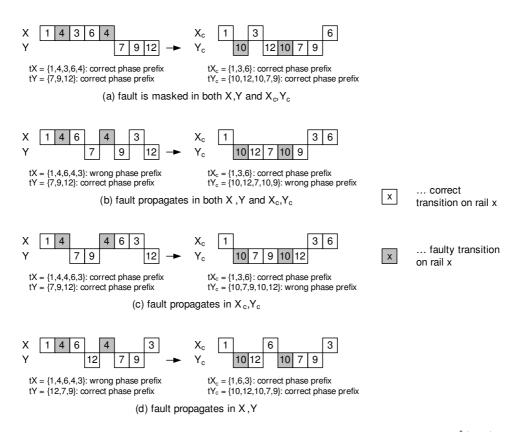

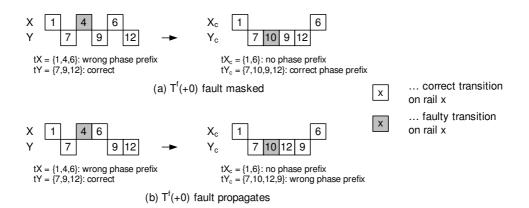

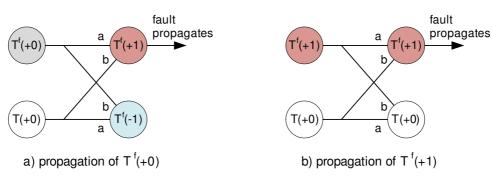

In the field of QDI circuits, different hardening strategies exist. Based on the insights gained from the trace based fault model, a new method called *duplication and rail cross-coupling* is derived. The idea is to re-arrange the particular rails of QDI signals in such a way that a transient fault will lead to an illegal code that prevents the fault from being processed. Such a hardened QDI circuit simply waits until the transient fault decays or it deadlocks for indefinite time, but without propagating any data errors. The initial approach was refined and led to the modified DRXS / DRXX / DRS methods, which are investigated in more detail.

For a systematic assessment of the proposed hardening methods two complementary approaches using simulation and hardware based fault injection are applied. While related tools are described in literature, these do not appropriately consider the peculiarities of QDI logic. Consequently, two customized fault injection tools are developed, one for *fault simulation* and one for *fault emulation*. These tools allow an adequate investigation of transient fault effects, thereby backing up the theoretic results from both the trace based fault model as well as the proposed hardening methods. Several basic test circuits as well as one moderately complex signal processing application are selected to verify the predicted fault tolerance of the different hardening strategies. It is shown that a clever rearrangement of a duplicated QDI circuit helps to improve the tolerance against transient faults significantly, while keeping the hardware overhead low.

## Kurzfassung

Asynchrone *Quasi Delay-Insensitive* (QDI) Logik liefert eine im Vergleich zu synchroner Logik verbesserte Fehlertoleranz. Die delay-unabhängige Kodierung macht sie nicht nur robust gegenüber veränderlichen Verzögerungen sondern auch insensitiv gegen transiente Fehler, da solche mit hoher Wahrscheinlichkeit illegale Daten erzeugen die einfach ignoriert werden.

Um die Effekte von transienten Fehlern zu beschreiben, muss zuerst ein Modell mit sämtlichen Annahmen und Randbedingungen gefundent werden. Existierende Modelle gehen dabei oft einen Kompromiss zwischen Detailierungsgrad und Komplexität ein. In dieser Arbeit wird ein auf *Traces* basierendes Modell entwickelt, das sowohl ungeschützte als auch gehärtete QDI Schaltungen ausreichend detailiert beschreibt und gleichtzeitig den Aufwand zur Analyse von realistischen Schaltungen in Grenzen hält. Ein Trace beschreibt die Abfolge aller Signalereignisse einer Schaltung. Da diese Abfolge auch zur Synthese von QDI Schaltungen verwendet werden kann, scheint es nur natürlich die selbe Methodik auch für die Schaltungsbeschreibung in einer fehlerbehafteten Umgebung einzusetzen. Das entwickelte Modell dient sowohl zur Identifizierung von problematischen Fehlerszenarios als auch zur Berechnung deren relativer Wahrscheinlichkeit.

Im Bereich der QDI Schaltungen existieren unterschiedliche Härtungsverfahren. Auf Basis der Erkenntnisse des Trace-Modells wird eine neue Methode namens *duplication and rail cross-coupling* abgeleitet. Die Idee ist die einzelnen Leitungen eines QDI Signals so umzuordnen, dass ein transienter Fehler zu einem illegalen Code führt, der eine Weiterverarbeitung verhindert. Die Schaltung wartet bis der Fehler wieder verschwindet oder bleibt für immer stehen, ohne falsche Daten zu verbreiten. Der erste Ansatz dieser Idee führt schließlich zu den verfeinerten DRXS / DRXX / DRS-Methoden, welche genauer untersucht werden.

Für eine systematische Untersuchung der vorgeschlagenen Verfahren werden komplementäre Fehlerinjektionsexperimente auf Simulations- und Hardware-Ebene angewandt. Da etablierte Verfahren die Besonderheiten von QDI Logik nicht ausreichend berücksichtigen, werden zwei individuell angepasste Fehlerinjektionswerkzeuge entwickelt, eines für *Fehlersimulation* und eines für *Fehleremulation*. Diese erlauben eine adquate Untersuchung von transienten Fehlereffekten und erlauben so eine Bestätigung der theoretischen Erkenntnisse des Trace-Modells als auch auf die vorgeschlagenen Härtungsverfahren. Einige grundlegende Testschaltungen sowie eine komplexere Signalverarbeitungsanwendung werden ausgewählt, um die prognostizierte Fehlertoleranz der unterschiedlichen Verfahren zu überprüfen. Es wird gezeigt, dass eine intelligente Neu-Anordnung einer duplizierten QDI Schaltung die Toleranz gegen transiente Fehler signifikant verbessert, während der zusätzliche Schaltungsaufwand klein gehalten werden kann.

# Contents

| 1        | Intr | oducti  | ion                                                                                                                                            | 1  |

|----------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

|          | 1.1  | Motiva  | ation                                                                                                                                          | 1  |

|          | 1.2  | Scope   |                                                                                                                                                | 3  |

|          | 1.3  | Contri  | $ibution \ldots \ldots$ | 4  |

|          | 1.4  | Outlin  | ne and Methodology                                                                                                                             | 5  |

| <b>2</b> | Bac  | kgrour  | nd                                                                                                                                             | 7  |

|          | 2.1  | Async   | hronous Logic                                                                                                                                  | 7  |

|          |      | 2.1.1   | General                                                                                                                                        | 7  |

|          |      | 2.1.2   | Classification                                                                                                                                 | 9  |

|          |      | 2.1.3   | Operating Modes                                                                                                                                | 10 |

|          |      | 2.1.4   | Handshake Protocols                                                                                                                            | 10 |

|          |      | 2.1.5   | Quasi Delay-Insensitive Logic                                                                                                                  | 12 |

|          | 2.2  | Faults  | and Errors in QDI Circuits                                                                                                                     | 17 |

|          |      | 2.2.1   | Definitions and terms                                                                                                                          | 17 |

|          |      | 2.2.2   | Fault Classification                                                                                                                           | 18 |

|          |      | 2.2.3   | Logic Fault Models                                                                                                                             | 19 |

|          |      | 2.2.4   | Masking Effects                                                                                                                                | 20 |

|          |      | 2.2.5   | Fault Model                                                                                                                                    | 22 |

|          |      | 2.2.6   | Error Classification                                                                                                                           | 24 |

| 3        | Fau  | lt Dese | cription                                                                                                                                       | 27 |

|          | 3.1  | Relate  | ed Work                                                                                                                                        | 27 |

|          |      | 3.1.1   | Transition Based Fault Description                                                                                                             | 27 |

|          |      | 3.1.2   | Token Based Fault Description                                                                                                                  | 28 |

|          | 3.2  | Circui  | t Definition $\ldots$                                         | 29 |

|          |      | 3.2.1   | Signal Transition Graph                                                                                                                        | 29 |

|          |      | 3.2.2   | State Graph                                                                                                                                    | 31 |

|          |      | 3.2.3   | Trace Theory                                                                                                                                   | 31 |

|          |      | 3.2.4   | Delay-Insensitivity                                                                                                                            | 32 |

|          | 3.3  | Nomir   | al Behavior of QDI Circuits                                                                                                                    | 34 |

|   |     | 3.3.1  | Combinational Circuits               |

|---|-----|--------|--------------------------------------|

|   |     | 3.3.2  | Sequential Circuits                  |

|   |     | 3.3.3  | Nominal Trace Description            |

|   | 3.4 | Trace  | Based Fault Description              |

|   |     | 3.4.1  | Introduction                         |

|   |     | 3.4.2  | Boundary Conditions                  |

|   |     | 3.4.3  | Token Classes                        |

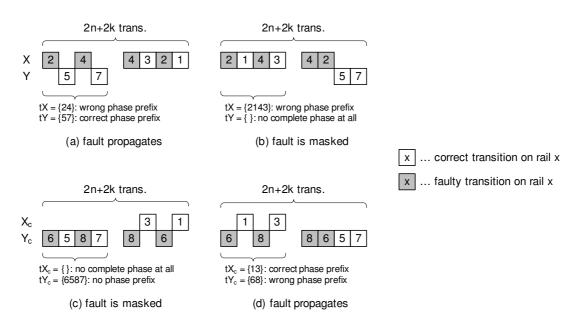

|   | 3.5 | Fault  | Effects                              |

|   |     | 3.5.1  | Effects at Block Interconnections    |

|   |     | 3.5.2  | Effects in Combinational Logic       |

|   |     | 3.5.3  | Effects in Sequential Logic          |

|   | 3.6 | Summ   | nary                                 |

| 4 | Fau | lt Mit | igation 59                           |

| 1 | 4.1 |        | luction                              |

|   | 1.1 | 4.1.1  | Soft Error Rate    60                |

|   |     | 4.1.2  | Fault Trace Propagation    62        |

|   |     | 4.1.3  | Assessment of Soft Error Probability |

|   |     | 4.1.4  | Principle of Redundancy              |

|   | 4.2 |        | ed Work                              |

|   |     | 4.2.1  | Hardware redundancy methods          |

|   |     | 4.2.2  | Duplication                          |

|   |     | 4.2.3  | Rail synchronization                 |

|   |     | 4.2.4  | Re-calculation                       |

|   |     | 4.2.5  | Forcing deadlocks                    |

|   |     | 4.2.6  | Concurrent error detection           |

|   | 4.3 | Trace  | Based Fault Assessment               |

|   |     | 4.3.1  | Evaluation of Fault Propagation      |

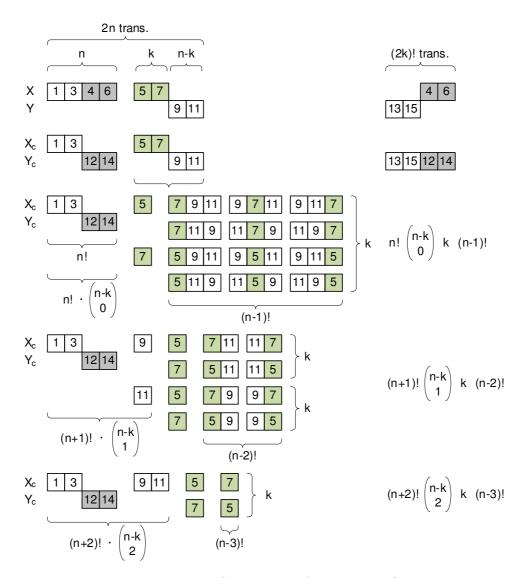

|   |     | 4.3.2  | Trace Re-ordering                    |

|   |     | 4.3.3  | Dependency on the encoding           |

|   |     | 4.3.4  | Impact of the handshake protocol     |

|   |     | 4.3.5  | Multiple rail transitions            |

|   | 4.4 | Duplie | cation and Rail Cross-coupling       |

|   |     | 4.4.1  | Principle                            |

|   |     | 4.4.2  | Evaluation of Fault Masking          |

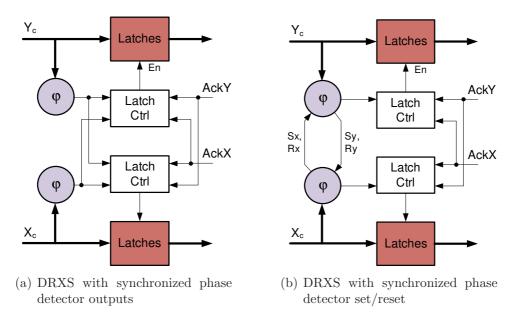

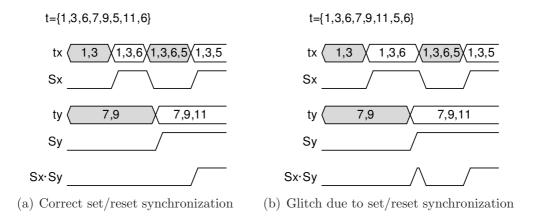

|          |                | 4.4.3   | Synchronized rail cross-coupling                            |

|----------|----------------|---------|-------------------------------------------------------------|

|          |                | 4.4.4   | Tolerance against multiple errors                           |

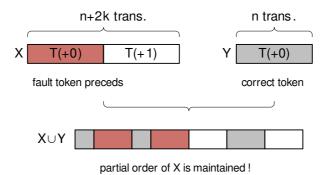

|          |                | 4.4.5   | Fault propagation and storage in cross-coupled circuits 102 |

|          |                | 4.4.6   | Rail comparison                                             |

|          |                | 4.4.7   | Summary                                                     |

|          | 4.5            | Fault   | Injection Overview                                          |

| <b>5</b> | $\mathbf{Sim}$ | ulatio  | n 115                                                       |

|          | 5.1            | Relate  | ed Work                                                     |

|          | 5.2            | Fault   | Simulation in QDI Logic                                     |

|          | 5.3            | The F   | OSTER Tool                                                  |

|          |                | 5.3.1   | Description of the Tool                                     |

|          |                | 5.3.2   | Error detection                                             |

|          |                | 5.3.3   | Random Tests                                                |

|          |                | 5.3.4   | Evaluation of Token Classes                                 |

|          |                | 5.3.5   | Interpretation of Soft Error Probability                    |

|          | 5.4            | Simula  | ation of DRXS Hardened Circuits                             |

|          |                | 5.4.1   | Test Setup                                                  |

|          |                | 5.4.2   | Test Circuit Selection                                      |

|          |                | 5.4.3   | Results                                                     |

|          | 5.5            | Summ    | ary                                                         |

| 6        | Em             | ulation | 153                                                         |

|          | 6.1            |         | ed Work                                                     |

|          |                |         | Emulation in QDI Logic                                      |

|          | 0.2            | 6.2.1   | Error Coverage                                              |

|          |                | 6.2.2   | Reproducibility                                             |

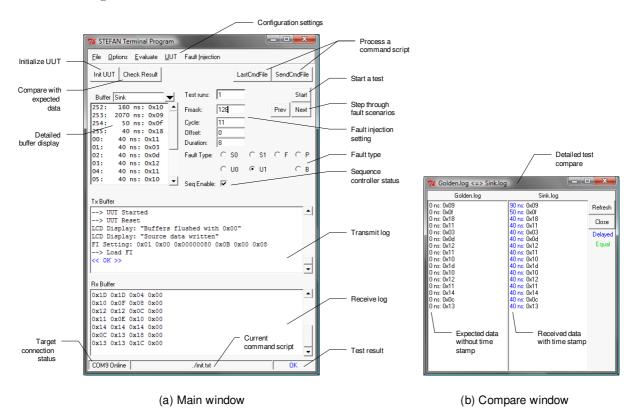

|          | 6.3            |         | TEFAN Tool                                                  |

|          | 0.0            | 6.3.1   | Description of the Tool                                     |

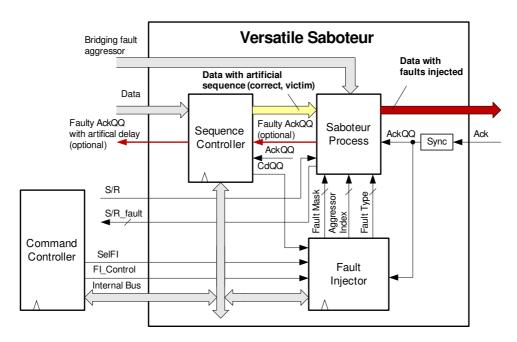

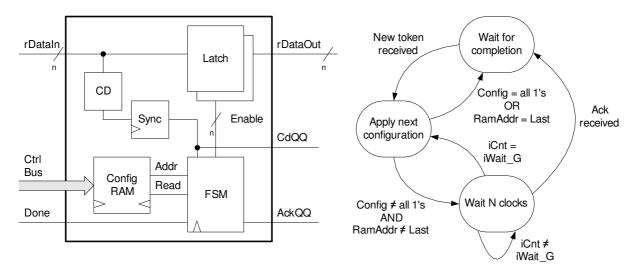

|          |                | 6.3.2   | A Versatile Saboteur                                        |

|          |                | 6.3.3   | Usage                                                       |

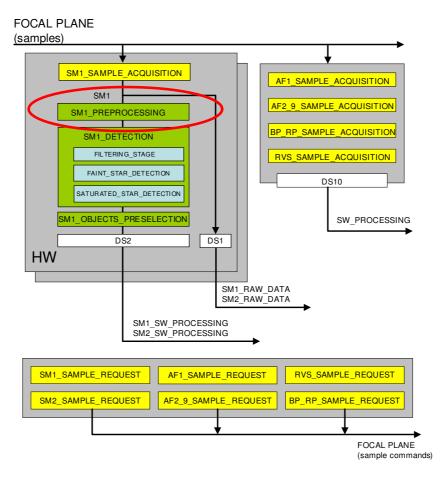

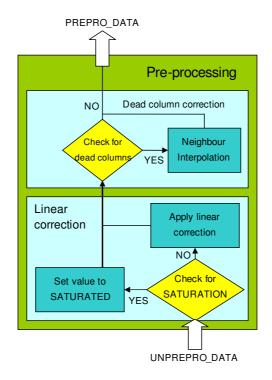

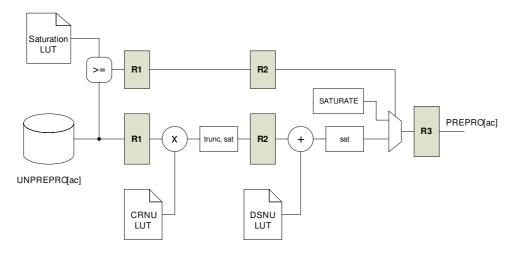

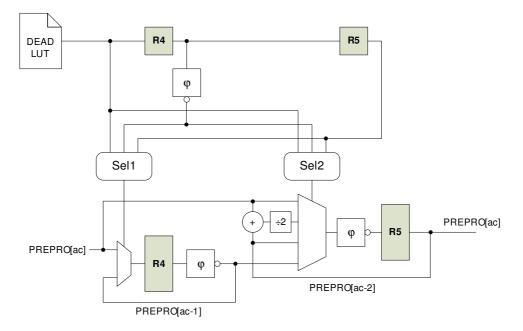

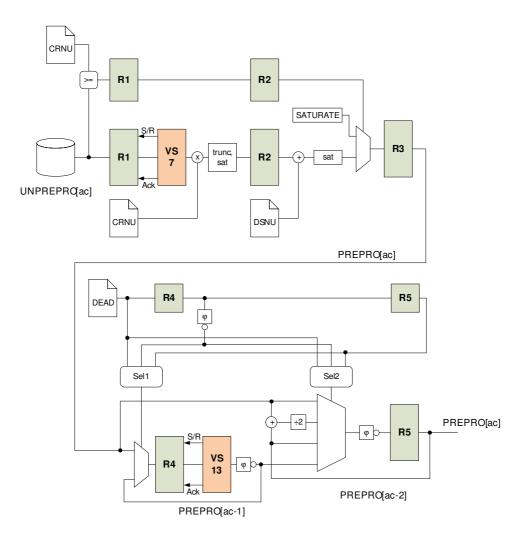

|          | 6.4            |         | eation: The GAIA Video Pre-Processing Algorithm             |

|          | 0.1            | 6.4.1   | The GAIA Mission                                            |

|          |                | 6.4.2   | The GAIA Pre-Processing Algorithm                           |

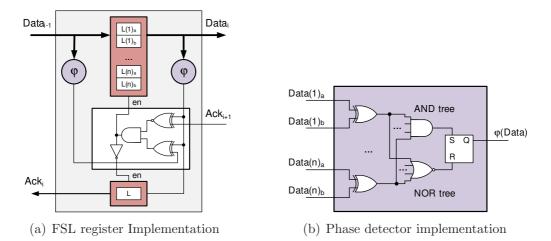

|          |                | 6.4.3   | FSL Implementation                                          |

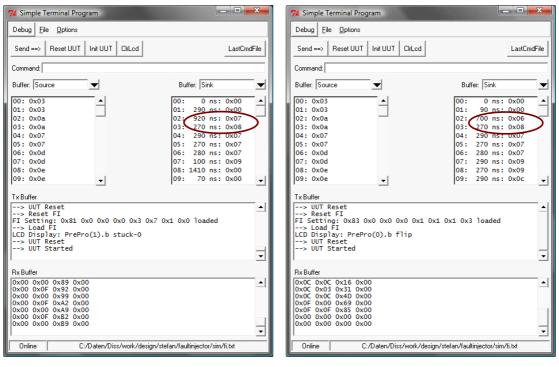

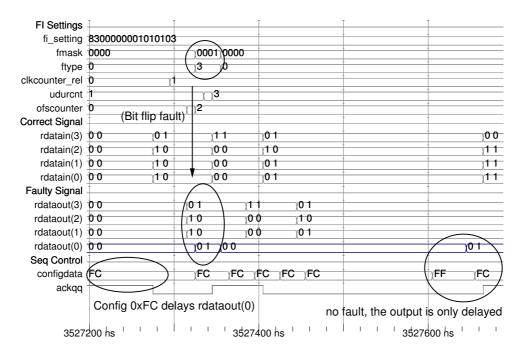

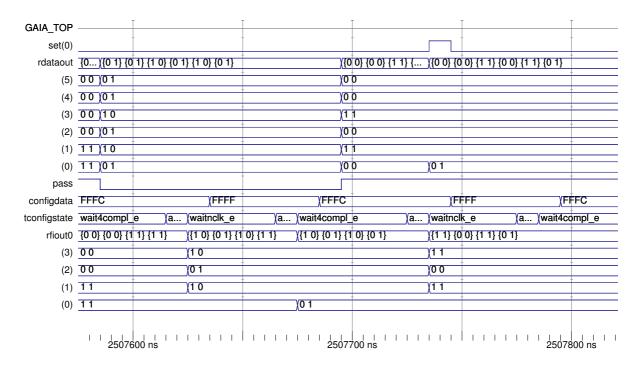

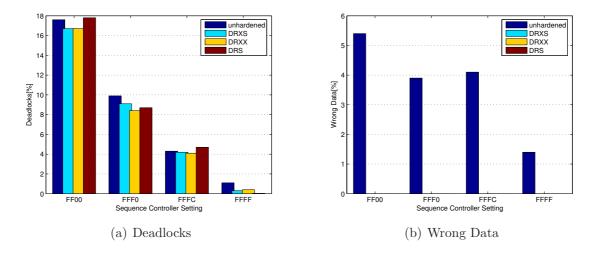

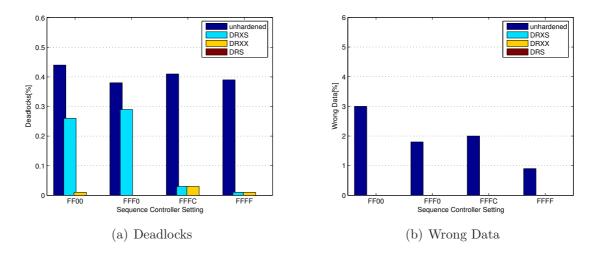

|          |                | 6.4.4   | Emulation of the GAIA Algorithm                             |

|          | 6.5            |         | ary                                                         |

| 7  | Con   | clusion 18 | 83 |

|----|-------|------------|----|

|    | 7.1   | Summary    | 83 |

|    | 7.2   | Outlook    | 85 |

| Bi | bliog | raphy 18   | 87 |

# Introduction

This chapter gives an overview of the motivation behind this thesis. It briefly describes the main objectives and the contribution that is made.

#### 1.1 Motivation

Today's modern integrated circuits are still facing a continuing down-scaling process. The smaller feature size has lead to several improvement trends as shown in Table 1.1. The most remarkable trends are higher integration, faster operation and decreasing cost per function, which has led to significant improvements microelectronic products [1]. At the same time, the supply voltage is reduced as well leading to a higher power efficiency.

| TREND             | EXAMPLE                           |

|-------------------|-----------------------------------|

| Integration Level | Components/chip, Moore's Law      |

| Cost              | Cost per function                 |

| Speed             | Microprocessor throughput         |

| Power             | Laptop or cell phone battery life |

| Compactness       | Small and light-weight products   |

| Functionality     | Nonvolatile memory, imager        |

Table 1.1: Improvement Trends for ICs Enabled by Feature Scaling from [1]

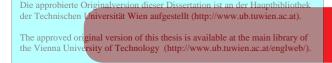

That higher integration and improved performance is paid by an increased fault sensitivity as the amount of electric charge that defines a logical value in a digital circuit (critical charge) is becoming smaller. Fig. 1.1(a) depicts the critical charge versus the circuit technology. As the circuit's environment is not affected by that trend, it becomes more easy to disturb the logic state of a circuit node [2], [3] and soft errors mainly caused by high-energy cosmic neutrons are becoming a major source of errors in modern integrated circuits [4].

The effect of the reduced critical charge is an increased soft error rate as depicted in Fig. 1.1(b). Thereby the soft error rate for SRAM cells did not change significantly. The

reason for this is the compensation of the smaller critical charge by a disproportionate reduction in the cell area and an improvement in technology. However, for logic elements and latches, the soft error rate grows as predicted by the critical charge reduction.

(a) Critical charge for SRAM/latches/logic (b) Soft error rate / chip for SRAM/latches/logic

Figure 1.1: Critical charge and soft error trends versus technology [5]

Although the analysis in [5] has been performed already in 2002, the results are confirmed by recent research [6]: The soft errors in logic cells start to overtake the soft errors in SRAM cells and will become the dominating source of errors in future technologies. Table 1.2 compares the SEU (single event upset, soft error) rates in microprocessors that are designed in different technologies. The failures in time (FIT) per bit are declining, while the higher integration density lead to an overall increase in the SEU rate for the complete device. Even worse, it was shown that shrinking feature sizes lead to an increase of multi-cell upsets, i.e. a single particle incident will disturb several logic cells. These multiple upsets primarily affect memory cells, thus more complex error correcting codes are required to minimize the system level effects [6].

| Tech.<br>(nm) | Relative SEU rate<br>in FITs/kbit | Approx. Mbits per<br>microprocessor | Relative uncorrected<br>SEU rate per micro- |

|---------------|-----------------------------------|-------------------------------------|---------------------------------------------|

|               |                                   |                                     | processor (kFIT)                            |

| 250           | 3.2                               | 1.52                                | 4.95                                        |

| 180           | 3.0                               | 1.52                                | 4.29                                        |

| 130           | 2.4                               | 3.28                                | 10.24                                       |

| 90            | 1.0                               | 33.6                                | 33.60                                       |

| 65            | 0.7                               | 44.3                                | 30.46                                       |

Table 1.2: Raw SEU Rate per Microprocessor from [6]

Especially for high reliability (hi-rel) applications, an improvement in circuit performance that is accompanied with a reduction in dependability is not acceptable. Moreover, radiation effects that have been known for a long time in fields such as space engineering or radioactive applications for science, medicine or military have now found their way into commercial products. Soft errors, induced by e.g. irradiation with high energetic particles are becoming a concern for terrestrial applications [7], [8], [9], [10]. Aside these reliability issues, modern highly integrated microcircuits make it harder to distribute a low skew central clock signal across a chip and to maintain the necessary timing margins for synchronous technology. Providing a reliable communication between particular on-chip modules is getting more challenging as well [1].

Within this field, asynchronous circuits are becoming more popular [11]. They show some properties that make them superior to their synchronous counterparts. The clock distribution problem is eliminated, the obtained performance is more an average case than a worst case as every single module runs at its own maximum speed and no timing margins have to be considered. Further the asynchronous modules are easy to compose as they are based on a local handshake that autonomously adapts to the slowest device. Transitions take place only when they are needed, which reduces electromagnetic emission and susceptibility as well as dynamic power consumption. Asynchronous designs also offer an improved fault tolerance, not only to internal process variations but also to external faults.

On the other hand, asynchronous circuits have a clear disadvantage in terms of area compared to equivalent synchronous circuits. The design market thinks and acts synchronous. Tools for developing asynchronous circuits are in the minority compared to synchronous tools and often limited to university usage. Although synchronous tools can be utilized, their outcome and performance is not as satisfactory.

While there is a lot of research done on fault tolerance in synchronous systems, less attention has been paid to asynchronous circuits. Well established error detection techniques applied to synchronous circuits cannot be directly applied to asynchronous designs. Further, the different classifications of asynchronous circuits [12] – bounded delay (Huffman), speed independent, (quasi) delay-insensitive circuits – entail different methods of error detection.

#### 1.2 Scope

The main objective of this work is the investigation of transient fault effects in asynchronous *Quasi Delay-Insensitive* (QDI) circuits [12] and the development of hardening strategies to mitigate these faults. Thereby both the fault effects and their countermeasures are applied at the register level, which regards general combinational logic and registers as primitive items. That level of abstraction provides more simplicity as well as yields general, technology independent results compared to more fine grained levels such as the gate or transistor level. Similarly, as the mitigation of faults is also applied to the register level, higher level hardening methods such as checksums or parity protection are not applicable. Therefore the developed mitigation strategies will be system independent as well.

Although this work provides a general treatment of QDI circuits, a focus is set on a special member of the QDI family, namely *Four-State Logic* (FSL) [13], which describes one possible implementation of the *Level Encoded Dual-Rail* (LEDR) [14] protocol. The robustness of an asynchronous FSL processor was investigated in [15] and showed a high inherent robustness to transient faults, which is based on the delay-insensitive encoding of QDI logic. Basically, the fault mitigating feature of QDI logic relies on its inherent

tendency to block manipulated data: A fault rather stops a QDI circuit instead of producing any functional errors. If the circuit is stopped forever, it is said to be deadlocked. It depends on higher level requirements, whether such a deadlock is preferable not.

While a deadlock can be assumed for nearly all kinds of permanent faults, that is not necessarily true for transient faults and it has been shown that transient faults have become the major source of errors [16]. Traditional methods applied to synchronous circuits cannot be directly mapped to asynchronous circuits [17], [18]. There is no global clock that produces a new set of valid data each clock edge that can be used for e.g. comparison with a redundant data set. The absence of a clock also prevents synchronous fault injection test methods to be applied to asynchronous designs [19]. This thesis aims to improve both, simulation and hardware based transient fault injection in QDI logic. Thereby the characteristics of QDI circuits are taken into account, especially when using commercial design tools that have been developed for synchronous circuits.

#### **1.3** Contribution

Within this thesis a comprehensive investigation of transient fault effects in QDI logic is performed:

**Trace Based Fault Model** – A new fault model is developed to describe the effect of transient faults in QDI logic and to derive proper hardening techniques. Contrary to existing models that are based on transition [20] or token level [21], this model is based on trace theory [22]. The trace based approach is well suited for the description of events in asynchronous circuits and it combines the benefits of transition (high level of details) and token based methods (simplicity).

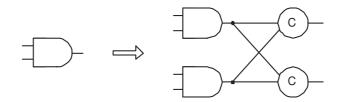

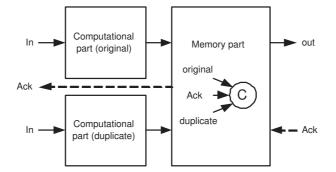

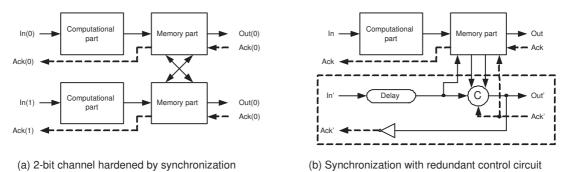

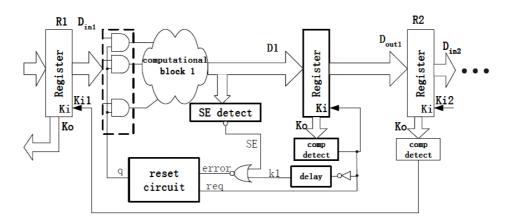

**Duplication and Rail Cross-coupling** – Various methods are examined to mitigate transient faults in asynchronous QDI logic. A new method called *duplication and rail cross-coupling* was derived. It is based on duplication but comes along with a minimum amount of supplemental hardware by modifying the signal trace during a transient fault. Thereby the hardware overhead is minimized, which is one of the main drawbacks of asynchronous circuits. The properties, benefits and drawbacks of this new method are discussed and compared to established hardening techniques such as duplication and double checking [18].

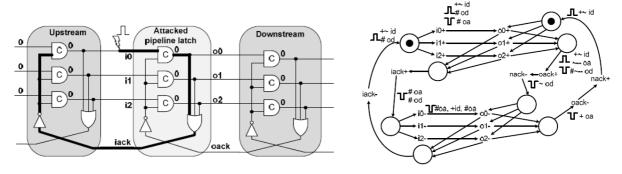

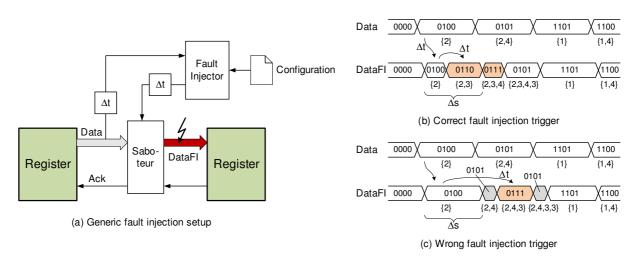

**Consideration of latching effects in QDI simulation** – A widely used technique to evaluate different fault effects, hardening methods or the robustness of a system is fault simulation. One key difference between synchronous and asynchronous circuits is the transparent phase of a storage element. In flip-flop based, synchronous logic that phase is very short, limited by the rise time of the clock and the internal delays. In asynchronous circuits a storage element may be transparent for a considerable amount of time, leading to different effects. A special *fault injection tool* for VHDL simulation was developed that considers these peculiarities. It allows to simulate both soft errors and transient errors without modifying the underlying circuit architecture and may be used for all kind of synchronous and asynchronous circuits if transient faults shall be examined. The benefit of this tool over existing methods is its simplicity and a minimum computation effort. **QDI fault injection considering controlled traces** – Contrary to simulation, emulation offers improved performance as the circuit's operation takes place in real hardware and does not need to be simulated. A common practice is to add invasive elements, or saboteurs, that provoke faults. The problem with asynchronous circuits opposed to synchronous circuits is to achieve a full fault coverage. In a synchronous design the clock is the only event that generates a new state. In an asynchronous design each signal event triggers a new state, which requires not only to control the logic value of a fault and the moment of its occurrence but also to control the sequence when events take place – the trace. A new *hardware fault injector* has been designed that allows to control that trace. Thereby, a deterministic and reproducible fault investigation of QDI circuits in hardware is obtained, which takes care of the state coverage problem that is commonly disregarded in other tools.

#### 1.4 Outline and Methodology

The thesis is structured in different chapters, which are – as far as possible – selfstanding parts providing the interested reader a more efficient way to study the subjects he is interested in without working through the whole document.

Chapter 2 gives a brief introduction in asynchronous logic especially in QDI logic. It comprises the idea behind the asynchronous design style and introduces the peculiarities it is accompanied by. A general overview of the different faults and fault models in QDI logic is provided. Fault tolerance and its application in QDI logic is described.

Chapter 3 presents an overview of the different fault models that are suited for QDI logic. It describes the *trace based model* that has been developed during this thesis and applies that model to different circuit parts, especially interconnections as well as combinational and sequential circuits. The chapter derives the necessary rules and boundary conditions of the trace based model, which are then applied in the following chapters to determine the mitigation of transient faults.

Chapter 4 handles the general aspects of soft errors and what mitigation strategies may be applied. It introduces the concept of *duplication and rail cross-coupling* and investigates the properties of this method applying the trace based fault model that has been developed in Chapter 3. The duplicated and rail cross-coupled method aims to improve the logical masking capability of a system. Several implementations of this concept are compared with respect to fault tolerance but also in terms of hardware overhead.

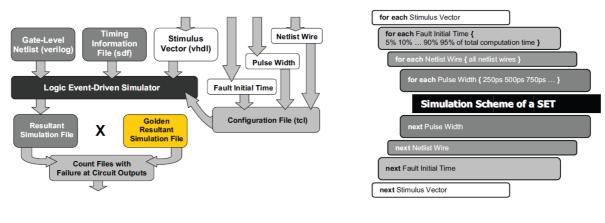

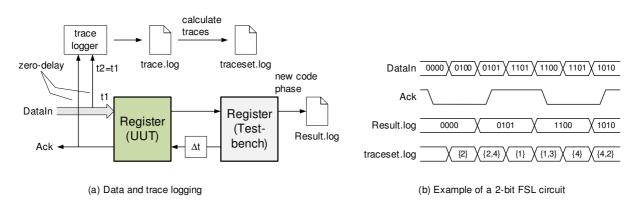

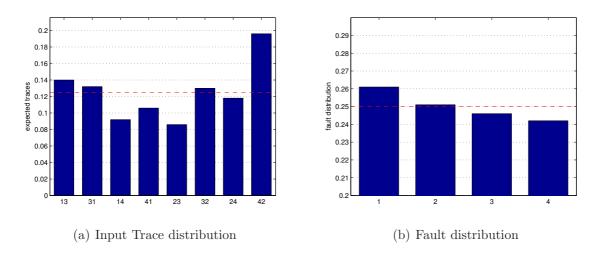

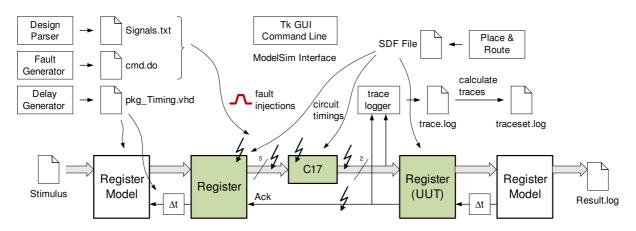

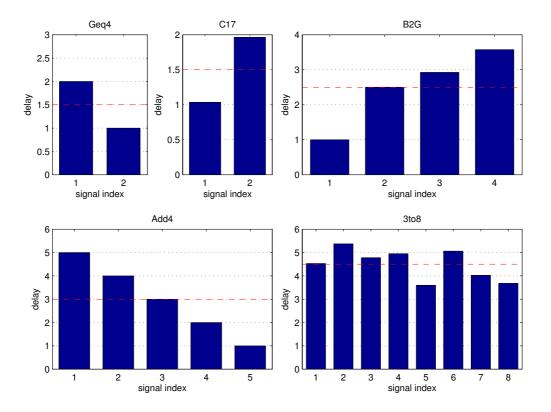

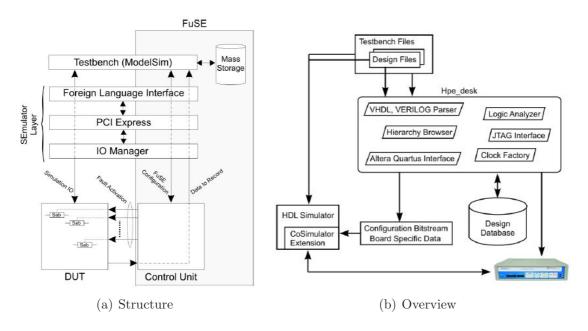

Chapter 5 describes the simulation of QDI circuits that are subjected to transient faults. Thereby the characteristics of QDI logic is highlighted, which lead to the design of the FOur STate ERror injection tool (FOSTER). Originally, that tool was developed to simulate transient faults in Four State Logic (FSL), which is a special design style of QDI logic. In principle it can be also mapped to other common styles such as 4-phase dual-rail. This chapter investigates the theoretically derived results from the previous chapters by means of simulation based experiments using typical building blocks of digital systems.

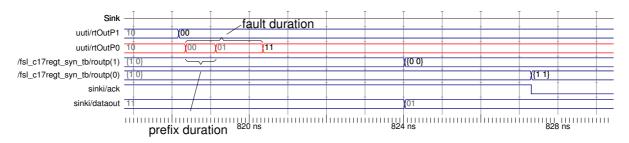

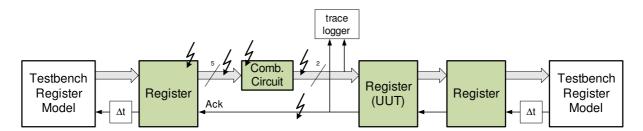

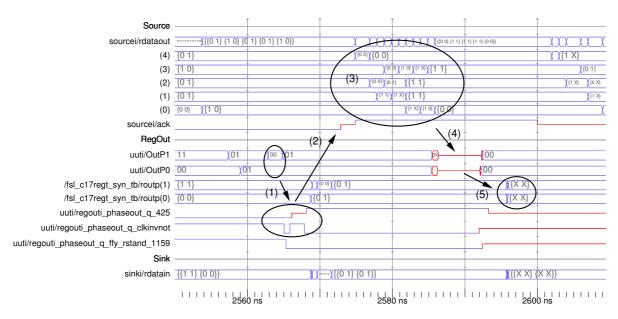

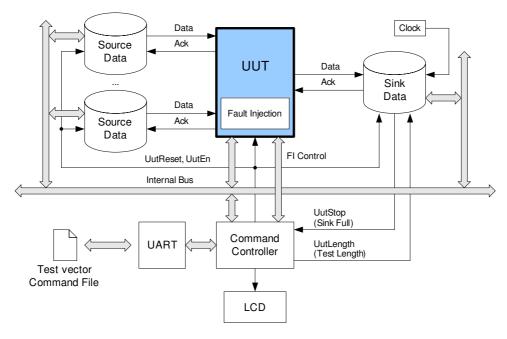

Chapter 6 deals with the fault emulation of QDI circuits, focusing on an optimum error coverage and reproducibility of the fault injection. Thereby the trace based model is applied to real hardware by means of the **S**ynthesizable **T**est **E**nvironment **F**or Asynchronous Networks (STEFAN). That tool allows to test QDI circuits in a deterministic manner by presenting a new type of saboteur that takes over the control over a circuit's trace. The new fault injection method is applied to a real signal processing application. Thereby the fault tolerance of the different duplication and rail cross-coupling architectures is investigated.

Chapter 7 draws a conclusion and gives an outlook to remaining fields of investigation on this subject.

# 2 Background

This chapter provides necessary background for this thesis. First an introduction to asynchronous logic, especially into *Quasi Delay-Insensitive* (QDI) circuits is given. The different types of faults in asynchronous logic are presented and an overview of the state of the art in fault tolerant QDI circuits is reviewed.

#### 2.1 Asynchronous Logic

#### 2.1.1 General

Digital logic deals with binary signals. An analog signal, typically a voltage, is assigned to discrete boolean values TRUE/FALSE or 0/1. Fluctuations in the analog nature of information are not relevant as long as the boolean value remains unchanged. Another simplification in the design of digital circuits is the assumption of a common, discrete time – defined by the clock signal [23]. A discrete time resolves many problems, since the actual behavior of a signal between two consecutive clock edges is of no importance. Properties such as different propagation delays (skew), glitches or hazards do not alter the logic function as long as all transients have settled to a stable state before the next clock edge occurs. That fundamental constraint manifests in the setup and hold time known from synchronous flip-flops. If these timings are violated a correct operation is not guaranteed and metastability may occur. As long as the circuit operates solely in a synchronous domain, which means that no asynchronous signals have to be processed, the setup and hold problem can be solved by simply reducing the clock frequency. Thereby the transients have a longer time to settle. An asynchronous signal does not follow a discrete time, i.e. events on such a signal may occur at any time and are not related to the clock signal.

Asynchronous circuits neither assume a discrete time nor do they have a common clock signal. The communication between the sender and the receiver of data is based on a local handshake between these two instead of a global clocking scheme. Thereby the actual speed of the circuit depends on the actual propagation delays of the particular circuit elements and not on an externally imposed clock frequency. Any communication actually takes place when it is needed and not at pre-defined time intervals such as clock edges. This fundamental principle generally results in considerable benefits compared to synchronous circuits [23], [11], [12], [24]:

- Less dynamic power Asynchronous circuits only perform an action when such an event is requested by the local handshake and not at every clock edge. Fewer switching reduces the dynamic power consumption.

- Average case performance In synchronous circuits, the clock frequency must be selected according to the worst case delay for a correct operation. Asynchronous circuits, especially those which are insensitive to delays show an average case performance as they regulate their operational speed inherently.

- Adaptivity Asynchronous circuits are not affected by environmental variations that change the operating speed of the circuit. They simply adapt their local handshake protocol to the new conditions.

- *Modularity* The local handshaking as well as the reduced impact of actual delays makes asynchronous circuit highly modular. Components may be simply replaced without considering synchronization issues or making worst case timing analyzes.

- No clock skew problem The distribution of a low skew, high-speed clock signal is not needed any more.

- *Reduced electromagnetic emission* Since there is no dominant regular switching operation at every clock edge but rather a distributed, smooth activity across the circuit the electromagnetic emissions are reduced.

- Security Less emissions of asynchronous circuits make them more rugged to security attacks. It is harder to both scan as well as disturb a system that operates at rather arbitrary time instants.

- *Robustness* The reduced susceptibility to delays, environmental impacts and the lack of a common clock signal that affects all parts of a design makes asynchronous circuits inherently very robust.

- *Reliability* The clock signal constitutes a single point failure in a synchronous circuit. Asynchronous circuits eliminate that source of errors, since no clock is needed. As the circuit operation is more evenly distributed across a chip, the wear-out of specific circuit parts is reduced, which improves the life time of a component.

Of course, all the above items are more general statements that have to be treated on case-by-case basis. Detailed information about asynchronous logic can be found in various books and articles such as [25], [26], [27], [23], [12], [24], [28] [29], [30] to name a few.

However, asynchronous circuits also face considerable drawbacks. In general, they are not as efficient as an equivalent synchronous circuit especially in terms of area overhead. Although they consume less dynamic power and offer average case performance, their increased area and complex design may annul these benefits when overall power and performance is compared. The design methodology is more complex and asynchronous circuits are neither easy to test nor easy to develop due to the lack of commercially available CAD tools. For prototyping tasks, these drawbacks become much more evident as typical platforms such as FPGAs are optimized for synchronous designs. Although a synchronous FPGA can be used for asynchronous designs they resulting design may even have a worse efficiency than predicted, which makes a fair comparison asynchronous versus synchronous even harder.

This thesis focuses on the investigation of transient fault effects and their mitigation in asynchronous circuits. The deficiencies such as area overhead are of secondary concern, although they are briefly tackled.

#### 2.1.2 Classification

Asynchronous logic is not a new principle and lasts back to the 1950s. Pioneers in that field, such as D. A. Huffman [31, 32] and D. E. Muller [33], derived different methods of digital asynchronous circuit design. There exist several possibilities to classify asynchronous circuits. One of the most obvious methods is the delay model the system adheres to. In principle, there are two disjunctive models:

- 1. The *Bounded Delay* model places certain constraints on the propagation delays of gates and wires in a circuit.

- 2. The *Unbounded Delay* model allows arbitrary delays for at least some parts of a circuit.

Within the unbounded delay model, two main families can be distinguished: Speed Independent (SI) and Delay-Insensitive (DI) circuits. SI circuits assume positive, unknown delays in gates but zero delays on wires. DI circuits do not apply any delay restrictions, neither in gates nor on wires. Unfortunately, the class of DI circuits is limited to circuits that only consist of inverters and so called Muller C-gates [34]. A less restrictive sub-class of DI circuits are *Quasi Delay-Insensitive* (QDI) circuits, which allow unbounded delays in all elements except in *isochronic forks*. Such forks assume the difference in the delay of each branch is negligible, i.e. a transition that starts at the root of the fork will arrive at the end of each branch at the same time. With that limitation the class of QDI circuits becomes bigger and thus more practicable than pure DI logic. If all forks in a QDI circuit are required to be isochronic, the circuit essentially becomes a SI circuit. In this case, the wire delays are transferred into their associated gates, as the SI paradigm allows arbitrary gate delays. In practical QDI circuits, such isochronic forks are applied to the gate level implementation of basic building blocks (gates, registers), where the matched delays are more easy to control, while at a higher level the connection between these blocks is truly DI |12|.

Synchronous circuits also adhere to the bounded delay model. The synchronous paradigm assumes that all transient states have settled to a steady state by the next clock edge. Asynchronous circuits that follow the bounded delay model require certain timing assumptions and operation modes. They are also referred to as *Self-Timed* [23].

#### 2.1.3 Operating Modes

The classification of asynchronous circuits according to their delay model does not define the interaction with their environment. There are two basic operating modes [24]:

- 1. Fundamental Mode

- 2. Input-Output Mode

The fundamental mode was developed by D. A. Huffman [31, 32]. This mode requires that the next input must not be applied until the circuit has settled to stable state. Thus an upper limit must be placed on the delays of the circuit as the internal states of the circuit are not visible to the environment. Fundamental mode circuits always adhere to the bounded delay model. The classic fundamental mode only allows one single input to be changed at a time. The *burst mode* [35] extends that single-input limitation and allows several inputs to be changed at once. The environment still has to wait until the circuit has stabilized before the next input burst may be applied. The completion of an operation in a fundamental mode circuit cannot be concluded by solely looking at the outputs as these may change due to transient, intermediate states as well.

In the *input-output mode* developed by D. E. Muller [33], the environment may apply the next input as soon as an output change has been observed. So there exists a causal relation between input and output transitions. The internal signals as well as internal states of the circuit are not regarded, so each output transition must be a valid one. No transient or intermediate output transitions are allowed. Therefore a circuit that operates in the input-output mode must be at least speed-independent.

#### 2.1.4 Handshake Protocols

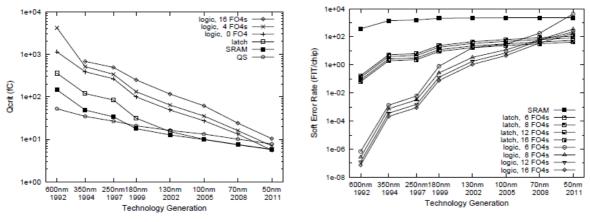

In a synchronous circuit, the clock signal determines when data is valid. So new data will be sampled at the clock edge only. Asynchronous circuits have no clock that defines the validity of data and triggers the capture process. Thus some kind of handshake protocol between the circuit and its environment is needed to decide when data is valid and may be captured. In general, two handshake events are required as shown by Fig. 2.1:

- 1. A request event, which signals the receiver that new data is available.

- 2. An *acknowledge* event, which signals the source that data has been captured.

In the nominal case, i.e. without any faults, these two events will alternate. A request is followed by an acknowledge, which will be followed again by a request and so on. In synchronous circuits, the clock serves as global request event that triggers the storage of new data. An acknowledge signal is not needed as the synchronous principle requires that data is processed by the next clock event. In asynchronous circuits, there exist several handshake implementations.

In bounded delay circuits, such as Huffman state machines operating in the fundamental mode, the handshake is implicitly provided by the delay of the environment

Figure 2.1: Principle of handshake

before consecutive data is applied. Therefore, fundamental mode circuits operate similar to synchronous circuits. Other types of bounded delay circuits and especially circuits that operate in the input-output mode, require dedicated handshake signals.

In *bundled data* circuits, the handshake information is explicitly transmitted together with the data. The handshake signals comprise one request signal and one acknowledge signal for N data signals. Thereby the request signal has to be delayed to guarantee that data is valid when the request event is received. Therefore, bundled data circuits follow a bounded delay model and require a positive timing margin between the propagation delay on the request line and the worst case propagation delay on the data lines. For the acknowledge signal, no such timing constraint is required. Other asynchronous design techniques, such as SI and (Q)DI circuits do not require a dedicated request line. In these circuits, the validity of data is implicitly determined by the data encoding.

The request and handshake events may be level or edge encoded. The type of encoding defines whether the event is defined by the logic state (*level signalling*) of the handshake lines or by the change of that state (*transition signalling*) [36]. In general, level signalling results in simpler circuits as transition signalling requires the circuit to react on signal events rather than on signal states.

Within the handshaking, either the sender or the receiver may initiate the communication. In general, the sender performs this task by means of providing new data. This standard configuration is known as *push channel*. On the other hand, the receiver may also control the handshaking by asking for new data, which is referred to as *pull channel*.

The handshake protocol can be classified by the number of operation phases it consumes. The *four phase protocol* (4-phase) uses a simple return-to-zero encoding for the handshake. Although this protocol does not convey any information in the return to zero phases, the 4-phase protocol allows to design quite simple circuits and is therefore the most popular one. Second, the computation time in an asynchronous circuit may be much longer than the transmission time, so the return to zero phases do not have a large weight in the overall budget and justify the more simple circuit design. The *two phase protocol* (2-phase) is a good choice when this is not the case. It uses a non return-to-zero encoding. That protocol does not waste the time of the reset phases, however, a 2-phase circuit design is generally more complex than a 4-phase circuit. Some asynchronous designs utilize the benefit of both protocols by applying the 4-phase protocol to the computational part of the circuit and the 2-phase protocol to the interconnection parts [37], [38]. Another improvement of data throughput for asynchronous handshake protocols is *Level Encoded Transition Signalling* (LETS), which combines a return-to-zero encoding with 1-of-N codes [39]. An example for a practical 4-phase realization that has been placed commercially on the market in the 90's is *Null Convention Logic* (NCL) [40].

The classification of an asynchronous circuit does not define its physical implementation. For instance, a DI circuit may use a 4-phase or a 2-phase protocol. Additionally, the properties of bounded and unbounded delay can be combined as in the *Micropipeline* [41], which uses a DI control circuit for the handshaking but bounded-delay data path.

#### 2.1.5 Quasi Delay-Insensitive Logic

As already highlighted, real DI circuits do not comprise a lot of practical applications. Thus QDI logic is applied instead, provided the limitation of isochronic forks is acceptable – which is often the case considering practical designs. Due to the unbounded delay the sender does not know when the receiver has captured the requested data. Therefore the receiver must explicitly inform the sender about such an event by means of an acknowledge signal. The sender is not allowed to transmit the next data until it has received an acknowledge.

On the other hand, the receiver must only process valid data. Bundled data circuits solve that problem by attaching a dedicated request signal to the data signals. That request signal must always be late compared to the data, which requires a bounded delay model. In case of arbitrary, unbounded delays a temporal order between any signals is not guaranteed anymore. Therefore, data must be transmitted using a *delay-insensitive* or *unordered code*. Thus the receiver is able to detect new, valid data by simply evaluating its code. There is a variety of delay-insensitive codes [42]. The combination of a delay-insensitive code and a handshake protocol allows different styles.

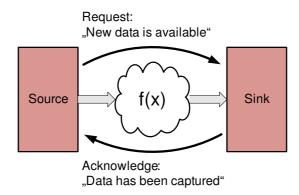

The most widely applied handshake scheme is the 4-phase protocol, which is shown in Fig. 2.2(a). Actually only two phases carry valid data and acknowledge events while the other two phases are used to reset the data and the acknowledge signal to their initial value. The drawback of this protocol is invalid data (I) between the valid code words (V). The advantage is a rather simple circuit implementation. More efficient is *Level Encoded Dual-Rail Signalling* (LEDR) [14] that uses a 2-phase protocol. Data is transmitted in two alternating *phases*,  $\varphi 0$  and  $\varphi 1$ , as depicted by Fig. 2.2(b). No invalid codes are needed, however, the circuit implementation is in general more complex.

Figure 2.2: Data sequence using a 4-phase and a 2-phase protocol

Table 2.1 shows two possible implementations of QDI logic. Both map a boolean variable  $x \in \{0, 1\}$  to a dual-rail variable y comprising the two rails a and  $b: x \mapsto y_a y_b$  with  $y_a, y_b \in \{0, 1\}$ . The most widely applied style is a 1-of-2 one hot or simple dual-rail code together with a 4-phase protocol. In 4-phase dual-rail, data alternates between the valid code set  $V = \{01, 10\}$  and the invalid code  $I = \{00\}$ . The remaining code  $\{11\}$  is not used, which means only three of the four possible code states are used.

|           | 2-ph. dual-rail<br>(four-state coding) |                       | 4-ph. dual-rail<br>(three-state coding) |                |

|-----------|----------------------------------------|-----------------------|-----------------------------------------|----------------|

| $y_a y_b$ | x                                      | code set              | x                                       | code set       |

| 0 0       | 0                                      | arphi 0               | -                                       | Ι              |

| 01        | 0                                      | $\varphi 1$           | 0                                       | V              |

| 1 0       | 1                                      | $\varphi 1$           | 1                                       | $\overline{V}$ |

| 11        | 1                                      | $\overline{\varphi}0$ | -                                       | Not used       |

Table 2.1: Truth table of 2- and 4-phase dual-rail logic

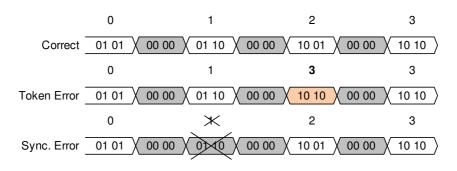

The invalid code in a 4-phase dual-rail protocol does not convey any information and is purely used to separate consecutive code words or *tokens*:

**Definition 2.1.1.** A token describes any legal data in an asynchronous system that can be interpreted.

To be legal, data must be *consistent* as well. During the transition between the code phases, the encoding reaches intermediate states that are *inconsistent*. Both terms are detailed later on. In addition to illegal codes, such as '11' in 4-phase dual-rail, there is a second reason for illegal data. Once a token has been consumed, the data held by the predecessor becomes obsolete. In this case the token in the predecessor is transformed into a *bubble*.

**Definition 2.1.2.** A token is transformed into a bubble after it has been consumed, i.e. acknowledged, by the successor.

Any QDI circuit may only receive a token if it holds a bubble. During the operation, tokens travel from the source to the receiver, while at the same time bubbles travel from the receiver to the source. This token – bubble game describes the data flow in an asynchronous circuit. For more details refer to [12].

Within this thesis, the term *illegal* means any code that does not comply with the circuit's protocol, while the term *inconsistent* means that the code word cannot be evaluated. In general, a QDI circuit shall be designed such that it will never process inconsistent data. Regarding illegal codes, it depends on the circuit implementation whether it will process such data or not. For example, the illegal code '11' in 4-phase dual-rail may be used for error detection [43], [17], but it can as well be simply ignored to save area.

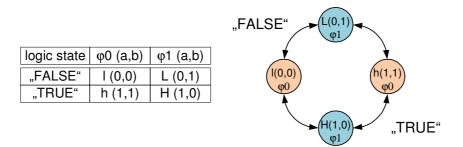

In LEDR a more efficient dual-rail encoding together with a 2-phase protocol is used. As this style uses all four possible states of a dual-rail code it is also called *four*state coding compared to the previously described *three-state coding* [13]. One way to implement the LEDR protocol is Four State Logic (FSL) or 2-phase dual-rail. In FSL, data alternates between the two codes sets  $\varphi 0 = \{00, 11\}$  and  $\varphi 1 = \{01, 10\}$  as shown in Table 2.1 and Fig. 2.3. Each phase uniquely defines the boolean states FALSE and TRUE. Phase  $\varphi 0$  is also called the even phase and  $\varphi 1$  is called the odd phase, which stems from the modulo-2 sum of the two rails in the code. Contrary to the 4-phase protocol, both FSL code sets carry valid information. The benefit of the 2-phase protocol is higher speed [44], thereby LEDR allows to build circuits with more acceptable complexity compared to classical transition signalling [36]. Within this thesis the terminology FSL refers to the design style of a LEDR encoded QDI circuit.

Figure 2.3: FSL encoding and state transitions

The most promising application of LEDR lies in the realization of asynchronous interconnections. For example, a single buffer implemented in LEDR has 187% higher throughput but consumes only 62% of the energy compared to an equivalent 4-phase dual-rail buffer [38]. In [45] a very fast asynchronous shift register designed for high speed bit serial on-chip interconnection channels is presented. The interconnection channel was implemented using LEDR signalling. Simulations showed a speed of 67 Gbps in 65 nm CMOS and at the same time an immunity to in-die process variations in the order of  $10\sigma$ , with  $\sigma$  being the standard process variation.

In Fig. 2.2, the boolean sequence  $x = \{..., 0, 1, 1, 0, ...\}$  has been transferred to both common 3-state QDI logic using a 4-phase protocol and to FSL using a 2-phase protocol. From that example, two fundamental properties can be derived, which have to be satisfied by all types of QDI circuits:

- (I) Data is always processed in alternating code phases, which is called the *alternation property*.

- (II) Any QDI function z = f(Y) with  $Y = \langle y_1, ..., y_n \rangle$  will produce a *consistent* output z if and only if its input Y is also *consistent*. Otherwise the current output is preserved, which is called the (strong) *completeness property*.

Property (I) allows to distinguish consecutive data, while property (II) prevents the mixture of code phases. The concept of consistency is an important property that distinguishes QDI from common synchronous logic. To formally describe consistency, the *code set*  $\Phi$  is introduced:

**Definition 2.1.3.** The code set  $\Phi$  holds all legal codes that can be processed by a QDI function.

Similarly, the code set can be split into subsets that only hold legal codes of their own code phase. For dual-rail and 1-of-N codes there are two subsets  $\Phi_0$  and  $\Phi_1$ :

**Definition 2.1.4.** The code subset  $\Phi_p \subset \Phi$  holds all legal codes of the code phase p. For dual-rail and 1-of-N codes one can state  $\Phi_0, \Phi_1 \subset \Phi$  and for complete codes such as FSL  $\Phi_0 \cup \Phi_1 = \Phi$ , i.e. the complete code set is covered by two subsets. Further the code sets are disjoint, i.e.  $\Phi_0 \cap \Phi_1 = \emptyset$ .

The code phase of a signal vector  $Y = \langle y_1, y_2, ..., y_n \rangle$  can be calculated by the consistency function  $\varphi(Y)$ :

$$\begin{aligned} \varphi(Y) &= 0 &\Leftrightarrow \quad \forall y_i \in Y : y_i \in \Phi_0 \\ \varphi(Y) &= 1 &\Leftrightarrow \quad \forall y_i \in Y : y_i \in \Phi_1 \\ \varphi(Y) &= \mathbf{X} &\Leftrightarrow \quad \exists y_k, y_l \in Y | y_k \in \Phi_0 \land y_l \in \Phi_1 \end{aligned} \tag{2.1}$$

For a one-bit dual-rail signal y the code phase can be calculated with a simple XOR function of the two rails:  $\varphi(y) = y_a \oplus y_b$ . For an (n > 1)-bit signal vector the code phase is logical 1/0 if and only if the code phase of each bit in the vector is logical 1/0. Otherwise the code phase is not defined, which is expressed by X. For a completion detection circuit that is used in all types of QDI logic to determine the current code phase, no unknown state is defined. Thus if a completion detector cannot evaluate its output because at least two bits are not in the same code phase, the last known output is maintained.

In LEDR, all possible members of the code set are used, while 4-phase dual-rail does not have this property. Here, the code '11' is not used. Depending on the actual implementation, '11' may be a legal code or not. In the first case,  $\{11\} \in \Phi$  and the code is processable. In the latter case,  $\{11\} \notin \Phi$  and the circuit will not be able to evaluate the next code phase. So for a QDI function to process a code, it is mandatory that the code is legal and consistent. This requirement applies to all bits of the code word.

**Definition 2.1.5.** A code word  $Y = \langle y_1 ... y_n \rangle$  is called *consistent* if all bits  $y_i$  are member of the code set and have the same code phase:

$\{\forall y_k, y_l \in Y : k, l = 1...n : y_k, y_l \in \Phi \land \nexists y_k, y_l | \varphi(y_k) \neq \varphi(y_l) \}.$

The definition of consistency does not define whether the data is valid or invalid. In QDI circuits, only valid data conveys information. It is mandatory that valid data must be both legal and consistent. However, the same applies for invalid data, which is used as a spacer in e.g. 4-phase dual-rail or 1-of-N circuits. For these codes we can derive another property that is helpful in the analysis of QDI logic.

**Definition 2.1.6.** The transition between consecutive dual-rail code words is performed by one single rail transition for each bit of the code, which is called the *single-event* property.

The above properties can be used describe the behavior of combinational and sequential QDI circuits. The completeness property implies that even combinational QDI circuits require state holding elements. Any inconsistent code must not be interpreted and lead to the completion of an output. The word completion is important in this context because the completeness property only applies to atomic QDI gates. An atomic gate performs any boolean function, no matter how many terms it is composed of, in one distinct computation step without requiring any intermediate results. If circuits composed of atomic gates adhere to the completeness property they are called *strongly indicating* [12]. In this case, the outputs will be only computed if all inputs have the same code phase. On the other hand, QDI combinational functions can also be designed *weakly indicating*, i.e. they will begin to produce valid outputs even if not all inputs are in the same code phase. Nevertheless, the complete output will not be created before the complete input is in the same phase. A simple example for a weakly indicating circuit is a ripple carry adder. The adder may start to produce an output on its lower bits provided the associated input bits are consistent. The complete result will only be generated if the complete input is consistent.

For sequential QDI circuits, that prerequisite for processing an input must be extended by the handshake protocol.

**Definition 2.1.7.** Any sequential FSL function will process its input if and only if (i) it is consistent, (ii) its code phase is inverse to the code phase of the currently stored token and (iii) the successor has already acknowledged the current token, which is called the *acknowledge property*.

Sequential gates or registers control the data flow in a QDI circuit, while combinational functions are transparent to the handshaking. The acknowledge property is one of the fundamental properties of any QDI design.

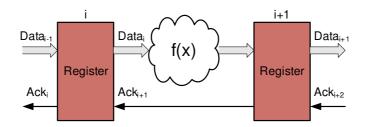

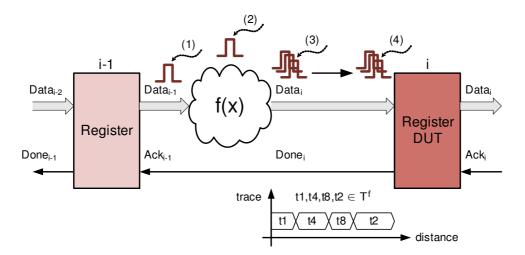

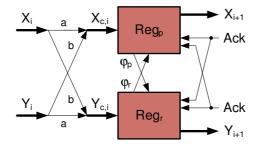

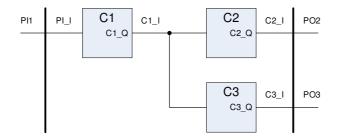

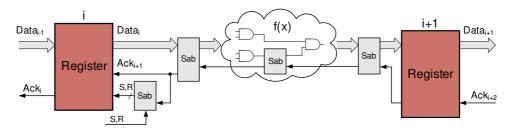

A typical implementation of a QDI circuit is the pipeline in Fig. 2.4. Data is passed from stage (i) to stage (i+1) via the (optional) combinational function f(x). The handshake is controlled by the registers, while the combinational functions are transparent to the handshake. More details, especially on the implementation of FSL in synchronous FPGAs are given in [46], [47].

Figure 2.4: Generic QDI pipeline

The physical implementation of QDI circuits is often combined with certain delay assumptions especially when regarding the basic building blocks such as plain registers or simple combinational gates. For the internal design of a practical QDI circuit nearly all forks are required to have matched delays. Additionally, the control signals of latches need to have a minimum pulse width for a correct operation [47], [37], [39]. If these timing constraints are fulfilled, the QDI function can be treated as atomic gate and any circuit that is composed of such functions will be delay-insensitive.

#### 2.2 Faults and Errors in QDI Circuits

#### 2.2.1 Definitions and terms

Some frequently used terms related to fault tolerance and error detection shall be clarified. The terms *failure*, *error* and *fault* are understood as established in the Working Group 10.4 (WG10.4) on Dependable Computing and Fault Tolerance of the International Federation For Information Processing (IFIP), summarized in [48]:

- A *failure* occurs when the delivered service deviates from the correct system function, the latter being what the system is aimed at.

- An *error* is that part of the system state which is liable to lead to a subsequent failure. An error is an observable discrepancy between the computed and the correct value due to the activation of a fault.

- A *fault* is the adjudged or hypothesized cause of an error.

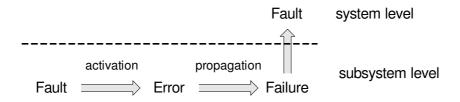

The chain in Fig. 2.5 describes the causal relationship between faults, errors and failures: A fault will generate an error provided the fault is activated and not dormant. The produced error will lead to a failure provided the error changes the intended behavior of the system. Basically, an error must propagate to the system boundaries to trigger a failure. This causal chain is continued on the next higher level. A failure in a subsystem may be regarded as fault on the higher system level.

Figure 2.5: Fault-Error-Failure Chain (adapted from [49])

When applying *error detection* the result of a function is checked to validate its correctness. The detection of errors can be conducted during the operation of a system, which is called *Concurrent Error Detection* (CED). On the other hand, when *preemptive error detection* is applied, the operation has to be stopped while the error detection takes place. In this thesis, whenever the term error detection is used, it is regarded as CED.

**Example 2.2.1:** Let's consider a simple serial protocol where a message of 8 bits is followed by one parity bit. Due to electromagnetic interference, a transient fault occurs and corrupts one data bit during the transmission. We assume the receiver will detect a parity error and ignore the message. Although the error has been identified, the system has failed if we consider the delivery of the message as an integral requirement of the system.

In contrast, *fault tolerance* means the system is able to provide the correct service despite the presence of faults. Fault tolerant systems require error detection to identify

the error plus some kind of recovery mechanism to correct the error and to re-establish the correct function or service.

**Example 2.2.2:** Memories of reliable computing systems are often equipped with an *Error Detection And Correction* (EDAC) code that stores the information together with check bits. Typically, an EDAC code not only allows to detect errors but also to correct them. The number of detectable and correctable errors must not necessarily be the same and varies with the EDAC code structure. In this example, the system is fault tolerant as the error will not propagate and become a failure.

The main purpose of error detection schemes is to improve a system's *dependability*, which defines the ability to deliver a service that can be justifiably trusted [49]. Dependability is seen as an integrative concept that includes attributes such as reliability, availability, safety and security.

#### 2.2.2 Fault Classification

Faults can be classified according to their persistence in *transient* and *permanent* faults. Sometimes the term *intermittent* fault is added to this collection, which is used to describe faults that occur repetitive but not continuously [50].

Transient faults may be introduced by three main radiation effects [9]: High-energy cosmic neutrons that interact with the silicon nuclei of semiconductor devices [51], lowenergy cosmic or thermal neutrons that interact with insulation layers [52] and alpha particle radiation due to package imperfections [53]. As today's integrated circuits generally use advanced processes with purified materials, high energetic cosmic neutrons are the dominating radiation effect [9]. Beside radiation, transient faults could also be provoked by *electromagnetic interference* (EMI) due to external sources or signal integrity problems such as ground bounce. Transient faults, especially those generated by particle strikes can be modeled by an electric charge injected to or removed from a circuit node that is represented by the boolean signal x. Thereby the charge is typically described by a double exponential current pulse [54]. Together with the total node capacitance, the injected current pulse modifies the electric voltage of the node. If the injected charge is high enough, the logic threshold of the circuit's technology may be exceeded in either direction and a positive  $x \uparrow$  or negative  $x \downarrow$  logic transition is generated. At the same time, the injected charge is restored by the node's driver, thus the disturbed signal will return to its initial state after the fault duration  $t_f$  depending on the amount of charge, the circuit technology and the node's driver strength. Eventually, the transient fault manifests itself either as a positive or negative digital pulse on the subjected signal x. Our main interest lies in this secondary effect – the corruption of the boolean value of x. The shape or the amplitude of the induced current are not important in the digital domain.

Cosmic rays or other charged particles will induce transients with a pulse width  $t_f$  of 100 to 200 ps. In modern microcircuits with feature sizes below 0.35  $\mu$ m, these transients are no longer attenuated within the gates and will propagate like normal digital signals [55]. At high energies, transient faults longer than 1 ns are predicted for 100 nm bulk CMOS at both proton-rich space environments but also for terrestrial neutron environments [56]. At 90 nm the nodal capacitance and the supply voltage are further

reduced, decreasing the critical charge that defines the logical value of a node to a few femto-coulomb. That increases the probability that a charged particle induces a logical disturbance of a few hundred picoseconds [57]. Faults that originate from e.g. glitches on the supply voltage or due to EMI can be described similarly although their underlying primary source is different.

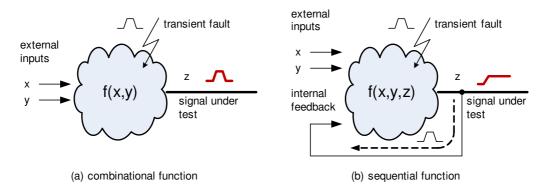

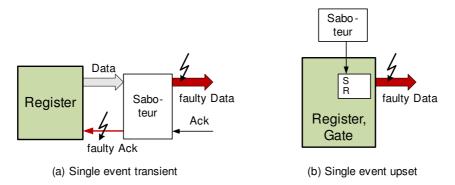

If a transient fault is injected into a circuit without feedback elements, it will only generate a logic pulse at the output of the circuit. Especially in space engineering, such pulses are called *Single Event Transients* (SET) [58]. In circuits with feedback elements, e.g. in a latch, a transient fault may be memorized and generate a permanent upset or error, which is also referred to as *Single Event Upset* (SEU) or simply as *soft error* [59].

Permanent faults are typically used to model physical defects, such as fabrication imperfections, malfunctions due to excessive voltage, current, power or wear out effects such as electro migration [60] or gate oxide break down [61]. Contrary to transient faults, a permanent fault cannot be restored or removed. This fact has to be observed, especially when permanent faults are compared with soft errors. For example, both a transient and a permanent fault may corrupt a memory cell. The transient fault may result in a soft error that can be restored by updating the affected memory with the correct value. If a permanent fault corrupts the memory cell, it cannot be restored, therefore the effect of a permanent fault is also called a *hard error*.

*Intermittent faults* are assumed to be a sub-class of transient faults, since they occur regularly but will disappear after some time. Thus they can be described the same way as transient faults.

Within this thesis, only the effects and mitigation of transient faults are treated.

#### 2.2.3 Logic Fault Models

At the logic level, faults can be modeled in different ways. One popular method is the *Single Stuck-At Fault* (SSAF) model [62], which disconnects a circuit node from its surrounding elements and forces the isolated node either to the power supply or to ground. The result is either a stuck-at-1 (s@1) or stuck-at-0 (s@0) fault. The SSAF model was originally defined for permanent faults, but can be applied to transient faults as well. The difference lies in the fault duration  $t_f$ . Although the SSAF model is simple, it can cover at least 70% of all fabrication defects [17]. Therefore this model is widely applied.

A drawback of using the stuck-at model for transient faults is its inherent activation problem. If a s@0 or s@1 fault is applied, there is a certain probability that the fault will force the subjected signal to its anticipated value. That probability has to be taken into account in the analysis as well as in the practical conduction of fault experiments, otherwise the results could be falsified. As an alternative, *bit-flip* faults are popular because they invert the logic value of the victim signal and therefore avoid the activation problem of stuck-at faults [63]. However, a simple inversion of the fault-free signal is not a good representation of a physical transient fault. Consider a logic signal that is forced to its opposite value. Now, during the fault duration  $t_f$  the original signal changes its logic state. The bit flip model will again invert that value. Thus any transition of the fault-free signal will be inverted by the bit flip model. Such a behavior deviates from the original physical effects of transient faults that will rather hold the subjected signal at either logical value until the disturbed charge has been removed by the signal's driver.

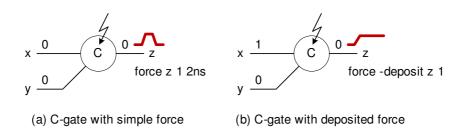

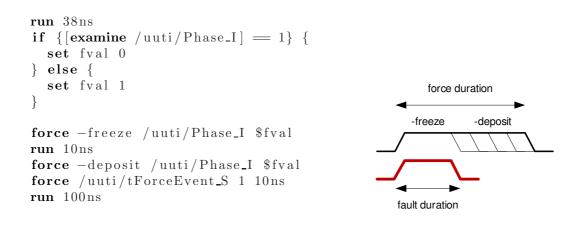

A more realistic representation is a pulse that forces the fault-free signal to the inverse value at the fault occurrence and maintains that state during the complete fault duration [64]. This *pulse model* requires the knowledge of the fault-free signal before the fault is applied. Although such a behavior is easy to simulate it is more difficult to emulate in real hardware. Here, a pure combinational saboteur function is not sufficient anymore. The pulse model requires a state holding element that maintains the faulty state during the fault duration.

In the past, gate delay was the major delay source in an integrated circuit. However, with smaller feature sizes, the delays in wires and interconnects are becoming the dominating source of delay and determine a circuit's performance. Thus *delay faults* are gaining more importance, especially for devices with very high quality and reliability requirements [1]. This is also due to the parameter variations in gates.

Other types of faults that are getting more important are *open faults*. This fault just disconnects and isolates a circuit node from its environment. Since the node has no associated driver anymore its logic state is controlled by the surrounding noise and may fluctuate and probably lead to oscillations. A *bridging fault* occurs, when the logic state of a node called victim is controlled by another signal called aggressor. For example, a s@0 fault could also be described as a bridging fault to the lower supply voltage rail, typically ground.

#### 2.2.4 Masking Effects

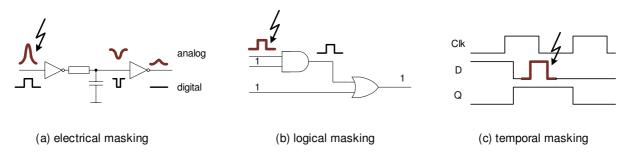

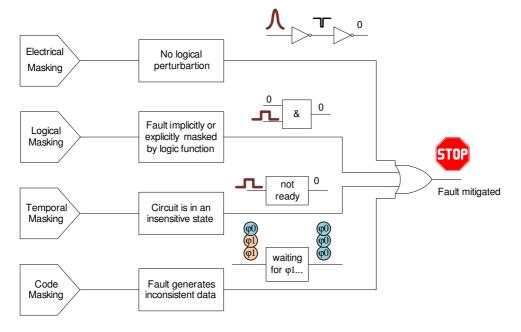

Masking prevents a fault from becoming active and generating an error. In general, there are three main reasons for fault masking [5]:

- 1. *Electrical masking*: Although a fault is injected on the electrical level, it does not have an impact on the logical level. For example, the current pulse induced by a charged particle, see 2.2.2, is not large enough to corrupt the boolean value. Or there is a glitch on the subjected node but this glitch is attenuated by subsequent gates or wire and eventually has no effect.

- 2. Logical masking: The fault corrupts a boolean signal, however, the logic function that is connected to that faulty signal does not take it into account. An example is implicit logical masking: e.g. a faulty logic 1 pulse at one input of an AND-gate will only propagate if the other input is also at logic 1. Hence, implicit logical masking also depends on the input data of the affected circuit as well. Another example is explicit logical masking: adding a majority voter to replicated functions will block an erroneous replica as long as the fault-free replicas are in the majority.

- 3. Temporal (latching-window) masking: The fault disturbs a signal but the fault is not captured. That type of masking only applies in circuits with state holding elements. For example, a transient fault between two clock edges in a synchronous circuit has no effect as long as its effect is removed by the next clock event. In a QDI circuit, a faulty input will not be captured if the successor circuit has not yet sent its acknowledge.

Fig. 2.6 illustrates these basic masking effects. One might regard fault masking as a separate mechanism that allows to mitigate a fault without explicit error recovery measures [49].

Figure 2.6: Classical fault masking

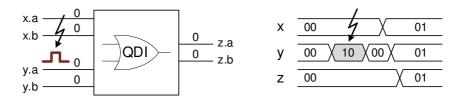

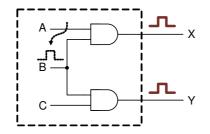

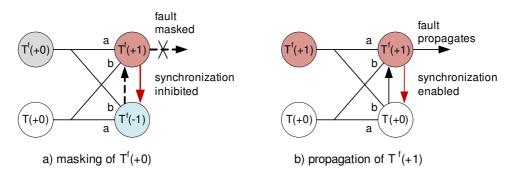

For this thesis, another masking effect is introduced that deals with QDI logic, namely *code masking*. Fig. 2.7 shows a QDI OR-gate that receives a transient fault at one of its inputs. The fault generates a logic 1 value that would propagate to the output due to the logic OR function. However, as the second input is not in the same code phase, the faulty input is masked and the output remains in its current state. Code masking considers the fundamental property of processing only consistent tokens, while inconsistent tokens – independent whether their content is correct or wrong – are rejected:

4. *Code masking*: A fault is rejected by a QDI circuit, if it leads to an inconsistent token. Such a token is prevented from propagating any further as long as it persists.

Figure 2.7: Principle of code masking

Code masking may also be interpreted as logical masking, since the logic function of the receiver does not evaluate the token. Contrary to the logical masking as described above, it is not the data content that leads to the masking effect but the code phase of that data. Therefore, the term code masking has been introduced to highlight that fundamental difference. A similar approach has been presented in [65], where the terminology C-element masking is used. However, that masking effect is described solely for C-elements that receive different inputs, while the definition of code masking is more generally applicable to any type of QDI logic. The authors also mention the masking of delay faults, which is not explicitly highlighted in this work as QDI logic is immune to this type of faults by definition.

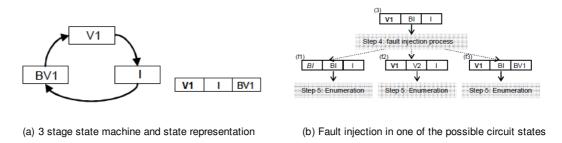

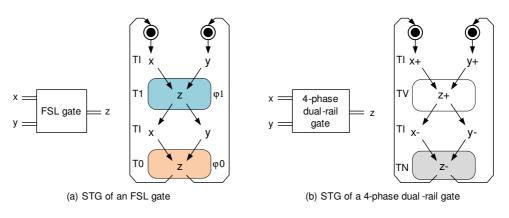

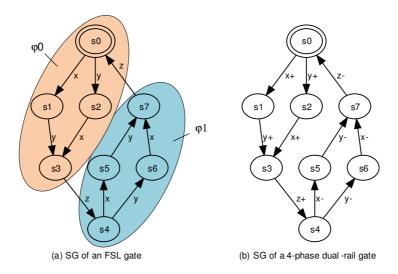

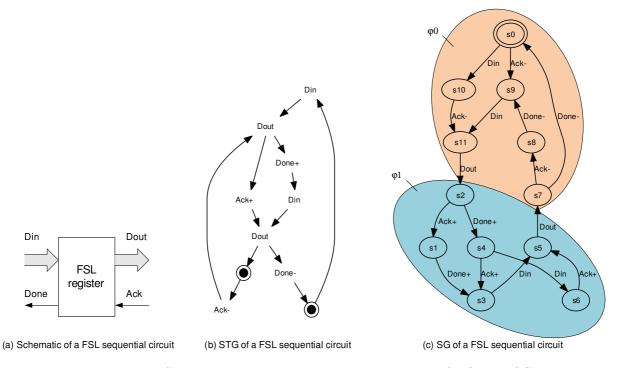

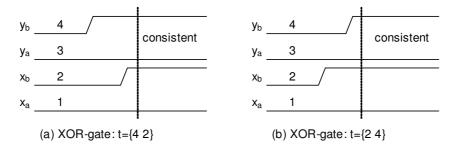

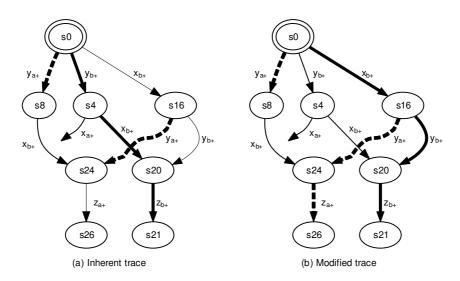

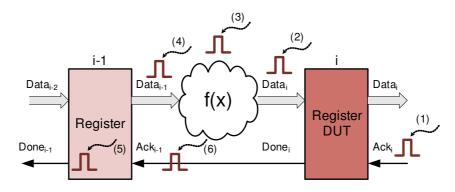

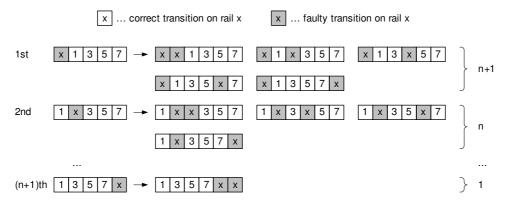

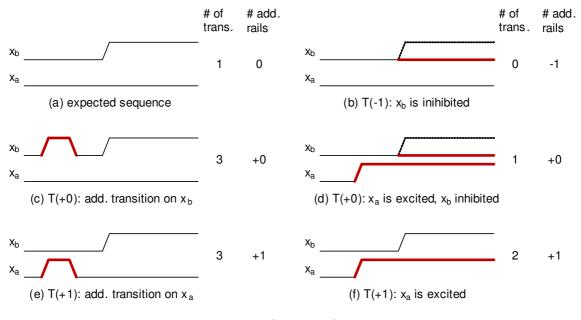

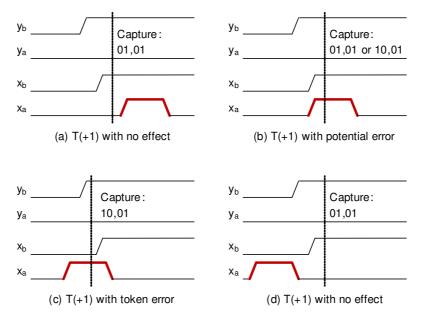

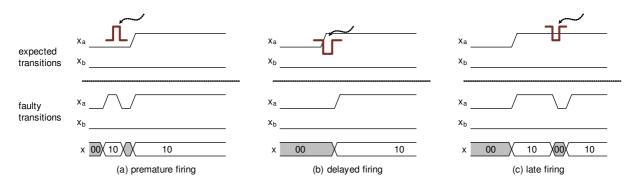

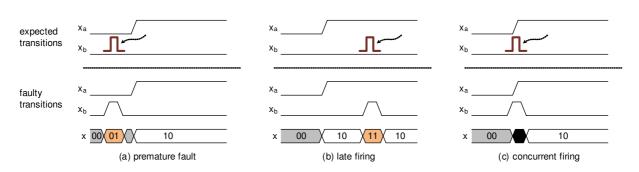

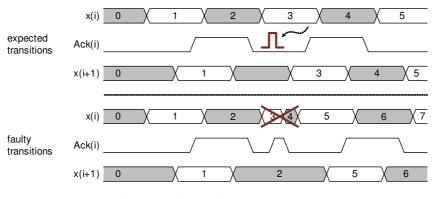

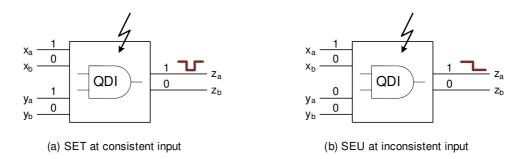

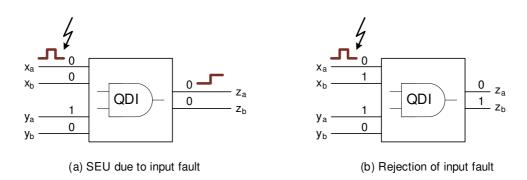

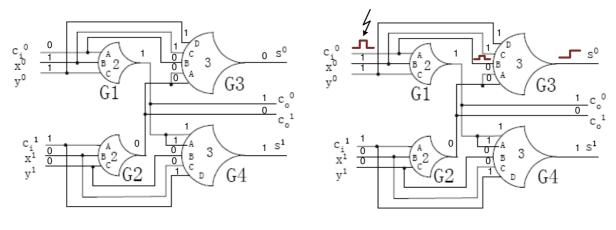

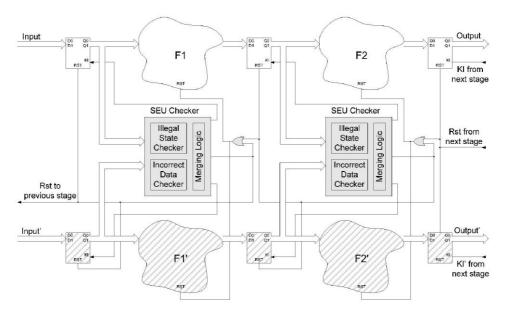

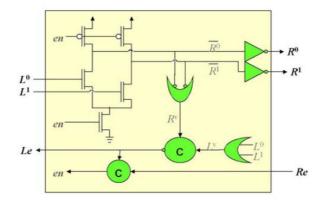

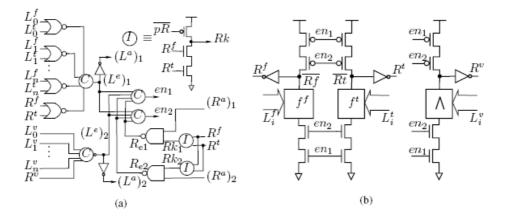

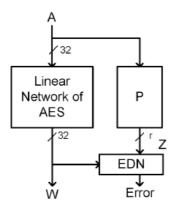

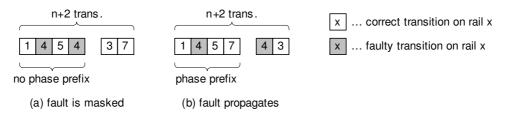

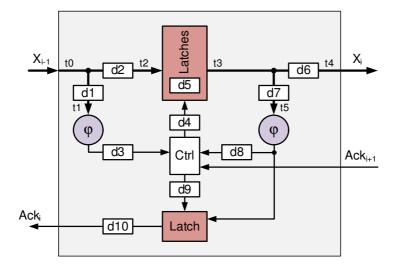

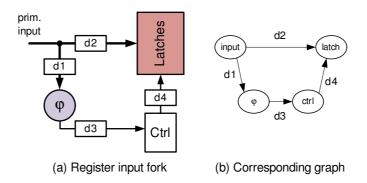

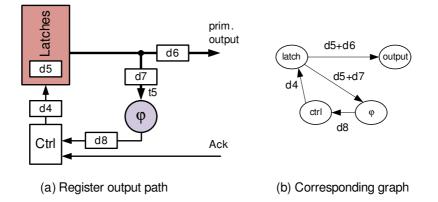

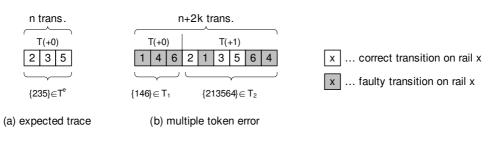

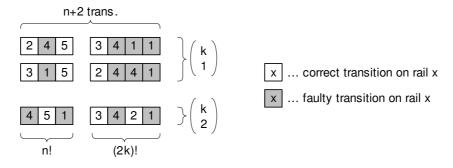

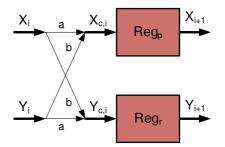

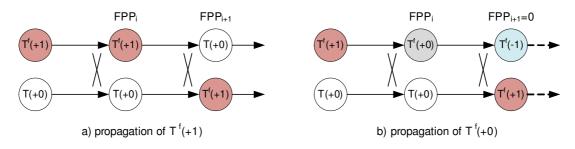

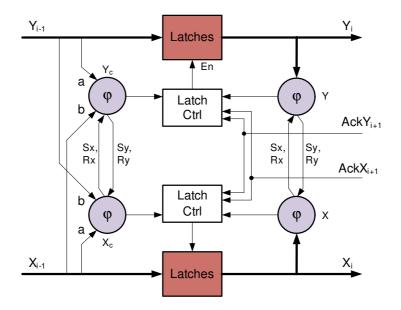

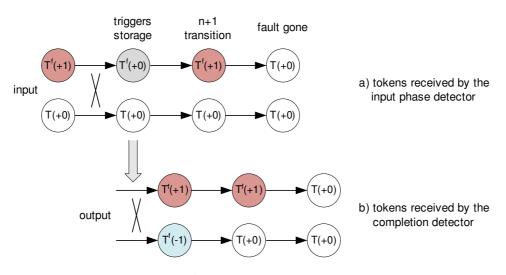

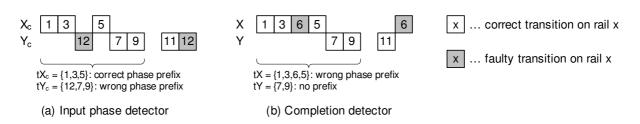

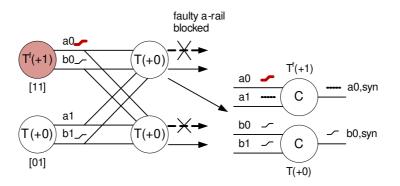

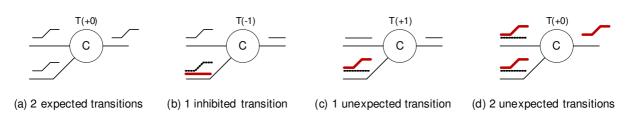

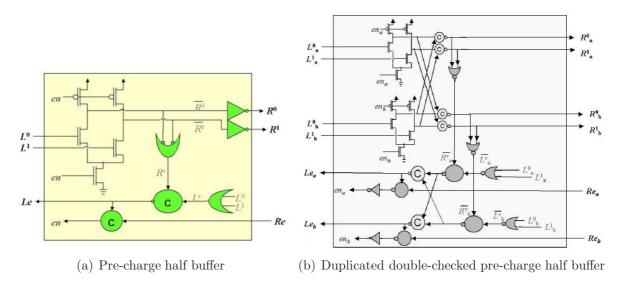

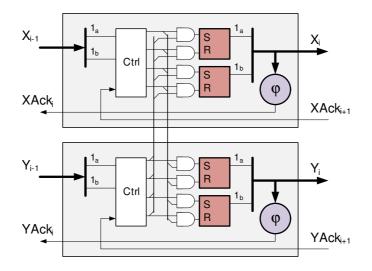

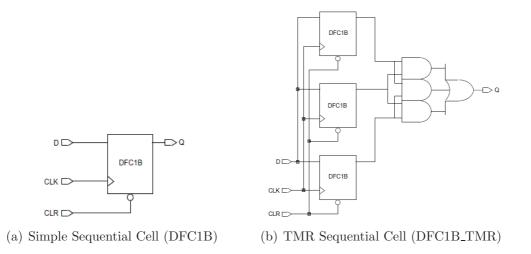

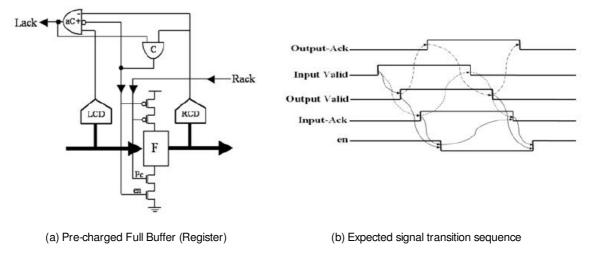

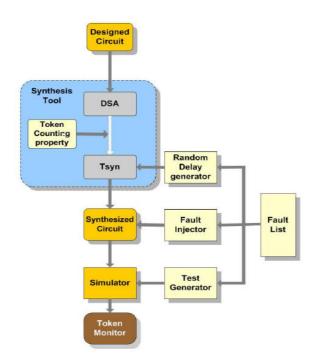

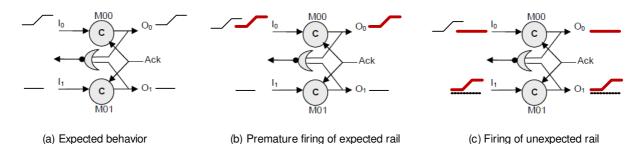

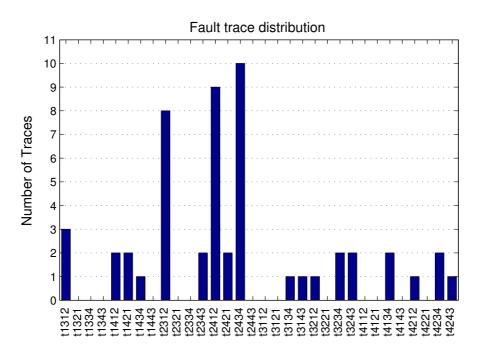

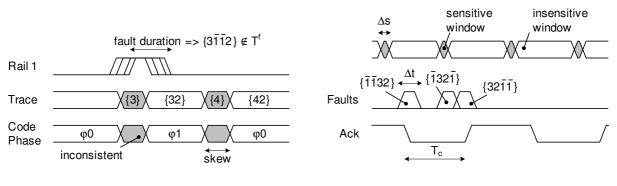

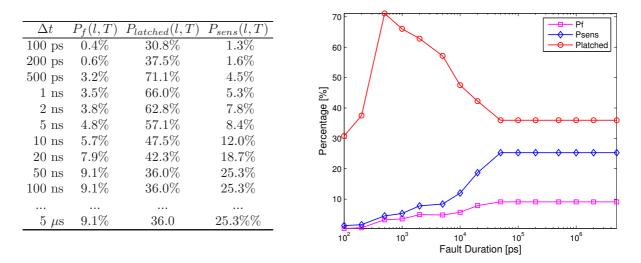

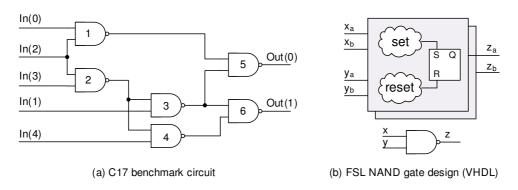

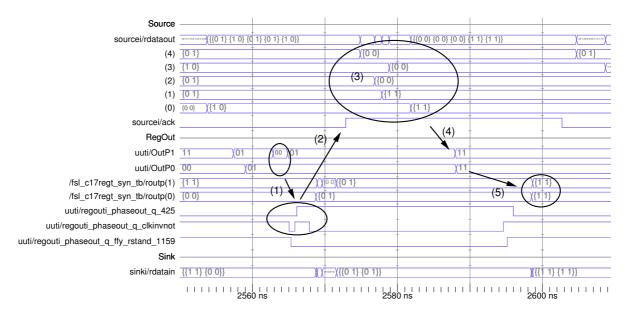

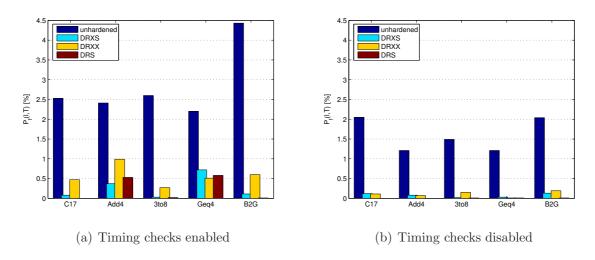

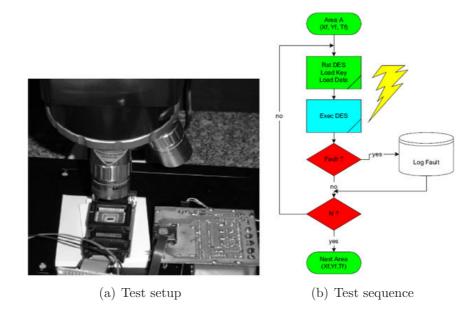

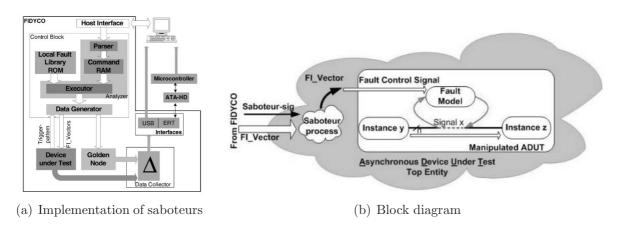

Fig. 2.8 shows a boolean tree of how masking effects help to mitigate faults. Small graphics highlight the masking effect. The electrical masking branch attenuates a faulty glitch. The logical masking branch blocks the positive going pulse via the implicit AND-gate masking. The temporal masking branch rejects the fault as the receiving circuitry is