Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

## Diplomarbeit

# Synthese und elektrische Charakterisierung von Si Nanowire – GaAs Heterostrukturen

Ausgeführt zur Erlangung des akademischen Grades eines Diplom – Ingenieurs

unter der Leitung von

O.Univ.Prof. Dr.phil. Emmerich Bertagnolli

Institut für Festkörperelektronik

und

Ass.Prof. Dipl.-Ing. Dr.techn. Alois Lugstein

Institut für Festkörperelektronik

Eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik

von

Winkler Karl Mat. Nr. : 0525734 Flatzerstraße 152 2620 Flatz

| Wien, am 22.11.2011     |                                         |

|-------------------------|-----------------------------------------|

| VIIOII, aiii 22.11.2011 | *************************************** |

## Kurzfassung

Nanostrukturen sind ein interessantes und viel versprechendes Forschungsgebiet mit diversen Einsatzgebieten unter anderem in der Elektronik und Optoelektronik. Aufgrund ihrer geringen lateralen Abmessungen und der damit verbundenen Eigenschaft, Verspannungen innerhalb weniger Atomlagen ohne Zerstörung des Kristallaufbaus, abzubauen, bieten insbesondere Nanowires die Möglichkeit zum Aufbau von Halbleiter-Heterostrukturen. Sowohl Materialübergänge innerhalb des Nanowires, als auch Heteroübergänge zwischen Substrat und Nanowire bieten die Möglichkeit zur Herstellung derartiger Bauelementen.

In dieser Diplomarbeit wurde die Erzeugung und Charakterisierung von Silizium Nanowires auf Galliumarsenidsubstraten gezeigt. Die große Bedeutung von GaAs für die Optoelektronik und die gute Kontrollierbarkeit des Wachstums von Si Nanowires machen diese Materialkombination besonders interessant. Ein weiterer Grund für die Untersuchung von Nanowire-Hetero-Strukturen mit dieser Halbleiterkombination ist, dass epitaktisches Aufwachsen der beiden Materialien aufeinander in durchgehenden Schichten schwierig ist. Der Grund dafür sind die unterschiedlichen Gitterkonstanten, die unterschiedlichen thermischen Ausdehnungskoeffizienten und der polare Kristallaufbau von GaAs.

Nach einer kurzen Einleitung in das Themengebiet wird eine Einführung in die theoretischen Grundlagen über die verwendeten Materialien und Prozesse angeführt. Der dritte Teil behandelt mit der experimentellen Untersuchung der Nanowiresynthese den Hauptteil der Diplomarbeit. Der Einfluss der Substratreinigung auf das Nanowirewachstum und die Auswirkungen von mehreren nasschemischen Ätzverfahren auf das VLS Wachstum in einem Niederdruck-Gasphasen Prozess, mit Silan als Precursorgas wurden systematisch untersucht. Als Katalysator für das Nanowirewachstum wurde Gold verwendet. Dieses wurde in Form von Kolloiden, sowie in Form von gesputterten Goldschichten aufgebracht. Der Einfluss des Lösungsmittels, mit dem die Kolloide verdünnt wurden, wurde ebenso untersucht, wie die ideale Dicke der Goldschicht. Es wurde gezeigt, dass epitaktisches Wachstum auf Galliumarsenid im Vergleich zum Wachstum auf Silizium erst ab höheren Temperaturen möglich ist. Zu hohe Temperaturen führten im Fall von GaAs jedoch zu einer Zersetzung des Substrats. Mit einer weiteren Testreihe wurde der optimale Druck für das Wachstum und die am besten geeigneten Gasflüsse ermittelt. Um den so erzeugten Heteroübergang elektrisch vermessen zu können, wurden die Nanowires in einer Isolationsschicht eingebettet. Damit konnten einzelne Nanowires, isoliert gegen das GaAs- Substrats kontaktiert und vermessen werden.

Der letzte Teil enthält die Ergebnisse der elektrischen Messungen. Es wurden das Strom-Spannungsverhalten des Bauteils bei Raumtemperatur sowie das Verhalten der Halbleiter-Heterodiode bei tiefen Temperaturen untersucht, diskutiert und daraus die Bandstruktur des Halbleiter-Heteroübergangs berechnet.

#### **Abstract**

Quasi-one-dimensional nanowires have attracted tremendous attention as a playground to study fundamental mesoscopic effects such as quantum confinement or single-electron transistor phenomena, and potential technological applications, enabling extraordinary progress for nanoscale electronics, sensors, photonic devices, solar cells, as well as catalysis and life science. Because of the relatively small lateral nanowire dimensions it is possible that stress induced by lattice mismatches at a hetero-interface can be released within a few atomic layers without causing damage to the inner crystal structure of the wire. Thus, it is possible to produce devices with heterostructures within one wire as well as between nanowire and substrate.

The main focus of this diploma thesis is on the investigation of epitaxial silicon nanowire growth on a GaAs substrate and the electrical characterization of the interface. To the best of my knowledge no work on this topic was published before. The great importance of GaAs for optoelectronics and the good controllability of Si nanowires synthesis make this combination that interesting. Another reason for the research on this material combination at the nanoscale is the fact, that layer growth of these Si-GaAs Systems is very complex due to the great lattice mismatch.

At the beginning a short introduction into the field of research is given. The theoretical part contains growth process concepts as well as a short review on the material properties. The third chapter contains experimental investigations of nanowire synthesis which is the main part of the thesis. The importance of the substrate cleaning is shown and the influences of different wet etching processes for the VLS process in an low pressure chemical vapor deposition reactor growth with silane as precursor gas are explored. Gold is used as a catalyst for this work and is either deposited on the substrate in the form of nanoparticles dissolved either in isopropyl alcohol or in water or sputtered onto the substrate. The influence of the solvent is investigated and the thickness of the gold layer optimized. It will be shown that the growth-temperature for epitaxial growth of nanowires on a GaAs substrate has to be higher than for Si substrates but too high temperatures will cause decomposition of the substrate. Also the best parameters for growth will regard to temperature pressure and gas flow will be determined. To perform electrical measurements on the interface between substrate and wire the device has to be covered with an isolating layer and individual nanowires have to be contacted with Ti/Au pads.

The last part of the work includes the results of the electrical characterization. Current-voltage measurements are performed at room temperature and also at low temperatures. The results are discussed in the last chapter.

## **Danksagung**

An dieser Stelle möchte ich allen Personen danken, die mich während meines Studiums und meiner Diplomarbeit unterstützt haben und mir geholfen haben meine Freude am Studium aufrecht zu erhalten.

Als erstes möchte ich meinem Betreuer Herrn Ass.Prof. Dipl.-Ing. Dr.techn. Alois Lugstein für die gute und intensive Betreuung während meiner Diplomarbeit danken, welche eine große Hilfe zur raschen und positiven Abwicklung gewesen ist. Ebenso möchte ich Herrn O.Univ.Prof. Dr.phil. Emmerich Bertagnolli für die Möglichkeit danken, meine Diplomarbeit am Institut für Festkörperelektronik der TU Wien zu absolvieren.

Ich möchte auch der gesamten Arbeitsgruppe, der ich während meiner Zeit als Diplomand angehört habe, für alle hilfreichen und anregenden Diskussionen danken. Davon besonders hervorheben möchte ich Herrn Dipl.-Ing. Martin Hetzel. Er hat mir bei der Durchführung der Arbeiten für meine Diplomarbeit mit Ratschlägen beiseite gestanden und mir insbesondere bei der Kontaktierung meiner geholfen.

Mein ganz besonderer Dank gilt meiner Mutter Angela Winkler. Ohne Sie wäre mein Studium gar nicht möglich gewesen. Ich möchte Ihr für die mentale als auch finanzielle Unterstützung während meiner gesamten Ausbildung danken. Ihre aufbauenden Worte haben mir geholfen, auch in nicht motivierten Zeiten an meinem Studium festzuhalten und es erfolgreich abzuschließen. Auch meinem Bruder Franz Winkler möchte ich Dank aussprechen dafür, dass er mich als Vorbild ermutigt hat mein Studium in der Fachrichtung Elektrotechnik zu beginnen und mit gutem Erfolg zügig abzuschließen. Ebenso möchte ich mich bei seiner Frau Eveline Winkler bedanken, welche mich immer gerne mit Rat und Tat unterstützt hat.

Auch meinen Studienkollegen/innen, die mich durch mein Studium begleitet und mit denen ich in Zusammenarbeit auch die schwierigsten Übungen absolvieren konnte, möchte ich danken.

Als letztes möchte ich mich bei meiner Freundin Beate Ungerböck und allen meinen Freunden sowie Musikkollegen der Trachtenkapelle Flatz und meiner Musikgruppe "Die Blaubären" bedanken, welche mir zu einem guten Ausgleich zwischen Arbeit und Freizeit verholfen haben und so auch zum Gelingen meines Studiums beigetragen haben.

### **INHALTSVERZEICHNIS**

| 1     | EINLEITUNG                                                              | 2       |

|-------|-------------------------------------------------------------------------|---------|

| 2     | THEORETISCHE GRUNDLAGEN                                                 | 4       |

| 2.1   | Der Halbleiter Silizium                                                 | 4       |

| 2.2   | Der Halbleiter Galliumarsenid                                           | 6       |

| 2.3   | Synthese von Nanowires                                                  | 8       |

| 2.3.1 | Das Vapour-Liquid-Solid Verfahren                                       | 8       |

| 2.3.2 | Parameterabhängigkeit des VLS Verfahrens                                | 10      |

| 2.3   | 3.2.1 Einfluss des Katalysators auf das Nanowirewachstum                | 11      |

| 2.3   | 3.2.2 Einfluss der Prozesstemperatur auf das Nanowirewachstum           | 12      |

| 2.3   | 3.2.3 Einfluss des Prozessdrucks auf das Nanowirewachstum               | 15      |

| 2.3.3 | Epitaxie                                                                |         |

| 2.3   | 3.3.1 Epitaktisches Wachstum von Si Nanowires auf einem Si-Substrat     | 17      |

| 2.3   | 3.3.2 Heteroepitaxie von Nanowires                                      | 20      |

| 2.4   | Elektrische Eigenschaften von Halbleiter-Übergängen                     | 22      |

| 2.4.1 | Der pn Übergang                                                         | 23      |

| 2.4.2 | Der Halbleiter-Heteroübergang                                           | 26      |

| 2.4.3 | Der GaAs-Si-Heteroübergang                                              | 29      |

| 3     | EXPERIMENTELLE DURCHFÜHRUNG                                             | 31      |

| 3.1   | Herstellungsprozess einer Nanowire Halbleiter Hetero- Diode             | 31      |

| 3.2   | Nanowiresynthese                                                        | 33      |

| 3.2.1 | Substrat Reinigung                                                      | 34      |

| 3.2.2 | Aufbringen des Katalysators                                             | 35      |

| 3.2   | 2.2.1 Au – Kolloide als Katalysator                                     | 35      |

| 3.2   | 2.2.2 Aufbringen des Au Katalysators durch plasmaunterstützes-Sputtern  | 35      |

| 3.2.3 | Nanowirewachstum mittels Niederdruck-Gasphasen-Abscheidung              | 36      |

| 3.3   | Isolierung der Si Nanowires                                             | 38      |

| 3.4   | Kontaktierung der Nanowires                                             | 40      |

| 3.4.1 | Strukturieren der Kontaktflächen mittels Elektronenstrahllithographie   | 40      |

| 3.4.2 | Erstellung von Kontaktflächen zur Vermessung von Nanowires              | 40      |

| 3.5   | Methoden der elektrischen Charakterisierung von Halbleiter-Heteroübergä | ngen 41 |

| 3.5.1 | Elektrische Vermessung der Halbleiter-Heterodiode                       | 41      |

| 352   | Tieftemperaturmessungen                                                 | 42      |

| 4     | RESULTATE UND DISKUSSIONEN                                                                        | 45 |

|-------|---------------------------------------------------------------------------------------------------|----|

| 4.1   | Heteroepitaktische Synthese von Si-Nanowires auf einem GaAs – Substrat                            | 45 |

| 4.1.1 | Versuchsablauf                                                                                    |    |

| 4.1.2 | Reinigen der GaAs Substratoberfläche                                                              |    |

| 4.1.3 | VLS – Wachstum                                                                                    |    |

| 4     | .1.3.1 Katalysator für das VLS Wachstum                                                           | 50 |

| 4     | .1.3.2 Einfluss der Prozesstemperatur auf das Nanowirewachstum                                    | 56 |

| 4     | .1.3.3 Druck- und Zeitabhängigkeit des Nanowire- Wachstums                                        | 59 |

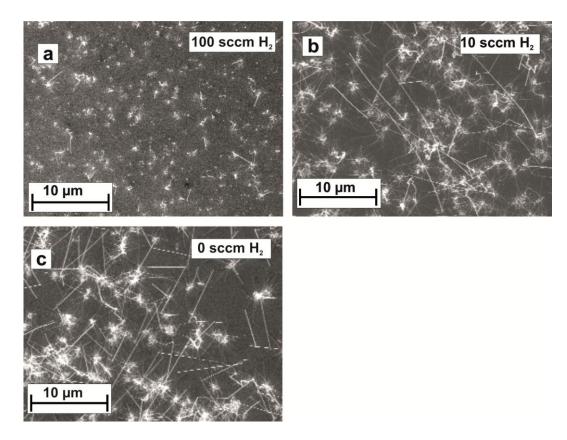

| 4     | .1.3.4 Einfluss von Prozessgasflüssen                                                             | 61 |

| 4.2   | Herstellen des Messmodules zur elektrischen Charakterisierung des Si Nand<br>GaAs Heteroübergangs |    |

| 4.3   | Elektrische Charakterisierung der Halbleiter-Hetero-Diode                                         | 67 |

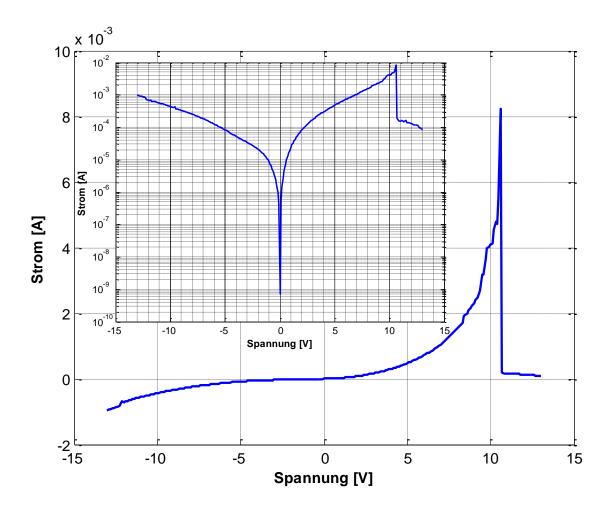

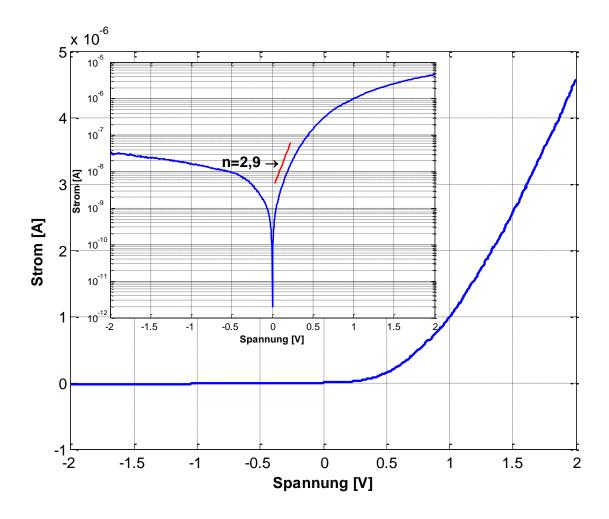

| 4.3.1 | Elektrische Charakterisierung bei Raumtemperatur                                                  |    |

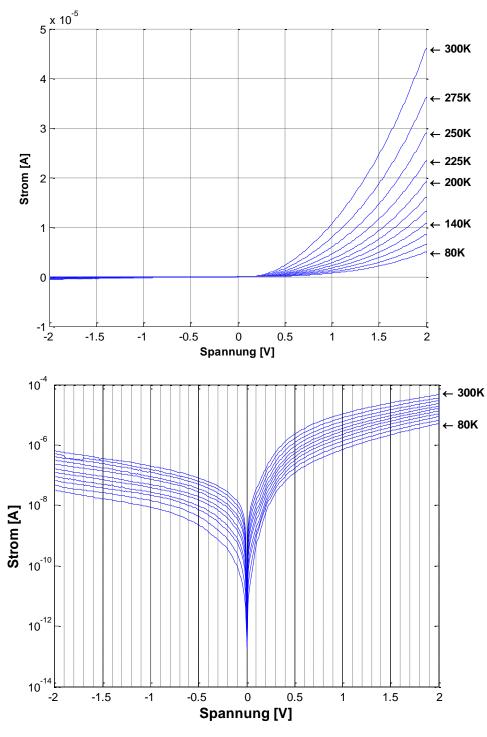

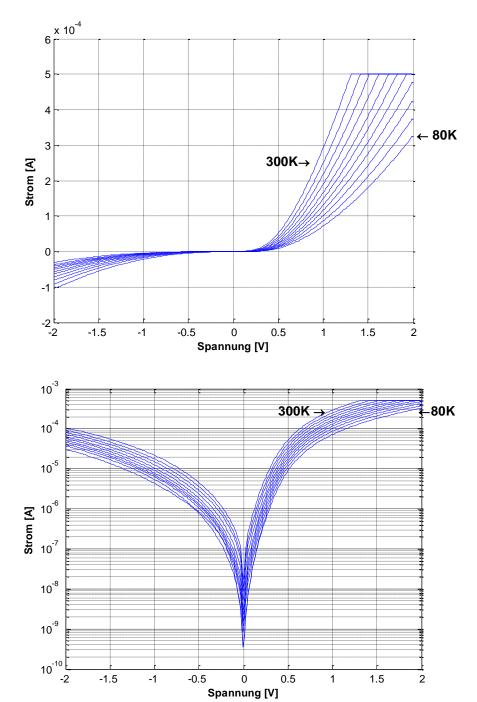

| 4.3.2 | Temperaturabhängigkeit der Strom/Spannungs-Kennlinie                                              | 72 |

| 5     | ZUSAMMENFASSUNG UND AUSBLICK                                                                      | 76 |

| 6     | LITERATURVERZEICHNIS                                                                              | 78 |

| 7     | ABBILDUNGSVERZEICHNIS                                                                             | 83 |

## 1 Einleitung

Der Bereich der Mikroelektronik ist derzeit einer, der sich am schnellsten entwickelnden Bereiche der Technik. Die von Gordon E. Moore getätigte Vorhersage dass sich die Anzahl der Bauteile pro Mikrochip vervielfältigt während die Produktionskosten stetig abnehmen hat sich längst bewahrheitet. [1] Die rasante Leistungssteigerung integrierter Schaltungen ist nur durch eine Erhöhung der Packungsdichten und der damit verbunden Verkleinerung der Strukturen möglich. Diese fortschreitende Miniaturisierung scheint nun aber im Bereich der optischen Lithographie an ihre Grenzen zu stoßen. Ebenso kommt es durch die Verringerung der Strukturgrößen und der damit verbunden Gateoxid-Dicke zu vergrößerten Leck-Ströme und, damit verbunden, zu einer erhöhten Energieaufnahme.[2] Um diesen Problemen entgegen zu wirken, können moderne Ansätze wie Gate-all-around Transistoren oder auch Heterobauelemente verwendet werden.

Um den Anforderungen des rasanten Wachstums und der ständig zunehmenden Komplexität der Schaltungen weiter nachkommen zu können, sind alternative Herstellungsverfahren notwendig. Ein vielversprechender Ansatz dazu ist der Wechsel zu 1D Strukturen wie Nanowires, welche durch den VLS Prozess, welcher 1964 von R.S. Wagner und W.C. Ellis präsentiert wurde, hergestellt werden können. Die Synthese von Si Nanowires z.B. basiert auf der Übersättigung eines Katalysators mit Silizium. Das Silizium nukleiert an der Grenze von Katalysator zum Substrat. Dadurch stellt sich Nanowirewachstum ein, wobei im Idealfall des epitaktischen Wachstums die Kristallrichtung des Substrats fortgesetzt wird. Der Prozess findet bei Temperaturen über dem eutektischen Punkt der Gold-Silizium Legierung statt.[3]

Nanowires haben aufgrund ihrer speziellen Eigenschaften und der vielseitigen Einsatzgebiete stark an Bedeutung gewonnen und sind ein wichtiger Forschungsbereich. Es konnten damit bereits elektronische Bauelemente, wie z.B. Feldeffekt-Transistoren [4] oder Esaki-Tunneldioden [5], aber auch Sensoren, sowie optoelektronische Bauelemente erzeugt werden.[6] Die zur Herstellung von Nanowires verwendeten Materialien umfassen neben Silizium und Germanium auch viele III-V und II-VI Halbleiter, wie GaAs, InAs, InP oder CdS. [4],[7]

Besondere Bedeutung hat auch die Erforschung von Nanowire Heterostrukturen erhalten. Die Erzeugung von solchen Heteroübergängen erfordert bei Verwendung des VLS-Verfahrens lediglich ein Umstellen des Precursorgases während des Wachstums. Auf diese Weise können sowohl axiale Heterostrukturen, welche einen Wechsel des Halbleitermaterial in Wachstumsrichtung, bei idealerweise gleichbleibendem Durchmesser aufweisen, als auch radiale Heterostrukturen, bei welchen die Halbleitermaterialien einen Kern-Mantel-Aufbau aufweisen hergestellt werden.[4],[7]

#### 1 Einleitung

Aber nicht nur der Halbleiterübergang innerhalb eines Nanowires kann für technische Anwendungen genutzt werden, sondern auch der Übergang vom Substrat zum Nanowire. So konnte z.B. für einen Übergang von p-Si-Substrat auf n-CdS Nanowire bei angelegter Vorwärtsspannung eine breitbandige Elektrolumineszenz realisiert werden. Bei Erhöhung der Spannung ändert sich das Spektrum auf ein schmalbandiges Laserspektrum.[8]

Um diese Halbleiter-Hetero-Bauelemente realisieren zu können, müssen einige wichtige Voraussetzungen erfüllt sein, insbesondere ein gezieltes und gut kontrollierbares, epitaktisches Wachstum der Nanowires. Diese Diplomarbeit beschäftigt sich mit der Erzeugung von GaAs-Substrat - Silizium-Nanowire Heterostrukturen. Es werden alle, für die Synthese wichtigen Prozessschritte untersucht. Darunter fallen sowohl die Substratreinigung, als auch die Wahl des Katalysators und dessen Aufbringungsart. Die Substrat-Nanowire-Übergänge der epitaktisch gewachsenen Drähte werden charakterisiert und somit eine Basis für weiterführende Untersuchungen geschaffen.

#### 2.1 Der Halbleiter Silizium

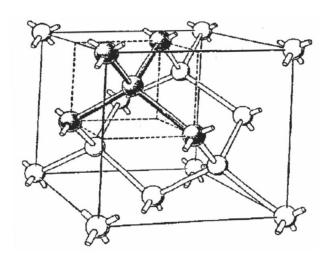

Si ist der meist verwendete Halbleiterwerkstoff in der Mikroelektronik und gehört der IV Hauptgruppe an. Die Kristallstruktur von Si ist die Diamantstruktur, welche in Abbildung 3 dargestellt ist. Alle Atome der Einheitszelle sind Si-Atome wobei die Gitterkonstante 5.431 Å beträgt.[2] Ein Si Atom geht eine Bindung mit vier weiteren Si Atomen ein. Der Winkel zwischen den Atomen beträgt 109,47°, wodurch sich eine Tetraeder-Form bildet. Eine solche ist in der Abbildung durch die dunkel schraffierten Atome und deren Verbindungen dargestellt. Silizium wird für die Halbleiterindustrie meist mit dem Kristallziehverfahren nach Czochralski, oder, für die Fertigung von hochreinem Silizium, mittels des tiegelfreien Zonenzieh-Verfahrens hergestellt. Der Schmelzpunkt von Si liegt bei 1688 K, darunter hat Silizium einen linearen Wärmeausdehnungs- Koeffizienten von  $\alpha_{TH}$ =2,6x10 $^{-6}$  K $^{-1}$ .

Abbildung 1: Schematischer Aufbau der Kristallstruktur von Si das in einer Diamantstruktur kristallisiert. [9]

Das bei Temperaturen um 1273 K in O<sub>2</sub> Atmosphäre entstehende SiO<sub>2</sub> ist einer der Gründe, warum es sich als wichtigster Halbleiter in der Mikroelektronik durchgesetzt hat. Dieses Oxid weist gute Eigenschaften als Isolator auf, ist chemisch und physikalisch resistent gegen Umwelteinflüsse und weist gute Grenzflächeneigenschaften auf. Das sich bei Raumtemperatur und an Luftsauerstoff bildende native Oxid hat eine Dicke zwischen 10-20 Å. SiO<sub>2</sub> Schichten können relativ leicht mittels

nasschemischer Reinigung unter Verwendung von Flusssäure (HF) entfernt werden. HF weist eine gute Selektivität zwischen Si und SiO<sub>2</sub> auf.[**2**]

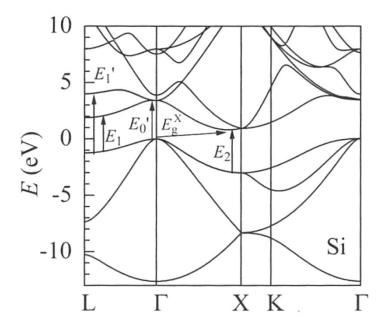

Abbildung 2: Energie-Bänderschema von Silizium mit eingezeichneter Bandlücke. Für den indirekten Übergang wird eine Energielücke von E<sub>g</sub>=1,11eV bei Raumtemperatur bestimmt. [10]

In der vorangehenden Abbildung 2 ist das Bänderschema von Silizium abgebildet. Silizium ist ein indirekter Halbleiter mit einer Bandlücke von 1,11 eV bei einer Temperatur von 300 K. Aus dem abgebildeten Bänderschema ist dies ersichtlich, da das Maximum des Valenzbandes im F-Punkt liegt, während das Minimum des Leitungsbandes bei X liegt. Die Elektronenaffinität χ ist die Energie mit welcher ein Elektron an ein Atom gebunden ist. Sie ist die das Gegenstück zur Ionisierungsenergie, welche die Energie angibt, welche notwendig ist um ein Elektron von der Leitungsbandkante bis zum Vakuumniveau anzuheben und somit vom Kristall zu trennen. Die Elektronenaffinität  $\chi$  beträgt in Si E<sub>G</sub>=4,01 eV.[11] Der spezifische Widerstand von intrinsischem Si beträgt  $\rho_{\text{Si}}$ =2,3x10<sup>5</sup>  $\Omega^*$ cm und kann durch Einbringen von Dotierstoffen in weiten Bereichen gezielt eingestellt werden. Durch das Einbringen von Fremdatomen in den Si Kristall welche ein Elektron mehr bzw. weniger als Si haben, werden freie Elektronen oder Löcher eingebracht. Dadurch wird das Ferminiveau verschoben und rückt im Fall von n-Dotierung näher an die Leitungsbandkante und im Fall von p-Dotierung näher an die Valenzbandkante. Durch dieses gezielte Einbringen von freien Ladungsträgern kann die Leitfähigkeit gezielt verändert werden. Als Dotierstoffe werden meist Bor als Akzeptor und Arsen, Antimon oder Phosphor als Donatoren verwendet.

Die Leitfähigkeit von Halbleitern hängt von der Anzahl freier Ladungsträger, sowie der Elektronen- und Löcherbeweglichkeit in Silizium ab. Bei einer Temperatur von 300 K beträgt die Elektronenbeweglichkeit  $\mu_{n(300)}$ =1500 cm²/(Vs) und ist damit mehr als dreimal so groß wie die Löcherbeweglichkeit, welche  $\mu_{p(300)}$ =450 cm²/(Vs) beträgt.

#### 2.2 Der Halbleiter Galliumarsenid

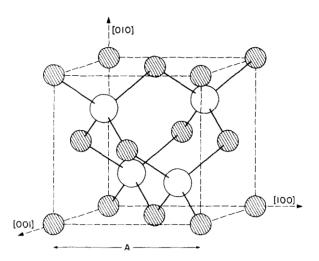

GaAs ist eines der bedeutendsten Materialien in der Optoelektronik. Es ist ein Halbleiterwerkstoff aus der III-V Familie. Er wird für die Herstellung von elektronischensowie von optoelektronischen- Bauteilen verwendet. Durch austauschen von geringen Mengen von Ga durch In oder Al kann die Energie der Bandlücke verändert werden. Diese Materialkombinationen können abrupt innerhalb weniger Atomlagen aufeinander aufgewachsen werden und so komplexe Heterostrukturen erzeugt werden. Die Kristallstruktur von GaAs ist eine Sphalerit-Struktur (Zinkblende-Struktur) bestehend aus zwei kubisch-flächenzentrierten Gittern. Diese bestehen aus Gallium (Ga) oder Arsen (As) Atomen und sind je um ein Viertel der Raumdiagonalen gegeneinander verschoben. Die unterschiedlichen Basen der beiden Gitter liegen somit bei (000) und  $(\frac{1}{4}, \frac{1}{4}, \frac{1}{4})$ . Ein Ga Atom geht Verbindungen zu je vier benachbarten As Atomen (und gegengleich ein As Atom vier Bindungen mit benachbarten Ga Atomen) in Form eines Tetraeders unter einem Winkel von 109,47° ein, und hat eine Gitterkonstante von 5.65325 Å.[12] Die folgende Abbildung 3 zeigt schematisch den Aufbau der Kristallstruktur von GaAs.

Abbildung 3: Schematischer Aufbau der Kristallstruktur von GaAs mit zwei, um ¼ der Raumdiagonalen verschobenen fcc-Gittern aufgebaut aus Ga oder As Atomen. [12]

Hochreines GaAs für die Wafer-Fertigung wird meist mit dem Liquid-Encapsulated-Czochralski Verfahren hergestellt.[13] Der Schmelzpunkt von GaAs liegt bei 1513 K.[12] Der lineare Wärmeausdehnungskoeffizient von Gallium schwankt abhängig von der Temperatur in einem großen Bereich und beträgt bei 300 K etwa  $\alpha_{TH}=6,03*10^{-6}\,\text{K}^{-1}$ .[14]

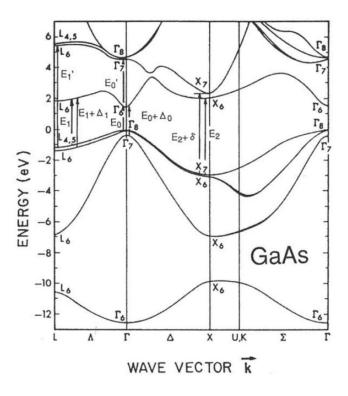

In Abbildung 4 ist das Bänderschema von GaAs abgebildet. Man sieht, dass sowohl das Maximum des Valenzbandes als auch das Minimum des Leitungsbandes beim  $\Gamma$ -Punkt liegen. Der Abstand zwischen diesen Extremwerten entspricht der Bandlücke von GaAs welche bei 300K  $E_G$ =1,424 eV beträgt. Die Elektronenaffinität  $\chi$  beträgt  $\chi_{GaAs}$ =4,07 eV.[11]

Abbildung 4: Energie- Bänderschema von GaAs mit der direkten Energiebandlücke welche im im Γ-Punkt liegt und bei Raumtemperatur E<sub>α</sub>=1,424eV beträgt. [15]

Der intrinsische Widerstand von GaAs beträgt  $\rho_{GaAs}$ =3,3\*10<sup>8</sup>  $\Omega$ cm. Um die Anzahl der freien Ladungsträger in GaAs gezielt steuern zu können, werden ebenso wie in Si Dotierstoffe in das Kristallgitter eingebracht. Im Fall von GaAs wird dafür oft Si verwendet. Si ist aus der IV Hauptgruppe und kann, abhängig von den Prozessbedingungen sowohl als Donator als auch als Akzeptor wirken, da es sowohl den Platz eines Ga Atoms als auch den eines As Atoms einnehmen kann. Dies kann bei bestimmten Dotierprofilen zu Problemen führen. Meist wird das Si aber anstelle

eines Ga Atoms im Kristall integriert und wirkt so als Donator.[16] Um eine p-Dotierung herzustellen, können Stoffe aus der zweiten Hauptgruppe verwendet werden. Einer der meist verwendeten Akzeptor Stoffe für GaAs ist Beryllium.[17]

Die Elektronenmobilität von undotiertem GaAs ist wesentlich höher als bei Si und beträgt bei 300 K  $\mu_n(300)$ = 8000 cm²/(Vs). Die Löchermobilität hingegen ist bei Raumtemperatur mit einem Wert von  $\mu_p(300)$ =320 cm²/(Vs) niedriger als bei Si.[12] Das natürliche Oxid, welches sich bei Umgebungsluft und Raumtemperatur bildet, ist im Gegensatz zu Siliziumdioxid ein mehrlagiges, komplexes Oxid mit einer Dicke von 20 – 25 Å. Teile des Oxids sind wasserlöslich und könne durch Spülen mit Wasser entfernt werden der andere Teil ist wasserbeständig und kann nur durch Desorption des Sauerstoffs unter Hochvakuum und hohen Temperaturen oder durch chemische Ätzprozesse entfernt werden.[18]

## 2.3 Synthese von Nanowires

Nanostrukturen und deren Anwendungen haben in den letzten Jahren immer mehr an Bedeutung gewonnen. Nanostrukturen besitzen von ihrer Größe abhängige Eigenschaften, welche durch gezielte Herstellungsprozesse für elektronische und optoelektronische Anwendungen genutzt werden können. In diesen Bereich fallen auch Nanowires, welche durch die Eigenschaft Verspannungen innerhalb weniger Atomlagen zu relaxieren auch die Möglichkeit bieten Heterostrukturen mit Materialien unterschiedlicher Gitterkonstante herzustellen. Zur Herstellung von Nanowires können verschiedenste Herstellungsverfahren verwendet werden, wie zum Beispiel Molekularstrahlepitaxie[19], thermisches Aufdampfen, Laserablation[20] oder das Vapour-Liquid-Solid (VLS) Verfahren. [3] Auf das in dieser Diplomarbeit verwendete VLS Verfahren und dessen Eigenschaften soll im Folgenden genauer eingegangen werden.

#### 2.3.1 Das Vapour-Liquid-Solid Verfahren

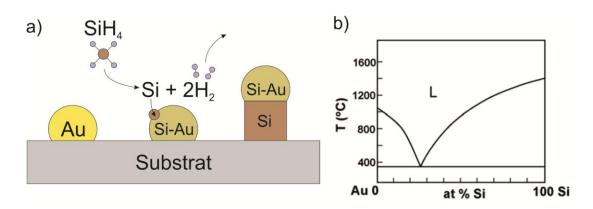

Das Vapour-Liquid-Solid (VLS) Verfahren zur Erzeugung von Nanowires ist ein katalysatorunterstützter Gasphasenabscheidungsprozess (engl. chemical-vapour-deposition, CVD-Prozess). Er basiert auf der Übersättigung eines Katalysator-Partikels mit dem zu wachsenden Material und einer anschließenden Abscheidung an der Katalysator-Substrat Grenze. Im Fall von Silizium Nanowires wird als Katalysator meistens Gold verwendet. Das Halbleitermaterial wird durch ein Precursor-Gas bereitgestellt, dass sich an der Katalysator-Oberfläche zersetzt, anfänglich mit diesem eine Legierung bildet und bei weiterer Zufuhr zu einer Übersättigung führt. Im Fall von

Si kommen die Precursor-Gase Silane (SiH<sub>4</sub>), Disilane (Si<sub>2</sub>H<sub>6</sub>) oder Siliziumtetrachlorid (SiCl<sub>4</sub>) am häufigsten zum Einsatz.[3], [4] In der folgenden Abbildung 5a ist der schematische Ablauf des VLS Prozesses zur Herstellung von Si-Nanowires mittels SiH<sub>4</sub> dargestellt. Auf das Substrat wird Gold als Katalysator durch Sputtern oder mittels Kolloiden aufgetragen. Durch Aufheizen während des Nanowirewachstums bilden sich flüssige Goldcluster auf der Substratoberfläche. Auf der Goldoberfläche kommt es zur Zersetzung des Silans in Silizium und Wasserstoff. Das Si diffundiert in den Goldtropfen, während der Wasserstoff über das Vakuumsystem abtransportiert wird. Dieser Vorgang findet solange statt, bis sich der Goldtropfen mit Si übersättigt hat. Ab einer kritischen Konzentration beginnt das Si sich an der Substrat-Gold Grenzfläche zu nukleieren. Die Kristallorientierung wird bei epitaktischem Wachstum vom Substrat übernommen und durch das Si Nanowirewachstum wird der Goldtropfen von der Substratoberfläche abgehoben. Das Nanowirewachstum kann durch abpumpen des Silans gezielt gestoppt werden.

Bei Verwendung von SiCl<sub>4</sub> als Precursor muss dem Gasgemisch zusätzlich Wasserstoff zugeführt werden. An der Goldoberfläche reagiert das SiCl<sub>4</sub> mit dem Wasserstoff zu Si und HCl. Das Si diffundiert in den Goldpartikel, während sich die HCl Moleküle vom Goldpartikel lösen und im CVD Reaktor abgesaugt werden. Der Wasserstoff liefert eine H<sub>2</sub> terminierte Nanowireoberfläche und führt so zur Passivierung der Silizium-Oberfläche. Es wird dadurch die Bildung einer amorphen Hülle um den Nanowire verhindert und die Oberflächenrauigkeit verringert.[21]

Abbildung 5: Grundlagen des Nanowirewachstums.

a) Schematischer Ablauf des VLS-Prozesses bei Verwendung von SiH<sub>4</sub> als Precursor. Das über die Gasphase zugeführte Silan zersetzt sich durch eine katalytische Reaktion am Gold. Das Si diffundiert in den Au-Tropfen, führt zu einer Übersättigung und in weiterer folge durch Nukleation an der Au-Si Grenzschicht zu Nanowirewachstum.

b) Binäres Au-Si Phasendiagramm mit einem eutektischen Punkt bei ca. 635 K. [20]

Die Zersetzungsreaktion des Precursors liegt normalerweise bei Temperaturen, welche wesentlich höher sind als die praktisch angewandten Wachstumstemperaturen. Der Goldpartikel bewirkt als Katalysator jedoch eine Verringerung dieser Schwellentemperatur.

Abbildung 5 b zeigt das binäre Phasendiagramm einer Gold-Silizium Legierung. Diese hat bei ca. 636 K einen eutektischen Punkt. Diese Temperatur liegt damit deutlich niedriger als die Schmelzpunkte der beiden Materialien in reiner Form. Das Silizium schlägt sich aus dem übersättigten Goldpartikel auf der Gold-Substrat Kontaktfläche nieder. Das kontinuierliche Wachstum von Nanowires beruht daher auf der ständigen Übersättigung des Katalysatorpartikels durch Adsorption aus der Gasphase.[20]

Beim Wachstum von Nanowires mittels VLS Verfahren ist der Durchmesser des Katalysatorpartikels nicht nur für die Dimensionen des Drahtes ein bestimmender Faktor, sondern auch für die Wachstumsrichtung. Nanowires mit einem Durchmesser unter 20 nm wachsen bevorzugt in <110> Richtung, bei Durchmessern größer als 40 nm größtenteils in <111> Richtung. Bei einem Querschnitt zwischen diesen Bereichen kommen beide Orientierungen vor und zusätzlich noch Nanowires in <112> Richtung. Der Grund für die durchmesserabhängige Wachstumsrichtung ist, dass sich bei unterschiedlichen Durchmessern die bevorzugten Richtungen als energetisch Günstiger erweisen. Über Berechnungen der Oberflächen- und Randenergien des Goldkatalysator–Si-Substrat Übergangs können die bevorzugten Wachstumsrichtungen errechnet werden. [21],[22] Die unterschiedlichen Wachstumsrichtungen hängen allerdings nicht nur, wie in den eben angeführten Quellen beschrieben, vom Durchmesser des Katalysators ab, sondern auch vom Wachstumsdruck.[23] Eine genauere Betrachtung dieser Einflussgröße wird in Kapitel 2.3.2.3 genauer angeführt.

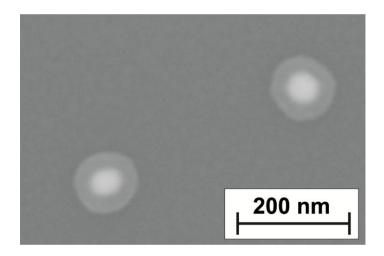

Der Durchmesser des Nanowires wird in erster Linie von der Größe des Katalysatorpartikels bestimmt. Es können Drähte mit einem Durchmesser von mehr als 100 µm bis zu Drähten im Bereich von wenigen Nanometern erzeugt werden. Bei Verwendung von 2 nm großen Gold-Clustern können beispielweise Nanowires mit einem Durchmesser von ca. 3,3 nm gewachsen werden. [3], [4]

#### 2.3.2 Parameterabhängigkeit des VLS Verfahrens

Das VLS ist ein gängiges Verfahren durch welches auf relativ einfache Weise anisotropes Kristallwachstum erzielt werden kann. Um dieses kontrolliert zu ermöglichen, müssen alle Prozessparameter genau kontrolliert werden. Die Temperatur sowie der Druck in der Prozesskammer während des Wachstums müssen einstellbar sein und über den Wachstumszyklus konstant gehalten werden können. Ein gleichmäßiger Fluss der Prozessgase sowie das richtige Verhältnis zwischen Precursor und Trägergas sind für ein gleichmäßiges Wachstumsergebnis ebenfalls

erforderlich. Die Länge der Nanowires kann durch gezieltes Einstellen der Wachstumsdauer geregelt werden. Durch Abstellen des Precursor-Gasflusses und Spülen der Wachstumskammer mittels eines inerten Gases, wie z.B. Helium, kann das Wachstum gezielt gestoppt werden. Im Folgenden werden die Einflüsse der einzelnen Parameter auf die Nanowiresynthese genauer erläutert.

#### 2.3.2.1 Einfluss des Katalysators auf das Nanowirewachstum

Als Katalysator für das Wachstum von Si Nanowires wird meistens Gold verwendet. Da jedoch für spezielle Anwendungen in der Elektronik oder im Bereich der Photovoltaik auch kleine Mengen von im Nanowire vorhandenem Gold Probleme verursachen können, wird auch an anderen Katalysatoren geforscht. Als alternative Katalysatoren für das Wachstum von Silizium-Nanowires werden auch Kupfer, Platin, Aluminium, Nickel oder Silber verwendet. [24], [25] Um ein Nanowirewachstum für diese verschiedenen Materialien zu ermöglichen, müssen vor allem die Wachstumsparameter Temperatur sowie Gaszusammensetzung und Druck angepasst werden. [25]

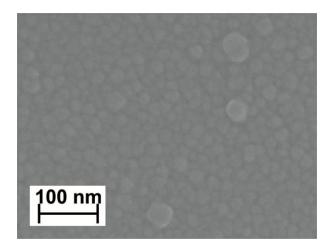

Der Katalysator kann auf unterschiedliche Arten aufgebracht werden. Für großflächiges Nanowirewachstum wird zumeist eine durchgehende Goldschicht auf die Substratoberfläche, mittels Aufdampfen oder Aufsputtern aufgebracht. Bei Verwendung einer aufgedampften oder aufgesputterten Goldschicht entstehen die für das Wachstum von einzelnen Nanodrähten erforderlichen vereinzelten Gold-Cluster durch thermische Behandlung der Schicht. Die durchgehende Goldschicht wird vor dem Wachstum bei Temperaturen um 773 K getempert. Dadurch entstehen vereinzelte Goldtropfen, deren Größe von der Dicke der zuvor aufgebrachten Schicht abhängt. Die Position der Nanowires kann durch lithographische Strukturierung des Katalysators bestimmt werden.[20] Gold, in Form von einzelnen Clustern, kann als Aerosol oder in flüssiger Lösung auf die Probe aufgebracht werden.

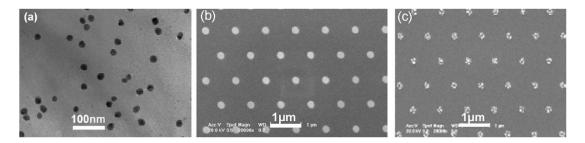

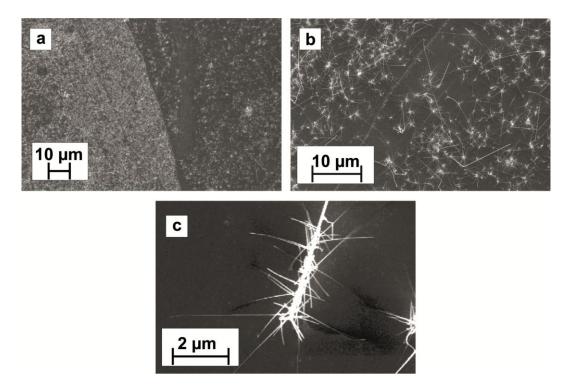

Abbildung 6 zeigt drei, durch Tempern einer gesputterten Goldschicht entstandene Katalysatorverteilungen. Teilbild a zeigt das Ergebnis eines Tempervorganges mit einer durchgehenden Goldschicht. Die Anordnung der Au Cluster auf der Oberfläche ist willkürlich verteilt. Die in Abbildung b gezeigte Verteilung wurde durch lithographische Strukturierung der Goldschicht erzielt. Es ist deutlich eine regelmäßige Verteilung von soliden Goldpartikeln annähernd gleicher Größe zu erkennen, welche zu ebenso angeordneten Nanowires führen würden. Die in Teilbild c erzeugte Struktur wurde auf dieselbe Weise erzeugt wie jene in Abbildung b. Die Dicke der aufgesputterten Goldschicht war jedoch dünner. Durch Tempern der besputterten Struktur brechen die zuvor definierten Goldflächen in einzelne, kleinere Au Tropfen auf. Dies hat zur Folge dass bei einem anschließenden Nanowirewachstum mehrere kleine Nanowires entstehen würden.

Abbildung 6: Durch Tempern einer Goldschicht entstandene Gold-Cluster. [20]

- a) Golkluster nach Tempern einer durchgehenden Goldschicht.

- b) Gold-Cluster nach Tempern einer mittels E-Line vorstrukturierten Goldschicht.

- c) Vorstrukturierte Goldschicht welche aufgrund einer zu dünnen Goldschicht weiter zu kleineren Goldtropfen aufgebrochen ist.

#### 2.3.2.2 Einfluss der Prozesstemperatur auf das Nanowirewachstum

Der gezielte Wachstumsprozess von einzelnen Nanowires mittels des VLS Prozesses ist auf Grund der relativ niedrigen Aktivierungsenergie der Reduktionsreaktion von Silan am Katalysator, im Vergleich zur notwendigen Energie für die direkte, unkatalytische Schichtabscheidung auf dem Substrat aus der Gasphase, möglich. So findet die Reaktion von SiCl<sub>4</sub> mit H<sub>2</sub>, ohne Einfluss eines Katalysators, erst bei Temperaturen über 1073 K statt. Darunter wird beinahe kein Silizium auf dem Substrat abgeschieden. Unter Einfluss eines Katalysators wird diese Reaktionstemperatur erheblich verringert. Wodurch sich der Katalysator schon bei niedrigeren Temperaturen mit Si übersättigt und damit Nanowirewachstum durch Ausfällen von Si an der Grenzschicht zwischen Katalysator und Substrat einstellt.[20]

Durch gezielte Regelung der Temperatur kann auch die Form der Nanowires beeinflusst werden. Beim Wachstum von Si Nanowires in Silan Atmosphäre bei einem Druck von ca. 5 mbar können durch erhöhen der Temperatur Si Nanowires in Kegelform hergestellt werden. Bei einer Wachstumstemperatur von unter 823 K wachsen die Nanowires gleichmäßig, ohne Abnahme des Durchmessers während des Wachstums. Wird die Wachstumstemperatur, bei gleichbleiben der anderen Wachstumsparameter weiter erhöht, verkleinert sich der Katalysatortropfen ausgehend von einer ursprünglichen Größe von 50 nm im Laufe des Wachstums und damit auch der Nanowire Durchmesser. Aufgrund der hohen Temperaturen kommt es aber auch zu unkatalytischer Abscheidung von Si auf der Nanowireoberfläche, wodurch konische Nanowires entstehen. Der Durchmesser des Nanowires am Übergang zum Substrat ist deshalb wesentlich Größer als der ursprüngliche Katalysatortropfen. Bei einer Temperatur von 923 K hat sich der Goldkatalysatorpartikel an der Spitze des Nanowires nach dem Wachstum auf eine Größe von 5 nm, bei einer weiteren Erhöhung der Temperatur auf 973 K auf 3 nm verkleinert. Die Verkleinerung des

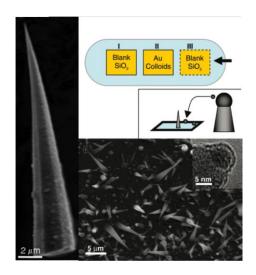

Katalysators während des Wachstums kann auf zwei Mechanismen zurückgeführt werden. Während des Wachstums werden Au Atome in den Nanowire eingebaut wodurch sich die Masse des Katalysators verringert. Bei einer energiedispersiven Röntgenspektroskopie (EDX) Messungen wurde allerdings nur große Mengen Au an der Spitze des Nanowires nachgewiesen und nur geringe Spuren im Rest des Nanowiresires. Eine weitere Möglichkeit für das Verschwinden des Goldes ist das Abdampfen des Katalysators während des Wachstums. Um dies Nachzuweisen wurde, eine mit Goldkolloiden versehene Probe während des Wachstums zwischen zwei, mit SiO<sub>2</sub> beschichtete Proben platziert. Der schematische Aufbau des Versuches ist in Abbildung 7 im rechten oberen Teilbild zu sehen. Nach Abschluss des Wachstumsprozesses waren sowohl auf der in Gasflussrichtung liegende als auch auf der, entgegen dem Gasfluss liegenden Probe Au-Katalysierte Nanowires nachzuweisen. Dies lässt darauf schließen dass das Gold von der, in der Mitte der drei Proben liegenden, mit Gold besputterten Probe über die Gasphase auf die zwei anderen Proben gelangt ist. In der folgenden Abbildung 7 ist das Ergebnis für Si Nanowirewachstum bei einer Temperatur von 923 K gezeigt. Im linken Bild ist ein Nanowire zu sehen, welcher mit einem 20 nm großen Katalysatortropfen gewachsen wurde. Es ist deutlich die konische Form des Nanowires zu sehen, welche auf die unkatalytische Abscheidung von Si auf der Oberfläche des Nanowires während des Wachstums bei sehr hohen Temperaturen zurückzuführen ist. In den rechten zwei Teilbildern sind die Versuchsanordnung für den Nachweis der Katalysatorübertragung über die Gasphase sowie das daraus resultierende Wachstumsergebnis zu sehen.[26]

Abbildung 7:Bei hohen Temperaturen mit Au-Kolloiden gewachsene Si-Nanowires.[26]

*links:* Durch unkatalytische Abscheidung von Si an der Nanowireoberfläche konisch gewachsener Nanowire. Der ursprüngliche Au-Katalysator hatte einen Durchmesser von 20 nm.

rechts oben: schematischer Versuchsaufbau zum Nachweis von Katalysatorschwund über die Gasphase.

rechts unten: Wachstumsergebnis auf der nicht mit Kolloiden versehenen Probe I

#### **Subeutektisches Nanowirewachstum**

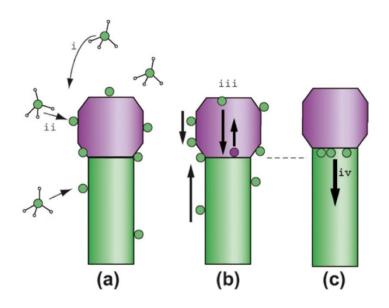

Die folgende Abbildung 8 zeigt den schematischen Ablauf des VSS – Prozesses. Das Precursor Gas zersetzt sich am Katalysator, bzw. an der Substratoberfläche. Da die, für das Halbleiterwachstum notwendige Energie aber nur durch die Abscheidungsenergie verringernde Wirkung des Katalysators möglich ist, müssen die abgeschiedenen Atome zur Katalysator-Halbleiter-Grenze diffundieren. Dort werden sie in den wachsenden Halbleiterkristall eingebunden und bewirken somit ein Anheben des Katalysators.[27]

Abbildung 8: Schematische Darstellung des VSS Wachstums von Nanowires. Der Precursor zersetzt sich am Katalysator und das Material diffundiert entlang der Oberfläche, und/oder durch den Katalysators hindurch. [27]

Das Nanowirewachstum ist auch bei Temperaturen unter dem eutektischen Punkt möglich. Der Katalysator ist in diesem Fall in fester Form vorhanden. Das auf diesem Prozess basierende Wachstumsverfahren wird Vapour-Solid-Solid Verfahren (VSS-Verfahren) genannt. Der Vorteil dieses Verfahrens ist, dass das Wachstum auch bei niedrigeren Temperaturen durchgeführt werden kann, welche nur hoch genug sein müssen, damit der verwendete Precursor am Katalysator aufgespalten werden kann. Der Precursor wird dabei, genauso wie beim VLS Verfahren in Gasform in den Wachstumsreaktor eingeblasen. Es zersetzt sich bevorzugt am Katalysator und wandert dann, durch Diffusion an der Oberfläche, oder durch den kristallinen Katalysator hindurch zur Substratoberfläche. Metallpartikel haben im Allgemeinen die Eigenschaft, dass sie, unabhängig von ihrem Aggregatszustand, die kinetische Barrieren-Energie, welche für das Halbleiterwachstum überwunden werden muss,

verringern.[27] In manchen Fällen kommt es auch zu einer Vermischung des VSS und des VLS Verfahrens, bei dem ein kristalliner KatalysatorKern von flüssigem Material umhüllt ist. In diesem Fall kommt das Wachstum durch ein vermischen der Prozesse zustande.

Die Temperatur hat starken Einfluss auf die Zersetzung des Precursors und somit auch auf Anzahl und Form der entstehenden Nanowires. Im Beispiel von Si Nanowires, die mittels 2 nm dicker, aufgesputterter Goldschicht mit Octochlorotrisilane als Precursor auf Si Substrat gewachsen werden, ist dies ersichtlich. Bei Temperaturen von 1173 K bis 873 K sinkt die Anzahl der Nanowires per Fläche sowie deren Länge von ca. 8 µm auf 1 µm. Der Durchmesser der Drähte schwankt ebenso in Abhängigkeit der Temperaturen. Bei hohen Temperaturen von 1173 K stellt sich ein dichtes Nanowirewachstum ein, wobei die Drähte viele Knicke aufweisen. Bei einer Verringerung auf 1073 K verringert sich die Anzahl der geknickten Nanowires und die Läng und der Durchmesser der Nanowires werden gleichmäßiger. Bei den alternativen, im vorhergehenden Kapitel erwähnten Precursor Materialien ist ein Wachstum auch unterhalb der eutektischen Temperatur möglich. Es wird angenommen, dass in diesem Fall der Katalysatorpartikel während des Wachstums im festen Zustand bleibt und das Wachstum auf einer Diffusion im Katalysatorpartikel beruht.[25]

#### 2.3.2.3 Einfluss des Prozessdrucks auf das Nanowirewachstum

Der Druck in der Prozesskammer während des Nanowirewachstums beeinflusst sowohl die Wachstumsgeschwindigkeit als auch die Wachstumsrichtung.[23],[28]

#### Druckabhängigkeit der Wachstumsgeschwindigkeit

Die Wachstumsgeschwindigkeit hat mehrere limitierende Faktoren, welche mit der Wachstumstemperatur und dem Wachstumsdruck zusammenhängen. Das Wachstum kann durch Änderung des Partialdruckes des Precursors gesteuert werden. Bei niedrigem Partialdruck ist der, die Wachstumsgeschwindigkeit bestimmende Faktor Siliziumzufuhr aus der Gasphase. Bei ausreichend hohem Partialdruck sind beliebig viele Silan Moleküle an der Oberfläche vorhanden und das Wachstum wird durch die Zersetzung des Precursors an der Katalysatoroberfläche und die Diffusion in den Katalysator bestimmt. Beides hängt vom verwendeten Precursor und der Wachstumstemperatur ab. Beim Wachstum von Silizium Nanowires bei einer konstanter Temperatur von 873 K, Verwendung von Silan als Precursor und einer 20 nm dicken, auf Si(111) Substrat aufgesputterten Goldschicht zeigen sich die eben erwähnten beschränkenden Mechanismen. Bei einem Druck von 10 mbar stellt sich eine Wachstumsgeschwindigkeit von unter 0,1 µm/minute ein, welcher mit

zunehmendem Wachstumsdruck linear ansteigt. Die Länge andert sich mit 2,5\*10<sup>-4</sup> μm/(min\*mbar) und ist auf eine Erhöhung der Precursor zufuhr zum Katalysator aus der Gasphase zurückzuführen.[28] Bei einem Druck von ca. 60 mbar kommt es bei 1,5 μm/min zu einer Sättigung der Wachstumsgeschwindigkeit und ein weiteres Erhöhen des Druckes hat keine Auswirkung mehr auf die Wachstumsgeschwindigkeit. Dies ist auf die, bei der verwendeten Temperatur limitierte Zersetzung des Precursors auf dem Katalysatortropfen zurückzuführen.[28]

#### Druckabhängigkeit der Wachstumsrichtung

Durch die Veränderung des Druckes innerhalb des CVD Reaktors während des Wachstums ist es für das betrachtete System möglich, eine gezielte Änderung der Wachstumsrichtung der zu erreichen. Im Fall von Si kann der Druck während des Wachstums, bei ansonsten gleichbleibenden Bedingungen, zwischen 3 mbar und 15 mbar variiert werden. Dabei ändert sich die Wachstumsrichtung der Nanowires. [23] Bei einem Druck von 3 mbar weisen die meisten Nanowires eine <111> Orientierung auf. Als bevorzugte Wachstumsrichtung bei 15 mbar stellt sich <112> ein. Bei einer Änderung des Druckes während des Wachstums von 3 mbar auf 15 mbar ist eine abrupte Änderung der Wachstumsrichtung erkennbar. Das Wachstum bei 15 mbar ist dabei mit einer Wachstumsgeschwindigkeit von 250 nm/min im Vergleich zu 33 nm/min bei 3 mbar wesentlich schneller. Der Grund dafür ist, dass die Zufuhr des Si aus der Gasphase der limitierende Faktor für das Wachstum ist. [23]

#### 2.3.3 Epitaxie

Unter Epitaxie versteht man ganz allgemein das monokristalline Aufwachsen von Kristallschichten auf einen Substratkristall, wobei die Kristallstruktur des Wirtskristalls in der aufgebrachten Schicht beibehalten wird. Je nach Zusammensetzung des Materials unterscheidet man zwischen Homoepitaxie Heteroepitaxie. Ist das abzuscheidende Material das Selbe wie das Substrat auf welches aufgewachsen wird, so spricht man von Homoepitaxie, wenn sich das aufzuwachsende Material vom Substratmaterial unterscheidet handelt es sich um Heteroepitaxie. Abscheidung Halbleitermaterials kann bei vielen Die des Materialkombinationen, durch Einstellen der Prozessparameter, gut kontrolliert werden. Dadurch ist ein gezieltes Dotieren, oder durch Variation des aufzubringenden Materials, auch eine Bildung von komplexen Heterostrukturen möglich. Im Idealfall bilden sich in der aufgewachsenen Schicht keine zusätzlichen Gitterfehler aus. Direkt Übergangsfläche bleiben die bereits am Substrat vorhandenen Oberflächendefekte bestehen, werden aber innerhalb weniger Atomlagen kompensiert. Im Fall von heteroepitaktische aufgewachsenen Schichten können sich aufgrund

unterschiedlicher Gitterkonstanten Verspannungen aufbauen, welche zur Zerstörung der Strukturen führen können. Bei Nanowire-Heterostrukturen können diese Verspannungen aufgrund des geringen Durchmessers leicht relaxieren. Somit sind auch Heterostrukturen von Materialien möglich, welche einen großen Unterschied in der Gitterkonstante haben und Schichtweise nicht abgeschieden werden könnten.[29] Verspannungen des Kristallgitters haben auch Einfluss auf die Bänderstruktur der Halbleiter und somit auch auf deren elektrischen und optischen Eigenschaften.[30], [20] Eine der interessantesten Kombinationen ist Silizium mit Galliumarsenid. Silizium ist der am meisten verwendete Halbleiter im Bereich der Mikroelektronik, mit auten Eigenschaften im Hinblick auf die Reinheit und Kristallinität, Prozessierbarkeit, Ladungsträgerbeweglichkeit und Wärmeleitfähigkeit. Galliumarsenid hingegen ist einer der bedeutendsten Halbleiter der Optoelektronik und hat durch seine höhere Elektronenmobilität auch einen wichtigen Stellenwert in der Fertigung von Hochgeschwindigkeits- Bauelementen. Um diese Vorteile kombinieren und nutzen zu können, ist es notwendig, einen abrupten und störstellenfreien Übergang zwischen den Materialsystemen zu realisieren. Im Fall des Si-GaAs Systems ist dieser epitaktische Übergang bei der Fertigung von ganzen Wafern aufgrund der Differenz der Gitterkonstanten, des thermischen Ausdehnungskoeffizienten und des Übergangs zwischen einem nicht polaren auf einen polaren Halbleiter im Schichtsystem nicht zu realisieren.[31]

#### 2.3.3.1 Epitaktisches Wachstum von Si Nanowires auf einem Si-Substrat

Für ein gezieltes epitaktisches Wachstum von Silizium Nanowires ist die Oberflächenbeschaffenheit des Si Substrates, auf welche die Nanowires aufgewachsen werden sollen, wichtig. Insbesondere muss die sogenannte native Oxidschicht entfernt und die Si Oberfläche H-terminiert sein. Beim Wachstum von Si-Nanowires mittels SiCl<sub>4</sub> als Precursor entsteht während des Wachstumsprozesses, durch das Zersetzen des Precursors am Au Katalysator in der Argon/Wasserstoff Atmosphäre, HCl als Reaktionsnebenprodukt. Die Salzsäure ätzt das native Siliziumdioxid während des Wachstumsprozesses von der Silizium-Oberfläche und sorgt so für eine saubere Kristalloberfläche. Auf dieser wachsen die Nanowires bevorzugt epitaktisch auf.[32]

Die Behandlung des Substrats vor dem Nanowirewachstum hat auch bei der Verwendung von Silan als Precursor einen starken Einfluss auf die Wachstumsdichte sowie auf die Epitaxie der Drähte. Die Behandlung des Substrates mit gepufferter Flusssäure erzeugt ebenfalls eine wasserstoffterminierte, oxidfreie Oberfläche. Nach dem Aufsputtern einer Goldschicht als Katalysator diffundiert das Si durch die Schicht und oxidiert schon bei Raumtemperatur mit dem Luftsauerstoff an der Oberfläche. Diese dünne Siliziumdioxid-Schicht blockiert die Diffusion von Si aus der Gasphase zum Katalysator und verhindert so ein Nanowirewachstum. Wird diese Oxidschicht vor

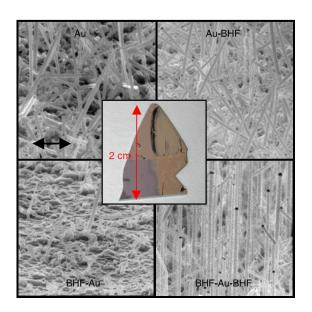

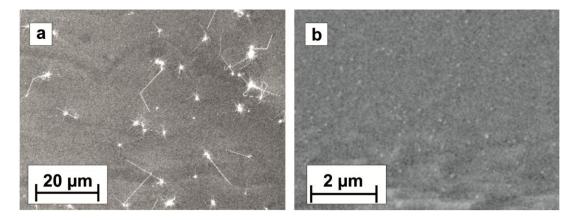

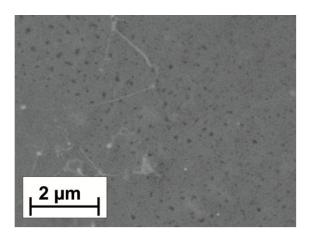

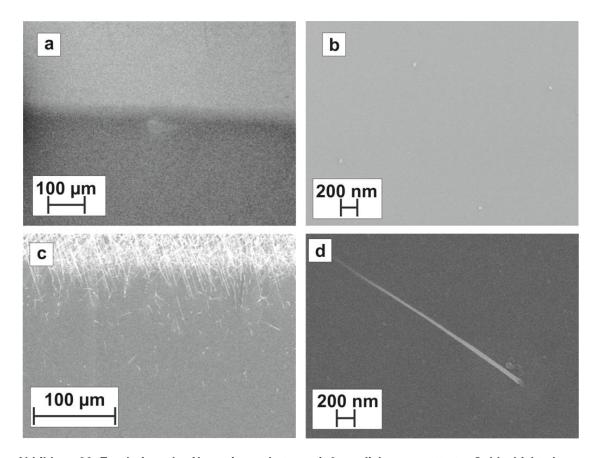

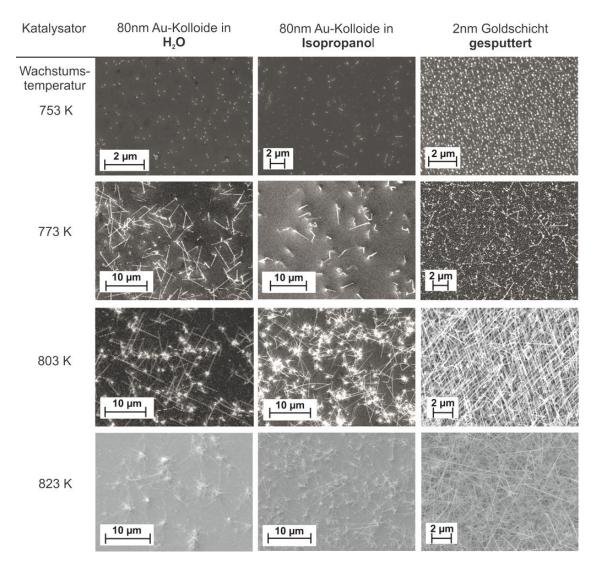

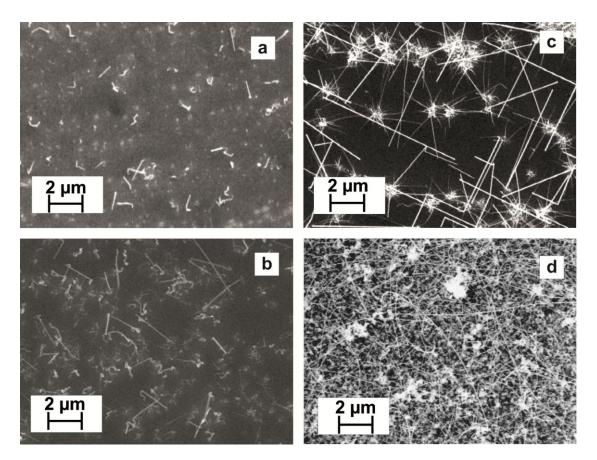

dem Wachstum wieder mit HF entfernt, stellt sich ein dichtes, epitaktisches Wachstum ein. Abbildung 9 zeigt eine Si Probe, bei der, durch unterschiedliche Behandlung mit gepufferter HF (BHF), vier Bereiche entstanden sind. Diese Unterscheiden sich dadurch, dass ein Teil, zu sehen im linken oberen Teilbild, vor dem Wachstum nicht mit HF behandelt wurde. Bei dem, links unten in der Abbildung zu sehenden Teil wurde nur eine Reinigung vor dem Aufsputtern der Goldschicht durchgeführt. Im Teilbild rechts unten wurde zusätzlich dazu auch eine kurze HF Behandlung nach dem Katalysator Auftrag durchgeführt. Die Aufnahme rechts oben in der Abbildung zeigt das Wachstum der Nanowires bei einer HF Reinigung nur nach aufsputtern der Au Schicht. [33] Wie man aus den erzielten Ergebnissen sieht, stellte sich das beste Wachstumsergebnis bei HF-Reinigung vor und nach Auftrag des Katalysators ein, da sowohl das Oxid zwischen Si und Au Schicht, als auch das auf der Goldschicht entstandene SiO<sub>2</sub> entfernt wurde.

Abbildung 9: SEM Aufnahme eines Si(111) Substrat auf welchem mittels aufgesputterter Au-Schicht Si Nanowires gewachsen wurden. Die Teilbilder zeigen die vier unterschiedlich behandelten Teilbereiche: li.o. Si ohne Reinigung mit BHF; li.u. Si mit BHF Reinigung vor aufsputtern einer Au Schicht; re.o. Reinigung mit BHF nach aufsputtern einer Au Schicht; re.u. Reinigung mit BHF vor und nach aufsputtern einer Au Schicht; Mitte Foto der Probe. [33]

#### Wachstumsrichtungen von Si Nanowires auf (100) und (111) orientierten Si-Substraten

Die Wachstums-Richtungen der Nanowires können, wie bereits zuvor erwähnt, durch die Wachstumsparameter, die Größe des Katalysators sowie durch die Substratorientierung beeinflusst werden. Für Silizium Nanowires auf Silizium

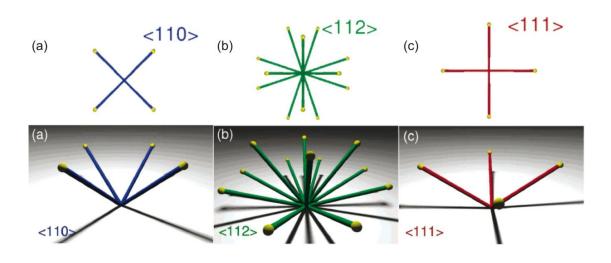

Substraten sind die bevorzugten Wachstumsrichtungen <111>, <110> und <112>. Weniger oft können auch die <100> Richtungen auftreten. Abbildung 10 zeigt schematische Bilder der drei bevorzugten Wachstumsrichtungen von Silizium Nanowires auf Silizium (100) Substraten. Die obere Bildreihe zeigt eine Aufsicht auf die Nanowires, wie sie bei Betrachtung normal zur Substratoberfläche zu sehen wäre. Die untere Zeile zeigt die Wachstumsrichtungen aus dem Blickwinkel der [-1-1-1] Richtung. Die Winkel zwischen Substratoberfläche und den Nanowires beträgt bei <110> Drähten 45°, bei <111> Drähten 35,3° und bei <112> Drähten 24,1° oder 35,5°.[22]

Abbildung 10: Schematische Abbildungen der drei bevorzugten Wachstumsrichtungen von Si Nanowires auf einem Si (100) Substrat. Die oberen Bilder zeigen eine Aufsicht der Probe, die untere Reihe zeigt eine Ansicht aus der [-1-1-1] Richtung. [22]

Auf (111) orientiertem Substrat gibt es hingegen vier Möglichkeiten für <111> orientierte Nanowires. Drei dieser Richtungen haben in der Aufsicht einen Winkel von 120° zueinander und einen Winkel von 19,5° zur Substratoberfläche. Die vierte Richtung steht in einem Winkel von 90°, normal zur Substratoberfläche. Ein gezieltes Wachsen der, für viele Anwendungen bevorzugten, aufrecht stehenden Nanowires ist durch Anpassen des Partialdruckes von Silan während des Wachstums möglich. Aus Experimenten mit unterschiedlichen Silan-Partialdrücken zeigt sich, dass die Anzahl der senkrecht stehenden Nanowires bei Partialdrücken unter ca. 0,2 mbar ansteigt. Der Anstieg ist bei Drähten mit unterschiedlichen Durchmessern zwischen 60 – 105 nm ersichtlich. Bei einer Erhöhung des Silananteiles verringert sich die Anzahl der aufrecht stehenden Nanowires und bei einem Partialdruck von ca. 0,5 mbar weisen beinahe alle Drähte einen Knick und ein anschließendes Wachstum in eine der anderen drei <111> Richtungen auf. Für höhere Wachstumstemperaturen von 873 K ist die Anzahl an

senkrecht stehenden Drähten ebenfalls verringert und steigt mit sinkender Temperatur an. Für eine optimale Ausbeute von senkrecht stehenden Nanowires sind ein Silan-Partialdruck von unter 0,1 mbar und Wachstumstemperaturen von weniger als 748 K notwendig.[34]

#### 2.3.3.2 Heteroepitaxie von Nanowires

Die Erzeugung von Nanowire-Heterostrukturen ist beim VLS Verfahren durch einfaches Umstellen des Precursorgases möglich. Ein Atomar scharfer Übergang von einem Ausgangsmaterial auf ein anderes ist aber aufgrund der noch im Katalysator vorhandenen Atome des Ausgangsmaterials nicht möglich. Durch das Vermischen der beiden Materialien innerhalb des Katalysators entsteht an der Heteroübergangsfläche ein kontinuierlicher Verlauf über eine bestimmte Dicke. Diese ist abhängig von der Zusammensetzung der Legierung aus Katalysator und Abzuscheidendem Material, welche aus dem Phasendiagramm ermittelt werden kann. Im Fall von Au-Si beträgt der Si Anteil in der Legierung etwa 19% Si. Die Größe der Übergangszone ist sowohl von den verwendeten Halbleitern, den Prozessparametern als auch vom Durchmesser des Nanowires abhängig. Ausnahmen bilden nur einige Materialkombinationen der III-V Halbleiter, bei denen ein scharfer Übergang bereits gezeigt werden konnte.[20]

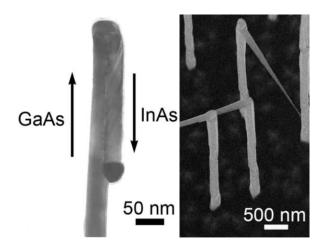

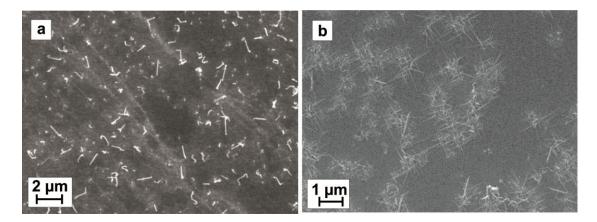

Ein weiteres Problem, das bei der Erzeugung von Nanowire Heterostrukturen auftreten kann, ist eine Änderung der Wachstumsrichtung am Übergang. Dies kann Knicke oder sogar abwärts wachsende Nanowires erzeugen. Beim Wachstum von Indiumarsenid (InAs) auf einem bestehenden GaAs Nanowire mittels VLS Mechanismus und Gold als Katalysator zeigt sich ein solches "rückwärts gerichtetes Wachstum" der Nanowires.

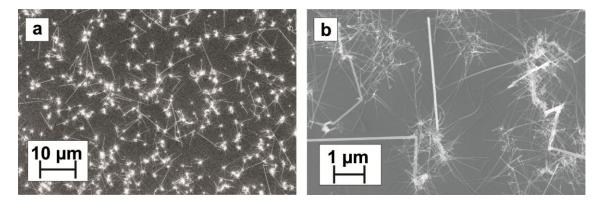

Abbildung 11: Wachstumsverhalten eines GaAs-InAs Heterostruktur-Nanowires. [35] links: TEM Aufnahme nach 1 min InAs Nanowirewachstum. rechts: SEM Aufnahme nach 30 min InAs Nanowirewachstum.

Die Änderung der Wachstumsrichtung ist energetisch betrachtet vorteilhafter. Die Grenzflächenenergie zwischen dem Au Katalysator und dem GaAs ist wesentlich geringer als die Grenzflächenenergie zu InAs. Dies bewirkt, dass sich der Goldtropfen beim Umstellen der Wachstumsparameter von GaAs auf InAs am GaAs Naowire entlang nach unten bewegt und so der InAs Nanowire dicht anliegend nach unten wächst. Zeitgleich findet jedoch eine unkatalytische InAs Abscheidung an der GaAs Nanowireoberfläche statt und bedeckt die Drahtoberfläche. Durch diese radiale Ablagerung wird das Abwärtswachstum gestoppt. Der Goldpartikel löst sich von der beschichteten GaAs Oberfläche und das Wachstum des InAs Nanowires setzt sich in Richtung <111>B fort. Abbildung 11 zeigt zwei solche Heterostruktur-Nanowires in unterschiedlichen Wachstumsstadien. Es wurde in beiden Teilbildern auf den zuvor gewachsenen GaAs Nanowire ein InAs Nanowire aufgewachsen. Die Wachstumsdauer des InAs Nanowires beträgt im linken Bild eine Minute. Man sieht deutlich, dass der InAs Nanowire entlang des bereits bestehenden GaAs Nanowires abwärts wächst. Das linke Teilbild zeigt eine solche Heterostruktur nach 30 Minuten InAs Nanowirewachstum. Nach anfänglichem kriechendem Wachstum löst sich der Goldkatalysator von der Oberfläche und bildet einen frei abstehenden Nanowire.[35]

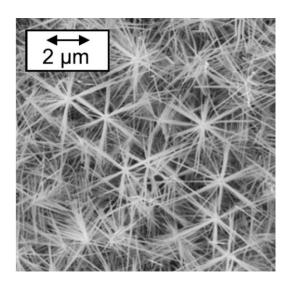

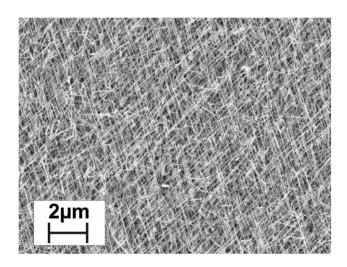

Epitaktisches Wachstum von Halbleiter-Heterostrukturen ist aber auch durch die Kombination von unterschiedlichen Wachstumsverfahren möglich. Im Fall des Silizium-Galliumarsenid Systems können durch gestaffeltes Wachstum von Si Nanowires mittels VLS Verfahren und anschließendem Weiterwachsen von GaAs Nanowires mittels Molekular Strahl **Epitaxie** (engl. molecular-beam-epitaxie, dreidimensionale Gebilde erzeugt werden. Die Si Nanowires in <111> Richtung weisen eine sechseckige Form, begrenzt von (112) orientierten Facetten auf. Auf diesen Facetten findet bevorzugt das Wachstum der GaAs Nanowires in Wurzit-Gitter-Form statt. Die Drähte wachsen epitaktisch in [0001] Richtung, parallel zu den {112} Seitennormalen des Si Hauptdrahtes. Abbildung 12 zeigt eine SEM Aufnahme einer solchen Heterostruktur. Es sind die, in sechseckiger Anordnung wachsenden GaAs Nanowires zu sehen. Im Zentrum dieser Struktur befindet sich der Si Nanowire. Die so erzeugte Halbleiter-Heterostruktur eines IV und III-V Halbleiters ist interessant für weitere Forschung im Gebiet von Hochgeschwindigkeits- sowie optoelektronischen Bauelementen.[19]

Abbildung 12: Si-GaAs-Heterostruktur erzeugt durch Si Nanowirewachstum mittels VLS Verfahren gefolgt von MBE GaAs-Nanowirewachstum. [19]

#### Nanowire-Heteroepitaxie bestimmende Größen

Um eine gezielte Integration von Nanowires in elektronische Bauelemente zu ermöglichen, muss die epitaktische Wachstumsrichtung kontrollierbar sein. Beim Wachstum von Nanowires bestimmen die Grenzflächenenergien zwischen Precursor und Katalysator sowie Katalysator und Substratoberfläche die Wachstumsrichtung. Je nach Vorzeichen der Energiedifferenzen stellt sich bevorzugt Schicht- oder Insel-Wachstum ein. Diese Differenz ändert sich bei Vertauschen der Materialreihenfolge und somit ändert sich auch das Wachstumsverhalten. Beim Aufwachsen von Silizium oder Germanium auf Galliumarsenid ergibt eine solche Berechnung, dass sich Inselwachstum einstellen wird. Dieses Ergebnis wird auch in der Praxis bestätigt und bewirkt ein geknicktes Wachstum. Die Keimbildung an einer lokalen Stelle des Träger-Nanowires und dessen anschließende Vergrößerung bewirkt ein Verdrängen des Goldkatalysators entlang der GaAs Oberfläche und so ein kriechendes Wachstum entlang des Träger-Drahtes oder ein weiterwachsen in verändertem Winkel.[29]

## 2.4 Elektrische Eigenschaften von Halbleiter-Übergängen

Als Halbleiter-Übergang wird ein Wechsel zwischen zwei halbleitenden Materialien mit unterschiedlichen Eigenschaften bezeichnet. Dies können sowohl Übergänge zwischen zwei unterschiedlich dotierten Bereichen desselben Halbleiters (z.B. p-n Übergang in Silizium), Übergänge zwischen Materialien mit einer geringen Änderung der chemischen Zusammensetzung (z.B. GaAs – Al<sub>x</sub>Ga<sub>1-x</sub>As), aber auch Übergänge

zwischen unterschiedlichen Halbleitern sein (z.B. Silizium – Galliumarsenid Heteroübergang).

Durch optimierte Herstellungsprozesse ist die Erzeugung von abrupten Übergängen für manche Materialkombinationen beinahe ideal herstellbar.[36] Der p-n Übergang ist einer der wichtigsten Grundbausteine für die moderne Mikroelektronik und ist die Grundlage für viele Bauelemente, wie z.B. Dioden oder Transistoren. Halbleiter-Heteroübergange sind eine wichtige Grundlage im Bereich der Optoelektronik, für die Herstellung von Foto-Detektoren und Lasersystemen sowie für die Herstellung von Hochgeschwindigkeitstransistoren.

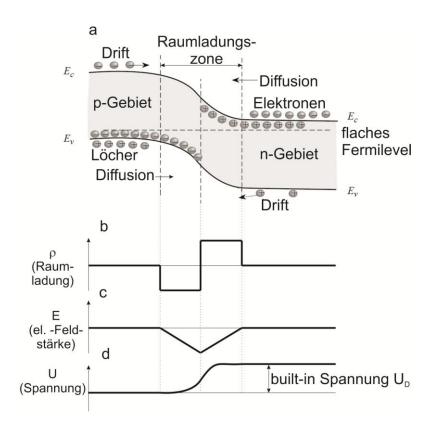

#### 2.4.1 Der pn Übergang

Als p-n Übergang bezeichnet man den Übergang von einem p-dotierten Gebiet zu einem n-dotierten Gebiet innerhalb eines Halbleiters. Er ist eine der wichtigsten Anordnungen in der Halbleiterelektronik und wird in Form eines elektronischen Bauteils als p-n Diode bezeichnet. Führt man in einem Gedankenexperiment, einen idealen Halbleiter mit konstant dotiertem p-Gebiet zu einem ebenfalls konstant dotierten n-Gebiet, bildet sich an der Kontaktzone anfänglich kein elektrisches Feld aus. Durch das Ladungsträgerungleichgewicht, am Übergang zwischen den unterschiedlich dotierten Zonen, stellt sich ein Diffusionsstrom ein, welcher Elektronen in das p-dotierte Gebiet und Löcher in das n-dotierte Gebiet strömen lässt. Dieser Ausgleichsstrom führt zu einer Ladungsträgerverarmung an den beiden Randgebieten der Kontaktzone. Die über die Grenze fließenden Elektronen besetzen die im p-Gebiet vorhandenen Löcher der Akzeptoren und hinterlassen im Randgebiet des n-dotierten Gebiets die positiv geladenen Donatoren. Eine analoge Betrachtung der Ausgleichsvorgänge ist auch für die Löcher der p- dotierten Seite möglich. Durch die positive bzw. negative Aufladung der Grenzschicht baut sich am Übergang eine hochohmige Verarmungszone auf. In dieser sogenannten Raumladungszone (RLZ) bildet sich damit ein elektrisches Feld aus, welches dem Diffusionsstrom entgegen wirkt. Der Fluss der Ladungsträger ins jeweilig anders dotierte Gebiet findet nun so lange statt, bis das sich aufbauende elektrische Feld die Diffusion zum Erliegen bringt.[9] Im ausgeglichenen Zustand hat sich zwischen den Rändern der Raumladungszone ein Potentialunterschied gebildet, welcher als Built-in-Spannung oder Diffusionsspannung bezeichnet wird. Dieser Potentialunterschied hat eine Verschiebung der Energiebänder der unterschiedlich dotierten Gebiete zur Folge, welche soweit geht, bis sich ein einheitliches Ferminiveau im gesamten Gebiet eingestellt hat. Das Maximum der elektrischen Feldstärke liegt genau an der Grenzfläche zwischen den unterschiedlich dotierten Gebieten. Die folgende Abbildung 13 zeigt schematisch die Bandverbiegung der Zonen sowie den Verlauf der Raumladung, des elektrischen Feldes und der Spannung in der Kontaktzone.[37]

Abbildung 13: Schematischer Verlauf des Energiebandschemas, der Raumladungszone und des elektrischen Feldes eines p-n Übergangs.

- (a) Verbiegung der Energiebänder im Übergangsbereich von p- auf n- dotierten Bereich. [37]

- (b) Verlauf der Raumladung im Kontaktbereich.

- (c) Verlauf des elektrischen Feldes in der RLZ.

- (d) Built-in-Spannung des pn-Übergangs.

Im Fall einer angelegten äußeren Spannung U<sub>e</sub> an den p-n Übergang kommt es zu einer weiteren Verbiegung der Energiebänder um e\*U<sub>e</sub>. Im Fall eines in Sperrrichtung gepolten p-n Übergangs liegt das höhere Potential an der n-dotierten Seite der Diode. Dadurch werden weitere Ladungsträger vom Rand der Raumladungszone in den neutralen Teil des dotierten Halbleiters hinein gesaugt, was eine weitere Verbreiterung der Raumladungszone bewirkt. Dies hat ein weiteres Auseinanderziehen der Energiebänder der beiden Zonen zur Folge.

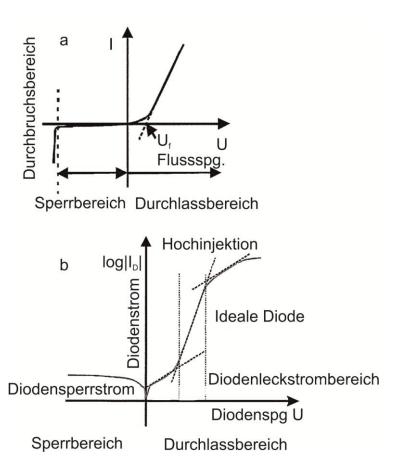

Bei einer Polung der Diode in Durchlassrichtung liegt das höhere Potential an der p-dotierten Seite der Diode und das negativere Potential an der n-dotierten Seite an. Ein steigender Potentialunterschied bewirkt eine Verkleinerung der Raumladungszone. Ist diese vollständig abgebaut, stellt sich ein exponentieller Stromanstieg ein. In der

folgenden Abbildung 14 werden schematische Darstellungen einer Diodenkennlinie, in a) linearer und b) in halblogarithmischer Darstellung mit den jeweiligen Arbeitsbereichen, gezeigt.

Abbildung 14: Exemplarische Darstellung einer Dioden-Kennlinie.

a) Kennlinie einer idealen Diode.

b) Vergleich einer idealen/realen Dioden-Kennlinie in halblogarithmischer Darstellung. [38]

Die Diffusionsspannung  $U_D$  (siehe Abbildung 13) hängt bei der Diode von den Dotierungen in p-Gebiet und n-Gebiet ( $N_D$ ,  $N_A$ ...Dichten der Donatoren, Akzeptoren) sowie von der Betriebstemperatur (T) ab. Weiters fließen in die Berechnung auch die Elementarladung eines Elektrons (e) und die Bolzmannkonstante (k) ein.  $U_D$  kann nach folgender Formel berechnet werden[9]:

$$U_D = \frac{k * T}{e} * \ln \left( \frac{N_A * N_D}{n_i^2} \right)$$

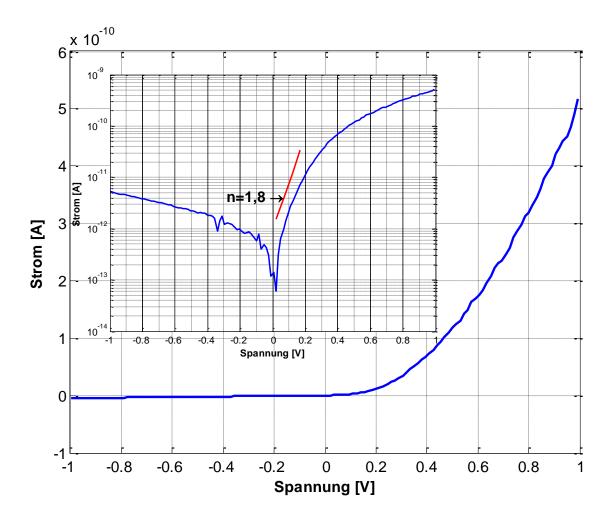

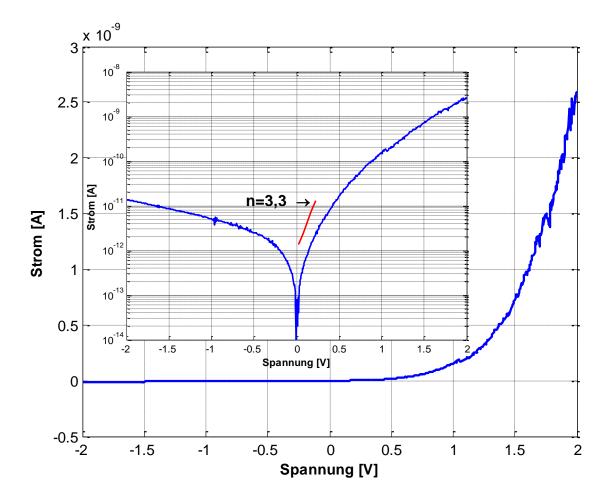

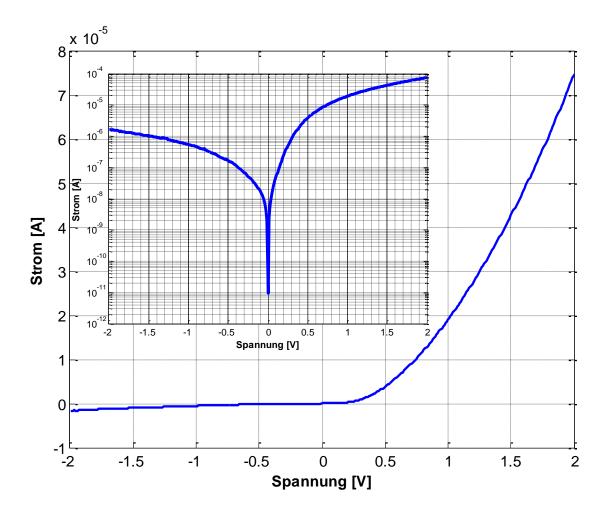

Der Diodenstrom I verläuft exponentiell und ist von der Temperatur T, der angelegten Spannung U sowie vom Diodensperrstrom I₀ abhängig.[39]

$$I = I_0 * (e^{\frac{e*U}{n*k*T}} - 1)$$

Bei der realen Diode weicht das Strom - Spannungsverhalten aufgrund verschiedener Mechanismen von dem, der idealen Diode ab. Diese Abweichungen werden durch eine Vergrößerung des Idealitätsfaktors berücksichtigt. Bei herkömmlichen p-n Dioden liegt n zwischen eins und zwei. Der Idealitätsfaktor n ist bei der idealen Diode gleich eins. Der Sättigungs-Sperrstrom  $I_0$  wird durch die Querschnitts-Fläche des Verarmungsgebiets A, durch die Diffusionskonstanten für Löcher  $(D_P)$  und Elektronen  $(D_N)$ , die Diffusionslänge der Minoritätsladungsträger im n-  $(L_P)$  und im p-  $(L_n)$  Gebiet, durch die Akzeptoren-  $(D_P)$  und Donatoren-  $(D_n)$  Dichte sowie durch die intrinsische Ladungsträgerdichte  $n_i$  bestimmt.

$$I_0 = e * A * n_i^2 * (\frac{D_N}{L_N * N_A} + \frac{D_P}{L_P * N_D})$$

Bei ungleicher Dotierung der beiden Gebiete des p-n-Übergangs kann I<sub>0</sub> vereinfacht werden, da der Bereich mit geringerer Dotierung eine wesentlich größere Anzahl an Minoritätsladungsträgern hervorbringt und somit in der Gleichung für I<sub>0</sub> dominiert. Der Sättigungssperrstrom ist auch stark von der Temperatur abhängig, da die intrinsische Ladungsträgerdichte n<sub>i</sub> exponentiell mit der Temperatur ansteigt. Die Größe von n<sub>i</sub> ist bei Raumtemperatur von der Bandlücke im jeweiligen Halbleiter abhängig.[39]

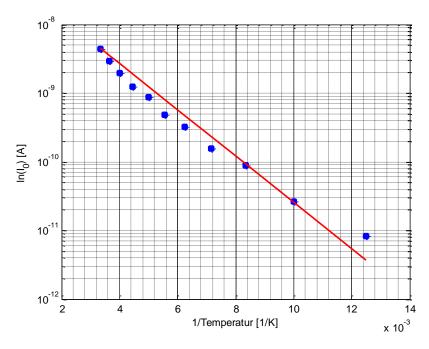

Es kann angenommen werden, dass bei relativ geringen Durchlass-Spannungen der Ladungsträgertransport in einer Diode durch Tunnelprozesse bestimmt wird. Der Sättigungs-Sperrstrom  $I_0$  weist dadurch eine exponentielle Proportionalität von der Temperatur auf, welche in der folgenden Formel angegeben ist:

$$I_0 \propto A * e^{\frac{-\Delta E_A}{k * T}}$$

Man sieht aus der Formel, dass  $I_0$  nur von einer temperaturunabhängigen Konstante A, der Bolzmannkonstante k, der Temperatur T und einer Aktivierungsenergie  $\Delta E_A$  abhängt. Die Größe  $\Delta E_A$  ist die Aktivierungsenergie der Ladungsträger bei in Flussrichtung gepoltem pn-Übergang.[40],[41]

#### 2.4.2 Der Halbleiter-Heteroübergang

Als Heteroübergang bezeichnet man, wie bereits erwähnt, einen Übergang zwischen zwei verschiedenen Halbleitern. Eine Möglichkeit, Heteroübergänge und deren Eigenschaften zu charakterisieren, ist die Einteilung aufgrund der Lage der

Energiebänder bzw. der Bandlücke der beteiligten Materialien. Dabei wird zwischen folgenden drei Typen unterschieden:

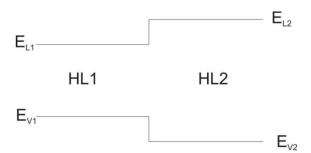

- Typ I (gespreizte Bandlücke)

- Typ II (gestufte Bandlücke)

- Typ III (unterbrochene Bandlücke)

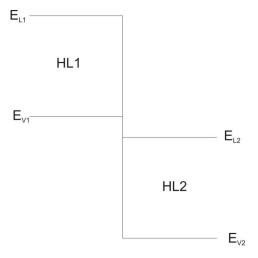

Bei der gespreizten Bandlücke treffen zwei Halbleiter mit, relativ zueinander, großer und kleiner Bandlücke zusammen. Eine schematische Zeichnung des Bänderschemas eines solchen Übergangs unter Flachbandbedingungen ist in Abbildung 15 gezeigt. Dies bedeutet, dass die, durch den Ausgleich des Ferminiveaus über den gesamten Bereich hervorgerufene, Bandverbiegung an der Kontaktstelle vernachlässigt wird. Werden die beiden Halbleiter miteinander verbunden, so liegt im Fall des Typ I Heteroübergangs sowohl die Leitungsbandenergie (E<sub>L</sub>) als auch die Valenzbandenergie (E<sub>V</sub>) des ersten Halbleiters mit kleinerer Bandlücke (HL 1) im Bereich der Bandlücke des zweiten Halbleiters (HL 2). Beim Übergang von HL 1 auf HL 2 wirkt, in dieser Art von Bänderanpassung, auf Elektronen und Löcher eine Potentialbarriere.

Abbildung 15: Bänderschema eines Typ I Heteroübergangs - Die Bandlücke des Halbleiters HL1 liegt vollständig innerhalb des verbotenen Bandes des Halbleiters HL2.

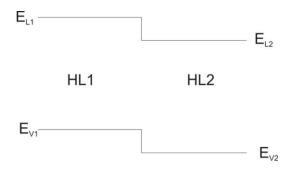

Beim Typ II Heteroübergang, dem gestuften Übergang, sind beide Energielevels  $E_L$  und  $E_V$  des ersten Halbleiters höher oder tiefer als die des zweiten Halbleiters. Beim Stromfluss über die Grenzfläche ist, je nach Lage des Energiebandes in Relation zu dem des zweiten Halbleiters, entweder für die Löcher oder für die Elektronen eine Energiebarriere sichtbar. In Abbildung 16 ist ein gestufter Übergang wieder unter Flachbandbedingungen schematisch dargestellt.

Abbildung 16: Bänderschema eines Typ II Heteroübergangs - Die Bandlücke des ersten Halbleiters liegt nur teilweise innerhalb der, des zweiten Halbleiters.

Als Typ III Halbleiter, dem Heteroübergang mit unterbrochener Bandlücke, wird ein Übergang verstanden, bei dem weder  $E_L$  noch  $E_V$  des ersten Halbleiters innerhalb der Bandlücke des zweiten Halbleiters zu liegen kommen. Abbildung 17 zeigt das Bänderschema des Typ III Halbleiters.[42]

Abbildung 17: Bänderschema eines Typ III Heteroübergangs - Die Bandlücken der beiden Halbleiter haben keine Überlappung.

Da sich die Valenzbandkante von einem der beteiligten Halbleiter über der Leitungsbandkante des zweiten Halbleiters befindet, besitzen solch Heterostrukturen keine effektive Bandlücke. Sie besitzen somit halbmetallischen Charakter und sind in direkter Form für die Halbleitertechnik nicht interessant. Die Herstellung von dünnen Schichten, mit schichtdicken unter der de Broglie Wellenlänge, ist Fertigungstechnisch

mit manchen solchen Materialkombinationen (z.B. InAs/GaSb) jedoch relativ leicht realisierbar. Bei einer solchen Struktur ist die Bandlücke nicht mehr vom Material, sondern nur von der Schichtdicke abhängig. Dadurch können Heterostrukturen erzeugt werden, die vor allem für Anwendungen im Bereich von mittleren und fernen Infrarotwellenlängen gut geeignet sind.[43]

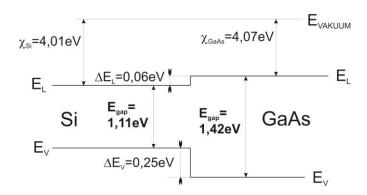

#### 2.4.3 Der GaAs-Si-Heteroübergang

Um die Art des Überganges zu bestimmen, kann man mittels des Anderson-Band-Diagramm-Modells den sich einstellenden Bänderverlauf abschätzen. In diesem Modell wird die Annahme verwendet, dass die Vakuum Energie ( $E_0$ ) beider Halbleiter gleich ist. Mit Hilfe der Elektronenaffinität  $\chi$  der beiden Materialien können die Lagen der Bänder zueinander ermittelt werden. Die Lage der einzelnen Leitungsband-Energien und deren Unterschied können nach folgender Formel berechnet werden:

$$E_L = E_0 - \chi$$

$\Delta E_L = E_{L2} - E_{L1} = \chi_1 - \chi_2$

Die folgende Abbildung 18 zeigt eine schematische Darstellung des zuvor besprochenen Bänderschemas einer Si/GaAs Heterostruktur unter Flachbandbedingungen.

Abbildung 18: Schematischer Verlauf der Bandstruktur eines Si/GaAs Halbleiter-Heteroübergangs.

Der Verlauf der Bandstruktur entspricht dem eines Typ I Heteroübergangs.

Für das Materialsystem GaAs - Si ergibt dies mit den Parametern aus Kapitel 1.1 und 1.2 einen Leitungsbandunterschied von 0,06 eV. Der Unterschied in der Valenzbandenergie beträgt 0,25eV und berechnet sich am Übergang zwischen den beiden Materialien mit dem Unterschied der Bandlücken durch folgende Formel [11]:

$$\Delta E_V = (E_{Gap2} - E_{Gap1}) - \Delta E_L$$

Die Berechnung mit dieser Methode dient allerdings nur zum qualitativen Abschätzen des Banddiagramms. Die genauen Werte können experimentell über die Kapazitäts-Spannungs- Methode, bei der aus den Messungen der Sperrschichtkapazität eines Heteroübergangs in Anhängigkeit der angelegten Spannung, sowohl die Diffusionsspannung als auch die Höhe der Potentialbarriere der beiden Bänder, bestimmt werden. Eine weitere Methode zur experimentellen Bestimmung der Barrierenhöhe basiert auf der Änderung des Strom-Spannungsverlaufes in Abhängigkeit von der Temperatur.[41]

Bei dem in dieser Arbeit untersuchten Heteroübergang zwischen Si Nanowires und einem GaAs Substrat handelt es sich um einen Typ I Heteroübergang. Das epitaktische Wachstum von Si und GaAs ist, aufgrund der unterschiedlichen Gitterkonstanten der unterschiedlichen Temperaturausdehnung, und Schichtsystemen schwierig. Der Unterschied in den Gitterkonstanten beträgt ungefähr 4% und bewirkt bei Schichtabscheidung von GaAs auf Si eine hohe Dichte an Kristalldefekten in der aufgewachsenen Schicht. Die unterschiedliche Temperaturausdehnung der beiden Stoffe bewirkt bei größeren Temperaturänderungen weiters die Bildung von Rissen in den Schichten. Beim Wachstum von GaAs Schichten auf Si Substraten können deshalb nur geringe Wachstumstemperaturen verwendet werden was zu der oben erwähnten hohen Defektdichte führt.[31] Beim Wachstum von Nanowires sind diese Faktoren, aufgrund der geringen Kontaktfläche und des dadurch möglichen, elastischen Stressausgleichs, vernachlässigbar. Aufgrund der geringen Übergangsfläche kann sich die durch die unterschiedlichen Gitterkonstanten entstehende Spannung radial abbauen.[44]

## 3 Experimentelle Durchführung

In diesem Kapitel ist die Herstellung einer Si-GaAs Halbleiter-Hetero Diode beschrieben. Es werden alle notwendigen Prozesse, deren Parameter und Durchführung beschrieben. Die genauen Prozessparameter der Synthese werden erst in Zusammenhang mit den Ergebnissen angeführt. Der erste Unterpunkt liefert eine schematische Übersicht über den gesamten Herstellungsprozess der Halbleiter-Hetero Diode. Der zweite Teil dieses Kapitels beschäftigt sich mit der Nanowiresynthese und allen dafür notwendigen Prozessschritten. Die darauffolgenden Kapitel beschreiben die Vorgangsweise zur Herstellung des Messmoduls und der elektrischen Charakterisierung.

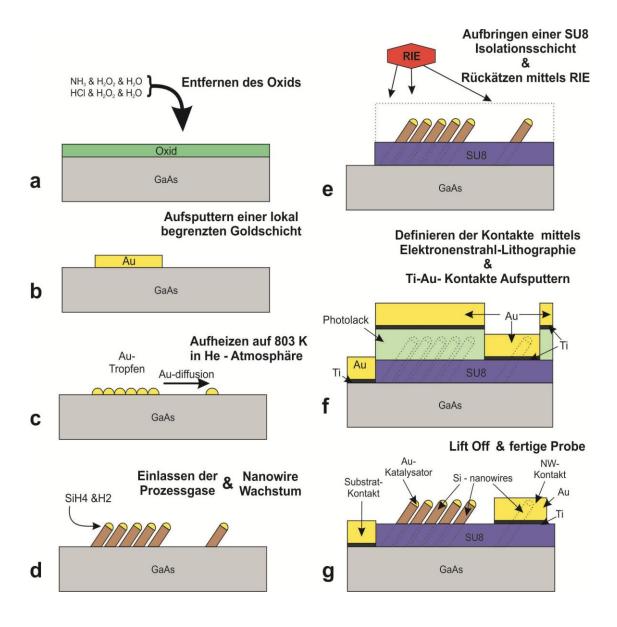

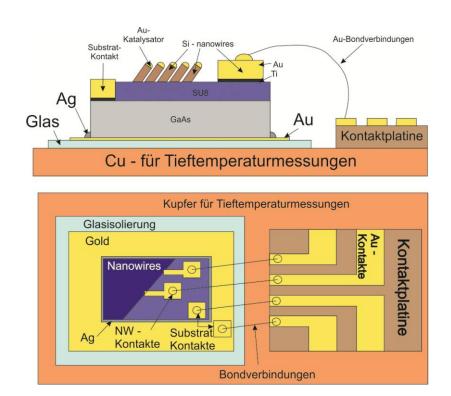

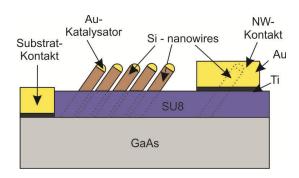

#### 3.1 Herstellungsprozess einer Nanowire Halbleiter Hetero- Diode

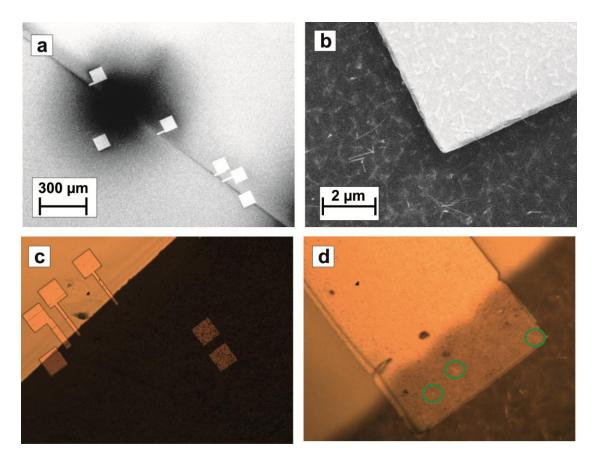

In der folgenden Abbildung 19 ist der Prozessablauf zur Herstellung eines Messmoduls abgebildet. Es zeigt die Si Nanowiresynthese, sowie die darauf folgenden weiteren Prozessschritte, mit welchen die Isolationsschicht auf das Substrat aufgebracht und rückgeätzt, sowie die Kontakte aufgebracht werden. Um eine optische Betrachtung und elektro-optische Messungen zu ermöglichen, werden anstatt von Titan-Gold Kontakten, transparente Indium-Zinn-Oxid (engl. Indium-Tin-Oxide, ITO) Kontakte verwendet.

Abbildung 19: Schematischer Herstellungsablauf einer Halbleiter- Hetero- Diode;

- a) Verunreinigungen und native Oxide werden durch nasschemische Ätzverfahren entfernt.

- b) Mittels Schattenmaske wird ein örtlich begrenzter Bereich mit Gold besputtert.

- c) Durch das Aufheizen des Substrats während des Nanowirewachstums bilden sich aus der durchgehenden Goldschicht Goldtropfen, welche entlang der Oberfläche diffundieren und eine, vom besputterten Bereich getrennte Diffusionszone bilden.

- d) Das Nanowirewachstum wird durch einlassen von Silan in den LPCVD Reaktor gestartet.

- e) Rückätzen der SU8 Isolationsschicht mittels RIE Prozess.

- f) Definierung der Kontakte mittels e-Line Prozess und besputtern der Kontaktflächen mit Ti und Au.

- g) Fertig prozessierte Messanordnung einer Si-GaAs Halbleiter-Heterodiode.

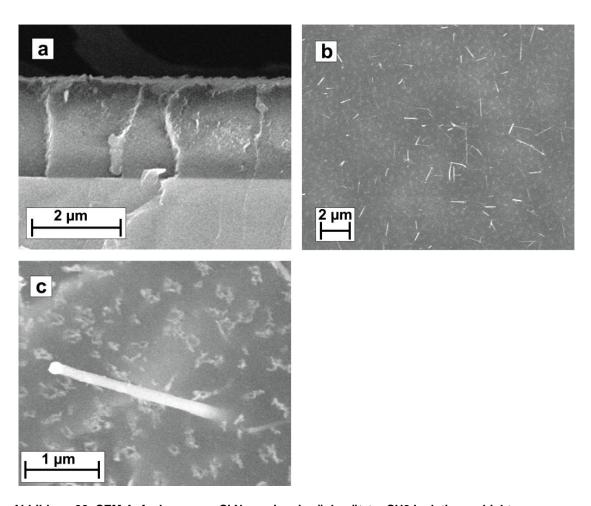

Zu Beginn des Herstellungsprozesses muss die Probe von Verunreinigungen und nativen Oxiden gesäubert werden. Teilabbildung a zeigt schematisch den nasschemischen Reinigungsvorgang mittels eines zweistufigen Reinigungsprozesses (Standard RCA Reinigung). Abbildung b zeigt das Substrat mit einer, auf der Oberfläche örtlich begrenzten Goldschicht. Die Goldschicht wurde durch Verwendung einer Schattenmaske während des Sputterns definiert. Durch Aufheizen des mit Katalysator versehenen Substrates in He Atmosphäre auf 803 K während des Wachstums schmilzt die durchgehende Goldschicht zu einzelnen Goldtropfen auf. Einige dieser Tropfen diffundieren entlang der Oberfläche und bilden einen spärlich mit Katalysatortropfen bedeckten Bereich außerhalb der besputterten Zone. Ab dem Zeitpunkt des Umschaltens des Gases auf eine Gasmischung, bestehend aus Silan verdünnt in Helium und Wasserstoff beginnt das Wachstum der Nanowires. Abbildung d zeigt dieses Wachstum, ausgehend von den zuvor gebildeten und diffundierten Goldtropfen. In Abbildung e sind die Prozessschritte gezeigt, mit denen die Nanowires gegen das Substrat isoliert werden. Das SU8 Isolationsmaterial wurde mittels Spinner auf die Probe aufgetragen. Die minimale Dicke der Isolationsschicht, welche durch aufspinnen erzeugt werden kann, beträgt 5 µm und wird mittels reaktivem Ionen Ätzen (engl. Reactive-Ion-Etching, RIE) auf eine dicke von ca. 700 nm rückgeätzt. Auf der so präparierten Probe, werden mittels Elektronenstrahl Lithographie die Kontaktflächen definiert. Teilbild f zeigt die Positionierung und die beiden abgeschiedenen Metallschichten der Kontaktflächen. Diese sind so platziert, dass sich nur ein einzelner Nanowire unter der Kontaktfläche befindet. Die Kontakte bestehen aus einer Ti Haftschicht unter der eigentlichen Au Kontaktschicht. Die so hergestellte Halbleiter Hetero-Diode ist nach dem Lift off des Fotolacks fertig prozessiert und in Abbildung g dargestellt. Um den Heteroübergang am Spitzenmessplatz zu vermessen werden zwei Messkanäle benötigt. Eine der Messspitzen wird auf dem NW-Kontakt und die andere auf dem Substratkontakt aufgesetzt. Wird nun eine Spannung an den Messspitzen angelegt, so kann sich aufgrund der SU8 Isolierung nur ein Stromfluss vom NW-Kontakt über den Nanowire, durch den Heteroübergang in das Substrat und über das GaAs-Substrat auf den Substratkontakt einstellen. Dabei kann aufgrund der hohen Substratdotierung der Widerstand des Substrats und die parasitären Effekte des Übergangs von Substrat zum Substratkontakt vernachlässigt werden.

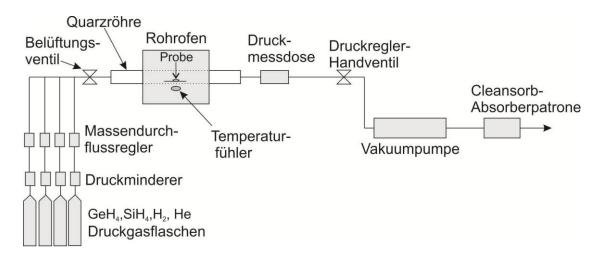

# 3.2 Nanowiresynthese

In diesem Teil der Diplomarbeit sind die notwendigen Prozessschritte zur Herstellung von Si Nanowires auf einem GaAs Substrat angeführt. Diese umfassen alle Teilschritte von der Reinigung des Substrates über das Aufbringen des Katalysators, bis hin zum eigentlichen Nanowirewachstum im LPCVD-Ofen.

# 3.2.1 Substrat Reinigung

Der Einfluss verschiedener Reinigungsprozesse auf das heteroepitaktische Wachstum von Si Nanowires auf GaAs zeigte sich als entscheidend und wurde im Laufe dieser Diplomarbeit intensiv untersucht. Die Angaben der Mischverhältnisse der Reinigungsprozesse beziehen sich auf die folgenden Ausgangsstoffe:

Ammoniakal Lösung (NH<sub>3</sub> in H<sub>2</sub>O) 30%

Wasserstoffperoxid (H<sub>2</sub>O<sub>2</sub> in H<sub>2</sub>O) 35 w.t.%

Salzsäure (HCI) ca. 27%

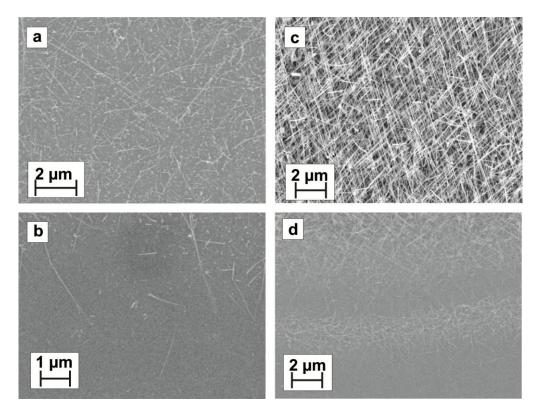

Gepufferte Flusssäure (NH₄F, HF; BHF, 7:1)