FAKULTÄT FÜR INFORMATIK

**Faculty of Informatics**

# Self-Healing Asynchronous Circuits for High-Reliability Applications

## DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

## Doktor der technischen Wissenschaften

by

## Dipl.-Ing.(FH) Thomas Panhofer

Registration Number 9825811

to the Faculty of Informatics at the Vienna University of Technology

Advisor: a.o.Univ.-Prof. Dipl.-Ing. Dr. Andreas Steininger

The dissertation has been reviewed by:

(a.o.Univ.-Prof. Dipl.-Ing. Dr. Andreas Steininger) (Prof. Dr.-Ing. Heinrich Theodor Vierhaus)

Vienna, January 2012

(Dipl.-Ing.(FH) Thomas Panhofer)

# Erklärung zur Verfassung der Arbeit

Dipl.-Ing.(FH) Thomas Panhofer Anton-Wenzel-Pragergasse 7-9/4/4, 3002 Purkersdorf

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasserin)

# Danksagung

Ich danke meinem Betreuer, Andreas Steininger, für die jahrelange Unterstützung und die zahlreichen Diskussionen, wertvollen und richtungsweisenden Tipps, sowie das Verständnis für meine private und berufliche Situation. Weiters möchte ich Martin Delvai danken, der in den Anfängen mit seinen visionären Ideen so manchen wichtigen Beitrag geliefert und damit grundlegend zum entstandenen Konzept beigetragen hat.

Danke auch an meinen Arbeits- und Studienkollegen Werner Friesenbichler, mit dem ich viele wertvolle Diskussionen geführt habe. Die nicht immer nur technischen Gespräche haben auch über so manches Motivationstief hinweggeholfen. Ebenfalls danken möchte ich der Firma RUAG Space für die finanzielle Unterstützung bei einigen Konferenzen.

Ein grosses Danke gebührt auch meinen Eltern, die die Grundsteine für meine Ausbildung und meinen Ehrgeiz gelegt haben.

Meiner Frau Irene möchte ich danken, da sie aufgrund ihrer kritischen Einstellung gegenüber dem "Zeiträuber" Dissertation kontinuierlich dafür gesorgt hat, daß unsere Freunde, vor allem aber die Familie, nicht zu sehr vernachlässigt werden.

Zuletzt möchte ich mich bei allen entschuldigen, die unter meiner Dissertation gelitten haben, sei es durch reduzierten Kontakt, langweilige Vorträge über selbstheilende Elektronik oder schlafmangelbedingte schlechte Laune.

Viele haben durch die richtigen motivierenden Worte zur Entstehung der Arbeit beigetragen. Meine größte Stütze aber sind Irene, Natalie und Julian gewesen. Danke, daß ihr da seid.

## Abstract

New generations of integrated programmable logic devices offer more and more resources, which makes them very attractive for implementing even complete systems on chip. Advancing miniaturization, higher integration, continuously decreasing supply voltage and other changing parameters lead to a situation where fault effects that previously were an issue only in extremely harsh environments, e.g. space missions, are now impacting the circuits also in "normal" environments. At the same time the probability for multiple faults occurring during operation is increasing. This diverging evolution – increasing complexity vs. decreasing (system) reliability – is getting a serious problem for high reliability applications.

While a lot of methods exist to handle transient faults, there are no consolidated concepts available for permanent faults. Traditional fault tolerance concepts, e.g. TMR, are usually costly in terms of hardware resources, mass and power consumption. Furthermore, for highly complex systems it is difficult to predict the failure modes. In particular for those high-reliability applications, where a repair is very expensive or even impossible, the trend goes towards adaptive systems, that can autonomously cope with failure situations as they arise.

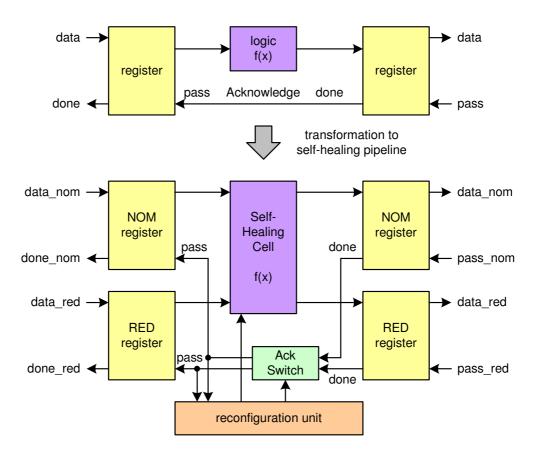

In this thesis a self-healing concept for integrated digital logic is presented. The approach is based on asynchronous circuits and uses uses a redundant pipeline as basic circuit structure. Combinational logic is replaced by reconfigurable Self-Healing Cells (SHC). The inherent properties of the asynchronous design style FSL simplifies the design of a fault tolerant system, as it features e.g. fail-stop behavior without additional effort. A watchdog circuit monitors the circuit's activity and triggers the reconfiguration controller to start the circuit reconfiguration in case of a deadlock. As soon as a valid data and acknowledge path is established, the pipeline autonomously starts working again. In general, this procedure works without loss or corruption of data. However, the pipeline structure and the applied reconfiguration algorithm influence the sensitivity to timing effects and the probability for a successful repair.

To verify the function of the concept, a VHDL model of the self-healing pipeline as well as of several different reconfiguration controllers was designed. In addition an abstract Matlab model was established and used for exhaustive fault injection simulations. Finally, the circuits were implemented in a Xilinx Virtex-4 FPGA and hardware fault injection experiments were performed. All models used the same stimulus interface, so that identical situations could be investigated and compared on different abstraction levels.

The results justify the suitability of the approach for increasing the fault tolerance of integrated circuits: All single faults, more than 80% of the double faults and nearly 60% of triple faults can be tolerated by the developed concept, while introducing a hardware overhead comparable to a TMR system.

# Kurzfassung

Neue Generationen von integrierten, programmierbaren Bauelementen stellen ausreichend Ressourcen zur Verfügung, um komplette "Systems-on-Chip" (SoC) zu realisieren. Fortschreitende Miniaturisierung, höhere Integrationsdichten, sinkende Versorgungsspannungen und einige andere Parameterveränderungen führen dazu, daß Fehlereffekte, die bisher nur in extremen Umgebungsbedingungen wie z.B. im Weltraum von Relevanz waren, nun auch Schaltungen in normaler Umgebung stören können. Gleichzeitig steigt auch die Wahrscheinlichkeit für Mehrfachfehler während des Betriebs. Diese divergierende Entwicklung – steigende Komplexität und sinkende (System-) Zuverlässigkeit – wird zunehmend zu einem signifikanten Problem für hochzuverlässige Anwendungen.

Während für die Mitigation von transienten Fehlern zahlreiche etablierte Methoden existieren, ist die Behandlung von permanenten Fehlern weitgehend unerforscht. Traditionelle Massnahmen, wie z.B. TMR, sind oft aufgrund ihres Ressourcenverbrauchs, zusätzlicher Masse und erhöhter Leistungsaufnahme unattraktiv. Weiters sind die Fehlerauswirkungen in komplexen Systemen schwer vorherzusagen. Insbesondere für Anwendungen, in denen eine Reparatur sehr teuer oder sogar unmöglich ist, wird nun versucht, eine gewisse Autonomie in der Fehlerbehandlung zu erzielen.

Diese Dissertation beschreibt ein selbstheilendes System für integrierte digitale Logik. Das Konzept verwendet eine redundante asynchrone Pipeline als Ausgangsstruktur. Kombinatorische Logik wird durch sogenannte selbstheilende Zellen (SHC) ersetzt. Insbesondere die asynchrone Design-Methodik FSL bietet einige inhärente Eigenschaften, die für ein fehlertolerantes System von Vorteil sind (z.B. "fail-stop" Verhalten). Ein Watchdog überwacht die Schaltungsaktivität und startet im Fehlerfall eine Rekonfiguration. Sobald gültige Signal-Pfade vorhanden sind, setzt die Pipeline ihre Arbeit fort. Grundsätzlich werden die Daten dabei nicht gestört. Die enstehende Struktur der Pipeline beeinflusst jedoch das zeitliche Verhalten und kann zu Problemen führen.

Für die Verifikation des Konzepts wurde ein VHDL Modell sowohl der Pipeline als auch unterschiedlicher Algorithmen entwickelt, sowie auch ein abstraktes Modell in Matlab. Schließlich wurde die Schaltung in einem Xilinx Virtex-4 FPGA implementiert und umfangreichen Experimenten unterzogen. Alle Modelle verwenden den gleichen Kontollmechanismus, sodass idente Situationen in allen Modellen auf unterschiedlichen Abstraktionsebenen untersucht werden konnten.

Die Ergebnisse beweisen die Eignung des Konzepts für die Erhöhung der Fehlertoleranz in integrierten Schaltungen: alle Einzelfehler, mehr als 80% der Doppelfehler und fast 60% der Dreifachfehler konnten behoben werden, während der zusätzliche Ressourcenaufwand vergleichbar mit TMR Systemen ist.

# Contents

| Co | ontent | S                                                    |                                              | ix |  |  |  |  |  |  |

|----|--------|------------------------------------------------------|----------------------------------------------|----|--|--|--|--|--|--|

| 1  | Intro  | oduction                                             | a                                            | 1  |  |  |  |  |  |  |

|    | 1.1    | Motiva                                               | tion                                         | 3  |  |  |  |  |  |  |

|    | 1.2    | Contrib                                              | pution and Objectives                        | 4  |  |  |  |  |  |  |

|    | 1.3    | Structu                                              | re of the Thesis                             | 5  |  |  |  |  |  |  |

| 2  | Prin   | Principles of Fault Tolerance and Asynchronous Logic |                                              |    |  |  |  |  |  |  |

|    | 2.1    | Basics                                               | of Fault Tolerance                           | 7  |  |  |  |  |  |  |

|    |        | 2.1.1                                                | Terminology                                  | 7  |  |  |  |  |  |  |

|    |        | 2.1.2                                                | Fault Classification                         | 9  |  |  |  |  |  |  |

|    |        | 2.1.3                                                | Fault Models                                 | 9  |  |  |  |  |  |  |

|    |        | 2.1.4                                                | Masking Effects                              | 10 |  |  |  |  |  |  |

|    |        | 2.1.5                                                | Fault Hypothesis With Respect to This Thesis | 10 |  |  |  |  |  |  |

|    | 2.2    | Increas                                              | sing Circuit Reliability                     | 11 |  |  |  |  |  |  |

|    |        | 2.2.1                                                | Introduction                                 | 11 |  |  |  |  |  |  |

|    |        | 2.2.2                                                | Methods                                      | 11 |  |  |  |  |  |  |

|    | 2.3    | Introdu                                              | ction to Asynchronous Logic                  | 14 |  |  |  |  |  |  |

|    |        | 2.3.1                                                | General                                      | 14 |  |  |  |  |  |  |

|    |        | 2.3.2                                                | Classification of Asynchronous Circuits      | 15 |  |  |  |  |  |  |

|    |        | 2.3.3                                                | Asynchronous Protocols                       | 15 |  |  |  |  |  |  |

|    | 2.4    | Four-S                                               | tate-Logic                                   | 16 |  |  |  |  |  |  |

|    |        | 2.4.1                                                | General                                      | 16 |  |  |  |  |  |  |

|    |        | 2.4.2                                                | Combinational Logic                          | 17 |  |  |  |  |  |  |

|    |        | 2.4.3                                                | Registers                                    | 18 |  |  |  |  |  |  |

|    |        | 2.4.4                                                | Timing Parameters                            | 19 |  |  |  |  |  |  |

|    |        | 2.4.5                                                | Faults in Asynchronous Circuits              | 21 |  |  |  |  |  |  |

| 3  | State  | e of the                                             | Art of Circuit Reconfiguration               | 25 |  |  |  |  |  |  |

|    | 3.1    | Introdu                                              | iction to Autonomous Self-Repair             | 25 |  |  |  |  |  |  |

|    | 3.2    |                                                      | Reconfiguration                              | 27 |  |  |  |  |  |  |

|    |        | 3.2.1                                                | Runtime Reconfiguration with FPGAs           | 27 |  |  |  |  |  |  |

|    |        | 3.2.2                                                | Dynamic Rotation and Free for Test           | 28 |  |  |  |  |  |  |

|   |      | 3.2.3    | Fine-Grained Self-Healing Hardware 30                        |

|---|------|----------|--------------------------------------------------------------|

|   |      | 3.2.4    | Dynamic Reconfiguration using Atomic Fault Tolerant Blocks 3 |

|   |      | 3.2.5    | Column-Based Precompiled Configuration                       |

|   |      | 3.2.6    | Roving STARS         33                                      |

|   |      | 3.2.7    | Node Covering Technique                                      |

|   |      | 3.2.8    | Method of Shifting Configuration Data                        |

|   |      | 3.2.9    | Nature-Inspired Methods                                      |

|   |      | 3.2.10   | Self-Repair using Re-Configurable Logic Blocks (RLBs)        |

|   |      | 3.2.11   | Self-Healing Asynchronous Arrays 40                          |

|   | 3.3  | Compa    | urison and Conclusion                                        |

| 4 | Self | -Healing | g Approach 45                                                |

|   | 4.1  | Introdu  | uction                                                       |

|   | 4.2  | Archite  | ecture Overview                                              |

|   |      | 4.2.1    | Concept and Fault Hypothesis                                 |

|   |      | 4.2.2    | Fault Locations                                              |

|   |      | 4.2.3    | Reconfiguration of Combinational Logic                       |

|   |      | 4.2.4    | Reconfiguration of Control Logic                             |

|   |      | 4.2.5    | Reconfiguration Unit                                         |

|   |      | 4.2.6    | Self-Healing Reconfiguration Unit                            |

|   |      | 4.2.7    | Default State of Configurable Elements                       |

|   |      | 4.2.8    | Transformation from FSL to SH-FSL                            |

|   | 4.3  | The Pr   | inciple of Pipeline Reconfiguration                          |

|   |      | 4.3.1    | Introduction                                                 |

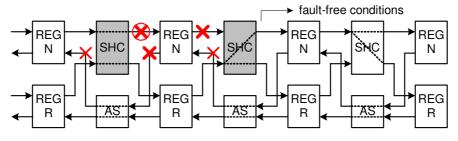

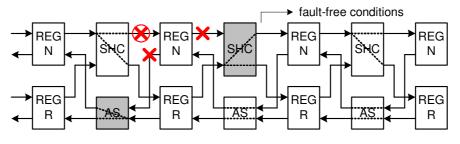

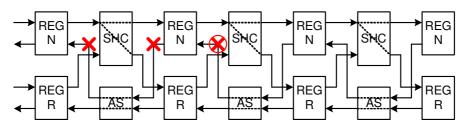

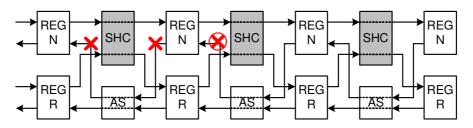

|   |      | 4.3.2    | Faults at SHC Inputs                                         |

|   |      | 4.3.3    | Faults at Register Inputs                                    |

|   |      | 4.3.4    | Faults at Acknowledge Signals                                |

|   |      | 4.3.5    | Timing Investigation of Different Pipeline Configurations    |

|   |      | 4.3.6    | Summary                                                      |

|   | 4.4  | Fault I  | Diagnosis in a Pipeline                                      |

|   |      | 4.4.1    | General                                                      |

|   |      | 4.4.2    | Fault at SHC Input   62                                      |

|   |      | 4.4.3    | Fault at Register Input    63                                |

|   |      | 4.4.4    |                                                              |

|   |      | 4.4.5    | Observable Symptoms                                          |

|   |      | 4.4.6    | Effects due to Multiple Faults                               |

|   |      | 4.4.7    | Summary                                                      |

|   | 4.5  | Recont   | figuration Rules and Algorithm Efficiency                    |

|   |      | 4.5.1    | Reconfiguration on Pipeline-Level                            |

|   |      | 4.5.2    | Embedded Fine-Granular SHC Reconfiguration                   |

|   | 4.6  |          | ead of the Self-Healing Approach                             |

|   |      |          |                                                              |

| 5 | Ana  | -        | mulations and Experimental Results 81                        |

|   | 5.1  | Introdu  | iction                                                       |

|   |      |          |                                                              |

| 5.2  | Enviro  | nment                                                          | 82  |

|------|---------|----------------------------------------------------------------|-----|

|      | 5.2.1   | General                                                        | 82  |

|      | 5.2.2   | Simulation Environment for Pipeline Reconfiguration            | 82  |

|      | 5.2.3   | Environment for Hardware Experiments                           | 85  |

| 5.3  | Reconf  | figuration of Self-Healing Cells                               | 88  |

|      | 5.3.1   | Fault Tolerance of Fine and Coarse Granular Self-Healing Cells | 88  |

|      | 5.3.2   | Optimization of Self-Healing Cells                             | 90  |

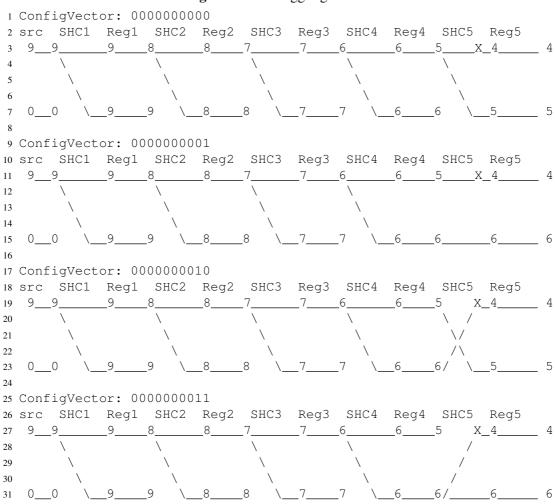

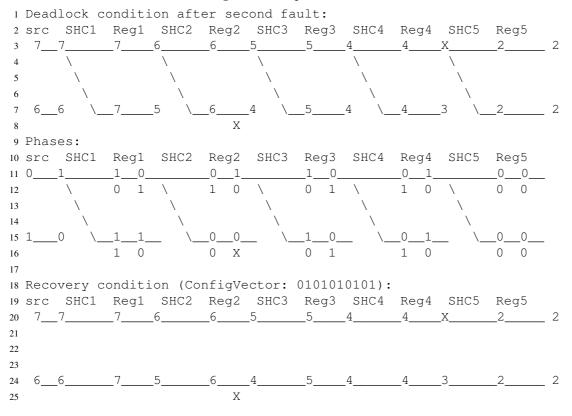

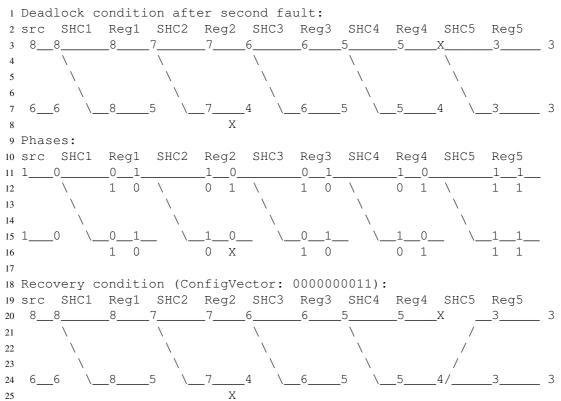

| 5.4  | Simula  | tion of Pipeline Reconfiguration                               | 94  |

|      | 5.4.1   | Simulation of a Deadlock Recovery                              | 94  |

|      | 5.4.2   | Simulation Results of Different Reconfiguration Algorithms     | 96  |

|      | 5.4.3   | Result Summary and Comparison                                  | 105 |

| 5.5  | Hardw   | are Fault Injection Experiments                                | 107 |

|      | 5.5.1   | General                                                        | 107 |

|      | 5.5.2   | Results of Pipeline without Acknowledge Switches               | 110 |

|      | 5.5.3   | Results of Pipeline with Acknowledge Switches                  | 112 |

|      | 5.5.4   | Summary                                                        | 114 |

| 5.6  | Hardw   | are Implementation of a Complex Self-Healing Circuit           | 115 |

|      | 5.6.1   | Introduction                                                   | 115 |

|      | 5.6.2   | The GAIA Pre-Processing Algorithm                              | 115 |

|      | 5.6.3   | FSL Implementation                                             | 118 |

|      | 5.6.4   | Self-Healing GAIA Algorithm                                    | 119 |

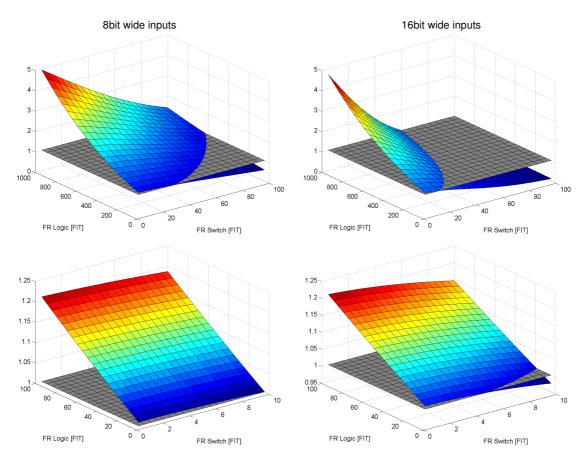

|      | 5.6.5   | Results                                                        | 121 |

| 5.7  | Reliabi | ility Analysis of Self-Healing Circuit                         | 123 |

|      | 5.7.1   | Introduction                                                   | 123 |

|      | 5.7.2   | GAIA Reliability Estimation                                    | 124 |

| 5.8  | Compa   | arison with State-of-the-Art Methods                           | 125 |

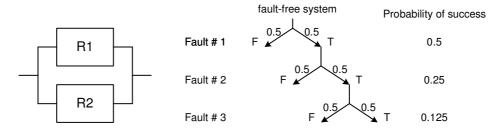

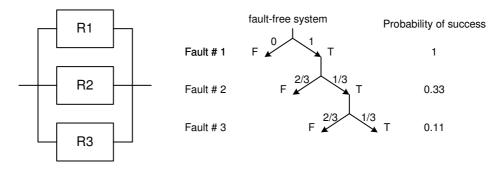

|      | 5.8.1   | Duplex System                                                  | 125 |

|      | 5.8.2   | TMR System                                                     | 126 |

|      | 5.8.3   | Comparison with Self-Healing Approach                          | 126 |

| 5.9  | Summa   | ary and Discussion                                             | 128 |

|      | 5.9.1   | Fault Frequency                                                | 128 |

|      | 5.9.2   | Timing Assumptions                                             | 129 |

|      | 5.9.3   | Mis-alignment of Nominal and Redundant Path                    | 129 |

| 5.10 | Annex   |                                                                | 130 |

| c    |         |                                                                | 445 |

| Con  | clusion | and Outlook                                                    | 135 |

|      |         |                                                                |     |

## Bibliography

6

139

## CHAPTER

## Introduction

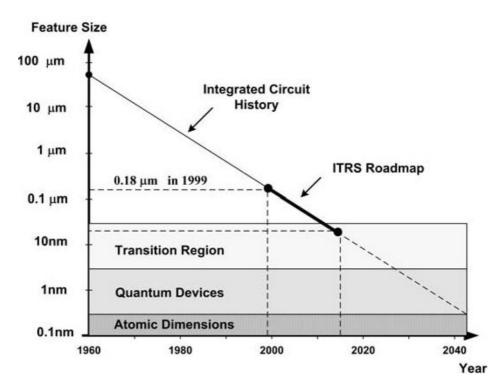

The complexity of applications is continuously increasing and at the same time the requirements on power consumption, reliability and performance become more and more stringent. The semiconductor industry is following the demands from application side very well and offers more resources, higher operating speed and less power consumption at lower supply voltage each new chip generation. In 1965 Gordon Moore [91] predicted a duplication of resources per square inch every 18 months<sup>1</sup>. More than 40 years later the International Technology Roadmap for Semiconductors (ITRS) [58] shows that this prediction is still fairly true and, as can be seen in Figure 1.1 [119], has not yet reached the end.

Although this evolution was and is one of the major contributors for the level of technology we have reached, the designers are also facing new challenges:

- Susceptibility to Faults: Due to the lower charge stored at the circuit nodes the chips become more prone to various fault effects. For example, in the past transient faults like Single-Event-Upsets (SEUs) were a serious problem only in extreme environments such as space, but now become problems even in on-ground applications [46,63,94,128]. Apart from soft-errors, the increased technology scaling causes more and more manufacturing imperfections [39, 93, 110]. On the one hand, this decreases the yield and thus increases the component costs. On the other hand, some of these faults might even not be detected during manufacturing tests, and may appear as permanent faults even after a long time of successful operation. So, recently also permanent defects gained higher attention [4, 72]. Moreover, the single-fault model seems to become outdated. The probability for multiple errors caused by a single fault event is increasing, and a massive number of defects has to be assumed [1].

- 2. System Complexity: The increasing complexity of the applications makes system failures more difficult to predict and to understand. Thus, they are often not considered sufficiently in the system design. Furthermore, new and powerful technologies and semiconductor

<sup>&</sup>lt;sup>1</sup>The time horizon varies between 12 and 24 months but seems to settle at 18 months.

Figure 1.1: Trend of Feature Size [119]

processes are often either not available or not tolerated, respectively, in conservative industries (such as space), or are not robust enough - and the available robust technologies typically lack in performance. For example, radiation-tolerant anti-fuse FPGAs offer less than 1/10 of the resources compared to SRAM-based FPGAs [40]. As a consequence, the components selected for such applications often have to be operated at their limits.

- 3. Electromagnetic Field (EMF) Pollution: The operation environment becomes harsher due to increasing EMC disturbances caused by the huge number of wireless services (WiFi, Bluetooth, mobile communication, GPS, etc.).

- 4. Extreme Application Demands: The progress in technology causes new areas of applications to evolve. For example, interplanetary space missions [22] where the spacecraft is "on the way" for several years, require a highly robust circuit and autonomous failure detection, isolation and repair (FDIR), as a manual repair is not possible.

- 5. Use of complex integrated circuits in critical applications: While failing systems and subsystems due to defective components might be tolerated to some extent in consumer electronics, this is absolutely not acceptable in applications where human life is jeopardized or where human interaction (e.g. repair) is not possible or extremely expensive. Typical examples for the latter ones are automotive, aerospace and space applications.

This list is certainly not complete, but illustrates some important issues that need particular attention.

In conservative industries, e.g. the space industry, the traditional approach to gain high reliability is *fault avoidance* by using screened components and reducing component stress by parameter derating. Of course, high quality components are very expensive, and nevertheless there is a limit that can only be overcome by additional means. Rather than trying to make the components perfectly reliable, the trend now changes to build reliable systems from unreliable components [4] – which requires *fault tolerance* techniques.

### **1.1 Motivation**

The traditional approach to increase fault tolerance of unreliable modules is to apply hardware redundancy on system level [115]. The granularity is typically rather coarse and thus quite expensive in terms of hardware costs. In addition, dedicated fault control mechanisms are required, which regularly check some characteristics of the system and decide, when the redundant section shall be used. A significant amount of resources usually has to be spent on the management of the implemented fault tolerance mechanisms.

Each new generation of programmable logic devices, such as FPGAs and ASICs, provides more and more resources, so that these components are increasingly used to accomplish the main functionality of an application. However, as they comprise the functionality of a huge system of earlier days in a single chip, this implies that they become critical elements in the system. Although their failure rate is rather low [16], in particular for long mission times the probability for even multiple faults can become an issue. While a lot of methods for handling transient faults are well established, there are hardly any concepts available to deal with permanent faults.

From an application point of view there is a demand on a generic and reliable hardware platform, which can handle transient as well as permanent faults, and which is able to autonomously recover from faults without external interaction. Runtime reconfiguration is deemed to be a promising way to provide such features.

Methods applied on transistor level are considered to be too specific, and furthermore would require completely new component libraries. The solution to be found should therefore apply on gate level, which will also ease the development and prototyping.

Irrespectively of the implementation, some kind of diagnosis is required first to locate the fault. Here asynchronous logic has significant advantages, as it is inherently tolerant against timing variations e.g. caused by changed circuit routings, and it tends to stop operation in the presence of permanent faults [3]. Although asynchronous logic is not well established at least for large applications and lacks from appropriate design tools, it was already shown that it is possible to implement reasonably complex asynchronous circuits such as processors even in standard FPGAs [14].

The main drawback of asynchronous circuits is the inherent logic overhead due to the design technique, e.g. handshake protocols, dual rail encoding, etc. However, by improving the design flow it is possible to reduce the overhead significantly [26]. Anyway, the hardware overhead is not seen as major criterion for this thesis.

## **1.2** Contribution and Objectives

This thesis describes an adaptive system, which is able to autonomously perform all necessary tasks to stay alive, while the higher level application can rely on a correctly working hardware and can concentrate on the intended function instead of dealing with fault tolerance.

The concept implements *autonomous self-repair within integrated circuits on gate level* and can be based on existing processes and design tools. This requires to decompose the circuit into parts with appropriate granularity, which are then implemented by flexible, reliable structures. These elements allow being reconfigured in case errors occur to bypass the defective resources with working ones. The concept is based on asynchronous logic and makes use of the inherent properties, such as fail-stop behavior. The reconfiguration is performed during runtime and is transparent to the application. The only impact is increased delay, which is tolerated by definition of an asynchronous circuit.

The methodology presented in this thesis is called *self-healing*, as the aim is to achieve a completely autonomous handling and repair of faults occurring during operation. The main objectives can be summarized by the following items:

- Recover from multiple permanent faults and errors

- occurring in integrated circuits, irrespectively of their origin

- within a predictable timing

- with deterministic measures

- by autonomous reconfiguration

- transparent to the application

- using existing processes and standard libraries

Although the considerations in this thesis are not focused on a particular application, harsh environment and high reliability as e.g. needed in space applications, are always kept in mind regarding their special requirements. This implies e.g. that the circuit behavior shall be deterministic and reproducible so that it can be well analyzed although the circuit architecture might evolve during operation.

To achieve these goals a novel structure of self-repairing blocks was developed. Three important topics, namely fault detection, diagnosis and repair, are of particular interest and needed to be harmonized. The behavior of asynchronous pipelines in the presence of permanent (multiple) faults is investigated in detail and various reconfiguration options are analyzed. An architecture as well as algorithms for fault removal are presented and the optimum reconfiguration strategy is elaborated. The effectiveness and suitability of the concept is proven by simulations and hardware experiments.

Within the scope of this thesis several generic tools as well as simulation and analysis models were established, which allow comparing different implementations, architectures and algorithms in a structured and deterministic way.

## **1.3** Structure of the Thesis

**Chapter 2** briefly describes the terminology used in this thesis and gives an overview about the considerations for fault tolerant systems on chip level. Furthermore, the basic principle of asynchronous logic in general and the used design style *Four State Logic (FSL)* in particular is described.

**Chapter 3** presents the state-of-the-art of circuit reconfiguration in integrated circuits. The concepts are presented and evaluated with respect to the requirements and needs defined for this thesis.

**Chapter 4** presents details about the developed architecture and the methodology for circuit reconfiguration. It is explained how to apply the concept to a standard FSL circuit. The behavior of FSL pipelines in failure cases and the respective observable symptoms are derived, which builds the prerequisite for establishing an appropriate reconfiguration algorithm later on. Lastly, the overhead of the self-healing approach is assessed.

In **chapter 5** the results of all simulations, analysis and experiments as well as a description of the used tools, development and prototyping environments is presented. Different reconfiguration algorithms are implemented in a simulation model as well as in hardware and compared with each other. The proof-of-concept is established by - among several other simulations and experiments - the implementation of a complex video processing circuit and by hardware fault injection experiments. A reliability analysis is performed for an exemplary circuit to evaluate the gain of reliability for the developed concept. The results are compared with other state-of-the-art methods.

Finally, **chapter 6** forms the conclusion. The work is compared with the initial goals and an outlook to future work is given.

# CHAPTER 2

# Principles of Fault Tolerance and Asynchronous Logic

## 2.1 Basics of Fault Tolerance

This section presents an overview and clarification of commonly used terms related to reliability and fault tolerance. Details can be found e.g. in [2].

#### 2.1.1 Terminology

Errors may appear unpredictably in every electronic circuit. The method, how to cope with the error and to which extent this has to be done, depends on the application and its criticality in the system. The threats to a system can be distinguished into three main categories: *faults, errors* and *failures* [73].

- The term *fault* is used to describe the *cause of an error* in a system. A fault is an action or event that affects a system in a way that an error can occur, however, the existence of faults does not necessarily imply that an error occurs. Possible faults could be e.g. single event effects due to radiation.

- *Error* describes an unintended system state due to a manifested fault. Errors may be explicitly related to external events (e.g. EMC or radiation) or e.g. due to defective components, aging effects of components inside the chip, etc. The existence of an error still does not necessarily imply that the system fails. If the error is e.g. located in unused resources or in a currently unused circuit part, it will not affect the circuit functionality, at least until this part or these resources come into operation. An error that has not yet triggered a failure is called *latent*.

- *Failure* is the effect visible from the outside world, i.e. a deviation from the system specification caused by an error that has propagated to the system boundary. This could be e.g.

a wrong result or a result produced at a wrong (unexpected) time. Failures can already occur at component level, e.g. if a transistor does not fulfil its specified performance any more. A failure in a subsystem might become a fault in the higher level system.

The causal relationship between these terms and the propagation between system boundaries can be expressed by the "fundamental chain" [2]:

$$\dots \rightarrow failure \rightarrow fault \rightarrow error \rightarrow failure \rightarrow fault \rightarrow \dots$$

A system should be designed so that no *single-point failure* exists, i.e. that no single fault/error causes the system to deviate from the specification. Typically, this is analyzed in a *Failure Mode, Effects and Criticality Analysis* (FMECA) [95].

While some effects can be handled by preventive actions aiming for *fault avoidance* (e.g. shielding to reduce radiation dose), others require appropriate *fault and error detection* techniques to be able to detect and repair the error before it propagates in the system and results in a failure, i.e. *fault tolerance*. The method to be applied depends on the application and on its criticality in the system.

Doumar et.al. [18] further introduces the term *defect tolerance*, which is used to describe techniques performed by the manufacturer, i.e. handles defects that occur during manufacturing, whereas fault tolerance describes the method done by the user to heal errors which occur during operation of the circuit.

Before a fault can be corrected, it must be detected and correctly identified. There exist several ways of error detection, a very common example in particular for serial transmissions is parity information [115].

The aim of fault tolerance is to provide the requested service even in the presence of faults, i.e. the system must be able to re-construct the information transmitted by the sender from the received faulty data. Of course, fault tolerance mechanisms can only correct faults and errors that have been considered in the fault hypothesis. Typically, the limitation is the number of faults and the fault frequency. For example, memories can be protected by an *Error Detection and Correction* (EDAC) mechanism. Depending on the number of syndrome bits (which limit the useable memory size) one or more faults can be detected and corrected [115]. With the EDAC an error may be removed before it affects the system.

The term *dependability* summarizes the attributes *reliability*, *availability*, *maintainability*, *safety*, *integrity* and *confidentiality* [2]. Except of reliability and availability the attributes are rather qualitative and cannot be quantified by measurements. Reliability describes the probability that a system provides its specified service at a particular time. Availability gives the relation between the time the system fulfils its specification and the time the system is repaired (maintenance time), i.e. the readiness of usage. For systems without repair (e.g. typically in space systems) the reliability defines the mission success, as the system is considered to be failed after the first fault occurrence. An important parameter for reliability analysis is the failure rate of the used elements, which expresses the probability of failure per time. In fact, components cannot have a failure rate, as they cannot be repaired, but anyhow the term failure rate is commonly used for components to express the contribution to the system failure rate.

The time until a system fails the first time is called *Mean Time To Fail* (MTTF). For repairable systems a *Mean Time Between Failure* (MTBF) can be defined (MTBF = 1/failure rate), as well as a *Mean Time To Repair* (MTTR), i.e. the average time it takes to repair a system. Obviously, in order to be become practically usable, the MTTR must be significantly lower than the MTBF.

#### 2.1.2 Fault Classification

Faults can be classified into different categories [2], of which the distinction by their persistence into *temporary* and *permanent* faults is of particular interest for this thesis.

Transient faults are temporary faults originating from the physical environment. They are present for a limited time and can be caused e.g. by radiation [24] or by *Electromagnetic Inter-ference* (EMI). Radiation induced faults are also called *Single Event Effect* and can be further classified into *Single Event Transient* (SET), *Single Event Upset* (SEU), *Single Event Latchup* (SEL) and *Single Event Burnout* (SEB).

In general, radiation induced particle strikes change the electrical charge stored at a circuit's node and thus the voltage of this node. Depending on the amount of charge stored and removed/induced, as well as the circuit's technology and the driver's strength, the logic level of the signal is changed. A SET is a logic transition that is restored by the driver. If the changed logic level is stored and thus remains, the effect is called SEU. A SEU can be removed by re-defining the signal state or resetting the storage element. The duration of radiation induced transient faults is in the order of 1ns [17]. SEUs do not alter the hardware, and are thus defined as *soft error* [116].

Permanent faults typically model physical defects. Possible causes are manufacturing imperfections, overstress, electromigration [25], or can be a consequence of transient faults. Sometimes a particle strike triggers a parasitic thyristor and the signal remains in the wrong state, unless the device is power-cycled. This effect is called SEL. It is potentially destructive because high currents can be induced, leading to a SEB, which may destroy the device. The SEB was first seen in power MOSFETs and causes a physical (hardware) defect of the device due to high current. It is thus defined as *hard error*. As hardware defects cannot be removed, they lead to *permanent errors*. The effect in MOSFETs is also called single event gate rupture (SEGR). A similar effect has been observed in CMOS circuits and is there called single event dielectric rupture (SEDR) [38].

In SRAM based FPGAs these definitions become a bit indistinct. As the function is defined by a bitstream stored in a SRAM, a soft error can change the circuit structure, which would be visible as permanent error, although the hardware is not defect (i.e. a permanent soft error). Such an error could be resolved by restoring the original function e.g. by scrubbing or a device reset.

#### 2.1.3 Fault Models

A very popular model to describe the fault behavior of a circuit under test is the *(single) stuck-at fault model* (SSAF) [39, 64, 103]. According to this fault model a circuit line is stuck-at one or zero if it is disconnected from any other circuit's wires and connected to the power supply or ground.

Although it is a very simple model, it covers at least 70% of fabrication defects [76] and is well suited to model permanent faults. In contrast to "open" faults, i.e. simply disconnecting a signal from its target, stuck-at faults represent shorts and thus need particular handling with respect to fault isolation.

*Bridging faults* model connections to other signals, i.e. the logic state is controlled by another signal that is connected due to a physical fault [39].

Since some fault effects could be masked by the simple stuck-at fault model or the bridging model (if the fault forces the signal to the same logical value as it has anyhow), some other fault models have been developed.

The *bit-flip* model simply inverts a signal state. This can be troublesome as e.g. for latent faults the signal could toggle its state several times, which does not represent the correct physical behavior. Other fault models such as *delay faults* or *pulse faults* do not affect the circuit's logical function and are only relevant for the investigation of transient fault behavior, which is out of scope for this thesis.

#### 2.1.4 Masking Effects

Faults might be masked and thus prevented from becoming active due to mainly the following three reasons [114]:

- Temporal masking: The fault does not affect the circuit function because it appears at a time where the signal is not evaluated (e.g. between clock edges).

- Electrical masking: The fault is attenuated sufficiently by gates, wires, etc. so that it does not change a signal state.

- Logical Masking: The logical function receiving a faulty input is insensitive to the signal state, e.g. an OR gate does not change its output if one input has state 1 and the fault forces the other input to 0.

The only relevant masking effect in the scope of this thesis is the logical masking, which could delay the occurrence of inconsistent data.

#### 2.1.5 Fault Hypothesis With Respect to This Thesis

The fault hypothesis summarizes all conditions, under which faults are assumed to occur, and forms the basis for fault handling in an application.

Within this thesis the following fault hypothesis applies:

- The faults are modeled according to the stuck-at fault model. Both stuck-at-1 and stuckat-0 faults may occur.

- Only permanent faults are considered, irrespectively of their origin. Whenever the term *fault* is used, it refers to a *permanent fault*.

- Multiple faults are considered with the restriction that only one fault occurs at a time. As permanent faults are considered, they are all existent simultaneously in the system at the end, but there was sufficient time to repair a fault before the next one occurred.

- Faults are modeled at register level. With this restriction the internal design of basic elements need not be taken into account, and thus the faults can be simulated at different platforms and target devices (e.g. FPGA design vs. ASIC design).

## 2.2 Increasing Circuit Reliability

#### 2.2.1 Introduction

Ideally, a circuit shall never fail after it is switched on, i.e. have a reliability of 100%. Clearly this is not possible, as components degrade over time and the environment influences various parameters that might reduce the lifetime. In order to increase the reliability of a circuit, either faults have to be avoided (fault avoidance) or the application must be able to deal with faults (fault tolerance).

There exist basically three methods to improve the reliability of a circuit/system.

- 1. Reduce the stress the components are exposed to in order to reduce the failure rate and to add additional design margin (fault avoidance)

- 2. Use high quality (screened) components offering higher reliability and robustness against faults (fault avoidance)

- 3. Implement redundancy in the circuit (fault tolerance)

In the following sections these methods are described in more detail.

#### 2.2.2 Methods

#### **Component Stress**

The lifetime, reliability and performance of components are affected by several factors, such as e.g. voltage/current stress and temperature. Temperature is one of the main contributors that decrease the component reliability [16], and the relation between part failure rate and device temperature can be expressed by the Arrhenius law [62].

A very common approach to reduce the stress is to *derate* the design parameters, having the advantage that the higher reliability is "built-in" and does not need any further actions during operation. Derating rules and methods for analysis have been established and standardized by the industry, such as by the "European Cooperation for Space Standardization" [27], so that it's basically straightforward to provide evidence for the compliance to these rules. The drawback of component derating is that oversized components might be needed, which require more board space, are more expensive and often also have higher power consumption.

Recently methods for thermal de-stressing in integrated components [70] have been published, where the circuit is reconfigured to use redundant resources to reduce the stress of e.g. clock trees. Currently no results of field experiments are available to evaluate the practicability and gain in reliability in real applications.

#### **Component Quality**

Component screening means to expose components to stringent tests to find those with outstanding performance even under extreme conditions. It is obvious that such components are very expensive and have long lead times.

Particular processes have to be used to harden components against radiation effects. Unfortunately, these components often provide reduced electrical performance and have higher power consumption. Since dedicated design measures have to be applied, modern components are rarely available in hardened technology. Furthermore, such components are often subjected to export regulations which increases both lead time and cost. Basically, the trend currently goes towards building highly reliable systems from less reliable but cheaper components [4].

As for the parameter derating, the higher reliability is "built-in" and does not need to be handled during operation. Software tools for reliability calculations according to established models, such as MIL-HDBK-217 [16], allow to assign the component quality for standardized screening so that the effect on the system can be analyzed very easily.

#### Redundancy

Redundancy means to add additional information to a data path so that it is possible to determine at least the correctness of data, or even to correct it in case of errors. Basically, redundancy can be applied (i) in time (e.g. dual calculation), (ii) in the value domain (e.g. correcting codes) or (iii) in hardware. While time redundancy and codes are well suited to correct effects caused by transient faults, only hardware redundancy is able to handle permanent errors. Subsequently, whenever the term "redundancy" is used, it refers to hardware redundancy.

In hardware redundancy alternate paths in a circuit/system are implemented that take over in case of a failure, or provide additional information that is used by voters to take a decision on the correctness of results.

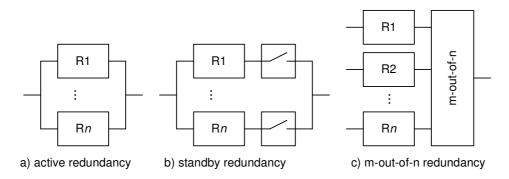

Redundancy can be distinguished into *active redundancy* (Figure 2.1a) and *standby redundancy* (Figure 2.1b). In active redundant systems the spare resources are continuously powered simultaneously with the nominal circuit, e.g. two power supplies that are ORed with diodes. A particular active redundant system is *N-modular redundancy* (Figure 2.1c), where the majority m-out-of-n redundant results is used. The most common and widely accepted majority voting system is the *Triple Modular Redundancy* (TMR) structure, where the results of three paths are evaluated by a majority voter.

In a standby redundant system the spare elements are by default powered down and put into operation when the nominal circuit fails. Standby redundant systems need a dedicated fault detection logic and a controller which performs all necessary boot actions (e.g. transferring internal states), i.e. the circuit/system will be down for some time. A redundant system with one parallel path is also called *duplex system*, and is usually used in standby redundancy.

Redundancy can be implemented on different levels and in different granularity. In general, component redundancy is superior to system redundancy ([115], chapter 3.3) because the finer

granularity implies more alternate paths<sup>1</sup>. However, implementing redundancy is a complex task and not all theoretical solutions can be realized. Switches, voters and redundancy controllers significantly contribute to the system reliability, as they add series elements in the reliability path and thus lower the overall reliability. Particular techniques might be necessary, e.g. to split the triplicated logic and the voter into different components [121]. Furthermore, components can not always be parallelized (e.g. two brake pedals in a car would be an impractical solution; also electrical components cannot simply be put in parallel). The impact of the series elements and additional interconnect resources also puts practical limits on the granularity of redundant systems [1].

Figure 2.1: Redundancy Techniques

Finally, it must be considered that detection, diagnosis and repair circuits add additional resources to the application, that itself are susceptible to faults and thus limit the achievable reliability.

Triple Modular Redundancy (TMR) is one of the most popular techniques and can be implemented on gate as well as an system level [109]. Tools are available that assist the implementation during the design process [12,13]. Such structures can even be implemented e.g. in flip-flop resources in FPGAs [8] to make them tolerant against SEUs.

Typically, TMR is well suited to increase the tolerance against transient faults, as the result will be correct without delay and additional diagnosis. As in case of SRAM FPGAs a SEU can change the circuit structure, a possible approach is to triplicate the design (three identical FPGAs) and use an external voter [109]. If an error is detected, the correct FPGA configuration can be recovered by partial reconfiguration [131, 132] without affecting the functionality of the operating circuit. Similar approaches are described in [122] and [121]. In [121] three soft CPU's are implemented in an SRAM based FPGA and are voted externally by a rad-had antifuse FPGA. In case of an error the SRAM-based FPGA is scrubbed to recover from the upset. However, the internal states are lost by this action. The Maxwell Super Computer for Space SCS750 [122] contains three non-rad-hard PowerPC's and a rad-hard voter FPGA to detect the errors and control the recovery actions. Once an error occurs, the processor registers are stored, the processors are reset and then the old register contents are restored to be able to start from the previous state.

<sup>&</sup>lt;sup>1</sup>Note that "component" does not necessarily mean "electrical component" in this context. A component could e.g. be a turn indicator in a car.

In [67, 77] TMR based approaches combined with time-redundancy are presented, in order to reduce the area overhead. The results show that it depends both on the type of data structure that shall be protected (throughput logic, state-machine logic, I/O logic, special features) and the location of the voter (only at the last output, inside the design) how efficient and costly the implementation is.

For permanent faults TMR soon reaches its limits as after two faults in different redundancy elements it is not possible any more to correctly conclude on a majority. TMR in its basic variant is thus only effective for short mission times unless repair is possible [115, 134]. Various methods for TMR systems to improve the long-time reliability are proposed in [29, 30, 35, 36], however, they can only handle soft errors in the configuration memory but not real hardware defects, so these approaches are not considered any further within this thesis. To lengthen the mission time, it is necessary to handle permanent errors by changing the circuit structure and replacing defective elements by working ones, e.g. as proposed in [65]. In [129] an evolutionary voting system is described, where a genetic algorithm tries to bring a faulty module back to operation. The results indicate that this approach could be useful, however, only simulations with a simple model of an FPGA have been performed.

In synchronous circuits implementing a TMR system is straight-forward, as all results are available at the same time instant. TMR in asynchronous circuits is a bit more complex, as a fault in the asynchronous logic could prevent the result to appear at the output and thus block the comparison permanently [102]. In [41] a modified TMR architecture is proposed that can be used also for asynchronous circuits.

#### **2.3** Introduction to Asynchronous Logic

This chapter gives an overview about asynchronous logic in order to understand the described self-healing concept later on. For details the reader is referred to e.g. [47, 78, 92, 120].

#### 2.3.1 General

Digital circuits can be distinguished into two significant areas - *synchronous logic* and *asynchronous logic*. While any transition in synchronous logic is triggered by a clock, which thus defines the timing of the whole circuit, asynchronous logic relies on other mechanisms.

One big advantage of the discrete timing in synchronous logic is that the logic states are only relevant at a clock edge. Between the clock edges the signals may enter other states, e.g. due to faults, without having any effect on the circuit functionality. This property simplifies the circuit design, but implies a restriction on the maximum reachable speed. The circuit must be designed to achieve the design goal even under worst case propagation delays, setup and hold times.

Asynchronous circuits do not require a clock, instead a local handshake provides the information that new data is available and ready to be processed. The speed of the circuit is therefore determined by the propagation delay of the involved elements, and data is processed when it is available, and not at discrete times.

Apart from several other benefits compared to synchronous logic, such as lower power consumption [81, 127] and lower electromagnetic emissions [81, 99], the main advantage of asynchronous logic with respect to this thesis is the inherent robustness against faults. Due to the insensitivity to circuit timings, a lot of environmental effects, such as thermal drifts, do not influence the behavior of the design.

Although this basically sounds excellent for electronic circuits, asynchronous logic also has some drawbacks. Currently, there exist no comfortable design tools, the design itself is more complex and it requires more resources than synchronous logic. Furthermore, although research on asynchronous FPGAs is ongoing [48, 123], there are no commercial prototyping environments available, which makes integration tasks very difficult. As will be shown later, it is possible to use standard FPGAs to implement asynchronous designs, however, the results with respect to resource effort, timing and efficiency are not very representative, as these FPGAs are optimized for synchronous designs.

#### 2.3.2 Classification of Asynchronous Circuits

Asynchronous logic can be distinguished into two main models:

- the bounded delay model, which constrains gate and wire delays

- the *unbounded delay model*, which admits arbitrary delays at least for some parts of the circuit

Synchronous circuits follow the bounded delay model, as it is assumed that all transient states have settled to a steady state before the next clock edge occurs. Asynchronous circuits following the bounded delay model require particular timing assumptions and are also referred to as *self-timed* circuits [47].

Two families of asynchronous circuits following the unbounded delay model can be distinguished, which are the *speed independent* (SI) and *delay insensitive* (DI) circuits. While speed independent circuits assume positive but unknown delays in gates and zero delays on wires, delay insensitive circuits do not apply any restriction on delays in gates and wires. The family of delay insensitive circuits is, however, restricted to circuits consisting only of Muller-C gates and inverters [79], which limits its usability for practical applications. The class of *Quasi Delay-Insensitive* (QDI) circuits is a bit less restrictive, and allows unbounded delays with the exception of *isochronic forks*. These forks anticipate that all transitions starting at the root of a fork reach the end at the same time, i.e. the difference of the branch delay is negligible. This assumption is feasible from a practical point of view, and the class of circuits becomes much bigger. If all forks in a circuit are isochronic, the circuit can be considered to be speed independent. In a practical implementation, isochronic forks can be achieved on gate level (gates, registers), where matched delays are easier to control. The connection between such blocks is then delay insensitive [118].

#### 2.3.3 Asynchronous Protocols

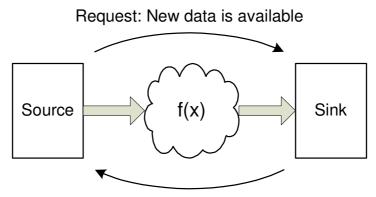

Without a clock, the validity and capturing of new data must be determined by some kind of *handshake protocol*. As shown in Figure 2.2, a *request event* is needed to inform the receiver

that new data is available, and an *acknowledge event* to inform the sender that the data has been captured. During fault-free conditions these two events will alternate.

Acknowledge: Data has been captured

Figure 2.2: Handshake Principle in Asynchronous Circuit

In synchronous circuits no handshake is needed, as the clock signal serves as global event that triggers any storage of data. In asynchronous logic different handshake protocols are possible, which can be distinguished e.g. by their encoding (level or transition) or by the number of protocol phases [53, 59, 86, 92, 117, 125].

The following section provides an overview about *Four State Logic* (FSL), also known as *Level Encoded Dual-Rail Signalling* (LEDR), which is the design style the self-healing concept is based on.

#### 2.4 Four-State-Logic

#### 2.4.1 General

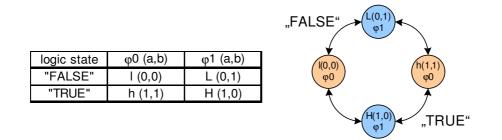

FSL is a *Quasi Delay Insensitive* asynchronous design style [118] that uses a two-phase handshake protocol. Consecutive data is separated by two alternating, diverse code sets  $\varphi 0$  and  $\varphi 1$ , called *phases*. Figure 2.3 shows the encoding and transition between the boolean values TRUE/ FALSE denoted as 'h'/'l' in phase  $\varphi 0$  and 'H'/'L' in  $\varphi 1$ . Each logic value is encoded by the two signal rails *a* and *b* [15]. A data vector is called *token*.

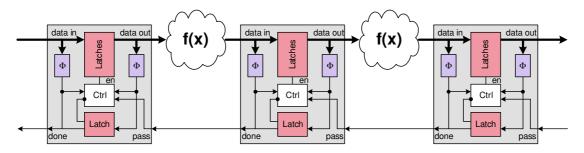

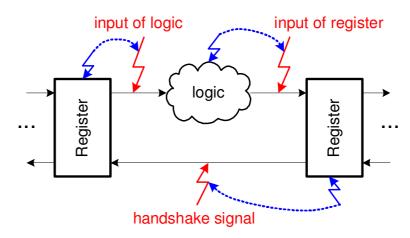

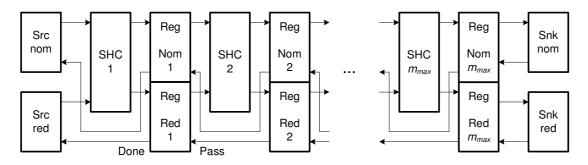

The data path of FSL circuits is modeled similarly as Sutherland's micropipeline [120] and is shown in Figure 2.4.

It comprises *capture-done registers* with combinational functions between the stages. The registers handle the handshake protocol, as they only capture and pass through new data if the subsequent stage has stored the current data.

The combinational functions between the particular pipeline stages are calculated by FSL gates, having an inherent synchronization mechanism: A new output is only generated when all inputs are in the same phase, otherwise the old output is preserved. This property is called

Figure 2.3: FSL Encoding and State Transitions

Figure 2.4: FSL Pipeline Structure

*strongly indicating*<sup>2</sup>. Thus, even a pure combinational function requires storage elements, which generates considerable area overhead compared to common single-rail logic.

An FSL based asynchronous embedded processor has already been successfully implemented [15].

#### 2.4.2 Combinational Logic

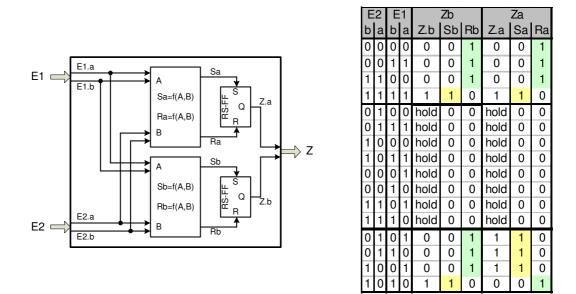

FSL combinational functions can be designed with basic gates, such as AND, OR, XOR, etc. functions. With these basic gates larger and more complex circuits can be built by connecting them together such as with "normal" synchronous logic gates. As an example, an FSL AND gate is described in detail. Table 2.1 shows the truth table on signal levels for a 2-input FSL AND gate.

If the inputs are consistent and have the same phase, the AND function is applied, and the output is generated in the same phase as the inputs. For all other cases the last valid output is preserved (designated with "hold"). This means that storage elements are needed in combinational FSL functions, as shown in Figure 2.5.

On rail level the truth table needs to be defined for two rails per signal (input). For each rail of the output a logic function is required that generates the respective set and reset signals for the RS flip-flops.

$<sup>^{2}</sup>$ In *weakly indicating* asynchronous logic single bits could already change, while the whole vector is still not valid.

| 7  | , | E1   |      |      |      |

|----|---|------|------|------|------|

| 2  |   | h    |      | Н    | L    |

|    | h | h    |      | hold | hold |

| E2 | Ι | Ι    |      | hold | hold |

| L2 | Н | hold | hold | Н    | L    |

|    | L | hold | hold | L    | L    |

Table 2.1: 2-Input FSL-AND Truth Table (Signal Level)

Figure 2.5: Schematic of 2-Input FSL AND Gate and Truth Table on Rail Level

#### 2.4.3 Registers

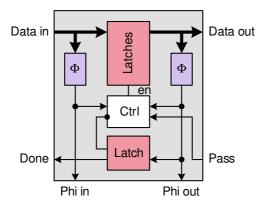

An FSL register (Figure 2.6) contains phase detectors at the input and output and control logic for the handshake control. The phase detectors check that all input signals are within the same phase. If this is not the case, the phase detector output corresponds to the last phase. The input phase detector  $\Phi$  enables the internal latches when all inputs are in the same phase, while the output phase detector freezes the latches after the complete data has been captured. Finally, an acknowledge signal informs the preceding stage to issue new data. To store new data, (i) the phase of the latched data inside the register must differ from the phase of the data applied to the register inputs and (ii) the subsequent stage must have acknowledged that it is ready for new data, i.e. it has captured the last token.

In order to distinguish the handshake signals, the following terms are used within this thesis:

- *Done* is an output of the register and indicates that the register has captured new data. The logic state equals the phase of the captured data. This signal is fed towards the *Pass* input of the preceding register.

- *Pass* is an input to the register and indicates that the subsequent register has captured the last issued data. This signal is coming from the *Done* output of the subsequent register.

Figure 2.6: FSL Register

#### 2.4.4 Timing Parameters

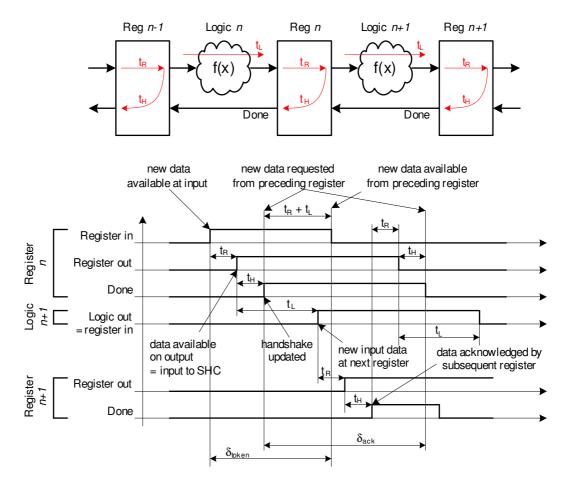

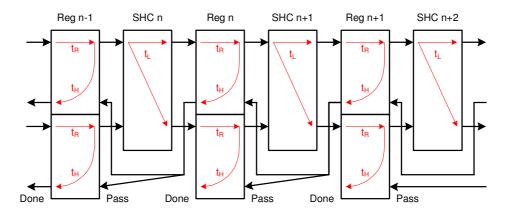

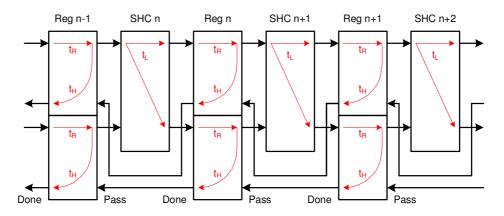

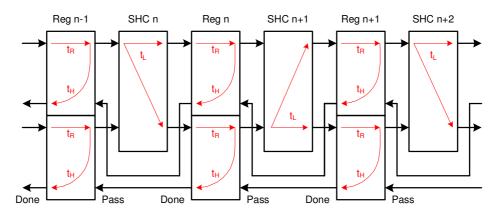

The following three timing parameters have to be considered in an FSL pipeline. Figure 2.7 shows the meaning of these parameters in a timing diagram.

- $t_R$  is the time data needs to propagate from a register input to the output.

- $t_H$  is the time between availability of new data at the register output until the *Done* signal is set accordingly.

- $t_L$  is the time the data needs to propagate through the FSL logic f(x).

A register will become ready to capture a new token if (i) it has captured the last valid token and (ii) it has received the corresponding acknowledge from the subsequent pipeline stage. The capturing process can be triggered by two conditions, depending on whether a new token or the acknowledge signal is provided earlier:

Figure 2.7: Timing Parameters

- 1. If the last captured token i was acknowledged to register n by the subsequent register (n+1) before a new token (i+1) in the other phase is provided to the input of register n, the new capturing process will start as soon as the new token is available at the input of register n.

- 2. If the preceding stage (n-1) provides a new token (i+1) to the input of register n before the subsequent stage (n+1) has acknowledged the last token i, the new capturing process at register n will start as soon as the acknowledge signal (*Done* output of register (n+1)) is received on the *Pass* input of register n.

In case of a stuck-at fault either the new token is inconsistent and will thus not be processed, or the acknowledge signal has the wrong state. In both cases the capturing process will not be started. Transient faults causing toggling signals could even lead to the loss of tokens [28], but transient effects are out of scope for this thesis and thus not considered in the following definitions.

The time  $\delta_{ack}$  is defined as the duration between two subsequent toggles of the *Done* signal of the same register, and  $\delta_{token}$  is the duration between two subsequent tokens (in alternating phases) being available at the same register input. In order to guarantee a correct capturing two constraints must be fulfilled:

**Constraint 1** The register n must not receive the acknowledge from the subsequent stage (n + 1) for capturing token i before register n has captured the token i and has acknowledged this to the preceding stage (n - 1):  $\delta_{ack}(n + 1) > t_R(n) + t_H(n)$

**Constraint 2** Any register must not receive a new token at its input before the last token has been captured and acknowledged:  $\delta_{token}(n) > t_R(n) + t_H(n)$

If any of these constraints is violated, the register might either not capture the data or capture wrong data. In a standard pipeline as shown in Figure 2.7  $\delta_{ack}$  is determined by the time the preceding stage (n - 1) needs to provide new data after stage n has issued the *Done* signal (return path), and by the time the subsequent stage (n + 1) needs to capture the last token and assign the *Done* signal correctly (forward path).

Equation 1  $\delta_{ack} = max(\delta_{ack,min}(return); \delta_{ack,min}(forward))$

**Equation 2**  $\delta_{ack,min}(return)(n) = t_R(n-1) + t_L(n-1) + t_R(n) + t_H(n)$

**Equation 3**  $\delta_{ack,min}(forward)(n) = t_L(n) + t_R(n+1) + t_H(n+1) + t_R(n)$

Note: Equation 2 describes the minimum time, assuming that register (n-1) receives valid inputs fast enough.

The duration  $\delta_{token}$  is defined by the time the register *n* needs to capture the token *i* and by the time the new token (i + 1) needs to propagate from the preceding stage to the input of register *n* after the *Done* signal was asserted.

**Equation 4**  $\delta_{token,min}(n) = t_R(n) + t_H(n) + t_R(n-1) + t_L(n-1)$

In a practical implementation constraint 2 is always fulfilled in the fault-free case because register (n-1) will not become transparent and issue a new token (i + 1) before register n has acknowledged the capturing of token i. Constraint 1 would only be violated if the handshake path of register n would be slower than the sum of data and acknowledge path of stage (n + 1), which can easily be avoided by careful routing.

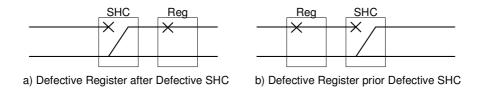

#### 2.4.5 Faults in Asynchronous Circuits

Asynchronous circuits behave different to synchronous circuits in many points. They are insensitive to timing variations and are therefore robust against many radiation effects that affect timing [60]. However, SEUs can cause deadlocks or other types of erroneous behavior. Traditional methods such as TMR cannot easily be applied to asynchronous circuits, as a fault in the asynchronous logic could prevent the result to appear at the output and thus block the comparison permanently [101, 102].

A detailed investigation of the effect of various fault types on asynchronous circuits is presented in [76, 80]. Methods to harden asynchronous circuits against transient faults/errors are presented in [60, 61, 88–90, 108] but are not considered any further in this chapter as the thesis focusses on permanent errors. In [103] and [49] various methods of testing asynchronous circuits are presented.

With FSL registers and combinational logic designed as described above, only consistent data will propagate through a pipeline. Permanent faults at the handshake lines between elements or at the data inputs/outputs will either directly stop the handshake process or cause inconsistent data and indirectly lead to a deadlock. Any permanent fault inside the elements (e.g. register control logic) will show an effect on the external interfaces (e.g. inconsistent data, wrong handshake signal, etc.) and thus can be covered by an appropriate fault model on pipeline level (for details refer to chapter 4).

However, the anticipation that only consistent data is processed in an FSL pipeline is only true on boolean level, i.e. in the fault-free case. As soon as a permanent fault exists in an FSL circuit it is not hazard-free any more. As will be shown below, this can lead to the case that consistent, but wrong data moves through the pipeline.

As an example, such a case is given for the FSL AND gate described in a previous section. A fault at the b-rail of input E2 shall be assumed. The applied tokens will thus be changed to inconsistent tokens if the affected rail would have a different logic state than appears due to the fault.

Figure 2.8 below presents the Karnaugh map for the Set-signal of the latch defining the arail of the output. Table 2.2 lists a sequence of input tokens to the AND gate, the resulting input pattern due to the fault and the effect if the transition causes a hazard. It can be seen that due to the fault there exist transitions which can cause hazards and generate consistent data values, which are, however, wrong.

|       | Sa     |        |        |        |       |  |  |

|-------|--------|--------|--------|--------|-------|--|--|

|       | E2.b   | /E2    | 2.b    | E2.b   |       |  |  |

| E2.a  | 1 (hh) | 0 (Lh) | 1 (LL) | 0 (hL) |       |  |  |

|       | 0 (Hh) | 0 (lh) | 0 (IL) | 1 (HL) | E1.a  |  |  |

| /E2.a | 0 (HH) | 0 (IH) | 0 (II) | 0 (HI) |       |  |  |

| E2.a  | 0 (hH) | 1 (LH) | 0 (LI) | 0 (hl) | /E1.a |  |  |

|       | E1.b   |        | /E1.b  |        |       |  |  |

Figure 2.8: Karnough Chart of Sa Signal for 2-Input FSL AND Gate

This issue has not been treated within this thesis, as it is an inherent problem of FSL logic and needs to be handled on higher level. A detailed investigation of such timing dependent effects and their probability of occurrence can be found in [28].

For the simulations and experiments the combinational logic has been chosen appropriately so that the described effect does not occur. Details are described in chapter 5.

| A  | pplied |               | Faul | ty Token | Transition | Output | Expected | Status |

|----|--------|---------------|------|----------|------------|--------|----------|--------|

| 11 | (0000) | $\Rightarrow$ | lH   | (0010)   |            |        |          |        |

| LL | (0101) | $\Rightarrow$ | Lh   | (0111)   | via LH     | L      | L        | O.K.   |

| hl | (1100) | $\Rightarrow$ | hH   | (1110)   | via hh     | h      | 1        | WRONG  |

| LL | (0101) | $\Rightarrow$ | Lh   | (0111)   | via LH     | L      | L        | O.K.   |

| hl | (1100) | $\Rightarrow$ | hH   | (1110)   | via hh     | h      | 1        | WRONG  |

Table 2.2: Exemplary Token Sequence and Effect for Faulty FSL Logic Input

# CHAPTER 3

### State of the Art of Circuit Reconfiguration

#### 3.1 Introduction to Autonomous Self-Repair

So far, achieving high hardware reliability in critical applications (e.g. for space missions) was only possible by combining the three measures (i) reducing component stress, (ii) increasing component quality and (iii) implementing redundancy (see section 2.2.2). It is quite obvious that traditional repair, e.g. exchanging a defective component, cannot be performed as soon as the affected electronics is in space. Consequently, since the fault density is increasing [1], the traditional methods of reducing component stress and screening the components might not be sufficient any more.

Redundant systems are typically designed to be tolerant against a single fault. After the first fault the redundant part can take over, but a second fault occurring in the redundant part will lead to a system failure.

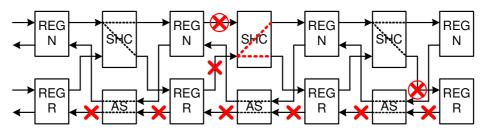

One possible way to improve the tolerance also against multiple faults and to increase the reliability is to repair the faulty part to bring it back to operation. If the circuit/system cannot be repaired by exchanging hardware elements, the circuit must be reconfigured so that defective resources are bypassed and replaced by working ones. Systems that can perform such repair-actions autonomously are called *self-healing* systems.

The term *self-healing* and its differentiation to fault-tolerance is extensively discussed [71] and still not clearly defined. One basic identification is that for fault tolerance the aim is to keep the system at 100% functionality, while self-healing systems allow to operate at less than 100% after the healing procedure [111].

The following definitions of self-healing were published:

- *Tosi* [126] describes the need for *self-management* to handle the increasing complexity of computing systems. Due to the increasing state-space of fault combinations not all effects can be foreseen. As a consequence, systems that can adopt to new situations and conditions as they arise are needed. *Self-healing* is one important category of self-management and is defined as "*the system ability to examine, find, diagnose and react to system mal-functions*".

- According to Saha [112], who describes a software-based self-healing system, "self-healing deals with imprecise specification, uncontrolled environment and reconfiguration of system according to its dynamics".

- *Gericota* [36] describes self-reconfiguration (of FPGAs) as a "method to give the currently configured functions the control of (re-)configuring areas of the same FPGA".

- Rodosek et.al [111]: "A system is showing the self-healing characteristic if it is able to monitor and heal itself from the inside, which requires the ability of this system to decide about and perform recovery actions to return itself to a behavior conforming to its initial specification, especially without external interference".

- *Laster* et.al [113] describes self-healing as a closed-loop cycle, where the processes "monitoring", "error detection and diagnosis", "analysis and selection of a repair operation" and "execute repair and operation (self-repair)" are continuously followed.

Self-repair is already state-of-the-art in regular circuit structures such as memories [54]. In irregular circuits self-repair is a complex task, but gains more and more interest as redundant resources can be used in a much finer granularity and distributed redundancy and repair (distributed self-healing) can significantly increase the circuit's lifetime [105].

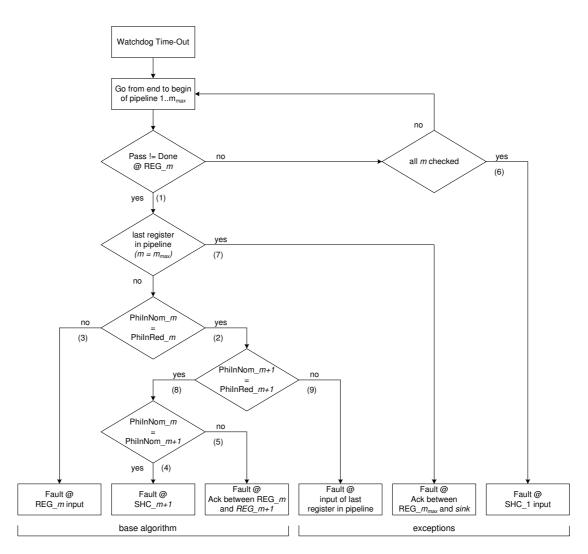

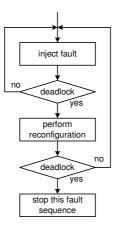

A self-healing system thus must be able to perform autonomously the following tasks:

- 1. fault detection: detect the fault, either offline or online

- 2. fault diagnosis: identify the faulty unit/element in the circuit/system

- 3. fault isolation: remove the faulty element from the operational circuit, e.g. by switches

- 4. redundancy allocation: replace the defective parts by redundant elements

- 5. repair validation: test/validate the performed repair

Within this thesis the self-healing procedure (circuit reconfiguration) shall be performed during runtime, thus not only the logic functionality and the interconnections, but also the internal states have to be restored. The following section assesses the possibilities for circuit reconfiguration in integrated digital circuits. A summary and conclusion about the suitability for self-healing is presented at the end of this chapter.

#### 3.2 Circuit Reconfiguration

#### 3.2.1 Runtime Reconfiguration with FPGAs

This section does not describe a dedicated method for circuit reconfiguration, but gives a general overview about FPGAs and in particular about those that offer (runtime-) reconfiguration capabilities. This feature can be used in several approaches described in the subsequent paragraphs.

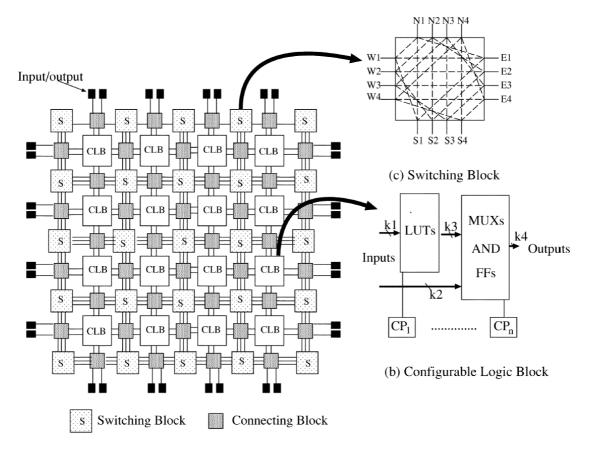

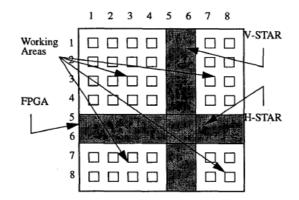

Field Programmable Gate Arrays (FPGA) are integrated circuits that consist of configurable logic blocks (CLBs), vertical and horizontal routing paths, and programmable interconnections (switch boxes). Figure 3.1 [18] shows the basic architecture of an FPGA. The actual function of the circuit as well as the interconnections are programmed by the user. Depending on the type of FPGA the configuration is either stored in an internal SRAM (*SRAM-based FPGA*, e.g. [10, 56]), which can also be updated, or by burning fuses (*anti-fuse FPGA*), which results in one-time-programmable devices [5].

(a) FPGA Structure

Figure 3.1: Basic FPGA Architecture [18]

In the past FPGAs were mostly used for prototyping and low volume applications. Increased performance, memory size and flexibility of modern FPGAs, as well as lower costs, make them now an attractive alternative to ASICs.

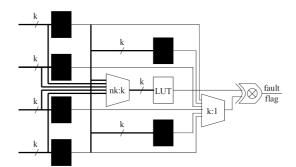

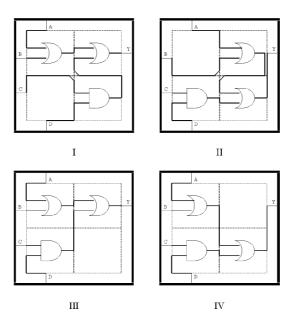

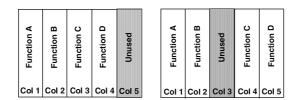

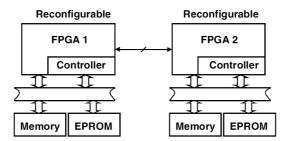

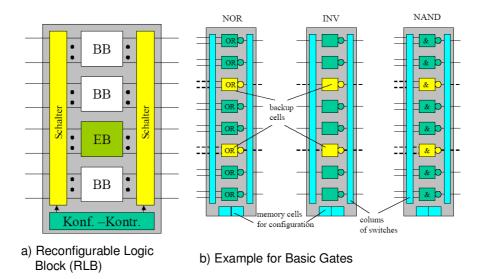

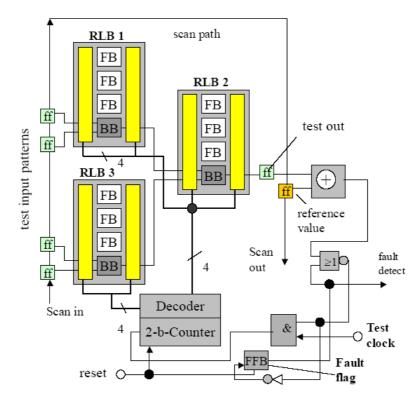

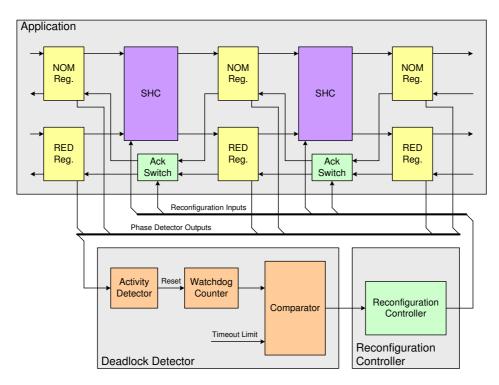

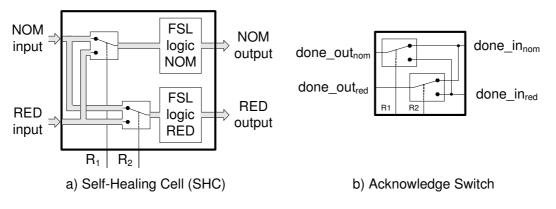

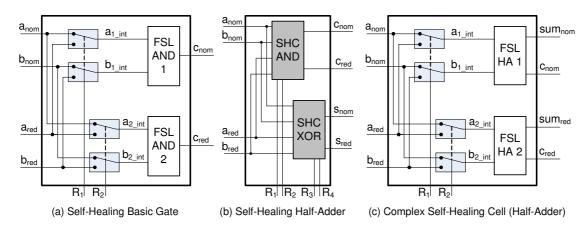

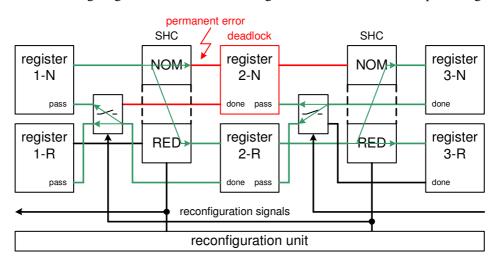

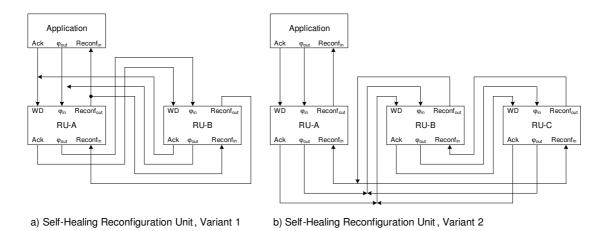

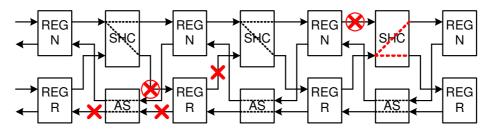

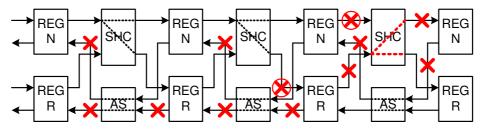

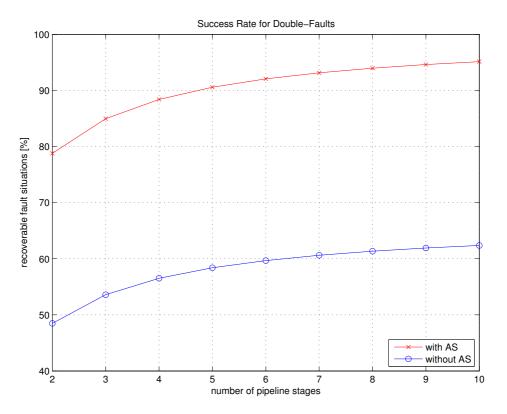

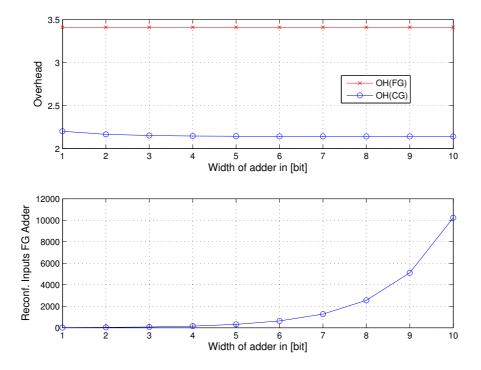

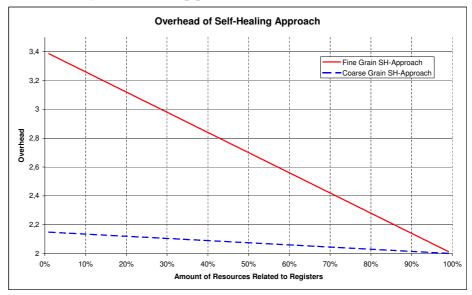

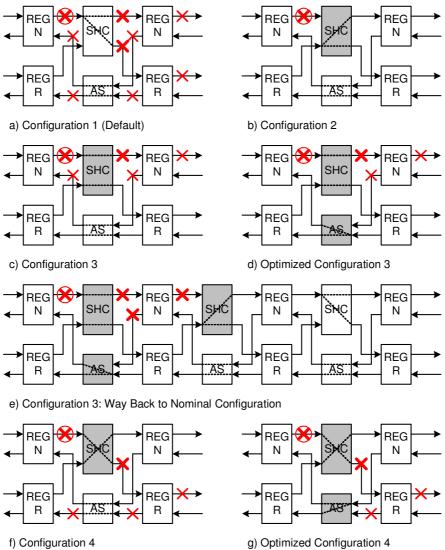

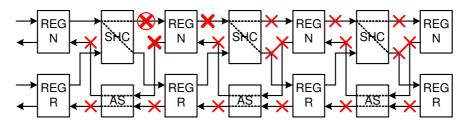

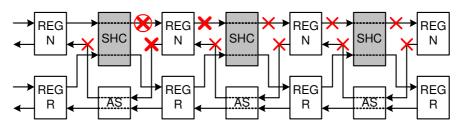

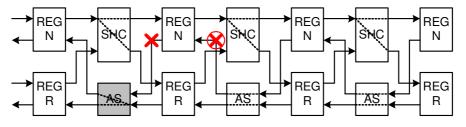

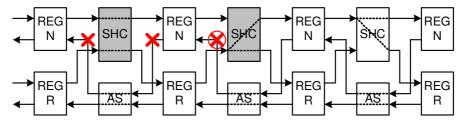

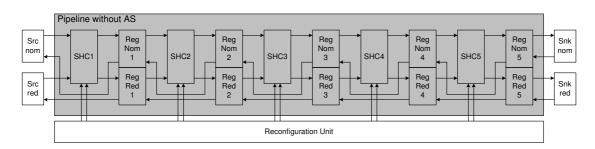

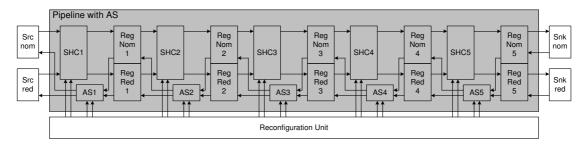

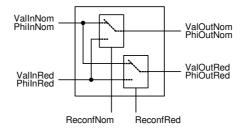

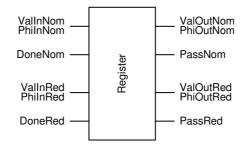

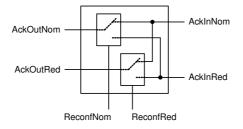

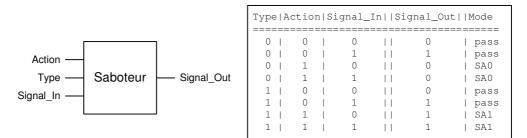

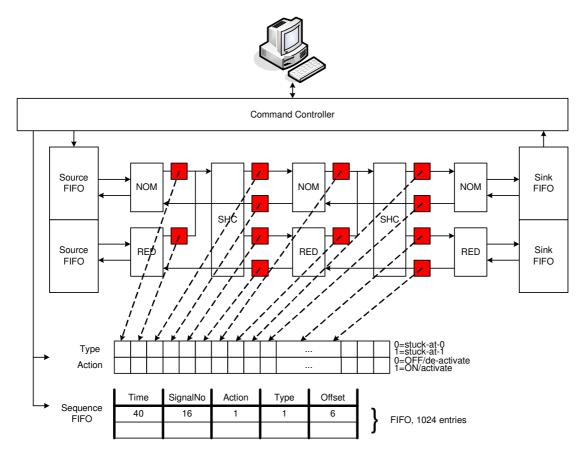

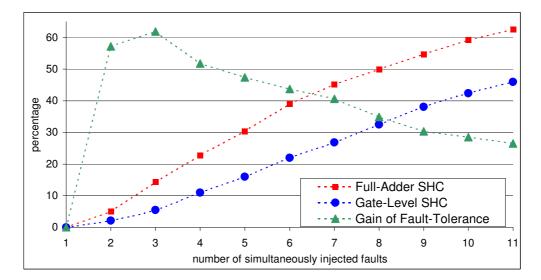

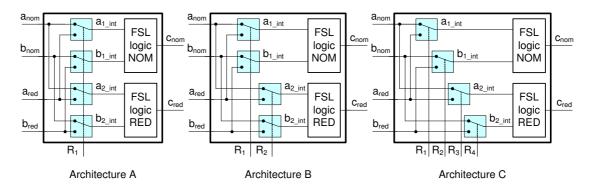

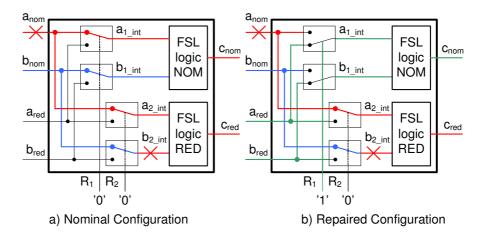

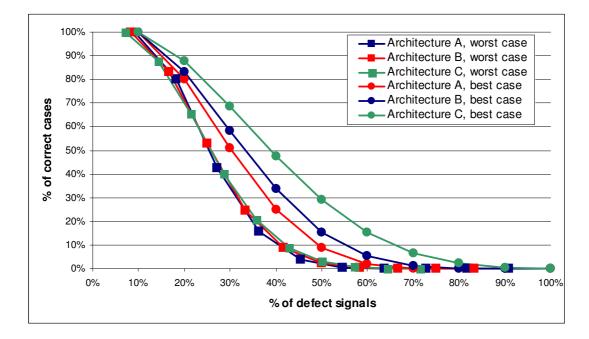

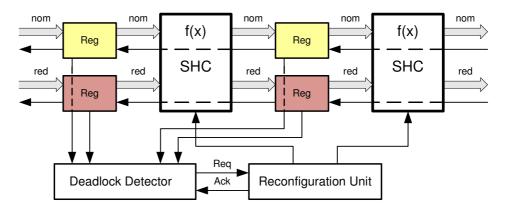

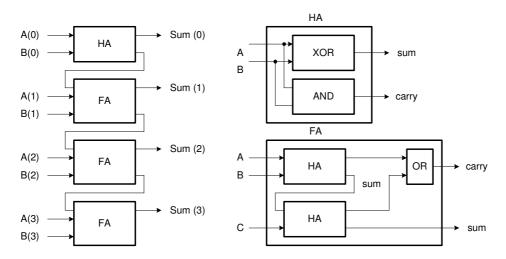

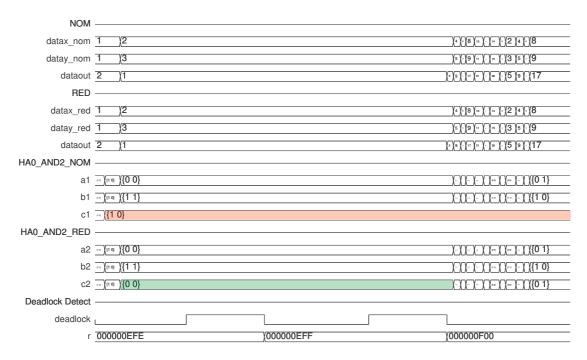

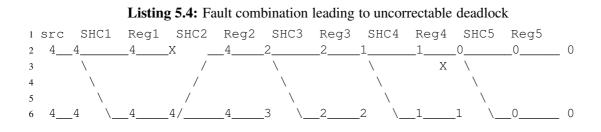

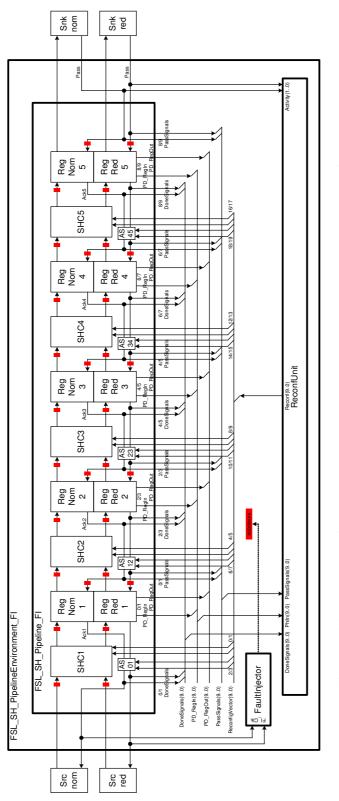

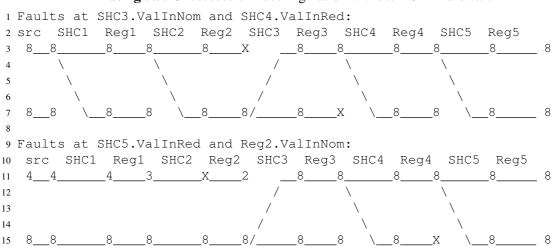

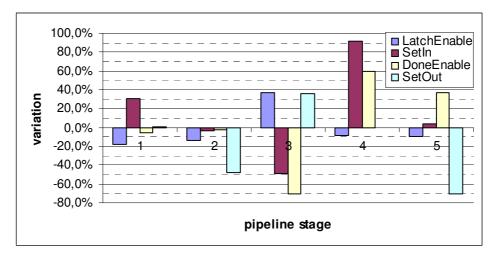

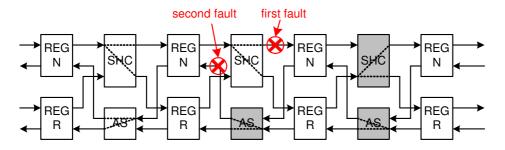

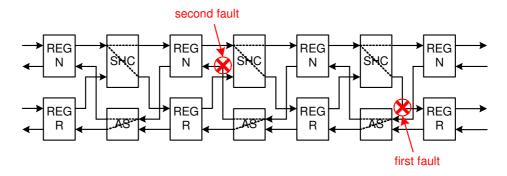

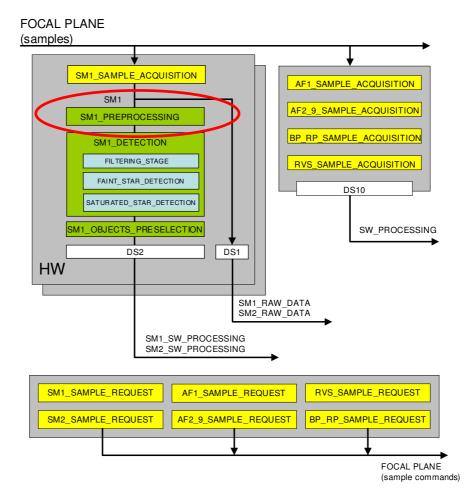

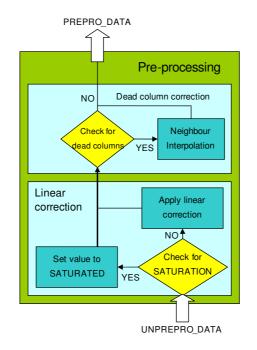

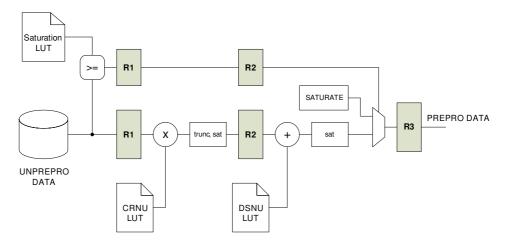

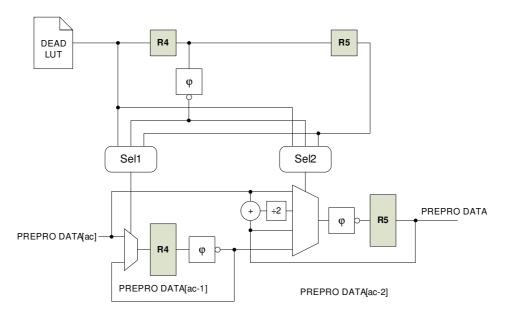

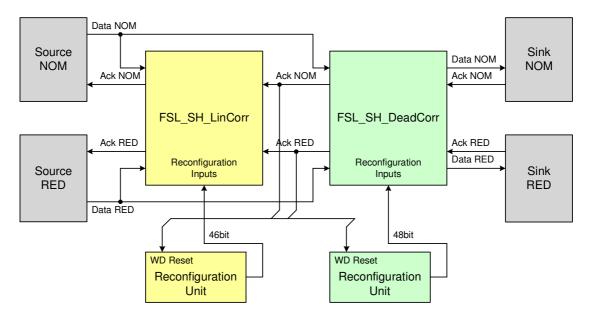

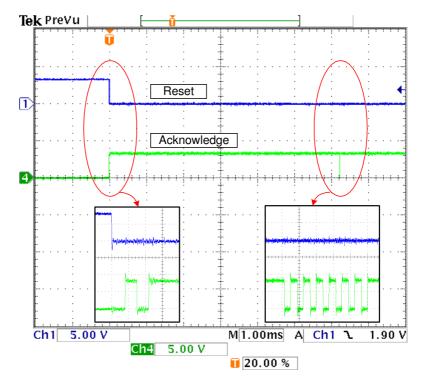

A rather new area of FPGA applications is *reconfigurable computing*, which allows to share hardware between different applications, to adapt hardware algorithms, increase the resource utilization, and allows to upgrade the hardware remotely [66]. Possible applications in this scope are e.g. reconfigurable accelerator processors in supercomputers [55], where algorithms are out-sourced into hardware to speed up calculations. The same component can be used for other calculations at a later point in time.