# Asynchronous Logic in Real-Time Systems

## DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

## Doktor der technischen Wissenschaften

by

Dipl.-Ing. Markus Ferringer

Registration Number 0025578

to the Faculty of Informatics at the Vienna University of Technology

Advisor: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger

The dissertation has been reviewed by:

(Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger) (Prof. Dipl.-Ing. Dr. Gerhard Fohler)

Wien, 15.12.2011

(Dipl.-Ing. Markus Ferringer)

# Erklärung zur Verfassung der Arbeit

Dipl.-Ing. Markus Ferringer Bäuerlegasse 3/10, 1200 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit - einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

# Kurzfassung

Es ist mittlerweile unbestritten, dass asynchrone Logik zahlreiche Vorteile im Vergleich zur herkömmlichen synchronen Logik hat. Ein zentrales Problem jedoch ist die schwierige Vorhersagbarkeit der zeitlichen Abläufe eines asynchronen Designs. Aufgrund eines fehlenden (hochpräzisen) Schwingquarzes hängt die tatsächliche Ausführungsgeschwindigkeit maßgeblich von Faktoren wie Umbgebungstemperatur und Versorgungsspannung ab, wobei bereits minimale Fluktuationen messbare Auswirkungen auf die Geschwindigkeit haben können. Klarerweise werden asynchrone Schaltungen daher als gänzlich ungeeignet für den Einsatz in Echtzeitsystemen angesehen. Diesem Umstand soll mit dem Projekt ARTS<sup>1</sup> (Asynchronous Logic in Real-Time Systems) entgegengewirkt werden, indem die genauen zeitlichen Charakteristika von ungetakteten Digitalschaltungen auf ihre Tauglichkeit für Echtzeitsysteme (und zwar speziell für das zeitgesteuerte Protokoll TTP) untersucht werden. Zu diesem Zwecke wird in dieser Arbeit ein geeignetes Zeitmodel entwickelt, welches neben deterministischen auch probabilistische Signallaufzeitvariationen modellieren kann. Darauf aufbauend wird ein sich automatisch auf den TTP Datenstrom kalibrierendes System entwickelt, welches eine geeignete (asynchrone) Zeitbasis für einen asynchronen TTP-Kontroller zur Verfügung stellt. Wie sich heraus stellt, sind unter allen Designalternativen jene mit linear rückgekoppelten Schieberegistern (LFSR) am besten für unsere Anforderungen geeignet. Um die Funktionsfähigkeit und Robustheit der vorgestellten Lösung zu demonstrieren, unterziehen wir das Design verschieden empirischen Tests, wie zum Beispiel Temperatur- und Spannungstests, und untersuchen die jeweiligen Auswirkungen auf Jitter und Frequenzstabilität.

In Verbindung mit den theoretischen Untersuchungen können einige sehr interessante Erkenntnisse im Zusammenhang mit zeitlicher Vorhersagbarkeit von asynchronen Schaltungen gemacht werden: Trotz der speziellen Eigenschaften des verwendeten Design-Stiles gibt es erheblichen datenabhängigen Signaljitter. Weiters wurde festgestellt, dass Herstellungsvariationen gravierenden Einfluss auf die Geschwindigkeit und Jittercharakteristika haben. Nichtsdestotrotz wirken sich diese Einflüsse nicht negativ auf die automatische Kalibrierung aus. Untersuchungen am fertigen und funktionierenden asynchronen TTP-Kontroller zeigen deutlich, dass es grundsätzlich möglich ist, asynchrone Logik für Echtzeitanwendungen — mit gewissen Einschränkungen — einzusetzen.

<sup>&</sup>lt;sup>1</sup>Das Projekt ARTS mit der Projektnummer 813578 wird vom FIT-IT Programm des Österreichischen Ministeriums für Verkehr, Innovation und Technology (bm:vit, http://www.bmvit.gv.at/) finanziert.

# Abstract

While asynchronous logic has many potential advantages compared to traditional synchronous designs, one of the major drawbacks is its unpredictability with respect to temporal behavior. Having no high-precision oscillator, a self-timed circuit's execution speed is heavily dependent on temperature and supply voltage. Small fluctuations of these parameters already result in noticeable changes of the design's throughput and performance. Without further provisions this jitter makes the use of asynchronous logic hardly feasible for real-time applications. In this work, which is part of project  $ARTS^2$  (Asynchronous Logic in Real-Time Systems), we investigate the temporal characteristics of self-timed circuits regarding their usage in real-time systems, especially the Time-Triggered Protocol. We propose a timing model capable of dealing with deterministic as well as probabilistic timings caused — besides others — by PVT (process, voltage, temperature) variations, and elaborate self-adapting circuits which shall derive a suitable notion of time for an asynchronous TTP controller. Out of the proposed variants we find the simple LFSR (linear feedback shift register) implementation with rate correction most promising for our purposes. We further introduce and analyze the jitter compensation concept, which is a three-fold mechanism to keep the asynchronous circuit's notion of time tightly synchronized to the remaining communication participants. To demonstrate the robustness of our solution, we perform different tests and investigate their impact on jitter and frequency stability. These tests include, e.g., varying operating temperature, changing core supply voltage, and process variations among several devices of the same type.

The experiments in combination with the theoretical analysis reveal some interesting insights for the temporal behavior of self-timed circuits: Even though the used design style is strongly indicating, considerable data-dependent jitter effects can be identified. It also turns out that process variations significantly influence the jitter characteristics and performance of asynchronous circuits. Nevertheless, the proposed self-adaptive time reference generation circuit is capable of tolerating different temporal conditions. Measurements with the fully functional asynchronous TTP controller reveal that it is indeed possible to use asynchronous logic in real-time systems. However, there are some major limitations (especially for actively sending messages in a time-triggered system) that must be considered.

<sup>&</sup>lt;sup>2</sup>The ARTS project received funding from the FIT-IT program of the Austrian Federal Ministry of Transport, Innovation and Technology (bm:vit, http://www.bmvit.gv.at/), project no. 813578.

For Daniela

# Contents

| 1        | $\mathbf{Pre}$ | face                                                                                                                                         | 1      |

|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------|

|          | 1.1            | Motivation                                                                                                                                   | 1      |

|          | 1.2            | Design Methodologies                                                                                                                         | 3      |

|          |                |                                                                                                                                              | 4      |

|          |                | 1.2.2 Globally-Asynchronous Locally-Synchronous                                                                                              | 6      |

|          |                | 1.2.3 Asynchronous Paradigm                                                                                                                  | 8      |

|          | 1.3            | Asynchronous Circuit Design                                                                                                                  | 0      |

|          |                | 1.3.1 Delay Models                                                                                                                           | 0      |

|          |                | 1.3.2 Micropipelines $\ldots \ldots 1^{4}$ | 4      |

|          |                | 1.3.3 Two-Phase Dual-Rail                                                                                                                    | 5      |

|          |                | 1.3.4 Application Examples                                                                                                                   | 8      |

|          | 1.4            | Asynchronous Design Flow                                                                                                                     | 0      |

|          | 1.5            | The Time-Triggered Protocol                                                                                                                  | 2      |

|          | 1.6            | ARTS - Aims and Contributions                                                                                                                | 5      |

|          |                | 1.6.1 Contribution $\ldots \ldots 22$                    | 7      |

|          | 1.7            | Chapter Organization                                                                                                                         | 8      |

| <b>2</b> | Inte           | erfacing Asynchronous Circuits 31                                                                                                            | 1      |

|          | 2.1            | Related Work                                                                                                                                 |        |

|          |                | 2.1.1 Synchronization Techniques                                                                                                             | 2      |

|          |                | 2.1.1.1 Loosely-coupled $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 32$                                                  |        |

|          |                | 2.1.1.2 Strongly-coupled                                                                                                                     | 3      |

|          |                | 2.1.2 Conversion Techniques                                                                                                                  | 4      |

|          | 2.2            | Lockstep Conversion                                                                                                                          | 5      |

|          |                | 2.2.1 LEDR to NCL                                                                                                                            |        |

|          |                | 2.2.2 NCL to LEDR                                                                                                                            |        |

|          |                | 2.2.3 Bundled Data as Consumer                                                                                                               | 0      |

|          |                |                                                                                                                                              | n      |

|          |                | 2.2.4 Bundled Data as Producer                                                                                                               | U.     |

|          | 2.3            |                                                                                                                                              | -      |

|          | 2.3            | Free Conversion                                                                                                                              | 2      |

|          | 2.3<br>2.4     | Free Conversion                                                                                                                              | 2<br>4 |

| 3        | Ten               | poral Characteristics 51                                                                                                                                       |

|----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 3.1               | Related Work                                                                                                                                                   |

|          |                   | 3.1.1 Jitter in Synchronous Circuits                                                                                                                           |

|          |                   | 3.1.2 Timing Analysis $\ldots \ldots \ldots$   |

|          | 3.2               | Jitter in QDI Circuits                                                                                                                                         |

|          | 3.3               | Circuit Timing                                                                                                                                                 |

|          |                   | 3.3.1 Data-Dependent Execution Jitter                                                                                                                          |

|          |                   | 3.3.2 Timing Variations                                                                                                                                        |

|          |                   | $3.3.2.1  \text{Interconnect Delay}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                          |

|          |                   | $3.3.2.2  \text{Gate Delays} \dots \dots$                |

|          | 3.4               | Case Studies                                                                                                                                                   |

|          |                   | 3.4.1 Measurement Setup $\ldots \ldots \ldots$ |

|          |                   | 3.4.2 Voltage-Temperature Characteristics                                                                                                                      |

|          |                   | 3.4.3 Data-Dependent Execution Jitter                                                                                                                          |

|          |                   | $3.4.3.1  4-bit Counter \ldots \ldots$  |

|          |                   | 3.4.4 16-bit Counter                                                                                                                                           |

|          | 3.5               | Chapter Notes                                                                                                                                                  |

| 4        | <b>A</b>          | nchronous Reference Time 73                                                                                                                                    |

| 4        | <b>Asy</b><br>4.1 | nchronous Reference Time       73         Related Work       74                                                                                                |

|          | 4.1               | 4.1.1 Design Options                                                                                                                                           |

|          |                   | 4.1.1.1 Distributed Clocks                                                                                                                                     |

|          |                   | 4.1.1.2 Self-Timed Oscillator Rings                                                                                                                            |

|          |                   | 4.1.2 Allan Variance                                                                                                                                           |

|          |                   | 4.1.3 PVT Variations                                                                                                                                           |

|          | 4.2               | Implementation Concept                                                                                                                                         |

|          | 1.2               | 4.2.1 Requirements                                                                                                                                             |

|          |                   | 4.2.2 Temporal Properties                                                                                                                                      |

|          | 4.3               | Implementation Details                                                                                                                                         |

|          | 4.4               | Experimental Results                                                                                                                                           |

|          |                   | 4.4.1 Measurement Setup                                                                                                                                        |

|          |                   | $4.4.2  \text{Comparison}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                    |

|          |                   | 4.4.3 Temperature Tests                                                                                                                                        |

|          |                   | 4.4.4 Supply Voltage Tests                                                                                                                                     |

|          |                   | 4.4.5 Fabrication Variations                                                                                                                                   |

|          |                   | $4.4.5.1$ Simulation $\ldots \ldots \ldots$    |

|          |                   | 4.4.6 Frequency Stability                                                                                                                                      |

|          | 4.5               | Chapter Notes                                                                                                                                                  |

| -        |                   |                                                                                                                                                                |

| <b>5</b> | v                 | Implementation Dataila 106                                                                                                                                     |

|          | 5.1               | Implementation Details1065.1.1Hardware106                                                                                                                      |

|          |                   | 5.1.1 Hardware                                                                                                                                                 |

|          |                   | 0.1.2 DULWALC                                                                                                                                                  |

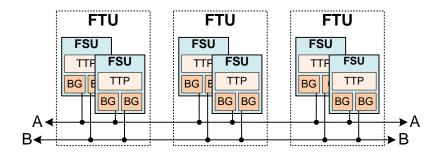

|   |      | 5.1.3  | TTP Cluster                 | 111 |

|---|------|--------|-----------------------------|-----|

|   | 5.2  | Limita | ations and Restrictions     | 114 |

|   | 5.3  | Experi | imental Results             | 115 |

|   |      | 5.3.1  | Passive Communication       | 115 |

|   |      | 5.3.2  | Active Communication        | 118 |

|   |      | 5.3.3  | Discussion                  | 121 |

|   | 5.4  | Chapte | er Notes                    | 124 |

|   |      |        |                             |     |

| 6 | Con  | clusio | n and Outlook               | 127 |

| A | Soft | ware I | Implementation              | 131 |

|   | A.1  | Regist | er Definitions              | 131 |

|   |      | A.1.1  | Status Register             | 131 |

|   |      | A.1.2  | Configuration Register      | 132 |

|   |      | A.1.3  | Timer Register              | 133 |

|   |      | A.1.4  | Control Register            | 133 |

|   |      | A.1.5  | LFSR Register               | 135 |

|   |      | A.1.6  | Asynchronous Timer Register | 135 |

|   |      | A.1.7  | Timestamp Register          | 136 |

|   | A.2  | Messag | ge Descriptor List          | 137 |

|   | A.3  | Messag | ge Data Structure           | 137 |

|   | A.4  | TTP A  | Application                 | 138 |

|   | A.5  | Index  | to LFSR conversion          | 139 |

|   |      |        |                             |     |

# List of Figures

| 1.1  | General flow control (handshaking) of logic circuits [20]                | 3  |

|------|--------------------------------------------------------------------------|----|

| 1.2  | The synchronous design paradigm.                                         | 4  |

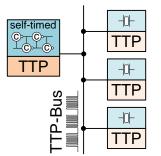

| 1.3  | Exemplary GALS system structure (Source: [83])                           | 7  |

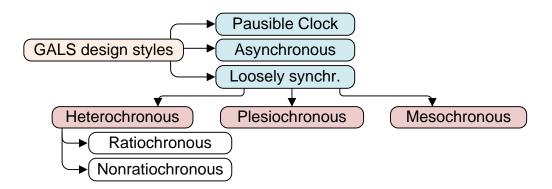

| 1.4  | GALS taxonomy (Source: [83]).                                            | 7  |

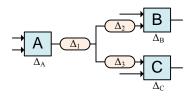

| 1.5  | Example circuit to illustrate different delay models (Source: [81]).     | 10 |

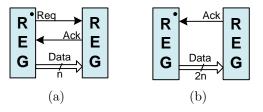

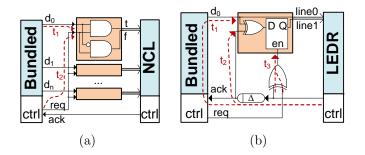

| 1.6  | Bundled Data (a) and Dual-Rail approach (b) (Source: [81]).              | 11 |

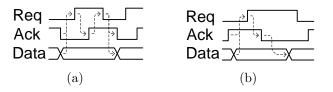

| 1.7  | Four-Phase (a) and Two-Phase bundled data protocol (b) (Source: [81]).   | 12 |

| 1.8  | 4-Phase Dual-Rail example waveform (a) and encoding (b) (Source: [81]).  | 12 |

| 1.9  | Micropipeline control structure without (a) and with data processing (b) |    |

|      | (Source: $[82]$ )                                                        | 14 |

| 1.10 | LEDR coding scheme (a) and exemplary LEDR waveform (b)                   | 16 |

| 1.11 | Example LEDR circuit structure                                           | 17 |

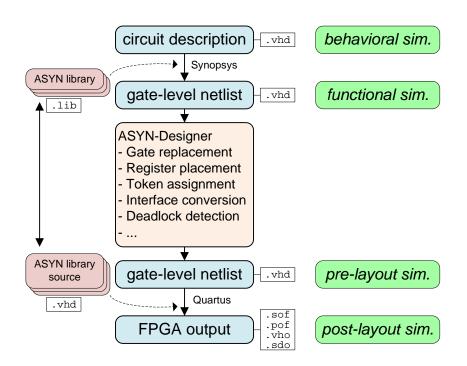

| 1.12 | ASYN design flow.                                                        | 21 |

| 1.13 | LEDR AND gate block diagram [19] (a) and technology mapping for Altera   |    |

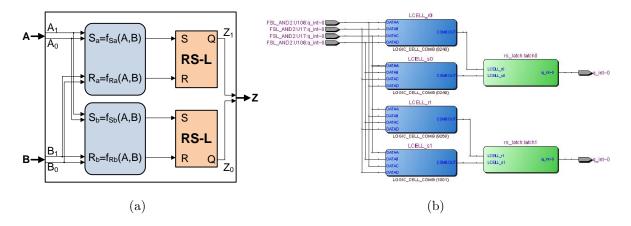

|      | Cyclone II FPGA (b)                                                      | 22 |

| 1.14 | TTP-system structure $[48]$                                              | 23 |

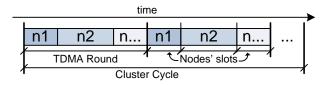

| 1.15 | Time Division Multiple Access scheme.                                    | 23 |

| 1.16 | ARTS system setup.                                                       | 25 |

| 1.17 | TTP-node block diagram.                                                  | 26 |

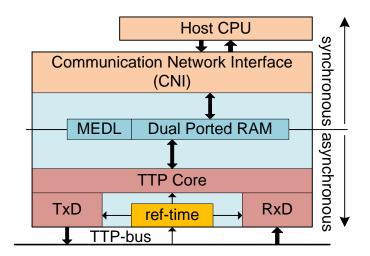

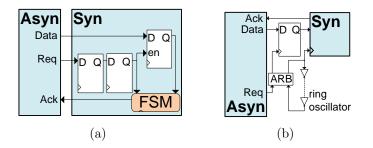

| 2.1  | Loosely coupled: 2-stage synchronizer (a), and stoppable clock (b)       | 33 |

| 2.2  | Strongly coupled: Request/Data driven (a), and Globally Synchronous Lo-  |    |

|      | cally Asynchronous (b).                                                  | 34 |

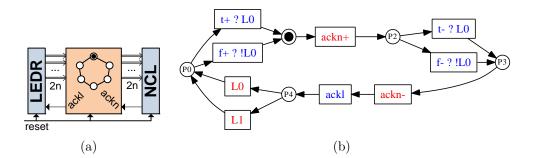

| 2.3  | Conversion interface for LEDR to NCL (a), and Petri-Net representation   |    |

|      | (b)                                                                      | 35 |

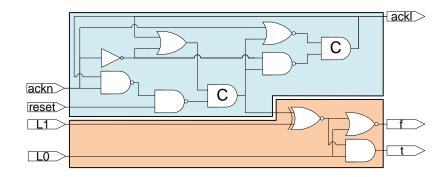

| 2.4  | Synthesized conversion circuit.                                          | 37 |

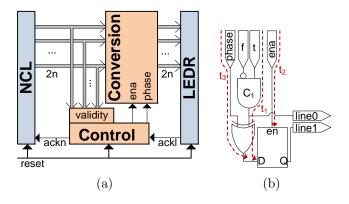

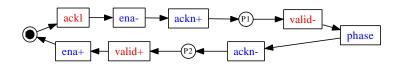

| 2.5  | NCL to LEDR block diagram (a) and single bit conversion circuit (b)      | 38 |

| 2.6  | NCL to LEDR Petri Net representation.                                    | 38 |

| 2.7  | Conversion circuit for bundled data to NCL (a) and LEDR (b)              | 41 |

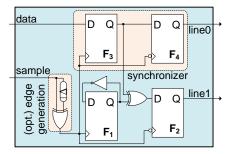

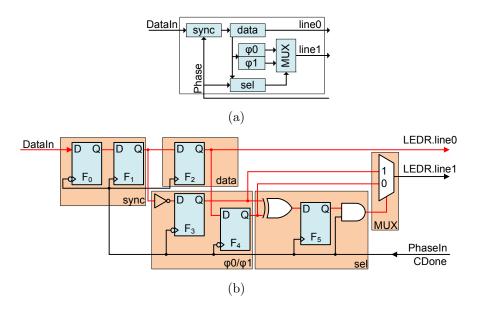

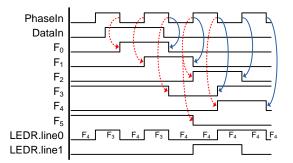

| 2.8  | Converting single bits to LEDR without back-pressure                     | 42 |

| 2.9  | Alternative circuit implementation (b)                                   | 44 |

| 2.10 | Example waveform of synchronizer.                                        | 45 |

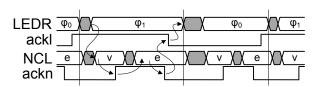

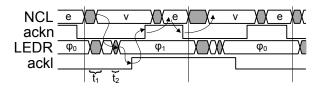

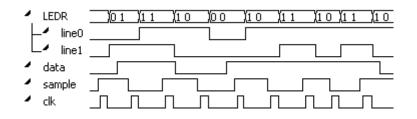

| 2.11 | Simulation of LEDR to NCL conversion.                                    | 46 |

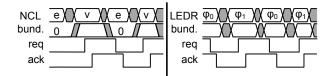

| 2.13         | Simulation of NCL to LEDR conversion                                                                                                                 | 47<br>47<br>47 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

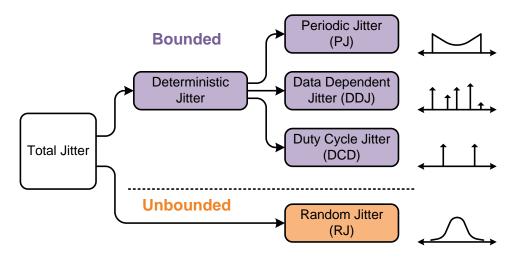

| $3.1 \\ 3.2$ | Jitter classification scheme (Source: [85])                                                                                                          | 53             |

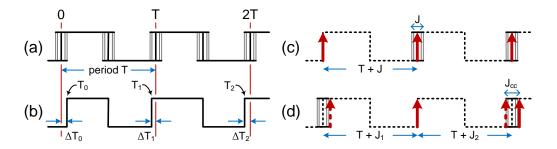

|              | Cycle-to-Cycle jitter (d) (Source: [94])                                                                                                             | 55             |

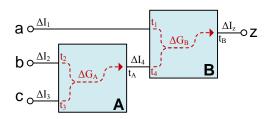

| 3.3          | Timing model, example circuit.                                                                                                                       | 61             |

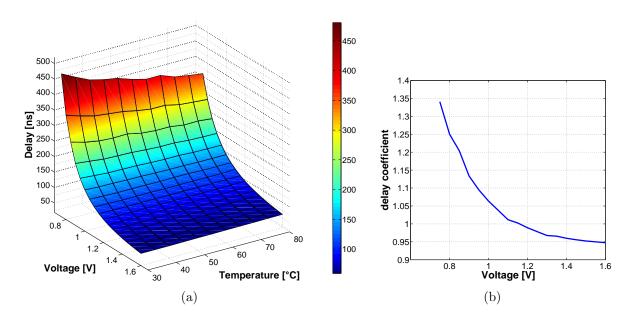

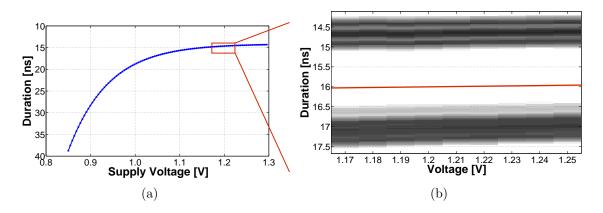

| 3.4          | Voltage, temperature, delay relationship for Cyclone II FPGA (a) and voltage dependent temperature coefficient $\Gamma$ (b)                          | 68             |

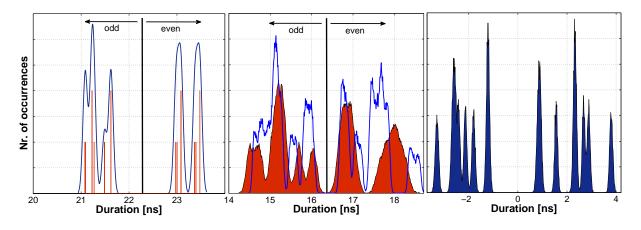

| 3.5          | Post-layout simulation (left), FPGA measurements and Monte Carlo sim-<br>ulation (middle), and cycle-to-cycle jitter (right) of a 4-bit asynchronous | 60             |

| 3.6          | counter's cDone signal                                                                                                                               | 69             |

|              | mized (b) 16-bit counter                                                                                                                             | 71             |

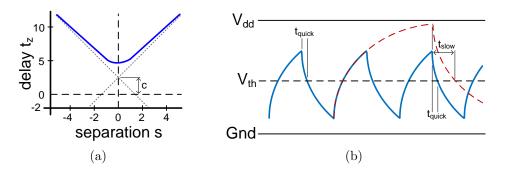

| 4.1          | Charlie Diagram (Source: [93]) (a) and Drafting Effect (Source: [85]) (b).                                                                           | 77             |

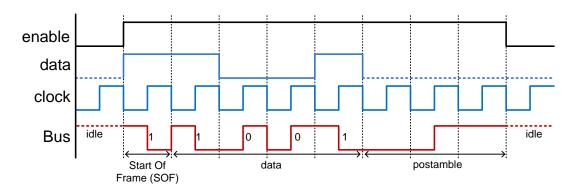

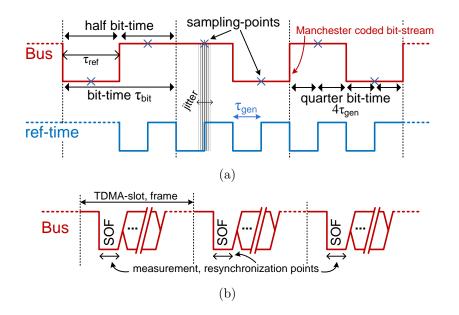

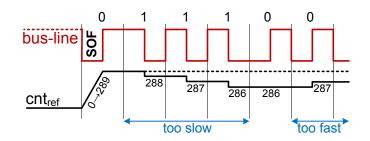

| 4.2          | TTP-specific Manchester encoding of frames.                                                                                                          | 81             |

| 4.3          | Manchester code with sampling points (a), TTP-slots, resynchronization (b).                                                                          | 83             |

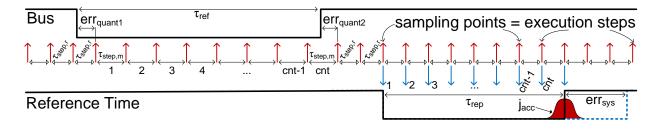

| 4.4          | Illustration of all characteristic temporal system properties                                                                                        | 86             |

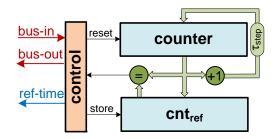

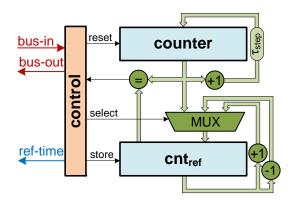

| 4.5          | Basic structure of the time-reference generation circuit                                                                                             | 87             |

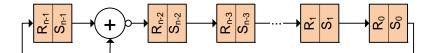

| 4.6          | LFSR counting at half speed due to shadow registers $S_i$                                                                                            | 89             |

| 4.7          | Optimized structure of the time-reference generation circuit with continu-                                                                           |                |

|              | ous rate correction                                                                                                                                  | 90             |

| 4.8          | Synchronization with continuous rate correction                                                                                                      | 90             |

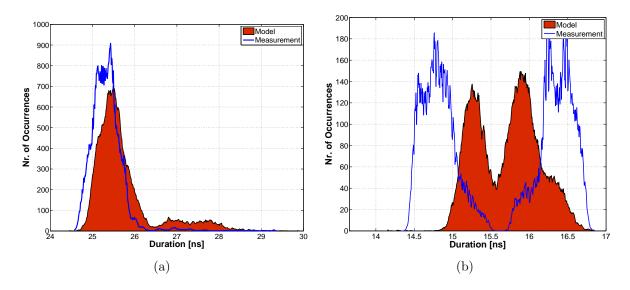

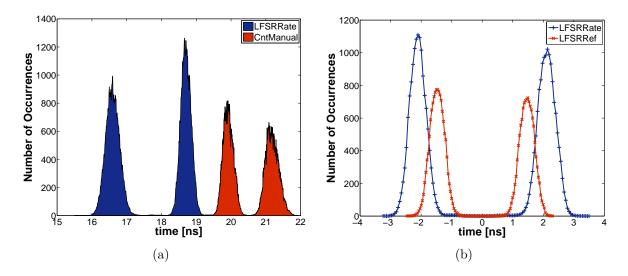

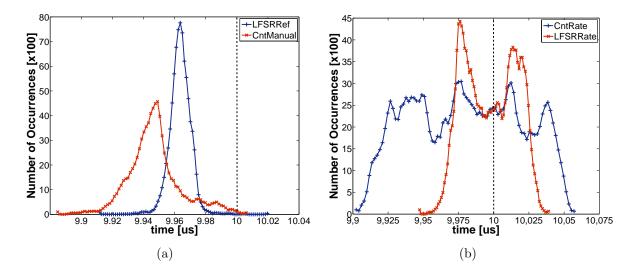

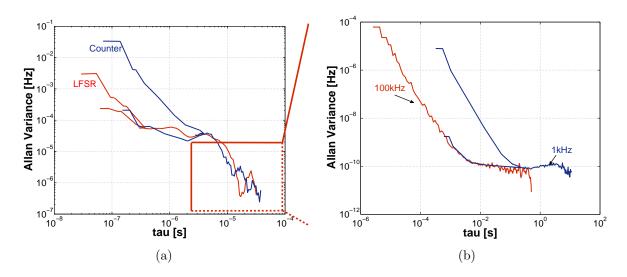

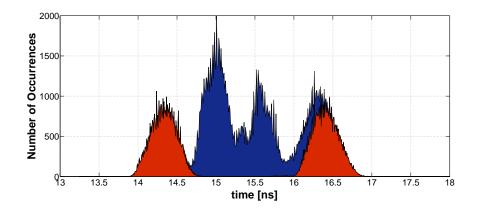

| 4.9          | Exemplary histograms (a) and cycle-to-cycle jitter (b) for signal ${\tt cDone.}$                                                                     | 93             |

| 4.10         | Histograms for design without (a) and with (b) continuous rate correction                                                                            |                |

| 4.11         | for signal ref-time                                                                                                                                  | 94             |

|              | drates (b)                                                                                                                                           | 95             |

| 4.12         | Temperature vs. normalized execution speed (a) and LFSR-index $cnt_{ref}$                                                                            | 00             |

|              | vs. duration $\tau_{rep}$ of ref-time (b)                                                                                                            | 96             |

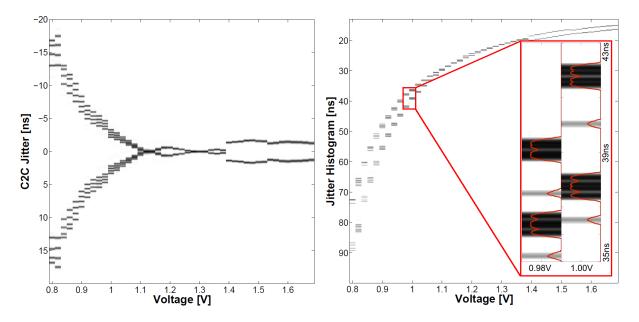

| 4.13         | Cycle-to-Cycle jitter (left) and jitter histograms of signal cDone (right)                                                                           |                |

|              | under varying supply voltage.                                                                                                                        | 98             |

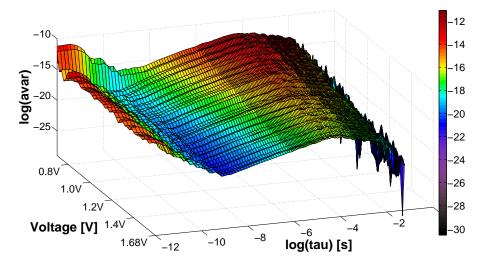

| 4.14         | Allan Variance of ref-time under varying supply voltage                                                                                              | 98             |

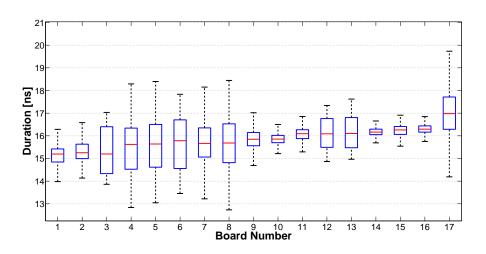

|              | Box-and-whiskers plot of cDone signal for all 17 boards                                                                                              | 99             |

|              | Voltage-speed relationship (a) with detailed measurements around 1.2V (b).                                                                           | 100            |

|              | Jitter histograms for two exemplary boards.                                                                                                          |                |

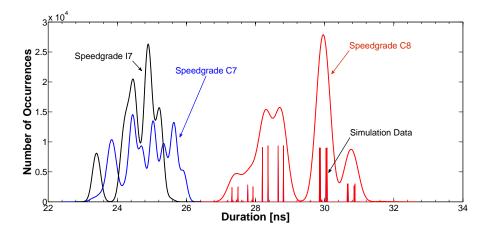

|              | Simulation histograms for three different speed-grades                                                                                               |                |

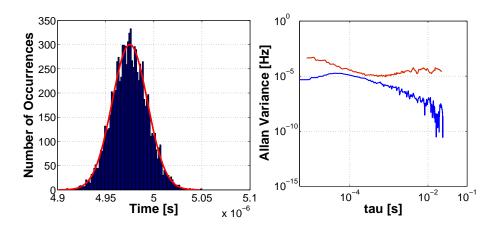

|              | Reference time histogram (left) and Allan Variance with and without resyn-<br>chronization (right).                                                  |                |

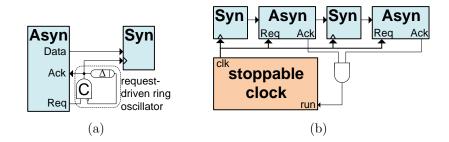

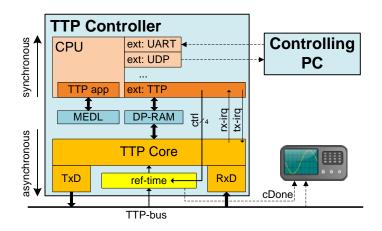

| 5.1          | Block diagram of simplified asynchronous TTP controller.                                                                                             | 106            |

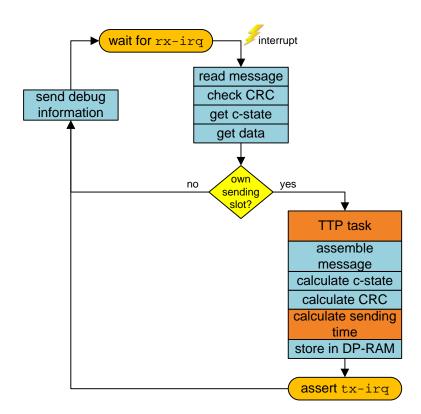

| 5.2  | Flow chart of the main controlling application software                          |

|------|----------------------------------------------------------------------------------|

| 5.3  | TTP cluster architecture, symbolic photo (with the courtesy of TTTech            |

|      | Computertechnik AG, source: http://www.tttech.com/products/ttp/) 112             |

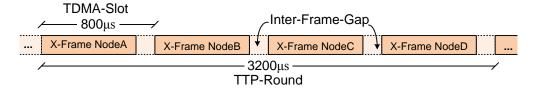

| 5.4  | TTP schedule (nodes, TDMA slots, TTP-round)                                      |

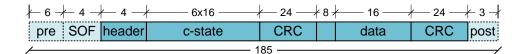

| 5.5  | Bit-fields of X-frames for our configuration                                     |

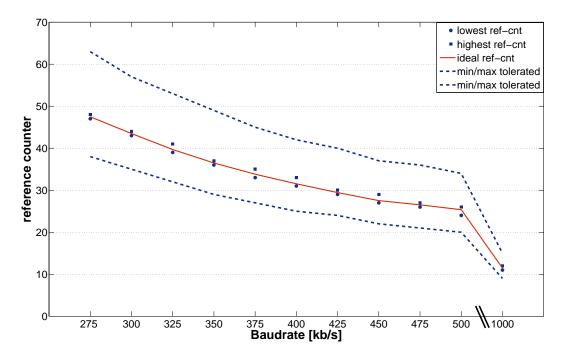

| 5.6  | $cnt_{ref}$ values for different baudrates with upper and lower bounds for cor-  |

|      | rect message reception                                                           |

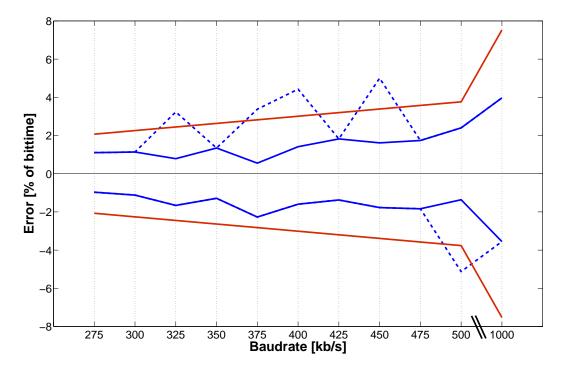

| 5.7  | Relative error in percent of one bittime with 1 LSB upper/lower bounds $117$     |

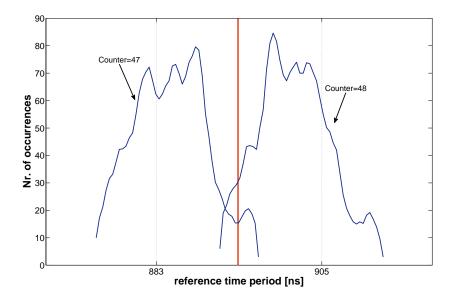

| 5.8  | Exemplary jitter histogram for $275k$ for two $cnt_{ref}$ values                 |

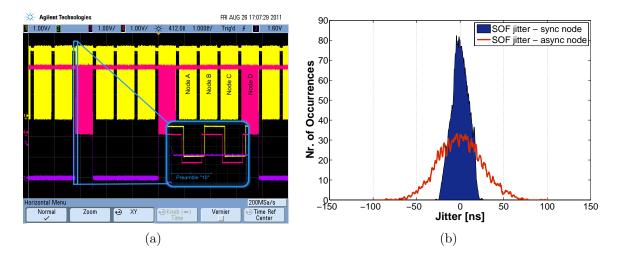

| 5.9  | Scope screenshot of running TTP cluster (a) and jitter of SOF transition         |

|      | of synchronous and asynchronous node (b)                                         |

| 5.10 | Absolute error made for $cnt_{ref} = 47$ (large slope) and $cnt_{ref} = 48$ (low |

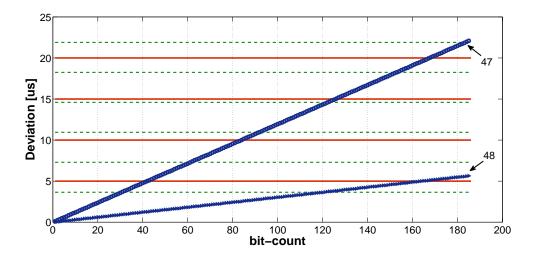

|      | slope)                                                                           |

|      |                                                                                  |

# List of Tables

| 3.1 | Characteristic figures of example circuits                                          |

|-----|-------------------------------------------------------------------------------------|

| 4.1 | Comparison of the implementation alternatives for the time reference gen-<br>erator |

| 5.1 | Overview of the different function blocks (cf. Figure 5.1)                          |

| 5.2 | Semantics of the 16-bit data field for the host application                         |

| A.1 | Register overview for TTP extension module                                          |

| A.2 | Bit-definitions of status-reg                                                       |

|     | Bit-definitions of config-reg                                                       |

|     | Bit-definitions of timer-reg                                                        |

|     | Bit-definitions of control-reg                                                      |

|     | Bit-definitions of lfsr-reg                                                         |

|     | Bit-definitions of asyn-timer-reg                                                   |

|     | Bit-definitions of timestamp-reg                                                    |

## Chapter 1

# Preface

In the beginning the Universe was created. This has made a lot of people very angry and been widely regarded as a bad move.

Douglas Adams

### 1.1 Motivation

Asynchronous circuit design techniques can provide economic solutions in cases where the traditional synchronous design is facing its limitations [89]. Still, however, industry in general is reluctant to consider asynchronous design a viable alternative in these cases. There are several reasons for this, one prominent being the common belief that asynchronous logic is not suitable for real-time applications due to its apparently unpredictable temporal behavior.

One of the most frequently cited statements in conjunction with asynchronous designs is that they operate as fast as they can, thereby achieving average case performance. Although this property clearly is one of the biggest advantages of asynchronous circuits, it also manifests as a major drawback when it comes to temporal predictability. Furthermore, asynchronous circuits' ability to adapt their operating speed to the respective environmental conditions directly translates into a variation of the hardware execution time for a given task. The origin is the inherent closed-loop flow control that allows for automatic adaptation of the operating speed, which stands in contrast to the rigid temporal (open-loop) control in synchronous systems. The seemingly undetermined behavior is due to a complex interaction of several factors — starting from the switching speed of each single transistor to the handshake interaction of entire functional blocks. All these aspects have to be considered when determining an asynchronous circuit's speed of operation. However, in a synchronous design we have to deal with all these effects as well. The main difference is that the synchronous paradigm divides the task of system design into two separate parts [20]: The timing analysis deals with low level aspects of digital circuits and provides the clock period as a result. The logic and functional design considers the behavior of the system at a high level of abstraction and uses the clock period as basic time unit. In this way synchronous systems have a clear separation/interface between those domains, which allows considering each part independently from the other — thereby simplifying the modeling of the entire system with respect to functionality and timing. However, this separation has its price, as it results in a waste of performance and reduced robustness. As a matter of fact, the temporal behavior of asynchronous circuits is by no means more undetermined than the synchronous one. After all, the underlying technology is the same. However, it is more complex to model, since asynchronous circuits do not have a clock signal that would enable a separation between logic design and timing analysis. At the same time this clearly leverages a higher potential for optimization and robustness.

Nowadays, to allow for minimal clock skew throughout the die and of course for maximum performance, lots of effort is invested in designing the clock distribution network properly [13, 35, 46, 58, 76]. Furthermore, highly sophisticated power saving mechanisms are implemented: Reducing the clock frequency in case of low CPU load, lowering the chip's supply/core voltage, and clock gating are only some examples. Again, asynchronous circuits have great potential to overcome at least some of the limiting issues of their synchronous counterparts. Regarding the enormous power dissipation of cutting-edge technology, one of the most promising properties of asynchronous designs might be that the underlying functional blocks are only running if there is indeed work to be done. Clearly, such power-saving behavior can only be achieved by a thorough system design, which is - generally speaking — also one of the major drawbacks of asynchronous circuits: The entire design process is far more complex compared to synchronous designs. This situation is further worsened by the fact that almost all available development tools are optimized for synchronous logic only. Also rapid prototyping with Field Programmable Gate Arrays (FPGA) still is difficult, as estimates on performance, chip size, and power dissipation are hardly representative for asynchronous systems. Nevertheless, a lot of academic research is conducted in this area, and various impressing asynchronous designs have already been realized (e.g., asynchronous processors [38, 92], cryptographic applications [84], or clockless crossbar switches [16], also refer to Section 1.3.4).

Simultaneously, while industry still seems to avoid this promising design alternative in their products, it is important to increase the reputation and acceptance of the asynchronous design paradigm, especially with respect to reliability, determinism, and predictability. In the course of this work we want to make a step in this direction by combining real-time systems and asynchronous logic. Our goal is to design an asynchronous communication controller for the Time-Triggered Protocol (TTP) that is able to communicate with a set of synchronous counterparts even under changing environmental conditions (such as voltage and temperature variations). In this context we elaborate a model for determining the timing behavior of a suitable asynchronous logic design style. As there is no high-precision reference clock available, we need to exploit the strict determinism and predictability of TTP to derive a feasible notion of time for the low-level

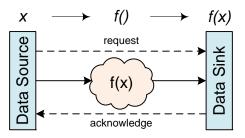

Figure 1.1: General flow control (handshaking) of logic circuits [20].

system services. Without a dedicated clock, however, the jitter of logic circuits becomes a major issue: If the execution cycles of the designs jitter too much, synchronization with TTP cannot be maintained. To this end, high-frequency jitter (as induced by classical jitter sources such as simultaneous switching noise or cross-talk) as well as low-frequency jitter (e.g., temperature drift or voltage fluctuations) must be addressed and compensated accordingly.

Before we start with a detailed description of our research project Asynchronous Logic in Real-Time Systems (ARTS), the following sections provide a comprehensive summary of several important topics that are directly related to this work. In the next section we will introduce different logic design styles and point out their major benefits and drawbacks. Section 1.3 then describes delay-insensitive asynchronous design methodologies which we use for implementing our circuits. Before finally taking a closer look at the aims and contributions of the project ARTS in Section 1.6, Section 1.5 explains the basic concepts of the Time-Triggered Protocol.

## 1.2 Design Methodologies

When considering (real-world) logical circuits in general, one might notice that functional blocks almost always follow the simple data flow model [20] of Figure 1.1: There is a data source, which provides the input data x, a (boolean) function f which implements the desired functionality and maps x to the respective result y = f(x), and a data sink which finally stores the computation result y. Although this basically is the definition of a simple mathematical function  $f : x \mapsto f(x)$ , there are some major issues to consider for practical electrical/digital systems, which severely complicate things compared to the strict mathematical formulation above. For the sake of simplicity let us assume that a data word x is represented as a vector of n bits  $x_i, 0 \leq i < n$ . The bit-widths of input xand output y do not necessarily have to be the same.

• Acknowledgement: The source must hold its current value until all processing has finished and the sink has successfully stored the result. Only then new data can safely be assigned to the source's output<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>For this overview we assume the combinational logic to obey the inertial delay model rather than, e.g., the transport delay model as supported by VHDL [91].

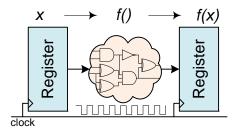

Figure 1.2: The synchronous design paradigm.

• Request: Furthermore, there must be a way to signal the arrival of new data to the sink — even if the result f(x) does not change for two successive and probably different input words x. This is realized by means of completion detection: Assuming input vector x to be stable and consistent<sup>2</sup> at the source, the calculation of the result y = f(x) needs some (variable) time  $\Delta$  to finish. To be more precise, each bit  $y_i, 0 \leq i < m$  of the resulting data vector y may need some slightly different amount of time until the final and correct value is reached. Consequently, the sink must have some means to determine a point in time when it is safe to store the entire calculation result, i.e., when all bits are stable and consistent. We will present different methodologies for implementing completion detection in Sections 1.2.1 and 1.3.3.

As one can imagine, there are many different ways to solve the above issues on the logical level [20]. The following paragraphs give an overview to existing and well-established digital design methodologies. We will see that the applied solutions are indeed quite diverse, and cannot easily be mixed or exchanged.

#### 1.2.1 Synchronous Paradigm

In industry, synchronous designs are by far the most common ones. In a synchronous logic circuit, there is a periodic, globally available clock signal. This signal not only defines the speed of operation, but also solves the basic issues described above (illustrated in Figure 1.2). The desired functionality is implemented using "ordinary" boolean logic (which is considered "formally incomplete" [25] as it does not provide any means for expressing validity, consistency, or temporal relationships), whereas the data sinks and data sources are realized as edge-triggered registers. All registers of an isochronic region [3] are connected to a common, periodic clock signal, whose (usually positive) edges mark points in time where new data is assigned to all registers. The basic assumption for this mechanism to work properly is that the clock's signal transitions occur almost simultaneously all over the chip. In this context, the clock signal is a very simple way to solve all fundamental issues:

<sup>&</sup>lt;sup>2</sup>Informally speaking, consistency means that all logical values represented by the single bits  $x_i$  of a data vector x belong the the same data word.

- In synchronous designs, there is no need for an explicit *acknowledgement* from the sink to the source, as the mere progression of time (i.e., a positive clock transition) guarantees proper storage of data at the sink.

- Likewise, an explicit *request* signal from the source to the sink can also be omitted as each positive clock transition is automatically interpreted as new request. *Completion detection* is moved to the time domain by setting the period of the clock signal to an appropriate duration for the logic function *f* to safely complete its operation and produce stable output. The data sink can thus be sure by design that its input is consistent and stable whenever a positive clock edge occurs.

All implementation and technology specific timing properties and constraints (as defined in [20], e.g.) are directly or indirectly masked by the concept of a global clock in the time domain. To put it in other words, the synchronous design methodology solves all "synchronization issues" between source and sink in the time domain rather than in the signal/information domain. This clearly has some remarkable advantages. To mention just a few, the resulting circuitry is very simple and efficient. Designers can focus on implementing the desired functionality instead of thinking about control flow, and on the logical level there is hardly any overhead. Furthermore, as the clock is usually generated with high-precision crystal oscillators, an accurate notion of time can be derived without additional effort. All in all, the synchronous design paradigm has proven itself very useful and efficient in many terms.

However, with every upside comes a downside as well. Especially the last few years have shown that it becomes more and more difficult to further increase the clock frequencies. With ever increasing performance requirements and technology scaling, not only the rapidly increasing power consumption, but also the design of the clock distribution network [35] itself become limiting factors. Without sophisticated compensation mechanisms a multi-GHz chip can no longer be considered isochronous, as clock skew becomes too large throughout the complex clock tree [35, 46]. Another issue related to the synchronous design style is reduced robustness against process variability and changing operating conditions, since they directly influence the execution speed of the underlying hardware. Consequently, appropriate safety margins need to be foreseen when specifying a system's clock frequency. After all, the overall clock frequency is determined by a static worst case timing analysis. Yet another drawback comes at system or module interfaces: Systems running with different clocks (even if their nominal frequencies match) cannot easily be connected. Special synchronizer circuits must be implemented [40], thereby increasing not only complexity but possibly also reducing performance. While considerably simplifying the design process, decoupling the control flow from the data flow by means of a global time reference negatively impacts on performance, flexibility, and power consumption. It is not easily possible to switch off idle modules (i.e., zero-skew clock gating [13,76]), or to combine modules with different performance.

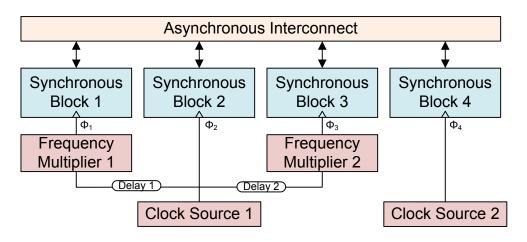

### 1.2.2 Globally-Asynchronous Locally-Synchronous

A possible solution to the clock skew and distribution problems is the so called Globally-Asynchronous Locally-Synchronous (GALS) approach [14, 51, 83]: A complex design is built up of several independent functional units, each of which has its own clock signal. The relatively small blocks can be implemented using the conventional synchronous design approach with all its advantages (and without some of the disadvantages coming with technology scaling and increased system complexity). The communication among the synchronous blocks has, because of the independent clock sources, to take place asynchronous interconnect is responsible for data transfer between the different synchronous blocks. As indicated in the figure, these blocks generally do not have the same operating frequency. Depending on the exact system setup, the following taxonomy of timing relationships between the different clock domains is commonly used in literature [61,83]. This classification directly impacts the actual implementation of the asynchronous interconnect.

- A mesochronous relationship between two synchronous blocks means that both communication participants operate at exactly the same frequency. However, there is a stable but unknown phase difference between the two blocks. For example, blocks 1, 2 and 3 in Figure 1.3 share the same clock source. If the frequency multipliers are set to 1, these three nodes are said to be mesochronous.

- Assume that both clock sources in the figure have the same nominal frequency. Now, blocks 2 and 4 are said to be *plesiochronous*. While having the same nominal operating speed, the two independent clock sources are subject to drifting phases (e.g., due to minor frequency deviations in the range of a few parts per million).

- Finally, when a sender and receiver operate at totally different clock frequencies, the blocks are considered *heterochronous*. Assuming that both clock sources and frequency multipliers are set to different values, all four blocks are heterochronous with respect to each other.

The latter class of heterochronous systems can further be subdivided into *ratiochronous* and *nonratiochronous* designs. Again consider Figure 1.3: Blocks 1, 2 and 3 share the same clock source, but nodes 1 and 3 have frequency multipliers and additional delays in their clock path. As the frequency multipliers are also fed by Clock Source 1, there is a predictable and periodic relationship between the different clocks' phases. This relationship is called ratiochronous (as the clocks are exact rational multiples of each other) and can be exploited when designing the asynchronous interconnect.

According to Figure 1.4, all the above "synchrony characteristics" belong to the superior class of *loosely synchronous* GALS designs. However, a more distinctive classification can be made due to the different possible GALS design styles.

• Loosely Synchronous. This design style exploits the known relationships between the operating frequencies of communicating blocks in order to optimize throughput

Figure 1.3: Exemplary GALS system structure (Source: [83]).

Figure 1.4: GALS taxonomy (Source: [83]).

and latency, as well as to ensure that all timing constraints are met. While allowing for high efficiency (for both area consumption and performance), this style suffers flexibility as changes in the clock frequencies cannot be handled without a redesign.

- Asynchronous. This style represents the most flexible way of communication between different clock domains. Usually, explicit *request* and *acknowledge* signals are used for implementing flow control in asynchronous systems (see Section 1.3 for more details). It is not necessary to make any assumptions on the relationships of the respective clock domains. However, this advantage comes with the severe drawback of reduced throughput and relatively high latency.

- *Pausible Clock.* In this design style the clocks are usually generated locally by means of (pausible and stretchable) ring oscillators. While data transmission is active, the clock can be paused, thus totally avoiding potential metastability. While pausing the clock introduces performance penalties on the respective synchronous block, robustness and power consumption are the main benefits of this approach (no dynamic power is consumed while the clock is paused).

While the idea of pausible clocks sounds reasonable and efficient, the main problem with industrial designs are the ring oscillators. As they are strongly sensitive to operating temperature, supply voltage and process variations, they need careful (and thus expensive) calibration. A general issue with all GALS approaches is that the asynchronous interconnect will degrade system performance due to the overhand introduced by the handshaking protocols. On the other hand, GALS designs have great potential when it comes to power reduction, as it is easily possible to set the supply voltage and operating frequency of each synchronous block independently. Furthermore, the single blocks may also save some power due to the reduced complexity of the clock distribution network. Another important advantage especially for industrial designs originates in reduced electromagnetic interference. The different (possibly uncorrelated) clock domains may significantly reduce signal noise because register switching is distributed in time, thus leading to a flatter power spectrum. This can also weaken the requirements on the power supply network and the needed number of power pads. Interestingly, a flatter power spectrum (caused by different uncorrelated clocks) may also increase immunity against power analysis attacks, thus rendering GALS designs useful especially for cryptographic applications [42].

To summarize one can say that GALS designs offer an interesting alterative to the ordinary, strictly synchronous design approach. They combine some possible advantages of asynchronous designs (e.g., power consumption, modularity, etc.) with the comfort of synchronous circuit design. As system integration and technology scaling further advance, one can expect GALS design style — besides other alternative digital design methodologies — to gain more importance in future.

### 1.2.3 Asynchronous Paradigm

Today's mostly synchronous logic is based upon two assumptions: First, signals are limited to binary values, and second, it is assumed that time is discrete. The former allows for the

use of simple boolean logic, whereas the latter facilitates that hazards and feedbacks can mostly be ignored [43]. For asynchronous circuits, these central assumptions are basically removed: On the one hand, replacing the global clock with local handshaking protocols allows events to happen at any time (they are not triggered by clock-edges any more). On the other hand, multi-rail encodings are often used to represent data in different code-sets and allow for efficient completion detection. Appropriate examples for such encodings are presented in Section 1.3. By changing the logic design paradigm, some interesting potential benefits can be identified [43,81,89]:

- Since there is no (global) clock signal, *clock skew* and all related problems (e.g., clock distribution) can be ignored by definition.

- Without a clock signal, unused modules are not clocked and therefore need less power. The overall *power consumption* can benefit from an asynchronous design, without implementing dedicated power saving mechanisms.

- The clock frequency in synchronous designs results from the critical path's propagation delay, which is the worst case performance. Even worse, steadily increasing process and fabrication variations result in a very pessimistic estimation of the worst case timing. In contrast, asynchronous systems generally do not need to wait for any clock transition if a task is finished. This *average case performance* may lead to considerable improvements in speed.

- Not having a system clock, asynchronous circuits need alternative means for completion detection. These circuits often have the benefit of automatically adapting themselves to changing physical and environmental conditions (e.g., temperature drift, supply voltage fluctuations, fabrication process variations).

- The often problematic *electromagnetic emissions* generated by thousands of almost simultaneously switching registers are significantly reduced in asynchronous designs. The reason for this behavior is based on the fact that signal transitions tend to occur without synchronization to a global clock.

- The simple handshake interfaces allow for better *composability and modularity*.

Unfortunately, many asynchronous design styles have a significant overhead in area consumption. This is mainly caused by the — compared to synchronous logic — relatively complex control structures (e.g., completion detection, handshaking, etc.), and may also negatively influence system performance. From an engineer's point of view, the lack of sophisticated CAD tools that actually support asynchronous design methodologies is one of the most severe drawbacks. Another major issue concerns testability, as asynchronous circuits cannot simply be stopped and started by means of clock transitions. Design for testability is thus far more complex and thereby increases the overall costs dramatically.

It is undoubted that asynchronous circuit design has great potential and offers a lot of new possibilities to hardware engineers. It is important to notice that the existing

Figure 1.5: Example circuit to illustrate different delay models (Source: [81]).

asynchronous design styles (some examples are presented later in this chapter) all have strengths and weaknesses of their own. The challenge is to find solutions that combine most of the above properties, and simultaneously keep the design and resource overheads low.

### **1.3** Asynchronous Circuit Design

In the last sections we have discussed some abstract design methodologies for digital circuits. We have seen that asynchronous logic offers interesting properties and opportunities to design engineers. In this section, we now take a closer look to asynchronous logic design and its underlying principles. We present the most common delay models, exemplary asynchronous design techniques, as well as various asynchronous application examples. Furthermore, we discusses the design style used for our implementations in more detail.

### 1.3.1 Delay Models

There are four major delay models to classify asynchronous circuits [43, 65, 81]. These models form the very basis of each design (asynchronous as well as synchronous) because they make fundamental assumptions about signal, gate, and wire delays. Clearly, these assumptions have to be based upon the physical properties of the target technology, and if they are violated the circuit will most likely not work at all. To better illustrate the different delay models, Figure 1.5 shows a simple circuit consisting of three gates A, B, Cwith associated propagation delays  $\Delta_{A,B,C}$  and the corresponding interconnect with delays  $\Delta_{1,2,3}$ , respectively.

• Self-Timed. Also often called bounded delay model, the timing characteristics of digital circuits are modeled on an elaborate engineering level. The propagation delays of wires and gates are defined to be bounded and known. This model therefore is the basis for all synchronous designs, as a sophisticated critical path timing analysis is only possible with detailed knowledge of the technology's timing properties. For the example in the figure this means that all delays have well-defined values. The worst case propagation delay can therefore be easily expressed as  $\Delta_A + \Delta_1 + \max(\Delta_2 + \Delta_B, \Delta_3 + \Delta_C)$ .

Figure 1.6: Bundled Data (a) and Dual-Rail approach (b) (Source: [81]).

- Speed-Independent (SI). These types of asynchronous logic are also known as Muller circuits. The delay model assumes that while gate delays are bounded but unknown, wire delays are negligible, i.e., zero. For Figure 1.5 this requires all three  $\Delta_A, \Delta_B$ , and  $\Delta_C$  to arbitrary (but greater than zero), and  $\Delta_1 = \Delta_2 = \Delta_3 = 0$ .

- Quasi Delay-Insensitive (QDI). By going one step further and allowing also arbitrary  $\Delta_1$  and  $\Delta_2$ , but at the same time requiring  $\Delta_2 = \Delta_3$ , we obtain the so called Quasi Delay-Insensitive (QDI) model. Since wire delays can not be considered negligible (in fact they already dominate gate delays significantly), the QDI model makes more realistic assumptions on wire delays (compared to SI). By introducing isochronic forks, which have the property that signal transitions reach all end-points at the same time, the gap between SI and DI (see below) circuits is closed.

- Delay-Insensitive (DI). An extremely robust delay model is obtained by allowing all delays for gates and wires to be unbounded, finite, and unknown. For Figure 1.5 this leads to arbitrary (positive) values for all the delays  $\Delta_{A,B,C,1,2,3}$ . As the designer cannot make any predictions on the actual delays, validity of data must be implemented in the value domain rather than in the time domain (as it is done in synchronous designs, e.g.). The weak assumptions made by this design model result in a very limited number of truly DI circuits, because only C-elements [75] and inverters may be used as building blocks [59].

As we will see in Section 1.3.3, delay-insensitive circuits built out of usual boolean gates (such as AND or XOR) are, strictly speaking, only quasi delay-insensitive: The basic building blocks (e.g., delay-insensitive boolean gates) are modeled on a low abstraction level, where the designer can directly control the wire delays. All necessary timing assumption are hidden inside these basic low-level blocks. A complex circuit composed of such gates can indeed be considered delay-insensitive, because all timing dependencies are masked at a higher level of abstraction.

The following few paragraphs will provide an overview over the most common types of asynchronous (handshake) protocols [81]. In Figure 1.6, the initiator (sender) is marked with a black dot.

**Bundled Data**. In this single-railed approach data values are encoded as usual boolean values. All bits of an entire data-vector are bundled, and associated with a pair of request and acknowledge signals. These control signals are used to communicate

Figure 1.7: Four-Phase (a) and Two-Phase bundled data protocol (b) (Source: [81]).

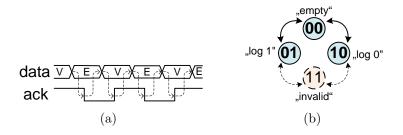

Figure 1.8: 4-Phase Dual-Rail example waveform (a) and encoding (b) (Source: [81]).

with handshaking when new data is available (request) at the sender, and when data has been captured (acknowledge) by the receiver (cf. Figure 1.6(a)). In order to exchange n bits of data between sender and receiver, n+2 signal wires are necessary. There are two possible implementation alternatives for the actual handshaking protocol. As illustrated in Figure 1.7, the 4-phase protocol works in return-to-zero (RTZ) fashion using state signaling: The sender prepares the data and sets its **request**. The receiver captures the data and asserts is acknowledge line. In response, the sender de-asserts request, followed by resetting acknowledge to its initial value. Obviously, the last two transitions (both request and acknowledge return to zero) cost unnecessary time and energy. This can be overcome using the two-phase protocol depicted in Figure 1.7(b), which is based on transition signaling and therefore also called *non-return-to-zero (NRZ)* protocol. Again, the sender prepares the data which shall be transmitted and generates a transition on the request line. After the receiver has captured the data, it sends a transition back on acknowledge, which finalizes the data transfer. Although this method in principle saves time and energy, logic responding to signal events (rather than signal states) is considerably more complex. Both these handshaking protocols have in common that they rely on the correct order of events (at both sender and receiver<sup>3</sup>), as the data-vector needs to be stable before the receiver starts capturing. Clearly, neither the SI nor (Q)DI delay model can guarantee this prerequisite, leaving self-timed the only option for the bundled data

**Dual-Rail**. In contrast to single-rail encoding, a logical value is represented by two physical signal lines in dual-rail circuits. As four different states can be encoded with two binary signals, it is possible to move part of the handshaking (and of the associated

<sup>&</sup>lt;sup>3</sup>Different lengths in signal wires may lead to an inconsistent view of the order of events at sender and receiver. Therefore, special care must be taken when placing and routing these components.

timing constraints) to the value domain. Depending on the exact coding scheme, one can again distinguish between two-phase and four-phase protocols. While the former is explained in greater detail in Section 1.3.3, we will focus on the latter in this paragraph. Both methodologies have in common that they need 2n + 1 wires to transmit n bits of data, as indicated in Figure 1.6(b). The four-phase protocol, however, uses a different coding scheme (cf. Figure 1.8(b)) to represent logical values than the two-phase protocol. According to the state diagram in the figure, logical values are *one-hot* encoded, and any two consecutive logical values are always separated by the empty state (the fourth state marked as "invalid" is not used). This leads to the exemplary waveform shown in Figure 1.8(a): As a response to valid data (V) (which is basically a request encoded in the data bits themselves) the acknowledge line is asserted, signaling that data has been captured. The source then assigns the "empty" data word (E) as a spacer, which is followed by de-asserting acknowledge to its initial value. This powerful encoding is fully delay-insensitive, as wire delays do not matter any more: A bit is considered valid as soon as one of its signal lines is 1, regardless of the (routing) delays that might occur. It is of course also possible to bundle n dual-rail data bits to a data vector, as completion detection (i.e., a check whether all data bits are valid) comes down to a simple test of any bits still being "empty". Speaking more formally, there are three disjoint (and practically easy to identify) sets of codewords [90]: (i) The empty codeword contains n "empty"-only data bits. (ii) The *intermediate codewords* contain some "empty" and some "valid" data bits. (iii) The valid codeword contains n "valid"-only data bits. Generally, the transition from (i) to (iii) and vice versa also includes a period of time where intermediate codewords (ii) can be observed. The subsequent circuitry "just" has to wait until the intermediate state is left.

This clever encoding in combination with the properties (i)-(iii) allows for a rather efficient implementation scheme for delay-insensitive circuits. It is called Null Convention Logic (NCL) and was proposed (and also used in numerous applications) by Theseus Logic, Inc., in 1996 [25] (refer to Section 1.3.4 for application examples). The main advantages of NCL are its great flexibility, high modularity, and inherent robustness. Especially when it comes to changing environmental conditions (e.g., huge temperature and supply voltage fluctuations) and fabrication process variability, delay-insensitive circuits can show their full potential.

**Others**. The implementation schemes described so far are only a subset of the various possibilities that exist for implementing asynchronous logic. For instance, the bundled data protocols can be adapted from acting as *push channel* (i.e., actively offering data to the receiver) to a *pull channel*, where data is requested explicitly by the receiver. Clearly, the protocol needs to be changed such that data is valid when the receiver actually wants to capture it. It is also possible to extend the protocol for exchanging data in both directions, e.g., by bundling data of node A with **request** and data of node B with the **acknowledge** signal.

In this section we introduced some of the most important and most often used methodologies to implement asynchronous logic. Especially the delay-insensitive alternatives

Figure 1.9: Micropipeline control structure without (a) and with data processing (b) (Source: [82]).

(2-phase and 4-phase dual-rail) are directly or indirectly based on micropipelines. Furthermore, the structure of micropipelines forms a powerful and relatively simple control structure for asynchronous circuits in general. Thus they are worth explaining in the following section.

#### 1.3.2 Micropipelines

In 1989, Ivan E. Sutherland first introduced the amazing and extremely powerful — yet relatively simple — concept of micropipelines [82]. Generally speaking, if no processing logic is inserted into any pipeline, it just acts like a series of storage elements through which data can pass. Pipelines can be categorized into clocked or event-driven and elastic or inelastic. As the names suggest, clocked pipelines depend on a globally distributed clock signal whereas event-driven pipelines are controlled by locally generated events. A pipeline is said to be inelastic if the amount of data in it is fixed, which implies that the input and output data rates must match. On the other hand, an elastic pipeline may contain a varying amount of data because of internal buffering. Without any processing logic, inelastic and elastic pipelines can be compared to shift registers and FIFOs, respectively. Sutherland's micropipelines are event-driven and elastic. This solution totally avoids setup- and hold-time violations normally induced by different clock sources at the FIFO's inputs and outputs.

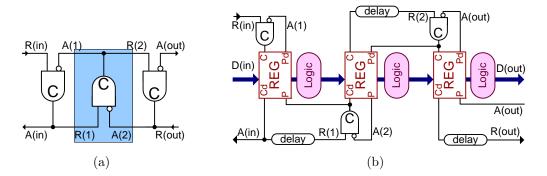

**Control Circuit**. Figure 1.9(a) shows the control circuitry of a three-stage micropipeline. Each of these stages i has a **request** input (coming from the previous stage i-1) and output (going to the next stage i+1) as well as an **acknowledge** output (to confirm the request to its predecessor i-1) and input (to get a confirmation from its successor). The composability of micropipelines benefits from this interface since single stages (which may run at different speeds) can easily be connected together. The behavior of the micropipeline can be explained by looking at a single stage (i.e., a C-element with one inverted input): "if the predecessor and the successor differ in state then copy predecessor's state else hold present state" [82]. Assuming that all stages are in the same state

(which corresponds to an empty pipe), an input transition on  $R_{in}$  propagates through the pipeline stage by stage. Without an acknowledgement on  $A_{out}$ , all but the last stages are then in the same state (now, the pipe is partially filled). Further input transitions on  $R_{in}$  will eventually cause the pipe to be full, which is characterized by opposite states of adjacent stages. An acknowledgement on  $A_{out}$  will remove the rightmost transition from the pipe, thereby producing an empty stage. This empty slot now moves backwards, stage by stage, until it reaches the pipe's beginning, which is signaled via  $A_{in}$  to the environment — a new input transition on  $R_{in}$  is allowed to occur. This concept can abstractly be seen as "bubbles" and "tokens" moving back and forth in the pipe. As we will see in Section 1.3.3, the method of dual-rail two-phase asynchronous circuits is quite similar.

Micropipeline with Processing. A micropipeline that contains both storage elements and combinational logic is presented in Figure 1.9(b), and can be seen as yet another way to realize asynchronous circuits (in addition to the methods presented in the previous section). To realize such a FIFO, special event-driven storage elements must be used. As indicated in the figure, each register *REG* has two control inputs (Capture and Pass) and two control outputs (Capture done and Pass done). Whenever the values of C and P match, data can directly pass through the register (thus not acting as storage element). Otherwise, i.e., when  $P \neq C$ , the current value is preserved. The control outputs Pd and Cd are slightly delayed copies of the corresponding control inputs and serve as acknowledgement signals (they are applied as soon as the register has finished its work). The delay elements explicitly included in the drawing are of fundamental importance: The control signals must be delayed long enough for the combinational logic to finish its computations, in order to guarantee stable data when the next stage is activated (matched delays, refer to the self-timed delay model in the previous section). In comparison with the presented delay models, Micropipelines can be seen as combination of the bundled-data and bounded-delay models.

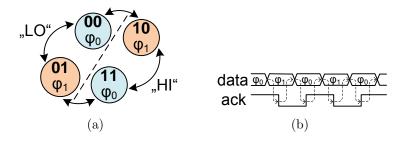

#### 1.3.3 Two-Phase Dual-Rail

We have already learned about Null Convention Logic and its encoding and properties in Section 1.3. Recalling the dual-rail coding scheme of Figure 1.8(b), the question arises if there is another, from a mathematical point of view maybe more efficient, way to represent the logic values. Not surprisingly, the answer to this question is yes. As illustrated in Figure 1.10(a), the coding differs from its four-phase counterpart in that it uses all available states as valid codewords. Thereby, the logical values 0 and 1 are both represented by two codewords each. Hence, in addition to the logical value itself, the codewords also contain a *phase*, which is either  $\varphi_0$  or  $\varphi_1$ . This is also evident from Figure 1.10(b), where an exemplary waveform is illustrated. Each *transition* of the **acknowledge** line (in combination with a transition of exactly one of the two signal rails per bit) signals a new data wave, making an explicit "empty" state superfluous and thereby potentially increasing performance. State transitions are only allowed between codewords of alternate phase, i.e., two successive states always differ in at least their phase (and maybe

Figure 1.10: LEDR coding scheme (a) and exemplary LEDR waveform (b).

their logical value). The coding was chosen in a way that from one state to another, exactly one physical signal needs to change its value. In literature, this encoding scheme is usually referred to as Level-Encoded (Two-Phase) Dual-Rail (LEDR) [18,60]. In [56], *phased logic*, an entire new design methodology based upon LEDR, was proposed. It allows to design delay-insensitive, asynchronous circuits while conceptually still supporting the well-known synchronous design paradigm.

When directly comparing LEDR to NCL, one might wonder which of these two design alternatives is better suited for implementing delay-insensitive circuits. To answer this question, one can use a code's characteristic *rate* R and *redundancy* r [90], defined as follows:

$$R = \frac{\log M}{n} \tag{1.1}$$

$$r = n - \log M \tag{1.2}$$

In these equations, n is the code's length (number of bits per word), and M is the code's size (number of valid codewords). For the two-phase code we have  $M_{2-phase} = 4$ , as all possible codewords are valid "messages". In contrast,  $M_{4-phase} = 2$ , because one codeword is unused, and the empty codeword does not encode actual data. Clearly, both codes are dual-rail and hence share n = 2. While  $R_{2-phase} = 1$  and  $r_{2-phase} = 0$  is the optimum that can be reached, the four-phase scheme having  $R_{4-phase} = 0.5$  and  $r_{4-phase} = 1$  is by far not optimal from a strictly mathematical point of view. However, it is also important how efficiently a code can be ciphered and deciphered by the communication participants. As it turns out, actual hardware implementations are significantly more efficient (in terms of area consumption and as a consequence also performance) for the four-phase methodology. We have already mentioned earlier that transition signaling (e.g., LEDR) is more complex to handle than state signaling (e.g., NCL).

For all asynchronous implementations in our project we use LEDR, as they exhibit more pronounced "asynchronous" properties than bounded delay circuits, and we have already gained some practical experience with it [19,45]. The target technology are Field Programmable Gate Arrays (FPGAs), so obviously the actual implementations follow the QDI delay model. However, on LEDR-gate abstraction level (e.g., 2-input dual-rail logic gates) the circuits can be considered delay-insensitive. In this approach, completion

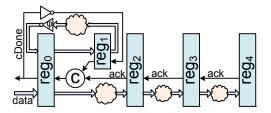

Figure 1.11: Example LEDR circuit structure.

detection comes down to a check whether the phases of all associated signals have changed and match. As usual, handshaking between register/pipeline stages is performed by virtue of a *capture done* signal (and the request implicitly coded in the data rails).

Figure 1.11 shows an exemplary LEDR circuit with two sequential registers  $(req_{0\rightarrow 2})$ and a feedback loop  $(reg_{0\to 1\to 0})$ . Direct feedback (i.e., without a shadow register like  $reg_1$ ) is not possible, as race conditions and deadlocks may occur when a register issues its own acknowledges and requests. Also notice the phase inverter in the feedback path. The acknowledge line is a combination of acknowledges from all n directly succeeding stages, combined by an *n*-input C-gate. The structure resembled in the figure (with the exception of  $req_1$ ) has some similarities to micropipelines. The inherent handshaking between the register stages leads to virtual "tokens" and "bubbles" moving back and forth in the pipeline, depending on the "fill state" of the pipeline. Notice that in contrast to synchronous logic, the single stages are only active if new data is assigned to their inputs, and the succeeding stages have already issued their acknowledge. In principle, the single logic stages can perform their operations concurrently. Similar to synchronous designs, where fast stages have to idly wait on the next clock transition, fast LEDR stages need to wait for new data (or the respective acknowledge) from neighboring slower stages. Consider a simple LEDR pipeline with n stages, each of which having a unique stage delay  $\Delta_i, 1 \le i \le n$ . Now the following observations concerning the total propagation delay in case of a full  $(\tau_f)$  and empty  $(\tau_e)$  pipeline can be made (compared to the synchronous case  $\tau_s$  with a clock period  $\Delta_{clk}$ ):

$$\tau_f = n \max\left(\Delta_i\right) \tag{1.3}$$

$$\tau_e = \sum_{i=1}^n \Delta_i \tag{1.4}$$

$$\tau_s = n\Delta_{clk} \ge n \max \Delta_i \tag{1.5}$$

Consequently, when looking at LEDR circuits at pipeline abstraction level, average case performance is generally possible. However, when directly considering the function blocks themselves (e.g., combinational logic), one can observe that they are *strongly indicating* [81] and therefore always exhibit worst case latency. Strongly indicating means that a function block does not compute *any* output until *all* its inputs are valid and consistent. Obviously, both the LEDR and NCL design methodologies as we have presented them fulfill this property.