## DISSERTATION

# ON THE ROLE OF HYDROGEN IN SILICON DEVICE DEGRADATION AND METALIZATION PROCESSING

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der

technischen Wissenschaften

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und

Informationstechnik von

## MAG. THOMAS AICHINGER

Die Dissertation wurde betreut von Prof. Tibor Grasser (TU Wien) und Dr. Michael

Nelhiebel (Infineon Technologies Austria) und ausgeführt am

Kompetenzzentrum für Automobil- und Industrie-Elektronik (KAI)

Villach, am 13. August 2010

Ich erkläre hiermit an Eides statt, dass ich die vorliegende Arbeit selbständig sowie ohne unzulässige Hilfe Dritter und ohne Benutzung anderer als der angegebenen Hilfsmittel angefertigt habe. Die aus anderen Quellen direkt oder indirekt übernommenen Daten und Konzepte sind unter Angabe der Quelle gekennzeichnet.

Villach, am 13. August 2010

## Acknowledgment

**F**<sup>IRST AND FOREMOST I want to thank Prof. Tibor Grasser and Dr. Michael Nelhiebel for supervising and supporting me during the entire three years of my PhD thesis. Thank you for all our fruitful discussions, for paper reviewing and for motivation.</sup>

I am also very grateful to my colleagues BSc. Schascha Einspieler, DI Gregor Pobegen and DI Stefan Puchner who supported me with measurements and discussions during their internships, master and PhD thesis at KAI.

I thank Prof. Herbert Grünbacher and Dr. Thomas Detzel for giving me the opportunity to join KAI, for providing me an excellent infrastructure and measurement equipment in the lab, and for the great industrial and academic network represented by KAI, Infineon and the TU Vienna.

Last but not least I want to thank all members of my family for financial and mental support. Many thanks, in particular, to my mother and my girlfriend who have always been taking care for me, provided me love and gave me a home.

## Kurzfassung

**B**<sup>AUELEMENT-Degradation und Gateoxid Zuverlässigkeit spielen in der modernen Halbleiterin-dustrie eine zunehmend wichtige Delles beiter in der</sup> dustrie eine zunehmend wichtige Rolle, da die Anforderungen an die Bauteile mit zunehmender Miniaturisierung, höheren Belastungen in der Schaltung und innovativen Technologieentwicklungen stetig steigen. Neben der Zuverlässigkeit von mechanischen Lötstellen und Verdrahtungen im Produkt, ist es besonders wichtig, den Transistor schon in einem früheren Stadium der Prozessierung gegen Umweltkontaminationen und mechanische Verspannungen zu schützen. Um nebenbei noch die verlustarme Schaltung von hohen Strömen sowie Kurzschlussfestigkeit gewährleisten zu können, werden am Ende der Prozessierung eines Leistungshalbleiters (back-end of line) verschiedene Isolations- und Metallisierungsebenen (layer stacks) in einer gut durchdachten Zusammensetzung und Reihenfolge auf die elektrisch aktiven Bereiche des Transistors aufgebracht. Es ist bekannt, dass sich verschiedene Passivierungskonzepte und Schichtsequenzen auch auf die elektrische Charakteristik und Zuverlässigkeit des Siliziumbauteils auswirken, da im back-end Prozess Wasserstoff in grossen Mengen in das System eingebracht wird. Es wird angenommen, dass hohe Temperaturen, wie sie zum Beispiel bei der Abscheidung und dem thermischen Ausheilen auftreten, den eingebrachten Wasserstoff in Richtung Gateoxid diffundieren lassen, wo er Defekte im Oxid oder an der Grenzfläche absättigen kann. Unter elektrischem und thermischem Stress kann sich dieser Wasserstoff jedoch in weiterer Folge wieder ablösen, wodurch zuvor passivierte Defekte wieder freigelegt werden.

So wie viele Halbleiterhersteller weltweit, hat sich auch Infineon Villach in der Vergangenheit wiederholte Male mit dieser Problematik auseinandergesetzt und obwohl einzelne empirische Lösungsansätze für bestimmte Technologien bereits vorliegen, fehlt noch immer ein globales Verständnis der zugrundeliegenden Physik vom Wechselspiel zwischen Prozessierung und Bauelement-Degradation. Da zu erwarten ist, dass neue Probleme ähnlicher Natur bei zukünftigen Technologien auftreten werden, ist es besonders wichtig, ein physikalisch fundiertes Modell zu entwickeln, dass die Zusammenhänge von Defektgeneration und Passivierung mit einzelnen Prozessschritten in Verbindung bringt.

Neben den oben erwähnten Prozesseinflüssen ist auch die Physik hinter den Schädigungsmechanismen von Gateoxid und Grenzfläche noch lange nicht verstanden. Einer der wichtigsten Degradationsmechanismen ist die sogenannte 'Negative Bias Temperature Instability' (NBTI), die bei Belastung des Gateoxid mit hoher Temperatur und Spannung zeitabhängige Einsatzspannungdriften verursacht. NBTI ist in Hinblick auf den back-end Prozess von besonderem Interesse, da angenommen wird, dass die Degradation in unmittelbaren Zusammenhang zur Wasserstoffpassivierung der Si–SiO<sub>2</sub> Grenzfläche steht. Ein Ziel dieser Dissertation ist es, die Rolle des Wasserstoffs bei der Bauelement-Degradation (NBTI) zu untersuchen und die Erkenntnisse anhand von Prozesssplits zu verifizieren. Ein spezielles Augenmerk liegt dabei auf Hochvolt (HV) MOSFET Bauelementen mit 30 nm SiO<sub>2</sub> Gateoxiden, wie sie bei Infineon Villach gefertigt werden. Bisweilen konzentrierte sich die Literatur vor allem auf ultradünne (nitridierte oder high– $\kappa$ ) Oxide, wohingegen Power Technologien bislang kaum untersucht wurden.

Zu Beginn werden grundlegende Signaturen der 'Bias Temperature Instability' (BTI) mit herkömmlichen Messmethoden auf 30nm SiO2 Bauelementen zusammengetragen und mit Resultaten neuerer Dünnoxid high-k Technologien verglichen. Diese einleitende Studie beinhaltet Überlegungen zur Elektrostatik und Dynamik von Degradation und Recovery und dient dazu, fundamentale elektrische Eigenschaften der auftretenden Defekte zu erfassen. Ein Literaturüberblick über das gegenwärtige mikroskopische Bild verschiedener Arten von Punktdefekten und deren Wechselwirkung mit Wasserstoff soll in weiterer Folge das physikalische Verständnis vertiefen. Die gesammelten Erkenntnisse werden dann benutzt, um neue Messvorschriften und experimentelle Prozeduren zu entwickeln, mit denen man in der Lage ist, Einsatzspannungsdriften auf verschiedene Arten zu charakterisieren und die jeweiligen Anteile bestimmten Defektklassen mit speziellen Eigenschaften zuzuordnen. Anhand der Daten und Schlussfolgerungen wird ein mikroskopisches Degradationsmodell vorgeschlagen, das (zumindest qualitativ) in der Lage ist, das Beobachtete anschaulich zu erklären. Um die Brücke zum Wasserstoff zu schlagen, werden die neuen Messmethoden auf verschiedene Prozesssplits angewandt, welche nachweislich über unterschiedliche Wasserstoffhaushalte im Gateoxid verfügen. Die Resultate werden mit den Vorhersagen des vorgeschlagenen mikroskopischen Degradationsmodells verglichen, Übereinstimmungen werden aufgezeigt und Schlussfolgerungen über den Prozesseinfluss werden gezogen.

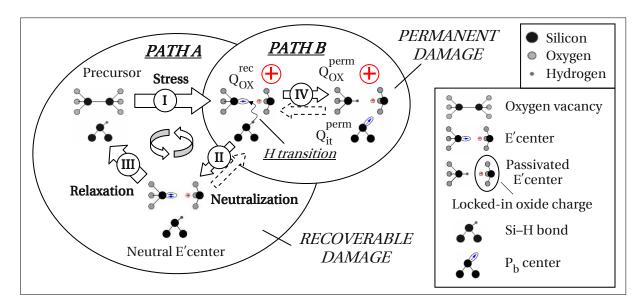

Das aktuelle mikroskopische Model beschreibt die Bauelement-Degradation unter NBTI als einen Zweistufenprozess, dessen Ausgangsdefekt eine Sauerstofffehlstelle (oxygen vacancy) im amorphen SiO<sub>2</sub> Gateoxid ist. Unter thermischen und elektrischen Stress (NBTI) kann die verspannte Fehlstelle aufbrechen, wodurch ein positiv geladener Defekt im Oxid entsteht. Dieser Defekt ist unabhängig von der Wasserstoffpassivierung, kann umgeladen werden und wieder ausheilen, vorausgesetzt, er wurde zuvor elektrisch neutralisiert. Die zweite Defektklasse besteht aus Grenzflächenzuständen (dangling bonds), die durch feld- und temperaturunterstützes Ablösen von Wasserstoff erzeugt werden. Untersuchungen deuten darauf hin, dass sich der abgelöste Wasserstoff mit einer aufgebrochenen Sauerstofffehlstelle verbinden kann, wodurch die Ausheilung des Oxiddefekts blockiert wird (locked-in oxide defect). Diese dadurch entstehenden quasi-permanenten Defekte spielen eine wichtige Rolle für die NBTI-Stabilität einer Technologie, da sie nur langsam und nur unter bestimmten Voraussetzungen ausheilen und wegen ihres Wasserstoffbezugs stark vom back-end Prozess abhängen.

## Abstract

**D**<sup>EVICE</sup> degradation and gate oxide reliability has become more and more important in modern semiconductor industry because the challenges for devices increase with miniaturization, larger stress within the circuit, and due to innovative technologies. Besides the reliability of mechanical soldering and wiring, it is of considerable importance to protect the transistor already in the early stages of processing from environmental impurities and mechanical stress. To furthermore guarantee the switching of high currents with minimum power dissipation as well as short-circuit stability, different isolation and metalization layers are deposited in a specific composition and sequence on the active areas of the transistor at the end of device fabrication (back-end of line). It is an accepted fact that different passivation concepts and layer sequences affect the electric characteristics and the reliability of silicon devices, because a lot of hydrogen is incorporated into the system during the back-end process. It is assumed that high temperatures going along with layer deposition and annealing support hydrogen diffusion toward the gate oxide where it may passivate defects within the oxide and at the interface. When subjecting the device afterwards to electrical and thermal stress, the hydrogen may be released again, thereby re-activating previously passivated defects.

Just like any semiconductor manufacturer worldwide, Infineon Villach has repeatedly encountered the problem in the past, and although particular solutions to some technologies have already been found, a global understanding of the underlying physics behind the interplay of processing and degradation is lacking. Because it is likely that new problems with the same roots may become relevant in future technology development, it is of fundamental importance to develop a physically based model which is able to link defect generation and passivation to single process steps.

Besides the above mentioned process impacts, also the physics behind the degradation mechanisms of gate oxide and interface are far from being understood. One of the most important degradation mechanisms is the so-called 'Negative Bias Temperature Instability' (NBTI) which leads to time dependent threshold voltage shifts when the gate oxide of the device is stressed at an elevated temperature and bias. NBTI is particularly interesting for the back-end process since it is assumed that the degradation mechanism is closely connected to hydrogen passivation of the Si–SiO<sub>2</sub> interface.

One aim of this PhD thesis is to investigate the role of hydrogen in NBTI and to verify the results by means of process splits. Specific emphasis is put on high voltage (HV) MOSFET devices having 30 nm SiO<sub>2</sub> gate oxides, as processed at Infineon Villach. Until now the scientific community has mainly been focusing on ultrathin (nitrided or high– $\kappa$ ) oxides whereas contributions on thicker oxides relevant for power technologies are hardly found in literature. At first, basic signatures of the 'Bias Temperature Instability' (BTI) of  $30 \text{ nm SiO}_2$  devices are collected using common measurement methods and the results are compared to state-of-the-art thinoxide high- $\kappa$  technologies. This preliminary study contains considerations on electrostatics and dynamics of degradation and recovery and helps to collect fundamental electric characteristics of emerging defects. A literature study on the current understanding of different species of point defects and their correlation to hydrogen is presented in order to enhance the physical understanding. The collected results are used to develop new measurements setups and experimental procedures which enable us to characterize threshold voltage shifts in various ways and assign the different contributions to certain defect classes with particular attributes. From the data and conclusions a microscopic degradation model is going to be suggested which is capable of explaining (at least qualitatively) the obtained results. In order to include hydrogen, the new measurement routines are performed on different split wafers which provide demonstrably different hydrogen budgets within the gate oxide. The results are cross-checked with the predictions of the suggested microscopic degradation model, agreements are highlighted and conclusions are drawn on the process impact.

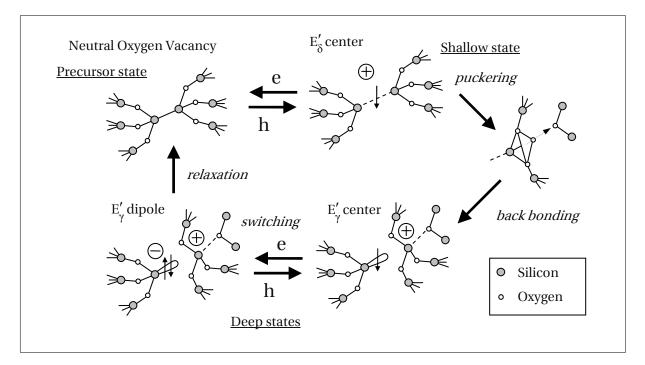

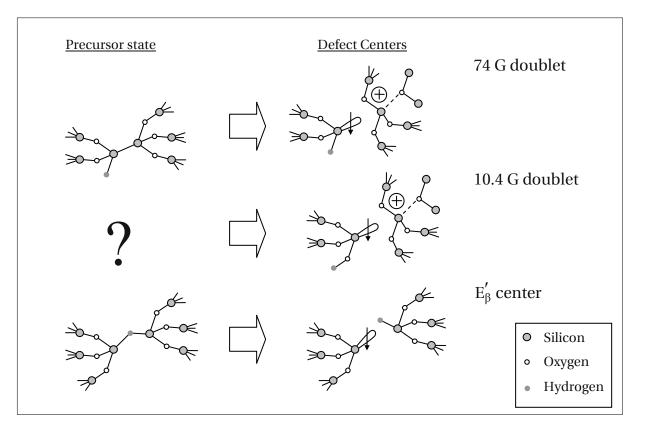

The current microscopic model explains device degradation under NBTI as a two stage process, the precursor being an oxygen vacancy defect in the amorphous  $SiO_2$  gate oxide. By subjecting the device to thermal and electrical stress (NBTI) the bond may be broken, thereby creating a positively charged defect. This defect is independent of hydrogen, rechargeable and can be annealed, provided it has been neutralized in advance. The second defect class consists of interface states (dangling bonds) which are created due to field- and temperature-assisted release of hydrogen. Studies suggest that the released hydrogen may become trapped in the broken oxygen vacancy, thereby blocking the relaxation of the oxide defect. These quasi-permanent defects play an important role for the NBTI-stability of a technology since they recover just slowly and only under certain conditions, and due to their correlation to hydrogen, their concentration depends strongly on the back-end process.

## Contents

| 1 | The                                      | Negat                                                | ive Bias Temperature Instability                                                          | 1  |  |

|---|------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------|----|--|

|   | 1.1 Industrial Background and Motivation |                                                      |                                                                                           |    |  |

|   | 1.2                                      | Historical Background and Relevance                  |                                                                                           |    |  |

|   | 1.3                                      | Opera                                                | ating conditions causing bias temperature instability                                     | 3  |  |

| 2 | Elec                                     | ctrosta                                              | tics of NBTI degradation                                                                  | 6  |  |

|   | 2.1                                      | Effects of NBTI on analogue transfer characteristics |                                                                                           | 6  |  |

|   |                                          | 2.1.1                                                | Influence of mobility degradation and defect charges on the total $V_{\mathrm{TH}}$ shift | 9  |  |

|   |                                          | 2.1.2                                                | Spurious $V_{\text{TH}}$ shift due to mobility degradation $(\Delta V_{\text{TH}}^{\mu})$ | 10 |  |

|   |                                          | 2.1.3                                                | $V_{\rm TH}$ shift due to defect charges ( $\Delta V_{\rm TH}^{ m q}$ )                   | 12 |  |

|   |                                          | 2.1.4                                                | Relevance of defect charge induced $V_{\rm TH}$ shift and mobility degradation            | 15 |  |

|   |                                          | 2.1.5                                                | Case study                                                                                | 16 |  |

|   | 2.2                                      | Classi                                               | fication of defect charges by their electrical response time                              | 19 |  |

|   |                                          | 2.2.1                                                | Charge pumping as a qualification tool                                                    | 20 |  |

|   |                                          | 2.2.2                                                | Energetic mismatch between the CP technique and the static DC approach $\ldots$           | 23 |  |

| 3 | Dyn                                      | amics                                                | of NBTI degradation and recovery                                                          | 27 |  |

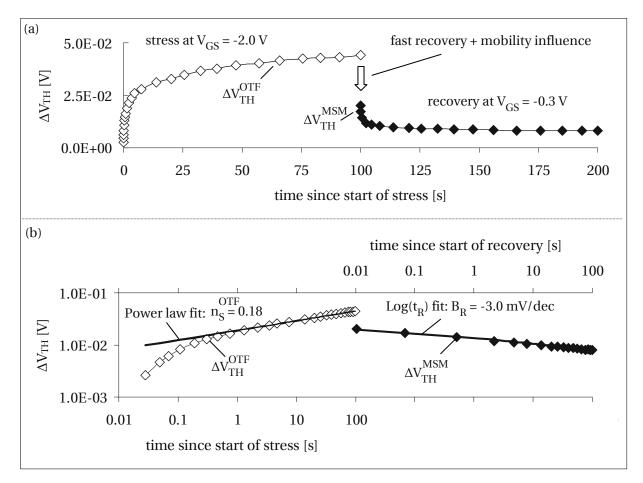

|   | 3.1                                      | Static                                               | MSM and OTF                                                                               | 29 |  |

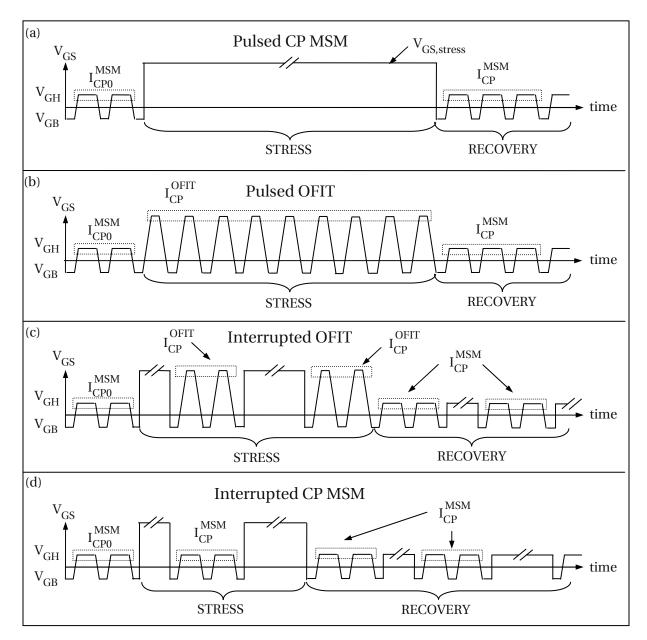

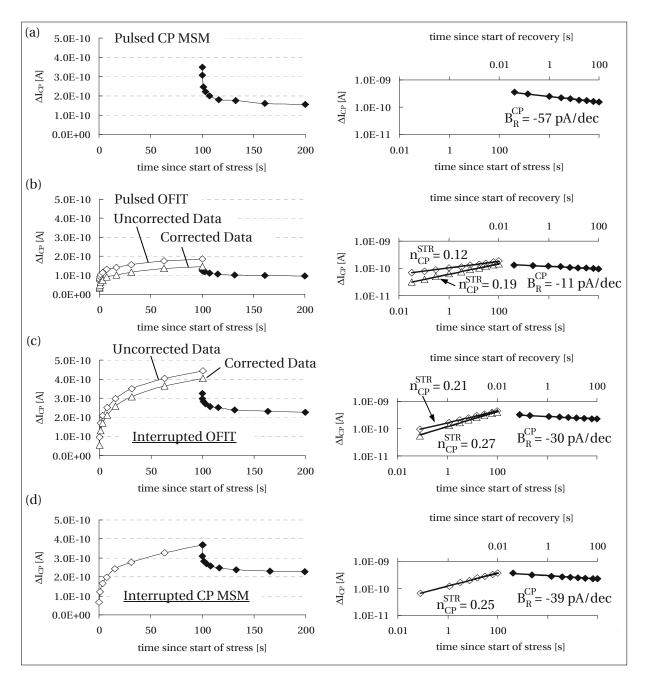

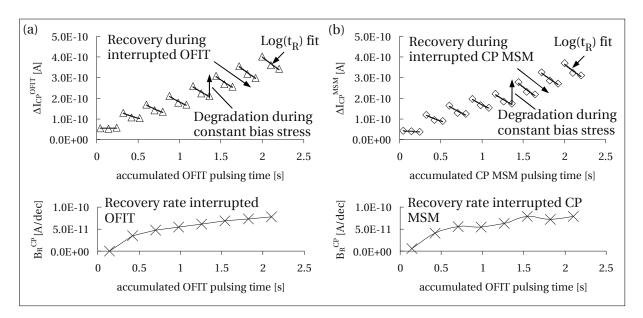

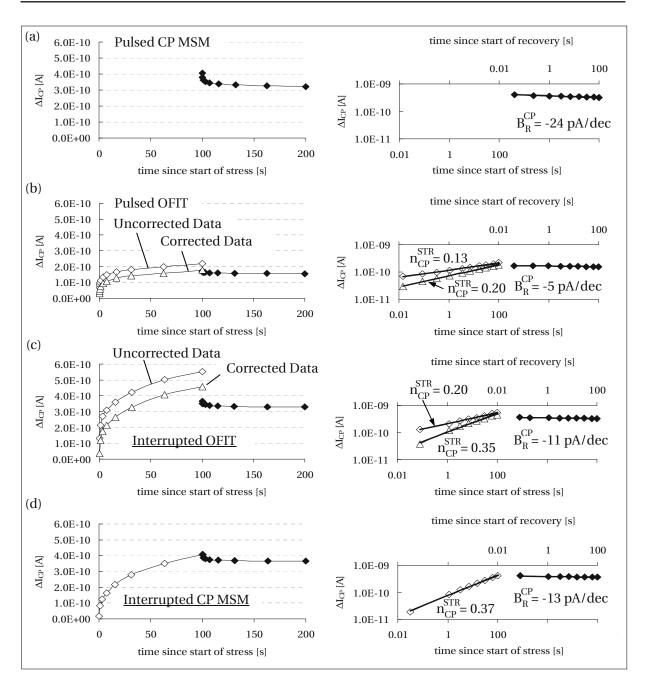

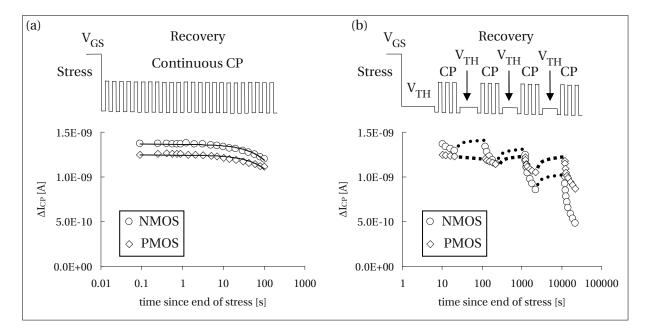

|   | 3.2                                      | CP MSM and OFIT                                      |                                                                                           | 32 |  |

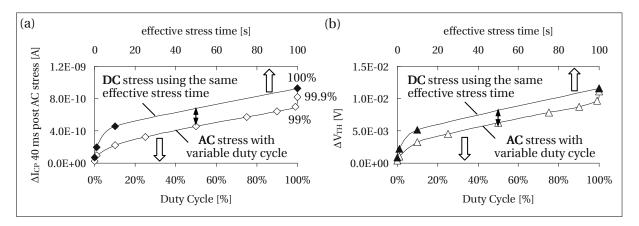

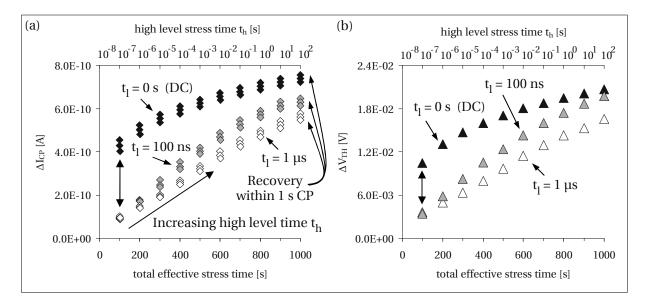

|   | 3.3                                      | Duty cycle dependence of NBTI degradation            |                                                                                           |    |  |

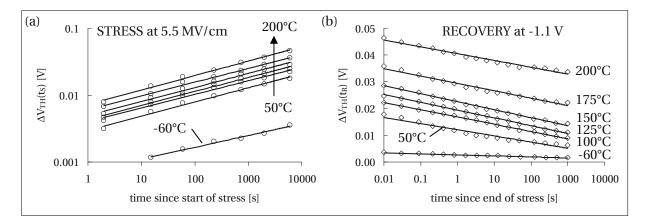

|   | 3.4                                      | Temp                                                 | erature and oxide field – the driving forces of NBTI degradation                          | 44 |  |

|   |                                          |                                                      |                                                                                           |    |  |

|   |     | 3.4.1 The role of the stress/recovery temperature                                                                                                                                               | 45       |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|   |     | 3.4.2 The role of the stress field                                                                                                                                                              | 47       |

|   |     | 3.4.3 Recovery saturation                                                                                                                                                                       | 49       |

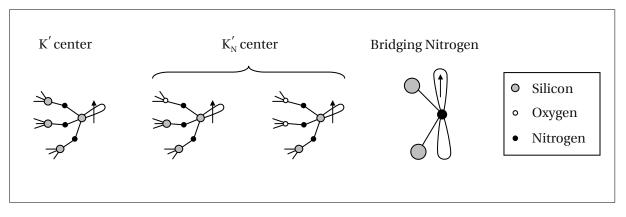

| 4 | Poi | nt defects and their correlation to hydrogen                                                                                                                                                    | 51       |

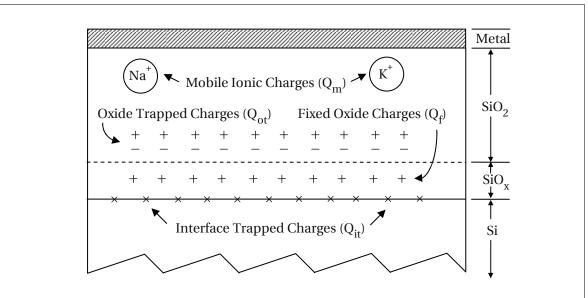

|   | 4.1 | Terminology and defect classes                                                                                                                                                                  | 51       |

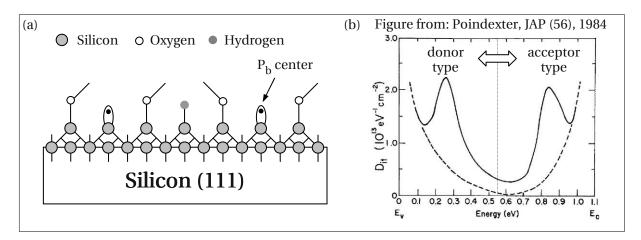

|   | 4.2 | The P <sub>b</sub> center                                                                                                                                                                       | 52       |

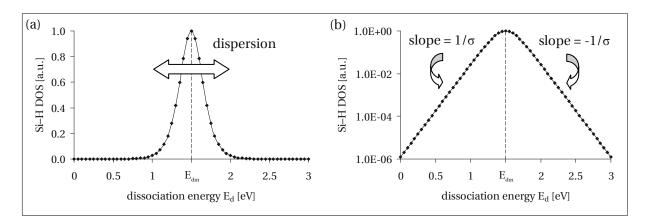

|   | 4.3 | The E' center                                                                                                                                                                                   | 54       |

|   | 4.4 | The K' center                                                                                                                                                                                   | 57       |

| 5 | Bia | s dependence of degradation and recovery                                                                                                                                                        | 60       |

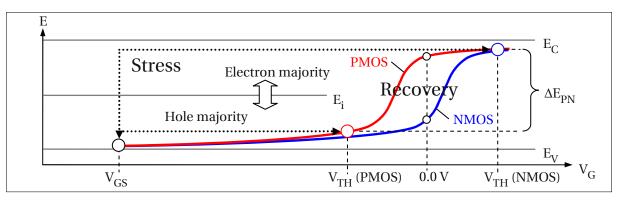

|   | 5.1 | PMOS & NMOS Combination Technique                                                                                                                                                               | 61       |

|   | 5.2 | Bias dependence of the CP current recovery                                                                                                                                                      | 62       |

|   | 5.3 | Bias dependence of the $\Delta V_{\text{TH}}$ recovery $\ldots \ldots \ldots$   | 64       |

|   | 5.4 | Bias dependence of the $\Delta V_{\text{TH}}$ extraction $\ldots \ldots \ldots$ | 66       |

|   | 5.5 | Conclusions – Bias dependence of the $\Delta V_{\text{TH}}$ shifts $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                    | 67       |

| 6 | The | role of temperature in NBTI characterization                                                                                                                                                    | 69       |

|   | 6.1 | Fast heating and cooling using in-situ polyheaters                                                                                                                                              | 69       |

|   |     | 6.1.1 Hardware assembly and polyheater design                                                                                                                                                   | 70       |

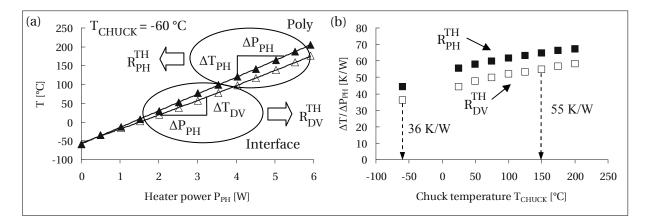

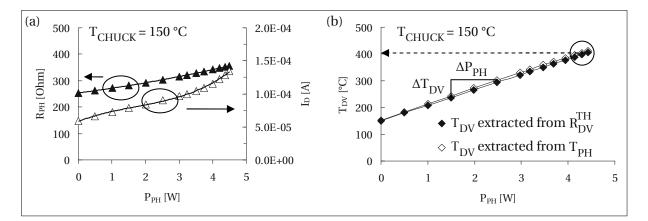

|   |     | 6.1.2 Calibration of heater and device temperature                                                                                                                                              | 71       |

|   |     | 6.1.3 Maximum accessible temperature range                                                                                                                                                      | 73       |

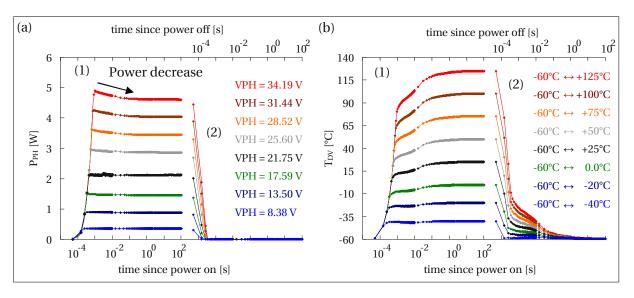

|   |     | 6.1.4 Heating and cooling dynamics                                                                                                                                                              | 75       |

|   |     |                                                                                                                                                                                                 |          |

|   |     | 6.1.5 Summary of the polyheater features                                                                                                                                                        | 76       |

|   | 6.2 | 6.1.5 Summary of the polyheater features      On the temperature dependence of NBTI recovery                                                                                                    | 76<br>77 |

|   | 6.2 |                                                                                                                                                                                                 |          |

|   | 6.2 | On the temperature dependence of NBTI recovery                                                                                                                                                  | 77       |

|   | Hardware                     |                                                                  |                                                                                                  |     |  |

|---|------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----|--|

|   | 9.2                          | Variat                                                           | ion of the transconductance with the interface state density                                     | 130 |  |

|   | 9.1                          | Transo                                                           | conductance as a function of the gate bias overdrive                                             | 129 |  |

| 9 | Арр                          | endix                                                            |                                                                                                  | 129 |  |

| 8 | Sun                          | nmary                                                            | and Conclusions                                                                                  | 126 |  |

|   | 7.3                          | Concl                                                            | usions on the role of hydrogen in the NBTI                                                       | 125 |  |

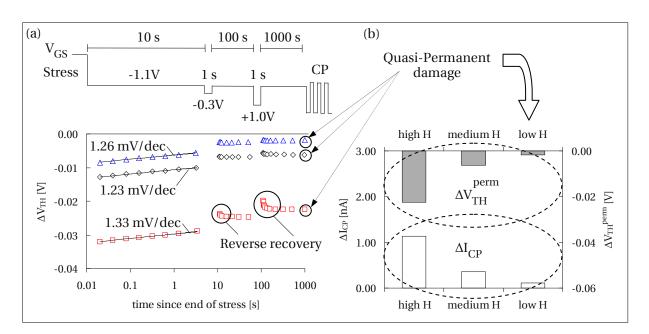

|   |                              | 7.2.2                                                            | Interaction of hydrogen with recoverable and quasi-permanent damage                              | 121 |  |

|   |                              | 7.2.1                                                            | Energetic distribution and dynamic evolution of recoverable oxide traps                          | 119 |  |

|   | 7.2                          | 2 Interaction of hydrogen with degradation and recovery dynamics |                                                                                                  | 119 |  |

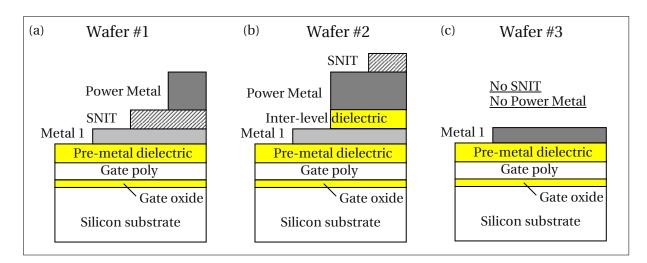

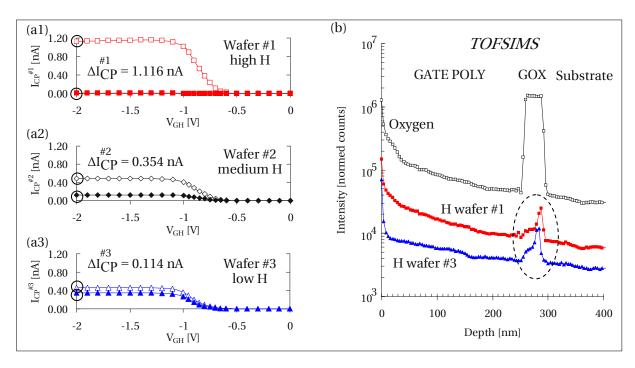

|   | 7.1                          | Basic                                                            | signatures linked to BEOL hydrogen incorporation                                                 | 116 |  |

| 7 | The                          | role of                                                          | hydrogen in NBTI degradation                                                                     | 115 |  |

|   |                              | 6.4.6                                                            | Extension of the microscopic model explaining NBTI induced defects                               | 111 |  |

|   |                              | 6.4.5                                                            | Discussion on the power-law exponent                                                             | 109 |  |

|   |                              | 6.4.4                                                            | Correlation between interface states and $V_{\rm TH}$ shift $\ldots \ldots \ldots \ldots \ldots$ | 106 |  |

|   |                              | 6.4.3                                                            | Discussion on the stress dependent recovery rate                                                 | 103 |  |

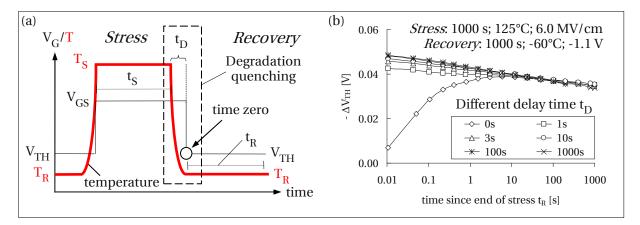

|   |                              | 6.4.2                                                            | Experimental setup for low temperature characterization                                          | 102 |  |

|   |                              | 6.4.1                                                            | Experimental constraints associated with conventional MSM techniques                             | 101 |  |

|   | 6.4 NBTI at low temperatures |                                                                  | 100                                                                                              |     |  |

|   |                              | 6.3.4                                                            | Conclusions on the microscopic origin of NBTI induced defects                                    | 100 |  |

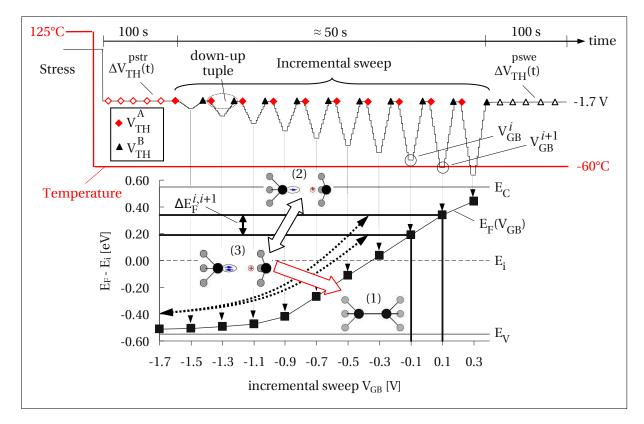

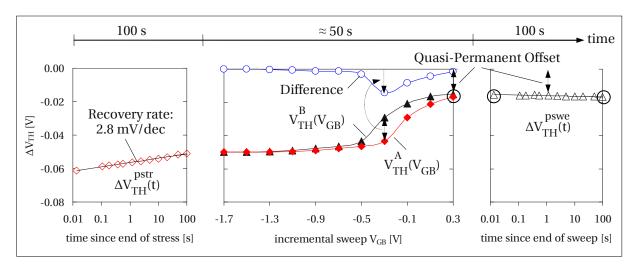

|   |                              | 6.3.3                                                            | Energetic profiling of recoverable oxide defects                                                 | 96  |  |

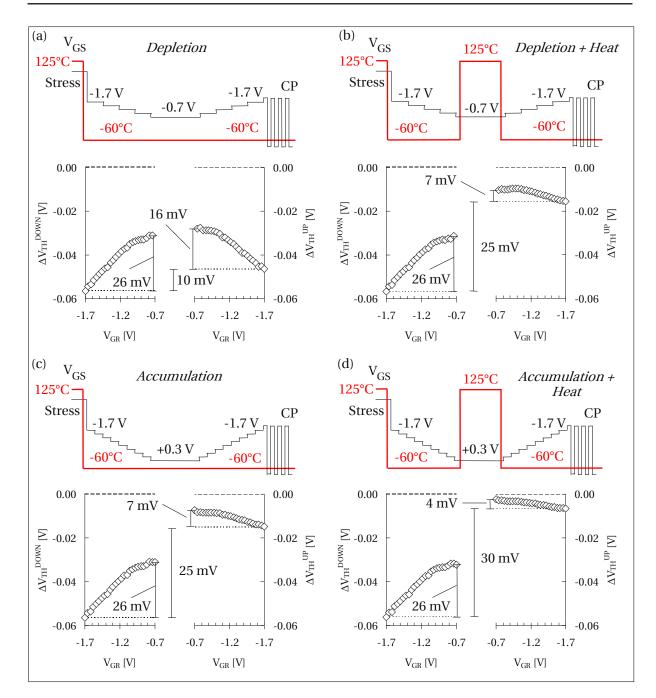

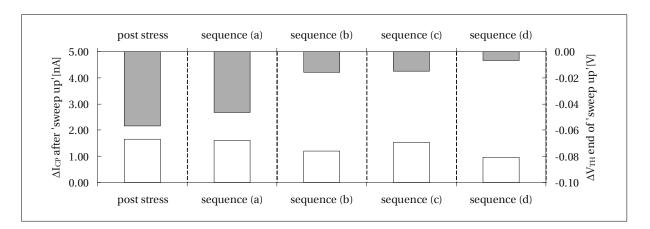

|   |                              | 6.3.2                                                            | Individual experimental setups and results                                                       | 92  |  |

|   |                              | 6.3.1                                                            | Basic experimental approach and proposed underlying model transitions                            | 90  |  |

|   |                              |                                                                  | fication of defects by their recovery characteristics                                            | 89  |  |

|   |                              | 6.2.5                                                            | Conclusions – T-dependence of $\Delta V_{\text{TH}}$ and CP current recovery                     | 87  |  |

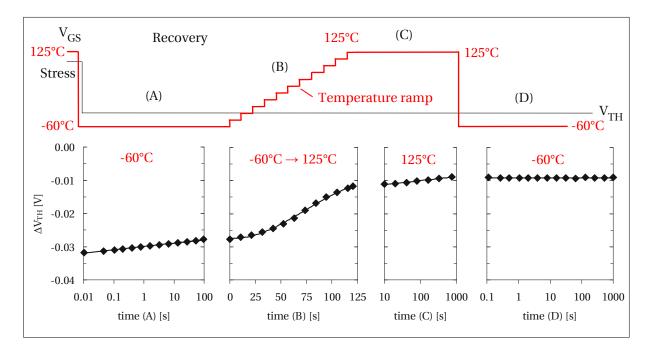

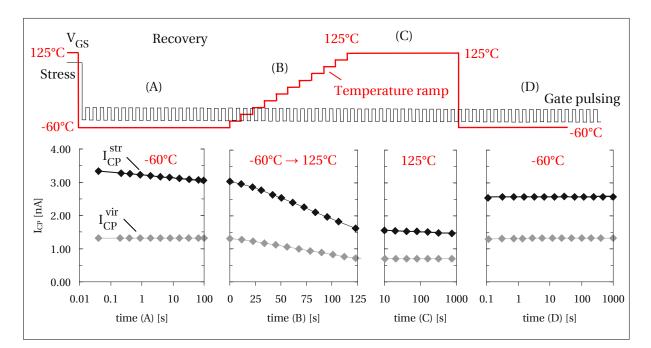

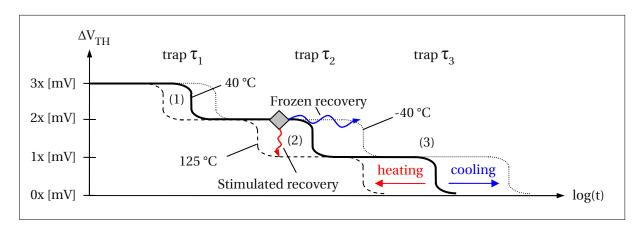

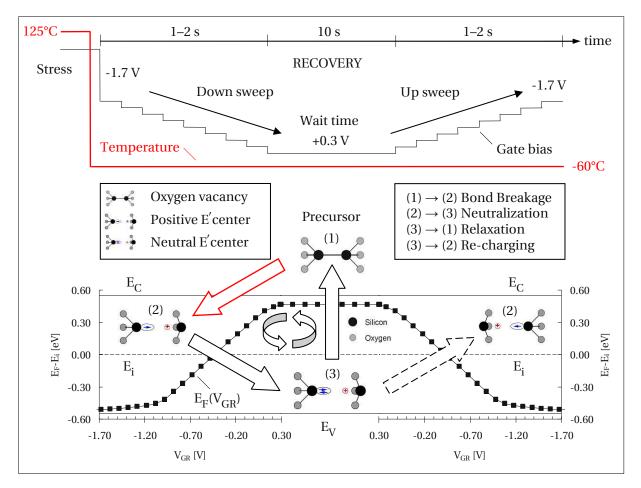

|   |                              | 6.2.4                                                            | Identically stressed devices subjected to temperature ramps                                      | 84  |  |

| Bibliography     | 132 |

|------------------|-----|

| Own Publications | 146 |

| Acronyms         | 148 |

| Symbols          | 151 |

| Curriculum vitæ  | 156 |

1

## The Negative Bias Temperature Instability

### 1.1 Industrial Background and Motivation

ONCE a new device technology is released from product line, it has to overcome several qualification procedures before it finally gets approved for delivery to the customer. Within those qualification tests it is checked for example whether the new product is working regularly and whether it meets the proposed parameter specifications. Besides initial parameter testing, also the reliability of random samples is monitored meticulously during different stages of the fabrication (i.e. wafer level, package level). This is done in order to collect statistics about extrinsic defect densities causing early device failure and parameter drifts causing gradual degradation of the device within years under operating conditions. Furthermore, fundamental conclusions are drawn on process changes which go along with device shrinking and upgraded innovation standards. Companies invest a lot of money and man power in this area to develop, produce, monitor and evaluate reliability test chips on split wafers that are specifically designed for gaining experience in process influences helping to optimize device performance while simultaneously minimizing production costs. Hence, physically based models explaining process influences on device performance are highly demanded and of great economical interest.

During reliability testing every important device parameter is assigned to a certain drift margin which has to be satisfied and finally determines the lifetime of the product. Considering that the aimed lifetimes of most semiconductor products lie in the range of several tens of years whereas a single qualification test has to be completed within hours, it would be highly inefficient and much too time consuming (if not impossible) to perform lifetime prediction tests under use conditions. Thus, in order to guarantee within a reasonable testing time that an airbag chip will still work at the end of

the cars' lifetime, it is necessary to subject devices to extreme test conditions (accelerated tests). For the analysis of the data, elaborated acceleration models are required allowing to estimate the actual parameter drift under use conditions from a parameter shift measured under accelerated conditions. Thus, in order to make reliable lifetime predictions, physically based acceleration models are urgently needed for each degradation mechanism. So far most existing models are empirical.

One of the most popular degradation mechanism affecting the gate oxide and the interface of metal oxide semiconductor field effect transistors (MOSFETs) is the so-called negative bias temperature instability (NBTI). As opposed to destructive failure modes like time dependent dielectric breakdown (TDDB), NBTI does not cause hard failures (short circuits across the oxide) which limit the possibilities of post stress characterization dramatically but rather leads to a creeping shift in the threshold voltage (typically several tens of mV) and to a gradual degradation of the channel mobility and the transconductance of a conventional metal oxide semiconductor (MOS) transistor. The resulting variations in the analog transfer characteristics of the device can cause severe problems especially when the afflicted transistor is incorporated in a digital network or when the demanded specification margin of the technology is very narrow. Since NBTI is very sensitive to variations in device processing, it is particularly hard to control the NBTI resistivity of a technology during device development. The main focus of this PhD thesis is to broaden the knowledge around NBTI by performing stress/recovery experiments on specifically designed test chips. Furthermore, correlations of the effect with process influences, in particular with hydrogen introduced during the back-end of line (BEOL) fabrication, are studied extensively by means of wafer splits produced at Infineon Technologies Austria.

### 1.2 Historical Background and Relevance

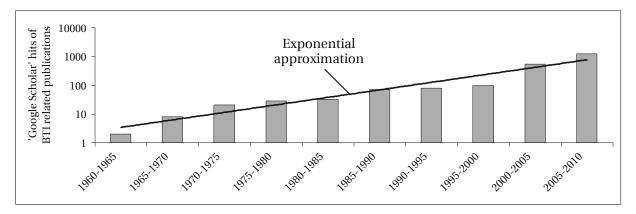

The bias temperature instability (BTI) in MOS devices has been known since the middle of the 1960s [1–4] and has been attributed to defects located at the Si–SiO<sub>2</sub> interface since the beginning of the 1970s [5]. Since that time BTI has been a vigorously discussed topic in the semiconductor community and numerous papers focusing on measurement techniques, modeling attempts and technology impact circulate in various scientific journals and conference proceeding. The increasing importance of the topic may be illustrated schematically by searching via 'Google Scholar' for publications containing variants of the keywords 'bias temperature stress', 'silicon' and 'oxide' itemized by the past decades of years. In Fig. 1.1 the result of such a simple keyword search is depicted as 'number of Google Scholar Hits' graded by five year intervals since the 1960s.

Naturally, the exact number of hits will depend considerably on the selected keywords making their absolute values somewhat arbitrary. Nevertheless, the overall roughly exponentially increasing trend of BTI related publications is likely to be reproduced independently of the subjective choice of the keywords.

The first attempt to describe the BTI phenomenon by a micro-physical degradation model is due to Jeppson and Svensson in 1977 [6] who assumed the surface trap growth as being caused by hydrogen release from Si–H bonds located at the interface. The dynamics of degradation were assumed to be

**Figure 1.1:** 'Google Scholar hits' of BTI related publications since the 1960s to the present date (2010). The number of hits (column bars) found by 'Google Scholar' increase roughly exponentially from the 1960s to 2010 (solid line). Within the past five years between 2005 and 2010 'Google Scholar' lists more than 1200 hits for the selected keywords.

diffusion controlled at low fields and tunneling limited at high fields. Since that time a lot of progress has been made to get the BTI under control. Although, numerous papers have been published on the topic, the issue is still far from being closed. There are a lot of open questions left which have to be resolved in order to understand discrepancies in experimental data and eliminate inconsistencies between suggested models. Since the BTI problem is going to become even more relevant in the future due to continuous processing and scaling changes, a universally valid model including process influences is urgently needed. Besides that a fundamental understanding of BTI may also lead to a better understanding of related degradation mechanisms like hot carrier injection (HCI) or TDDB.

## 1.3 Operating conditions causing bias temperature instability

When performing a bias temperature stress (BTS) on a MOS transistor, the device is usually heated to a defined stress temperature ( $T_S$ ) and is then subjected to a relatively large electric field ( $E_{OX}$ ) across the gate oxide (GOX) by applying a defined stress bias to the gate junction of the transistor. In general, the degradation characteristics following BTS depend strongly on the polarity of the applied gate bias during stress and on the doping type of the device under test (DUT). When applying for instance a *positive* gate bias during stress, one speaks of positive bias temperature instability (PBTI) [7], while degradation following a *negative* bias stress gives the classical NBTI [8–12]. The largest amount of damage is usually observed when subjecting a p-channel metal oxide semiconductor (PMOS) transistor to negative bias temperature stress (NBTS).

During NBTI stress, all transistor contacts except for the gate are grounded resulting in a relatively homogeneous stress field, hence generating uniformly distributed defects along the entire gate oxide area. When neglecting small variations of the doping profile along the transistor channel, in particular close to the source/drain implantations, the dimension of the problem is reduced by the symmetry of the stress profile from three to one, perpendicular to the gate oxide-substrate interface. The

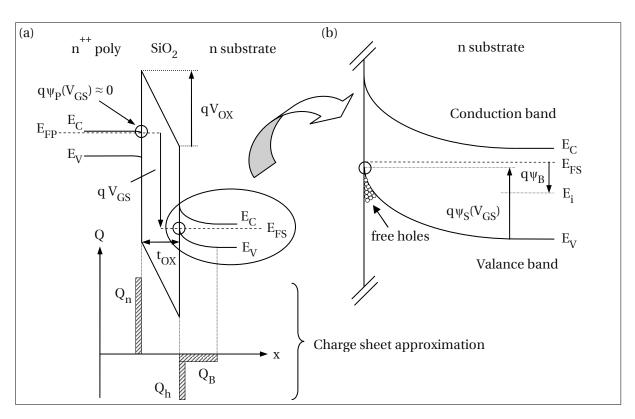

**Figure 1.2:** The band diagram and the charge balance of a PMOS transistor with an  $n^{++}$  gate poly during NBTS (a). The interface and the depletion region within the Si substrate is enlarged in (b).

band banding situation during NBTS is schematically depicted in Fig. 1.2 (a) for a PMOS transistor equipped with an  $n^{++}$  gate poly.

Due to the large negative gate voltage ( $V_{GS} \ll V_{TH}$ ) applied during stress, the interface of the n<sup>++</sup> gate junction ( $N_D \approx 10^{20} \text{ cm}^{-3}$ ) becomes heavily accumulated with majority electrons ( $Q_e$ ). Hence, the Fermi level ( $E_{FP}$ ) remains pinned close to the conduction band edge at the polysilicon/silicon dioxide (SiO<sub>2</sub>) interface, the band banding within the gate junction being approximately zero ( $\psi_P \approx 0$ ). On the other side of the gate oxide the moderately n-doped silicon substrate ( $N_D \approx 10^{16} \text{ cm}^{-3}$ ) becomes heavily inverted attracting injected minority holes ( $Q_h$ ) to the SiO<sub>2</sub>/silicon (Si) interface. The depletion layer containing the bulk charge ( $Q_B$ ) approaches its maximum extension increasing the surface potential ( $\psi_S$ ), thereby bending the valence band edge at the SiO<sub>2</sub>/Si interface toward the substrate Fermi level ( $E_{FS}$ ). Following Fig. 1.2 (b), the band bending during stress (maximum surface potential  $\psi_{S,max}$ ) may be estimated as

$$q\psi_{\rm S,max} \approx E_{\rm i} - E_{\rm V} + q\psi_{\rm B},\tag{1.1}$$

where  $E_i$  is the intrinsic energy,  $E_V$  is the valence band edge, q is the elementary charge and  $\psi_B$  is the bulk potential ( $\psi_B$ ) which is given by

$$\psi_{\rm B} = \frac{k_{\rm B}T}{\rm q} \ln\left(\frac{N_{\rm D}}{n_{\rm i}}\right). \tag{1.2}$$

In Eq. 1.2,  $k_B$  is the Boltzmann constant,  $N_D$  is the donor doping density of the substrate material and  $n_i$  is the intrinsic carrier concentration. When performing a full voltage loop along the band edges in Fig. 1.2 (a) one obtains

$$V_{\rm GS} = -V_{\rm OX} - \psi_{\rm S,max} - \psi_{\rm P} - V_{\rm FB}.$$

(1.3)

In Eq. 1.3,  $V_{OX}$  is the voltage drop across the gate oxide and  $V_{FB}$  is the flat band voltage which may be approximated as the difference in the work functions between the poly silicon gate junction and the silicon substrate assuming an ideal interface and no charges within the SiO<sub>2</sub> gate oxide:

$$V_{\rm FB} \approx \Phi_{\rm P} - \Phi_{\rm S} \approx \frac{E_{\rm G}}{\rm q} - \psi_{\rm S,max} - \psi_{\rm P}.$$

(1.4)

By inserting Eq. 1.4 in Eq. 1.3, one finds

$$V_{\rm GS} \approx -V_{\rm OX} - \frac{E_{\rm G}}{\rm q}.$$

(1.5)

From Eq. 1.5 a simple approximation for the electric field  $E_{OX}$  is obtained when stressing a PMOS transistor equipped with a n<sup>++</sup> gate poly under NBTS:

$$E_{\rm OX}^{\rm n++} = -\frac{V_{\rm OX}}{t_{\rm OX}} \approx \frac{V_{\rm GS} + 1.1 \,\rm V}{t_{\rm OX}},$$

(1.6)

1.1V being the silicon bandgap  $E_G$  at a typical stress temperature of 125°C. A similar deviation for a PMOS transistor equipped with a p<sup>++</sup> gate poly yields the following approximation for the electric field during NBTS [13]:

$$E_{\rm OX}^{\rm p++} = -\frac{V_{\rm OX}}{t_{\rm OX}} \approx \frac{V_{\rm GS} + |V_{\rm Poly}|}{t_{\rm OX}},\tag{1.7}$$

where  $V_{\text{Poly}}$  stands for the voltage drop within the gate poly junction (poly depletion) which is typically very small [14] due to the high poly doping density ( $V_{\text{Poly}} \approx 0.1 \text{ V}$  for  $N_{\text{A}} \approx 10^{20} \text{ cm}^{-3}$ ).

When comparing Eq. 1.6 and Eq. 1.7, we come to the conclusion that a PMOS transistor equipped with a  $n^{++}$  gate poly has to be stressed under a larger gate voltage of approximately 1.0V compared to a PMOS transistor equipped with a  $p^{++}$  gate poly in order to generate similar electric fields during NBTI stress. The same considerations hold for an n-channel metal oxide semiconductor (NMOS) transistor as well, the holes at the SiO<sub>2</sub>/Si interface being then supplied by the p-doped silicon substrate.

Typical stress fields applied during NBTI are between 2.5 MV/cm and 8.0 MV/cm [15]. The magnitude of degradation caused by fields below 2.5 MV/cm is usually very small and hence often below the detection limit at typical stress temperatures ( $50^{\circ}C - 200^{\circ}C$ ) within typical stress times (1 ms - 100,000 s). Fields above 8 MV/cm introduce different degradation mechanisms like impact ionization by 'hot' carriers which tunnel through the gate oxide causing intrinsic TDDB due to the gradual formation of a conductive percolation path across the oxide [16–18]. When stressing thick oxide devices, the effect emerges earlier since the voltage drop across the gate oxide ( $V_{OX}$ ) is larger at the same  $E_{OX}$ .

2

## Electrostatics of NBTI degradation

**T**<sup>HIS</sup> chapter addresses origins of NBTI induced drain current degradation in the linear and in the saturation operation regime of the transistor. The gate bias dependence of the threshold voltage shift is discussed theoretically and by means of a case study without taking time dependent degradation and recovery dynamics into account. An electrostatic treatment of the problem is basically justified when the time delay between stress and measurement is large enough so that defect relaxation during the measurement may be neglected.

Having identified the main causes of device degradation under DC bias conditions, the second part of this chapter introduces an experimental approach based on high frequency AC gate pulsing, allowing to separate charged defect classes which normally remain indistinguishable in a conventional DC experiment. This is because in DC experiments any kind of charged defect affects the threshold voltage shift in a similar way independent of its microscopic nature. Due to this superposition, it is not straight-forward to assign a certain contribution of the  $V_{\text{TH}}$  shift to a particular defect.

### 2.1 Effects of NBTI on analogue transfer characteristics

When stressing a MOS device under NBTS, we generally observe a variation in the drain current ( $\Delta I_D$ ) when measuring the same operating point (under the same bias conditions) again after stress. The linear and the saturation drain current of a long-channel PMOS transistor (such as mostly considered

here) above the threshold voltage of the device  $(|V_{GS}| \ge |V_{TH}|)$  can be approximated by the following equations [19]:

$$I_{\rm D,lin}(V_{\rm DS} < V_{\rm DSS}) \approx -\frac{W}{L} \mu_{\rm eff} C_{\rm OX} \left( (V_{\rm GS} - V_{\rm TH}) - \frac{1}{2} V_{\rm DS} \right) V_{\rm DS},$$

(2.1)

$$I_{\text{D,sat}}(V_{\text{DS}} \ge V_{\text{DSS}}) \approx -\frac{1}{2} \frac{W}{L} \mu_{\text{eff}} C_{\text{OX}} \left( V_{\text{GS}} - V_{\text{TH}} \right) V_{\text{DSS}}, \tag{2.2}$$

where the saturation drain voltage  $(V_{\text{DSS}})$  is approximately given by

$$V_{\rm DSS} \approx (V_{\rm GS} - V_{\rm TH}) \tag{2.3}$$

and the physically defined threshold voltage can be derived as

$$V_{\rm TH} \approx V_{\rm FB} - 2\psi_{\rm B} - \frac{\sqrt{2\epsilon_{\rm OX}qN_{\rm D}(2\psi_{\rm B})}}{C_{\rm OX}}.$$

(2.4)

In Eq. 2.1 and Eq. 2.2, the two unstable device parameters that may cause a degradation in the drain current during NBTS are the effective inversion carrier mobility ( $\mu_{eff}$ ) and the threshold voltage ( $V_{TH}$ ) of the device. The relative variation of the drain current as a function of the overdrive can be obtained by calculating the total derivative of Eq. 2.1 and Eq. 2.2:

$$\frac{\delta I_{\rm D,lin}}{I_{\rm D,lin}} \approx \frac{\delta \mu_{\rm eff}}{\mu_{\rm eff}} - \frac{\delta V_{\rm TH}}{V_{\rm GS} - V_{\rm TH}},\tag{2.5}$$

$$\frac{\delta I_{\text{D,sat}}}{I_{\text{D,sat}}} \approx \frac{\delta \mu_{\text{eff}}}{\mu_{\text{eff}}} - 2 \frac{\delta V_{\text{TH}}}{V_{\text{GS}} - V_{\text{TH}}}.$$

(2.6)

Eq. 2.5 and Eq. 2.6 demonstrate that the total degradation of the drain current is directly proportional to the change of the effective carrier mobility and to the change of the threshold voltage shift divided by the gate bias overdrive ( $V_{\text{GS}} - V_{\text{TH}}$ ). In the saturation region, the threshold voltage degradation has a larger influence on the drain current degradation than in the linear region making the signal vs. noise resolution as a function of the  $V_{\text{TH}}$  shift about two times better when measuring in the saturation region of the device. From Eq. 2.5 and Eq. 2.6 we further conclude that the measurement resolution of the drain current degradation is expected to decrease linearly, when increasing the gate voltage overdrive ( $|V_{\text{GS}}| \gg |V_{\text{TH}}|$ ).

Upon the build up of microscopic defects during NBTS, mobility and threshold voltage have been reported to degrade simultaneously which makes it difficult to differentiate between both effects. Once created, charged traps can act on the one hand as defect charges counterbalancing the applied gate potential ( $\Delta V_{TH}^{q}$ ) and on the other hand as Coulomb scattering centers decreasing the effective carrier mobility ( $\Delta \mu_{eff}$ ) and hence the on-resistance ( $R_{ON}$ ) of the device. In general, charged defects are particularly effective scattering centers when they are located close to or directly at the SiO<sub>2</sub>/Si interface. Following [20–22], the effective carrier mobility ( $\mu_{eff}$ ) can be empirically approximated as

$$\mu_{\rm eff} = \frac{\mu_0}{(1 + \alpha N_{\rm it})(1 + \Theta(V_{\rm GS} - V_{\rm TH}))}.$$

(2.7)

In Eq. 2.7  $\mu_0$  is the temperature and doping dependent low field mobility and  $N_{it}$  is the number of interface states per square centimeter. The first term of the denominator in Eq. 2.7 accounts for a reduction of this low field mobility as a consequence of enhanced Coulomb scattering at surface near charge centers ( $N_{it}$ ) while the second term considers mobility degradation caused by enhanced surface scattering when applying a vertical electric field. The coefficients  $\alpha$  and  $\Theta$  are empirical fit parameters which have to be determined experimentally from the stress induced shift in the transconductance ( $\alpha$ ) and from the curvature of the virgin transfer curve ( $\Theta$ ). From a physical point of view, following [22] and [23], the parameter  $\alpha$  is a scattering coefficient (capture cross section) that accounts for the interaction between charged interface states and inversion layer carriers. It has the unit [cm<sup>2</sup>] and may take values between  $10^{-12}$  cm<sup>2</sup> (depletion) and  $10^{-13}$  cm<sup>2</sup> (inversion), the lower limit being smaller due to carrier screening in deep inversion [24–26]. The parameter  $\Theta$  is the vertical field mobility coefficient [19] leading to a bending of the transfer curve in the triode region of the device. It has the unit [V<sup>-1</sup>] and considers the reduction of the mobility as a consequence of the growing electric field perpendicular to the moving direction of the inversion charge carriers.

Differentiating Eq. 2.7 with respect to the interface state density  $(N_{it})$  yields

$$\frac{\partial \mu_{\text{eff}}}{\partial N_{\text{it}}} = -\frac{\alpha}{1+\alpha N_{\text{it}}} \mu_{\text{eff}} + \frac{\Theta}{1+\Theta(V_{\text{GS}}-V_{\text{TH}})} \frac{\partial V_{\text{TH}}}{\partial N_{\text{it}}} \mu_{\text{eff}}, \qquad (2.8)$$

$$\frac{\Delta \mu_{\rm eff}}{\mu_{\rm eff}} = -\frac{\alpha \Delta N_{\rm it}}{1+\alpha N_{\rm it}} + \frac{\Theta \Delta V_{\rm TH}}{1+\Theta (V_{\rm GS} - V_{\rm TH})}.$$

(2.9)

Inserting Eq. 2.9 into Eq. 2.5 and Eq. 2.6, we may replace the variation in the effective mobility ( $\mu_{eff}$ ) by empirical constants:

$$\frac{\Delta I_{\rm D,lin}}{I_{\rm D,lin}} \approx -\frac{\alpha \Delta N_{\rm it}}{1+\alpha N_{\rm it}} - \left(\frac{1}{(V_{\rm GS} - V_{\rm TH})(1+\Theta(V_{\rm GS} - V_{\rm TH}))}\right) \Delta V_{\rm TH}^{\rm q},\tag{2.10}$$

$$\frac{\Delta I_{\text{D,sat}}}{I_{\text{D,sat}}} \approx -\frac{\alpha \Delta N_{\text{it}}}{1+\alpha N_{\text{it}}} - \left(\frac{2+\Theta(V_{\text{GS}}-V_{\text{TH}})}{(V_{\text{GS}}-V_{\text{TH}})(1+\Theta(V_{\text{GS}}-V_{\text{TH}}))}\right) \Delta V_{\text{TH}}^{\text{q}}.$$

(2.11)

Usually, when analyzing NBTI, the degradation of the drain current ( $\Delta I_{\rm D}$ ) is converted into a corresponding total threshold voltage shift ( $\Delta V_{\rm TH}$ ) by assigning the drain current measured post stress a corresponding gate voltage of the virgin transfer curve [27]. Following Fig. 2.1, the difference between the actually applied gate voltage during the drain current measurement and the hypothetical gate voltage corresponding to the same drain current recorded before stress on the virgin device gives the effective  $V_{\rm TH}$  shift ( $\Delta V_{\rm TH}$ ) describing a horizontal (voltage) shift of the transfer curve that is usually a function of the current gate bias due to the curvature of the transfer curve ( $\Theta$ ) and due to mobility degradation caused by defect scattering ( $\alpha$ ). Although the notation  $\Delta V_{\rm TH}$  is somehow related to the physically defined device threshold voltage (cf. Eq. 2.4), it is also common for shifts measured at arbitrary gate voltages.

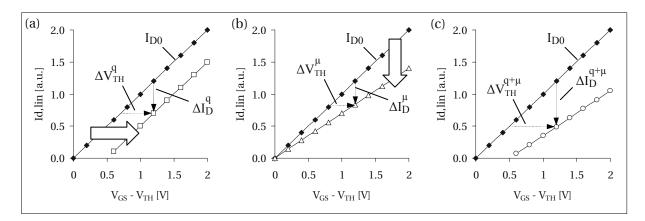

**Figure 2.1:** Schematic illustration of the individual components contributing to the threshold voltage shift depicted as a function of the gate bias overdrive. (a) Threshold voltage shift caused by a variation of the surface potential due to electrically active defect charges  $(\Delta V_{TH}^{q})$ ; (b) Spurious  $V_{TH}$  shift caused by a reduction in the channel transconductance due to mobility degradation  $(\Delta V_{TH}^{\mu})$ ; (c) resulting total  $V_{TH}$  shift caused by both components: mobility degradation and defect charges

#### 2.1.1 Influence of mobility degradation and defect charges on the total $V_{\rm TH}$ shift

As mobility and threshold voltage degrade upon the creation of various defects at the SiO<sub>2</sub>/Si interface and within the gate oxide during stress, the total  $V_{\text{TH}}$  shift calculated from  $\Delta I_{\text{D}}$  is affected by both components simultaneously, however, their relative contribution may change as a function of the gate voltage overdrive.

Defect charges modify the surface potential directly, thereby shifting the transfer curve with respect to the gate voltage axis (x-axis) ( $\Delta V_{TH}^{q}$ ). As a consequence, the drain current is degraded ( $\Delta I_{D}^{q}$ ) when measuring the same operating point again after stress. On the other hand, mobility degradation reduces the drain current directly due to a change in the channel resistance thereby shifting the transfer curve with respect to the drain current axis (y-axis). When converting the parasitic current reduction ( $\Delta I_{D}^{\mu}$ ) caused by the degradation of the channel resistance into an equivalent threshold voltage shift, it induces an extra  $V_{TH}$  component ( $\Delta V_{TH}^{\mu}$ ) superimposed to the 'real'  $V_{TH}$  shift caused by defect charges ( $\Delta V_{TH}^{q}$ ). The issue is discussed schematically in Fig. 2.1 where the influence of both components is illustrated separately and combined in the deep inversion regime of the transistor ( $|V_{GS}| \ge |V_{TH}|$ ).

The drain current values were calculated directly form Eq. 2.1 (neglecting for simplicity the curvature of the transfer curve ( $\Theta$ ) and the inversion carrier screening effect) and are plotted as a function of the gate bias overdrive. In Fig. 2.1 (a) – (c), the virgin drain current (labeled  $I_{D0}$ ; full diamonds) is depicted as a reference. The individually degraded drain currents are illustrated by open symbols. Fig. 2.1 (a) shows the defect charge induced  $V_{TH}$  shift component ( $\Delta V_{TH}^q$ ) as a function of the gate voltage overdrive. According to the considerably simplified drain current model described by Eq. 2.1, the stress induced shift of the transfer curve (in the triode region of the device) caused by defect charges is parallel making the reduction of the drain current ( $\Delta I_D^q$ ) independent of the gate voltage overdrive. Fig. 2.1 (b) illustrates the parasitic  $V_{TH}$  shift of the transfer curve ( $\Delta V_{TH}^{\mu}$ ) caused by a hypothetical 30% reduction of the channel mobility. Since mobility degradation generally implies a change in the

channel transconductance (slope of the transfer curve), the reduction of the drain current and hence the spurious  $V_{\text{TH}}$  shift ( $\Delta V_{\text{TH}}^{\mu}$ ) caused by surface state scattering increases linearily with the overdrive. A combination of both effects is illustrated in Fig. 2.1 (c), demostrating that the total  $V_{\text{TH}}$  shift ( $\Delta V_{\text{TH}}$ ) gained from the conversion of the total drain current degradation ( $\Delta I_{\text{D}}$ ) is generally a combination of a *parallel* shift due to the build up of defect charges and a *vertical* shift due to a change in the transconductance caused by enhanced scattering at charged defect centers:

$$\Delta V_{\rm TH} = \Delta V_{\rm TH}^{\rm q} + \Delta V_{\rm TH}^{\mu}.$$

(2.12)

The development of the total  $V_{\text{TH}}$  shift with the gate voltage overdrive can be estimated from Eq. 2.10 and Eq. 2.11 by considering the curvature of the transfer curve ( $\Theta$ ) and the scattering at charged defect centers located at the interface:

$$\Delta V_{\text{TH,lin}} = (V_{\text{GS}} - V_{\text{TH}})(1 + \Theta(V_{\text{GS}} - V_{\text{TH}}))\frac{\alpha \Delta N_{\text{it}}}{1 + \alpha N_{\text{it}}} + \Delta V_{\text{TH}}^{\text{q}}, \qquad (2.13)$$

$$\Delta V_{\rm TH,sat} = \frac{(V_{\rm GS} - V_{\rm TH})(1 + \Theta(V_{\rm GS} - V_{\rm TH}))}{2 + \Theta(V_{\rm GS} - V_{\rm TH})} \frac{\alpha \Delta N_{\rm it}}{1 + \alpha N_{\rm it}} + \Delta V_{\rm TH}^{\rm q}.$$

(2.14)

### **2.1.2** Spurious $V_{\text{TH}}$ shift due to mobility degradation ( $\Delta V_{\text{TH}}^{\mu}$ )

The first terms in Eq. 2.13 and Eq. 2.14 account for the spurious  $V_{\text{TH}}$  shifts in the linear and the saturation region of the device caused by mobility degradation. In general, the interface scattering parameter  $\alpha$  is not constant but depends on the gate bias overdrive due to the carrier screening effect [24–26]. As the density of inversion carriers increases when raising the gate voltage, they may crowd around charged point defects, thereby screening their Coulomb potential and reducing their scattering cross section. Experimental and theoretical investigations by [25, 26] revealed that the parameter  $\alpha$  decreases proportionally to the square root of the density of inversion layer carriers:

$$\alpha \propto \frac{1}{\sqrt{N_{\text{inv}}}} \Rightarrow \alpha \approx \frac{\alpha_0}{\sqrt{|V_{\text{OX}}|}} \approx \frac{\alpha_0}{\sqrt{|V_{\text{GS}} - \psi_{\text{S}} - \psi_{\text{P}} - V_{\text{FB}}|}} \approx \frac{\alpha_0}{\sqrt{|V_{\text{GS}} - V_{\text{TH}}|}}.$$

(2.15)

Considering the inversion carrier screening effect, the spurious  $V_{\text{TH}}$  shift in the linear and in the inversion regime of the device may be approximated as follows:

$$\Delta V_{\rm TH,lin}^{\mu} \approx -|V_{\rm GS} - V_{\rm TH}|^{1/2} \left(1 + \Theta(V_{\rm GS} - V_{\rm TH})\right) \frac{\alpha_0 \Delta N_{\rm it}}{1 + \alpha_0 N_{\rm it}},\tag{2.16}$$

$$\Delta V_{\rm TH,sat}^{\mu} \approx -\frac{|V_{\rm GS} - V_{\rm TH}|^{1/2} (1 + \Theta (V_{\rm GS} - V_{\rm TH}))}{2 + \Theta (V_{\rm GS} - V_{\rm TH})} \frac{\alpha_0 \Delta N_{\rm it}}{1 + \alpha_0 N_{\rm it}}.$$

(2.17)

The result demonstrates that the mobility induced shift of the threshold voltage  $(\Delta V_{\text{TH}}^{\mu})$  is proportional to the square root of the gate bias overdrive, the curvature of the transfer curve ( $\Theta$ ) and the increase of the interface defect density ( $\Delta N_{\text{it}}$ ). As already pointed out previously, the relative contribution  $\Delta V_{\text{TH}}^{\mu}$  is found to be increasingly smaller (more than a factor 2) when measuring in the saturation region of the device.

In order to estimate  $\Delta V_{TH}^{\mu}$  experimentally, we may express the interface scattering term in Eq. 2.16 and Eq. 2.17 by the shift of the transconductance recorded after electrical stress.

The transconductances in the linear and in the saturation regime representing the slopes of the transfer curve can be calculated by differentiating Eq. 2.1 and Eq. 2.2 by the applied gate potential. The derivations are performed in the appendix (9.1):

$$g_{m,lin} \approx \frac{I_{D,lin}}{V_{GS} - V_{TH}} \left( \frac{1}{1 + \Theta(V_{GS} - V_{TH})} + \frac{\alpha N_{it}}{2(1 + \alpha N_{it})} \right),$$

(2.18)

$$g_{\rm m,sat} \approx \frac{I_{\rm D,sat}}{V_{\rm GS} - V_{\rm TH}} \left( \frac{2 + \Theta(V_{\rm GS} - V_{\rm TH})}{1 + \Theta(V_{\rm GS} - V_{\rm TH})} + \frac{\alpha N_{\rm it}}{2(1 + \alpha N_{\rm it})} \right).$$

(2.19)

The first terms in Eq. 2.18 and Eq. 2.19 represent the reduction of the transconductance due to field dependent scattering while the second terms consider inversion carrier screening. In particular, ons finds that the relative variations of the transconductances in the linear and in the saturation regime are directly related to the interface scattering factors in Eq. 2.16 and Eq. 2.17. The derivations are performed in the appendix (9.2). In the linear regime, we may express the interface scattering factor by the relative change in the maximum transconductance:

$$\frac{\Delta g_{m,\text{lin}}^{\text{max}}}{g_{m,\text{lin}}^{\text{max}}} \approx -\frac{\alpha_0 \Delta N_{\text{it}}}{1 + \alpha_0 N_{\text{it}}}.$$

(2.20)

In the saturation regime, the deviation cannot be achieved in a straight-forward manner since the saturation transconductance has no maximum and therefore provides no characteristic operating point to refer on. In the vicinity of the threshold voltage, the variation of the transconductance may be approximated as follows:

$$\frac{\Delta g_{\mathrm{m,sat}}^{\mathrm{V}_{\mathrm{TH}}}}{g_{\mathrm{m,sat}}^{\mathrm{V}_{\mathrm{TH}}}} \approx -\frac{\alpha_0 \Delta N_{\mathrm{it}}}{1+\alpha_0 N_{\mathrm{it}}} - \frac{\Delta V_{\mathrm{TH}}^{\mathrm{q}}}{V_{\mathrm{GS}} - V_{\mathrm{TH}}}.$$

(2.21)

For gate voltages far away from the threshold voltage of the device, the equations proposed above are not valid anymore and may over- or underestimate the slope of the mobility induced threshold voltage shift. This is because the development of the transconductance is expected to change considerably due to field dependent scattering and inversion layer screening. By substituting the interface scattering factors in Eq. 2.16 and Eq. 2.17 by the transconductance related expressions derived in Eq. 2.20 and Eq. 2.21, we may express the spurious  $V_{\text{TH}}$  shifts in the linear in in the saturation regime by experimentally measurable quantities.

In the linear regime, the mobility induced  $\Delta V^{\mu}_{\mathrm{TH}}$  shift yields

$$\Delta V_{\rm TH,lin}^{\mu} \approx |V_{\rm GS} - V_{\rm TH}|^{1/2} \left(1 + \Theta(V_{\rm GS} - V_{\rm TH})\right) \left(\frac{\Delta g_{\rm m,lin}^{\rm max}}{g_{\rm m,lin}^{\rm max}}\right).$$

(2.22)

In the saturation regime, the  $\Delta V_{\rm TH}^{\mu}$  shift may be approximated as

$$\Delta V_{\rm TH,sat}^{\mu} \approx \frac{|V_{\rm GS} - V_{\rm TH}|^{1/2} \left(1 + \Theta(V_{\rm GS} - V_{\rm TH})\right)}{2 + \Theta(V_{\rm GS} - V_{\rm TH})} \left(\frac{\Delta g_{\rm m,sat}^{\rm v_{\rm TH}}}{g_{\rm m,sat}^{\rm v_{\rm TH}}} + \frac{\Delta V_{\rm TH}^{\rm q}}{V_{\rm GS} - V_{\rm TH}}\right),\tag{2.23}$$

demonstrating that  $\Delta V_{\text{TH}}^{\mu}$  grows proportional to the relative change of the transconductance which is originated in enhanced Coulomb scattering at stress induced interface charges. As a consequence of inversion carrier screening and field dependent scattering, the mobility induced  $V_{\text{TH}}$  shift does not actually increase linearly with the gate voltage overdrive as suggested in the simplest approximation illustrated in Fig. 2.1.

### **2.1.3** $V_{\text{TH}}$ shift due to defect charges ( $\Delta V_{\text{TH}}^{\text{q}}$ )

Once a defect is created during NBTS, it may exchange carriers with the silicon substrate thereby being charged either positively or negatively depending on the particular energy level of the defect and on the carrier situation at the SiO<sub>2</sub>/Si interface. Statistical thermodynamics stipulates that at absolute zero the quantum energy of the highest occupied quantum state in a system of fermions is defined by the Fermi energy. At finite temperatures the concept of the Fermi energy is replaced by the Fermi level (electro-chemical potential) since the separation between occupied and unoccupied states is not infinitely sharp anymore but has a half-width of approximately  $2k_{\rm B}T$ . In the operating temperature range of silicon devices this broadening is small ( $\approx 0.08 \,\mathrm{eV}$  at 200°C) so that we may generally consider defects above the Fermi level as unoccupied while traps below the Fermi level are considered as occupied.

The net charge state of a defect level generally depends on the number of electrons trapped. In principle, every defect can be amphoteric which means that it has a donor- and an acceptor-level, the first describing the defect in the *positive* charge state, where it may become neutralized upon the capture of one electron, the latter describing the defect in the *neutral* charge state, where it may become negatively charged upon the capture of an additional electron. Capture of an electron is naturally accompanied by a level shift because a higher energetic state is required. The amount of level shift depends on the local bonding environment of the defect within the solid and decides whether a defect state actually appears only in one or in in both (donor and acceptor) configurations during a particular experiment. Due to localized inhomogeneities in the lattice stress involving slight variations in the individual bonding strengths, defects close to the interface usually do not have a single energy level but a distribution of states described by a density of states (DOS) profile. The boundary between the highest donor-like state and the lowest acceptor-like state in a network of defects of the same type is called the amphoteric transition level ( $E_{amph}$ ). In thermal equilibrium, the total defect charge may be approximated as

$$Q_{\text{defect}} = q \int_{E_{\text{F}}}^{E_{\text{amph}}} D_{\text{defect}}(E) \, dE = \pm q \overline{D_{\text{defect}}} \Delta E_{\text{Q}}, \qquad (2.24)$$

where  $\Delta E_Q$  is the Fermi level dependent energy range of charged defects in thermal equilibrium:

$$\Delta E_{\rm Q} = \left| E_{\rm amph} - E_{\rm F} \right|. \tag{2.25}$$

The integral in Eq. 2.24 is positive (resulting in a net positive defect charge) when the Fermi level is below  $E_{amph}$ , whereas the net defect charge is negative when the Fermi level lies above  $E_{amph}$ . It has to be mentioned that a certain time is required to restore thermal equilibrium between all kinds of defect species and the silicon substrate. The trap level only gives the equilibrium occupancy but does not say anything about the time constant. In particular, deep traps located in the bulk of the oxide having energy levels far away from the silicon bandgap, provide large carrier exchange time constants and small capture cross sections so that it may take a long time for them to align with the Fermi level. In particular, when taking inelastic carrier trapping/detrapping into account, some defects located energetically above the Fermi level may also have a finite chance to exchange carriers with the silicon substrate leading to a large variety of time constants. The dynamics of trap creation and annealing will be discussed in detail in Chapter 3.

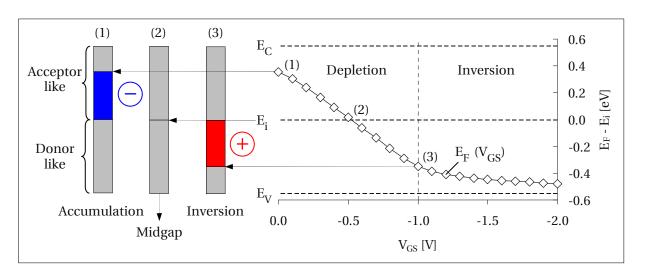

As opposed to deep traps in the bulk of the gate oxide (slow states), defects being located energetically within the silicon bandgap and spatially close to the SiO<sub>2</sub>/Si interface, exchange carriers very fast with the silicon substrate allowing to restore thermal equilibrium within a very short interval of time. Hence, the energy level of the highest occupied trap level may follow the development of the Fermi level (i.e. during a gate bias sweep) almost instantaneously. Interface states (P<sub>b</sub> centers) have such attributes, in particular, they provide a wide range of energy levels within the silicon bandgap having their amphoteric transition level around midgap ( $E_{amph} \approx E_i$ ). Following Eq. 2.24, this implies that their net charge contribution is negative when the Fermi level is located in the upper half of the silicon bandgap, zero at midgap and positive when the Fermi level lies in the lower half of the silicon bandgap, cf. Fig. 2.2. In the subthreshold region of the device, there is an almost linear relationship between the Fermi level and the gate voltage allowing defects to trap and emit carriers very efficiently. Hence, during a gate bias ramp between accumulation and inversion interface states change their net charge contribution continuously as described by the standard Shockley Read Hall (SRH) model [28]. The gate bias dependent Fermi level depicted in Fig. 2.2 was simulated numerically for a PMOS device (SM6P/30/H1) at room temperature [29].

At 0.0V, when the device is turned off, the Fermi level is pinned close to the conduction band edge  $E_{\rm C}$ . Consequently, acceptor-like interface states located between midgap ( $E_{\rm i}$ ) and  $E_{\rm F}$  are occupied by two electrons resulting in a net negative defect charge (1). Approaching midgap (-0.5V), previously negatively charged traps emit one of their two electrons resulting in an overall neutral interface at  $E_{\rm F} = E_{\rm i}$  (2). As the gate bias drives the Fermi level deeper toward inversion, donor-like defect levels located between  $E_{\rm i}$  and  $E_{\rm F}$  emit an additional electron resulting in a net positive defect charge at the threshold voltage of the device (-1.0V) (3). When driving the gate bias even deeper toward inversion (-2.0V), the Fermi level position does not change significantly anymore. Hence, the net positive interface charge can be considered as virtually constant once the gate bias has exceeded the threshold voltage of the device.

Except for classical interface states (SRH), it has to be mentioned that there might exist also a specific type of oxide traps (E' centers, cf. Section 4.3) located close to but not directly at the interface which may have similar carrier exchanging characteristics. However, as opposed to interface states, their charging-recharging time constants are probably larger since a thermodynamic barrier has to be overcome in order to communicate electrically with the silicon substrate.

While the energetic position of an individual trap type determines its equilibrium charge state, its spatial location within the gate oxide governs its relative impact on the observed threshold voltage shift ( $\Delta V_{TH}^{q}$ ). On a PMOS device, one usually observes a negative  $V_{TH}$  shift after NBTS, indicating the creation of predominantly donor-like defects which become positively charged during stress and may keep their charge state for a certain time after termination of the stress. In the case of a PMOS transistor, termination of the stress means switching the gate bias from a negative stress level to a considerably lower but also negative threshold voltage. Consequently, when recording the degraded drain current after stress, most defects remain positively charged since the Fermi level remains pinned close to the valence band edge (cf. Fig. 2.2).

Assuming a spatial distribution of positive defects  $\rho(x)$ , with x being the distance from the gate poly interface inside the SiO<sub>2</sub> gate oxide, the corresponding defect charge dependent  $V_{\text{TH}}$  shift ( $\Delta V_{\text{TH}}^{\text{q}}$ ) is given by Gauss's law:

$$\Delta V_{\rm TH}^{\rm q} = -\frac{1}{C_{\rm OX}} \frac{1}{t_{\rm OX}} \int_0^{t_{\rm OX}} x \rho(x) \, \mathrm{d}x, \qquad (2.26)$$

**Figure 2.2:** Dependence of the Fermi level on the gate bias in the subthreshold and inversion regime simulated numerically for a PMOS device (SM6P/30/H1) at room temperature. Within the depletion region of the device, their is a linear relationship between the gate bias and the Fermi level. In the inversion region, the Fermi level varies only slightly. On the left hand side of the figure the trap occupancy and the net interface trap charge is illustrated for three selected bias voltages. In accumulation (1) the net interface charge is negative, at midgap (2) zero and in inversion (3) positive.

where  $C_{\text{OX}}$  is the area related oxide capacitance:

$$C_{\rm OX} = \frac{\epsilon_0 \epsilon_{\rm OX}}{t_{\rm OX}} \approx \frac{3.45310^{-13}}{t_{\rm OX} [\rm cm]} [\rm F/cm].$$

(2.27)

Note that Eq. 2.27 is only accurate for thick oxide technologies ( $t_{OX} > 10$  nm), where the quantummechanical confinement of the inversion charge layer and the poly depletion may be neglected.

Assuming further all defects to be concentrated at the SiO<sub>2</sub>/Si interface ( $\rho(x) = q\Delta N_{it}\delta(x - t_{OX})$ ), the integral in Eq. 2.26 can be easily solved, giving the following simplified expression for the defect charge induced  $V_{TH}$  shift:

$$\Delta V_{\rm TH}^{\rm q} = -\frac{q\Delta N_{\rm it}}{C_{\rm OX}} = -\frac{q\Delta N_{\rm it}}{\epsilon_0 \epsilon_{\rm OX}} t_{\rm OX}.$$

(2.28)

The result demonstrates a linear correlation between the observed  $\Delta V_{\text{TH}}$  shift and the oxide thickness. This is an important (albeit trivial) finding, in particular, when comparing  $\Delta V_{\text{TH}}$  shifts of devices having different oxide thicknesses [15].

#### 2.1.4 Relevance of defect charge induced V<sub>TH</sub> shift and mobility degradation

Having calculated in Eq. 2.28 the real threshold voltage shift caused by electrically active defect charges  $(\Delta V_{\rm TH}^{\rm q})$  and in Eq. 2.16 and Eq. 2.17 the spurious threshold voltage shifts caused by field dependent mobility degradation  $(\Delta V_{\rm TH}^{\mu})$ , we may estimate the relative contribution of  $\Delta V_{\rm TH}^{\rm q}$  as a function of the gate voltage overdrive by assuming all charged defects to be located at the interface:

$$\frac{\Delta V_{\rm TH}^{\rm q}}{\Delta V_{\rm TH,lin}} = \left(1 + |V_{\rm GS} - V_{\rm TH}|^{1/2} \left(1 + \Theta(V_{\rm GS} - V_{\rm TH})\right) \frac{\alpha_0}{1 + \alpha_0 N_{\rm it}} \frac{C_{\rm OX}}{\rm q}\right)^{-1},\tag{2.29}$$

$$\frac{\Delta V_{\rm TH}^{\rm q}}{\Delta V_{\rm TH,sat}} = \left(1 + \frac{|V_{\rm GS} - V_{\rm TH}|^{1/2} \left(1 + \Theta(V_{\rm GS} - V_{\rm TH})\right)}{2 + \Theta(V_{\rm GS} - V_{\rm TH})} \frac{\alpha_0}{1 + \alpha_0 N_{\rm it}} \frac{C_{\rm OX}}{q}\right)^{-1},\tag{2.30}$$

indicating that the  $V_{\text{TH}}$  shift generated by defect charges is dominant when the capacitance is low (thick oxide devices), the overdrive is low and the overall interface state density is high. Considering a standard high voltage (HV) PMOS device with a 30 nm thick gate oxide, the curvature of the transfer curve ( $\Theta$ ) being -0.13V<sup>-1</sup>, the interface density being 10<sup>10</sup> cm<sup>-2</sup>, measured with an overdrive of -1.0V ( $\alpha_0 \approx 10^{-13} \text{ cm}^2$  [24]), the relative contribution of  $\Delta V_{\text{TH}}^{\text{q}}$  to the total  $\Delta V_{\text{TH}}$  shift amount to approximately 92% in the linear region and 96% in the saturation region of the device which is quite large in comparison to the small remaining contribution of  $\Delta V_{\text{TH}}^{\mu}$ . In particular, in the presence of additional defect charge within the oxide which does not affect the mobility but increases the parallel  $\Delta V_{\text{TH}}$  shift (i.e. charge centers located in the bulk of the oxide), the contribution of  $\Delta V_{\text{TH}}^{\mu}$  may become almost negligible. However, as the oxide thickness shrinks or the overdrive increases (i.e. during on-the-fly (OTF) measurements, cf. Section 3.1) the mobility contribution can exceed up to 40% of the total  $\Delta V_{\text{TH}}$  shift [21] representing then an important component which has to be considered.

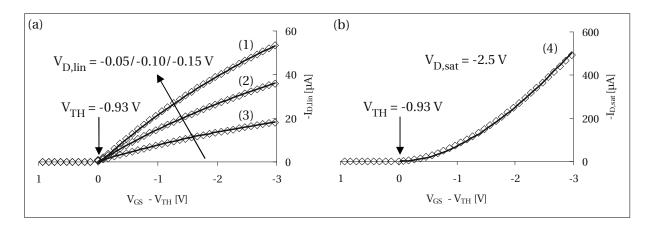

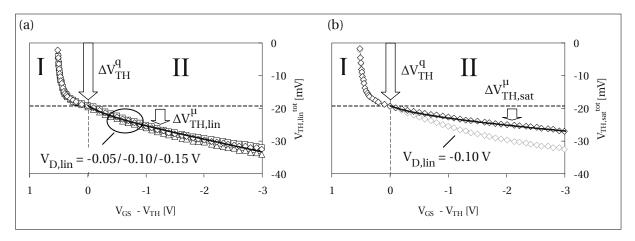

**Figure 2.3:** Virgin transfer curves measured at a temperature of 80°C in the linear (a) and in the saturation (b) drain current regime of a PMOS device (SM5P/30/H1) using drain biases of -0.05V (1), -0.10V (2), -0.15V (3) and -2.5V (4). The data points are depicted by open diamonds, the fits according to Eq. 2.1 and Eq. 2.2 are illustrated by thick solid lines. From parameter fitting a virgin threshold voltage of -0.93V and a  $\Theta$  of -0.13V<sup>-1</sup> was extracted.

#### 2.1.5 Case study

In order to demonstrate the impact of mobility degradation and defect charges on the drain current degradation and the  $V_{\text{TH}}$  shift, a PMOS device (SM5P/30/H1) was stressed at a temperature of 80°C under an electric field of approximately -6.0MV/cm for several thousand seconds. Before stress, virgin transfer curves were recorded between 0.0V and -4.0V (step size 0.01V) using constant drain biases of -0.05V (1), -0.10V (2) and -0.15V (3) in the linear regime ( $I_{\text{D,lin}}$ ) and -2.5V (4) in the saturation regime of the device ( $I_{\text{D,sat}}$ ). The three transfer curves measured in the linear regime of the device is depicted in Fig. 2.3 (a), the transfer curve recorded in the saturation regime of the device is depicted in Fig. 2.3 (b). From the measured data points (open symbols), the virgin threshold voltage  $V_{\text{TH}}$  and the vertical field dependent scattering factor  $\Theta$  is obtained by fitting the drain currents as a function of the gate bias overdrive according to Eq. 2.1 and Eq. 2.2. The fits are illustrated by thick solid lines yielding a threshold voltage of -0.93V and a  $\Theta$  of -0.13V<sup>-1</sup>.

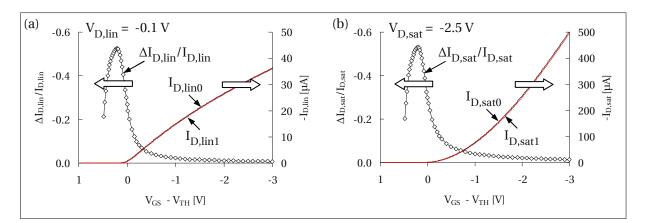

Having determined the virgin threshold voltage and the curvature parameter  $\Theta$ , we subject the device to NBTS. After stress, full transfer curves were recorded again serially in the linear and in the saturation regime of the device by ramping the gate voltage from accumulation toward inversion. It has to be mentioned that there were several seconds of delay following the termination of stress and the moment when the second set of transfer curves was finally recorded. Hence, some recovery has occurred during this floating period and during the measurement time itself. The recovery dynamics are going to be discussed in Chapter 3. In Fig. 2.4, the linear (a) and the saturation (b) drain currents recorded before (labeled '0') and after NBTI stress (labeled '1') at a constant drain bias of -0.1 V (linear regime) and -2.5V (saturation regime) are illustrated as a function of the gate bias overdrive. The degraded transfer curves measured post stress are shifted slightly toward a more negative gate voltage indicating the build-up of positive charge.

Furthermore, the relative shift of the drain current is depicted as well in Fig. 2.4 (a) and (b) demonstrating the parameter degradation more clearly. As predicted by Eq. 2.10 and Eq. 2.11 ( $|V_{GS}| > |V_{TH}|$ ), the relative variation of the drain current decreases gradually toward deeper inversion.

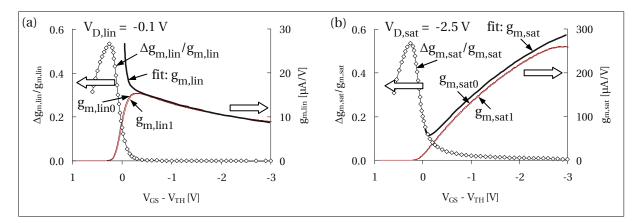

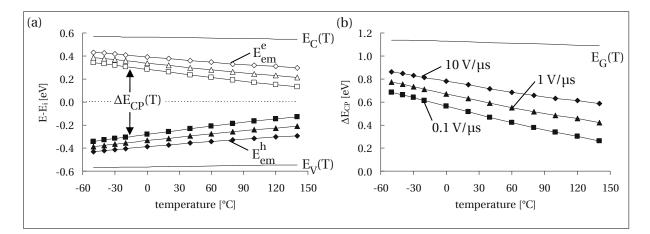

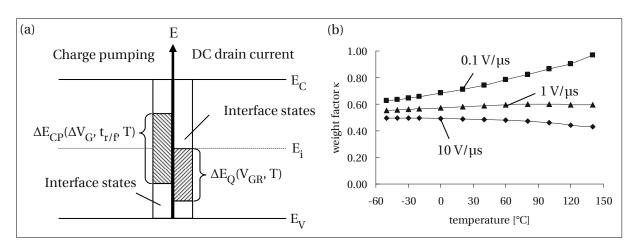

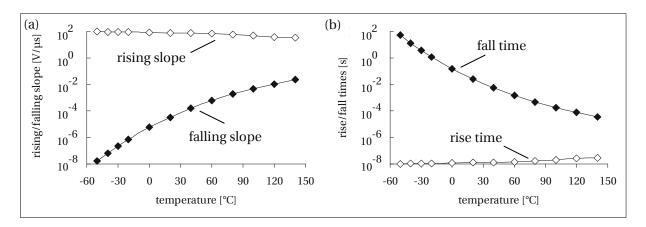

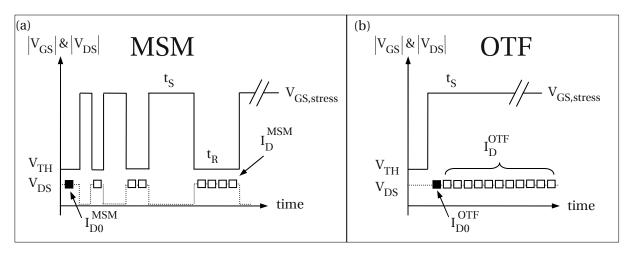

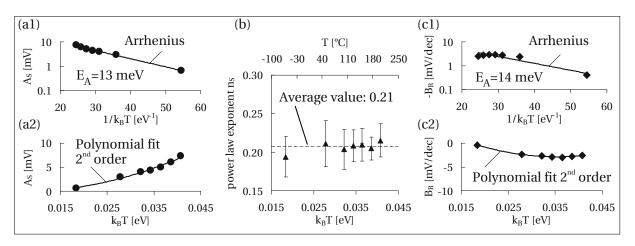

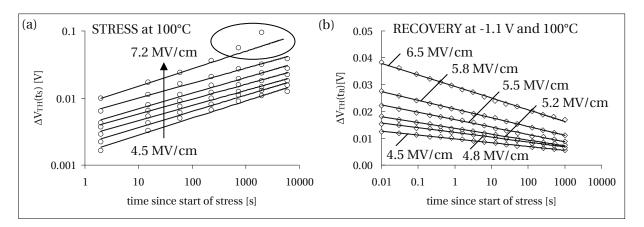

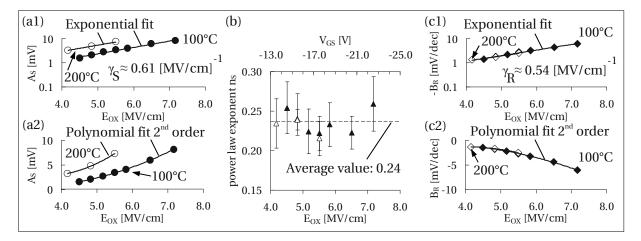

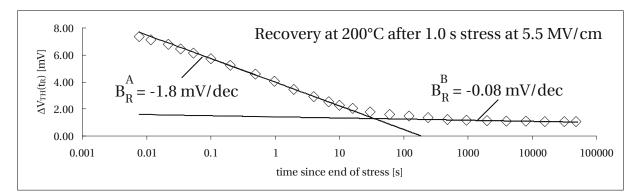

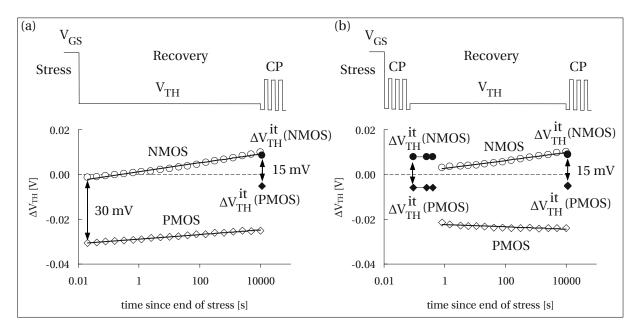

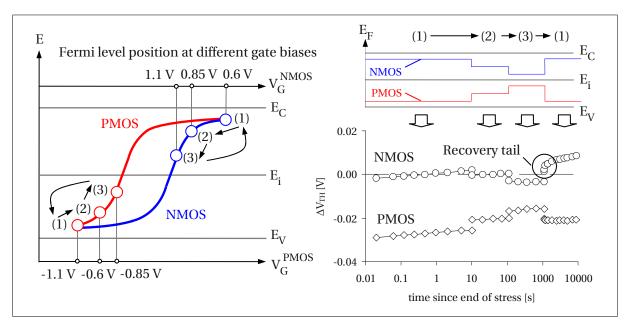

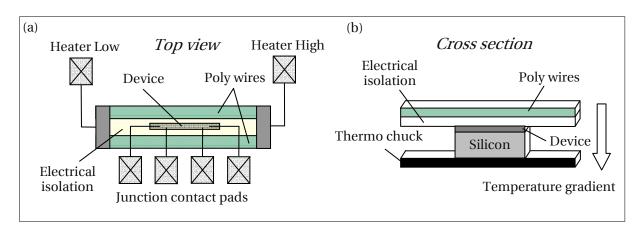

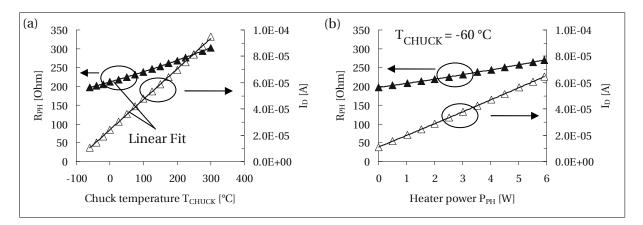

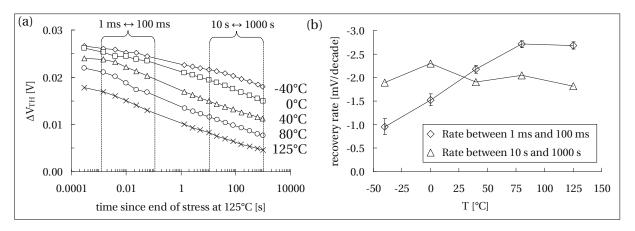

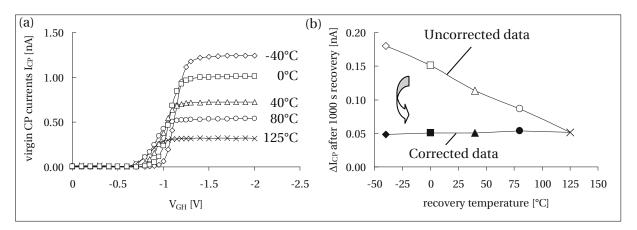

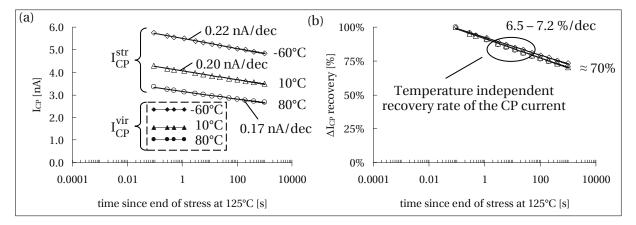

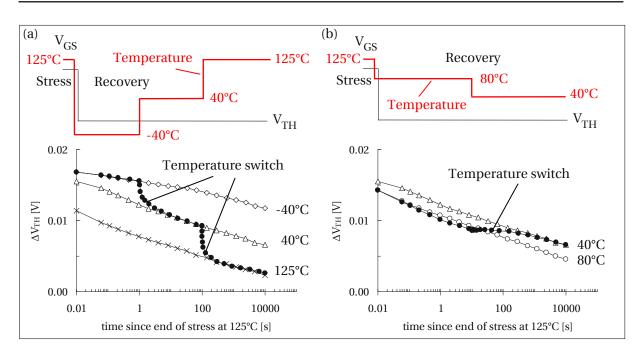

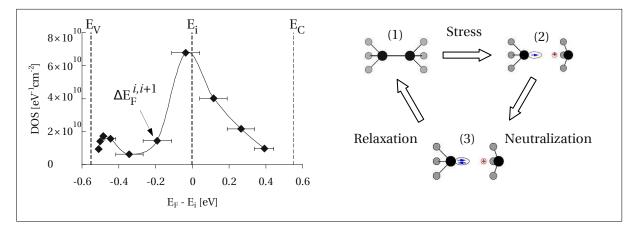

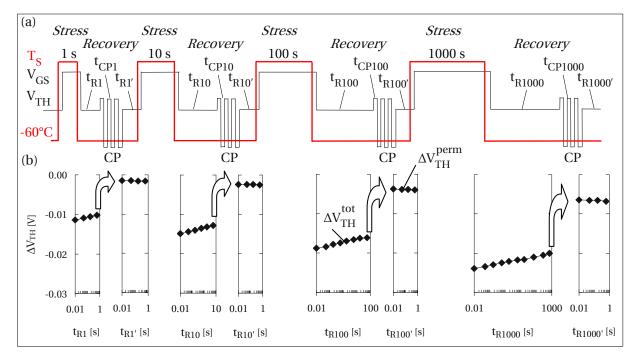

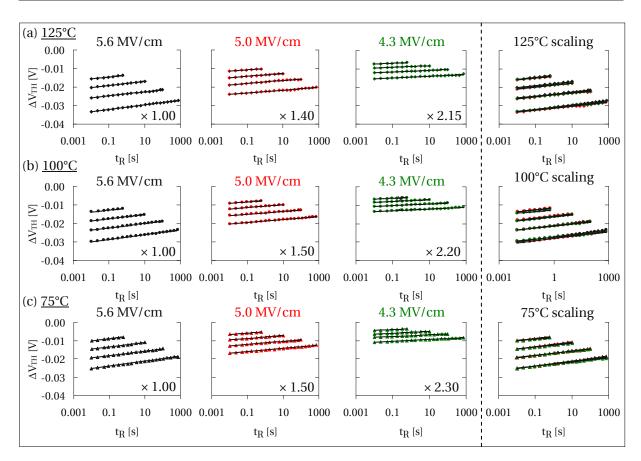

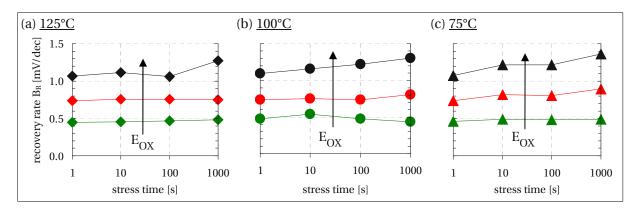

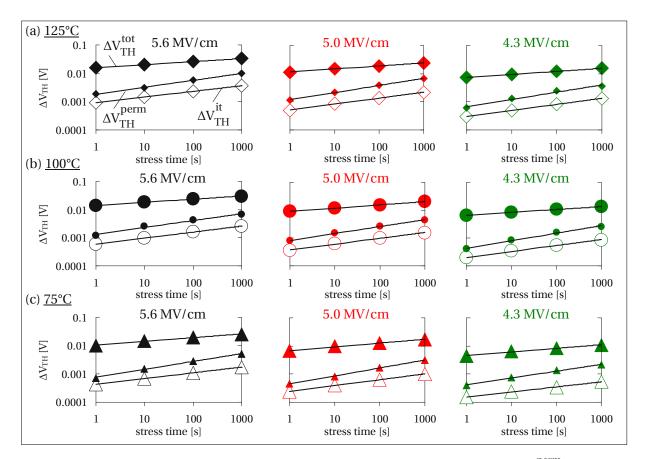

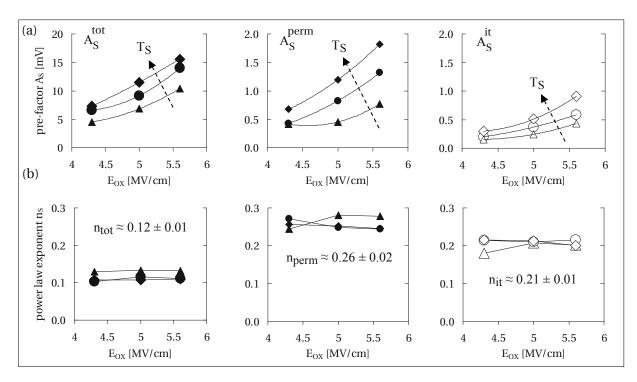

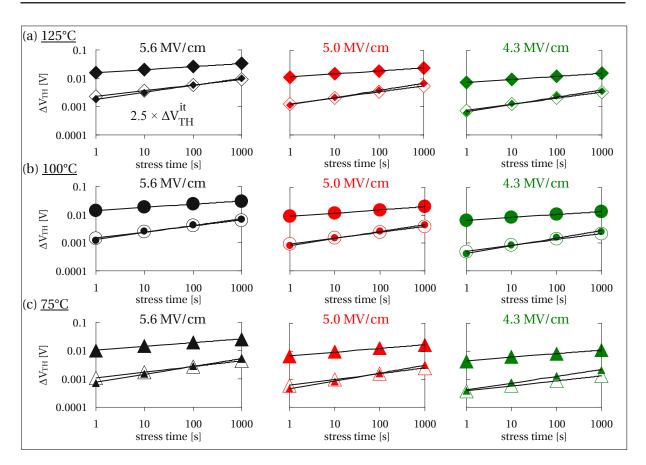

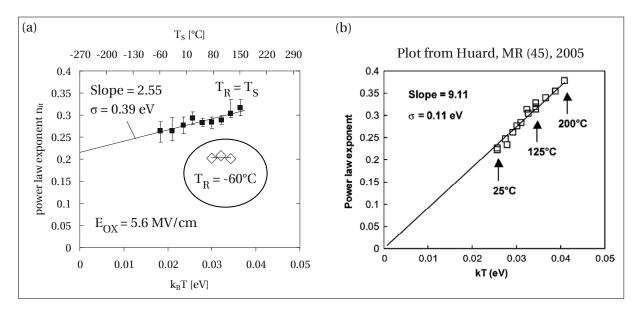

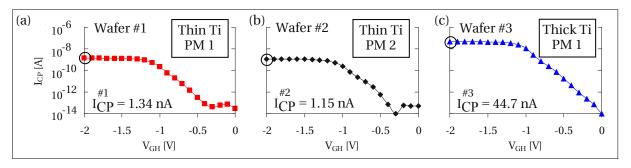

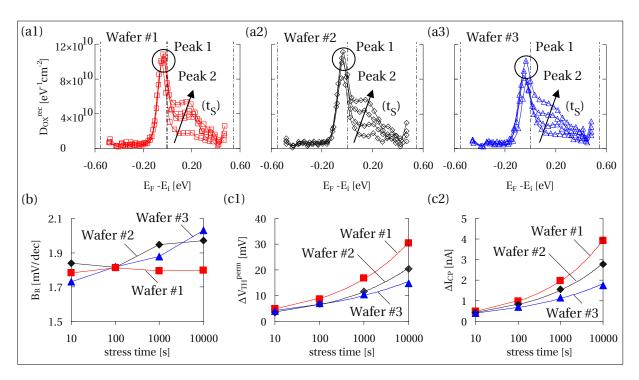

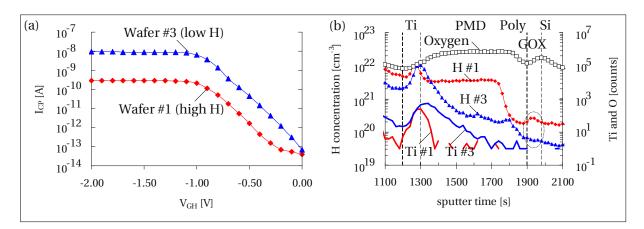

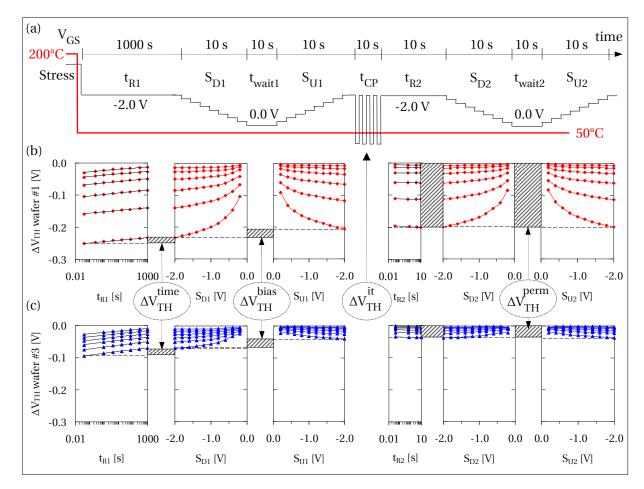

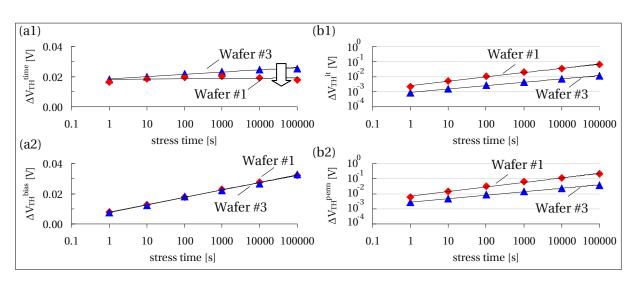

In Fig. 2.5, the transconductances in the linear (a) and in the saturation (b) regime recorded before (labeled '0') and after NBTI stress (labeled '1') are illustrated as a function of the gate bias overdrive. The thick solid line in (a) and (b) is a fit according to Eq. 2.18 and Eq. 2.19 which reflects the measured gradual decrease of the transconductance in the linear regime (a) and the convex curvature of the transconductance in the saturation regime (b) caused by vertical field dependent scattering ( $\Theta$ ). Note that inversion layer screening has been neglected in the calculation of the fit. The relative degradation of the transconductance is also depicted in Fig. 2.5 (a) and (b), demonstrating mobility degradation and inversion carrier screening. Due to the superimposed parallel shift of the threshold voltage caused by defect charges, the relative variation of the transconductance is peaked for  $(|V_{GS}| \rightarrow |V_{TH}|)$ and decreases in the deep inversion regime due to inversion layer screening. In the linear regime (a), the relative change of the transconductance at the gate voltage at which the transconductance reaches a maximum was found to be  $6.2 \times 10^{-3}$ . This is an important value since it can be used to determine the slope of the mobility induced V<sub>TH</sub> shift, cf. Eq. 2.22. In the saturation regime (b), a larger relative change of the transconductance is measured at the same gate voltage due to the parasitic influence of  $\Delta V_{\text{TH}}^{\text{q}}$ , cf. Eq. 2.23. When correcting this influence, a value of 8.0×10<sup>-3</sup> is obtained which is similar to the one extracted in the linear regime  $(6.2 \times 10^{-3})$ .