TECHNISCHE UNIVERSITÄT WIEN Vienna University of Technology

## DISSERTATION

## **On Enhanced Clock Synchronization Performance Through Dedicated Ethernet Hardware Support**

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

Ao. Univ. Prof. Dipl.-Ing. Dr. Wolfgang Kastner Institut für Rechnergestützte Automation, Arbeitsbereich Automatisierungssysteme und

Prof. Dr. Francisco Vasques Departement of Mechanical Engineering, University of Porto, Portugal

eingereicht an der Technischen Universität Wien Fakultät für Informatik

durchgeführt am Institut für Integrierte Sensorsysteme der Österreichische Akademie der Wissenschaften unter der Leitung von Dipl.-Ing. Dr. Thilo Sauter

von

Dipl.-Ing. Patrick Loschmidt Wienergasse 114-116/2/5 2380 Perchtoldsdorf Matr.-Nr. 9526652

Wien, im Dezember 2010

Patrick Loschmidt

# Contents

| 1 | Introduction 8 |                                                                |     |  |    |  |

|---|----------------|----------------------------------------------------------------|-----|--|----|--|

|   | 1.1            | The Necessity of Clock Synchronization in Distributed Systems  |     |  | 8  |  |

|   | 1.2            | Basic Terms                                                    |     |  | 12 |  |

|   | 1.3            | Clock Synchronization in Packet-Oriented Networks              |     |  | 14 |  |

|   |                | 1.3.1 Transmission Delay Boundaries                            |     |  | 15 |  |

|   |                | 1.3.2 Packet Relaying Effects                                  |     |  | 16 |  |

|   | 1.4            | Hardware Support for High-Precision Clock Synchronization      |     |  | 17 |  |

|   |                | 1.4.1 Required Elements                                        |     |  |    |  |

|   |                | 1.4.2 $$ Transfer of Timestamps and the OSI Reference Model $$ |     |  | 21 |  |

|   | 1.5            | Contribution of the Thesis                                     | ••• |  | 23 |  |

| 2 | Mot            | tivation of the Problem                                        |     |  | 25 |  |

|   | 2.1            | Remote Metering using Power Line                               |     |  | 25 |  |

|   |                | 2.1.1 Access Network                                           |     |  |    |  |

|   |                | 2.1.2 Power Line Network                                       |     |  | 27 |  |

|   | 2.2            | Wireless Position Determination                                |     |  | 28 |  |

|   |                | 2.2.1 Method for Localisation                                  |     |  | 29 |  |

|   |                | 2.2.2 Implementation Issues                                    |     |  | 31 |  |

|   | 2.3            | Control System for Particle Accelerators                       |     |  |    |  |

|   |                | 2.3.1 White Rabbit Communication Infrastructure                | ••• |  | 34 |  |

| 3 | Stat           | te of the Art and Related Work                                 |     |  | 41 |  |

|   | 3.1            | Synchronous Network Approaches                                 |     |  | 42 |  |

|   |                | 3.1.1 Synchronous Ethernet                                     |     |  |    |  |

|   |                | 3.1.2 Delay Compensation Techniques                            |     |  |    |  |

|   | 3.2            | Protocols                                                      |     |  |    |  |

|   |                | 3.2.1 Network Time Protocol (NTP)                              |     |  |    |  |

|   |                | 3.2.2 IEEE 1588                                                |     |  | 51 |  |

|   | 3.3            | Real-Time Networks                                             |     |  | 56 |  |

|   |                | 3.3.1 PROFINET                                                 |     |  | 56 |  |

|   |                | 3.3.2 TTEthernet                                               |     |  |    |  |

|   |                | 3.3.3 EtherCAT                                                 |     |  |    |  |

|   |                | 3.3.4 Ethernet POWERLINK                                       |     |  | 60 |  |

|   |                | 3.3.5 SERCOS-III                                               |     |  | 61 |  |

|   |                | 3.3.6 LAN eXtensions for Instrumentation (LXI)                 |     |  | 62 |  |

|   | 3.4  | Hardware Elements                                                                                                                                                        |  |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   |      | 3.4.1 National Instruments Synchronization Modules                                                                                                                       |  |

|   |      | 3.4.2 National Semiconductor PHY                                                                                                                                         |  |

|   |      | 3.4.3 Intel Gigabit Ethernet Controller                                                                                                                                  |  |

|   | 3.5  | Implications                                                                                                                                                             |  |

| 4 | Svet | em Characterisation 66                                                                                                                                                   |  |

| - | 4.1  | System Immanent Jitter Sources   66                                                                                                                                      |  |

|   | 4.2  | Oscillators                                                                                                                                                              |  |

|   | 1.2  | 4.2.1 Frequency Domain Characterisation                                                                                                                                  |  |

|   |      | 4.2.2 Time Domain Characterisation                                                                                                                                       |  |

|   | 4.3  | Ethernet Transmission Standards                                                                                                                                          |  |

|   | 1.0  | 4.3.1 $10 \text{ Mbit/s Ethernet} (10 \text{ Base-T}) \dots \dots$ |  |

|   |      | 4.3.2 100 Mbit/s Ethernet (100 Base-T)                                                                                                                                   |  |

|   |      | 4.3.3 1 Gbit/s Ethernet (1000 Base-T)                                                                                                                                    |  |

|   | 4.4  | Prerequisites for Hardware Support                                                                                                                                       |  |

|   | 1.1  | 4.4.1 Media Dependency and Event Access                                                                                                                                  |  |

|   |      | 4.4.2 Timestamp Transportation Issues                                                                                                                                    |  |

|   |      | 4.4.3 System Clock Structure                                                                                                                                             |  |

| _ |      |                                                                                                                                                                          |  |

| 5 |      | uation Architecture for High-Performance Synchronization 86                                                                                                              |  |

|   | 5.1  | Applying System Requirements                                                                                                                                             |  |

|   |      | 5.1.1 Clock Resolution                                                                                                                                                   |  |

|   |      | 5.1.2 Performance $\ldots$ 88                                                                                                                                            |  |

|   | 5.0  | 5.1.3 Software / Hardware Partitioning                                                                                                                                   |  |

|   | 5.2  | Basic Prototype and Proof of Concept                                                                                                                                     |  |

|   |      | 5.2.1 Timestamp FIFO                                                                                                                                                     |  |

|   |      | 5.2.2 Accuracy Counters and Amortisation                                                                                                                                 |  |

|   |      | 5.2.3 Event Timestamp Registers                                                                                                                                          |  |

|   |      | 5.2.4 Trigger Functionality $\dots \dots \dots$                          |  |

|   | ۳ ۵  | 5.2.5 AHB Register Interface                                                                                                                                             |  |

|   | 5.3  | Event-Based, High-Accuracy Cell                                                                                                                                          |  |

|   |      | 5.3.1 Prescaler $\dots$ 98                                                                                                                                               |  |

|   |      | 5.3.2 Adder-Based Clock Enhancements                                                                                                                                     |  |

|   | F 4  | 5.3.3 Tick-Based Architecture $\dots \dots \dots$                        |  |

|   | 5.4  | Media Independent Interface Scanner                                                                                                                                      |  |

|   |      | 5.4.1 Functionality $\dots \dots \dots$                                  |  |

|   |      | 5.4.2 Precision $\dots \dots \dots$                                      |  |

|   |      | 5.4.3 One-Step Clock                                                                                                                                                     |  |

| 6 | Syn  | hronization System 111                                                                                                                                                   |  |

|   | 6.1  | Hardware                                                                                                                                                                 |  |

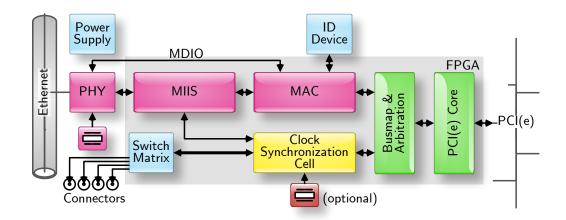

|   |      | 6.1.1 Network Interface Card $\ldots$                                                                                                                                    |  |

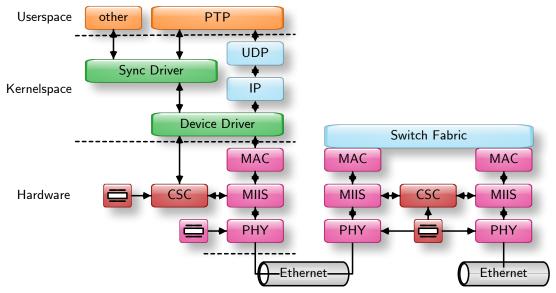

|   |      | 6.1.2 Time-Aware Switch                                                                                                                                                  |  |

|    |       | 6.1.3   | Support in Embedded Processors                         | . 118 |

|----|-------|---------|--------------------------------------------------------|-------|

|    | 6.2   | Softwa  | are                                                    | . 120 |

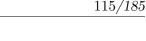

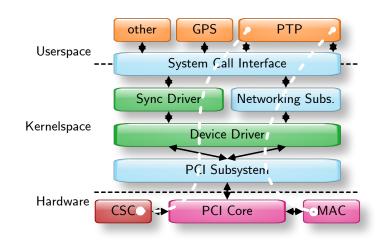

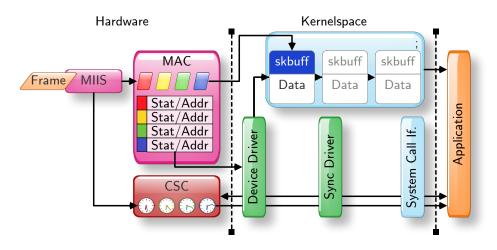

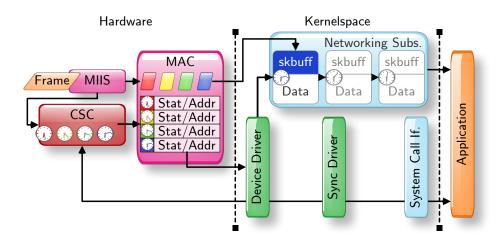

|    |       | 6.2.1   | Driver and Software Structure                          | . 121 |

|    |       | 6.2.2   | NTP Daemon Reference Clock Driver                      | . 129 |

|    |       | 6.2.3   | PTP Stack                                              | . 131 |

|    |       | 6.2.4   | GPS Stack                                              | . 136 |

| 7  | Vali  | dation  |                                                        | 138   |

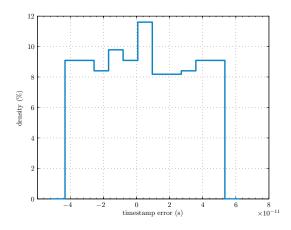

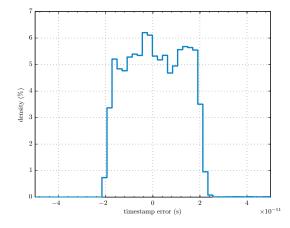

|    | 7.1   | Hardv   | vare Measurements                                      | . 138 |

|    |       | 7.1.1   | Applicability of Phase Estimation to Enhance Precision | . 138 |

|    |       | 7.1.2   | Synchronization Performance                            | . 141 |

|    | 7.2   | Simula  | ation                                                  | . 144 |

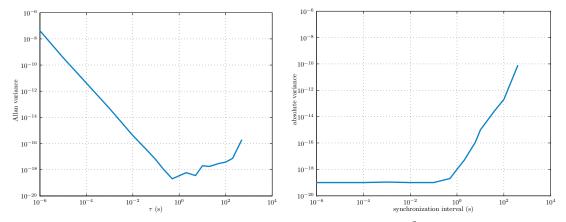

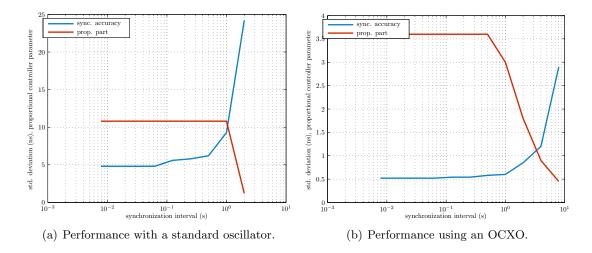

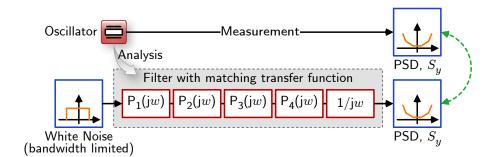

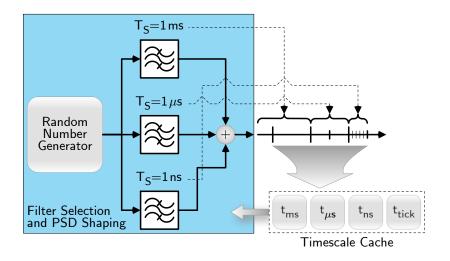

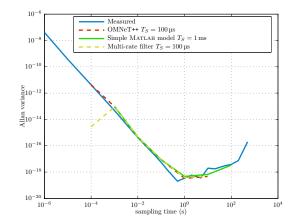

|    |       | 7.2.1   | Oscillator Model Concept                               | . 146 |

|    |       | 7.2.2   | Discrete Event Simulation (DES) Model Description      | . 150 |

|    |       | 7.2.3   | DES Model Implementation and Evaluation                | . 151 |

| 8  | Out   | look ar | nd Conclusion                                          | 154   |

|    | 8.1   | Layer   | 2 Implementations                                      | . 155 |

|    | 8.2   |         | dded Frequency Carrier for Wired Links                 |       |

|    | 8.3   | Wirele  | ess Links                                              | . 160 |

|    | 8.4   |         | Conclusions                                            |       |

| Ac | crony | ms      |                                                        | 165   |

## Abstract

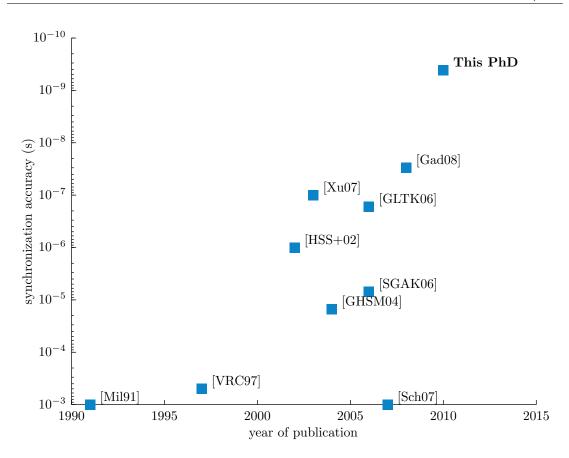

The evolvement of Ethernet in factory automation and test & measurement applications generated the need for high-accuracy clock synchronization. While factory communication can normally fulfil application requirements based on an average accuracy in the range of microseconds, test & measurement and several other applications (e.g. wireless position determination) seek for ultimate performance, meaning nanoseconds at most. This new demand, together with the issue of simplified node configuration, prepared the ground for a new protocol allowing for standardised synchronization in new dimensions.

The Precision Time Protocol standardised as IEEE 1588 addresses the topic of networked measurement and control systems by giving a set of rules for running high accuracy clock synchronization in a self-configuring topology. Due to the fact that not only the protocol itself is defined, but also the message timestamp point for several network technologies, it allows the implementation with hardware support. The latter enables the possibility to gain timestamps without jitter introduced by varying processing time in (software implemented) higher network layers.

The main goal of the present work is to analyse and propose a way to get from common PTP accuracy, which is about 100 ns, to systems being able to deliver sub-nanosecond performance. Although state-of-the-art devices for hardware timestamping PTP messages use the interface between the physical and data link layer, jitter sources remain, which can hinder high accuracy.

The aimed hardware support for highly accurate synchronization over Ethernet is as well targeted at the mentioned interface. This is argued by the fact that most network interface implementations use hardware blocks at this level and software routines for the higher functionalities. If the – for network synchronization indispensable – timestamps are drawn there, the effects of timely uncertainties of the software stack can be removed. Nevertheless, it is possible to operate at bit level.

An extensive analysis of existing disturbance factors on the synchronization accuracy and their (statistical) behaviour allows to design appropriate architectures and counter measures to further reduce the effects on the precision of drawn timestamps at this level. The examinations are partly done by measuring and modelling the disturbances and completed by mathematical expressions built from the knowledge of the type of the internal jitter source.

In order to show a complete picture of all relevant factors, not only the physical influence, but also structural issues are covered. These include the interaction of software with the time-keeping hardware, the analysis of external application requirements and the actual implementation of clock synchronizing hardware cells. To round network controlled systems off, the analysis describes design issues for synchronization systems and their relation to the actual hardware implementation.

## Zusammenfassung

Der verstärkte Einsatz von Ethernet in der Industrieautomatisierung und die zunehmende Verbreitung in Test- und Meßsystemen bewirkte den Bedarf an hochgenauer Uhrensynchronisation auf diesem Medium. Während Anforderungen in der Automatisierungstechnik üblicherweise im Bereich von einigen Mikrosekunden liegen, fordern Testund Meßaufgaben sowie zahlreiche andere Anwendungen (z. B. drahtlose Positionsbestimmung) extreme Genauigkeiten – oft unter einer Nanosekunde. Diese neuen Anforderungen und der Bedarf an vereinfachter Konfiguration der Netzwerkknoten schufen die Basis für ein neues Protokoll für standardisierte Uhrensynchonisation in einer neuen Dimension.

Das "Precision Time" Protokoll wurde als IEEE 1588 Standard veröffentlicht. Mit dem Hintergrund von Netzwerk basierten Meß- und Steuersystemen definiert es eine Reihe von Regeln für hochgenaue Uhrensynchronisation in selbstkonfigurierenden Topologien. Da neben dem Protokoll selbst auch der Zeitpunkt für die Zeitstempelung von Paketen in diversen Technologien definiert ist, erlaubt es auch den Einsatz von Hardwareunterstützung. Letztere erlaubt Zeitstempel zu generieren, die von den variablen Verarbeitungszeiten in höheren (in Software implementierten) Teilen des Netzwerkstacks unbeeinflusst sind.

Ziel dieser Arbeit ist es, durch Analyse der beteiligten Komponenten die aktuelle Genauigkeit von circa 100 ns auf Subnanosekunden zu verbessern. Obwohl aktuelle Implementierung für Hardware generierte Zeitstempel von Precision Time Protocol (PTP) Nachrichten die Schnittstelle zwischen physikalischer und Sicherungsschicht nutzen, verbleiben Jitterquellen, die eine hochgenaue Synchronisierung verhindern.

Die angestrebte Lösung setzt ebenfalls auf der erwähnten Schnittstelle auf. Dies ist vorteilhaft, da die meisten Lösungen in diesem Bereich noch Hardware einsetzen, während höhere Schichten bereits in Software implementiert sind. Zeitstempel an diesem Übergang sind daher unbeeinflusst von zeitlichen Schwankungen in der Verarbeitung durch die Software, dennoch ist ein Zugriff auf die Nachricht auf Bit-Ebene möglich.

Eine detaillierte Analyse der verbliebenen Störfaktoren für die Uhrensynchronisation und deren Charakteristik erlaubt den Entwurf geeigneter Architekturen und Gegenmaßnahmen, um den Einfluss auf die Präzision der benötigten Zeitstempel zu mindern. Die Untersuchungen erfolgen zum Teil durch Messung, aber auch durch Modellierung beziehungsweise mit Hilfe mathematischer Äquivalenzmodelle unter Kenntnis der typischen Eigenschaften der Störquelle.

Um die relevanten Faktoren vervollständigen zu können, werden nicht nur die physikalischen, sondern auch strukturellen Einflüsse analysiert. Dazu zählen die Abstimmung zwischen der notwendigen Software und der Zeitbasis, die Analyse externer Applikationsanforderungen und die Implementierung einer Uhrensynchronisationszelle. Für die Anwendung in Kontrollsystemen werden auch Entwurfsfragen bezüglich des Synchronisationssystems und deren Zusammenhang mit der Implementierung behandelt.

## Acknowledgement

I want to express my gratitude to everybody who helped me during the course of my studies. Concerning my dissertation I am thankful to Wolfgang Kastner and Francisco Vasques who both agreed to be the supervisors and gave a lot of helpful advice.

Special thanks also go to Thilo Sauter for his support. He made it possible for me to do all the required research since the early beginnings of the Institute. The supportive surroundings at work provided the base for my studies and their successful finishing.

Uncountable discussions, numerous critics, and countless hints were provided by my room mate, colleague and friend Georg Gaderer. There was no effort I could have asked for that he would not have taken to support my work. Thus, I am very thankful for all his help and the massive feedback to the document. He and his wife, Doris Richling, had the endurance to continuously push me towards the finish in which they now succeeded.

Special thanks go to all members of the CSI:WN (Clock Synchronization Investigation: Wiener Neustadt) group. In particular I want to thank my co-authors (Reinhard Exel, Aneeq Mahmood, Anetta Nagy, and Nataša Simanić) for their contributions to the topic and many discussions that helped me with a lot of enhancements to the topic of clock synchronization.

My friends Andrea Blatnek and Renate Hoffmann helped a lot with spell checking and always had an open ear for my problems, which made me endure the long way to the final document.

My parents not only supported my studies from the very beginning, but they also assisted me in any hard time I had and provided me suggestions how to solve difficult situations. Their advice always meant a lot to me and often brought me back to the essentials of a topic. Furthermore, they also helped me fixing numerous mistakes in the document with unbeatable care. As already with my previous works, whenever I needed support they found a way to give it to me.

## **1** Introduction

The successful spread of Ethernet based networks in the office area has prepared the ground for many interesting solutions enabling unique application requirements to be fulfilled by this general purpose networking technology. Together with the Internet Protocol (IP), interconnecting billions of nodes over the Internet via a universal approach, specialised network technologies like traditional fieldbuses lost importance. Although Ethernet and IP substantially lack real-time capabilities, classic fieldbuses and in particular sensorand control networks are replaced by appropriate solutions based on Ethernet for the sake of simplicity and cost-efficiency.

Important services, which were not foreseen in the design of Ethernet are real-time capabilities, in particular clock synchronization. First software-based approaches to tackle the problem originated from the Internet, where the problem of correct ordering of events and actions arose from the distributed character of applications. The early software implementations without any special measures limited the accuracy to milliseconds, but were nevertheless suitable for a wide range of applications.

The goal of the scientific work is to determine the limits of Ethernet-based clock synchronization, the various influencing factors, and efficient structures to accomplish the goal of high-precision clock synchronization with sub-nanosecond performance and long-term stability. This means that a timing node should be able to precisely track an upstream timebase in a continuous manner and therefore show the same behaviour as the source for time intervals significantly larger than the synchronization period.

## 1.1 The Necessity of Clock Synchronization in Distributed Systems

Distributed systems are referred to as a collection of spatially separated, independently running processes. In order to form a complete system, these processes or algorithms communicate with each other using message exchange. In case the transmission delay between two processes is not negligible compared to the time between two subsequent events in a single process, the term *distributed system* applies [Lam78].

Following this definition, implementations of distributed systems can have different appearances. One would be a system consisting of spatially wide distributed computers, which jointly process some task and therefore have to be coordinated. Another example is the interaction of different function blocks (e.g., processing and storage) on a chip. Both fulfil the requirement that the delay for messages exchange can be higher than the temporal distance between two events, which hinders the establishment of a common timebase.

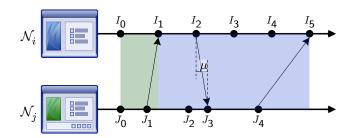

Figure 1.1: Ordering of events in a distributed system without a local timebase – parallelism as seen by node  $\mathcal{N}_i$

Resulting from the interaction and dependency on the results of remote blocks, there is a general need for ordering events in a distributed system. The essential question is, how the occurrence of events in separated function blocks can be ordered with respect to each other. The introduction of appropriate definitions, together with local clocks at each spatially distributed element, gives the theoretical background for handling such systems [Lam78].

The basic principle for ordering of events in a message exchanging system of two nodes (running some sort of process),  $\mathcal{N}_{i,j}$ , is shown in figure 1.1. Since concurrency of events is based on the information exchanged, seen from  $\mathcal{N}_i$ , all events occurring between two receptions of a message appear to be concurrent, i. e.,  $J_{0,1}$  to  $I_0$  and  $J_{2,3,4}$  to  $I_{2,3,4,5}$ . From the point of view of  $\mathcal{N}_j$  the events  $I_{0,1,2}$  are happening in parallel to  $J_3$  (and the events before). The parallelism can also be explained by the fact that always the remote node can only know about events after they happened and their occurrence was reported using a transmission (experiencing the delay  $\mu$ ). The remote node is not able to distinguish between events that took place between two message exchanges.

Based on that, another method to get ordered events in a distributed system is to provide a local timebase in each element exchanging messages with others. This allows for finer granularity without the dependency on the reception of a message after each event. The easiest approach for a general order is to have a physical local clock  $C_i$  keeping its value  $C_i(t)$  at node  $\mathcal{N}_i$ . It shall follow the global real time with only a negligible small error rate  $\kappa$ , which is equivalent to the requirement

$$|\mathrm{d}C_i(t)/\mathrm{d}t - 1| < \kappa \;\forall i, \kappa \ll 1.$$

$$(1.1)$$

This requirement still does not ensure the correct ordering of events between several nodes of a system, since the individual time scales still drift with respect to each other. Synchronization of the nodes, in order to limit the maximum absolute offset between them to a small value  $\varepsilon$ , is a further requirement and expressed by

$$|C_i(t) - C_j(t)| < \varepsilon \ \forall i, j.$$

$$(1.2)$$

Analogue to [Lam78], events can be correctly sorted, if the value  $C_i$  of a clock after a small progress in (absolute) time,  $\mu$ , is always greater than the value of all other clocks

before that step. This means that the occurrence of two events in different nodes  $\mathcal{N}_i$  and  $\mathcal{N}_j$  can be set in a clear sequence. From the point of view of a distributed system,  $\mu$  can be seen as the time required for exchanging a message between the two nodes. The condition is formulated as:

$$C_i(t+\mu) - C_j(t) > 0 \ \forall i, j, t.$$

(1.3)

In order to ensure the correct ordering of events, a relation between  $\kappa, \varepsilon$ , and  $\mu$  can be established. Applying equation 1.1 to 1.3 gives,  $C_i(t + \mu) - C_j(t) > (1 - \kappa)\mu$ . Since  $\varepsilon$  was defined to be the maximum offset between any two clocks, the inequality

$$\varepsilon/(1-\kappa) \le \mu \tag{1.4}$$

together with 1.1 and 1.2 ensures a unique sequential order of events in a distributed system.

The message transmission time and therefore the value of  $\mu$  is mostly given by the environment a distributed system runs in, i. e. the technical implementation and properties. In contrast, the drift of nodes with respect to some reference (see equation 1.1) and the offset between any two of them (see equation 1.2) can be controlled by using clock synchronization by the means of message exchange. Consequently, clock synchronization is an essential service required by any distributed system depending on an overall consistent order of events of all nodes. Commonly used methods and protocols, which provide this service for the scope of the thesis are discussed in section 3.

There are several examples for a distributed system, which require obeying the rules mentioned above to ensure proper functionality. The following list (based on an overview work on network synchronization [LGHD85]) explains some sample systems, which have an obvious need for clock synchronization:

- Within a *digital communication network*, e.g. a telecommunication network, there are several multiplexing points. These nodes can fulfil different tasks: they aggregate multiple input streams into one high-bandwidth output stream, are able to demultiplex, or extract individual low-bandwidth data streams out of a collection. For all these operations, the whole network has to be synchronous. Otherwise large buffers are required to compensate for varying data rates. Details about synchronous networks can be found in section 3.1.

- In networks, which use *Time-Division Multiplexing* each node is assigned a specific portion of time (slot) during a constant period (cycle) for all nodes in a system in which it is allowed to send data to a network. Since every node has to know when it is allowed to transmit data, synchronization is required. Most real-time networks (see section 3.3) rely on that scheme, which is also used in other digital (broadcast) networks, e.g. satellite or television.

- Sensor and control networks (often referred to as fieldbuses) as well as the wireless equivalents may require clock synchronization in order to provide time consistent sampling and coordinated execution of actions. The acquisition of data at a distinct

point in time at a large number of sensor nodes allows to give a consistent view of the overall system and summing up of values in order to compare it to a global value, e. g. sampling of current water consumption of households in a city to be compared to the overall water consumption to detect leaks.

Often it is also required to correlate the command execution of actuators. Large systems like particle accelerators demand specific magnetic field profiles to be present at a certain point in time. The overall performance is heavily dependent on the tight timely coordination of the beam direction magnets. The Large Hadron Collider (LHC) at the European Organisation for Nuclear Research (CERN) is one example for such a system, which is covered by section 2.3.

- For test & measurement systems the timely coordination of multiple measurement instruments is an important issue. Furthermore, the integration of signal generators and test instruments with the data acquisition allows to build automated test environments. So far, all these instruments were connected and controlled by the IEEE-488 bus, also known as General Purpose Interface Bus (GPIB) [IEE04b]. Modern devices replace this method by LAN eXtensions for Instrumentation (LXI) (see section 3.3.6) allowing to propagate timing, control information, and measurement data over Ethernet at much higher speed over significantly simpler cables.

- By detecting and timestamping the arrival of a common signal by several nodes within a network it is possible to implement *range measurements or position determination*, respectively. For the case of two nodes, e.g. the observation of overvoltage at the end of a power supply line, it allows to calculate the position of a lightning strike using the propagation speed and the timely difference. Similarly, the method can be applied to multiple receiving nodes in order to locate a wireless transmitter by calculating the position from the Time Difference of Arrival (TDoA) of a broadcast signal. For details see section 2.2.

- As for the example of localisation, spatially distributed *phased-array antennas* can also be seen as a distributed system with the immanent need for synchronization. Examples for such an application are world wide connected radar antennas or interferometric measurements in observatories for space observations. Not only the coordinated alignment of the antennas, but also the timely correlation of detected signals is an important information for position calculation. If the antennas are used to transmit signals, the slight shift in phase of the outgoing signal between individual antennas leads to directivity without the need for mechanical components.

- The interconnection of a number of computers for the goal of high performance is also called *distributed or grid computing* and requires synchronization as well, since events have to be ordered. The need is obvious for distributed databases, which have the requirement to order the incoming data change requests as well as for the general application of data synchronization, e.g., distributed file systems, backups, and version control systems. Modern grid computing networks (or in general tasks

for parallel computing) always face the problem of sequencing occurring events, which has to be solved by the methods of synchronized distributed systems.

- In *security* critical systems synchronized clocks can be used to achieve total ordering of messages and therefore prevent fabrication attacks. A Time Variant Parameter (TVP) is used to verify the sequence of messages, which can be if made available by a clock synchronization protocol a timestamp from a common clock. More information about hostile attacks on clock synchronization can be found in [Gra10].

- Operations that have to ensure tasks that are crucial for *safety* often depend on guaranteed reaction times. To that end, clock synchronization is used e.g. to provide timely access to the communication medium as well as real-time processing of the required events. Furthermore, stringent communication or reaction timeouts between the involved nodes can be implemented and handled in an easier way if a common timebase is available throughout the considered network.

- Distributed systems and embedded clock synchronization are also part of *scientific research* seeking either for investigation of advantages arising from the interconnection of nodes in a network or for high accuracy in order to improve the performance of the above mentioned applications.

In general, the establishing of a world-wide time distribution system is not limited to technical communication systems, but can also be encountered in other areas. The introduction of some sort of schedule to a certain area of life soon requires synchronization in the sense of a distributed system. The roadmap for trains or the timetable for air traffic are typical examples. Besides the technical examples there are also biological ones, like the synchronous blinking of fireflies described in [Buc88]. The principle was analysed to be used as an algorithm in technical applications [WATP+05]. Several proposals show the usability, especially in wireless sensor networks, where the method allows for tight synchronization while keeping the power consumption low [LE09].

### 1.2 Basic Terms

This section contains a collection of definitions, which are required for the area of distributed systems and clock synchronization. It is not intended to be a complete list, but will cover the terms used in the scope of the thesis.

- **Accuracy** is the closeness of agreement between a quantity value obtained by measurement and the true value of the measurand.

- **Precision** is the closeness of agreement between quantity values obtained by replicate measurements of a quantity, under specified conditions.

Both terms are standardised in [ISO07] and are important to be distinguished. Especially for the use case of clock synchronization, high precision within a limited number of nodes might be more important, than the accuracy. The first means corresponding simultaneous measurements by different nodes, while the latter is the agreement with a *perfect* clock, external to the system in question. In other words, the accuracy defines the mean of the time or frequency error between a clock and its perfect reference over a number of measurements. The precision is then a measure for the deviation of the error from the mean. [IEE08b]

- **Inner clock synchronization** refers to achieving a common agreement on the clock values between all nodes of a dedicated system. This requirement is formulated in equation 1.2 stating that the offset between any two nodes of the system is below a certain boundary at any time.

- **Outer clock synchronization** links a clock or a system of nodes to an external reference. The connection can be done via a single distinct node, e.g. the master node, or in a distributed way. The goal is always to achieve a global time scale within an enclosed system in order to get a correlation with other spatially separated systems.

The main distinction between the two terms with respect to a distributed system is a logical/structural one. Depending on whether the time reference is considered to be part of the considered network or not, the system performs inner or outer clock synchronization. Mostly, networks with only outer clock synchronization do not make much sense, whereas mere inner operation is quite common [Lis93].

- **Syntonization** is the process of adjusting the frequencies of two processes to be identical. For two clocks,  $C_{i,j}$ , this means in particular that they progress at the same rate and return the same duration value for a common external event. This is equivalent to the mathematical formulation  $dC_i(t)/dt = dC_j(t)/dt \forall t$ .

- **Delay compensation** is the method to cancel out the message exchange delay between two nodes. If the transmission time in a system cannot be neglected, delay compensation is required to get correct measurements of the absolute time, i. e. appropriate accuracy.

- **Synchronization** combines the previous two points and denotes the technique to keep the offset of two clock values,  $C_{i,j}$  below a certain boundary (see equation 1.2). In other words, the measurements of the time of a single event at an arbitrary time by the two clocks do not differ by more than the uncertainty,  $\varepsilon$ .

The three techniques mentioned above denote the basic services required to be performed by a clock synchronization system. Consequently, all synchronization methods mentioned in chapter 3 implement these services using different approaches to reach the desired consistent time on all participating nodes.

**Timescales** are used to define the begin (time value zero) and the divisions (scale) of time. The primary timescale is called international atomic time (TAI) and advances with the rate of the international system of units (SI) second. From TAI the Coordinated Universal Time [ITU02] (UTC) is derived by adding leap seconds to

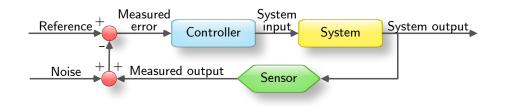

Figure 1.2: Single control loop with measurement noise

compensate for the slowing earth rotation. Nevertheless, both scales advance at the same rate and just differ by full seconds. Many technical systems requiring a timescale define their own in order to specify the start value, e.g., GPS, NTP, PTP.

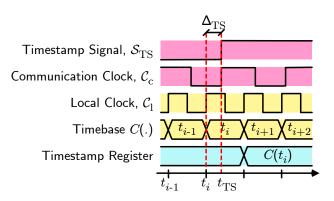

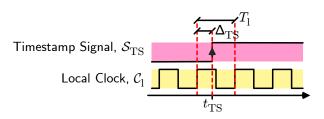

- **Timestamping** is the process of copying (freezing) the current value of the clock C on occurrence of an (external) event. The generated copy of C(t) at an instance in time is then called *timestamp*,  $TS_C = C(t)$ . Often, the timestamp and some sort of event identifier (e.g., sequence number, hash code) are stored together, in case it is necessary to be able to link the timestamp to the event later on. For details see chapter 1.4.2.

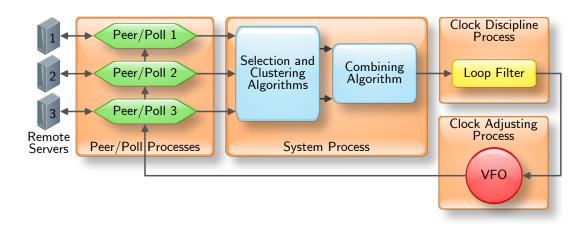

- **Control loops** consist of three basic elements shown in figure 1.2. The controller, the system, and the sensor form the well known closed loop of the control theory. For network-based control loops, the controller may be split up into the actual controller, calculating the value for the system input and the actuator, which generates the system input and is attached to the system. In digital communication systems, all components work as sampling systems, meaning that the values are exchanged between the components in a time discrete way (messages). Consequently, for digital networked control systems the considerations of chapter 1.1 concerning distributed systems apply.

- **Sensor and control networks** are communication systems that incorporate sensors for data acquisition, actuators for influencing the considered system, and one or more (distributed) appropriate controllers. All are interconnected in form of a distributed system. Characteristic properties of such networks are a large number of sensors, which are used to generate a consistent overall picture of a specific system and relatively low processing power per node. Especially the aim for a reliable overview requires exact timing of the recorded measurement data.

### 1.3 Clock Synchronization in Packet-Oriented Networks

From a historical point of view, the evolution of networks first began with dedicated links between all nodes [Kle10]. This method only allows a small number of participating clients, as soon the effort to interconnect a new member to the existing system becomes unmanageable. If only unidirectional links are considered, the number of required links, M, for n nodes calculates to  $M_{\text{uni}} = n \cdot (n-1)$ . Even if, more realistic, bidirectional links are taken into account, larger networks are still quite inefficient due to the growth of

$$M_{\text{bidir}} = \sum_{i=1}^{n} (i-1) = \frac{n \cdot (n-1)}{2},$$

(1.5)

which is still in the same order as the unidirectional version of the network, namely  $\Theta(M(n)) = n^2$ .

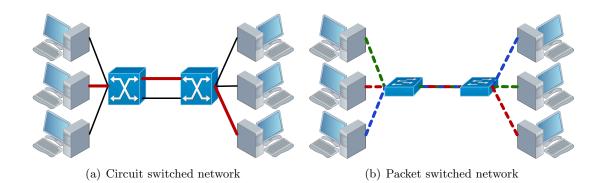

In order to build larger networks, the technique of *circuit switching* was introduced. In such a network dedicated connections are still used, but a central switching element establishes the direct link between two nodes on demand. In the optimal case every node only needs to be connected to the central element, which then reduces the order to  $\Omega(M(n)) = n$ . For large networks it is unlikely that all nodes can be connected to one centre point. To solve this issue, multiple switching elements are introduced, which are interconnected by dedicated links as any other node. The number of links between the elements has to be chosen in a way that the maximum number of nodes communicating with nodes of the other switching element can be assigned a link. Therefore n is the lower bound for the number of links and only valid for relatively small networks, larger versions require the afore mentioned additional connections between the switching elements. Modern digital versions of the network allow virtual links on one dedicated line using TDM. For details see chapter 3.1. This type was and still is used in telecommunication networks.

The next evolutionary step for communication networks was the introduction of *packet switching* and its special version *cell switching*. In contrast to the previously mentioned network types, packet switching allows more efficient use of the individual link capacity between nodes and/or network switches, since there is no need for static bandwidth assignments. This is due to the fact that in packet switched networks, every packet can (theoretically) take its own route through the network, which also increases fault tolerance based on redundant links. Additionally, cell switching ensures that all packets of a virtual connection (or any other common criteria) are routed on the same path. Routing is therefore semi-static but still gives the flexibility of the packet-oriented approach mentioned above.

Switching packets also allows to run many different services or user requests over a single network type taking advantage of bandwidth aggregation. This evidently increases the efficiency due to the flexible usage of resources at the expense of losing a dedicated connection, which can then only be emulated on higher protocol layers. This emulation differs from a real circuit switched connection mainly in its unknown delay behaviour.

#### 1.3.1 Transmission Delay Boundaries

Concerning distributed systems as defined in chapter 1.1, the most important issue is the afore mentioned undefined packet transmission delay. As shown, the time for transferring data,  $\mu$ , influences the achievable precision for the ordering of events. Although, for

Figure 1.3: Network types

any experiment with a finite number of samples (not considering packet loss) there is an upper bound of the delay, it cannot be assumed that this is the theoretical upper bound. Moreover, the significant gap that exists between any experimentally determined and the minimum delay makes the bound impractical for the purpose of synchronizing *n* clocks, since all deterministic algorithms that depend on an upper bound for the maximum communication delay cannot achieve a maximum deviation better than  $(\mu_{\max}-\mu_{\min})/(1-1/n)$  [CF03, WL88].

An efficient synchronization method for packet-oriented networks therefore should not assume any upper boundary on communication delays in order to work correctly. Since there is also a non negligible chance that packets can be dropped, all techniques explored in this thesis for synchronizing network nodes in packet-based distributed systems are able to cope with unexpectedly long (infinite) delays (equivalent to packet loss).

#### 1.3.2 Packet Relaying Effects

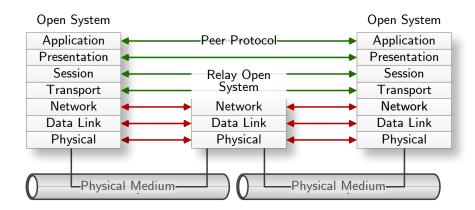

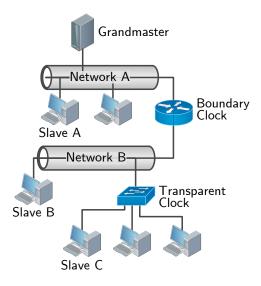

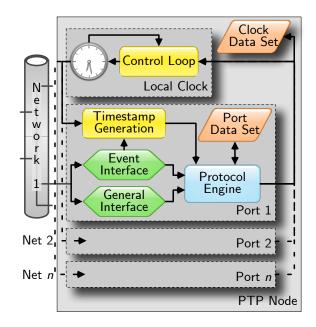

According to the International Organisation for Standardisation (ISO) Open Systems Interconnection (OSI) Basic Reference Model [ISO94] the lower three layers of the reference stack are required to deliver packets in a network with an unlimited number of nodes. Layer 3 is the last which is involved in path decisions and provides routing and relay independent functionality to higher layers. Consequently, the layers for the physical connection, data link and network layer have to be considered to contribute to the delay of a packet, when travelling from the sending to the receiving node. The overall system is illustrated in figure 1.4.

Depending on the layer where the relaying of packets is done, the elements are called *bridge* (layer 1), *switch* (layer 2), or *router* (layer 3). Each of these network elements, which might be placed between two end nodes, can add unknown jitter to the packet transmission time and contribute to the absolute value. Therefore each of them seriously influences the clock synchronization performance for a distributed system. Further, the delay is unbound and thus requires special consideration in the event ordering algorithm, as mentioned before. The details of the delay/jitter performance of the individual protocol layers are discussed in chapter 4.

Figure 1.4: Communication involving relay open system according to the ISO OSI Basic Reference Model

It is important to take into account that switching and routing are based on addresses stored in the packet to be delivered and therefore require processing of the data contained. Since these addresses have to be read out, processed, and then taken as the basis for a packet path decision, there is not only the propagation delay through the network element but also some processing delay. The latter can be different for each packet since it might be address or data dependent. While layer 2 is normally designed to allow for constant processing delays, typical protocols on layer 3 even feature variable size headers and therefore hinder steady packet forwarding by principle since the required information arrives at different times.

Two principles are known to be used in relaying elements. On the one hand *store-and-forward* technology receives the complete packet into a buffer, then processes the required information for routing path decision, and finally forwards the packet. On the other hand *cut-through* methods only buffer the part of a packet's header which is required to select the routing path and then immediately start forwarding the packet. This method significantly reduces the residence time of a packet in the relaying element. The disadvantage is that the Frame Check Sequence (FCS) is commonly stored at the end of a packet and therefore checks cannot be done before sending the packet. As a result, also damaged packets are relayed. Some implementations use a mixed strategy, which takes cut-through as long as the number of damaged frames stays below a certain limit and switches to store-and-forward otherwise.

## 1.4 Hardware Support for High-Precision Clock Synchronization

Besides a protocol for exchanging accurate timing information, high-precision clock synchronization requires dedicated hardware support. This is due to the fact that software implementations can only be as accurate as the underlying hardware processing, without taking advantage of statistical effect by special algorithms. The latter can as well be applied to hardware supported systems to further increase accuracy. In this thesis the term *dedicated hardware* support refers to some additional logic, which is specialised in processing of operations for clock synchronization. This can be a special real-time clock, high-precise timestamping, or immediate event processing for example. Contrary, common general purpose processors are able to run synchronization software but cannot react to events very fast (e.g. interrupt processing latency) and therefore hinder accurate timestamping. Also the other way round, generating events at exact moments in time is hindered by task switching delays within micro controllers or a Central Processing Unit (CPU).

The key issue with a generalised approach is that state-of-the-art processors require several clock cycles to make a context change. This originates from the necessity of saving the current processor state (registers) and then proceed at a different program (position). Also pipeline architectures within a modern CPU delay the actual reaction to an asynchronous event, because the pipeline of pre-loaded instructions has to be flushed and filled with the code to handle the exception. Since a number of processor instructions are always required to change the context, even with clock rates in the GHz range, the delay can reach several nanoseconds. If further OSI layers are involved, an operating system or similar software requires even more instruction cycles and can therefore shift the delay even to the micro- or millisecond range.

#### 1.4.1 Required Elements

The obviously indispensable element for hardware support is a timekeeping element, the clock C. This central element has to be reachable by all functions mentioned in the following. In other words, the required time to determine the current value C of the clock C has to be negligible compared to all other processing times in the system. The term distributed system consequently does not apply to the considered hardware subsystem and avoids the utilisation of special measures for message exchange delays. The sequence of events within the dedicated hardware support block is given by a common clock signal with pre-compensated propagation delay.

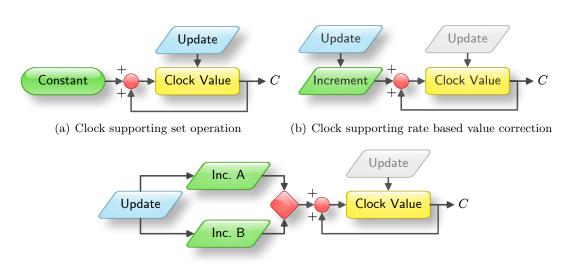

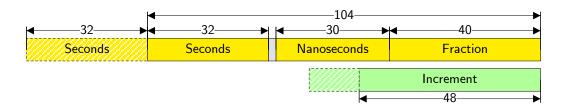

The clock has to fulfil a number of prerequisites concerning C and the available operations on this value. Firstly, C should be strictly monotonically increasing, so that for any two events, which do not happen at the same time, C shows a different value  $(C(t + \varepsilon) > C(t) \forall t, \varepsilon > 0)$ . This avoids some time values being used twice for non concurrent events due to a step back or a too slow progress of the clock.  $\varepsilon$  therefore has to be smaller than the shortest time between two events that should be distinguishable and gives the highest reachable precision. Secondly, in order to fulfil the just expressed premise, a controller is required to adjust C according to a master that has to be able to use special functions. A simple operation like *setting* the value of the clock (as illustrated in figure 1.5(a)) is not sufficient, since this would cause reoccurring time values in case the clock is ahead of time and has to be corrected.

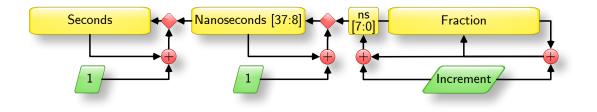

In order to overcome this problem, many modern implementations utilise a *rate* setting approach as shown in figure 1.5(b). This method uses an increment value, which is added to the current time of C with every tick of an oscillator. By increasing or decreasing

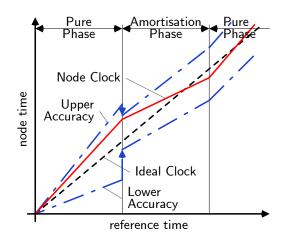

(c) Clock with two selectable increments

Figure 1.5: Structures for hardware clocks

the increment the progress of C can be speeded up or slowed down. Consequently, any inaccuracy of the node can be compensated by the controller. The obvious advantage over the previous is that C fulfils the requirement of a strictly monotonic increase even in case the node is ahead of time and has to be corrected back. This structure is called Adder-Based Clock (ABC). Figure 1.5(c) shows the next evolutionary step: the *amortisation*-based clock, which is an enhanced version of the ABC. This technique uses two values for the increment where the additional one can be set temporarily for a specific period of time. It allows to concentrate the required (possibly large) frequency change to compensate for a time offset to a specific period. Thus, it is possible to decouple e.g. round-trip delay measurements, which require a calibrated frequency, from the offset compensation.

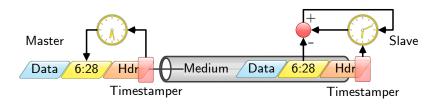

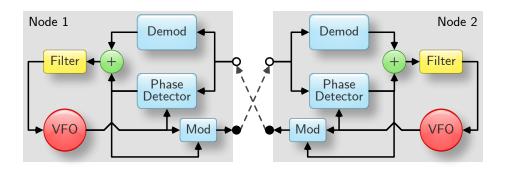

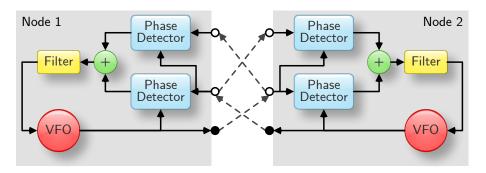

With the functionalities mentioned above, the clock is able to keep the time and can be adjusted by a controller. To build a closed control loop, it is necessary that the hardware clock is able to timestamp external events. In case of distributed systems where message exchange is required, a function block called *timestamper* is responsible for generating a timestamp signal on arrival of a network packet or message. This signal is then used to generate a copy of the current clock value. By comparing this timestamp to the time transmitted in the message, the current error of the local time value can be determined and used to feed the controller for adjustments. The principle is shown in figure 1.6. The timestamping functionality should be available separately for incoming as well as outgoing messages to support delay compensation schemes. The latter require bidirectional communication in the non preconfigured case and therefore hardware, which is able to timestamp messages on the ingress and egress path.

Besides the basic building blocks, the timekeeping clock itself and the timestamper required for operation in distributed systems, a complete clock synchronization core (e.g.,

Figure 1.6: Function principle of timestampers close to the physical medium on the egress path (master) and ingress path (slave) to compare clock values of two nodes.

chapter 5) should also provide additional functionalities to make use of the accurate local time. The most important issue with these operations is that they are executed in a deterministic way. In other words, the time passing between the execution and the instant in time the clock reaches the scheduled value should be negligibly small and fixed. Commonly required functions to benefit from a highly accurate local time in hardware include:

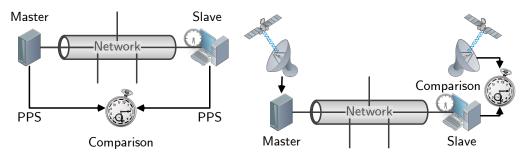

- *Periodic timers* are used to generate an external signal in fixed equidistant time intervals. The most prominent and widely used representative of this class is the 1 Pulse Per Second (PPS) signal. This type of signal is used in many synchronization related systems like atomic clocks (e.g., caesium (Cs<sub>133</sub>) or rubidium (Rb)), Global Positioning System (GPS) receiver, or the Inter Range Instrumentation Group (IRIG) standard time code B [Tel04].

- *Triggers* are used to set a signal (generate an edge) at a specific time value. The signal can be for instance an Interrupt ReQuest (IRQ) signal in a computing system to exactly trigger certain procedures. Furthermore, it can be used to transfer the occurrence of a special instant of time to any other external device.

- Many applications, like synchronous networks (see chapter 3.1) require a syntonized *frequency output* at each node in order to perform Time-Division Multiple Access (TDMA) on the network medium. Since this type of network also has some higher-level absolute event ordering, synchronization is required as well.

- Similar to output signals generated by triggers and periodic timers of the clock synchronization core, some input signals should allow *timestamping of external events* with the local time. This feature allows for example the synchronization of the core to some external time source, like the 1 PPS of a GPS receiver.

- For detailed and/or distributed network traffic analysis, *packet timestamping* for arbitrary messages is an essential function. Since it is inefficient to draw and transfer a timestamp for every incoming or outgoing packet to the software, the hardware timestamper should perform some pre-filtering and buffering. Consequently, there has to be the possibility of configuring the timestamping unit to produce timestamps for timing messages and in addition for the type of packets to be traced in the network.

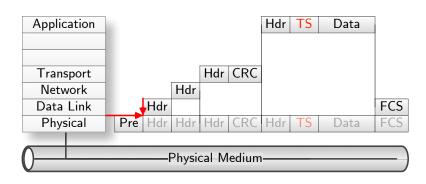

Figure 1.7: Illustration of layered assembly of an exemplary physical layer frame, using headers (Hdr), CRC, FCS, and the frame preamble (Pre). The arrows mark the last physically available interface on Ethernet, the MII, and the earliest (reasonable) timestamping point.

#### 1.4.2 Transfer of Timestamps and the OSI Reference Model

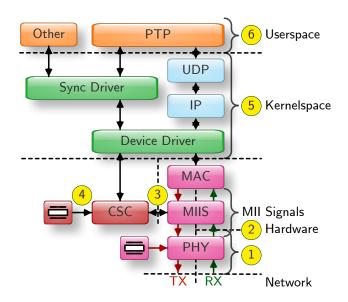

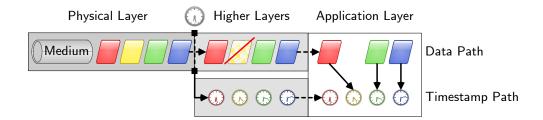

In order to avoid as many temporal uncertainties (jitter) caused by varying processing times in the different network layers, timestamping is desired to be as close to the physical medium as possible. This requirement on the other hand causes problems with respect to the layered approach of the OSI Reference Model. Since the task of synchronization is not foreseen in the standardised representation (as well as the most commonly used lower layer protocol implementations), it was implemented as an application function (peer protocol) on layer 7. Consequently, there is a need to transfer the timestamps from the layer of origin there. The induced difficulties occur from the fact that the ingress and egress path for messages does not allow to transfer timestamps in parallel (linked to the message).

The problem induced by the layered approach of the OSI reference model is that clock synchronization actually effects several layers. While the physical layer is desired to be the source of timestamps (due to the mentioned jitter issues), the synchronization of nodes is a global networking issue. Consequently, the transmission of timestamps in a network of a certain size requires the functionality of layer 2 and 3 unless an operation with a limited number of nodes can be accepted.

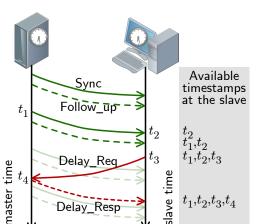

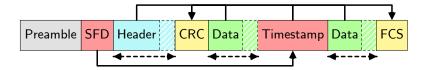

Several issues related to the protocol implementation on layer 7 and the need for accurate timestamping are illustrated in figure 1.7. The timestamp, TS(t), can be transferred to the synchronization engine using two methods, in-band or out-of-band. While the first technique encapsulates the timestamp into the frame to be sent or received, the second uses a separate path (e.g., First In – First Out (FIFO) buffer) to make it available to the application. The latter suffers from the fact that the timestamp has to be associated to the corresponding frame by other means (e.g., comparison of CRCs, sequence numbers). This is necessary because of the possibility that any layer between the gathering of the timestamp and the usage in the protocol software might reorder or even drop the frame. In this case the chronological order would be interrupted and cause false association resulting in an additional offset for the synchronization. For the egress path this method also requires the sending of a second packet (with the actual time the frame left the node), since the timestamp for an outgoing frame is only known after its transmission.

Drawing the timestamp close to the physical layer has the advantage that there is (at least for the case of Ethernet and many other transmission standards) a fixed temporal relation between the start of the frame and the timestamping point. The resulting timestamp is then identical for all devices and jitter is only subject to physical effects and not related to varying header length of the frame. Nevertheless, if the transmit timestamp is transported in the application layer protocol data, the following issues can hinder the correct insertion at the time it is generated.

For the egress path the insertion or update of the transmit timestamp,  $TS_{tx}(t)$ , can cause several issues that have to be considered to ensure correct functionality:

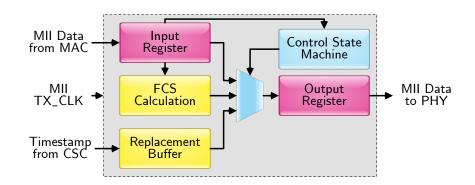

- The calculation of a CRC for the application data that is stored in front of the actual data is impossible due to the sequential and non-interruptible data transfer on the medium. Furthermore, since this interface to the medium is located already after the Media Access Control (MAC), there is a strict time behaviour and additional modules are not allowed to delay data transfer for processing. Since the hardware module has to draw a transmit timestamp at the beginning of the frame, the CRC would have to be recalculated for the unknown data part. The cyclic properties of the checksum allow to modify the CRC by adding the part for the (now known) timestamp to the existing value and then inserting the timestamp. Nevertheless, this requires knowledge of the pre-existing value of the timestamp (e.g., could be solved by choosing it to be zero) and the one of the CRC. The latter requires a transmission delay of the bit-time times the length of the CRC, which might not be allowed by the specification of the interface from layer 2 to 1. For more complex (cryptographic) checksums (e.g., MD5, SHA-1), this method fails, because they cannot be updated without knowing the actual data.

- If outgoing frames have an appended FCS it requires an update to take the actual value of the timestamp into account. Again, the frame can either be delayed by the size of the FCS times the bit time to make an incremental update, or the value can be completely recalculated for the whole frame during transmission, since the final value is known at the time it has to be inserted. For the latter technique, the timestamping functionality has to be integrated into the egress path of layer 2, because a recalculation of the CRC value on the interface by a separate unit corrects the FCS for bit errors happening between layer 2 and the intermediate timestamping unit to layer 1.

- The most challenging part for inserting a timestamp into the application layer data is to cope with varying header lengths. The hardware processing unit at layer 2 has to know the position where the timestamp should be updated. Due to varying headers (e.g., packet type or link layer encapsulation) the position might change. In order to recognise the timestamp independently of these issues, the timestamping hardware has to be able to calculate the actual position out of the leading headers.

This requires knowledge and basic parsing capabilities for upper layer protocols and introduces compatibility issues. The protocol parsing ability is (at least partly) a redundant implementation of the corresponding higher layers. Consequently, they have to match the realisation there to ensure correct functionality. The approach is quite complex and heavily violates the layered approach resulting in difficult realisations or limited universality.

For the ingress path almost the same issues apply, except for the fact that the timing of the incoming frame is not critical and therefore, more complex processing even on temporarily stored frames can be done for the recalculation of the CRC. Still, the complexity of parsing upper layer protocols and the fact that the application data area must foresee a field to be updated with the receive timestamp, remains. Simply appending the timestamp to the frame at layer 2 is normally possible, since the checksum is valid only for a given length and therefore not violated. Nevertheless, there are maximum frame lengths, which might be exceeded unless the necessary length for adding the receive timestamp is reserved on the sending side.

Summing up, drawing the timestamp at the layer close to the medium and propagating it to the synchronizing application according to the OSI Reference Model is not a trivial task. The chosen method has to fit the application layer protocol as well as the implementation of the intermediate network layers. This may involve the network stack of an operating system and therefore limits the possibilities for solutions.

### 1.5 Contribution of the Thesis

For the mentioned application areas, so far a number of dedicated interconnection solutions were used. For example automation tasks were covered by several fieldbuses [Sau10]. Nevertheless, for integration, availability, and of course also cost reasons, these dedicated solutions were replaced by Ethernet-based networks. The latter suffer from the fact that Ethernet was not designed for time sensitive use cases. Thus, a number of real-time enhancements (see chapter 3.3) were designed.

The present work analyses the historical approaches based on synchronous solutions and draws the path to nowadays wide spread packet-oriented (Ethernet) networks. More and more applications demand for higher clock synchronization accuracy from a technology that was not designed to fulfil this purpose. Therefore, the thesis covers the enhancement of Ethernet-based clock synchronization under the pre-condition of practicability and conformance to the relevant standards. Obviously, there could be more efficient solutions than the developed one, but not in conformance to the standard or under the prerequisite of commercial-of-the-shelf physical layer devices.

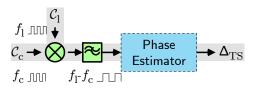

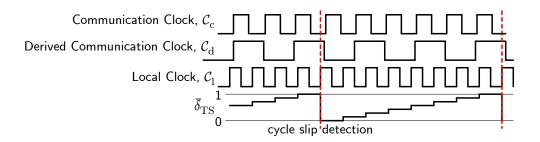

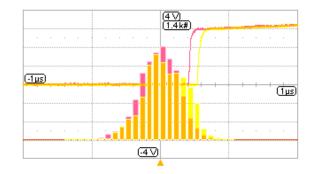

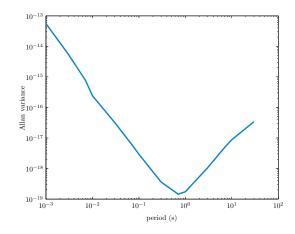

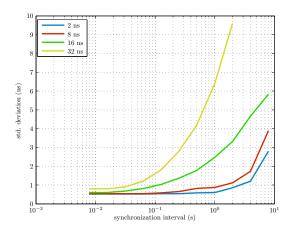

The detailed characterisation of the prerequisite, i.e. Ethernet, points out the influencing factors on clock synchronization. Furthermore, several possibilities for highly accurate timestamping methods, the necessary base, are analysed for their usability in Ethernet-based solutions. The combined phase/frequency estimation method turns out to allow for extremely accurate timestamping at the edge of the physical performance of the utilized hardware elements. Several aspects regarding oscillators, which are used as the clock source for the transmission as well as the timekeeping, are investigated for better understanding of the origin of inaccuracies. The work develops models to simulate the jitter sources and characterises the influence of the oscillator noise parameters on the performance of the overall synchronization system. Especially the interdependency between different system parameters, e. g. oscillator stability, synchronization interval, or timestamping resolution, are formulated and verified by measurements.

The overall goal of this work is to determine the limiting factors of current Ethernetbased clock synchronization systems by appropriate characterisation. This helps to find out about deficiencies in existing solutions that hinder higher accuracy. To this end a system-wide view on clock synchronization is necessary to cover the interdependencies of the involved hardware and software elements that influence the finally achievable accuracy.

The conclusion out of the analysis is then utilised to develop efficient structures for increased synchronization performance in the sub-nanosecond range. The investigation of relevant issues is started at the necessary clock source and the network link itself. Since all other logic elements depend on these two elements the decision for a specific implementation of them decides on the maximum achievable accuracy of a synchronization system.

## 2 Motivation of the Problem

Besides the general categories of applications for high-accuracy clock synchronization mentioned in section 1.1, this chapters exemplarily explains some applications that require precisely adjusted clocks. The selection follows the contribution of this work to the use cases that occurred in the outlined projects. The stated accuracy can be impressively seen in the given localisation accuracy, which is directly dependent on the synchronization performance of the receiving access points. Nevertheless, also distributed sensor networks with a large number of nodes do require relative high accuracies, as described in the following.

### 2.1 Remote Metering using Power Line

The investigated techniques to precisely synchronize distributed sensor nodes were integrated in an embedded processor described in section 6.1.3 for a large-scale remote metering application. A promising approach for low-cost clock distribution in large-scale systems is the usage of Power Line Communication (PLC) systems. For this type of communication medium clock synchronization is a crucial issue, not only because the PLC network itself requires synchronized clocks for maintaining time-sliced communication, but also the target application of remote read-out of domestic supply meter demands accurate synchronization.

In the lower levels of a hierarchical PLC system attention has to be paid to the special properties of the network with respect to varying network topologies, short message length and the like. Such an architecture has the advantage that using the existing wiring of power lines a communication infrastructure can be established in order to manage energy consumption more efficiently and inexpensively.

One issue of such networks is that fast log-on and log-off of nodes travelling from one access point to another has to be ensured. The demand originates from the fact that nodes and groups of nodes may disappearing on one side of the network and re-appear at different points – most likely at a different hierarchy as well. This is caused by the usual way of energy suppliers to switch whole net-groups from one transformer station to another, thus changing the logical hierarchy of the PLC network significantly.

Furthermore, interesting Supervisory Control and Data Acquisition (SCADA) applications that determine the loss (e.g. of water, electricity, or gas) depend on a central meter and an accurate sum of the data gathered from a high number of end-user meters. Using this communication infrastructure metering data can be retrieved without sending a physical person to read out the meter. Additionally, since the sum has to match the central amount it is necessary to synchronize the distributed meters in order to acquire the reading at single point in time to make the sum a meaningful value. Only

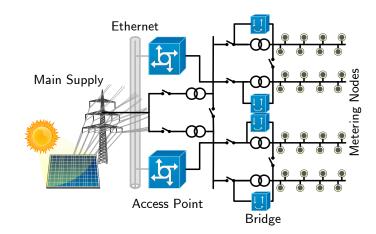

Figure 2.1: Remote metering network architecture using PLC. The switches allow failover or load balancing within the network, but can significantly change the topology. Similar structures can also be used for other supplies (e.g. water or gas)

then a global status of the system can be achieved that allows to determine the loss by subtracting the sub-meter sum from the value determined at a central point. This way, the detection of energy theft is done by advising all nodes in advance to record their meter values at a certain, predefined point in time. Thus, manipulations and energy thefts can be detected and localised more easily.

The realised implementation of the large-scale system with cascaded clocks reaches an overall accuracy of 200 µs in an area of several kilometres [GLTK06]. The solution tackles the accuracy at steady-state as well as the impact of transient effects like a coordinated, fast, and jitter-free power-up of the whole network. Figure 2.1 illustrates the network concept for the mentioned application scenario. It is split into two parts: an access network, which is based on Ethernet and the PLC structure to remotely access the domestic supply meters.

#### 2.1.1 Access Network

One important feature of the evaluation hardware that is particularly utilised in the presented use case is the technique for amortisation (see section 5.2.2). The synchronized nodes generate a frame clock for the communication slots on the PLC network. Therefore, it is important that a node in the power-up phase does not mess up the communication. Further, the parameter estimation and lock-in for the power line is rather time consuming. Thus, periodic timers, which are used to generate the frame clock on the PLC network, are compensated for steering values that exceed a certain limit. That way, a fast adjustment of the absolute time can be achieved, while the output frequency for the PLC frame clock can be kept constant.

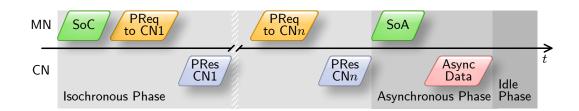

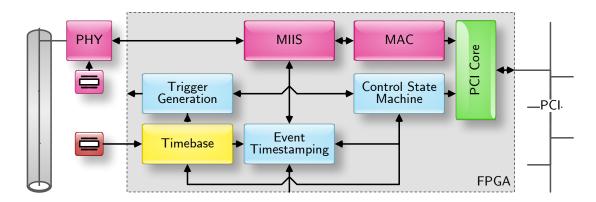

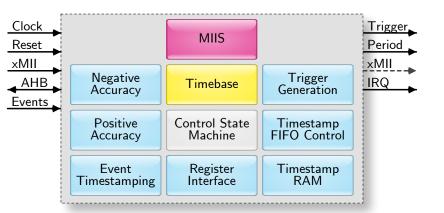

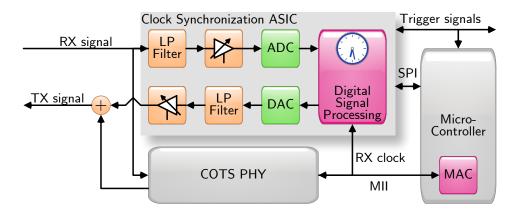

#### 2.1.2 Power Line Network

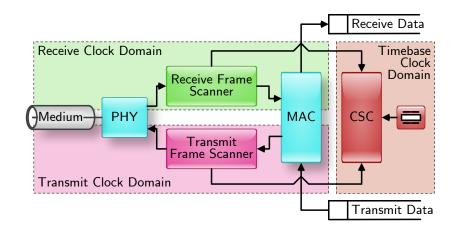

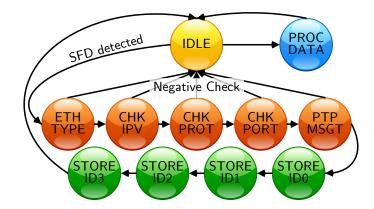

Besides the central embedded processor for handling the (communication) protocols, the PLC physical layer communication is implemented using a separate Application Specific Integrated Circuit (ASIC), which contains a signal processing unit for mixing, filtering, up- and sub-sampling as well as synchronization detection. A Finite State Machine (FSM) controls all operations related to transmitting and receiving data. It implements a master-slave-based, time-slotted communication scheme. In order to detect synchronization events properly, the complete module performs an energy normalised correlation of complex synchronization sequences on the equivalent complex base band. All nodes synchronize on bit-level to the master clock. The slotted communication is established by a configured slot length, regular packets indicating the start of a slot and additional absolute time information.

Since the PLC physical layer communication is handled by a separate, specialised Digital Signal Processor (DSP), only the frame-clock events, which are automatically generated by the state machine for PLC communication, can be detected by other modules of the node. Consequently, these events are timestamped by the synchronization hardware block, the Clock Synchronization Cell (CSC), which also generates timestamps in the Ethernet case. This has the advantage that the format of timestamps is, within the PLC network as well as in the backbone networks, fully compliant to the Institute of Electrical and Electronics Engineers (IEEE) 1588 format. Nevertheless, a clock synchronization using pure IEEE 1588 is not directly applicable to PLC for a number of reasons:

- The communication delay between power line master and slave is compared to the delay in the opposite direction highly asymmetric. IEEE 1588 is not able to deal with that form of delay, since the standardised round-trip delay measurements can only take the mean of both directions into account.

- Secondly, IEEE 1588 is in general not able to synchronize clocks with a high accuracy in networks where the network delay may change at any moment due to changing repeater levels caused by network topology changes (e.g., load balancing in electricity distribution grids).

- Finally, even the relative low number of one synchronization packet per period, sent out by a master to a network with potentially hundreds of nodes can overload the limited bandwidth resources of a power line network. This is due to the interconnection using a shared medium that requires signal repeaters, which further consume time-slots. The available bandwidth therefore decreases with the number of repeater levels.

The issue that the system is in general not capable to provide symmetric communication channels in terms of latency generates issues with the assumptions made by Precision Time Protocol (PTP), which relies on a symmetric channel. Therefore, if PTP is used without adaptations this would result in a non-negligible error. In order to compensate for asymmetric transmission delays on the power line, resulting from delays of the slotted communication scheme, predefined correction values are applied. The message transportation costs from a master are a further issue. Since in power line the upstream communication is disproportional slower than the other direction, the implementation simulates the IEEE 1588 Delay\_Req and Delay\_Resp messages by supplying predefined delays – calculated from the asymmetry factor and the slot delay – to the synchronization stack. The functionality is implemented by a special kernel driver module, which keeps track of the last 15 frame-clock events. Each time a telegram that contains an absolute time information from a master is received, it is matched with the appropriate clock event. This process is based on the repeater level information gathered from the network layer, which also assures that each packet is just received once. Every time a pair of absolute time and corresponding frame-clock event has been assembled it is passed on to the user process calculating the actual clock synchronization algorithm. Consequently, the line delay, which mainly consists of multiple slot delays, can be compensated. Since the accuracy requirements are in the microseconds range, there is no need for compensation of the line delay on the power line. Therefore, a number of transmissions can be saved in favour of user-payload.

The power line synchronization method also takes advantage from the fact that all messages are aligned to the system-wide frame clock as well. Thus, the adaptation layer also uses the occurrence of these messages to generate synchronization events. The drawback that no absolute time is sent with every message, can be tackled with a prediction function of scheduled frame-clock events, which is defined via the communication speed. The arrival of a timing packet containing absolute time information is used to adjust the prediction algorithm.

Tests with an evaluation board equipped with the mentioned embedded processor showed that the performance over four repeater levels – which is assumed to be the required number for a field test – can fulfil the requirements for accurate metering. [GLTK06]

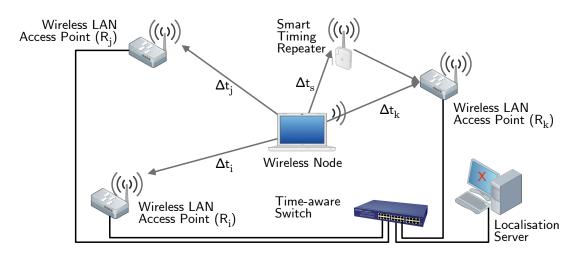

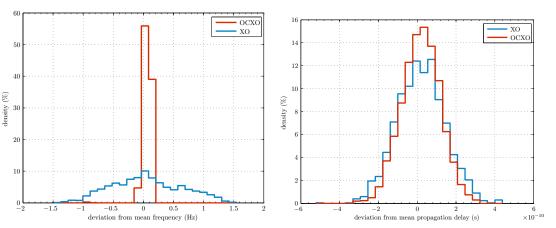

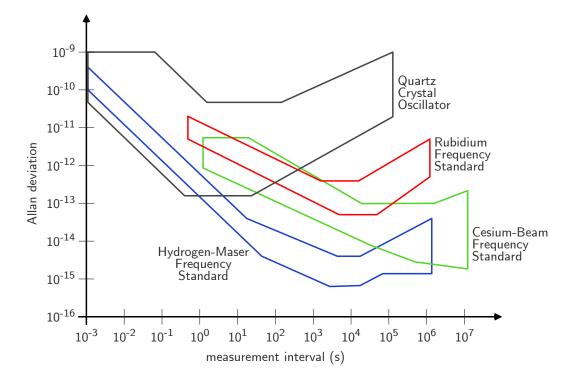

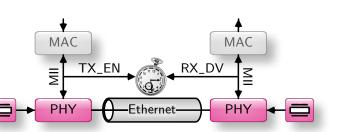

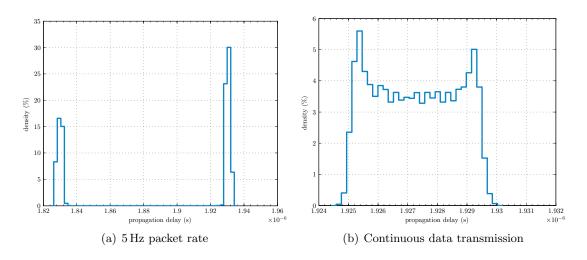

### 2.2 Wireless Position Determination