The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

FAKULTÄT FÜR INFORMATIK

**Faculty of Informatics**

# Hardware Transactional Memory for a Real-Time Chip Multiprocessor

## DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

#### **Technische Informatik**

eingereicht von

#### Peter Hilber

Matrikelnummer 0326179

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung Betreuer: O.Univ.Prof. Dipl.-Ing. Dr.techn. Herbert Grünbacher Mitwirkung: Assoc. Prof. Dipl.-Ing. Dr.techn. Martin Schöberl

Wien, 15.06.2010

(Unterschrift Verfasser)

(Unterschrift Betreuer)

## Erklärung zur Verfassung der Arbeit

Peter Hilber Pfeilgasse 3a/374 A-1080 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Wien, 15.06.2010

## Acknowledgements

I am grateful to my thesis advisors, Prof. Martin Schöberl and Prof. Herbert Grünbacher, for supervising my thesis, for providing advice, and for guiding my research efforts. Earlier work by Martin Schöberl, Florian Brandner and Jan Vitek laid the foundations for my thesis. Martin also provided editorial and technical advice and the used tag memory implementation. I would like to thank Martin for many interesting discussions. I would also like to thank the members of the Real Time Systems Group at the Vienna University of Technology for their constructive feedback. The Department of Computer Engineering at the Vienna University of Technology generously provided the used target hardware. Thanks go to http://www.alteraforum.com user Rysc for sharing a content addressable memory implementation.

I would like to thank my parents, my sisters, my brother and my grandparents for their support during the course of my studies. Special thanks go to Carina for her support while writing this thesis.

## Hardware Transactional Memory for a Real-Time Chip Multiprocessor

#### Abstract

Transactional memory is an alternative to conventional lock-based synchronization. Locks are difficult to use and not composable; transactional memory offers a simple programming model and the high concurrency desired for future multiprocessors. While actually multiple threads concurrently access shared data, the results look as if code sections (transactions) had been executed sequentially. Conflicts among concurrent transactions are automatically resolved.

To our knowledge, there is currently no transactional memory system suitable for hard real-time systems on multiprocessors. *Real-time transactional memory* (RTTM) is a proposal of a time-predictable transactional memory for chip multiprocessors. The main goals of RTTM are a simple programming model and analyzable timing properties. Static analysis detects non-conflicting transactions, which lowers the worst-case execution time bounds. In this master's thesis, RTTM was implemented on an FPGA and the viability of the implementation was evaluated.

For time-predictable execution, RTTM is hardware-based. Each core gets a small, fully associative cache which tracks the memory accesses in a transaction. RTTM was implemented on JOP, a time-predictable chip multiprocessor directly executing Java bytecode. The basic programming interface is the <code>@atomic</code> method annotation. Using Java facilitates link-time transformations and the abort of conflicting transactions.

The FPGA-based implementation supports small transactions suitable for synchronization in embedded real-time applications. Up to 12 cores fit on a low-cost Cyclone II FPGA running at 90 MHz with a device utilization of more than 90%. The RTTM hardware is costly due to the fully associative cache, but does not dominate the hardware resource consumption. The close relationship of the processor to the Java Virtual Machine enables some resource-saving optimizations. A part of RTTM was implemented in software in order to make the integration of the CPU nearly transparent and to lower the hardware costs. As a preparation for tool-based worst-case execution time analysis, the execution time of individual RTTM operations was bounded.

## Hardware Transactional Memory for a Real-Time Chip Multiprocessor

#### Kurzfassung

Transactional Memory (Transaktionaler Speicher) ist eine Alternative zur konventionellen Synchronisation mit Locks. Programmierung mit Locks ist aufwändig, fehlerhaft und nicht *composable*; Transactional Memory bietet ein einfaches Programmiermodell und die hohe Nebenläufigkeit, die für künftige Multiprozessoren benötigt wird. Obwohl mehrere Threads gleichzeitig auf gemeinsame Daten zugreifen, entsprechen die Ergebnisse einer sequentiellen Ausführung von Codeabschnitten (Transaktionen). Konflikte von Transaktionen werden transparent aufgelöst.

Nach meinem Wissen gibt es kein für harte Echtzeitsysteme geeignetes Transactional Memory für Multiprozessoren. *Real-Time Transactional Memory* (RTTM) ist der Entwurf eines echtzeitfähigen Transactional Memories für Chip-Multiprozessoren. Die Entwurfsziele von RTTM sind ein einfaches Programmiermodell und analysierbares Zeitverhalten. Statische Analyse der potentiellen Konflikte von Transaktionen ermöglicht eine Verringerung der Worst-Case Execution Time Bounds. In dieser Diplomarbeit wurde RTTM auf einem FPGA implementiert und die Implementierung evaluiert.

Um echtzeitfähig und performant zu sein, ist RTTM hardware-basiert. Ein jedem Prozessor zugeordneter, vollassoziativer Cache verfolgt die Speicherzugriffe in einer Transaktion. Die Implementierungsplattform ist der echtzeitfähige Chip-Multiprozessor JOP, der Java Bytecode direkt ausführt. Die wesentliche Programmierschnittstelle ist die @atomic Method Annotation. Die Verwendung von Java vereinfacht Codetransformationen zur Link Time und den Abbruch von in Konflikt stehenden Transaktionen.

Die FPGA-basierte Implementierung ermöglicht Transaktionen zur Synchronisation von eingebetteten Echtzeitanwendungen. Auf einem Cyclone II FPGA können bis zu 12 Prozessorkerne laufen, mit einer Taktfrequenz von 90 MHz und einer Nutzung von über 90% der FPGA-Ressourcen. Die RTTM-Hardware ist wegen des vollassoziativen Caches aufwändig, dominiert aber nicht den Ressourcenverbrauch. Die Verwandtschaft von JOP mit der Java Virtual Machine ermöglicht Ressourcen sparende Optimierungen. Ein Teil von RTTM wurde in Software implementiert, um die Integration der CPU zu vereinfachen und den Ressourcenverbrauch zu vermindern. Als Vorbereitung auf eine toolbasierte Worst-Case-Execution-Time-Analyse wurde die maximale Ausführungszeit der einzelnen RTTM-Operationen analysiert.

# Contents

| Acknowledgements ii |          |                                            |      |  |  |

|---------------------|----------|--------------------------------------------|------|--|--|

| At                  | Abstract |                                            |      |  |  |

| Kı                  | ırzfas   | ssung                                      | vii  |  |  |

| Li                  | st of l  | Figures                                    | xiii |  |  |

| Li                  | st of [  | <b>Fables</b>                              | xiii |  |  |

| Li                  | st of l  | Listings                                   | xiv  |  |  |

| 1                   | Intr     | oduction                                   | 1    |  |  |

|                     | 1.1      | Transactional memory                       | 2    |  |  |

|                     | 1.2      | Real-time transactional memory (RTTM)      | 3    |  |  |

|                     | 1.3      | The Java Optimized Processor               | 7    |  |  |

|                     | 1.4      | The SimpCon SoC interconnect               | 8    |  |  |

|                     | 1.5      | Problem statement                          | 8    |  |  |

|                     | 1.6      | Overview                                   | 9    |  |  |

| 2                   | Rela     | ited Work                                  | 11   |  |  |

|                     | 2.1      | Hardware transactional memory              | 11   |  |  |

|                     | 2.2      | Transactional memory for real-time systems | 13   |  |  |

| 3                   | Cha      | racterization of implementation            | 17   |  |  |

|                     | 3.1      | Semantics                                  | 17   |  |  |

|                     | 3.2      | Implementation characteristics             | 22   |  |  |

|                     | 3.3      | Programming interface                      | 23   |  |  |

|                     |          | 3.3.1 Software commands                    | 24   |  |  |

|                     |          | 3.3.2 Diagnostics                          | 25   |  |  |

|                     | 3.4      | Scheduling                                 | 25   |  |  |

| 4 | Imp                      | lementation                                                                                               |   |  |

|---|--------------------------|-----------------------------------------------------------------------------------------------------------|---|--|

|   | 4.1                      | HW/SW-Partitioning                                                                                        | 2 |  |

|   | 4.2                      | Hardware layer                                                                                            | 2 |  |

|   |                          | 4.2.1 The RTTM module                                                                                     | - |  |

|   |                          | 4.2.2 The memory arbiter                                                                                  |   |  |

|   |                          | 4.2.3 Influence of target technology                                                                      |   |  |

|   |                          | 4.2.4 Tag memory implementation                                                                           |   |  |

|   |                          | 4.2.5 Interfaces of the read tag memory and write buffer                                                  |   |  |

|   |                          | 4.2.6 The transaction cache                                                                               |   |  |

|   |                          | 4.2.7 The state machine                                                                                   |   |  |

|   |                          | 4.2.8 Transaction states                                                                                  |   |  |

|   |                          | 4.2.9 Pipelining                                                                                          |   |  |

|   |                          | 4.2.10 Memory access classification                                                                       |   |  |

|   | 4.3                      | 4.2.11 Summary of hardware integration                                                                    |   |  |

|   | 4.3                      | Software layer4.3.1The transaction wrapper4.3.1                                                           |   |  |

|   |                          | 4.3.1       The transaction wrapper         4.3.2       Transaction rollback                              |   |  |

|   |                          | 4.3.2         Transaction forback                                                                         |   |  |

|   |                          | 4.3.4 Summary of runtime system integration                                                               |   |  |

|   | 4.4                      | Link time transformations                                                                                 |   |  |

|   | 5.1<br>5.2<br>5.3        | gramming for RTTM         Recommended programming style         Limitations         Testing and debugging |   |  |

| 6 | Evaluation               |                                                                                                           |   |  |

|   | 6.1                      | Hardware resource consumption and performance                                                             |   |  |

|   | 6.2                      | Worst-case temporal behavior                                                                              |   |  |

|   | 6.3                      | Discussion                                                                                                |   |  |

| 7 | Conclusion               |                                                                                                           |   |  |

|   |                          | Imary of contributions                                                                                    |   |  |

| A | Acronyms                 |                                                                                                           |   |  |

| B | Code Listings            |                                                                                                           |   |  |

| С | Source code availability |                                                                                                           |   |  |

| D | Mea                      | asurements                                                                                                |   |  |

Index

#### Bibliography

85

87

# **List of Figures**

| 1.1  | RTTM overview                                         | 4  |

|------|-------------------------------------------------------|----|

| 1.2  | RTTM commit                                           | 5  |

| 1.3  | JOP chip multiprocessor                               | 9  |

| 4.1  | RTTM implementation layers                            | 28 |

| 4.2  | Conventional JOP CMP components                       | 29 |

| 4.3  | RTTM implementation hardware components               | 29 |

| 4.4  | Interfaces of an RTTM module                          | 30 |

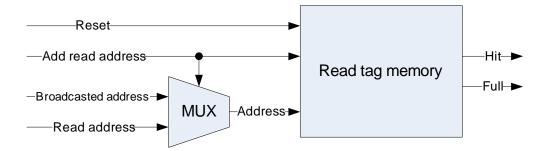

| 4.5  | Read tag memory interface                             | 37 |

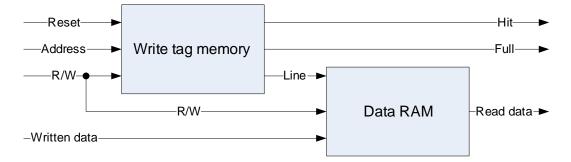

| 4.6  | Write buffer interface                                | 37 |

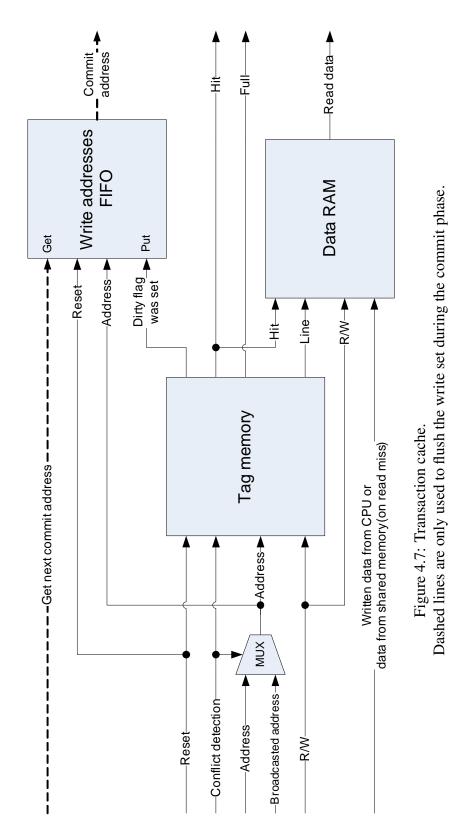

| 4.7  | Transaction cache                                     | 39 |

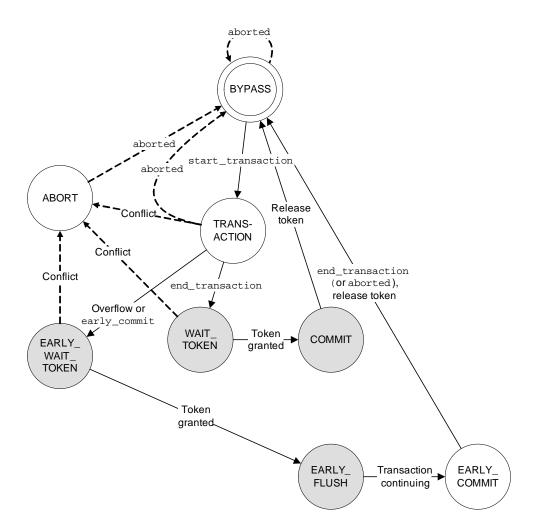

| 4.8  | RTTM module state machine                             | 41 |

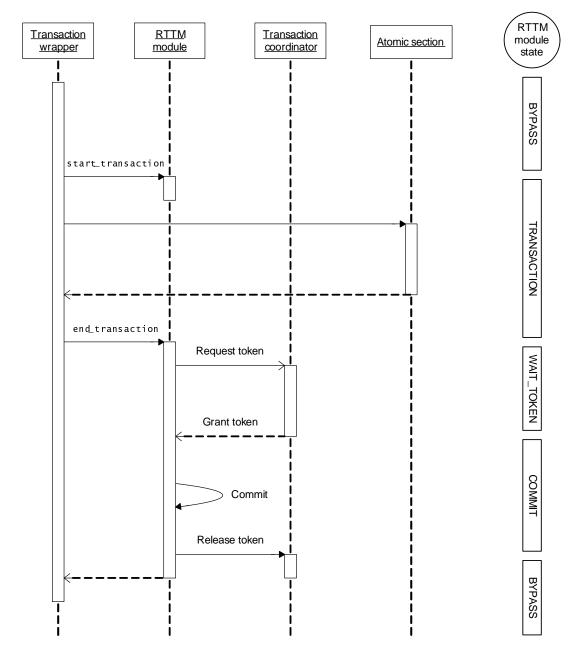

| 4.9  | Sequence diagram of successful transaction            | 42 |

| 4.10 | Interfaces to conventional part of CMP                | 48 |

|      | Zombie bytecode                                       | 54 |

| 6.1  | Components and interfaces affecting temporal behavior | 64 |

# **List of Tables**

| 1.1 | Read set/write set overlaps | 6  |

|-----|-----------------------------|----|

| 3.1 | Glossary of used terms      | 18 |

| 3.2 | Example of data-handoff     | 19 |

| 3.3 | Privatization safety        | 20 |

| 3.4 | Publication safety                                      | 20 |

|-----|---------------------------------------------------------|----|

| 3.5 | Data race during publication                            | 20 |

| 3.6 | Publication in a conditional                            | 21 |

| 4.1 | Hardware commands                                       | 31 |

| 4.2 | SimpCon signals in RTTM implementation                  | 32 |

| 4.3 | Comparison of tag memory variants resource requirements | 37 |

| 4.4 | Transaction cache fields                                | 38 |

| 4.5 | Non-conflicting memory areas                            | 47 |

| 4.6 | Modifications to JOP runtime system                     | 56 |

| 6.1 | Implementation platform reference values                | 62 |

| 6.2 | Scaling with tag memory size                            | 62 |

| 6.3 | Scaling with # of cores                                 | 63 |

| 6.4 | rdy_cnt values during non-transactional write           |    |

# **List of Listings**

| 3.1         | Example of atomic method                       | 23 |

|-------------|------------------------------------------------|----|

| 3.2         | earlyCommit() example                          | 25 |

| 4.1         | Tag memory line encoder with priority          | 35 |

| 4.2         | Tag memory line encoder without priority       | 35 |

| 4.3         | Transaction wrapper for not nested transaction | 51 |

| <b>B</b> .1 | Java code similar to transaction wrapper       | 75 |

| B.2         | Transaction using RTTM hardware interface      | 76 |

| B.3         | Fully associative tags using memory blocks     | 77 |

| D.1         | Script to reproduce measurements               | 83 |

# CHAPTER

## Introduction

Performance of sequential processors has increased exponentially in past decades, but this growth has slowed down in recent years. The gains by heavier use of instruction level parallelism and pipelining are diminishing and complex and fast clocked processors need more power than sustainable [OH05]. Moore's law about the exponential increase of the number of transistors available on an integrated circuit [Moo98] appears to remain valid for the next years, however [LR07].

The past increases in computational power have rendered possible increasingly capable software, and further increases of computational power are highly desirable. *Chip multiprocessing* is seen as a way to continue performance growth by using thread level parallelism. This does however necessitate the parallelization of applications, which is seen as a major problem [OH05]. Parallelization is usually not transparent to the programmer. *Parallel programming* is considered "fundamentally more difficult than sequential programming" [LR07, p. 2]. Concurrency and nondeterminism make it difficult to write parallel programs and reason about them.

In contrast to message passing systems, *shared memory* reduces the need for manual data distribution [KMVR90]. When using task parallelism (as opposed to data parallelism), concurrent threads are then usually coordinated using *lock-based concurrency control* such as semaphores, mutexes and monitors. The employed mechanisms are at a low level of abstraction.

*Abstraction*<sup>1</sup> and *composability*<sup>2</sup> are very important for handling complex systems [Kop08]. Abstraction and composability are extensively used in software engineering. Traditional, lock-based concurrency control does however not compose [Her06, Ch. 18.1].

<sup>&</sup>lt;sup>1</sup>"An *abstraction* is a simplified view of an entity, which captures the features that are essential to understand and manipulate it for a particular purpose." [LR07, p. 3]

<sup>&</sup>lt;sup>2</sup>"*Composition* is the ability to put together two entities to form a larger, more complex entity, which in turn is abstracted into a single, composite entity." [LR07, p. 4]

When manipulating data, it is often necessary to lock multiple exposed objects to guarantee invariants mandated by the application. A classical example is the atomic movement of an item between two data structures. It is necessary to lock both data structures in order to guarantee atomic movement, but this may lead to deadlocks when performing concurrent movements and taking locks in different order.

### **1.1 Transactional memory**

*Transactional memory* (TM) is an alternative to conventional lock-based synchronization. Transactional memory allows a simple and composable programming model and potentially high concurrency. The name stems from analogies to transactions used in database systems. Database transactions have the ACID properties: (failure) atomicity, consistency, isolation and durability [HR83]. In a transactional memory system, a computation executing in a thread is wrapped in a transaction. Such a transaction has *ACI properties* (durability is not needed for in-memory transactions). *Failure atomicity* means that a transaction either fully completes or does not change anything at all. *Consistency* means that a transaction, when starting from a consistent state, will leave the system in a consistent state. Consistency is application dependent and may be represented as invariants on data structures. *Isolation* ensures that each transaction produces correct results regardless of any concurrently executing transactions [LR07].

The ACI properties make programming parallel systems easier: the results of transactions look as if they had been executed one after the other, while actually they might have been executing concurrently. For example, efficient parallel read and write access to a FIFO queue is difficult with locks because there can be contention when the queue has fewer than two elements [MS96]. When using transactional memory, such a parallel data structure is a non-issue. Ideally, a programmer only needs to mark code blocks which are to be executed atomically. When using other synchronization mechanisms, one has to specify explicitly which shared data is accessed, except when using coarse grain locking such as a single global lock. The semantics of transactional memory is however not fully specified by the ACI properties, since the interaction of transactional and non-transactional code is not defined [LR07]. There is not yet a consensus how the semantics of transactional memory should be described and how strong such semantics should be [MBS<sup>+</sup>08, Boe09, Luc08, SDMS08]. An often proposed semantics is *single* global lock atomicity [MBS+08], where transactions behave as if each was encompassed by a reentrant single global lock. Transactional memory systems differ in the semantics they provide as well as in their implementation.

In a TM system, a transaction can end with either a *commit* or an *abort*. A commit makes all changes of a transaction visible outside of the transaction, while an aborted transaction has no visible effects. Transactional memory systems are usually a form of optimistic concurrency control and execute multiple transactions in parallel. In case of

conflicting accesses to shared resources, some of the involved transactions are aborted and possibly restarted. There are different strategies how to save the *tentative updates* of a transaction and how to *detect conflicts* among transactions. For hardware-based TM implementations (hardware transactional memory, HTM), updates are commonly buffered in a CPU-local write buffer. If a transaction is aborted, the TM system undoes any visible changes. For a HTM, this includes changes to the program counter, the register file etc. HTM implementations usually detect conflicts by recording the *read set* and *write set*, which represent the memory addresses read resp. written during a transaction. Conflict detection often does not preclude some false positives (e.g. if the granularity of conflict detection is a cache line). The time at which conflicts are detected can also vary, since it might not be feasible to detect a conflict detection. A more comprehensive introduction to transactional memory can be found in [LR07].

Transactional memory was first proposed by Herlihy and Moss as a hardware extension to cache coherency protocols [HM93]. There have been many hardware based transactional memory system proposals since then (e.g. [HWC<sup>+</sup>04, MBM<sup>+</sup>06, KHR<sup>+</sup>08, BHHR]). However, transactional memory has not been implemented in available commercial microprocessors yet.<sup>3</sup> As an alternative approach, *software transactional memory* (STM) systems have been proposed, beginning with [ST95]. STM designates transactional memory systems implemented in software. STM systems have the benefit of running on off-the-shelf hardware. STM implementations are also more flexible, which is an advantage given the missing experience with transactional memory [LR07, GZU<sup>+</sup>09]. Hardware transactional memory (HTM) systems, i.e. systems with only a moderate software component, usually also have some intrinsic limitations due to fixed-size hardware structures and therefore cannot efficiently support transactions with a large read set and write set. Hybrid TM systems combine hardware and software implementation [DFL<sup>+</sup>06, Lie04].

#### **1.2 Real-time transactional memory (RTTM)**

*Real-time transactional memory* (RTTM) is a proposal of a time-predictable transactional memory by Martin Schoeberl, Florian Brandner and Jan Vitek [SBV10b]. RTTM targets chip multiprocessors with a shared memory. It is to our knowledge the first transactional memory system intended for real-time systems with hard deadlines running on multiprocessors. Other work on transactional memory for real-time systems is discussed in Section 2.2. The main design goals of RTTM are a simple programming model and analyzable timing properties. Design decisions were taken considering their impact on the worst-case execution time (WCET) estimates. High average case throughput is not a goal of RTTM.

<sup>&</sup>lt;sup>3</sup>Sun's Rock processor has limited support for transactional memory.

RTTM transactions are small, i.e. they only have a small read set and write set. RTTM assumes that there are many pairs of transactions which do not conflict with each other. Static program analysis of conflicts among transactions is then used to provide competitive WCET estimates. A discussion of transactional memory variants related to RTTM is in Chapter 2.

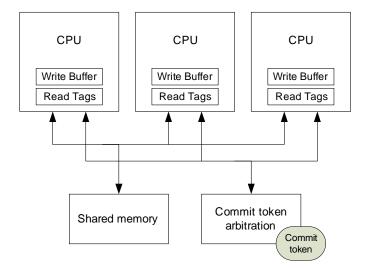

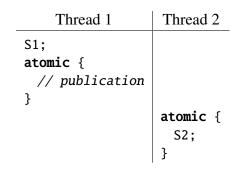

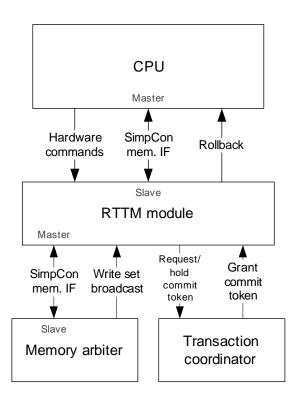

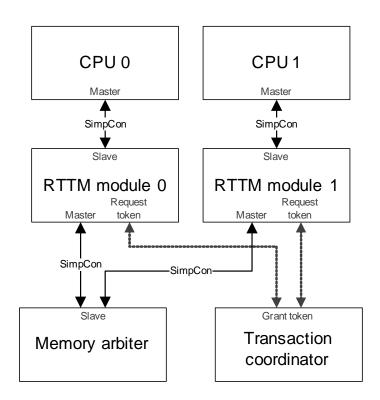

Figure 1.1: RTTM components

RTTM is a hardware-based transactional memory system. It assumes a chip multiprocessor (CMP) with a global shared memory. Each CPU of the CMP is equipped with its own *write buffer* and *read tag memory* (cf. Figure 1.1). The write buffer contains the memory addresses and data written by the corresponding CPU during a transaction (i.e. the write set of a transaction). The read tag memory contains the memory addresses read by the CPU during a transaction (i.e. the read set of a transaction). During a transaction, all writes to the shared memory are buffered in the write buffer.

For time-predictable and efficient memory accesses, the write buffer and read tag memory need to be realized in hardware. To avoid false conflicts, accesses are logged at the data word level. The caches implementing the write buffer and read tag memory are fully associative to avoid unpredictable cache usage. Since fully associative caches are expensive in terms of hardware consumption [Hyd03, Ch. 11.4.2], their size and therefore the read set and write set size are limited. The implications of this restricted size for programmers are discussed in Chapter 5 and [SBV10b].

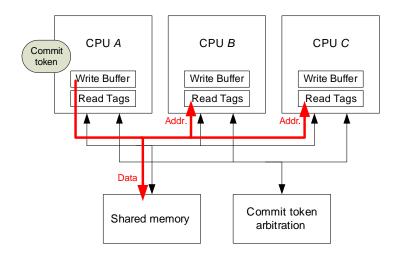

**Commit** During a commit, which happens at the end of a transaction, the contents of the write buffer are written to the shared memory. The addresses being written to the shared memory are also broadcasted to all other CPUs (somewhat similar to bus snooping). This is depicted in Figure 1.2 on the next page. Before committing, a CPU  $\mathcal{A}$

has to acquire the single *commit token*. During the commit,  $\mathcal{A}$  holds the commit token. During  $\mathcal{A}$ 's commit, all other CPUs which are currently executing a transaction compare the addresses being written and broadcasted by  $\mathcal{A}$  to the addresses they have read so far, i.e. their read tag memory. A match on another CPU  $\mathcal{B}$  indicates an overlap of  $\mathcal{B}$ 's read set with the write set of  $\mathcal{A}$ . Any conflict between transactions will lead to such a match in one of the transactions. On a match,  $\mathcal{B}$  will abort its transaction.

Figure 1.2: RTTM commit

**Early commits** The situation that the write set resp. read set of a transaction is bigger than the capacity of the write buffer resp. the read tag memory should be avoided by static program analysis. In the exceptional case that such an *overflow* occurs, an *early commit* is done: The CPU will attempt to acquire the commit token. If the CPU succeeds in acquiring the commit token, it will hold the token while continuing the transaction and broadcasting any addresses written during the transaction. The early commit phase stretches until the end of the transaction.

After the commit token has been acquired by a transaction t, no other, possibly non-conflicting, transaction will be able to commit until t has ended. Parallelism is therefore crippled by an early commit, which should however not happen frequently during normal operation. Early commits may also be used to execute I/O operations during a transaction, which usually cannot be rolled back.

From the point of view of other CPUs, there are few differences between a transaction performing a commit and one performing an early commit (disregarding temporal behavior). In both cases the commit token is held and there are writes to the shared memory and corresponding broadcasts. **Conflict detection** In RTTM, conflicts are violations of the serialization of memory accesses implied by the commit order. All conflicts among concurrent transactions are detected as overlaps of the write set of some committing transaction t and the read set of another still running transaction. The conflicts are detected during t's commit. Possible overlaps of the read set and write set are depicted in Table 1.1. Two transactions  $t_1$  and  $t_2$ , where  $t_1$  commits first, are conflicting iff  $t_2$  read an address from the shared memory before  $t_1$  wrote to it.<sup>4</sup> In all other cases, the serialization is already implied by the commit order.

| Committing transaction $(t_1)$ | Running transaction $(t_2)$ | Corresponding<br>data hazard | Conflict resolution           |

|--------------------------------|-----------------------------|------------------------------|-------------------------------|

| Read                           | Read                        |                              | No conflict                   |

| Write                          | Write                       | Write-After-Write            | No conflict (order respected) |

| Write                          | Read                        | Read-After-Write             | Rollback of running trans.    |

| Read                           | Write                       | Write-After-Read             | No conflict (order respected) |

Table 1.1: Read set/write set overlaps

As a kind of *late conflict detection*, this can be implemented efficiently in hardware, as only a single (committing) CPU broadcasts to the other CPUs at the same time. (By contrast, *early conflict detection*, where writes to the write buffer are immediately broadcasted, requires *n* CPUs to listen to the n-1 other CPUs.) Early and late conflict detection lead to a similar WCET. When a conflict is detected, the committing transaction wins and the other transaction performs a *rollback* and a subsequent *retry* of the transaction.

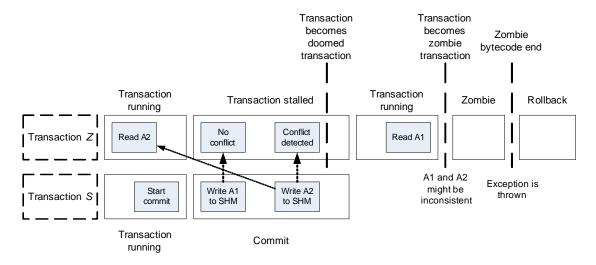

In RTTM, a (failing) transaction may see inconsistent data if it read memory modified by a conflicting, committing transaction. Similar to [DS07, p. 4], we define a *zombie transaction* as "a transaction that is still running after having read an inconsistent view of global data".<sup>5</sup> In general, zombie transactions may behave incorrectly. Incorrect behavior may include – depending on the implementation characteristics – invalid memory accesses, exceptions, infinite loops or infinite recursions [LR07, Section 2.3.5]. An RTTM implementation must therefore provide *zombie containment* until the conflict was detected and the transaction was aborted. The global state – in particular the shared memory – will not be influenced by a zombie transaction.

**WCET analysis** The basic programming model of RTTM is the definition of atomic sections. Source code blocks marked with an **@atomic** annotation are executed in a

<sup>&</sup>lt;sup>4</sup>A transaction performing an early commit may write multiple times to the same address in the shared memory, in which case the time of the last write is relevant.

<sup>&</sup>lt;sup>5</sup>In the RTTM paper [SBV10b], the term *zombie transaction* has a slightly different meaning. It refers to "transactions that are marked as aborted, but continue to run their transaction".

transaction. Because of the limited size of the read set and write set, (tool-based) static analysis should be employed to assure that no overflows occur. If all transactions are executed as part of a periodic task, WCET analysis is possible [SBV10b]. The number of transaction retries in the worst case depends on the number of conflicting transactions. Under the simplifying assumption of the same WCET for all transactions, the maximum number of retries of a transaction is one less than the number of conflicting transactions. More complex sets of transactions lead to pessimistic but safe bounds. Static analysis should also be used to detect which transactions are not conflicting. In the RTTM paper [SBV10b], static analysis is discussed and considered viable.

#### **1.3 The Java Optimized Processor**

The *Java Optimized Processor* (JOP) [Sch05, Sch08] developed by Schoeberl is the prototype implementation platform for RTTM. JOP is a hardware implementation of the *Java Virtual Machine* (JVM) [LY99]. This means it executes Java *bytecodes*<sup>6</sup> directly, rather than interpreting or dynamically translating them. JOP is targeted at real-time systems and aims therefore to provide WCET bounds as low as possible. It is a simple design suitable for embedded systems. The hardware architecture of JOP strives for low resource requirements and low WCET bounds. Common case optimizations such as branch prediction or a conventional data cache have been omitted.

The processor is optimized towards the Java Virtual Machine specification [LY99] and the bytecode instruction set. As the JVM is a CISC (complex instruction set computer), the bytecodes are internally mapped to sequences of simple microcode instructions. Simple bytecodes (e.g. integer addition) are mapped to single microcode instructions. Bytecodes of greater complexity (e.g. field access) are translated to microcode sequences. Very complex bytecodes (e.g. object creation) are implemented in a subset of Java.<sup>7</sup> These mechanisms enable JOP, which is itself a RISC (reduced instruction set computer), to implement a complex instruction set.

As the JVM instruction set is stack-based, an efficient implementation of the stack is important for a hardware implementation. A JOP microcode instruction accesses at most the top two stack elements and a single further stack element. Therefore JOP uses registers for the top two stack elements and an on-chip RAM for deeper positions [Sch09, Section "The Stack Cache"]. The strong guarantees of the JVM also make a special form of an instruction cache feasible: a *method cache* holds entire methods, so that an instruction cache miss may only occur on an invocation or return from a method. This facilitates WCET analysis.

JOP provides a base to implement the *Connected Limited Device Configuration* (CLDC) [Sun03] subset of Java. The JOP runtime system provides a real-time profile

<sup>&</sup>lt;sup>6</sup>The instruction set of the Java Virtual Machine and other virtual machines is denoted as *bytecode*.

<sup>&</sup>lt;sup>7</sup>This subset of Java gets translated into other bytecodes.

similar to Safety Critical Java [HHL+09].8

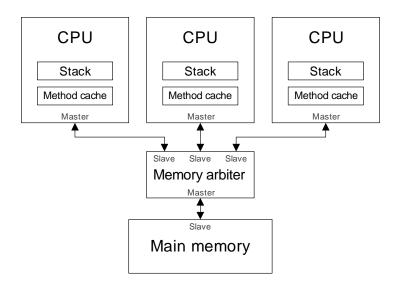

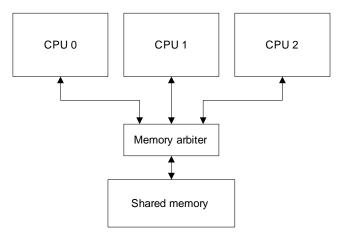

Pitter has developed a chip multiprocessor version of JOP providing a shared memory [Pit09]. A priority based preemptive scheduler is provided, with a timer interrupt used for scheduling. A *memory arbiter* provides the JOP cores with access to the shared main memory. Several arbitration strategies have been analyzed. When using a time division multiple access (TDMA) based memory arbitration strategy, WCET analysis is possible.

FPGA-based systems are considered a "viable platform for CMP research" [WCN<sup>+</sup>07]. JOP runs on several low-cost FPGAs and is easy to adapt. This and several other features – related to the implementation and discussed in Section 6.3 – make JOP an appropriate platform for an implementation of RTTM.

### **1.4 The SimpCon SoC interconnect**

The *SimpCon* interconnection standard [Sch07] is used in JOP to connect modules (e.g. coprocessors) and peripherals (e.g. a memory controller). SimpCon is designed for on-chip interconnections of system-on-chip (SoC) components and is fully synchronous.

SimpCon specifies a point-to-point master-slave connection. The slave informs the master using a *ready counter* signal (rdy\_cnt) how many cycles are at most left to finish a read or write access (possibly an unbounded number). Through this, SimpCon supports pipelining of read and write operations. The ready counter is used for an early restart of the pipeline in the master. Different levels of pipelining are possible.

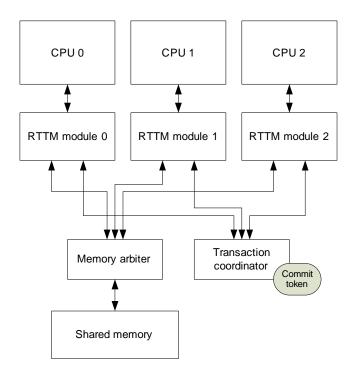

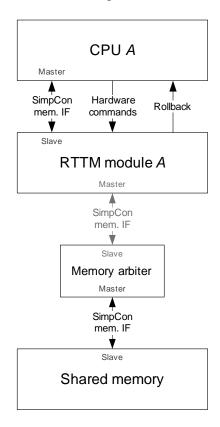

In the uniprocessor JOP, the CPU and memory controller communicate using the SimpCon standard (with the CPU acting as master). In the CMP version, each CPU is individually connected to the memory arbiter. The arbiter is in turn connected as SimpCon master to the memory controller. This is depicted in Figure 1.3 on the next page. The arbiter forwards reads and writes from the CPUs to the memory controller according to the arbitration strategy. In the RTTM implementation, the RTTM specific hardware is inserted by redirecting the SimpCon interconnects between each CPU and the memory arbiter.

#### **1.5 Problem statement**

To our knowledge, no transactional memory system for multiprocessors has been considered for use in hard real-time systems. Transactional memories for real-time systems will be discussed in Section 2.2. RTTM is a proposal of a time-predictable hardware TM for chip multiprocessors. The basic RTTM functionality has been simulated in a behavioral

<sup>&</sup>lt;sup>8</sup>Safety Critical Java is JSR (Java Specification Request) 302, http://jcp.org/en/jsr/detail? id=302.

<sup>&</sup>lt;sup>9</sup>Figure adapted from [Pit09].

Figure 1.3: JOP chip multiprocessor. The connections use the SimpCon interconnect standard. The stack and the method cache are CPU-internal.<sup>9</sup>

level simulation of the JOP CMP [SBV10b, Muc09]. These simulations have indicated that the read set and write set size is small when using appropriate programming styles.

The objective of this master's thesis is the first implementation of RTTM and the evaluation of its viability. Given the high costs for a fully associative tag memory (and the limited capacity of the target, a low-cost FPGA), the resource consumption is of critical importance. Since a main goal of RTTM is a simpler programming model for parallel systems, the semantics and the limitations of transactional code are also of interest. As the RTTM proposal targets hard real-time systems, all operations in the implementation should have analyzable execution time bounds. A full, tool-based WCET analysis is considered future work.

#### **1.6** Overview

The remainder of this thesis is organized as follows: Chapter 2 discusses related transactional memory systems and compares them to RTTM. Chapter 3 describes the semantics, the programming interface and other characteristics of the implementation. Chapter 4 describes the implementation and justifies implementation decisions. Chapter 5 gives some advice on programming using RTTM. Chapter 6 evaluates the resource consumption and performance of the implementation and RTTM in general, where possible. Chapter 7 concludes and gives an overview of the directions of future work.

# CHAPTER 2

## **Related Work**

### 2.1 Hardware transactional memory

First, we describe some hardware transactional memory systems which are related to RTTM. None have been considered for use in real-time systems.

#### An architecture for mostly functional languages

Knight [Kni86] describes a hardware system which speculatively parallelizes *sequential* code written in a functional language on a multiprocessor. It is credited with being the first paper "to use caches and cache coherence to maintain ordering among speculatively parallelized regions of a sequential code in the presence of unknown memory dependences" [LR07, Ch. 4.3.2].

The hardware organization bears similarities to many later HTM systems, including RTTM. The functionality of the *depends cache* and the *confirm cache* roughly corresponds to that of the *read tag memory* and *write buffer*, respectively. Cache coherency is maintained by the depends cache observing values written by other processors and dropping incorrect speculation. An important difference to later transactional memory proposals is that transactions are always committed in the order of the sequential code regions.

#### **Transactional memory**

*Transactional memory: Architectural support for lock-free data structures* [HM93] coined the term *transactional memory.* The paper proposed an extension of a MESI-style<sup>1</sup> cache coherence protocol ([Goo83]) to detect conflicts among transactions. New

<sup>&</sup>lt;sup>1</sup>MESI stands for the possible cache line states: modified, exclusive, shared, invalid.

instructions for transactional loads and stores are introduced. A small *transactional cache* tracks memory accesses and buffers stores. The transactional cache has, in addition to a MESI state, a special cache line state. Both the original and the tentative value are stored in the cache and are dropped on a commit or abort, respectively. Conflicts are detected on their occurrence. Commit and abort are CPU-local operations, i.e. they produce no cache coherency traffic or memory traffic. The proposal requires explicit validation to detect conflicts and allows inconsistent reads. In our understanding (and as suggested in [LR07, Ch. 4.3.5]), an asynchronous abort on a detected conflict would also have been possible. In the described implementation, a transaction is aborted when it performs a conflicting write (when it tries to revoke access from another transaction). The implementation does not guarantee forward progress, but relies on software-level adaptive backoff instead. Due to cache coherency mechanisms, non-transactional memory accesses could also be executed as if each was a transaction.

Similar to RTTM, the transactional cache is fully associative. On an overflow, a transaction is aborted (unless a larger transactional cache is emulated by software). The size of transactions is therefore limited.

#### **Transactional Memory Coherence and Consistency**

*Transactional Memory Coherence and Consistency* (TCC) is a hardware transactional memory system [HWC<sup>+</sup>04]. All code is executed in atomic transactions. TCC supports both optimistic synchronization of parallel programs and speculative parallelization of sequential programs. While MESI-style cache coherency protocols need to support updates of small cache lines with low latency, TCC replaces this hardware by a high bandwidth broadcast bus used to commit transactions by reporting the transactions' write set. The aim of TCC is to combine the simpler hardware used for and the implicit synchronization provided by message passing systems and the easier programming model offered by shared memory systems without relaxed consistency.

TCC and RTTM have a similar mechanism to guarantee atomicity and isolation of transactions. Writes are buffered locally and the read set is tracked through the cache. To commit, a processor tries to obtain the global commit token and, if successful, broadcasts the write set of the transaction to all other processors over a high bandwidth bus. These bandwidth requirements limit the scaling of TCC. The broadcast may also include the modified data, so that caches can be updated directly. However, this requires a higher broadcast bandwidth [HWC<sup>+</sup>04]. Conflict detection is similar to RTTM: If another processor detects an overlap of the broadcasted write set with its read set, it will perform a rollback.

When using TCC, the programmer inserts *transaction boundaries* into the code. The only requirement for error-free execution in the value domain is that "transaction breaks should never be inserted during the code between a load and any subsequent store of a shared value (i.e. during a conventional lock's critical region)" [HWC<sup>+</sup>04]. Other

inappropriate choices of transaction boundaries may however lead to frequent rollbacks and degraded performance. In general, transactions should be large, as long as conflicts are not frequent and the read set and write set do not become too big. When choosing transaction boundaries, it is possible to trade off development effort and performance. Transaction boundaries may also be inserted automatically. To preserve partial atomicity in this case, the programmer needs to mark sections where no boundary may be inserted.

Optionally, transactions may be ordered by assigning *phase numbers* to them. A transaction may only commit once all transactions with older phase numbers have been committed. If used, phase numbers are included in the broadcasts. Phase numbers may be used to avoid starvation of long transactions.

While it bears many similarities to RTTM, TCC is not geared towards time predictability. While RTTM expects the programmer to use small atomic sections for synchronization only, TCC executes all code in transactions. TCC hereby also avoids issues in the interaction of transactional and non-transactional code.

In simulations of a range of server applications adapted for TCC, the read set size and write set size was determined to be in the order of 6-12 KiB resp. 4-8 KiB for almost all transactions *with 64 Byte cache lines*.<sup>2</sup> There were a number of transactions and benchmarks with higher demands, however. Due to the need for fully associative tags, RTTM only supports smaller read sets and write sets. When using RTTM, the programmer only marks small code sections as transactional. In the real-time domain, the read set and write set size is also expected to be smaller [SBV10b]. While TCC's conflict detection has cache line granularity, RTTM has data word granularity to avoid false positives. In a TCC implementation, caches are likely not fully associative, but a victim buffer is used instead [MCC<sup>+</sup>05]. Similar to RTTM, an overflow will trigger an early commit, which limits parallelism. In RTTM, an early commit should be excluded by performing static analysis of the read set size and write set size.

Interestingly, there is also an FPGA-based prototype implementation of TCC (using a high-performance multi-FPGA board) [WCN<sup>+</sup>07]. This was the "first FPGA-based framework for research on CMPs with hardware support for transactional memory" [WCN<sup>+</sup>07]. The prototype is intended as a replacement of slow simulation; some FPGA-specific implementation issues are reported. We will briefly discuss similarities and differences of the implementations in Section 4.2.3 and Section 4.2.4.

#### 2.2 Transactional memory for real-time systems

To our knowledge, transactional memory implementations which are considered suitable for real-time systems have so far been limited to software transactional memory. These transactional memory implementations are restricted to single core processors, with the exception of [SQV09], which targets soft real-time systems. According to

<sup>&</sup>lt;sup>2</sup>We did not find data on how many words were actually changed.

[SQV09], "most of [the] existing solutions for real-time scheduling consider either tasks in multiprocessor systems or transactions in database systems, but not both together".

#### Preemptible Atomic Regions for Real-time Java

*Preemptible Atomic Regions* (PARs) [MBC<sup>+</sup>05] is a concurrency control abstraction for real-time systems. In order to minimize blocking time, PARs can be preempted by higher priority tasks. On preemption, the effects of a PAR are undone. PARs are a restricted form of software transactional memory. The original PAR design is for uniprocessors only. PARs were motivated by the possibility of interference between the non-real-time and real-time code in an RTSJ (*Real-time Specification for Java* [GB00]) environment. The authors report that, depending on semantics, programs can run faster and experience less jitter when using PARs instead of locks.

Since PAR is for uniprocessors, code within a PAR can update memory in place. On each write, address and original contents of the written location are also recorded in an *undo buffer* (undo log). A commit only resets a pointer to the undo buffer. When a PAR is aborted due to preemption, the original contents recorded in the undo buffer are restored in reverse order. Similar to RTTM, it is assumed that there are a limited number of writes in a PAR. While the undo buffer is maintained in ordinary memory, it must be small enough for a quick rollback on preemption. Since a PAR is aborted on every context switch, at most one PAR is aborted on a context switch. The worst-case blocking time is determined by the maximum number of writes performed in a PAR.

PARs avoid several issues of lock-based mutual exclusion: deadlocks, violation of isolation due to programmer errors and lock acquisition overhead. PARs also compose easier than locks and might require fewer context switches.

Similar to the RTTM implementation, the basic programming interface is a method annotation. PARs are an STM variant for uniprocessors, while RTTM is an HTM system for CMPs. While PARs were devised to minimize blocking time for higher priority tasks, there is no notion of priority in RTTM.

Inside a PAR, duplicate methods which maintain the undo buffer through additional instructions are invoked instead of the original methods. The PAR implementation does also target a real-time Java Virtual Machine. Similar to the RTTM implementation, the PAR implementation uses the exception mechanism of Java to abort a PAR and does not track writes to local variables. Some issues were encountered when integrating the PAR semantics into the (virtual) machine. Some modifications of the virtual machine kernel state should not be undone when aborting a PAR. Virtual machine kernel code is therefore compiled without logging. The exception handling mechanism was modified to specially treat exceptions aborting a transaction. Other integration issues are also described in the paper. Similar to RTTM, there are restrictions to the code executed in PARs. On an undo buffer overflow, interrupts are disabled, which is similar to an early commit.

#### 2.2. TRANSACTIONAL MEMORY FOR REAL-TIME SYSTEMS

#### Other related real-time capable work

*Real-Time Support for Software Transactional Memory* (RT-STM) [SQV09] is, to our knowledge, the only transactional memory system besides RTTM where concurrent real-time transactions run on a multicore. The paper focuses on the scheduling of these transactions. While RTTM strives to guarantee deadline compliance, RT-STM reduces the number of deadline violations of soft real-time transactions. The paper formalizes real-time transactions and introduces a deadline-based real-time scheduler. Existing STMs are adapted and the performance with different real-time scheduling policies is compared.

Supporting lock-free synchronization in Pfair-scheduled real-time systems [HA06] bounds the number of retries when using lock-free synchronization on multiprocessor systems using *proportionate fairness* real-time scheduling. Such lock-free operations are however not intended as a replacement for locking synchronization. Instead they should allow more efficient implementation of simple data structures, such as queues. Assumptions regarding the behavior of the lock-free algorithms are also made for the analysis: when a lock-free operation is retried and how long the operation takes at most.

*Response time analysis of software transactional memory-based distributed real-time systems* [FRJ09] considers distributed systems where each node executes separated STMs. An algorithm to bound the response time is presented. There is also work on real-time database transactions (e.g. [ARMJ97]) and lock-free data structures for real-time systems (e.g. [HA06], [ARJ97]).

# CHAPTER 3

## **Characterization of implementation**

Transactional memory systems differ greatly both in their semantics and in their implementation [LR07, Ch. 2]. In the following, we will describe the semantics, the programming interface and the implementation characteristics of the RTTM prototype implementation developed as part of this thesis. The paper proposing RTTM [SBV10b], as presented in Section 1.2, does not specify details of the behavior and leaves some decisions to the implementation.

Table 3.1 on the following page explains some terms used in the following which were not introduced yet. With respect to other terminology, the thesis follows [LR07].

#### **3.1** Semantics

RTTM transactions satisfy the ACI semantics – failure atomicity, consistency and isolation – that is the key property of transactional memory systems [LR07, Ch. 1]. ACI semantics have been introduced in Section 1.1. In Section 1.2, esp. page 5, I have argued that RTTM satisfies these properties. Atomicity is fulfilled because each transaction performs its changes only in a non-interruptible step (during the commit/early commit), if at all. Isolation is fulfilled because there is only a single commit token passed in the serialization order of transactions. In the current implementation, transactions have *exactly-once semantics* (and not at-most-once semantics). In the temporal domain, the number of retries of a transaction is bounded by the number of conflicting transactions (see page 6).

If a program is *segregated*, i.e. "all mutable shared memory locations are accessed either exclusively inside or exclusively outside a transaction" [MBS<sup>+</sup>08], there are no problems with the interaction of transactional and non-transactional code [MBS<sup>+</sup>08]. If

| Term                                                 | Definition                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Commit/Committing<br>transaction                     | From the point of view of other CPUs, there are few dif-<br>ferences between a committing and an early committing<br>transaction (disregarding temporal behavior). In both cases<br>the commit token is held and there are writes to the shared<br>memory and corresponding broadcasts.<br>Therefore the term commit resp. committing transaction |

| Preceding transaction                                | also refers to an early commit resp. early committing trans-<br>actions, unless otherwise noted.<br>All successful transactions are totally ordered by the order in<br>which they acquire the single commit token. A transaction<br>$t_2$ is <i>preceded</i> by another transaction $t_1$ iff $t_2$ has not yet                                   |

| Succeeding                                           | acquired the commit token when $t_1$ does.<br>A transaction $t_2$ succeeds another transaction $t_1$ iff $t_2$ acquires                                                                                                                                                                                                                           |

| transaction                                          | the commit token after $t_1$ .                                                                                                                                                                                                                                                                                                                    |

| Nested transaction                                   | Any transaction which is executed as part of another trans-<br>action.                                                                                                                                                                                                                                                                            |

| Doomed transaction                                   | A transaction $t_d$ which is conflicting with a <i>preceding trans-</i><br><i>action</i> $t_1$ (i.e. $t_d$ read from an address which will be broad-<br>casted by $t_1$ ). $t_d$ will fail (at the latest) during $t_1$ 's commit.                                                                                                                |

| <i>Current</i> write set/<br><i>Current</i> read set | The shared memory addresses written/read by a transaction<br>until a certain point in time.                                                                                                                                                                                                                                                       |

|                                                      |                                                                                                                                                                                                                                                                                                                                                   |

Table 3.1: Glossary of used terms

a program is not segregated, the semantics are more involved. In the following, we will discuss the semantics w.r.t. the interaction of transactional and non-transactional code.

RTTM implements the write  $\xrightarrow{hb}$  read model presented in [GMP06, Section 3.3]. In this model, the happens-before (hb) relationship between transactions only contains happensbefore edges from transactions writing a certain memory location to transactions reading a certain memory location. In RTTM, all transactional reads and writes satisfy the happensbefore relation, as illustrated in Table 1.1 on page 6. The write  $\xrightarrow{hb}$  read model supports the data handoff idiom outlined in Table 3.2 on the facing page. The RTTM model does also support a number of interactions between transactional and non-transactional code which are not supported by the write  $\xrightarrow{hb}$  read model [GMP06, Section 3.4].

Transactional memory systems are said to provide *strong isolation* if each access during non-transactional execution does behave as if the access was executed in an individual transaction [LR07]. Many software TM systems do not provide strong isolation, since it apparently has high overheads [SMDS07]. RTTM also does not provide

| Initially, ready = <b>false</b> |                                                                  |  |

|---------------------------------|------------------------------------------------------------------|--|

| Thread 1                        | Thread 2                                                         |  |

| data = 42;<br><b>atomic</b> {   |                                                                  |  |

| ready = <b>true</b> ;<br>}      | <pre>atomic {    tmp = ready; } if (tmp) {    r1 = data; }</pre> |  |

Table 3.2: Example of *data-handoff* from [GMP06]. tmp == true  $\Rightarrow$  r1 == 42

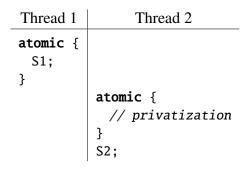

strong isolation. *Weak isolation* only isolates transactions from each other. In the case of weak isolation, one could demand that transactional and non-transactional accesses to a memory location must not overlap in time [SMDS07]. This requirement implies a partition into *shared* objects and objects *private* to some thread at any point in time [SMDS07]. A transaction may conduct *privatization* of an object *O* by modifying the shared data such that *O* will not be accessed by any subsequent transactions (e.g. remove an item from a linked list). This may however lead to *privatization problems*, which occur in some software TM systems [SMDS07]. In [MBS<sup>+</sup>08, Section 3], *privatization safety* is defined as the requirement "that an STM must respect a happens-before ordering relation from a transactional access S1 to a conflicting non-transactional access S2".<sup>1</sup> In the case of RTTM, the happens-before ordering relation is established by a transaction in the same task as S2 (preceding S2). This is depicted in Table 3.3 on the next page. RTTM provides privatization safety.<sup>2</sup>

*Publication safety* is defined as the requirement "that an STM must respect a happensbefore ordering relation from a non-transactional access S1 to a conflicting transactional access S2" [MBS<sup>+</sup>08]. In RTTM, the happens-before ordering relation is established by a transaction in the same task as S1 (following S1). This is depicted in Table 3.4 on the following page. Publication safety is not supported by RTTM, since data races can occur (see the example in Table 3.5 on the next page).

We think that RTTM also implements *encounter-time lock atomicity* [MBS<sup>+</sup>08, Section 7]. In a "semantically equivalent lock-based [execution] where each transaction is protected by some minimal set of locks such that two transactions share a common lock if and only if they conflict", these locks are acquired "at any point before the

<sup>&</sup>lt;sup>1</sup>In this context, *conflicting* means that the transactional and non-transactional access go to the same memory location.

<sup>&</sup>lt;sup>2</sup>RTTM is not affected by privatization problems, since it uses deferred updates and a single commit token. The use of a single commit token implies *commit linearization*, which provides privatization safety [MBS<sup>+</sup>08, Section 4.1.2].

Table 3.3: Privatization safety (from [MBS<sup>+</sup>08]). S1 and S2 are conflicting.

Table 3.4: Publication safety (from [MBS<sup>+</sup>08]). S1 and S2 are conflicting.

```

Initially data = 42, ready = false, val = 0

Thread 1

Thread 2

atomic {

ready = true;

}

if (ready)

val = tmp;

}

```

Table 3.5: Data race during publication (from  $[MBS^+08]$ ). val == 42 is allowed by the RTTM semantics.

#### 3.1. SEMANTICS

corresponding data is accessed" [MBS<sup>+</sup>08]. Encounter-time lock atomicity does support *publication in a conditional* (see Table 3.6).<sup>3</sup> [MBS<sup>+</sup>08] lists some idioms stronger than encounter-time lock acquisition which are not supported by the RTTM implementation.

Initially data = 42, ready = false, val = 0

Initially data = 42, ready = false, val = 0

Initially data = 42, ready = Thread 2

Initially data = 1;

atomic {

atomic {

if (ready)

ready = true;

}

}

Table 3.6: Publication in a conditional (example from [MBS<sup>+</sup>08]) is supported by RTTM. val != 42

Since the RTTM implementation tracks memory accesses at the word level, there are no problems with the granularity of transactional/non-transactional memory accesses, i.e. *granular safety* [MBS<sup>+</sup>08] is provided. *Observable consistency* [MBS<sup>+</sup>08] and *speculation safety* [MBS<sup>+</sup>08] is supported.<sup>4</sup> For an in-depth discussion of the implications of the various safety properties supported or not supported by RTTM, see [MBS<sup>+</sup>08].

**Stronger semantics?** More publication patterns could be supported if *all* writes to the shared memory would be broadcasted (which would be feasible in the prototype implementation). I assume that the semantics would then correspond to *asymmetric lock atomicity* [MBS<sup>+</sup>08]. The possible abort of transactions by non-transactional code would need to be accounted for in the WCET analysis, however. A notable property of RTTM is that conflicts are asymmetric, i.e. if transaction  $t_1$  possibly aborts  $t_2$ , this does not imply that  $t_2$  possibly aborts  $t_1$ . A transaction aborts automatically only if its read set overlaps with the write set of a preceding transaction. This prevents a behavior more similar to *single global lock atomicity*, where the program executes as if each transaction was protected by a single global lock.

An RTTM implementation could support *strong isolation* (for data types residing in a single memory word),<sup>5</sup> if, in addition, commits happened atomically. Else, one read could already see the modifications of a transaction and a successive read could see a value not yet updated by the transaction. As an alternative, static analysis could be considered to ensure segregation into transactional and non-transactional memory.

<sup>&</sup>lt;sup>3</sup>Speculative code motion is then disallowed. The RTTM implementation does not use compiler or hardware reordering.

<sup>&</sup>lt;sup>4</sup>Observable consistency and speculation safety are supported because the update of the shared memory is deferred.

<sup>&</sup>lt;sup>5</sup>Only long and double types do not reside in a single memory word.

**Transaction nesting** The implementation allows transactions to be nested. Nested transactions are *flattened*, i.e. aborting a nested transaction causes an outer transaction to abort, and committing a nested transaction has no effect. To support not flattened transactions, a more advanced write buffer and read tag memory would be necessary.

**Exceptions** Exceptions always abort, rather than commit, the current transaction. Terminating exceptions, which attempt to commit the transaction, are not supported. Handling of exceptions inside a transaction (catch or finally blocks) is also currently not supported, since it interferes with the transaction abort mechanism.

# **3.2 Implementation characteristics**

In this section, we characterize the implementation techniques used for the RTTM prototype. This is mostly done with regard to the taxonomy presented in [LR07, Ch. 2.3]. Most characteristics follow from the RTTM proposal.

**Granularity of conflict detection** RTTM conflict detection has *word granularity*, detecting conflicting accesses to a memory word. In the implementation platform JOP, all Java data items (such as elements of a boolean[]) and all implementation specific data structures modified in a transaction occupy one or more dedicated memory words. This excludes false positives. The conflict detection is currently largely language agnostic.

**Direct or Deferred Update** RTTM uses *deferred update* (the write buffer) during normal operation, as most HTM systems do. Memory words are *updated in place*. The single commit token makes updating the shared memory easy. On a buffer overflow/early commit, direct update is used.

**Concurrency control** RTTM uses *optimistic concurrency control*. W.r.t. *progress guarantees*, RTTM provides *wait freedom* if there is a single thread per CPU and as long as certain schedulability conditions are met [SBV10b] (and as long as no thread stalls while performing an early commit).

**Conflict Detection** RTTM detects conflicts among transactions *late* (i.e. not when they appear), during *validation* of a transaction. For each transaction, a read set and a write set is maintained, which remains private to the transaction. RTTM uses *lazy invalidation*, as defined in [Sco06]. According to [Sco06], this is the weakest consistency-ensuring conflict definition.

```

public class RingBuffer<T> {

// ...

@atomic public T read() {

if (rdPtr == wrPtr) {

return null;

}

T val = data[rdPtr++];

if (rdPtr == data.length) {

rdPtr = 0;

}

return val;

}

}

```

Listing 3.1: Example of atomic method

**Contention management** The *contention resolution policy* of RTTM is to always abort the conflicting transaction(s) which is (are) not committing. As argued in [SBV10b], the execution remains time-predictable if certain schedulability conditions are met.

# 3.3 Programming interface

Transactions are created by the programmer using an @atomic method annotation, as depicted in Listing 3.1. The @atomic annotation is the sole interface needed to use the functionality of RTTM, providing a simple interface for programming parallel systems.<sup>6</sup> The annotation provides the code executed in and invoked by the method with semantics as discussed in Section 3.1. Most Java language features are supported inside a transaction, as will be discussed in Section 5.2. The restriction to entire methods instead of code blocks is a pragmatic decision.<sup>7</sup> Annotated methods are modified at link time. A drawback of the restriction to *atomic methods* is that it may lead to fragmentation of code.

As an alternative, transactions may also be implemented using a special low-level method directly accessing the memory-mapped RTTM hardware interface, which will be described at page 31. An example is in the appendix (Listing B.2 on page 76). I believe that the use of a language feature is substantially less laborious and less error-prone.

<sup>&</sup>lt;sup>6</sup>Since Java method annotations do not alter the method signature, they can be transparently added without compromising an interface.

<sup>&</sup>lt;sup>7</sup>Code transformations are simpler and most local variables do not need to be restored on a transaction retry, as detailed in Section 4.3.1.

#### 3.3.1 Software commands

RTTM *software commands* provide additional functionality to the programmer. Software commands are invoked as Java methods. Their use can complicate the programming model of RTTM.

**retry()** The retry() statement, as introduced in [HMPJH05], lets the programmer roll back and restart the current transaction, as is also done transparently by RTTM if a conflict is detected. retry() can serve as a mechanism to coordinate transactions. [HMPJH05] proposes to delay the transaction restart until the data accessed has been changed. In an RTTM transaction, such a behavior can be attained by looping until an anticipated condition becomes true: while (!condition); . If a shared memory value evaluated in the condition is updated, the transaction will automatically retry.<sup>8</sup>

If an *early commit* was initiated earlier because of a buffer overflow or by the application, any writes before the retry() software command were already written to the shared memory and cannot be undone, violating the atomicity of transactions.<sup>9</sup>

**abort()** The abort() statement aborts the current transaction. It performs a rollback of all changes in the transaction and then exits the atomic method throwing a Java exception.<sup>10</sup> It has not been investigated which criteria should be used to abort a transaction. As in the case of the retry() statement, if an early commit was initiated earlier, any writes before the abort() software command will violate the atomicity of transactions.<sup>11</sup>

**earlyCommit()** An *early commit* is tried *a*) if the read tag memory or write buffer overflows or *b*) upon executing I/O operations (which usually cannot be rolled back). The implementation does not automatically try to commit before an I/O operation. Instead, the programmer needs to manually invoke the earlyCommit() software command before an I/O operation. Listing 3.2 on the next page shows an example use of the earlyCommit() software command to output an atomic snapshot. Because it blocks other transactions while generating output, this style of use is at most suited for diagnostic purposes.

If the earlyCommit() software command succeeded,<sup>12</sup> a subsequent abort of the transaction might violate the atomicity of the transaction, since all writes go directly to the shared memory during an early commit. An abort might happen a) if an exception terminating the current transaction is thrown due to a programming error or b) might be caused by the application (using the abort() or retry() software command).

<sup>&</sup>lt;sup>8</sup>This programming style will not work if an early commit has been performed in the transaction.

<sup>&</sup>lt;sup>9</sup>**retry()** could be ignored during an early commit.

<sup>&</sup>lt;sup>10</sup>As the AbortException is an unchecked exception derived from RuntimeException, an atomic method is not required to declare it in the throws clause.

<sup>&</sup>lt;sup>11</sup>abort() could also be ignored during an early commit.

<sup>&</sup>lt;sup>12</sup>Impossible for a transaction failing due to a conflict, since it will never acquire the commit token.

```

@atomic public void snapshot() {

// grab commit token

rttm.Commands.earlyCommit();

// can do I/O now

System.out.println("Linked list contents:");

// iterate through linked list

for (LinkedObject o = head; o != null; o = o.getNext()) {

System.out.println(o.getData());

}

}

```

Listing 3.2: Example use of earlyCommit() software command

#### 3.3.2 Diagnostics

For diagnostic purposes some basic per-CPU statistics, including the transaction commit and retry count and the maximum read set and write set size, may be measured without a probe effect.<sup>13</sup>

# 3.4 Scheduling

Context switches during a transaction are currently not possible. While executing a transaction, all interrupts are disabled. It would be straightforward to support context switches/interrupts during a transaction. Such a context switch/interrupt would simply abort the current transaction.<sup>14</sup> Transactions violating a deadline could then be aborted.

<sup>&</sup>lt;sup>13</sup>See class rttm.Diagnostics.

<sup>&</sup>lt;sup>14</sup>In JOP, interrupts are issued in a manner similar to exceptions (see page 53). In the RTTM implementation, Java exceptions are used to abort a transaction (see Section 4.3.2). When switching back to the thread running the interrupted transaction, an exception could be thrown to retry the transaction.

# CHAPTER 4

# Implementation

The RTTM prototype is implemented on the *Java Optimized Processor* (JOP), a *Java Virtual Machine* in hardware (see Section 1.3). RTTM is a hardware transactional memory system and language independent, as most HW TM systems [LR07, Ch. 4.1]. The prototype implementation does however rely on some of the strong guarantees and features of the Java programming language and the Java Virtual Machine (JVM), as will be discussed in the following.

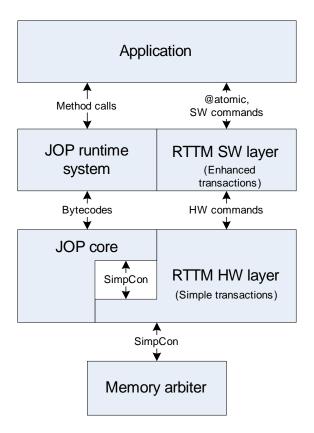

Significant parts of the functionality are implemented in software, which is also eased by the properties of the implementation platform. Figure 4.1 on the following page shows the layers in the RTTM implementation. The interfaces between them and the layers' implementation will be discussed in this chapter.

# 4.1 HW/SW-Partitioning

Next, we justify the partitioning in hardware and software and give an overview of the RTTM implementation. Memory accesses and conflict detection need to be implemented in hardware to be time-predictable and efficient. If the flush of the write buffer during the commit was to be performed by the CPU, additional HW-SW interfaces would be needed. On the other hand, the abort of transactions is currently implemented using the exception handling mechanism of Java – similar to the approach of the *Preemptible Atomic Regions* software TM [MBC<sup>+</sup>05]. The implementation does not introduce new CPU instructions.

The hardware part of RTTM has a simplified view of transactions. The hardware ignores the control flow associated with a transaction abort and has no concept of the retry of a transaction or of transaction nesting. The decision to keep the hardware simple has the benefit of keeping the interface between the CPU and the RTTM-specific hardware

Figure 4.1: RTTM implementation layers

simple and of requiring no changes to the CPU. It also avoids race conditions between the CPU and RTTM which would make maintaining the nesting count consistent difficult.

The software part of RTTM is implemented in a *transaction wrapper* which is transparently added to *atomic methods* at link time. The transaction wrapper implements *a*) the abort and retry of transactions and *b*) the nesting of transactions and *c*) saves and restores relevant CPU state. The use of software makes the implementation more flexible, e.g. w.r.t. the retry/abort strategy and the handling of Java exceptions.

# 4.2 Hardware layer

RTTM has been implemented by extending the CMP version of JOP (see page 8 and [Pit09]). In the conventional JOP CMP, each CPU is individually connected to the memory arbiter, as shown in Figure 4.2 on the next page. I/O is individually connected to each CPU.

<sup>&</sup>lt;sup>1</sup>Figure adapted from [Pit09].

Figure 4.2: Conventional JOP CMP components<sup>1</sup>

Figure 4.3: Hardware components related to RTTM implementation

In the RTTM implementation, depicted in Figure 4.3 on the preceding page, an *RTTM module* has been inserted between each CPU and the arbiter. The RTTM module comprises most of the RTTM functionality implemented in hardware. It contains the *write buffer* and *read tag memory* introduced in Section 1.2. The *transaction coordinator* grants the single *commit token* to an RTTM module requesting it.<sup>2</sup> An RTTM module which has been granted the token holds the token until it has completed the transaction.