Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

FAKULTÄT FÜR !NFORMATIK

#### Faculty of Informatics

# Description Methods for Asynchronous Circuits — A Comparison

### DIPLOMARBEIT

zur Erlangung des akademischen Grades

### **Diplom-Ingenieur**

im Rahmen des Studiums

### **Technische Informatik**

eingereicht von

### **Robert Najvirt**

Matrikelnummer 0526813

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung Betreuer: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger Mitwirkung: Dipl.-Ing. Jakob Lechner

Wien, 27.9.2011

(Unterschrift Verfasser)

(Unterschrift Betreuer)

## Erklärung zur Verfassung der Arbeit

Robert Najvirt Gessayova 25 851 03 Bratislava

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

## Abstract

The advances of silicon manufacturing technology make it possible to integrate billion-transistor systems on a single die but the price to pay is higher parameter variability, resulting in problems with reliability, difficult clock distribution, high power consumption and more. Proponents of asynchronous circuits claim them to be a possible solution to most of these problems and they are indeed becoming an increasingly interesting design choice.

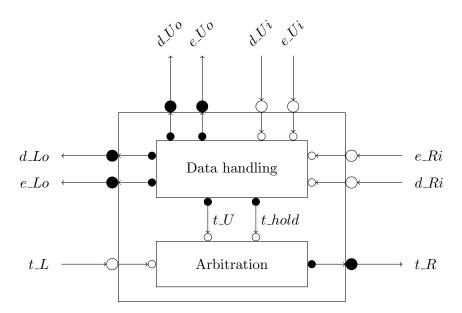

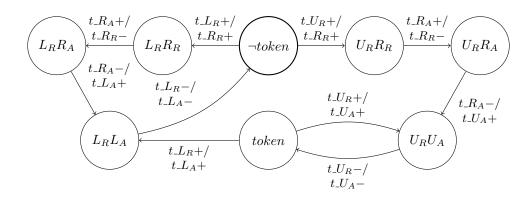

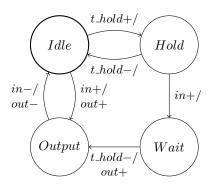

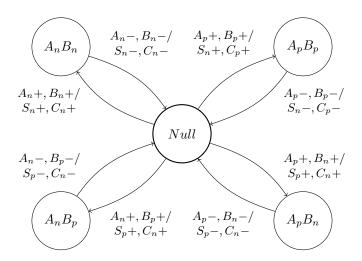

The aim of this work is to describe the most established description methods for asynchronous circuits, compare them in respect to a number of parameters and list their advantages and disadvantages. To further illustrate the differences, a simple ring topology network interface controller is described with all the considered methods and the implications of their use for the description are indicated. Next, to demonstrate the use of each description method in its typical field of application, selected parts of the faculty developed SPEAR2 processor are implemented with the methods.

As a result of this work a comparison of seven different description methods is now available that, unlike the existing literature so far, views these methods from the same angle, namely a carefully chosen set of criteria. This comparison, along with the selected demonstrative examples, could serve prospective designers of asynchronous circuits when choosing a description method for a project. At the same time, the extraction of the underlying concepts of the considered methods along with their comparison is also valuable for a didactic presentation of asynchronous design.

## Kurzfassung

Die Fortschritte in den Siliziumherstellungsverfahren ermöglichen es, Systeme mit Milliarden von Transistoren auf einem einzigen Chip zu integrieren. Die Nachteile einer solchen Miniaturisierung sind höhere Parametervariabilität, die zu Problemen mit Zuverlässigkeit führt, erschwerte Taktverteilung, hoher Energieverbrauch und andere. Beführworter von asynchronen Schaltungen behaupten, diese seien eine mögliche Lösung von den meisten dieser Probleme und sie sind tatsächlich eine zunehmend interessante Designmöglichkeit.

Das Ziel dieser Arbeit ist es, die etabliertesten Beschreibungsmethoden für asynchrone Schaltungen zu beschreiben, sie anhand einer Anzahl von Parametern zu vergleichen und ihre Vorteile und Nachteile zu benennen. Um die Unterschiede besser zu verdeutlichen, wurde ein einfacher Ringnetzwerkkontroller mit allen den betrachteten Methoden beschrieben und auf die Konsequenz derer Benutzung für die Beschreibung hingewiesen. Um die Benutzung von Beschreibungsmethoden in ihren typischen Anwendungsgebieten zu zeigen, wurden zusätzlich gewählte Teile von dem auf der Fakultät entwickelten SPEAR2 Prozessor mit den Methoden beschrieben.

Als Ergebnis dieser Arbeit ist jetzt ein Vergleich von sieben Beschreibungsmethoden vorhanden, die diese Methoden, im Gegensatz zu der bestehenden Literatur, vom selben Blickwinkel betrachtet, und zwar durch sorgfältig ausgewählte Beurteilungskriterien. Dieser Vergleich mit den gewählten anschaulichen Beispielen kann einerseits zukünftigen Entwicklern von asynchronen Schaltungen bei der Wahl einer Beschreibungsmethode für ein Projekt von Nutzen sein. Gleichzeitig aber kann sie durch die Erfassung der grundlegenden Konzepte der betrachteten Methoden zusammen mit deren Vergleich wertvoll für didaktische Präsentationen von asynchronem Design sein.

## **Table of Contents**

| In       | trod | uction 1                                                     |  |  |  |  |  |  |

|----------|------|--------------------------------------------------------------|--|--|--|--|--|--|

| 1        | Asy  | Asynchronous Circuits                                        |  |  |  |  |  |  |

|          | 1.1  | Why Asynchronous?                                            |  |  |  |  |  |  |

|          | 1.2  | Asynchronous Circuits                                        |  |  |  |  |  |  |

|          |      | 1.2.1 Timing models                                          |  |  |  |  |  |  |

|          |      | 1.2.2 Asynchronous communication                             |  |  |  |  |  |  |

|          |      | 1.2.3 Metastability                                          |  |  |  |  |  |  |

|          |      | 1.2.4 Typical components                                     |  |  |  |  |  |  |

|          | 1.3  | Properties of Asynchronous Circuits                          |  |  |  |  |  |  |

| <b>2</b> | Des  | scription Methods 15                                         |  |  |  |  |  |  |

| _        | 2.1  | Problems in asynchronous circuit design                      |  |  |  |  |  |  |

|          | 2.2  | Production Rule Sets                                         |  |  |  |  |  |  |

|          | 2.3  | Asynchronous Finite State Machines                           |  |  |  |  |  |  |

|          |      | 2.3.1 Fundamental Mode Asynchronous Finite State Machines 21 |  |  |  |  |  |  |

|          |      | 2.3.2 Burst-Mode Asynchronous Finite State Machines          |  |  |  |  |  |  |

|          | 2.4  | Signal Transition Graphs                                     |  |  |  |  |  |  |

|          |      | 2.4.1 Petri Nets                                             |  |  |  |  |  |  |

|          |      | 2.4.2 Signal Transition Graphs                               |  |  |  |  |  |  |

|          | 2.5  | Timed Event/Level Structures                                 |  |  |  |  |  |  |

|          |      | 2.5.1 Timed Event/Level Structures                           |  |  |  |  |  |  |

|          | 2.6  | CSP-Based Descriptions                                       |  |  |  |  |  |  |

|          |      | 2.6.1 Communicating Sequential Processes                     |  |  |  |  |  |  |

|          |      | 2.6.2 Common characteristics                                 |  |  |  |  |  |  |

|          |      | 2.6.3 Communicating Hardware Processes                       |  |  |  |  |  |  |

|          |      | 2.6.4 Haste                                                  |  |  |  |  |  |  |

|          |      | 2.6.5 Balsa                                                  |  |  |  |  |  |  |

| 3        | Cor  | mparison by Example 43                                       |  |  |  |  |  |  |

| 0        | 3.1  | The Circuit                                                  |  |  |  |  |  |  |

|          | 0.1  | 3.1.1 Building Blocks                                        |  |  |  |  |  |  |

|          |      | 3.1.2 Motivation for the Choice                              |  |  |  |  |  |  |

|          | 3.2  | The Descriptions                                             |  |  |  |  |  |  |

|          | 0.2  | 3.2.1 Production Rule Sets                                   |  |  |  |  |  |  |

|          |      | 3.2.2 Asynchronous Finite State Machines                     |  |  |  |  |  |  |

|          |      | 5.2.2 Asynchronous Finite State Machines                     |  |  |  |  |  |  |

|          |     | 3.2.3                          | Signal Transition Graphs           |  |  |  |  |  |  |  |

|----------|-----|--------------------------------|------------------------------------|--|--|--|--|--|--|--|

|          |     | 3.2.4                          | Timed Event/Level Structures       |  |  |  |  |  |  |  |

|          |     | 3.2.5                          | Communicating Hardware Processes   |  |  |  |  |  |  |  |

|          |     | 3.2.6                          | Haste                              |  |  |  |  |  |  |  |

|          |     | 3.2.7                          | Balsa 6                            |  |  |  |  |  |  |  |

| <b>4</b> | Cor | mparison 6                     |                                    |  |  |  |  |  |  |  |

|          | 4.1 | Arbitr                         | ation                              |  |  |  |  |  |  |  |

|          | 4.2 | Concu                          | rrency and Sequence                |  |  |  |  |  |  |  |

|          | 4.3 | Timin                          | g6                                 |  |  |  |  |  |  |  |

|          | 4.4 | Async                          | hronous communication              |  |  |  |  |  |  |  |

|          | 4.5 |                                | Event Sensitivity                  |  |  |  |  |  |  |  |

|          | 4.6 | Modularity and Parametrisation |                                    |  |  |  |  |  |  |  |

|          | 4.7 | Level                          | of Abstraction                     |  |  |  |  |  |  |  |

|          | 4.8 | Summ                           | ary                                |  |  |  |  |  |  |  |

| <b>5</b> | Exe | mplar                          | y Design 75                        |  |  |  |  |  |  |  |

|          | 5.1 |                                | rocessor                           |  |  |  |  |  |  |  |

|          | 5.2 | The E                          | xamples                            |  |  |  |  |  |  |  |

|          |     | 5.2.1                          | Production Rule Sets               |  |  |  |  |  |  |  |

|          |     | 5.2.2                          | Asynchronous Finite State Machines |  |  |  |  |  |  |  |

|          |     | 5.2.3                          | Signal Transition Graphs           |  |  |  |  |  |  |  |

|          |     | 5.2.4                          | Timed Event/Level Structures       |  |  |  |  |  |  |  |

|          |     | 5.2.5                          | Communicating Hardware Processes   |  |  |  |  |  |  |  |

|          |     | 5.2.6                          | Haste                              |  |  |  |  |  |  |  |

|          |     | 5.2.7                          | Balsa                              |  |  |  |  |  |  |  |

|          |     |                                |                                    |  |  |  |  |  |  |  |

### Conclusion

## Introduction

Despite the fact that asynchronous circuits have been an active research area for decades, their commercial application remains marginal. Amongst other factors, this is because there is a multitude of description method each having different advantages and disadvantages and each being bound to a different tool. The choice, which description method to learn and which tool to invest in is even more difficult due to the uncertain future of both, description methods and tools.

However, with the advances in silicon manufacturing technology, making it possible to integrate billion-transistor systems on a single die for the price of higher parameter variability, fully synchronous systems are becoming increasingly inefficient and difficult to design. As a result, asynchronous circuits and systems are becoming an increasingly interesting design choice and impressive circuits from both, academia and industry demonstrate the potential of this design style.

The objective of this work is to give an overview of established description methods for asynchronous circuits, compare them in respect to a number of parameters and list their advantages and disadvantages.

Hopefully, it will be able to serve prospective designers of asynchronous circuits when choosing, which description method to learn. In addition, the findings could be a valuable source of information for a didactic presentation of asynchronous design.

The work is structured as follows:

As some readers might not be fully familiar with asynchronous design, Chapter 1 introduces some of its basic concepts, the understanding of which is assumed in the argumentation in the analysis, comparison and discussion. The experienced reader may skip this chapter.

Chapter 2 introduces the considered description methods and describes them to the extent that the reader would understand the approach and the underlying concepts.

To further clarify the use of the methods and visualise the fundamental differences between them a simple circuit is described with all the considered methods in Chapter 3 as a comparative example. A short discussion about the implications and possibilities of the methods for that particular circuit follows.

Chapter 4 gives a summary of properties of description methods, comparing them directly.

A second, design example for each of the methods to support the arguments from the analysis, comparison and discussion is presented in Chapter 5. Parts of a processor core will be chosen to show the use of a method in its suggested application domain.

### Chapter 1

## **Asynchronous Circuits**

This chapter serves as an introduction to asynchronous circuit design for those, who are not familiar with the concepts. First, motivation for choosing asynchronous circuits is given. Then, basic concepts such as timing models, signal coding, handshaking and typical building blocks will be described. Finally, advantages and disadvantages of asynchronous circuits as compared to synchronous ones will be presented. The information presented in this chapter is considered prerequisite knowledge in the rest of this work.

### 1.1 Why Asynchronous?

This whole work is about description methods for asynchronous circuits. But why to use asynchronous design in the first place? Forshaw and Hahn wrote in their paper [1] from 1990: "With the advent of more sophisticated ASIC libraries and CAD tools it becomes increasingly important for the circuit designer to adhere to a synchronous design methodology."

No doubt, the rising complexity of integrated circuits required methods for a faster and more reliable design process. In the synchronous design style, all flip-flops in the circuit are clocked with the same central clock, the period of which is carefully set to allow all signals traverse even the longest combinatorial path between two flip-flops (the critical path) and possible hazards to resolve. This allows to model temporal behaviour separately from functionality. The advantages of this approach are excellent tool support, efficient testability and simplicity of design. As those are legitimate arguments for using it, modern highly integrated chips have been designed almost exclusively using the synchronous methodology.

Disadvantages of synchronous design according to Forshaw and Hahn include higher power dissipation and the necessity of clock distribution. This were acceptable problems compared to the advantages they brought.

In the present, 20 years after the paper has been published, the on-chip transistor count has increased by three orders of magnitude. Keeping the synchronous timing assumption valid in such highly integrated systems is becoming a painful problem and is always connected with large performance, power, and area overheads.

As can be seen in [2], only approximately 45% of the clock period represent the actual computation. The rest includes safety buffers for correct operation under worst case conditions such as high temperature and low voltage, accounting for imperfect clock distribution

(clock skew — the difference in the arrival time of the clock edge at various locations of the chip) and combinatorial path imbalance (waiting for the critical path to complete even if it was not utilised in the current computation). With deep submicron technology scaling, the inherently present parameter variability increases and further degrades the worst case conditions for certain fault probabilities.

Distributing the high fan-out clock signal over the whole chip area requires a considerable length of wires which results in a high parasitic capacitance. Driving a high frequency signal over this network and still retaining sufficiently steep edges to lower clock skew requires strong drivers. In high performance microprocessors, clock distribution consumes up to 40% of the total power [3]. The high dissipation causes problems with power delivery as well as thermal design.

The area overhead caused by the clock distribution, although usually in the range of 25% can go up to 45% for certain applications [4].

Moreover, the clock wires also act like antennas and radiate the high-frequency clock signal. This electromagnetic radiation introduces noise which, in signal processing applications, can alias into the processed frequency band and degrade the quality of such applications.

Proponents of asynchronous design claim it is the solution for these problems and evidence their claims with manufactured asynchronous circuits with impressive results (see Section 1.3 for examples).

### 1.2 Asynchronous Circuits

Asynchronous circuits, also referred to as *clockless* or *self-timed*, are those in which no global synchronisation by means of a clock signal takes place. Sources of communication synchronise with the destinations locally for each transfer.

In this section, the timing models used in asynchronous circuit design, the different possibilities of implementation of asynchronous communication and typical components asynchronous circuits contain will be described.

#### 1.2.1 Timing models

The assumption that all paths' delays globally share the same bound is abandoned. Instead, one of the timing assumptions supporting the asynchronous methodology is used by which the resulting circuit can be classified. The timing models frequently used in literature are:

**Delay Insensitive** Circuits that do not depend on any timing assumption for correct operation are called delay insensitive (DI). In this model, both gate and wire delays can be arbitrary (but finite). These circuits are insusceptible to parameter changes, be it operating conditions as temperature and voltage, migration to new process technology or rerouting. However, as Martin showed in [5], this class is very limited and virtually all practical circuits fall out of this class.

**Quasi Delay Insensitive** The least restrictive universally applicable model is called quasi delay insensitive (QDI). Its only assumption is that signals in certain wire forks arrive at their destination 'simultaneously'. More precisely, the difference in latencies of

Processed, accepting new data

Figure 1.1: Handshaking signals

the fork branches must be smaller than the gate delay of the following logic. Such forks are called *isochronic*. Only a fraction of wire forks in a circuit have to be isochronic — no timing assumption is made about the other wires or the logic. The QDI class of circuits is Turing-complete, as has been shown in [6].

**Speed Independent** The timing model which assumes that interconnect delays are negligible compared to gate delays is called speed independent (SI). In contrast to QDI, in SI circuits all wire forks are isochronic by definition.

There are also variations of this class in which the circuit is partitioned into smaller regions. The rather unrealistic assumption of negligible interconnect delay within a circuit is relaxed to hold only inside those so called *equipotential regions*. This model is also referred to as *self timed* [7].

**Bounded Delay** Circuits that fall into the bounded delay (BD) class, also referred to as *matched delay* or simply *self-timed* require that both logic and interconnect delays are bounded much like in synchronous design. However, each logic path is considered individually whereas in synchronous design one bound has to apply system-wide.

#### 1.2.2 Asynchronous communication

A communication link in asynchronous circuits is called a *channel* and is composed of two main parts, the wires carrying the actual data and means of synchronisation between the sender and the receiver. The synchronisation is called *handshaking* and is generally organised as an alternating sequence of a *request* for communication and the response to the request, called *acknowledgement*. One or both of those events can be coincident with data transfer.

Although a channel is a direct link, the same construct with combinatorial logic added to the data path is used to implement pipeline stages. A schema of a channel with optional logic is depicted in Figure 1.1.

The connection points for a channel, which are mostly located directly at the input to or the output from state holding elements, are also often called *ports*. This is the rule for external ports that are intended to connect a circuit to its environment.

Channels can also be categorised by the number of communicating parties. A *narrow*cast channel connects exactly one sender to one receiver. A *multicast* channel on the other hand connects one sender with multiple receivers. The handshaking in multicast channels must ensure that all receivers have processed previous data before the sender can transmit a new value. Having multiple senders is not possible, since a simultaneous transmission to the same channel would lead to undefined results and may even cause damage of the output drivers.

Another parameter of a channel is the direction of the request relative to the direction of the data exchanged. This determines, whether the sender or the receiver initiate the communication. If the request comes from the sender, the channel is referred to as a *push* channel. In a *pull* channel, on the other hand, the receiver requests the transmission. If data are exchanged in both directions, coincident with both, the request and the acknowledgement, the channel is referred to as a *biput* channel. A port that is on the requesting side of a channel is called *active*, while a port waiting for requests to acknowledge is called *passive*. This attribute is important for interconnecting black-box circuits, since active ports can only be connected to passive ports and vice versa.

Channels can also be used purely for synchronisation. They consist only of handshaking signals and are referred to as *dataless* or as *synchronisation channels*. Controlling access to a shared resource might be an example of the application of such channels (See also Chapter 3).

Using the request on a channel as a trigger for various actions, mostly however communication on other channels, and delaying the acknowledgement of the request until all actions complete is called *handshake enclosure*. A typical example for such behaviour is a sequencing element, which upon a request on its input port sequentially performs full handshake cycles on its output ports and only after the last output completes its handshake, the element finishes by acknowledging its input request.

#### Signal coding

Since most of the timing models for asynchronous circuits allow arbitrary gate delay, it is not possible to determine when consistent data are present at the end of a logic path, without observing the data itself. Unfortunately, the usual data coding based on signal levels, where a positive voltage indicates a '1' and the grounding of a signal indicates a '0', cannot be used because of this fact. As an example, it is not possible to determine whether the current level on a wire is the new value to be received or whether transition is still to come without assuming completion and therefore bounding the time allowed for stabilisation of the signal.

A more complex signal coding is therefore required for most of the timing models described above, which not only allows to distinguish between a '1' and a '0', but also provides some separation of successive values. Since this implies the encoding of more than two states. This is only possible with more than one wire per bit. A coding which uses two wires per bit is called *dual rail*.

The act of observing data to determine when new consistent data is present is called *completion detection*. The circuit required for completion detection is dependent on the coding of the observed data. The most common codings are listed below:

**Transition signalling** Transition signalling (also referred to as *rail transition* coding) is the most simple dual rail coding for understanding; for hardware implementation, it is one of the most complicated. Each bit of data is encoded as a transition on one of two wires. One wire, called the '0-wire' for example, is used for logic zeros while the other, the

Figure 1.2: The LEDR encoding scheme

'1-wire', is used for logic ones. Since each transmitted value corresponds to one transition, subsequent values can be accurately separated in time. For completion detection, the current states of the wires have to be compared to their states from when the last value input was processed. Thus, a state holding circuit is required for completion detection.

**Null convention logic (NCL)** In NCL, the two wires represent three different states. Apart from the two logic values to be encoded, a *NULL* is added. Usually, *NULL* is represented with both wires being at a low level and the logic values with exactly one of the wires being high. The fourth possible state (both wires being high) is not allowed.

For communication, alternating *phases* are used: A data phase where the data value is transferred followed by a *NULL* phase which serves as a separator between two subsequent values.

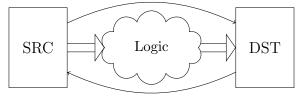

Level-encoded two phase dual rail scheme (LEDR) LEDR also uses phases to separate subsequent values like NCL, but uses all four possible states that can be encoded with two wires. Each of the two phases, either referred to as  $\varphi_0$  and  $\varphi_1$  or odd and even, can be represented by two of the four states available, one for each logic value. The state assignment is such that the change from one phase to another requires exactly one transition, no matter what values each phase encodes. Refer to Figure 1.2 for clarification.

**N-of-m coding** In *n*-of-*m* coding, *m* wires are used while transitions occur on exactly *n* of those wires for each data transfer. This gives  $\binom{m}{n}$  possible combinations. Usually, the highest power of two that fits that number (be it  $2^k$ ) limits the amount of useful codes, as all possible values that can be encoded with *k* bits will be distributed over these codes.

As can be seen, n-of-m coding is not a dual rail scheme where each bit is separately encoded in two wires. Instead, the value is distributed over multiple lines without a direct correspondence between the value and its code. This makes this scheme more difficult to implement and unsuitable for computation as even simple operations require complicated combinatorial functions. With n-of-m coding, it is however possible to communicate data values with less transitions than the number of bits they contain and/or use less wires than the double of the amount of bits, which gives it a power and area advantage. It is mostly used for long interconnects or network-on-chip.

Figure 1.3: Handshaking protocols

A subset of *n*-of-*m* coding is the one-hot coding, where *n* is always equal 1. As an example, the most popular 1-of-4 coding uses 4 wires with exactly one having a transition at each transfer. This gives  $\binom{4}{1} = 4$  possibilities and therefore 2 bits can be transferred at a time. This scheme uses the same amount of wires to encode an even number of bits as the above codes, however, in comparison to them needs only half the number of transitions to transfer a value.

An overview of different n-of-m codes as well as their implications on area and performance can be found in [8].

#### Handshake protocols

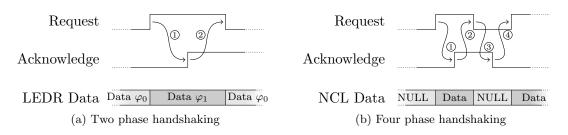

The simplest way to implement an asynchronous channel is to augment a standard data bus by two wires, a request and an acknowledgement wire. There are, however, two possibilities how to use those wires to signalise the handshaking events. Either a transition is used for each event, this corresponds to the *two phase handshaking protocol*, or one of the logic levels is used to signalise a pending transition, thus requiring two transitions for each event (one to bring the wire back to the idle state). The latter possibility is referred to as the *four phase handshaking protocol*.

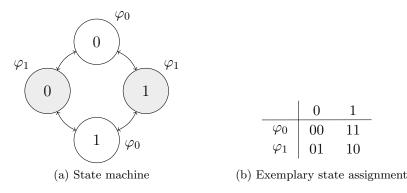

For clarification, Figure 1.3 shows the two protocols and the causal relationships between events. In the figure, a push channel is assumed and the transitions on explicit request and acknowledge wires are shown in the top two lines of the figure.

Figure 1.3a shows the two phase protocol with the two causal relationships. First the sender generates a request by a transition on the request wire. After observing the request and processing the data, the receiver acknowledges the request by a transition on the acknowledge wire (1). Only after the sender receives the acknowledgement, it can output a new value (2).

In Figure 1.3b, the four phase protocol is depicted. Again, the sender starts with a request which is acknowledged by the receiver upon reception (1). However, when the acknowledge event reaches the sender, the request wire must be returned back to its idle state (2). After observing this, the receiver resets the acknowledge wire, too (3). Only after this cycle is complete, the next value can be transmitted by a new request (4).

The approach of using a standard, one wire per bit data bus augmented by handshaking wires is called *bundled data*. Clearly, for correct operation, the request signal is required to arrive at the receiver later than the data after traversing possible logic. This is implemented by estimating the worst case timing of the data path and delaying the request signal accordingly. Since the correct operation of the resulting circuit is depending on a timing assumption bounding both gate and wire delays, only circuits of the bounded delay class can make use of such channels.

To design DI, QDI, or SI circuits, dual rail or more complicated signal codings supporting completion detection must be used. Since completion detection will indicate when consistent new data are present at the inputs of the destination, it can be used instead of the request signal. Note that while in push channels the data replace the request wire, in pull channels it is the acknowledge wire which is replaced by completion detection of the data. Biput channels use completion detection for all handshaking events. The codings can also be classified by equivalence to handshaking protocols. NCL has a default state (*NULL*) to which it has to return, which corresponds to the four phase handshaking protocol. With transition signalling and LEDR, each transition represents a new value, which corresponds to the two phase handshaking protocol. N-of-m codes can be used in both variants, with each n transitions denoting a new value (two phase) or with an idle state of the wires separating two values (four phase). In Figure 1.3, the equivalence of events on the request wire of a push channel and the completion detection of the data is shown using LEDR phases in the two phase handshaking protocol and NCL data validity in the four phase protocol.

Note that hybrid protocols are also possible where data use a four phase protocol while the acknowledge uses the two phase alternative or vice versa.

#### 1.2.3 Metastability

In synchronous systems, all registers are controlled with the same clock signal resulting in virtually simultaneous registration of data. This common clock event allows to assume that in each cycle, data arrive at the registration points at the same time in the whole circuit. As there is no such synchrony in asynchronous systems, no two events can be considered to occur at the same time<sup>1</sup>. The behaviour of a circuit is thus not only dependent on communicated data values, but also on the order of event occurrences, which also includes whether an event has occurred between other events or not.

Where parts of a circuit are not explicitly synchronised using handshaking on dedicated channels, there is no causal or temporal relationship between events from those parts. Such events can occur in any order, but also as close to each other that they could be considered simultaneous, and they are called *concurrent*. When a circuit is fed with concurrent events and its behaviour is dependent on the order of their occurrences, the choice between two virtually simultaneous events cannot be made unambiguously and the circuit can become *metastable*.

Metastability is a state of a bistable device where the output is stuck between the two stable states. The circuit will eventually resolve the metastable state and the output will turn into one of the stable states. However, no upper bound can be given on the resolution time [9] which means, that if a circuit prone to metastability is given limited time to resolve before reading its output (such as in synchronous or bounded delay asynchronous circuits), there will always remain a certain probability that it will fail. The correct operation of asynchronous circuits that do not bound gate delay is not affected by the resolution time of metastability, however the undefined signal level still has to be avoided.

<sup>&</sup>lt;sup>1</sup>This is true at a functional level. In the implementation, some signal arrivals can be assumed simultaneous (e.g. isochronic fork in QDI circuits).

Figure 1.4: An implementation of an arbiter

In properly designed synchronous systems, the only source of metastability are asynchronous external signals and clock domain crossings that can violate the setup and hold times of the input flip flops. In asynchronous systems, in addition to the sampling of external signal levels, it is the ordering of any two concurrent events, such as the choice of requests when accessing a shared resource.

#### **1.2.4** Typical components

There are a few building blocks, that solve some of the typical problems in asynchronous circuits, some of which will be described in this section. Where not stated otherwise, push channels are assumed in the descriptions. In the figures that show building blocks with exemplary input/output behaviour represented as tokens, the tokens are ordered by the time of occurrence with the earliest being at the right hand side.

The two probably most discussed functional blocks in literature are the arbiter and the synchroniser [10] which both implement functions that require the handling of potential metastability. The **arbiter** performs the task of choosing one of requests when these can occur simultaneously. When both requests are input at the same time, the arbiter makes a nondeterministic choice and delays the other request, until the chosen request is removed. An arbiter is called *fair*, if no request can be delayed infinitely. This means that a fair arbiter cannot choose one input over the other infinitely many times.

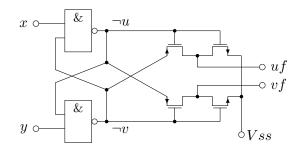

Figure 1.4 shows the implementation of a basic arbiter from [11], often referred to as a *mutual exclusion element* in literature. In the figure, x and y are the inputs,  $\neg u$  and  $\neg v$ are inverted, unstable, mutually exclusive outputs denoting which input has been selected and uf with vf are the stable outputs. The main functionality is implemented with the two logic gates. This part is called the *bare arbiter* (also, unstable arbiter) and produces inverted outputs susceptible to metastability. The four transistors form the *metastability filter*, an analog circuit preventing metastability to be driven at the outputs.

The **synchroniser** is used to sample a signal's value at a given point. It has two inputs, one accepting requests from the control circuit, the other for the sampled signal itself. In contrast to the arbiter, which requires requests not to be withdrawn until they are selected, the signal input of the synchroniser is allowed to change at any time. When the synchroniser receives a request, it outputs the current value of the signal and holds this value until the next request arrives. While this function can be implemented with a simple D flip-flop for signals being stable during the sample period, with signals that can potentially make a transition at a time very close to that of the request, the circuit becomes prone to metastability and a metastability filter as in Figure 1.4 has to be used.

Figure 1.5: An implementation of a Muller C-element

Again, no upper bound on the decision time for ambiguous signal states can be given and such decision is nondeterministic.

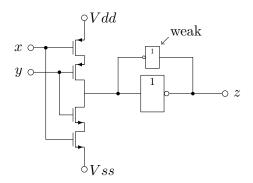

The Muller C-element [12], or Muller C-gate, is another building block frequently used in asynchronous circuits. It performs the function of an AND gate for transitions. In Boolean logic, the AND gate indicates when both inputs are at a high level but gives no information about the states of the inputs when at least one is low. Similarly, an OR gate only indicates when both signals are low. To form the conjunction of transitions, each transition on the output must indicate transitions on both inputs. The Muller C-element is a state holding operator that serves this purpose. When both input levels are equal, the output has the same signal level. When the inputs differ, the output holds its state until both inputs are equal again. Figure 1.5 shows one possible implementation of a Muller C-element.

While the above blocks work directly with signals on wires, the following blocks, motivated by [13], use channels for communication and have a higher abstraction level, since they only correspond with a hardware implementation when the channels and the handshaking protocols used are defined.

A **fork** splits one channel into multiple branches. The forward path can be implemented by simply forking all channel wires without any additional components. However, in the opposite direction, the signals must be joined so that the input request is acknowledged only after acknowledges on all output channels are received. This can be implemented with Muller C-elements.

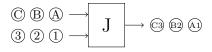

$$\mathbb{C} \ \mathbb{B} \ \mathbb{A} \longrightarrow F \xrightarrow{\longrightarrow} \mathbb{C} \ \mathbb{B} \ \mathbb{A}$$

Figure 1.6: A fork block with an exemplary input/output

The **join** block has inverse functionality to that of a fork. When requests from all input channels are received, a request on the output channel is generated. Again, this functionality can be implemented with Muller C-elements. The reverse path, that of the acknowledgements, can be implemented by forking the acknowledge wire to all input channels.

A merge can be described as a self-selecting multiplexer. Requests from input channels are selected one-by-one and passed to the output channel. Once the handshake on the

Figure 1.7: A join block with an exemplary input/output

output channel is completed, the incoming request is also acknowledged and the next request is selected. If requests on the inputs can occur simultaneously, the merge block must contain an arbiter to resolve possible conflicts. Where the input requests are guaranteed by the environment not to occur simultaneously, the merge block can be implemented with a simpler and faster circuit.

Figure 1.8: A merge block with an exemplary input/output

#### **1.3** Properties of Asynchronous Circuits

In this section, the advantages of asynchronous circuits as well as the most notable disadvantages will be listed.

Average case performance The clock period of a synchronous circuit has to be carefully set to make sure the longest register-to-register path in the whole clock domain has enough time to produce valid and stable outputs before the next clocking edge even when it is not used in the current computation. Therefore also rarely used blocks have to be optimised not to slow down the whole design and optimising other, frequently used blocks to be faster than the clock period does not bring any benefit.

An asynchronous circuit on the other hand waits for the data to become valid before registering them, instead of waiting for a global clock signal. This is either done by dual rail data encoding or a delayed request signal. In both alternatives, the actual registerto-register delay will depend on the current computation. Therefore when computing on short paths with a few logic gates only, the circuit is much faster than when computing on long paths with many gates. As a result, rarely used functions can be left unoptimised and still have only marginal effects on the overall performance while even slight optimisations on frequently used paths may have considerable effects, corresponding to Amdahl's law [14].

Of course, in a pipeline the throughput of consecutive stages is linked and if one stage has a constantly limited throughput, the design will not benefit from optimising the following stages to be faster. However, if one stage is very rarely performing a slow computation, this will only delay the pipeline for this occurrence and not for the whole computation and may be left unoptimised.

**Lower power** In standard synchronous circuits, the global clock signal is driving all state holding elements with a minimal skew which requires strong drivers and a large

distribution tree. The long wires along with the huge fan-out increase the power required for every transition. The clock, being global has to switch even when only a little part of the circuit requires it, e.g. when most of the pipeline is stalled because of a branch misprediction.

A typical technique to address this issue in synchronous design is clock gating. The circuit is divided into clock islands in which the clock signal can be turned off. This way, unused parts of the design do not consume dynamic power. However, the partition of the circuit can be done only in a coarse-grain manner and unnecessary switching can only be reduced, not avoided.

In asynchronous circuits, there is no clock signal, and switching only occurs in parts of the circuit currently performing a computation. All other parts are idle and consume only leakage power.

However, data encoding for DI, QDI and SI circuits can introduce some additional switching as consecutive values have to be distinguishable by transitions on the wires. As an example, NCL coding requires two transitions for every transferred bit, LEDR and transition signalling require one and in 1-of-4 coding, two bits will be transferred with every transition. Nevertheless, the dynamic power saving in circuits using such codes compared to their synchronous counterparts is still considerable.

Adaptation to physical variations The problems with variations as described in the beginning of this chapter, can be solved by using DI, QDI or SI circuits. Those are inherently free from predefined timing assumptions and operate as fast as the current environment allows. When a transient delay fault slows down the computation, the circuit will simply wait for it to finish. No statistical analysis is necessary to adjust the clock period to tolerate faults with a certain failure rate.

This also applies for operating temperature and the power supply voltage. In synchronous design, the operating conditions such as temperature range as well as the power supply voltage range are specified, and the clock period is set for the circuit to work under these conditions. However, the boundaries of these safe operation intervals are worst case conditions and most of the time (in an average environment) the circuit could safely perform better. A DI, QDI or SI asynchronous circuit adjusts to the environment and simply becomes slower with rising temperature.

**Technology migration and modularity** As a consequence of the above paragraph, migration of an existing asynchronous design to a new technology (e.g. from 90 to 45 nm) does not require any changes to the design (assuming delay insensitive design or similar). This also greatly simplifies modular design — to use a module a simple interconnection of data and handshaking signals is sufficient no matter which technology the module was designed for and which is actually used. No timing requirements have to be fulfilled to ensure correct operation.

**Lower electromagnetic emission** As the clocking edge in synchronous circuits is distributed over a large wire network and triggers a considerable amount of switching activity, the electromagnetic emissions of such circuits are concentrated around the clock frequency and its harmonics and, as a result, have high peaks at those frequencies.

The emission spectrum of asynchronous circuits is more evenly distributed over the frequency domain with much lower peaks as synchronisation occurs only between communication partners and not globally. This has advantages for example in devices with radio receivers which receive less disturbance from the digital signal processing unit and so achieve a better signal to noise ratio, possibly eliminating the need to switch off the processor during the reception of a message.

**Failure-free arbitration** The timing assumption in the synchronous approach, where each signal is allowed to change at a certain time window can only apply within a circuit. However, most circuits have to process external events such as interrupts which are inherently asynchronous. Such signals have to be synchronised before use to avoid timing faults such as metastability. Also, in clock domain crossings, signals have to be synchronised to the local clock.

The synchronisation process, for example using a synchroniser as described in the previous section, can take an arbitrary time to resolve. In synchronous circuits, the maximum resolution time is limited to allow correct operation with a certain probability. However, the longer the resolution time, the longer the delay introduced by the synchronisation process. The reliability of the circuit is therefore traded for its performance. Asynchronous circuits allow failure free synchronisation as no time bounds are applied (delay insensitivity or similar assumed), while not introducing additional delay to the average case.

There are three most notable disadvantages directly resulting from the requirements of asynchronous circuits.

**Larger area** Most asynchronous timing models require dual rail or other advanced signal coding schemes that allow the separation of successive values. This is usually associated with a 100% wiring overhead which undoubtedly increases the chip area occupied by the circuit.

**No masking of hazards** A considerable advantage of timing assumptions in synchronous and bounded delay circuits is the fact that all activity of combinatorial logic is ignored in the time between two clock edges. This allows all hazards to be resolved before a value is read. In DI, QDI and SI circuits, where each transition represents an event, hazards must be avoided with techniques such as masking with additional gates and small scale relative timing constraints similar to that of an isochronic fork.

Lack of tools In synchronous design, a vast majority of circuits are described in either VHDL or Verilog. These are supported by a wide range of high quality tools capable of code generation, synthesising to netlists for a multitude of back end technologies, simulation and much more. The tool sets available for asynchronous design, with a few exceptions, originate from academia and use own description methods as input. A commercially wide accepted design flow with a choice of high quality tools that can interchangeably be used for various steps is, however, yet missing.

**Testability** In the testing process of synchronous circuits, the global clock can be halted which causes the state of the whole circuit to be locked in state holding elements. By

added shift registers, the state can be read and/or altered to perform predefined tests. The testing of asynchronous circuits is more difficult because they cannot be simply globally halted, redundant logic used for masking hazards can also mask faults, and some faults, usually timing related, only become observable in certain operating conditions.

**Design complexity** The design of asynchronous circuits is arguably more difficult than that of synchronous ones. This is due to the need of local synchronisation in every path, analysis of the design to show the absence of deadlocks, the elimination of hazards in logic paths and the identification and meeting of (relative) timing constraints at the lowest design level. However, the complex design of a low skew, multi gigahertz clock distribution network for large chip areas in current technology, which is not needed in asynchronous circuits, mitigates the advantages of synchronous design.

Selected references for implementations of asynchronous circuits include the "Caltech asynchronous microprocessor" [15, 16], the series of "AMULET" processors [17, 18, 19], the "MiniMIPS" processor [20], the asynchronous 80C51 microcontroller [21], the ultra-low power "Lutonium" processor [22] and an asynchronous FPGA architecture [23, 24].

### Chapter 2

## **Description** Methods

In the beginning of this chapter, the typical problems in asynchronous design are extracted from the previous chapter, also serving as criteria for the later comparison. The following parts introduce the most popular description methods for asynchronous design, explain them and list some of their properties. Though the descriptions of the methods in this chapter do not fully show all their properties and capabilities, they are meant to be sufficient to give a good understanding of the methods and their underlying concepts.

### 2.1 Problems in asynchronous circuit design

The following list shows the typical problems in asynchronous circuit design extracted from Chapter 1.

**Timing** Even though the choice of timing models is more related to the circuit synthesis, the timing assumptions inherent to a description method are also very important to evaluate. Moreover, only methods that allow the specification of time bounds can be used to describe circuits in the bounded delay class.

**Communication** The communication in asynchronous circuits has many variants. Parameters such as the employed handshaking protocol, signal coding, the activeness and passiveness of ports must all match for successful communication between two circuits. The possibilities to chose these parameters in the description methods will be evaluated.

**Arbitration** One of the most important functional block in asynchronous circuits is the arbiter. While it prevents failure due to metastability, its unnecessary use where requests are known not to occur simultaneously decreases the performance and increases the area requirements of a circuit. Description methods thus should allow the description of mutual exclusion with or without the use of an arbiter. This will be evaluated using a merge block with optional arbitration. Also note that the metastability filter as part of the basic arbiter is an analog circuit that cannot be described using other building blocks such as the bare arbiter.

**Concurrency** Since an asynchronous circuit is a highly concurrent system with explicit synchronisation required for every communication, it is important to be able to describe it as such. Description methods should allow the description of concurrent functional block and the synchronisation between them.

**Sequence** Every description also contains events that are required to be sequential. For this purpose, a description method should provide a convenient way to define causal order between events.

**Level/Event sensitivity** A description method is said to be level sensitive, when the behaviour of circuits is described using signal levels. An event sensitive description method on the other hand, uses events which can range from transitions on wires to complete synchronised communications for the description of the circuit's behaviour.

**Level of abstraction** Similarly to synchronous circuits, a higher level of abstraction simplifies the design of complex circuits but hides some implementation details that might be important for simpler circuits. Each description method will be analysed for the abstractions it uses and the effects they have on the expressiveness of the method.

**Modularity and parametrisation** A key concept allowing feasible descriptions of complex circuits is modularity, which allows commonly used circuit blocks to be described as modules and then instantiated wherever they should be used. A further improvement is the possibility to describe parametrised modules which can be assigned parameters at the time of instantiation, allowing one module to describe several similar circuits thus improving it's applicability. It will be evaluated whether the description methods allow previously described blocks to be reused within another description.

#### 2.2 Production Rule Sets

As the first and at the same time the least abstract description method, the *Production* Rule Sets (PRS), originating from the Caltech asynchronous synthesis tools (CAST) [25] as an intermediate representation, will be described. The description is a summary of [11] and [26].

Production rules are based on Dijkstra's guarded commands [27] and have a very similar notation and semantics. A production rule (PR) is a construct of the form  $G \mapsto S$  where G is a Boolean expression called the guard of the production rule and S is a single or a comma separated list of assignments. The assignments can only be as simple as setting variables to a high or low logic level, in the sequel only referred to as true and false. The notation of an assignment which sets variable x to true is  $x \uparrow$ , for setting x to false it is  $x \downarrow$ . The guard can be any Boolean expression with one or more variables, however, some limitations to allow direct mapping to CMOS circuits and their correct operation apply.

The guards are restricted to be stable, which means that if the evaluation of the guard changes from *false* to *true*, it must remain at this value until the execution of the assignment. Two PRs that assign different values to the same variable are called

complementary and implement an operator. It is required, that for the guards  $G_1$ ,  $G_2$  of complementary PRs

$$\begin{array}{c} G_1 \mapsto x \uparrow \\ G_2 \mapsto x \downarrow \end{array}$$

$\neg G_1 \lor \neg G_2$  always holds. In other words, it is not allowed for two PRs to simultaneously assign different values to the same variable. This property is called *non-interference*. Additionally, if  $G_1 \lor G_2$  holds at all times, the variable x is always held at a logic level and the implemented operator is called *combinational*. If, however,  $\neg G_1 \land \neg G_2$  can hold at any time, x will by definition hold its last value in that time and the resulting operator is called *state holding*.

The concurrent composition of multiple production rules is called a *production rule set* (PRS). The behaviour of circuits described as blocks of interconnected PRSs is equivalent to the set union of all the PRs they contain with PRs specifying the connecting wires, in the form of identity functions, added to the set. In case two different PRs  $G_1 \mapsto S$  and  $G_2 \mapsto S$  have the same assignment at their right hand side, they are replaced by the new rule  $G_1 \vee G_2 \mapsto S$ .

The correspondence of operators described in PRs and the mapping to their CMOS implementations is straight-forward, possibly even direct. In a typical CMOS circuit, where *true* is represented by a positive voltage while *false* is represented by pulling a wire to ground, an operator is implemented by a P-stack of transistors pulling the output high and an N-stack of transistors pulling it low. The operation of each stack is controlled by a Boolean function of the inputs. This is equivalent to a simple assignment in PRs as the controlling functions for the P-stacks and the N-stacks are equivalent to guards of PRs that set a variable to *true* or *false*, respectively. See Figure 2.1 for clarification.

To allow a direct mapping of operators to their implementations, there is a restriction on the Boolean functions in the guards. For a negative assignment  $(x \downarrow)$ , the guard can only contain non-negated input variables. This allows to connect inputs directly to the gates of n-channel FETs. For a positive assignment  $(x\uparrow)$ , only negated forms of input variables can be used to allow the connection to p-channel FETs. Note that this limitation is reversed for some implementations of state-holding operators, where an additional inverter is placed at the output (e.g. the static implementation as shown below). The requirement of noninterference for complementary PRs prevents short circuit paths between the positive voltage supply and ground to be opened in operators by evaluating both guards to true. However, non-interference does not affect the presence of intermittent short circuits as a result of dynamic circuit behaviour.

In the implementation, also the difference between combinational and state holding operators becomes clear. Combinational operators force their output to the supply voltage or ground at all times. The output always has a 'strong' level. The state-holding operator, however, has states where neither the P-stack nor the N-stack are driving the output, which remains floating. The implementation has to ensure that its level does not change until it is driven again. In a *dynamic* implementation, this is done by timing assumptions ensuring that the output value will be used (or driven again) before it loses its charge and changes to an undefined level. An additional capacitor can be used to prolong this time. In a *static* implementation, a storage element such as that in Figure 1.5 is added to the

Figure 2.1: The CMOS implementation of a combinational operator with x being the variable in the assignment [26].

circuit to drive the output with the value assigned last.

As mentioned before, PRSs are the least abstract description method in this work, working with single operators, possibly equivalent to a transistor netlist. Handshaking protocols thus have to be implemented explicitly, every transition needs to be modelled.

As a simple example, the following PRS describes a fork block (see Section 1.2.4) with dataless push channels using RTZ four phase handshaking with all wires initially low. In the description, a is the input channel, x and y are the output channels and the *ack* and *req* indexes refer to the acknowledge and request wires the channels are composed of. The optional reset circuitry is omitted.

$$a_{req} \mapsto x_{req} \uparrow, y_{req} \uparrow$$

$$\neg a_{req} \mapsto x_{req} \downarrow, y_{req} \downarrow$$

$$x_{ack} \land y_{ack} \mapsto a_{ack} \uparrow$$

$$\neg x_{ack} \land \neg y_{ack} \mapsto a_{ack} \downarrow$$

As can be seen, the first two PRs implement a combinational operator with the identity function. This can be implemented with a simple wire fork with no transistors needed. The other two PRs implement a state-holding operator — a Muller-C element. Non-interference is trivially fulfilled. Stability has to be guaranteed by the environment. In this case, adherence to the four phase protocol is enough to ensure stability of the guards.

As mentioned at the beginning of this section, PRS are used as an intermediate representation in the CAST toolchain [25]. PRS are usually automatically generated using decompositions and transformations from a higher level description (see Section 2.6.3) but they can also be used as the design entry description method. Since PRS can already be straightforwardly mapped to CMOS operators, the further processing of PRS in the CAST toolchain is already part of the physical design. As a first step, the description is transformed into *extended production rule sets* (XPRS), where transistor sizing and gate ordering are added. The final step is the chip layout design using a place and route tool, which is also part of the CAST toolchain.

#### 2.3 Asynchronous Finite State Machines

A finite state machine (FSM) is a graphical model of an abstract computing device used to describe the behaviour of programs and digital circuits. It consists of a finite number of states, a function describing the transitions between the states and a function generating the outputs. An equivalent model used in formal computer science or mathematics is called a *finite transducer* or, if the only output is a Boolean variable (often used as indication of the acceptance of an input sequence), a *finite automaton* and both are backed up by rigorous theory. The two most common FSM models were introduced by Mealy [28] and Moore [29] and at present, these models are described in virtually every coursebook for digital design.

Formally, a finite state machine is a sextuplet  $FSM = (\Sigma, \Gamma, S, s_0, \delta, \omega)$ , where:

- $\Sigma$  is the input alphabet

- $\Gamma$  is the output alphabet

- S is the finite non-empty set of states

- $s_0$  is the initial state

- $\delta$  is the state transition function

- $\omega$  is the output function

At the beginning of a computation, each FSM is in its initial state  $s_0$ . The actual operation of an FSM consists of a possibly infinite sequence of atomic computing steps, each theoretically performed in zero time and incorporating these actions:

- Read the input. Formally, an FSM reads symbols, which are elements of  $\Sigma$ , from the input. For hardware description, the symbols represent states of all input wires.

- Perform a state transition according to the state transition function  $\delta: S \times \Sigma \mapsto S$ .

- Generate output according to the output function  $\omega$ . Formally, an output symbol from  $\Gamma$  is written to an output tape. The symbol can represent states of all output wires for hardware description.

There are two common alternatives for the output function  $\omega$  for FSMs. For a Moore FSM, the output function is  $\omega : S \mapsto \Gamma$ . That means that the output is only a function of the current state. In a Mealy FSM, the output function is defined as  $\omega : S \times \Sigma \mapsto \Gamma$ , therefore making the output dependent on the current state as well as the current input<sup>1</sup>. Although the Mealy FSM model seems to be mightier than the Moore FSM model, they are actually equivalent.

FSMs are most commonly represented in two ways, either graphically or with a table. The graphical representation is a labelled directed graph in which the vertexes represent the states, the initial state being drawn thickly, while the edges labelled with input values (symbols) represent the state transition function. The description of the outputs differs

<sup>&</sup>lt;sup>1</sup>The inputs are only read at the beginning of a computation step and therefore the current input is always the input that was read before the state transition.

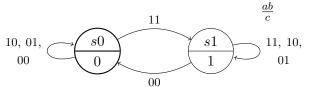

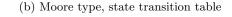

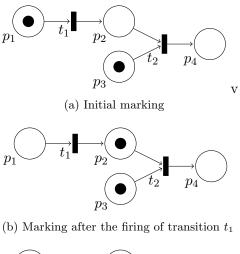

| ~      |               | input (ab) |    |    |    |  |

|--------|---------------|------------|----|----|----|--|

| it (c) | next<br>state | 00         | 01 | 10 | 11 |  |

| utpı   | s0/0          | s0         | s0 | s0 | s1 |  |

| ate/o  | s1/1          | s0         | s1 | s1 | s1 |  |

(a) Moore type, graphical representation

(c) Mealy type, graphical representation

(d) Mealy type, state transition table

Figure 2.2: An FSM describing a Muller C-element.

between the Moore and Mealy FSM. In a Moore FSM, the output values for each state are defined in the labelling of the vertexes. In a Mealy FSM, where more output values are possible for the same state depending on the input, the edges are labelled with the output that should be generated after the corresponding state transition. An example of the graphical representation of an FSM describing a Muller C-element with the inputs a, b and an output c can be seen in Figure 2.2a as a Moore FSM and Figure 2.2c as a Mealy FSM.

The tabular representation, called *state transition table*, is a table in which each row represents one state and each column one input value. For each state, the cells record the next state the FSM should change to after receiving the input corresponding to the column. The outputs to be generated, for a Moore FSM, are specified together with the states, one for each row. A Mealy FSM requires the outputs to be specified in the cells, one for each row/column combination. As an example, the same state machine like above, described with a state transition table, can be seen in Figure 2.2b for the Moore FSM and Figure 2.2d for the Mealy FSM.

Finite state machines are very efficient in describing circuit behaviour because they model functionality without considering the temporal behaviour of the implementation. For synchronous circuits, this is appropriate — the typical implementation of a FSM consists of a register holding the current state carefully clocked such that all combinational paths have finished evaluation and all signals are stable. The clock edge then initiates a new computing cycle by updating the state in the register which causes the next state to be generated.

In asynchronous circuits, however, time cannot be so easily abstracted away. For example, it is not possible to input zeros on a multiple wire bus as one symbol and ones on the same wires as the following symbol without observing the intermittent state of mixed zeros and ones on the wires as they are switching. Without timing assumptions or limiting the state transition function to use only inputs that can be recognised from previous ones, it is not possible to know when the switching is finished and the values on the wires represent a consistent input. Additionally, even when all accepted inputs are such that no

Figure 2.3: Example of a FSM fraction that cannot be implemented with a SIC fundamental mode AFSM

intermittent value represents a valid input which might cause a wrong transition, the state transition function must be designed to produce hazard-free outputs even with multiple inputs changing.

#### 2.3.1 Fundamental Mode Asynchronous Finite State Machines

The approach for the design of asynchronous circuits initiated by Huffman in [30] uses timing assumptions for both the circuit and the environment.

The environment that Huffman circuits operate in must adhere to the restriction that after a change on one input wire, the circuit is given enough time to stabilise before another input is allowed to change. An asynchronous FSM (AFSM) operating in such an environment is said to operate in *single input change* (SIC) *fundamental mode*. The stabilisation of the circuit is effectively the evaluation of the next-state function resulting in a state transition which, depending on the state machine's behaviour, may trigger another state change for the same inputs. Only after the FSM reaches a stable state, that is, a state in which for a given input the state transition function assigns the same state to be the next, the inputs may change again. The minimum time between two input changes is thus limited by the speed of the FSM and as a logical consequence, the gate and wire delay within the circuit have to be bounded to be able to determine this time.

A further requirement is that also the signals internally generated as the evaluation of the next-state function must adhere to the SIC fundamental mode. This is a consequence of the missing temporal masking of hazards as in synchronous FSMs. Practically, this means that additional delays have to be inserted in the feedback path of the state signals.

The SIC fundamental mode operation, however, also imposes limitations on the expressiveness of a state machine. As an example, consider the behaviour modelled by the FSM fragment in Figure 2.3. State S0 is a stable state with the input values being '00' (only incoming transition). If the designer wished to change to one state (S1) if a single input becomes high and to another (S2) if both become high, such an FSM would work without problems in the synchronous implementation. The SIC restriction, however, makes state S2 unreachable, as always one of the inputs have to change first and the circuit has to be given time to perform a state transition, which in this case would change the FSM to the state S1. This also applies to state signals, where a direct transition from a state encoded with '00' to a state encoded with '11' is not possible, if the intermittent signal values '01' or '10' could lead to different stable states.

#### 2.3.2 Burst-Mode Asynchronous Finite State Machines

To weaken the strong assumptions about the environment in SIC fundamental mode AF-SMs, *burst-mode* AFSMs were introduced.

Burst-mode AFSMs also work in fundamental mode, but restricted *multiple input* change (MIC) is allowed — predefined sets of transitions, so called *bursts*, are allowed to occur concurrently without any timing assumptions placed upon them. Even though AF-SMs allowing restricted MIC could also be described using one of the formalisms described above, the term "burst-mode AFSM" also refers to a new state machine formalism. In this work, every reference to burst-mode AFSMs refers to this formalism.

The formal definition of a burst-mode FSM, taken from [31], reveals the slight differences to standard FSMs as described above, especially in the description of the state transitions. A burst-mode FSM is a labelled directed graph,  $BM = (V, E, I, O, v_0, in, out)$ , where:

- V is a finite set of vertices (describing the states)

- E is the set of edges (describing the transitions)

- *I* is the set of inputs

- O is the set of outputs

- $v_0$  is the initial state

- *in* is a labelling function describing values of inputs in each state

- *out* is a labelling function describing values of outputs in each state

The edges  $E \subseteq V \times V$  form a relation describing which transitions are possible from each state. I and O are simply sets of input or output signals respectively, e.g.  $I = \{a, b\}$ and  $O = \{x\}$  for a circuit with inputs a, b and an output x. At the beginning of its operation, a machine is in the initial state,  $v_0$ . The functions  $in : V \to \{0, 1\}^{|I|}$  and  $out : V \to \{0, 1\}^{|O|}$  assign values of the input and output signals respectively to each state. While out is equivalent to the output function  $\omega$  in classical Moore-type FSMs (see the introduction of Section 2.3), the function in, rather than specifying which state the machine should change to with given inputs, as the state transition function  $\delta$  does, assigns the values of all inputs to each state, called its unique entry point. This implies, that no matter from where the machine changes to a state v, the input values have to be exactly in(v). This does not restrict the expressiveness of the notation, since specifications that do not meet this requirement can be transformed to valid ones by splitting states.

Although the behaviour of a burst-mode AFSM is described with the set of states, edges between them and functions labelling the states, in the graphical representation the more practical labelling functions for the edges are used. The functions are called  $trans_i : E \to \mathcal{P}(I)$  and  $trans_o : E \to \mathcal{P}(O)$  and they label each edge with a subset of input and output signals respectively that change their value between their source and destination state. In the label,  $trans_i$  is separated from  $trans_o$  with a slash and each signal name is augmented with a '-' or '+' depending on whether the signal changes from trueto false or vice versa. Apart from the requirement for each state to have a unique entry point, there is another restriction for valid burst-mode AFSM: Given some state, no possible input burst can be a subset of another one originating from the same state (formally,  $\forall v, u_1, u_2 \in$ V,  $trans_i(v, u_1) \subseteq trans_i(v, u_2) \Rightarrow u_1 = u_2$ ). This is called the *maximal set* property and eliminates the possibility of ambiguous behaviour of state machines when, after a valid input burst, it could either perform a state transition or wait for other inputs to change to complete another valid input burst.

An example of a tool for circuit synthesis from an AFSM representation is 3D, which was developed initially at Stanford University and later at the University of California, San Diego, from where it is currently available. It uses *extended burst mode* (XBM) AFSMs, introduced in [32] for circuit descriptions. Those add the possibility of sampling level sensitive signals as conditions for state transitions and *directed don't cares*, which allow to expand the path between a rising and a falling transition of a signal over multiple states by describing its value to be undefined in intermittent states. 3D uses the synthesis method described in [33, 34]. Another example is the toolkit *MINIMALIST* [35], developed at Columbia University, which is composed of different tools performing tasks such as state minimisation, state encoding and logic minimisation.

#### 2.4 Signal Transition Graphs

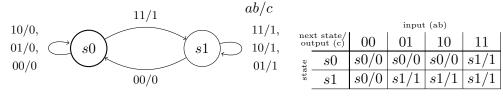

The first part of this section will describe *Petri nets*, a powerful graphical description method commonly used for the modelling of concurrent systems. *Signal transition graphs* (STGs) are the most common description method for asynchronous circuits using Petri nets and will be described in the second part of this section.

#### 2.4.1 Petri Nets

*Petri nets* (PN) are another graphical representation of an abstract machine performing a computation, which can be used to describe asynchronous circuits. They were introduced by C. A. Petri in [36]. An excellent source for information on Petri nets is [37].

Petri nets can be seen as a generalisation of finite state machines — each FSM can be directly transformed into an equivalent PN (see page 25). The advantages of PNs, compared to FSMs, are the ability to model concurrent, asynchronous, distributed systems and non-determinism, which allows the application of PN theory to prove properties like the absence of deadlocks.

Formally, a Petri net is a sextuple  $PN = (P, T, F, W, K, M_0)$ , forming a weighted directed bipartite graph consisting of interconnected *places* and *transitions*.

- *P* is the finite set of places

- T is the finite set of transitions

- F is the flow relation

- W is the weight function

- *K* is the capacity function

#### • $M_0$ is the initial marking

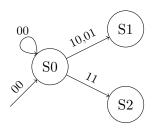

In the graphical representation, places are drawn as circles, transitions as possibly filled rectangles. The flow relation  $F \subseteq (P \times T) \cup (T \times P)$  defines the arcs of the graph. Note that since Petri net graphs are bipartite, only interconnections of places with transitions are possible. The directed arcs define the predecessor/successor relations — all places connected to a transition with incoming arcs are called *predecessor* places and ones connected with an outgoing arc are called *successor* places. The same applies with places and transitions reversed.

The state of a PN is given by its marking  $M : P \to \mathbb{N}_0$ , that assigns a non-negative amount of tokens, depicted as filled circles inside places in the graphical representation, to each place. The initial marking  $M_0$  describes the marking of a PN at the beginning of a computation. The weight function  $W : F \to \mathbb{N}$  assigns each arc a weight, equivalent to its multiplicity. The capacity function  $K : P \to \mathbb{N}$  assigns each place the maximal amount of tokens it can hold. A Petri net in which the capacity function is not defined, therefore all places have unbounded capacity, is called an *infinite capacity net*. When K bounds the capacity of places, the resulting net is referred to as a *finite capacity net*. Each finite capacity net can be transformed to an equivalent infinite capacity net.

Petri nets in which places are allowed to hold multiple tokens are useful for describing processes in a higher level. For example, one place could describe a FIFO buffer and the transitions connected to it would represent events adding and removing objects from that buffer. When describing circuits, however, PN transitions represent transitions of input or output signals and whether a place has a token or not is usually implemented as the logic value of a wire. To keep a close relationship between a PN and the resulting circuit, *1-bounded* Petri nets are used for the description of circuits. A Petri net is 1-bounded when every place has the capacity of maximally one token (formally,  $\forall p \in P$ , K(p) = 1). As each place in a 1-bounded PN can only have one or no tokens, using edges with weight more than one would permanently disallow the firing of the transition being either the source or the destination of such an edge. A PN, in which every edge has weight one is called *ordinary*. In the following, 1-bounded ordinary Petri nets are assumed. Note that such PNs can be specified without the weight and capacity function.

The semantics of Petri nets can be described with just a few rules:

- Transitions in which all predecessor places have tokens are *enabled*.

- All enabled transitions must eventually fire.

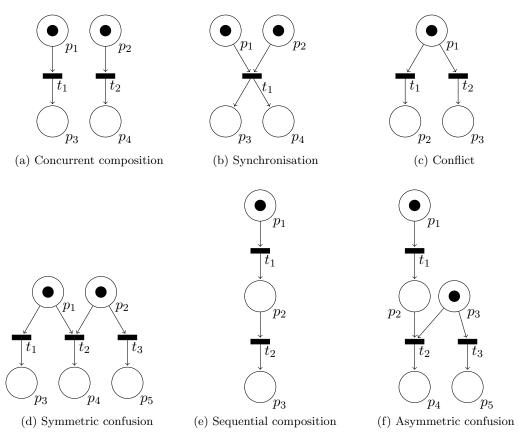

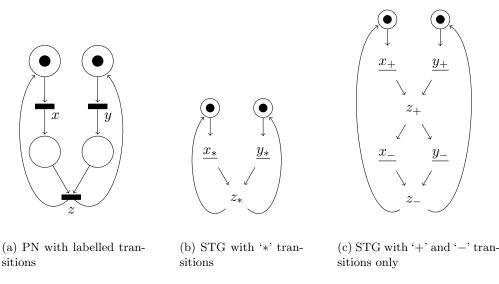

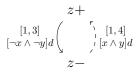

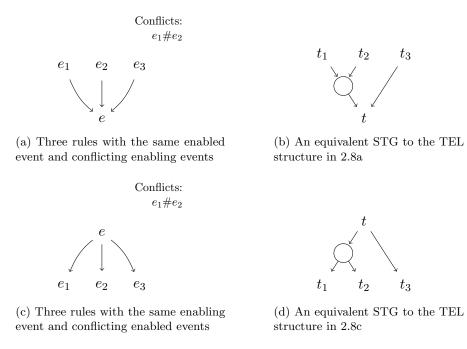

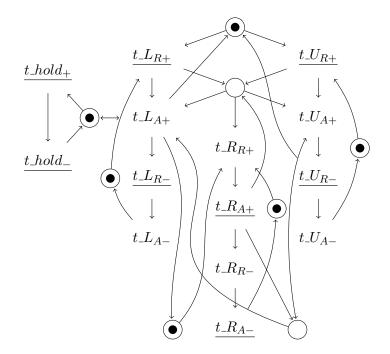

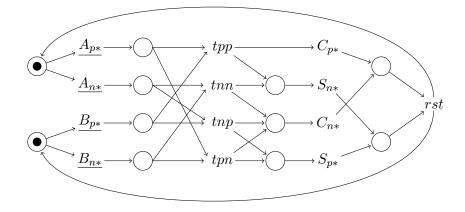

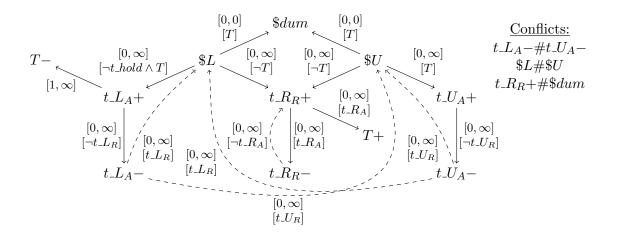

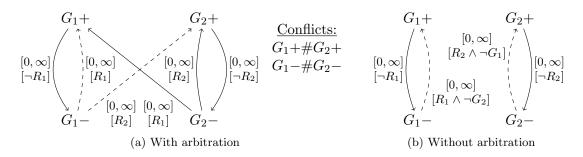

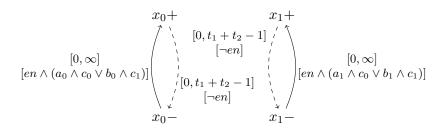

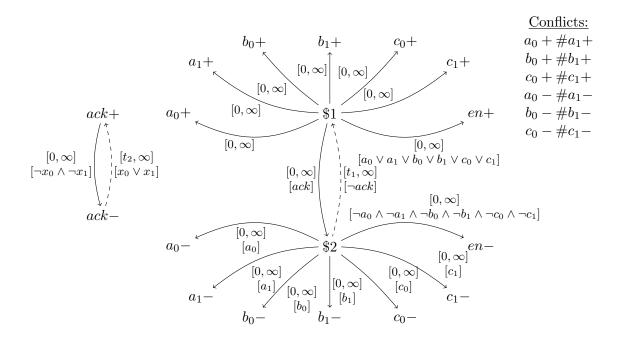

- When a transition fires, tokens are removed from all predecessor places and added to all successor places.