### DISSERTATION

# Ultra-Thin InAIN/AIN Barrier Enhancement-Mode High Electron Mobility Transistors

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

unter der Leitung von

Univ.-Prof. Dr. Gottfried Strasser Institut für Festkörperelektronik

eingereicht an der

Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

### DI Clemens Ostermaier

Mat.Nr. 0225978 Haymogasse 121 AUT-1230 Wien

Wien, im Jänner 2011

1. Gutachter : Univ. Prof. Dr. Gottfried Strasser

2. Gutachter : Univ. Prof. Dr. Nicolas Grandjean

Tag der mündlichen Prüfung: 03. Februar 2011

It is meant to answer a few questions but raise many more

#### Abstract

For the last two decades, significant and rapid advances in the growth and technology of III-N related semiconductors have yielded exciting performance for optical and electronic devices. Laser diodes from green to ultra-violet and light-emitting diodes based on gallium nitride and related wide band materials are already in mass production. Electron devices have shown outstanding results by high electron mobility transistors (HEMTs) utilizing the strong polarization from the III-N wurzite crystal structure. The excellent electronic properties such as high electric field strength due to the large bandgap, high saturation and overshoot electron velocity, and good thermal conductivity, make GaN-based transistors ideal for high power, high speed, and high temperature applications in harsh environments. In order to improve the efficiency, circuit design and safety of today's power amplifiers and converters, HEMTs with high current density, low on-state resistance, high breakdown voltage, operation in enhancement mode (E-mode, normally-off), and reliable surface passivation to minimize electron trapping are highly desired.

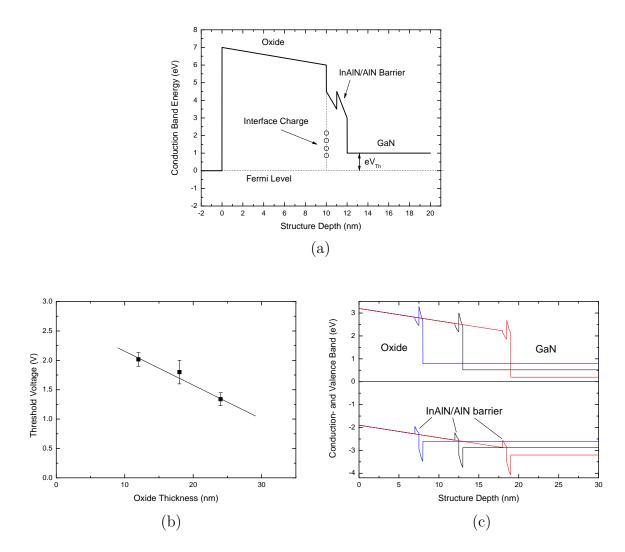

The main subject of this work is the design and realization of a high electron mobility transistor with a barrier thickness (2 nm) much below conventional devices, attaining enhancement-mode operation. The thinnest stress-free barrier could be realized using lattice-matched InAlN on GaN. The usual trade-off in enhancement-mode devices between the on-resistance and the threshold voltage has been extended by developing a novel passivation scheme using a highly doped GaN cap layer together with a selective recess process for the gate. This cap layer provides a state-of-the-art carrier density in the access region and shields the device channel from charge variations at the surface. This unique independency of surface traps was proven to be free of drain current dispersion without additional passivation, promising excellent device reliability. Another important design parameter for enhancement-mode devices is the surface potential of the barrier layer. Due to the lack of exact measurement methods of the surface potential, new characterization techniques have been developed allowing the investigation of the effective potential at Schottky and metal-oxide gates. Integration of those results led to an improved design of the ultra-thin barrier device with gate insulation, achieving a threshold voltage above +2V and a maximum feasible gate bias of 10V.

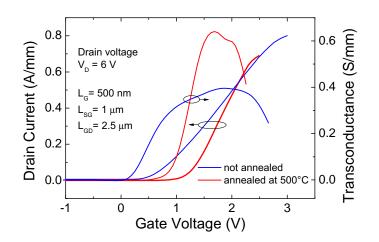

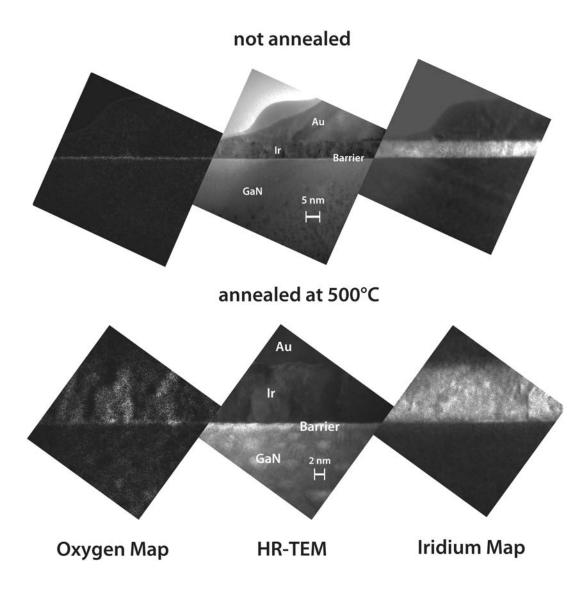

The thin barrier allows detailed analysis of the gate stack, which led to the discovery of a gate sinking effect for GaN devices. This effect was linked to diffusion of oxygen from an interfacial layer into the iridium gate metal and could be utilized to fabricate devices with record transconductance of 640 mS/mm for GaN HEMTs in normally-off operation.

#### Zusammenfassung

Die rasante Entwicklung von III-N Halbleitern während der letzten zwei Jahrzehnte begründet sich durch in die drastischen Erfolge in der Herstellung von optischen und elektrischen Bauteilen auf diesem Materialsystem. Laserdioden vom grünen bis zum ultraviolettem Spektralbereich sowie Leuchtdioden (LEDs) haben bereits ihre Tauglichkeit für die Massenproduktion bewiesen. Im Bereich der elektronischen Bauteile überzeugt der High-Electron Mobility Transistor (HEMT) mit außerordentlichen Leistungen dank der starken Polarisation des Wurzitkristalls von III-N Materialien. Die hohe elektrische Durchbruchsfestigkeit, die große Bandlücke, sowie die hohe Sättigungsgeschwindigkeit der Elektronen und gute Wärmeleitfähigkeit versprechen gute Anwendbarkeit von GaN Bauteilen im Hochleistungs-, Hochfrequenz- und Hochtemperaturbereich. Für die Verbesserung der Effizienz und der Sicherheit moderner Leistungsverstärker bzw. konverter sind Bauteile mit hohen Stromdichten, niedrigen Durchlasswiderständen, hohen Durchbruchsspannungen und zuverlässigen Oberflächenpassivierungen erwünscht. Besonders gesucht sind dabei Transistoren die sich ohne Schaltspannung am Gate im ausgeschalteten Zustand befinden (Anreicherungstyp, normally-off, enhancementmode).

Der Hauptteil dieser Arbeit beschäftigt sich mit der Entwicklung und Fertigung von GaN Transistoren (HEMT) mit sehr dünnen Barrierendicken (2 nm), welche eine positive Schwellspannung möglich machen. Die Barriere besteht dabei aus InAlN, welches bei entsprechendem Indiumanteil die gleiche Gitterkonstante besitzt wie GaN und daher zu keinen Verspannungen im Bauteil führt. Der übliche Kompromiss zwischen Durchlasswiderstand und Schwellspannung konnte durch die Entwicklung einer hoch dotierten GaN Schicht über der Barriere und dem dazu notwenigem Atzprozess für den Gatefuß erweitert werden. Diese Schicht dient nicht nur dazu, den Elektronenkanal hochleitend zu machen, sondern schirmt ihn auch vor äußeren elektrischen Einflüssen ab. Aufgrund der Unabhängigkeit von Oberflächenzuständen zeigt der Kanalstrom dieses Bauelementes keinerlei Dispersionseffekte und verspricht daher ausgezeichnete Zuverlässigkeit. Ein weiterer wichtiger Parameter für das Design von GaN Transistoren mit positiven Schwellspannungen ist das Oberflächenpotential der Barriere. Da in der Praxis keine exakten Messmethoden am bestehenden Bauteil existieren, wurden im Rahmen dieser Arbeit neue Wege zur Charakterisierung entwickelt. Diese können dazu verwendet werden, das Oberflächenpotential unter dem Gate und an der Grenzfläche zu Oxiden zu berechnen. Durch die Anwendung dieser Methoden konnte das oben beschriebene Design durch zusätzliche Isolationsschichten des Gates verbessert werden, wodurch Vorwärtsspannungen am Gate bis zu 10 V ermöglicht wurden.

Die Möglichkeit der präzisen Herstellung dieser 2 nm dünnen Barrieren ermöglichte weiters die genaue Analyse der parasitären Gatekapazitäten. Dadurch wurde der Ef-

fekt des "Gate Sinkings" entdeckt, welcher in ähnlicher Form bereits von GaAs Bauelementen bekannt ist. Durch elektrische und materialtechnische Untersuchungen wurde herausgefunden, dass sich zwischen Gatemetall und Barriere eine Sauerstoffhaltige Zwischenschicht bildete, welche bei höheren Temperaturen in das Gatemetall hineindiffundiert. Durch Ausnutzung dieses Effektes konnte die bis dahin höchste je gemessene Steilheit von 640 mS/mm bei GaN Transistoren mit positiven Schwellspannungen erreicht werden.

## Contents

| 1 | Intr                                                        | oduction                                                                                                                                               | 1                        |

|---|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 2 | <ul><li>111-N</li><li>2.1</li><li>2.2</li><li>2.3</li></ul> | N Electron Devices         Wide Bandgap Electronics         Benefits and Challenges of III-N Materials         InAlN - an alternative Barrier Material | <b>5</b><br>5<br>8<br>10 |

| 3 | Dev                                                         | ice Physics and Basic Technology                                                                                                                       | 13                       |

|   | 3.1                                                         | Basic Model of GaN HEMTs                                                                                                                               | 13                       |

|   | 3.2                                                         | Device Targets for Power HEMTs                                                                                                                         | 17                       |

|   | 3.3                                                         | Dispersion Effects                                                                                                                                     | 20                       |

|   | 3.4                                                         | Device Technology                                                                                                                                      | 23                       |

|   | 3.5                                                         | Characterization Techniques                                                                                                                            | 27                       |

| 4 | Nov                                                         | el Characterization Methods for HEMTs                                                                                                                  | 31                       |

|   | 4.1                                                         | Schottky Barrier Height Analysis by CV Method                                                                                                          | 31                       |

|   | 4.2                                                         | Characterization of Charge Injection Dual Gate Analysis                                                                                                | 40                       |

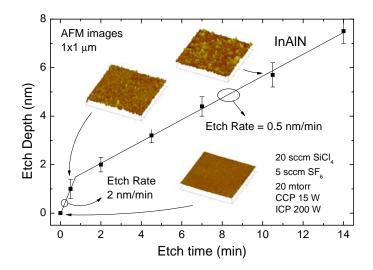

| 5 | Plas                                                        | ma-based Recessing of InAIN HEMTs                                                                                                                      | 53                       |

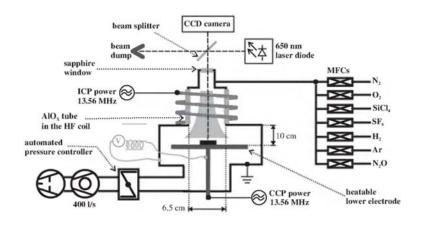

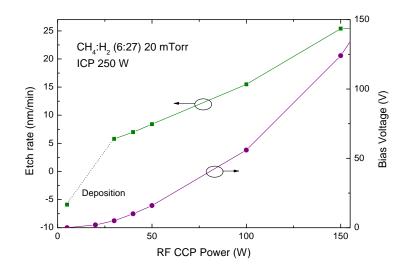

|   | 5.1                                                         | Inductively-Coupled Plasma RIE                                                                                                                         | 54                       |

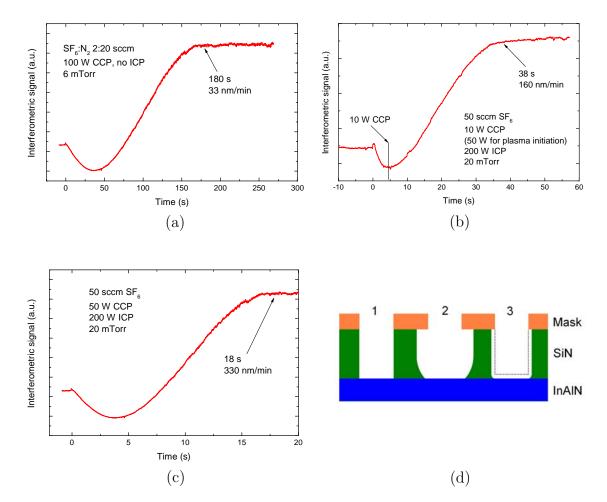

|   | 5.2                                                         | Recessing of Dielectrics on InAlN-Barrier Devices                                                                                                      | 55                       |

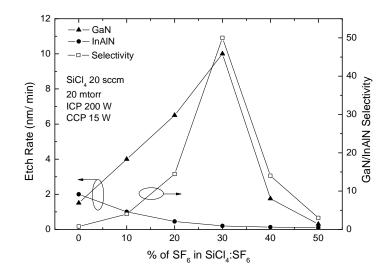

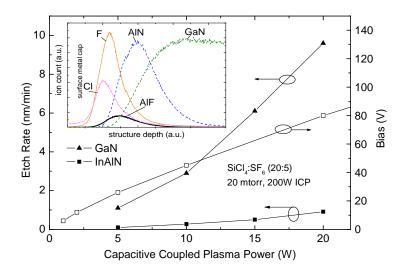

|   | 5.3                                                         | Selective Recessing of GaN over InAlN                                                                                                                  | 59                       |

|   | 5.4                                                         | InAlN Surface Oxidation by Oxygen Plasma                                                                                                               | 67                       |

|   | 5.5                                                         | Summary                                                                                                                                                | 69                       |

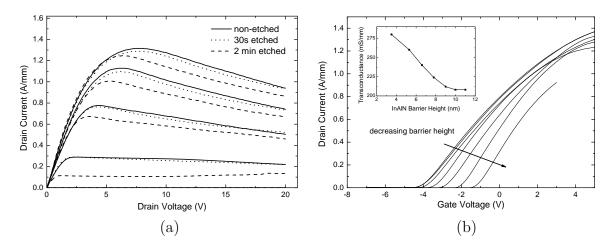

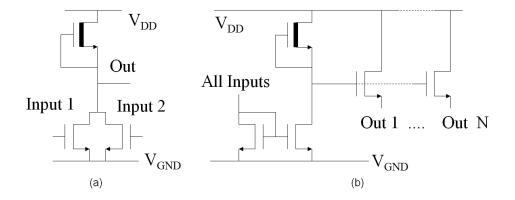

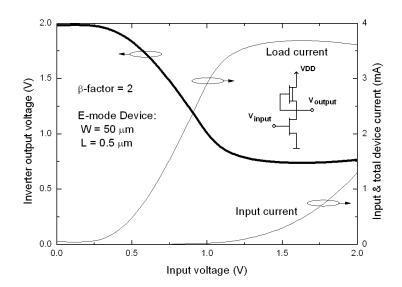

| 6 | Enh                                                         | ancement-mode Device with Surface Passivation by GaN Cap                                                                                               | 71                       |

|   | 6.1                                                         | Advantages and Challenges of E-mode Devices                                                                                                            | 71                       |

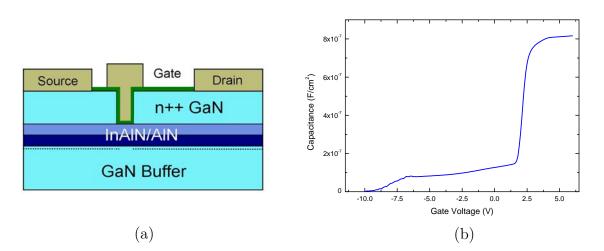

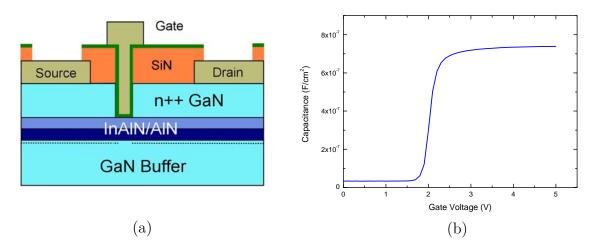

|   | 6.2                                                         | Device Idea and Structure                                                                                                                              | 73                       |

|   | 6.3                                                         | Device Fabrication                                                                                                                                     | 76                       |

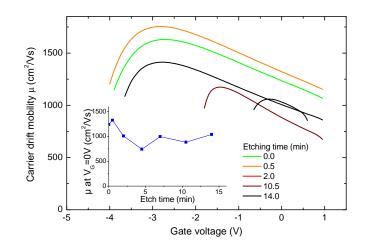

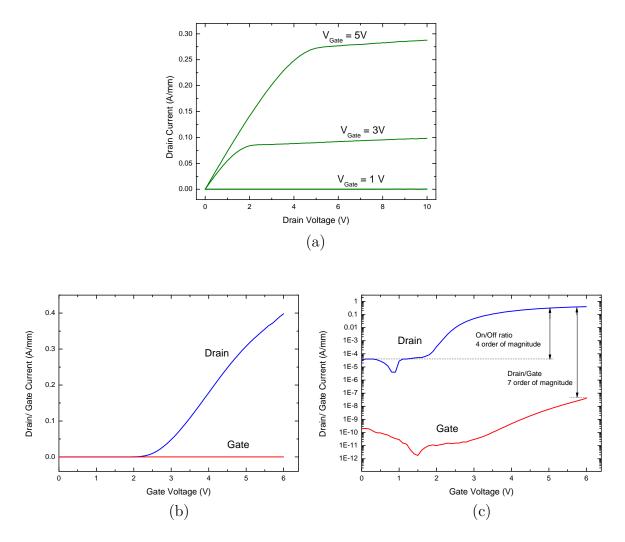

|   | 6.4                                                         | Experimental Results of E-mode Devices                                                                                                                 | 78                       |

|   | 6.5                                                         | Depletion-mode HEMTs                                                                                                                                   | 81                       |

|   | 6.6                                                         | Effect of $n^{++}$ GaN Cap on Access Resistance                                                                                                        | 83                       |

|   | 6.7                                                         | Application-based Device Variation                                                                                                                     | 85                       |

|     | 6.8    | Summary                                                                 | 93  |

|-----|--------|-------------------------------------------------------------------------|-----|

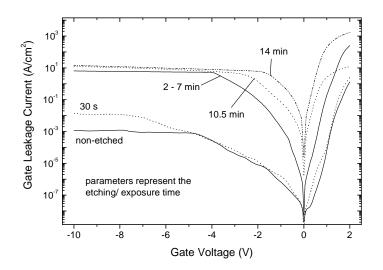

| 7   | Ana    | lysis of Gate Sinking in Ultra-Thin Barrier Devices                     | 95  |

|     | 7.1    | History                                                                 | 95  |

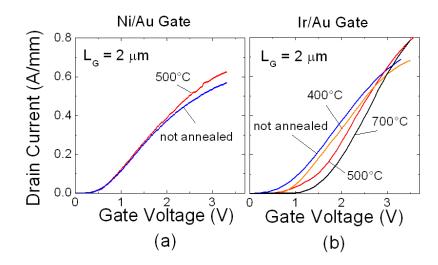

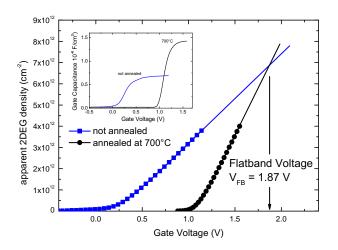

|     | 7.2    | High-Gain Devices through Gate Sinking                                  | 96  |

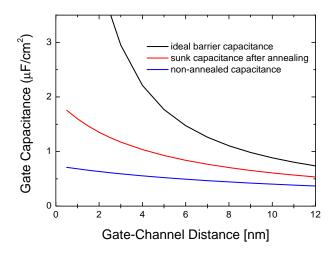

|     | 7.3    | Capacitive Analysis of Sinking Process                                  | 98  |

|     | 7.4    | Nanostructural Analysis                                                 | 103 |

|     | 7.5    | Summary                                                                 | 106 |

| 8   | Out    | look and Future Ideas                                                   | 107 |

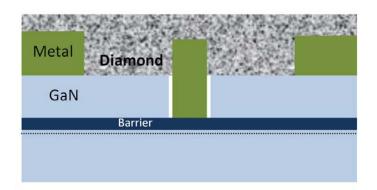

|     | 8.1    | GaN Cap Surface Passivation for direct Diamond Overgrowth $\ . \ . \ .$ | 108 |

|     | 8.2    | In-situ SiN Passivation                                                 | 109 |

|     | 8.3    | Self-aligned sub-nm Devices                                             | 110 |

|     | 8.4    | Improved Ohmic Contacts by Gradual InN Interlayer                       | 113 |

|     | 8.5    | GaN Power Switches                                                      | 113 |

|     | 8.6    | Charge Injection Mechanism into Passivation Layer                       | 114 |

| Ap  | openc  | lix A: Wafer Data Sheet                                                 | 115 |

| Ap  | opend  | lix B: MATLAB Code for CV Simulation                                    | 119 |

| Bi  | bliog  | raphy                                                                   | 121 |

| At  | brev   | iations                                                                 | 137 |

| Lis | st of  | Publications                                                            | 141 |

| Ac  | know   | vledgements                                                             | 147 |

| Cu  | ırricu | lum Vitae                                                               | 149 |

### **1** Introduction

Energy has become the number one issue in our society triggering new political and economical conflicts and processes. Increasing population and the ongoing request for market growth in order to increase or sustain social wealth has driven us into higher energy production and created new challenges for our local and global environment. Several alternative energy production solutions have been developed but are currently often too expensive or not sufficient to achieve significant market relevance and therefore sometimes have been replaced by conservative methods [1]. In addition to new methods for power generation, a lot of research and development has been done to increasing the efficiency along the whole power supply chain including the production, distribution, transformation, and the power conversion in consumer products. This issue has become very dominant as today's total energy efficiency, concerning the released energy from burning gas or the potential energy of water in comparison to the final service provided at the consumer, as extracted light or heated water, is typically below 10% [2].

The majority of today's electronic applications uses semiconductor devices replacing conventional electronic parts due to their improvement in complexity and capacity [3]. On one hand, these new technologies led to smaller, faster, and more energy efficient solutions. On the other hand, the increase of modern services in information technology caused also a rise of the total power consumption. Therefore, the efficiency of semiconductor devices has an enormous impact on the amount of required energy.

A very promising group of materials for this challenge are nitride-based wide bandgap semiconductors. The market penetration of high power nitride-based light-emitting diodes (LEDs) has been only the beginning of new electronic devices increasing the energy efficiency compared to conventional ones. The benefits of a larger bandgap are twofold [4, 5]. First, the increasing gap between the conduction band, filled with holes, and the valence band, filled with electrons, allows emission of photons with higher energy. Thus, blue, green, and even ultra-violet (UV) light sources (LEDs and laser diodes LDs) could be demonstrated [6, 7, 8, 9, 10, 11, 12]. Second, wide band semiconductors provide high electric strength as their bandgap is comparable to insulators [13, 14]. Hence, smaller devices with higher power density can be realized enabling higher frequencies and reducing losses compared to conventional semiconductors.

Latter case, which will be discussed further in chapter 2, has triggered a lot of efforts

to design highly efficient power devices for low and high frequency applications. One of the promising radio frequency (RF) applications for GaN-based devices will be in base stations for wireless communication [15, 16, 17, 18, 19, 20]. Achieving higher efficiency in combination with thermally robust devices should permit the reduction of cooling efforts and thus reduce energy consumption and costs twofold. Frequency performance above 100 GHz has been demonstrated for applications in radar systems mainly designed for military purposes [21, 22]. The main target application for lower frequency classes is the conversion of electrical power. New energy concepts as smart grid systems [23] require frequent transformation between energy distribution systems, energy storage systems and consumers. Even though conversion efficiencies above 96% are already standard, multiply transformations required for alternative energy sources as off shore wind generators reduce the overall performance. Therefore, gallium nitride based devices capable of high efficient and high temperature stable power electronics are needed as part of an efficient energy solution.

Nitride-based materials include indium nitride (InN), gallium nitride (GaN), aluminum nitride (AlN), and their ternary and quaternary compounds [24]. Sequential twodimensional growth of those materials allows a great freedom in the design of semiconductor devices. Similar to other III-V material systems based on arsenides, phosphides, and antimonide, two-dimensional electron gases can be achieved in III-N heterostructures. This allows the implementation of high electron mobility transistors (HEMTs) with enhanced mobilities and improved device characteristic by quantum confinement of the electrons compared to bulk structures.

While most results were shown on AlGaN/GaN barrier devices, InAlN/GaN based HEMTs have demonstrated high power and high temperature performance recently, constituting a new class of devices with even higher electron densities. However, high performance has been demonstrated only for normally-on transistors, which are not suitable for switching applications. In case of a failure, normally-on transistors open the channel providing a minimum resistance between source and drain which causes a short circuit. Therefore, normally-off or enhancement-mode (E-mode) devices are required to provide fail-safe operation.

The main part of this work is dedicated to the demonstration of a novel enhancementmode device structure using an ultra-thin barrier layer. Scaling the device barrier down to only 2 nm revealed new insight into the technology and physics of such devices. In addition, the design includes a new concept to reduce RF dispersion, which is still an important technological challenge in InAlN-barrier devices, by applying a surface cap on top of the barrier. The design is therefore suitable for RF and switching power applications. The impact of this cap on the device has been modeled and investigated.

Furthermore, a novel measurement technique analyzing the effective Schottky barrier height in a heterostructure Schottky gate was developed. Thus, detailed investigations of the electric potential at the gate are possible which is crucial for the design of normally-off devices. In cooperation with Prof. Kohn's group from Ulm University, an earlier proposed device technique was used to characterize the charge injection into surface passivation layers under long-time stress conditions leading to time delayed degradation and breakdown of the device.

#### **Outline of the Thesis**

After a brief motivation in the introduction, chapter 2 summarizes the key aspects of wide bandgap semiconductors with a few more details on III-nitride based materials including a discussion on the novel InAlN. This material has been investigated primarily as alternative barrier layer replacing the conventional AlGaN. Chapter 3 reviews the basic device physics and technological background necessary to understand the experimental chapters of this work. The presented content is seen as an impulse to the interested reader rather than a complete review. In addition, this part shows some general contributions from this work in the technology and characterization of GaN HEMT devices at the Vienna University of Technology. The main results of this work are summed up in the chapters 4 to 8. All experimental results include references to the fabricated substrate material listed in appendix A.

Chapter 4 presents two individual characterization methods which have been developed within the frame of this work and are closely related to the investigated device topics. In 4.1 an alternative Schottky barrier height method by capacitive measurement is shown. 4.2 reviews dual gated HEMT devices applied for device reliability measurements related to the surface passivation. Chapter 5 is dedicated to dry etching techniques on InAlN surfaces and focuses mainly on the recess technology of the ultrathin barrier device. The electrical results, physical models and simulation as well as application based variations of this novel normally-off design are presented in chapter 6. Furthermore, chapter 7 explains a gate sinking effect which was discovered on the same device due to the large capacitance of the ultra-thin barrier layer. Finally, a few project ideas which have been discussed and partially investigated within the frame of this work are summarized in chapter 8.

### 2 III-N Electron Devices

Some of the successful demonstrators of GaN devices have been already mentioned in the introduction. The following parts will briefly review the physical aspects of III-N materials in respect to other semiconductors with special focus on the recent developments in InAlN barrier devices. Further readings with supplemental information about wide bandgap semiconductors can be found in [25, 4, 26, 27, 5].

#### 2.1 Wide Bandgap Electronics

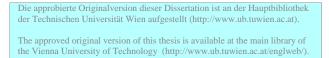

In contrast to metals, the Fermi level in semiconductors lies within an energetic gap without electronic states. Charge transport is therefore only possible by electrons in the conduction band or holes in the valence band. This splitting of the bands originates from bonding and anti-bonding states of the semiconductor material [28]. Most semiconductors of interest consist of a wurzite, zinc blende (diamond), or rock salt crystal structure. Depending on the semiconductor lattice, the position and width of the bandgap differs. Therefore, different semiconductor materials provide fundamentally different electric properties for electrons and holes with regards to their lattice structure, atoms, binding mechanism, and other aspects. Figure 2.1 shows the fundamental bands of wurzite GaN in different lattice directions. The minimum gap between conduction band and valence band determines the relevant bandgap for electrons and holes including their transport properties [28]. The bandgap for GaN with zinc blende lattice structure is slightly smaller. Its symmetric structure causes a non-polar lattice, which is of interest in optical applications. However, due to the growth difficulties of this metastable phase most efforts have been done on the hexagonal configuration.

The potential of certain semiconductor materials can be judged by theoretical criteria combined in so called figure of merits. Johnson defined such a parameter (JFOM = Johnson's Figure of Merit) in respect to the power-frequency product [30] taking into account the bandgap energy  $E_G$  and saturation velocity  $v_{sat}$ . Another figure of merit (KFOM) was specified by Keyes et al. which includes the thermal limitation in addition to the switching performance of the transistors [31]. Therein, the thermal conductivity  $\kappa$ , the dielectric constant  $\varepsilon_r$ , and  $v_{sat}$  are considered. Table 2.1 summarizes

Figure 2.1: Band structure (a) of conduction and valence band in wurzite GaN based on theoretical calulcations [29]. Fig. (b) shows the crystal directions of figure (a) based on the unit lattice cell.

some important electrical parameters of a few intensively investigated wide bandgap semiconductor materials in comparison to conventional ones as silicon or GaAs. It can be noted that diamond provides the largest bandgap and therefore also a high critical electric field for breakdown  $E_B$  in addition to an extremely good thermal conductivity  $\kappa$ . Gallium arsenide is the material with the highest mobility  $\mu$ . However, the saturation velocity is slightly above the value for silicon. Further the low breakdown strength in GaAs makes it a less applicable candidate for high power applications. SiC and GaN (hcp, hexagonal close-packed) are the intermediate candidates between GaAs and diamond, providing a large bandgap >3 eV, higher mobilities and saturation velocities compared to silicon and better thermal conductivity than GaAs.

Applying the electrical parameters from table 2.1 in order to derive the figure of merits for high power applications reveals the comparison listed in table 2.2. As expected diamond exceeds others by far. The apparent advantage of GaN to SiC regarding JFOM almost vanishes if the drop of the velocity saturation at high field (shown in brackets in tab. 2.1) is taken into account. On the other hand the lower outcome of GaN from KFOM due to the reduced thermal conductivity  $\kappa$  is also less relevant as GaN is commonly grown on foreign substrates including SiC [34] and diamond [35]. The theoretical thermal conductivity was found to be comparable to SiC [33]. However, defects, doping and oxygen impurities reduces the heat transport in epitaxially grown layers below 2 W/cmK [36, 37]. Higher values were only shown for bulk GaN layers [38].

Even though, diamond has clear benefits from a material aspect, it has not yet achieved

|           | $E_G$ [eV] | $\mu \; \left[ {\rm cm}^2 / {\rm Vs} \right]$ | $\kappa$ [W/cmK] | $E_B[MV/cm]$ | $v_{sat} \left[ 10^7  \mathrm{cm/s} \right]$ | $\varepsilon_r$ |

|-----------|------------|-----------------------------------------------|------------------|--------------|----------------------------------------------|-----------------|

| Si        | 1.12       | 1400                                          | 1.3              | 0.3          | 1                                            | 11.9            |

| GaAs      | 1.4        | 8500                                          | 0.55             | 0.55         | 1.2                                          | 10.9            |

| 4H-SiC    | 3.3        | 900                                           | 4.9              | 3            | 2                                            | 9.7             |

| 6H-SiC    | 3          | 400                                           | 4.9              | 3            | 2                                            | 9.7             |

| GaN (hcp) | 3.4        | 2000                                          | 4.1(1.3)         | 5            | 2.7(1.3)                                     | 8.9             |

| Diamond   | 5.5        | 2200                                          | 20               | 5.6          | 2.7                                          | 5.7             |

Table 2.1: Electrical parameters of several important semiconductor materials at room temperature (300K). Values in bracket correspond to measured results deviating from theoretically predicted values. [32, 33].

|           | JFOM | KFOM |

|-----------|------|------|

| Si        | 1    | 1    |

| GaAs      | 5    | 0.5  |

| 4H-SiC    | 400  | 5.3  |

| 6H-SiC    | 400  | 5.3  |

| GaN (hcp) | 1736 | 1.6  |

| Diamond   | 2540 | 25.3 |

Table 2.2: Comparison of semiconductor materials after Johnson's and Keyes' figures of merits [30, 31].

comparable device results [39]. One of the causes of wide bandgaps in semiconductors is the increased binding energy caused by decreasing atomic radius, leading to advanced challenges in the technologies of such materials. Consequently, higher bandgaps often involve increasing complexity in growth of the bulk material and the understanding of atomic surface behavior [40]. Therefore, the maturity of the technologies for such materials needs to be taken into account in addition to the results in table 2.2. The development of silicon technology has been strongly pushed by the early success of semiconductors and the fact that the native oxide on silicon provides an excellent controllable and stable interface. While diamond has been intensively studied in the early 90's, it was soon surpassed by activities on GaN with high expectations of new efficient lighting sources based on III-N LEDs. This rapid start on nitride activities has caused a wide understanding of this material which also benefited the development of electric devices. Today's activities are concentrated in cost effective solutions to be competitive with conventional devices in silicon and silicon carbide.

#### 2.2 Benefits and Challenges of III-N Materials

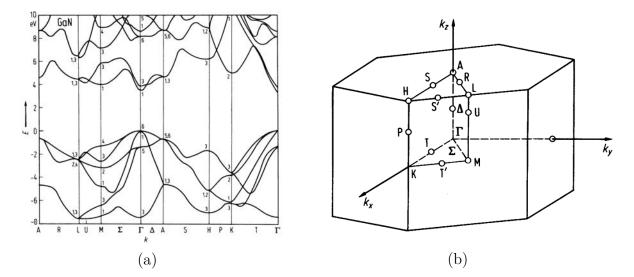

The group III-N semiconductor materials with wurzite lattice as shown in figure 2.2 consist of the binary materials GaN, AlN, and InN, the ternary alloys AlGaN, InGaN, and InAlN (blue lines), and the quaternary InAlGaN (grey area). Most electron devices based on III-N materials consist of a relaxed GaN buffer layer (chapter 3). Therefore, the lattice mismatch of any other layer needs to be considered in respect to GaN. Strongly non-relaxed layers can only be grown up to a certain thickness - the critical thickness. Even though stress in AlN on GaN produces a very inhomogeneous layer for thicknesses >1 nm [41], recently thicker layers without cracking have been demonstrated using in-situ SiN passivation [42]. Reducing the aluminum content to around 20% in AlGaN layers allows growing crack-free layers on GaN exceeding 30 nm. InAlN with an indium ratio of 17% can be grown lattice-matched to GaN [43]. Therefore, the vertical red line in figure 2.2 indicates all quaternary compounds with the same lattice constant as GaN.

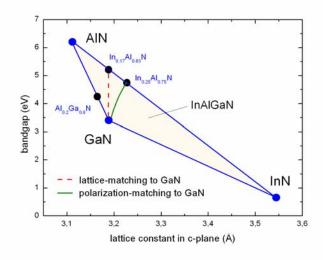

The ideal wurzite structure consists of symmetrical tetrahedrons of equal side length and equal angles. However, the wurzite configuration of III-N is distorted due to the strong ionic bonding caused by the metal-nitrogen bond [24]. Nitrogen has a small atomic radius and a high electron negativity causing a shift of the charge center away from the metal. Among III-N materials, this shift is highest for AlN and smallest for InN. The crystal structure for the two possible orientations can be found in figure 2.3.

Figure 2.2: Bandgap versus lattice constant of III-N semiconductors. The lines regarding ternary compounds do not consider the bowing factor. [44, 45, 24].

The main orientation that is used is along the [0001] direction, which corresponds to the vertical axis in figure 2.1b. The corresponding [0001] plane perpendicular to its direction is also referred to as c-plane following the notation of the lattice constants. The distorted wurzite lattice modifies the triple bonding structure of the tetrahedron in the horizontal c-plane (Fig. 2.3) in contrast to the vertical direction. Therefore the rotational symmetry in the [0001] plane sustains, causing zero net polarization. However, the distortion in [0001] direction results in a dipole moment throughout the whole lattice. This effect occurs without any external impact. Hence, it is called spontaneous polarization. It was found, that the dipole moments in III-N materials are up to ten times larger than in conventional III-V and II-IV compound semiconductors, except ZnO, where comparable values have been reported [46]. Due to the lattice orientation, the polarization in Ga-face and N-face lattices is reversed (Fig. 2.3) [24].

When external mechanical stress is applied, the polarization effect can be increased or decreased depending on the direction of the stress. This effect is called piezoelectric polarization, and is found when heterostructures with different lattice constants are grown subsequently without stress relaxation. In electronic devices, this effect can be utilized to increase the total polarization, consisting of the spontaneous and the piezoelectric polarization, in order to achieve higher electron densities (chapter 3) as in AlGaN/GaN heterostructures. Alternatively, the total polarization can be reduced, by reversing the stress. Growing heterostructures of materials with compositions along

Figure 2.3: Wurzite structure of GaN in Ga-face and N-face polarity. [47, 48].

the green line in figure 2.2, results in polarization-matched layers. The lattice stress therein caused by increasing indium content compensates the spontaneous polarization. Recently, it has been demonstrated, that such structures can be used to achieve normally-off devices [44]. However, the quality of indium-rich layers is strongly reduced as high stress is required to balance out the spontaneous polarization.

Growing heterostructures with materials of different bandgaps allows a lot of freedom in the design of complex electronic and optoelectronic devices, enabling i.e. terahertz emission in quantum cascade lasers [49] far below the bandgap energy. However, the strong electric polarization causes a distortion of the wells and barriers by the induced electric field. This field originates from interface charges induced by the terminated polarization at any boundary of a material layer. The induced electric field separates the charges within quantum wells and can lead to a significant reduction in the efficiency of optoelectronic structures. The polarization effects can be eliminated by growing on non-polar orientations of hexagonal III-nitride crystals [50, 51]. In electron devices, however, the two-dimensional charge layer formed by the polarization induced field is utilized to create strong confined channels with high electron mobilities.

#### 2.3 InAIN - an alternative Barrier Material

The first experiments on lattice-matched InAlN (referring to GaN) have been performed by Kubato et al. in 1989 revealing a smaller bandgap than GaN [43]. Combining lattice-matched heterostructures allows growing thick layers without introducing stress. The high aluminum content (83%) in lattice-matched (LM) InAlN causes a higher polarization compared to conventional AlGaN barriers with typical <30% aluminum [45, 52]. Consequently, the lattice-matched InAlN/GaN heterostructure offers a few advantages. Any described InAlN in this thesis is therefore lattice-matched with an indium/aluminum ratio of about 17/83.

Early experiments have shown that the critical thickness to form a two-dimensional electron gas (2DEG) in InAlN/GaN heterostructures is around 10 nm [45, 41, 53]. Thinning down the barrier compared to conventional AlGaN HEMTs with a typical barrier thickness above 20 nm allows shortening the gate to channel distance (chapter 3). This is very important in short-channel devices, where it has been shown that short-channel effects become dominant for gate lengths shorter than 15 times the gate-to-channel distance [54]. Hence, reducing the barrier thickness by more than a half compared to AlGaN device enables shorter gate lengths. The maximum frequency of a device is limited by the carrier transit time across the gate [55]. Therefore, shorter gate lengths allows higher frequency performances.

In frequency ranges up to 10 GHz, the gate length is not as much of an issue as for frequencies above. Therefore, the question arises whether a thinner barrier would actually lead to a better performance. So far reasonable InAlN/GaN devices have been demonstrated with current densities between 1 and 2 A/mm and corresponding breakdown voltages of 100 to 50 V, respectively [56, 57, 58, 59, 60]. These devices demonstrated a maximum output power above 10 W/mm at 4 GHz and prove a first technological step but still do not equalize or exceed the performance achievements shown on AlGaN barrier HEMTs [61]. There, breakdown voltages above 1000 V have been demonstrated on RF devices using electric field plates on the drain side of the gate [62, 63, 64, 65]. But even without field plates, breakdown voltages of 400 V have been demonstrated. In order to achieve such performance with InAlN devices, a surface passivation with sufficient high critical electric field is required, which also allows reliable large signal operation at radio frequencies.

The biggest advantage of InAlN that could clearly be demonstrated so far is the extreme robustness against harsh environments. In 2006, it was shown that devices with InAlN barriers are feasible to operate at 1000°C in vacuum [66]. Later on, Maier et al. found out that the damage in devices operated for many hours at 700 and 800°C was caused only by the degradation of the metals while the heterostructure did not reveal any damage [67, 68]. New metal schemes have been proposed [69] allowing overgrowth of fully fabricated devices with nano-crystalline diamond [70, 71]. Thus, even higher robustness against corrosion can be achieved. In addition, the excellent heat conductivity of diamond allows spreading the heat created in the device directly from its surface to a larger heat sink.

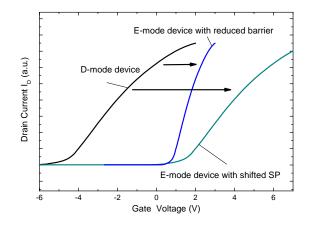

The first enhancement-mode device on InAlN barrier HEMTs was demonstrated by implantation of fluorine into the barrier [72]. Authors argued that negative charges in the barrier were the cause of the increase of the threshold voltage, similarly as it has been shown on AlGaN devices [73]. However, the electric characteristic of such devices was proven to be not very reliable. In 2010, a high performing recess HEMT has been demonstrated achieving 2.4 A/mm with a barrier layer of 3 to 4 nm [74]. The device achieved a record transconductance but exhibited a slightly negative threshold voltage. Recently, thermal oxidation of a 6 nm AlN barrier produced a positive threshold voltage even though the current density decreased drastically compared to its original value before oxidation [42].

In 2006 a new mechanism of device degradation was proposed by Joh et al. [75, 76, 77]. Authors reported on a field induced, non-recoverable damage caused by reversed gate bias. Further studies revealed that this effect seemed to correlate with the preexisting mechanical stress in the barrier. Reverse biasing of the gate increases the stress due to inverse-piezoelectric forces until the mechanical stress creates defects and electrical traps responsible for increasing gate leakage [77, 78]. However, it remains controversial, whether this effect applies only to highly stressed barriers as i.e. in high aluminum content AlGaN [79]. A comparative study on lattice-matched InAlN has demonstrated the absence of piezo-inverse degradation for such devices.[80].

# 3 Device Physics and Basic Technology

The provided topics presented in this chapter should offer the knowledge foundation for the following experimental chapters. As there exists already a large number of excellent books [81, 82, 83] on those issues, the topics are only briefly introduced.

#### 3.1 Basic Model of GaN HEMTs

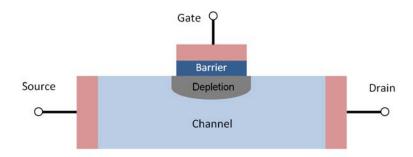

The general model of a field-effect transistor (FET) consists of a capacitively coupled gate electrode which controls the carriers in the channel flowing from source to drain (Fig. 3.1). Therefore it is important to insulate the gate in order to minimize parasitic current through the gate. In metal-oxide-semiconductor (MOS) FETs the gate is isolated by an oxide layer. Alternatively, the gate electrode can be implemented with a Schottky barrier providing a metal-semiconductor structure which is called MES-FET. The Schottky barrier provides a good insulation in reverse direction but needs to be operated carefully under forward bias. While MOSFETs build up the basis for silicon devices due to the high quality oxide interface achievable with silicon oxide, different approaches are often chosen for compound semiconductor devices. Using a higher bandgap material as barrier in combination with a lower bandgap material for the channel is the basic idea of heterojunction FETs (HFETs). The gate contact can be realized either by a Schottky contact similar to MESFETs or with an additional oxide layer (MOS-HFET). Since the barrier in a HFETs is a semiconductor itself, it can be doped. The bandgap discontinuity between the higher conduction band in the barrier and the lower one in the channel causes a depletion of the barrier layer and provides free carriers in the channel. These carriers form a high density layer at the interface, which is called the two-dimensional electron or hole gas (2DEG/2DHG). The latter refers to the analog case in the valence band. As the realization of hole channels is feasible but requires more technological challenges, most devices in GaN include an electron channel. The separation of dopants and free carriers in addition to the high carrier density reducing the Debye length [55] minimizes the scattering of electrons and allows higher mobilities above typical conduction band mobilities in bulk layers. Such devices

Figure 3.1: Basic structure of a field-effect transistor with source, drain and gate electrode.

are therefore also named high electron mobility transistors (HEMTs), even though in the most relevant high electric field applications for GaN-based devices, the electron velocity is limited by the saturation velocity  $\nu_s$ . In GaAs or InP devices the doping in the barrier can be increased until a separate channel in the barrier is formed. Thus the electron density is limited by the bandgap discontinuity [83].

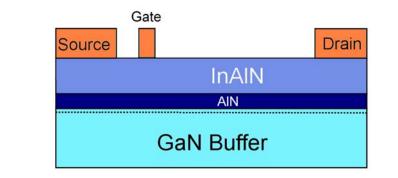

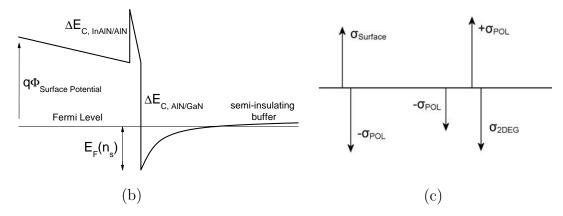

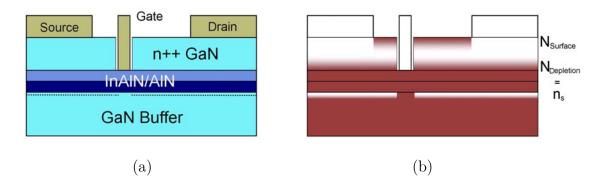

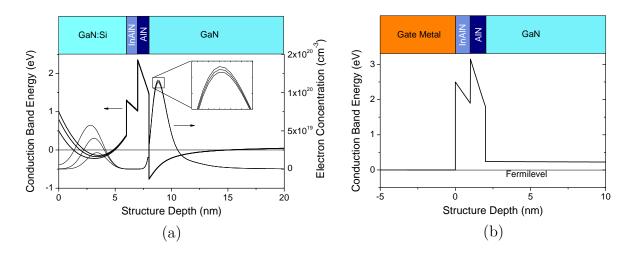

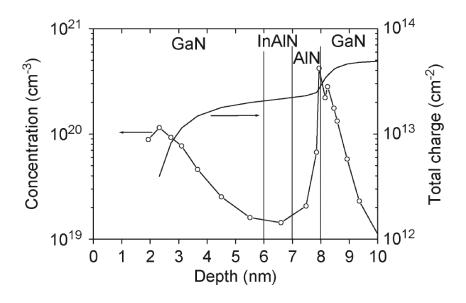

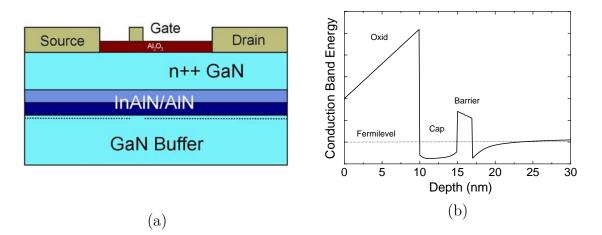

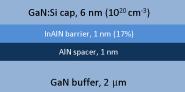

A typical GaN-based HEMT with corresponding conduction band structure and charge distribution diagram is shown in figure 3.2. In contrast to the schematic FET in figure 3.1, the channel in the heterostructure FET is confined below the barrier while the buffer itself is not conducting. The barrier consists of an InAlN/AlN heterostructure. Even though the source and drain contacts are placed on top of the barrier, reasonable ohmic contacts to the channel layer can be achieved.

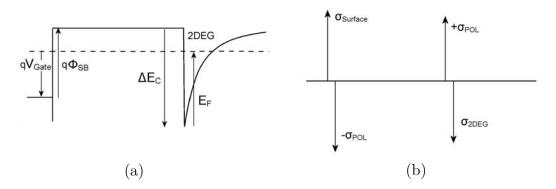

FETs based on wurzite-type GaN in [0001] direction (c-plane) exhibit a polarization which causes a large potential drop over the barrier (Fig. 3.2b). This potential drop allows achieving higher electron concentrations in the channel compared to conventional doping of the barrier layer. Enlarging the barrier thickness increases the potential at the free surface. It was found that surface donors are responsible for pinning the surface at a fixed surface potential [84]. The ionized donors create a positive surface charge density  $n_{Surface}$  which counters the free carriers in the channel  $n_s$ . Consequently, no channel would form considering an ideal surface without ionized surface donors until the potential drop across the barrier causes a 2DHG at the surface. The charge diagram in figure 3.2c shows the negative fixed charge density  $n_{pol,Surface} = \sigma_{pol,Surface}/q$  at the surface formed by the spontaneous and piezoelectric polarization P of the barrier. The positive fixed interface charge density at the 2DEG  $n_{pol,Interface} = \sigma_{pol,Interface}/q = -[P]/q$  depends on the difference in spontaneous polarization between the barrier and the buffer and the piezoelectric polarization of the barrier. The latter component

(a)

Figure 3.2: Schematic of epitaxial structure (a) of a typical GaN-based HEMT with an InAlN barrier and an AlN spacer including gate, source and drain metal electrodes. Band structure (b) and charge diagram (c) refer to a vertical cut through the device stack with a free surface.

depends on the stress in the barrier given by the difference in the lattice constant between the buffer and the barrier layer [48, 47, 85]. The charge balance across the barrier without the additional AlN interlayer can be written as

$$n_{Surface} + n_{pol,Surface} = n_{pol,Interface} - n_s, \tag{3.1}$$

Considering such a pinned surface allows defining the 2DEG density  $n_s$  by [86]

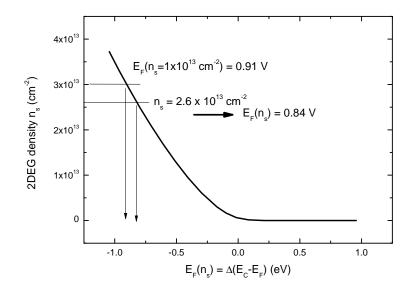

$$n_s = n_{pol,Interface} - \frac{\varepsilon_{Barrier}}{d_{Barrier} \cdot q} \left( \Phi_{SP} + \frac{E_F(n_s)}{q} - \frac{\Delta E_{C,Barrier/GaN}}{q} \right), \tag{3.2}$$

where  $\varepsilon_{Barrier}$  and  $d_{Barrier}$  is the dielectric contant and thickness of the barrier,  $\Phi_{SP}$ is the surface potential of the free surface being equal to the Schottky barrier height (SBH)  $\Phi_{SB}$  at the gate contact,  $E_F(n_s)$  is the energy difference between the conduction band at the bottom of the 2DEG and the Fermi level,  $\Delta E_C$  is the bandgap discontinuity between barrier and channel, and q is the elementary charge of an electron (Fig. 3.2). For simplicity, equation 3.2 corresponds to the homogenous barrier without AlN spacer in contrast to figure 3.2.

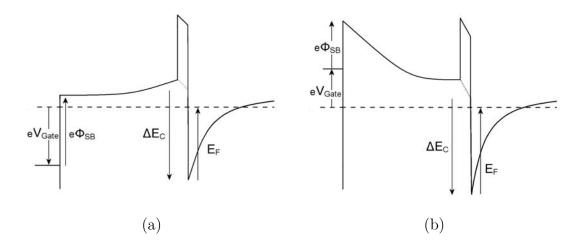

The threshold voltage, defined for the case of zero charge in the 2DEG below the gate  $(n_s = 0)$ , can be calculated setting equation 3.2 zero and considering the gate electrode using  $\Phi_{SP} = \Phi_{SB} - V_{Gate}$ :

$$V_{Th} = V_{Gate} \left( n_s = 0 \right) = \Phi_{SB} - \frac{\Delta E_C}{q} - \frac{q \cdot n_{pol,Interface}}{C_{Barrier}} = V_{bi} - \frac{q \cdot n_{pol,Interface}}{C_{Barrier}}, \quad (3.3)$$

where  $C_{Barrier}$  is the barrier capacitance and  $E_F(n_s) = 0$  for  $n_s = 0$ . The build-in voltage  $V_{bi}$  of the total gate contact is defined by material parameters. The threshold voltage depends therefore mainly on the 2DEG charge and the barrier capacitance. Taking into account the high polarization charge in GaN devices, a surface potential of around 1 eV, and typical barrier thicknesses >10 nm, reveals a threshold voltage  $V_{Th} < 0$ . From a technological point of view either the surface potential  $\Phi_{SP} = \Phi_{SB}$  or the barrier capacitance can be modified. Therefore, for a given surface potential, the gate capacitance needs to fulfill the following condition in order to achieve a normallyoff (enhancement-mode, E-mode) device with  $V_{Th} > 0$ :

$$C_{Barrier} > \frac{q \cdot n_{pol,Interface}}{\Phi_{SB} - \frac{\Delta E_C}{q}}.$$

(3.4)

Applying the described charge model, one can specify the source-drain current in the

transistor using the gradual channel approximation by the Schottky model [55]

$$I_{DS} = \mu C_{Gate} \frac{W_G}{L_G} \times \left( V_{DS} \left( V_G - V_{Th} \right) - \frac{V_{DS}^2}{2} \right), \tag{3.5}$$

which leads to a quadratic tendency on the gate bias in drain current saturation

$$I_{DS} = \mu C_{Gate} \frac{W_G}{L_G} \times \frac{(V_G - V_{Th})^2}{2}.$$

(3.6)

Therein,  $I_{DS}$  is the source-drain current,  $V_{DS}$  the corresponding voltage,  $C_{Gate}$  the gate capacitance (basically equal to  $C_{Barrier}$  in case of a HEMT),  $\mu$  the electron mobility, and  $W_G$  and  $L_G$  are the gate width and length, respectively. However, this equation is only valid for electron velocities  $\nu < \nu_s = \mu E_c$ , where  $\nu_s$  is the saturation velocity and  $E_c$  the corresponding critical field in the channel.  $E_c$  can be estimated macroscopically by the critical voltage  $V_c = E_c L_G$ . The mobility in GaN-based HEMT devices is usually above  $1000Vs/cm^2$  and hence the electron velocity reaches saturation for even small biases. In examples, electrons in a 1 µm long gate channel reach the saturation velocity at about 1.3 V. A first approximation of the velocity saturation can be achieved by a two-piece model [81], assuming a linear increase of the electron velocity until the electric field in the channel reaches  $E_c$ . Using this approach, the following expression was found [81]

$$I_{DS} = \mu C_{Gate} \frac{W_G}{L_G} \times V_c^2 \left[ \sqrt{1 + \frac{(V_G - V_{Th})^2}{V_c^2}} - 1 \right].$$

(3.7)

This equation be simplified using the approximation  $V_G - V_{Th} > V_c$

$$I_{DS} \approx C_{Gate} W_G \times \left( V_G - V_{Th} - V_c \right) \nu_s. \tag{3.8}$$

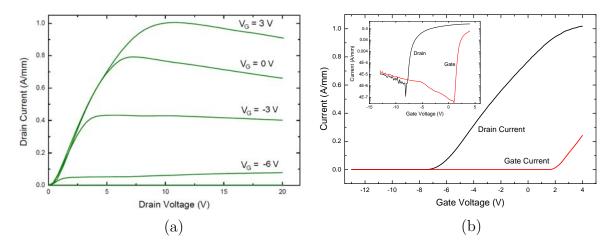

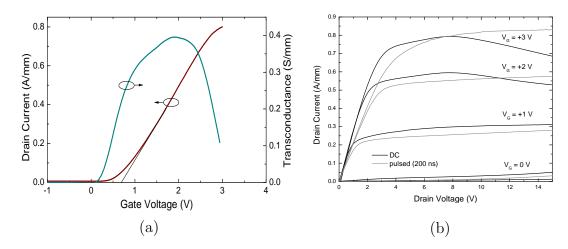

It shows that the transfer characteristic is linearly dependend on  $V_G$  due to the velocity saturation in contrast to long-channel transistors. This is also indicated by currentvoltage (IV) measurements of typical devices showing a linear transfer characteristic above 1 V.

#### 3.2 Device Targets for Power HEMTs

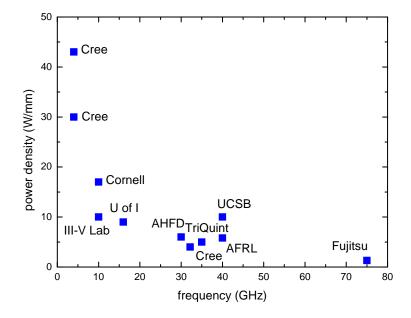

The material parameters from chapter 2 already suggest a strong focus on power applications for GaN-based devices. Therefore two major branches exist: high frequency

Figure 3.3: Summary of state-of-the-art RF power HEMTs [87, 88, 61, 57].

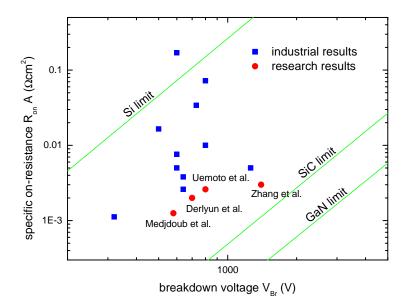

Figure 3.4: Comparison between on-resistance and breakdown voltage for recent results on GaN-based power switches [89, 90, 91, 42, 92].

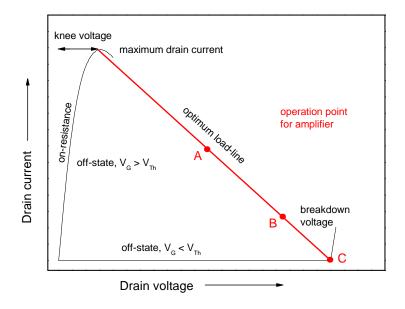

Figure 3.5: Important parameters in the output characteristic of a power transistor with load-line for class A, B, and C amplifiers [93].

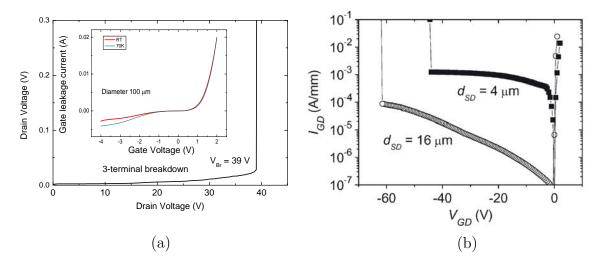

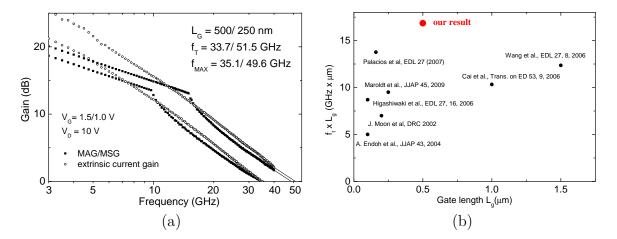

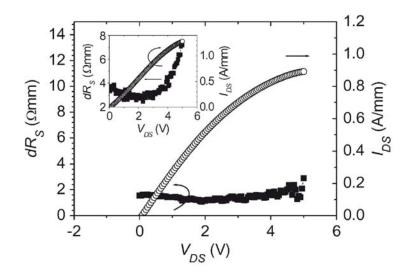

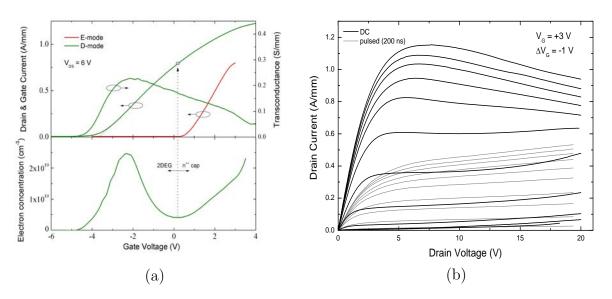

and high voltage power operation. High frequency power amplifiers typically start from around 1 GHz concerning wireless communication up to above 100 GHz covering all kinds of radar bands. A comparison between frequency and RF power for state-of-theart GaN-based devices [87, 88, 61, 57] is shown in figure 3.3. High voltage switches for power supply applications are settled at frequencies up to 1 MHz with switching voltages ranging from 100 V to 2 kV. A few recent results on power switching devices [89, 90, 91, 42, 92] are summarized in figure 3.4 showing that the physical limit of SiC (Tab. 2.1) has been almost reached by gallium nitride transistors. Even though several differences exist in the design and concept of power amplifiers and power switches, both are aiming for better efficiencies and higher thermal robustness using GaN in order to achieve higher output power.

Figure 3.5 summarizes fundamental aspects of a power transistor. It should provide a large drain voltage and current swing in order to provide a maximum output power across the load line. Thus a low knee voltage  $V_{Knee}$ , a high breakdown voltage  $V_{Breakdown}$ , and a high maximum drain current  $I_{D,max}$  are desired. In order to maximize the drain current, the sheet carrier density in the 2DEG and the electron saturation velocity needs to be increased. Therefore, high total polarization in the barrier and

low surface potentials are preferred. Increasing of the polarization can be achieved by increasing the tensile strain in the barrier until the channel mobility degrades by increasing interface roughness. The knee voltage is linked directly to the on-resistance in the linear part of the output characteristics. It depends therefore on the contact metal resistance, the ohmic contact resistance and the resistance in the source and drain access region. Achieving high breakdown voltages includes aspects of the buffer, the substrate, and the surface passivation [64, 94, 91, 95, 96]. For a class A amplifier the maximum output power is

$$P_{out} = \frac{V_{Breakdown} - V_{Knee}}{8} I_{D,max},\tag{3.9}$$

with an maximum efficiency  $P_{out}/P_{DC}$  of 50%. Low efficiencies caused by high electric losses require therefore large efforts on the thermal management for such devices. Modifications on the load-line in order to achieve class B or C amplifiers [93] (Fig. 3.5) for higher efficiencies involve a decline of the linearity of the amplification. Higher harmonics degrade the spectral bandwidth of a communication channel and therefore must be limited. An improved result can be achieved with a switch-mode amplifier (class S) [93]. This amplifier uses a pulse width modulation conversion of the analog signal which is than amplified by a switch-mode amplifier not requiring linearity. The analog signal can be recovered by a low-pass filter. While the efficiency of the power amplification is achieving a maximum in this configuration, the overall circuit reaches about 70% efficiency, due to the losses to higher spectral components [97].

#### 3.3 Dispersion Effects

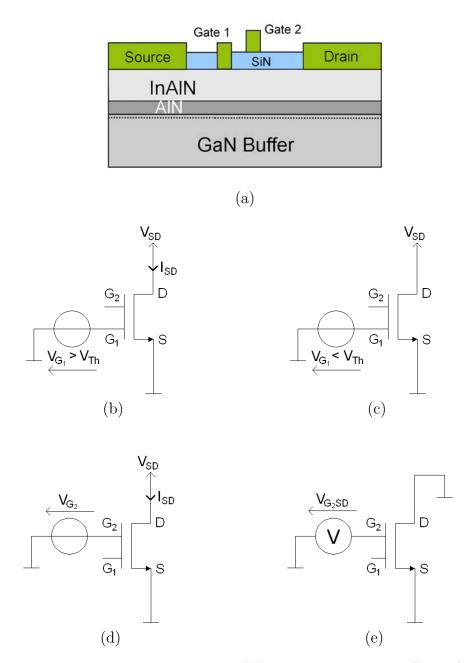

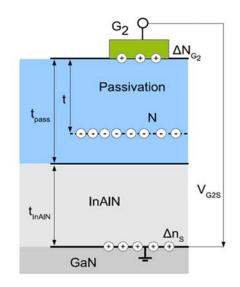

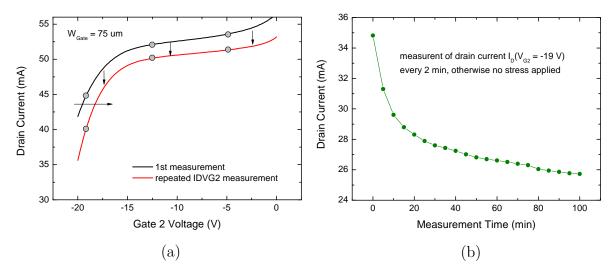

Dispersion of the drain current between RF and DC operation has been one of the major issues since the start of the development of GaN FETs. The dispersion causes an increase (walkout) of the knee voltage and a reduction of the maximum drain current. According to chapter 3.2, those effects reduce the maximum output power twofold. Therefore dispersion needs to be limited in the frequency range of the target application.

The origin of the RF dispersion was found to be donor-like traps at the surface [84]. It was described, in part 3.1, that the 2DEG in thin barrier structures originates from the surface donors. Without ionized surface donors the channel would not contain any free carriers due to charge neutrality of the polarization charges. The surface donors donate electrons to the structure, which are accumulated in the channel. The compensation charge at the surface is therefore required in order to have a 2DEG. During device operation electrons with sufficient thermal or electrical energy can be injected into traps in the buffer, barrier, surface or at any interface. If the device is operating in

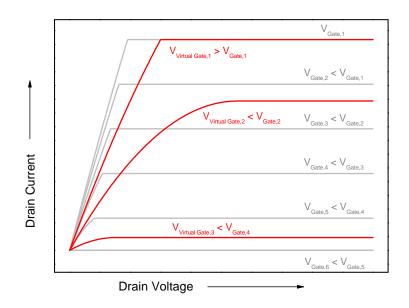

off-state ( $V_G < V_{th}$ , Fig. 3.5), a high electric field builds up at the drain-side of the gate electrode. This electric field can lower the potential barrier between gate and surface causing electron injection into donor states at the surface [84]. The neutralized donors reduce the electron density in the channel. In on-state ( $V_G > V_{th}$ , Fig. 3.5), the applied bias causes much lower or even reversed electric field at the surface reducing the number of trapped electrons. However, if the time constant of this trap emission mechanism is too low in comparison to the modulation frequency, the electrons cannot be fully removed from their trapped state. Thus, the trapped electrons are causing a virtual gate, which is acting as a current limiter comparable to the regular gate electrode. If the trapped charge density is small enough the effect can be seen only from an increase of the device on-resistance (Fig. 3.6). Once the density of trapped electrons exceeds the charge density at the gate at maximum forward bias, the dispersion effect reduces the maximum output drain current. The combination of the virtual gate and the actual gate electrode can simply be described as two transistors acting as two serial current sources. The current source with the lower output current dominates. Figure 3.6 shows an analytical calculation [98] of such a dual gated transistor, demonstrating gate and virtual gate, using a two-piece [81] approximation for the electron velocity. The grey lines correspond to the output characteristic of the regular gate without any limitation from the second electrode (virtual gate). The additional red curves represent the maximum drain current at maximum bias at the regular gate with decreasing bias on the virtual gate causing the apparent drop of the drain current and increase of the on-resistance.

Several concepts of surface passivation have shown excellent results for the suppression of drain current dispersion. Deposition of dielectrics can passivate the surface bonds which are causing electrical states within the surface bandgap. However, since the surface charges are needed in order to establish the 2DEG, an ideal passivation of the surface would lead to an increase of the surface potential and a depletion of the channel. Therefore, counter charges are needed in the passivation layer or on top of it to sustain the 2DEG. A thick passivation layer can increase the barrier for injected electrons and hence reduce the accessibility for electrons to be trapped. Further ideas on how to measure the electron injection can be found in chapter 4.2.

As stated before, RF dispersion needs to be suppressed in the frequency range of the specific application. A power amplifier working for wireless communication should operate in the range of 1 to 3 GHz. Hence, traps much faster than this can be neglected. An absolute verification, if the device is able to work at the required frequency can be done by load pull measurements. This method alters the output impedance in order to test the large signal response of a device for a certain load line (Fig. 3.5). The

Figure 3.6: Simulation of drain current in dependency of gate voltage and virtual gate potential. The qualitative potential value of the gate and the virtual gate correspond to comparable gate geometries. If the bias V is replaced by the surface potential  $\Phi$ , the figure becomes generally valid for all kinds of device structures. The grey curves represent the case without virtual gate. The red curves show the maximum drain current for the highest gate bias and decreasing virtual gate potential. The simulation was performed using an analytical dual gate model [98].

sweep across the load line includes biasing of the devices in off-state and on-state. The resulting output power is therefore a direct measure of the device performance. In addition, the actual dynamic load line can be measured, giving a clear indication whether the device is capable of reaching the maximum drain current from DC measurements [59]. Any current limitation by a virtual gate is therefore easy to detect. An alternative and faster way is to measure the output characteristic in pulsed mode. Such method is typically used to separate the self-induced heating effects in devices. Pulsing the gate with 100 ns long pulses from off-state to on-state allows investigating traps in frequency ranges up to 10 MHz. Since most relevant traps are known to be in this spectral range a quite good estimation can be achieved. However, if only the gate is pulsed, the device does not operate along the load-line with a lower drain bias in off-state. The measurement can simply be improved by increasing the drain voltage or pulsing gate and drain simultaneously. First one is however limited by the on-state breakdown which is typically lower compared to the off-state in compound semiconductors [99]. Another method to investigate surface traps is done by large signal load line measurements at frequencies in the MHz range. Increasing the drain bias for a fixed load allows sweeping through the output characteristic and investigate the time constant for electron trapping [84]. Due to electron injection, the decrease of the drain current at higher drain voltage is expected be faster. Alternatively, any of the above measurements can be included in long time stress tests in order to see a degradation of the passivation scheme. An approach that combines long time stress tests with detection of injected charges in the passivation layer is presented in chapter 4.2.

Finally, also capacitive-voltage (CV) measurements should be discussed in this context. They have been proven to be very effective in order to gain in-depth understanding of the oxide-semiconductor interface in silicon technology [100]. However, the adaptability of CV methods for wide bandgap semiconductors is limited due to larger time constants for deep traps. Additionally, electrons trapped at the barrier-insulator interface cannot be modulated by the gate potential and are therefore invisible in most characterization techniques. Furthermore, capture and emission time from the 2-terminal CV characterization does not correspond to the injection of electrons by the horizontal electric field under 3-terminal measurements.

#### 3.4 Device Technology

The following part reviews some important aspects of the technology of InAlN barrier devices. General information as well as personal experience from this work is presented. However, due to the wide range of this topic, the focus is primarily set on new developments rather than basics, which can be found elsewhere [101, 102].

|                | available<br>size (dev.) | lattice<br>mismatch | thermal<br>mismatch | dislocation<br>density<br>$[cm^{-2}]$ | thermal cond. $[W/_{cmK}]$ |

|----------------|--------------------------|---------------------|---------------------|---------------------------------------|----------------------------|

| Si (111)       | 12" (18")                | -16.9%              | 60%                 | $10^{11}$                             | 1.3                        |

| Sapphire       | 4" (6")                  | 16.1%               | -34.4%              | $10^{9}$                              | 0.41                       |

| 6H-SiC         | 4" (6")                  | 3.3%                | 25%                 | $10^{9}$                              | 4.9                        |

| Bulk-GaN       | 2"                       | -                   | -                   | $10^4 - 10^6$                         | 2.5                        |

| Diamond (s.c.) | <1"                      | 11.8%               | -21.6%              | n.a.                                  | 20                         |

Table 3.1: Comparison between typical used substrates for epitaxial growth of GaN at room temperature [103, 104, 38, 99, 89].

Epitaxial structures based on GaN are typically grown on different kinds of substrates by metal-organic chemical vapor deposition (MOCVD) or molecular beam epitaxy (MBE) due to the absence of bulk GaN substrates with reasonable prize and size. Commonly used substrates are sapphire, silicon, silicon carbide and recently diamond or composite substrates with diamond interlayer. Table 3.1 compares some important parameters including lattice mismatch and thermal mismatch to GaN, and available size for substrates used for GaN epitaxy. Silicon is the cheapest among all substrates but involves the highest lattice mismatch. This requires a transition layer to GaN in order to grow relaxed layers and reduce the defect density. SiC would be the most preferred substrate in terms of lattice constant and offers also a good thermal conductivity. However, to be considered in mass market production requires lower prices and availability of larger wafers. The best candidate in thermal robustness is diamond. Recently, Alomari et al. have demonstrated a HEMT device grown by MBE on singlecrystalline (s.c.) diamond [35]. However, the high lattice mismatch and small wafer size makes it only applicable for special market segments. Sapphire has been the ultimate candidate for research activities with its acceptable lattice mismatch and hence controllable growth complexity and lower prize compared to SiC.

Epitaxial growth by MOCVD and MBE are non-equilibrium processes. In an MBE system Ga, Al, In and N are offered by a vapor beam towards a heated substrate in ultra-high vacuum. Nitrogen can be included by  $NH_3$  or from a plasma source cracking  $N_2$ . Under suitable conditions, a layer-by-layer deposition is possible, achieving very sharp interfaces between neighboring layers. The growth temperature needs to be balanced between increasing defect density at lower temperatures due to reduced atom mobility at the surface and decomposition of GaN at higher temperatures. In contrast to MBE, MOCVD growth is performed at relatively higher pressures and higher tem-

peratures. The metal-organic precursor for GaN is typically trimethylgallium (TMG,  $Ga(CH_3)_3$ ). The challenge in the CVD process is the temperature uniformity across the wafer and the uniform distribution of reactants. The latter is defined by the design of the chamber. Improved performance and higher output capacity made MOCVD currently the method of choice for mass production of GaN epitaxy.

The growth of GaN-based HEMTs starts with a nucleation layer in order to achieve two-dimensional growth. A GaN buffer of about 2 µm is typically used to achieve a reasonable crystal quality for the channel. The buffer needs to be sufficiently insulating, otherwise it causes a parallel channel to the 2DEG. The ideal buffer would be a layer with the Fermi level around mid gap. Such a buffer can be achieved by Fe or C doping [105, 106, 107, 108, 109, 110, 111, 112]. While iron needs to be included into the growth by a separate precursor, carbon is already part of the metal-organic precursors. It has been demonstrated that the incorporation of carbon can be adjusted simply by the growth parameters and is therefore easy to switch on and off. In contrast, Fe doping is more difficult to control due to segregation on the growth surface and therefore requires thick Fe-free GaN layers below the channel [106].

Finally the top heterostructure can be grown. Switching the growth from the GaN buffer to the InAlN barrier requires no remnant gallium on the walls of the MOCVD reactor. This can be achieved by purging it for a few minutes with ammonia without insertion of other precursors. Before the barrier layer is grown, a thin AlN interlayer needs to be inserted which drastically improves the channel interface and hence the mobility [41].

Device isolation is done either by mesa-type recessing of the inter-device area leading to sidewalls which may affect the gate leakage and the device reliability [113]. Therefore industrial manufacturing uses preferred implantation of i.e. Ar to destroy the crystal lattice and create defects [114, 115]. Alternatively, local oxidation has been demonstrated to be very efficient even though only parts of the barrier layer were oxidized. However the induced stress in the neighboring devices may cause additional challenges for device reliability.

Ohmic contacts were formed by electron-beam evaporation of Ti/Al/Ni/Au layers with thicknesses of 30/180/40/50 nm, respectively [116]. The metal stack is annealed at 800°C for 30s. Maier et al. found that long time annealing improved the contact resistance slightly due to enhanced alloying of the metal stack [67]. Therefore the annealing time can be increased. Directly before metal deposition the samples with the ohmic mask layer are put into HCl:H<sub>2</sub>O with a ratio of 1:1 to 1:2 at 70°C to 80°C for at least 10 min in order to remove the native surface oxide. Alternatively, an Au-free metal scheme was tested for high temperature stability suggested by Alomari et al. [69]. Au was replaced by 100 nm thick Cu capped with a 20 nm of Ta to prevent oxidation of Cu. The Ta layer, which oxidizes during processing, needs to

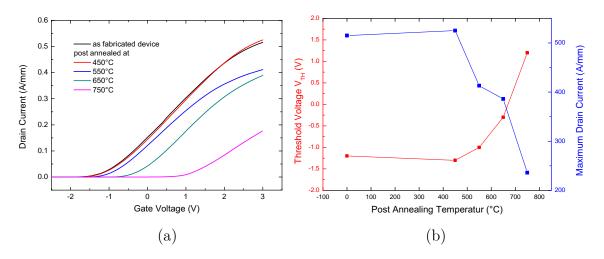

Figure 3.7: Shift of the transfer characteristic (a) influencing the drain current and threshold voltage (b) after post-fabrication annealing of unpassivated HEMTs (wafer AEC 1802, see App. A).

be removed by sputtering after final device processing. The ohmic contact resistance was extracted by the transfer line method (TLM) [55] using a 4 point measurement in order to deduce the variable tip-to-pad resistance. For simple 2 point measurements, the typical measurement error is between 1 to 2  $\Omega$ , causing random results as the tip pressure varies for each measurement.

As mentioned in chapter 2, InAlN was found to be stable up to 1000°C in vacuum. However, if the annealing chamber is contaminated with small traces of oxygen or water, the aluminum surface can react to form aluminum oxide. This thin layer can cause a loss of 2DEG electrons in the access region as well as below the Schottky diode. Figure 3.7a shows a series of measurements done on the same device after annealing for 2 min at different temperatures up to 750°C under nitrogen gas after device processing without surface passivation. The summary of the maximum drain current and threshold voltage is shown in figure 3.7b. Above 500°C annealing temperature, the increase of the threshold voltage indicates an increase of the surface potential due to surface oxidation. This thinning by oxidation reduces the potential drop induced by polarization charges across the barrier. However, this explanation was found to be not sufficient to explain the increase of the gate and channel resistance. Consequently, it was found that aluminum oxide thermally grown from InAlN or AlGaN causes an increase of the surface potential  $\Phi_{SP}$  (chapter 3.1) [117]. Finally, gate metallization is done by Ni/Au, Ir/Au, Pt/Au or Cu/Ta metal stacks.

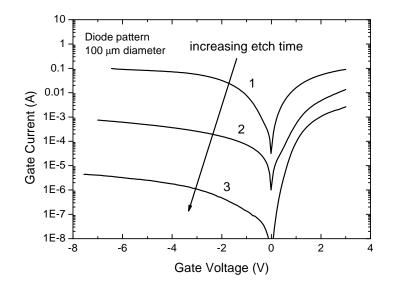

The complexity of the Schottky/heterostructure gate contact has caused several different models to describe the gate leakage current. Typically, a combination of tunneling and thermal emission is used to model the leakage current. In addition, it was shown that fixed charges in the passivation beside the drain-side edge of the gate electrode modify the electric field at the gate and therefore strongly influence the device behavior [118]. However, still a lack of understanding exists about the dominating mechanisms and in several reports basic gate leakage current models are applied using a large number of input parameters and allowing non-physical fitting of the electrical behavior [119].

Depending on the device design, samples can be passivated after gate process or before ohmic contact in order to insulate the gate electrode. Oxide deposition before ohmic metallization includes several advantages. First, without any metallization harsh cleaning procedures which attack the metal layers can be applied. Second, if metals are brought into the dielectric deposition chamber, the chamber can be contaminated especially at higher deposition temperatures. Surface passivation was achieved by silicon nitride deposition in a plasma-enhanced chemical vapor deposition (PECVD) at  $300^{\circ}$ C or with an atomic layer deposition depositing various high-k dielectrics in the temperature range from  $100^{\circ}$ C to  $300^{\circ}$ C. The thermal stability of SiN deposited by PECVD is limited due to the mismatch of the thermal expansion coefficient to sapphire. Therefore, only thin layers <100 nm could be deposited if high temperature treatments above  $800^{\circ}$ C were applied afterwards. Otherwise the SiN layer would crack and partially peel off the surface.

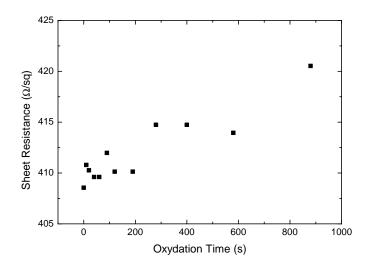

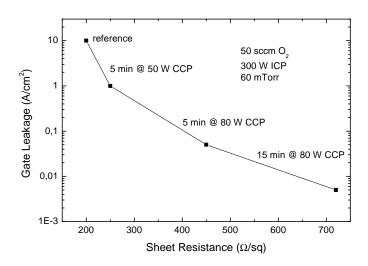

Another process that is commonly applied in microelectronics is plasma ashing. It is a very useful process to remove remnant organics from photo resist mask layers and clean the surface for the next process step. Since surface oxidation is harming the device performance as described above, plasma oxidation could do the same. However, it was found out that plasma ashing using a Faraday cage around the sample does almost not modify the sheet resistance as depicted in figure 3.8. The Faraday cage is usually applied on samples with metallic surface parts in order to prevent sparks. The cage reduces the energy of the ions and hence prevents damage of the surface.

## 3.5 Characterization Techniques

Evaluation of individual process steps was done by optical and electron microscopy as well as electrical measurements. Final devices were characterized by current-voltage (IV) measurements in DC and pulsed mode. A programmable semiconductor parameter analyzer (Keithley 4200 SCS) was utilized in order to perform long-term stress tests and repeated measurements.

Additionally, capacitive analysis was applied using a standard LCR meter. Capacitancevoltage (CV) measurements [100] provide one of the most powerful tools for electrical device investigations. In contrast to IV measurements, where the figure under investiga-

Figure 3.8: Impact of plasma asher with Faraday cage on the sheet resistance of a free InAlN surface (wafer AEC 1802, see App. A).

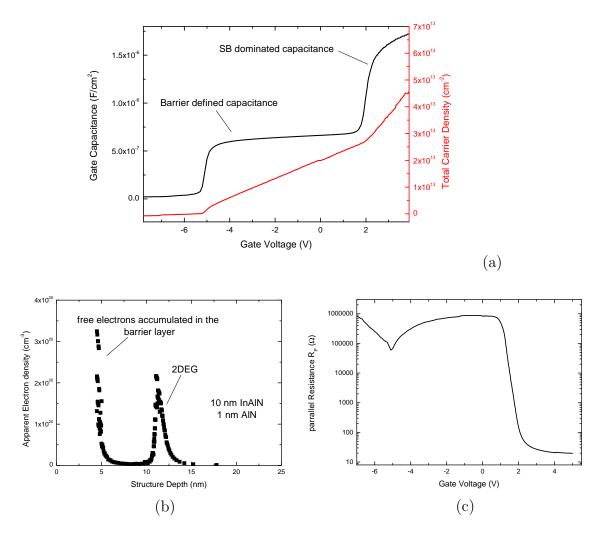

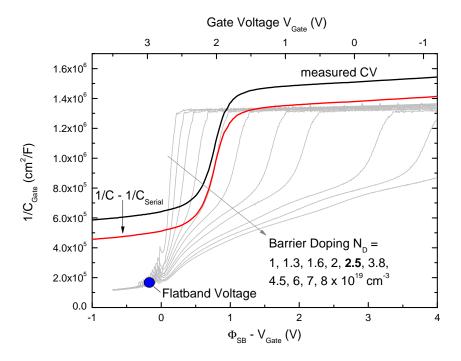

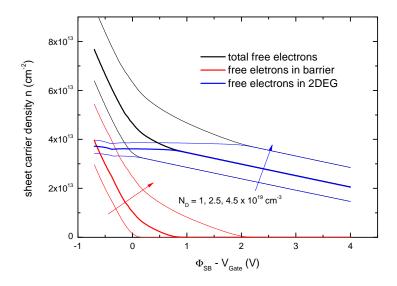

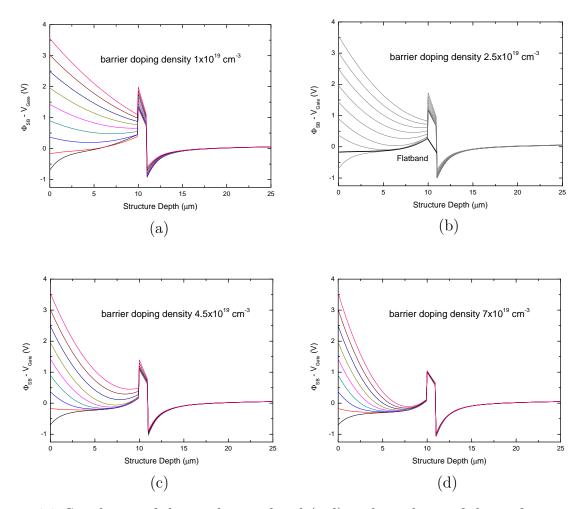

tion, mostly the drain current, depends on the carrier density times the carrier velocity, CV measurements reveal details on the carrier profile only. Thus it can be used to determine charge concentrations in any part of the structure. A very frequently applied method is therefore the characterization of interface charges at the semiconductor-oxide interface of MOS structures. Those charges can be extracted by comparing measurements with different parameters. Varying the frequency of the measurement allows to investigate traps of different time constant and hence energy position. Comparing measurements with and without above-bandgap light illumination allows measuring the CV with filled or empty interface states. The basic CV curve of the InAlN HEMT is shown in figure 4.3 in addition to the apparent total free carrier density N. The latter can be calculated by the depletion approximation using [55]

$$N\left(x = \frac{\varepsilon}{C'}\right) = \frac{2}{q\frac{\partial \frac{1}{C'^2}}{\partial V}\varepsilon}.$$

(3.10)

C' is the capacitance per area,  $\varepsilon$  the dielectric constant, V the applied gate voltage, and x the structural depth of the capacitance. Integrating the charge density over the gate voltage or the structure depth and assuming zero charges in the channel for  $V_{Gate} < V_{Th}$ , allows to calculate the 2DEG density (Fig. 4.3) in the channel.

If the charge density is known, one can also determine the carrier drift mobility. The drain current in the linear regions is determined by the number of charges, depending on the gate voltage, the mobility, and the electric field given by the drain voltage divided

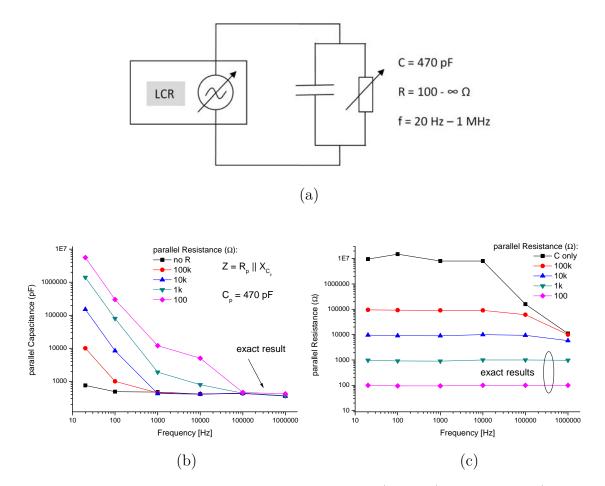

Figure 3.9: Measurement of given parallel capacitor (470 pF) and resistor (100 $\Omega$  to 100k $\Omega$ ) (a) at various frequencies (20 Hz to 1 MHz) investigating the accuracy of the LCR bridge for the parallel capacitance (b) and parallel resistance (c).

by the gate length. Inserting the already known charge density allows to extract the drift mobility at very low drain bias (i.e.  $V_D = 0.1$  V) for different gate biases. An example of such measurements is shown in chapter 5.

The capacitive measurement is usually performed in a bridge circuit to calculate the complex impedance of the connected circuit. Semiconductor devices mostly offer very small dimensions and therefore the measurable capacitance is typically within the pico-Farad range requiring femto-Farad accuracy. Hence, CV meters are usually built up as a 4-point measurement system and require open and short calibration to minimize parasitic effects. The measured impedance can be then transferred into a parallel or serial circuit of a capacitance and resistance. Since the serial resistance can be usually omitted, the parallel model is preferred for most analyses. However, if the measured impedance is comparably small to the serial resistance, one needs to consider a three part model. Since the complex result allows only the extraction of two real components,

one part needs to be determined elsewhere. This can be done by either calculating the serial resistance by its geometrical dimensions and the sheet resistance, or by extracting the constant value of the serial resistance above threshold where the parallel resistance can be neglected. This assumption can only be made if the leakage through the capacitance is not significant. Further, measuring capacitances with parallel leakage requires additional attention towards the accuracy of the results. If one of the two components of a parallel circuit is sufficiently smaller than the other one, the larger part cannot be extracted accurately. It is evident that the error gets larger if the angle  $\alpha$  of the complex impedance is close to 0° or 90°. In most cases the capacitance is of interest and therefore the parallel resistance must not be lower than a certain value. Additional adjustments can be done if the correct frequency range is chosen in order to increase or decrease the imaginary part  $X_C$  of the impedance. Figure 3.9 summarizes the measurement results of a fixed capacitor of 470 pF parallel to a variable resistor over frequency. The capacitance values become incorrect at low frequency when  $X_C$ , the capacitive reactance, is much smaller than the parallel resistance (Fig. 3.9b). In contrast, measuring a large parallel resistance gets an incorrect result for high frequencies when  $X_C$  decreases much below its resistive counterpart (Fig. 3.9c). Therefore if measuring capacitances with high parallel leakage, the CV measurement needs to be done at sufficient high frequencies and attention has to be taken to the validity of the result of the parallel resistance.

# 4 Novel Characterization Methods for HEMTs

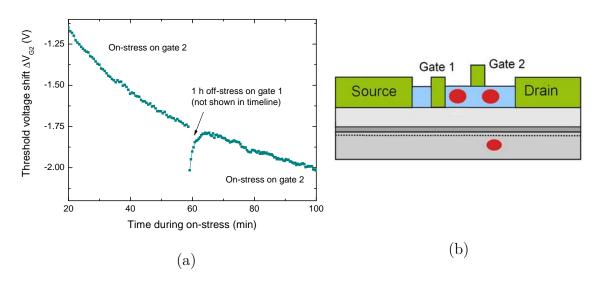

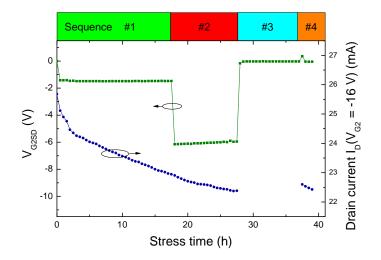

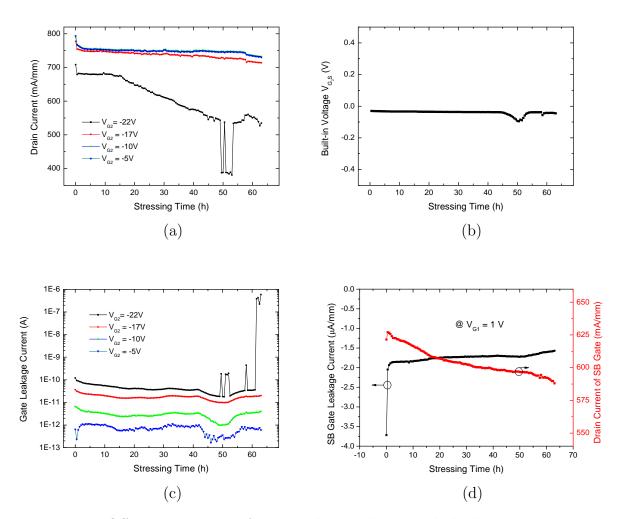

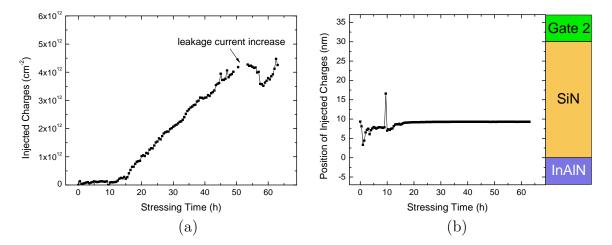

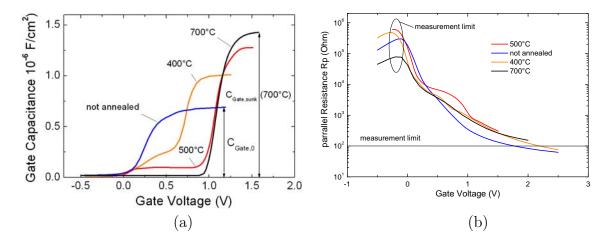

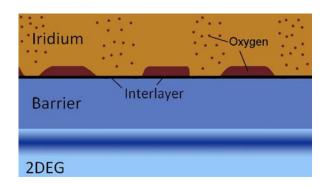

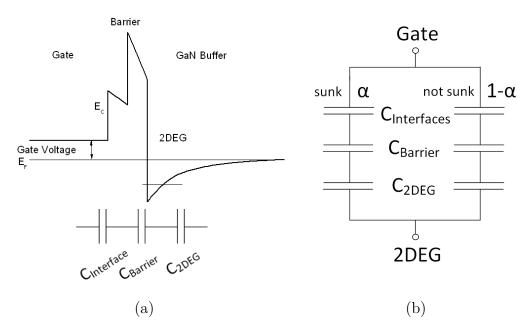

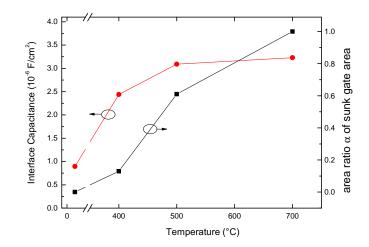

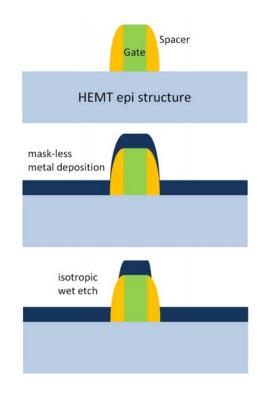

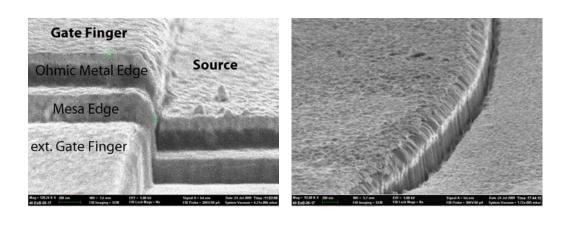

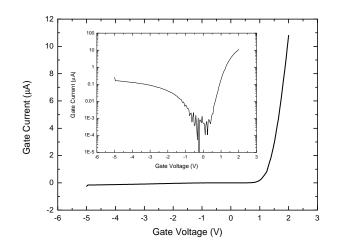

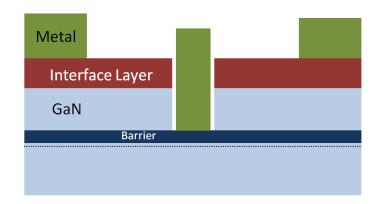

# 4.1 Schottky Barrier Height Analysis by CV Method