### DISSERTATION

# Multi-Mode Power Amplifiers for Mobile Handsets

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

> ao. Univ. Prof. Univ. Prof. Dr. Arpad L. Scholtz E389

Institut für Nachrichtentechnik und Hochfrequenztechnik

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

Dipl.-Ing. Bernhard Sogl Matrikelnummer 9826336 Dreyhausenstr. 5 A-1140 Wien

Wien, im März 2010

Die approbierte Originalversion dieser Dissertation ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at). The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

#### Abstract

In today's and future mobile communication systems mobile handsets have to support various coexisting standards like GSM, EDGE and WCDMA. To reduce the complexity and cost of separate radios (baseband, transceiver and front end) in the mobile terminal, the development of a single multi-mode radio is required. Up to now multi-mode capability is only implemented for the baseband and transceiver part. The front end still consists of separate paths for each standard. This work deals with the multi-mode capability of the front end power amplifier (PA). The investigations pursue two main goals:

- Reducing the current consumption over a large dynamic output power range, while maintaining high linearity.

- Reducing the sensitivity of PA parameters (e.g. output power, linearity) to antenna impedance variations.

Several concepts are examined to improve a single PA regarding these issues. As outcome of these investigations a novel concept is proposed, which uses a double balanced PA topology. An analytical design procedure for optimization of the proposed multi-mode PA is presented. The excellent results, obtained for the implemented prototype confirm the usefulness of this procedure and the potential of the concept to reduce the number of different PAs in current front end architectures.

The main achievements of this work comprise:

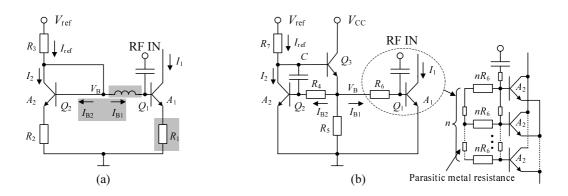

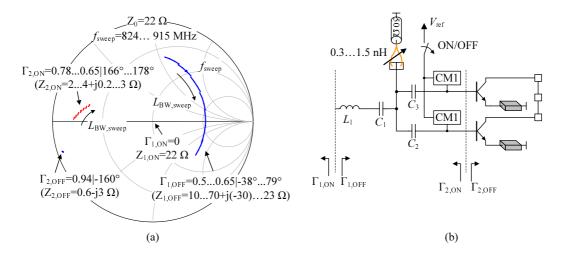

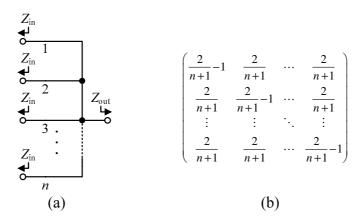

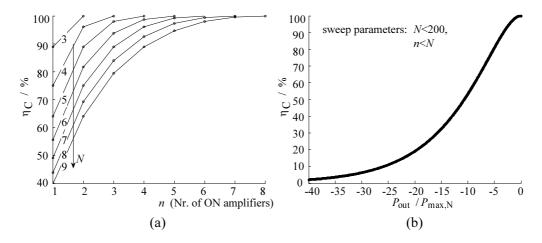

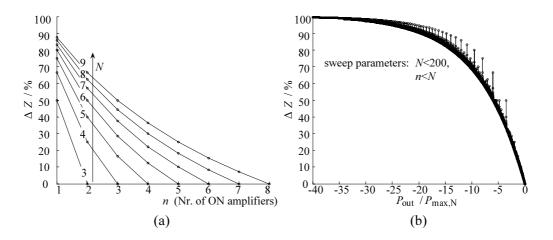

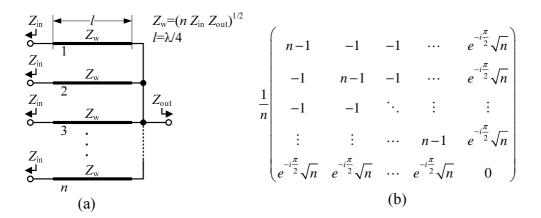

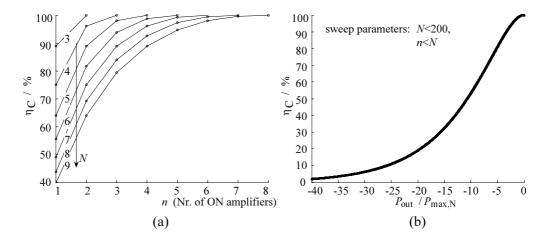

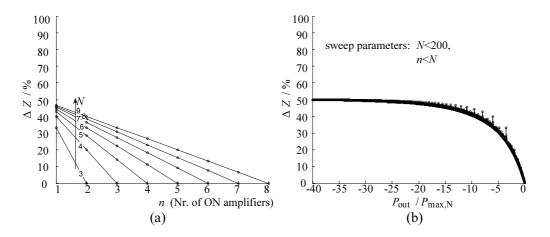

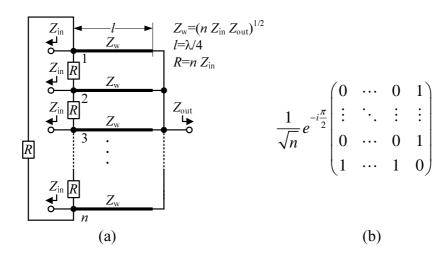

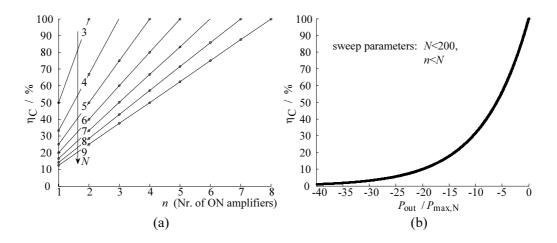

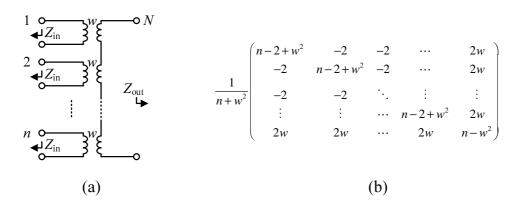

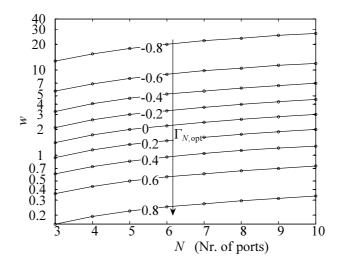

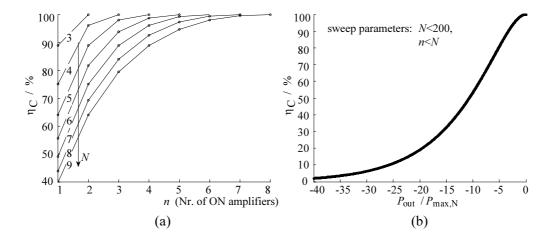

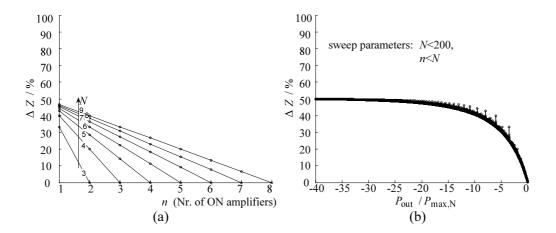

- A scattering parameter based method is proposed, which permits a unified analysis of PA configurations where transistor stages are deactivated only via bias current, not being isolated by RF switches. The efficiency improvement at power back-off and requirements for symmetrical multi-port power combiner networks are derived for the first time.

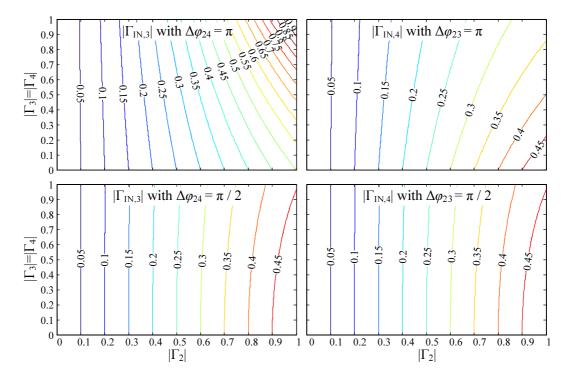

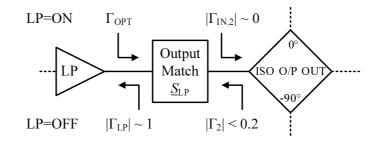

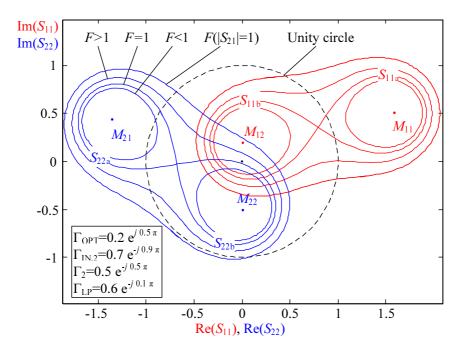

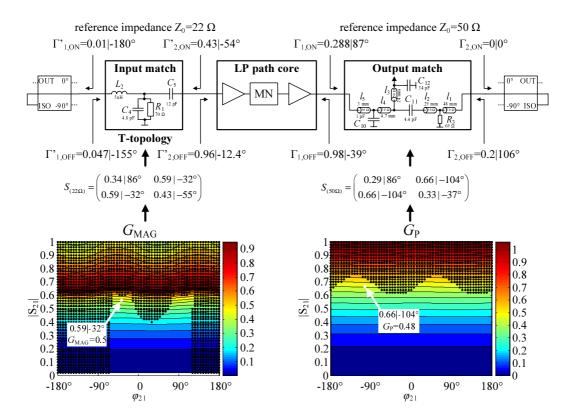

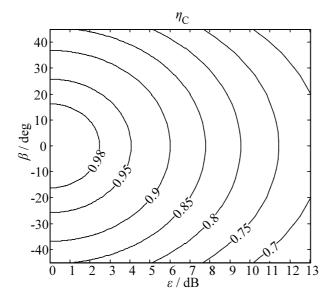

- A quadrature hybrid as special case of a power combiner is investigated. It offers inherent load insensitivity and the possibility to use its internal isolated port for applying a high efficient low power (LP) path. A detailed study of the mutual influence of high power (HP) path and LP path comes to the result that an independent optimization for highest efficiency is not possible. A compromise has to be accepted. Further considerations show that the best compromise can not be calculated in a closed form. Therefore a novel numerical method is developed to systematically iterate to an optimum.

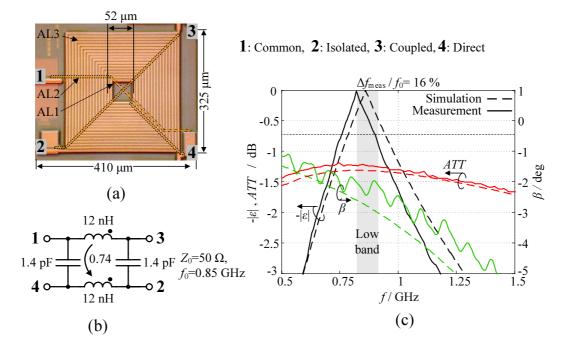

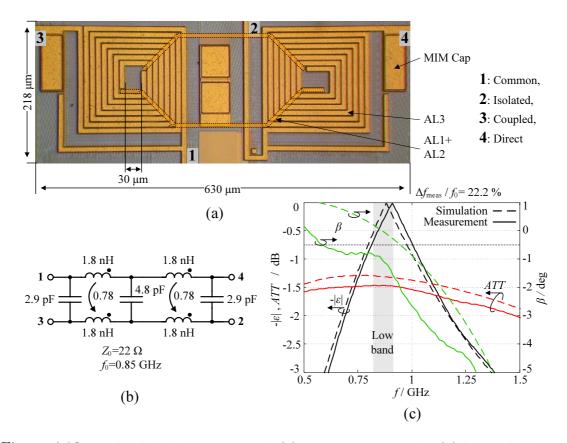

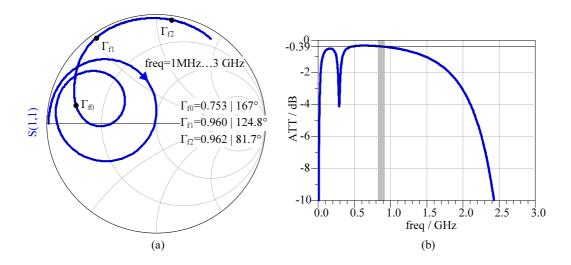

- A two stage inductively coupled quadrature hybrid, with attenuation < 1.5 dB, amplitude error < 0.75 dB and phase error < 2.9° over a relative bandwidth of 22.2 % is realized in SiGe technology. The design fulfills the requirements for the multi-mode PA and is furthermore suitable for on-chip integration.

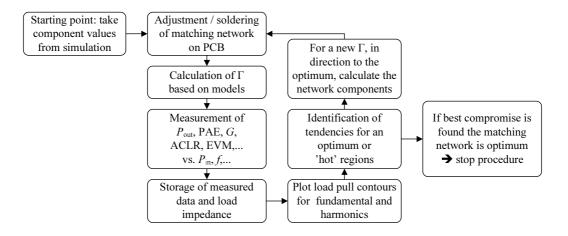

- A very time efficient load pull procedure is developed for experimental optimization of PA matching networks. In comparison to conventional load pull methods, here the use of costly and complicated deembedding structures is avoided.

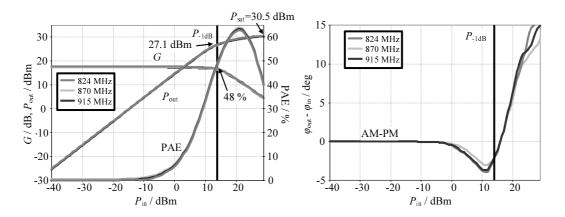

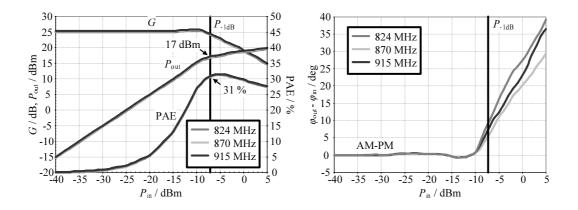

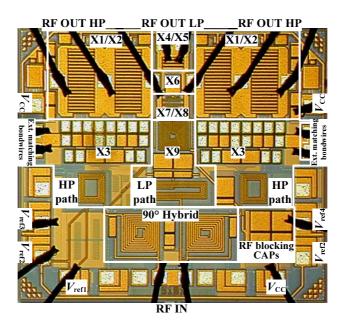

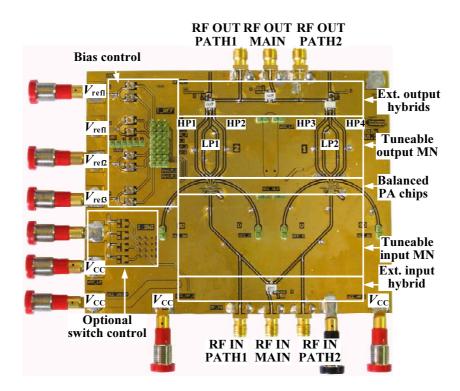

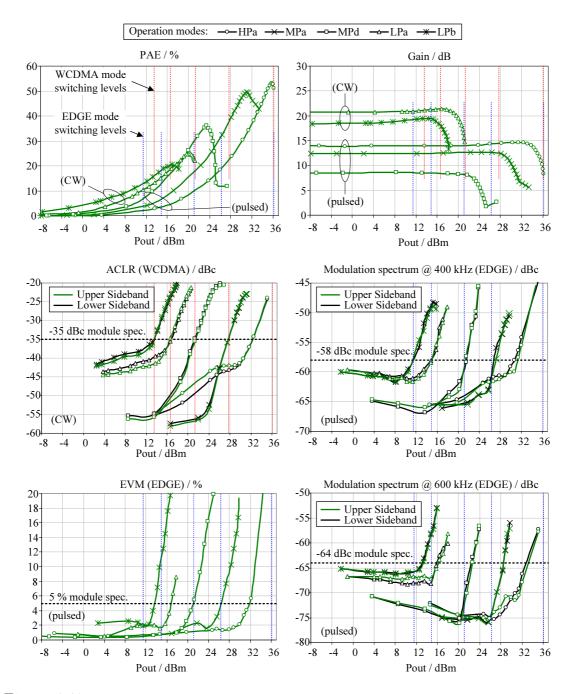

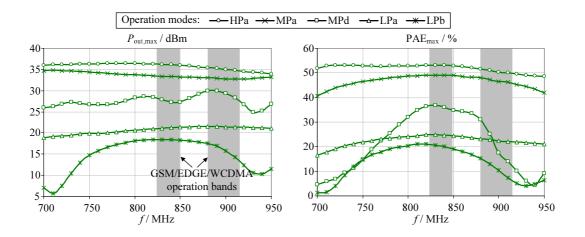

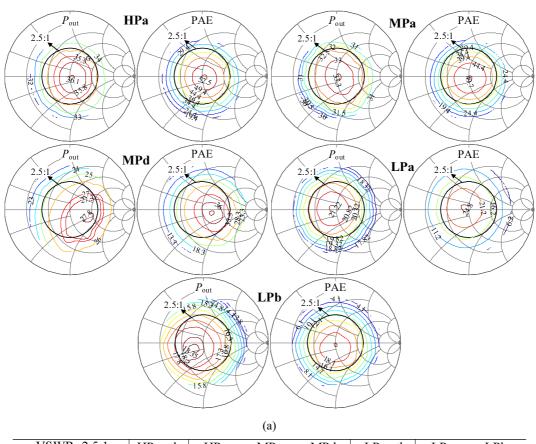

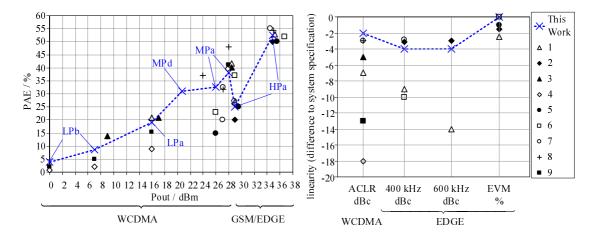

- A prototype of a double balanced switched path PA is fabricated in a low cost 0.35  $\mu$ m bipolar SiGe technology. At 840 MHz a peak power of 36.1 dBm with 52 % PAE was achieved for GSM operation. In back-off at 27 dBm, 16 dBm and 13 dBm efficiencies of 37 %, 18 % and 15 % for WCDMA signals were measured. For EDGE operation at 30 dBm a peak PAE of 30 % is achieved and held above 10 % over a dynamic output power range of 22 dB, by proper selection of the five amplifier modes. These performance characteristics are comparable to separate single mode PAs, each optimized for GSM/EDGE/WCDMA.

#### Kurzfassung

In heutigen und zukünftigen mobilen Kommunikationssystemen muss eine Vielzahl von nebeneinander bestehenden Standards, wie GSM, EDGE und WCDMA von den Mobiltelefonen unterstützt werden. Um die Komplexität und Kosten durch getrennte Funksysteme (Basisband, Sendeempfänger und Front-End) in den tragbaren Endgeräten zu reduzieren, ist die Implementierung eines einzelnen "multi-mode" Funksystems notwendig. Bisher wurde die multi-mode Tauglichkeit nur für Basisband und Sendeempfänger umgesetzt. Das Front-End besteht nach wie vor aus getrennten Pfaden, die an jeden Standard individuell angepasst sind. In dieser Arbeit wird die multi-mode Tauglichkeit des Front-End Leistungsverstärkers untersucht. Dabei werden zwei wesentliche Ziele verfolgt:

- Die Verringerung des Stromverbrauchs über einen großen Ausgangsleistungsbereich unter Aufrechterhaltung hoher Linearität.

- Die Verringerung der Empfindlichkeit von Verstärkerparametern (z.B. Ausgangsleistung, Linearität) gegenüber Änderungen der Antennenimpedanz.

In dieser Arbeit werden mehrere Konzepte untersucht, die eine Verbesserung eines einzelnen Verstärkers hinsichtlich dieser Punkte erlauben. Als Ergebnis dieser Untersuchungen wird ein neues Konzept präsentiert, das auf einer doppelt symmetrischen Topologie mit Quadratur-Hybriden basiert. Zusätzlich wird eine rechnerische Entwurfsmethode zur Optimierung des vorgeschlagenen multi-mode Verstärkers vorgestellt. Die ausgezeichneten Messergebnisse, die für den realisierten Prototypverstärker erreicht wurden, bestätigen die Brauchbarkeit der Vorgehensweise und zeigen, dass es mit diesem Konzept möglich ist, die Anzahl unterschiedlicher Leistungsverstärker in momentanen Front-End Architekturen zu reduzieren.

Die wesentlichen Leistungen dieser Arbeit beinhalten:

• Eine auf Streuparameter basierte Berechnungsmethode wird vorgeschlagen, welche eine vereinheitlichte Analyse von Verstärkerkonfigurationen ermöglicht, in denen Transistorstufen nur durch Abschalten des Ruhestroms deaktiviert werden und keine weiteren HF Schalter zur Isolation notwendig sind. Zum ersten Mal kann dadurch die Wirkungsgraderhöhung bei kleinen Leistungen und die Voraussetzungen für symmetrische Leistungskombinationsnetzwerke mit mehreren Toren allgemein abgeleitet werden.

- Der Quadratur-Hybrid als spezieller Fall eines Kombinationsnetzwerks wird weiter untersucht. Dieser bietet neben der Eigenschaft der Lastunempfindlichkeit auch die Möglichkeit, sein internes isoliertes Tor mit einem hoch effizienten Verstärkerpfad für kleine Ausgansleistungen zu verbinden. Eine detaillierte Analyse der gegenseitigen Beeinflussung der Pfade für hohe und niedrige Ausgangsleistung zeigt, dass eine unabhängige Optimierung für höchsten Wirkungsgrad nicht möglich ist. Es muss ein Kompromiss bezüglich des erreichbaren Wirkungsgrades zugelassen werden. Weitere Überlegungen zeigen, dass der best mögliche Kompromiss nicht geschlossen berechnet werden kann. Es wird daher eine neue numerische Methode entwickelt, mit deren Hilfe trotzdem systematisch in wenigen Schritten das Optimum zu erreichen ist.

- Ein zweistufiger indukiv gekoppelter Quadratur-Hybrid wurde in SiGe Technologie realisiert. Dieser besitzt eine Dämpfung von < 1.5 dB, einen Amplitudenfehler von < 0.75 dB und einen Phasenfehler von < 2.9°. Die Voraussetzungen für den Einsatz im multi-mode Verstärker werden dadurch erfüllt. Ausserdem kann dieser auf dem Chip zusammen mit den Transistoren integriert werden.

- Für die experiementelle Optimierung des Anpassnetzwerks für Leistungsverstärker wurde ein sehr effizientes und zeitsparendes "load pull" Verfahren entwickelt. Im Vergleich zu üblichen load pull Verfahren wird hier der Einsatz von teuren und aufwändigen Kalibrierstrukturen umgangen.

- Der Prototyp eines Leistungsverstärkers mit geschalteten Pfaden und doppelt symmetrischer Topologie mit Quadratur-Hybriden wurde in einer kostengünstigen 0.35 μm SiGe Bipolar Technologie realisiert. Dieser erreicht bei 840 MHz eine maximale Ausgangleistung von 36.1 dBm mit einem Gesamtwirkungsgrad von 52 % im GSM Betrieb. Bei reduzierten Ausgangsleistungen von 27 dBm, 16 dBm and 13 dBm werden Wirkungsgrade von 37 %, 18 % und 15 % im WCDMA Betrieb erreicht. Im EDGE Betrieb bei 30 dBm Ausgangsleistung wird ein Gesamtwirkungsgrad von 30 % erreicht, der über einen dynamischen Ausgangleistungsbereich von 22 dB über 10 % gehalten werden kann. Dies wird durch geeignetes Schalten zwischen den fünf Betriebsarten des Verstärkers erreicht. Diese Werte sind vergleichbar mit jenen von getrennten Leistungsverstärkern, die einzeln für GSM/EDGE/WCDMA optimiert sind.

# Contents

| 1        | Intr | oducti  | ion                                          | 1  |

|----------|------|---------|----------------------------------------------|----|

|          | 1.1  | Trends  | s in cellular communication                  | 1  |

|          | 1.2  | PAs in  | n mobile handsets                            | 4  |

|          | 1.3  | Thesis  | outline                                      | 6  |

| <b>2</b> | Pow  | ver An  | plifier Characteristics                      | 7  |

|          | 2.1  | Basic   | Parameters                                   | 7  |

|          |      | 2.1.1   | Output Power and Power Distribution Function | 7  |

|          |      | 2.1.2   | Gain and 1 dB compression point              | 7  |

|          |      | 2.1.3   | Efficiency                                   | 8  |

|          |      | 2.1.4   | Linearity                                    | 8  |

|          |      | 2.1.5   | VSWR                                         | 10 |

|          | 2.2  | Param   | neter table for GSM/EDGE/WCDMA               | 11 |

|          | 2.3  | Opera   | tion Classes                                 | 12 |

|          |      | 2.3.1   | Class A, AB, B and C                         | 12 |

|          |      | 2.3.2   | Class F                                      | 13 |

|          |      | 2.3.3   | Class E                                      | 14 |

|          |      | 2.3.4   | Class D                                      | 14 |

| 3        | Mu   | lti-Mo  | de PA Concepts                               | 16 |

|          | 3.1  | Power   | amplifier architectures                      | 17 |

|          |      | 3.1.1   | Single ended amplifiers                      | 18 |

|          |      | 3.1.2   | Push-Pull amplifiers                         | 20 |

|          | 3.2  | Efficie | ncy enhancement architectures                | 22 |

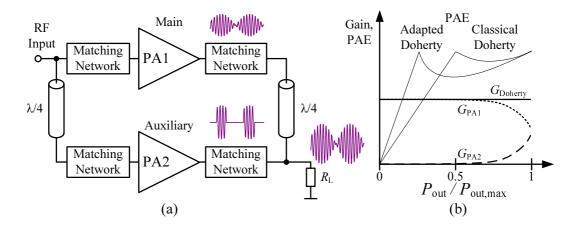

|          |      | 3.2.1   | Doherty amplifier                            | 24 |

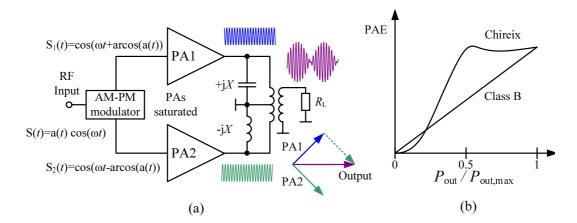

|          |      | 3.2.2   | Outphasing amplifier                         | 25 |

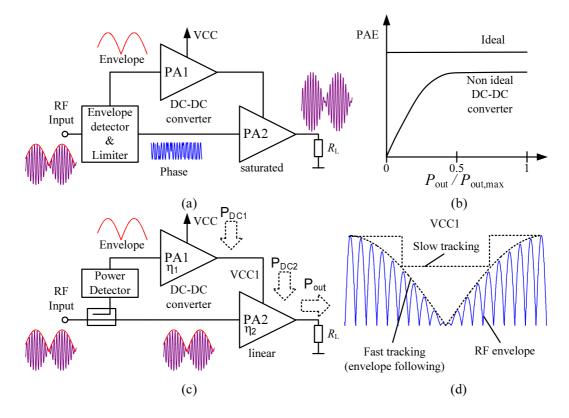

|          |      | 3.2.3   | Supply variation                             | 26 |

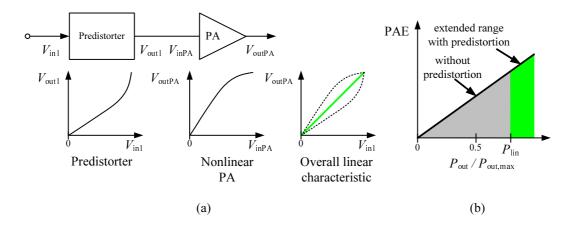

|   |     | 3.2.4  | Linearizing                                                                                                | 28  |

|---|-----|--------|------------------------------------------------------------------------------------------------------------|-----|

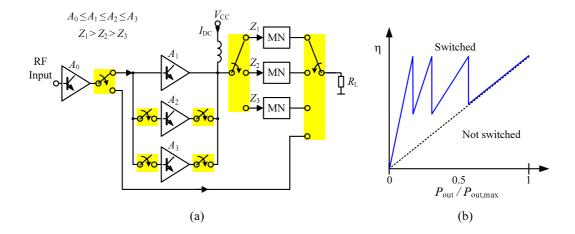

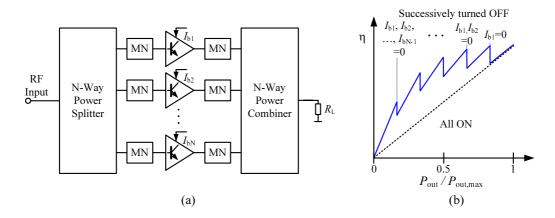

|   |     | 3.2.5  | Stage size- and load adaption (SSLA)                                                                       | 30  |

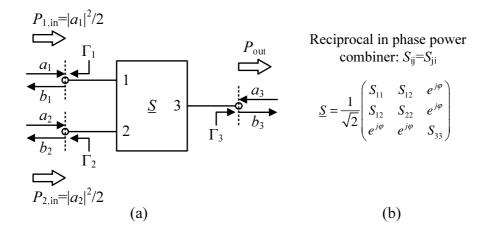

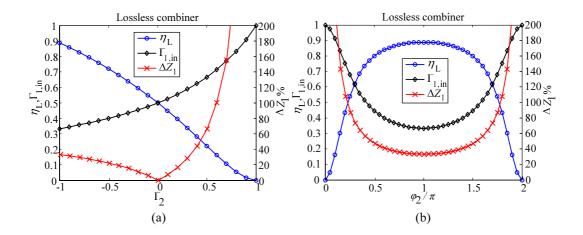

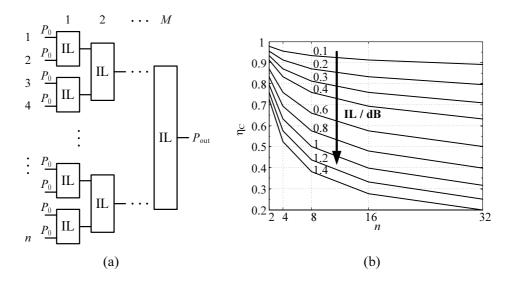

|   |     | 3.2.6  | Power Combining                                                                                            | 36  |

|   |     | 3.2.7  | Comparison of Concepts                                                                                     | 45  |

|   | 3.3 | Circui | its for reducing impact of VSWR                                                                            | 53  |

|   | 3.4 | Balan  | ced amplifier theory $\ldots \ldots \ldots$ | 57  |

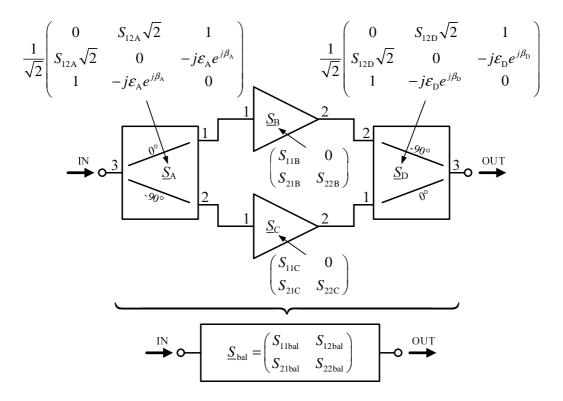

|   |     | 3.4.1  | State of the art concept                                                                                   | 57  |

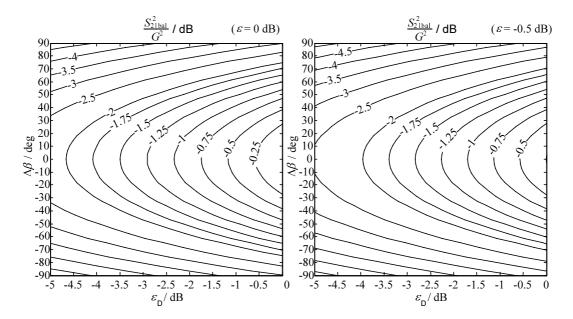

|   |     | 3.4.2  | Effect of non-idealities                                                                                   | 60  |

|   | 3.5 | Switch | h-less multi-mode PA – Balanced switched path PA $\ . \ . \ .$ .                                           | 64  |

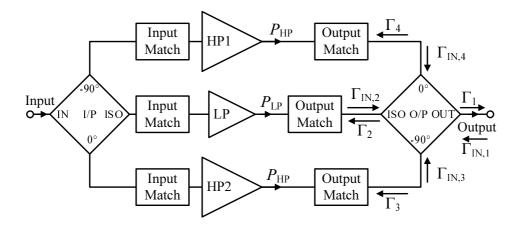

|   |     | 3.5.1  | Block diagram                                                                                              | 64  |

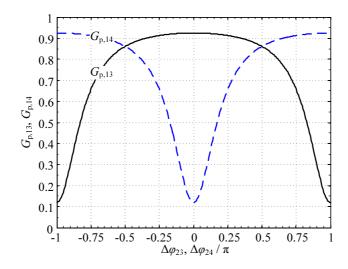

|   |     | 3.5.2  | Performance limits                                                                                         | 65  |

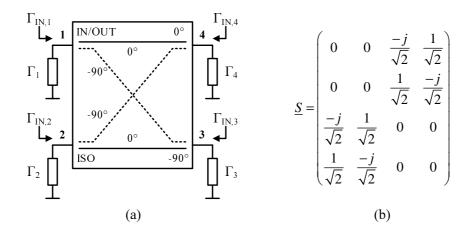

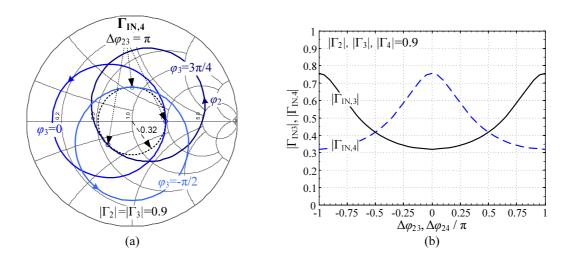

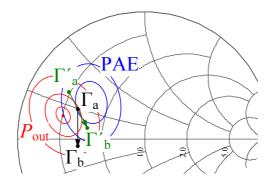

|   |     | 3.5.3  | Load Insensitivity                                                                                         | 78  |

|   | 3.6 |        | -mode PA with improved load insensitivity – Double balanced ned path PA                                    | 80  |

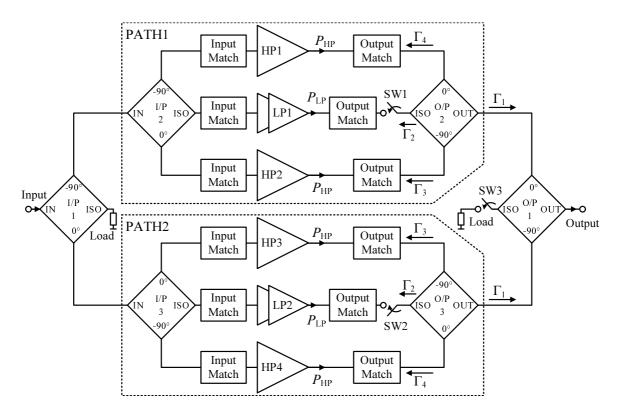

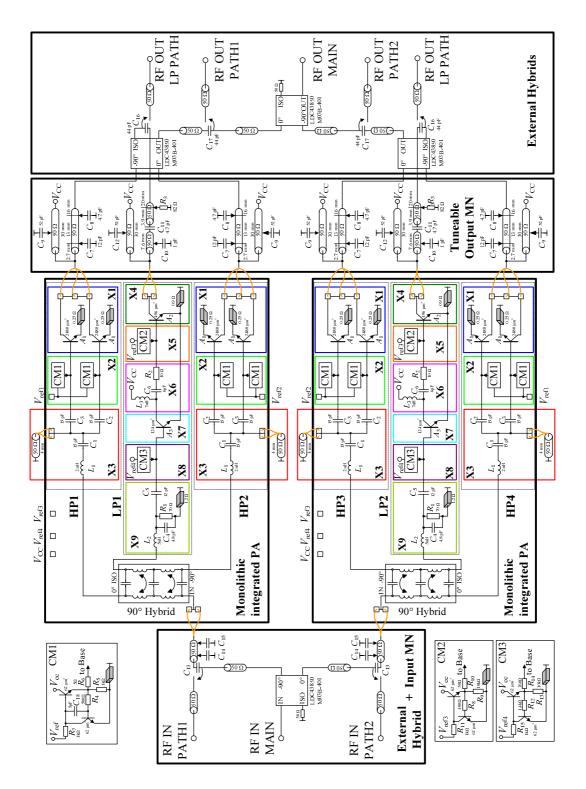

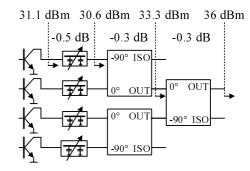

|   |     | 3.6.1  | Block diagram                                                                                              |     |

|   |     | 3.6.2  | Operation modes                                                                                            |     |

|   |     | 0.0.2  | Operation modes                                                                                            | 02  |

| 4 | Mu  | lti-Mo | de PA Circuit Design                                                                                       | 89  |

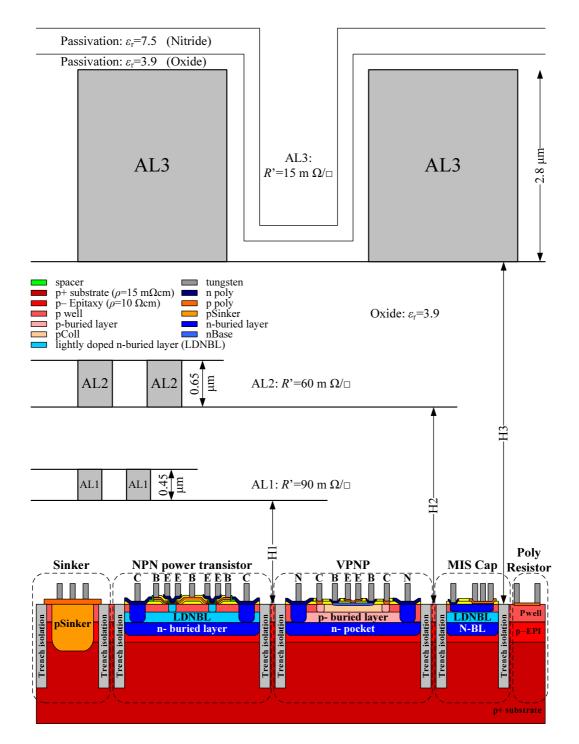

|   | 4.1 | SiGe:  | C bipolar technology and modeling $\ldots \ldots \ldots \ldots \ldots \ldots$                              | 89  |

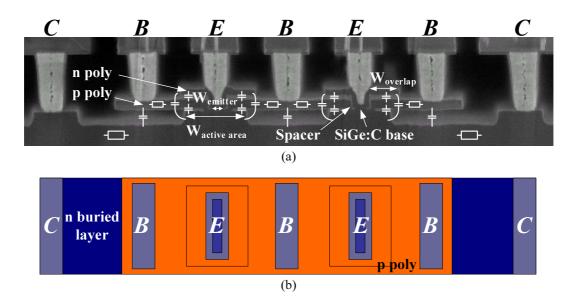

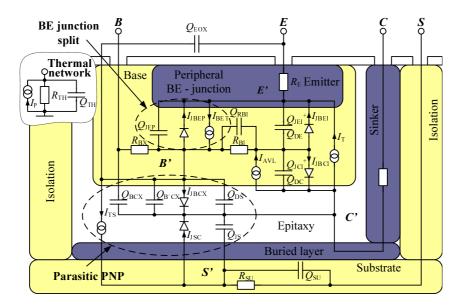

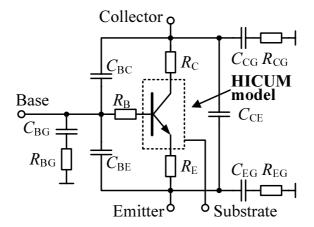

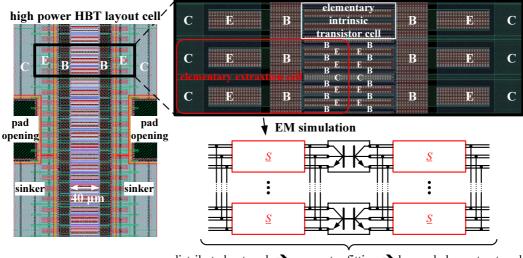

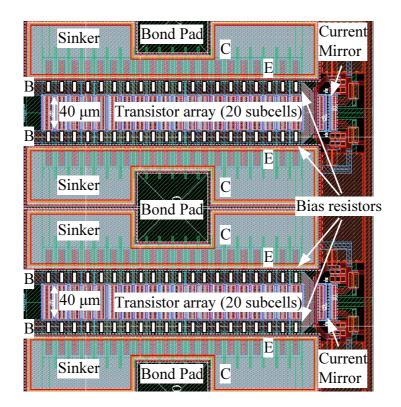

|   |     | 4.1.1  | High Power heterojunction bipolar transistor (HBT) $\ldots$ .                                              | 90  |

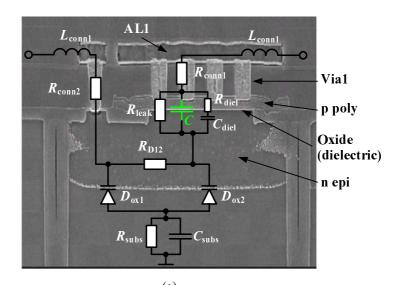

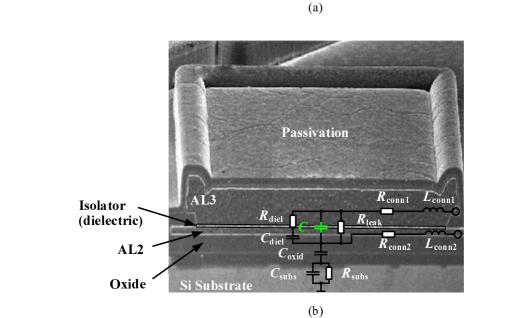

|   |     | 4.1.2  | Capacitors                                                                                                 | 97  |

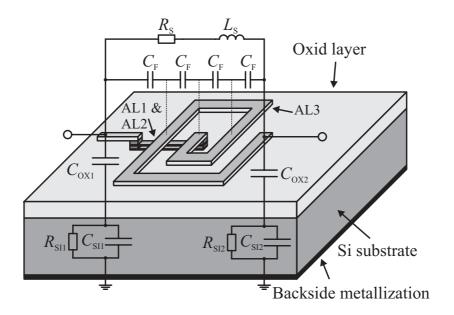

|   |     | 4.1.3  | Inductors                                                                                                  | 99  |

|   |     | 4.1.4  | Sinker                                                                                                     | 102 |

|   | 4.2 | Integr | ration of quadrature Hybrids                                                                               | 104 |

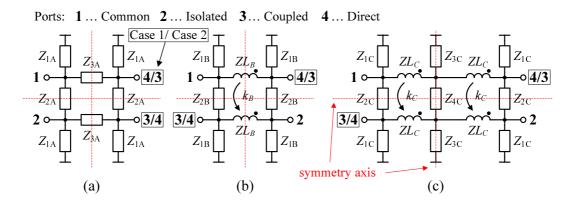

|   |     | 4.2.1  | Uncoupled lumped element hybrid                                                                            | 106 |

|   |     | 4.2.2  | Inductively coupled lumped element hybrid                                                                  | 108 |

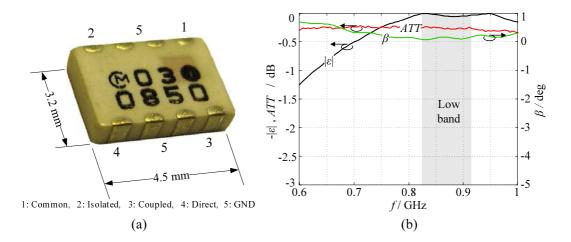

|   |     | 4.2.3  | Two section inductively coupled lumped element hybrid                                                      | 110 |

|   |     | 4.2.4  | Final hybrid design                                                                                        | 114 |

|   | 4.3 | On bo  | pard performance optimization                                                                              | 118 |

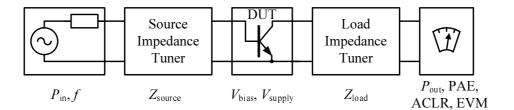

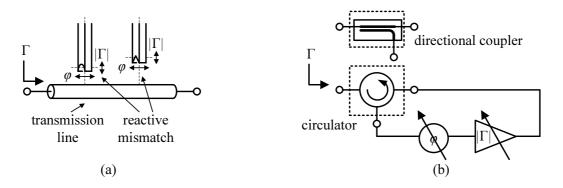

|   |     | 4.3.1  | Conventional Load Pull measurement procedures $\ldots \ldots$                                              | 118 |

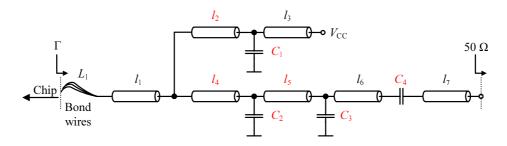

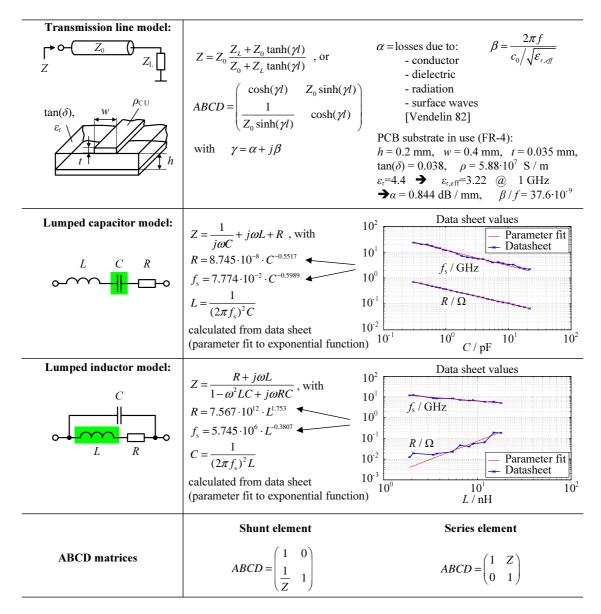

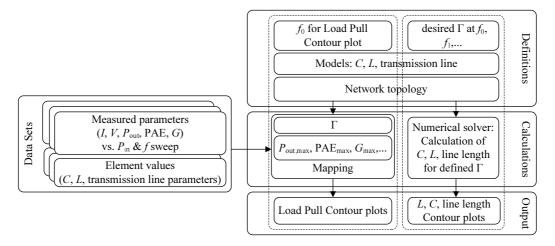

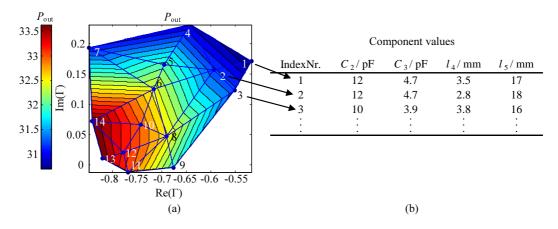

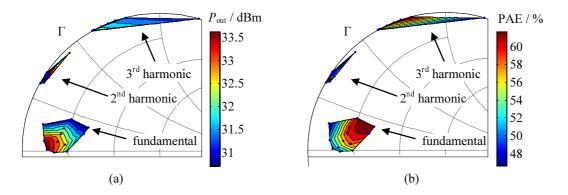

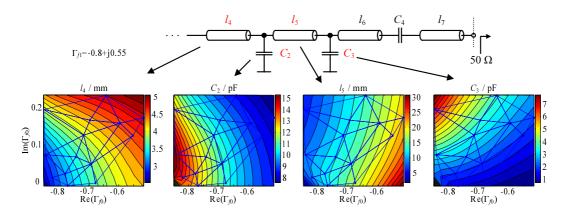

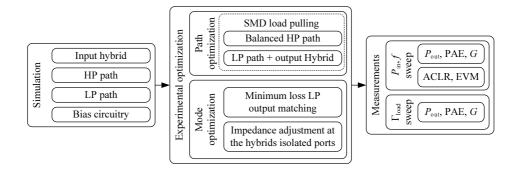

|   |     | 4.3.2  | SMD Load Pulling                                                                                           | 121 |

|   | 4.4 | Realiz | zation of the double balanced switched path PA $\ldots$                                                    | 129 |

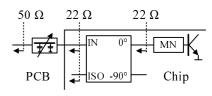

|   |     | 4.4.1  | Design overview                                                                                            | 129 |

|   |     | 4.4.2  | Simulations                                                                                                | 132 |

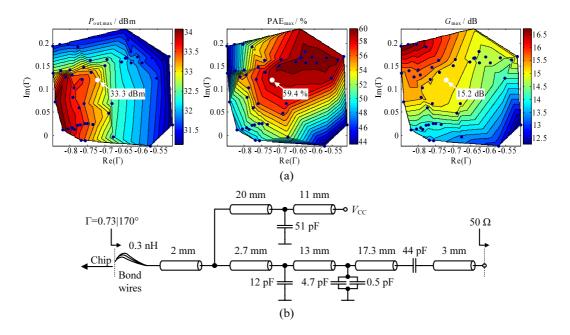

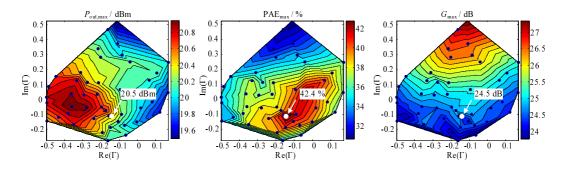

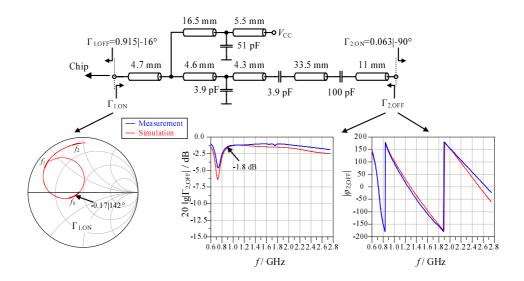

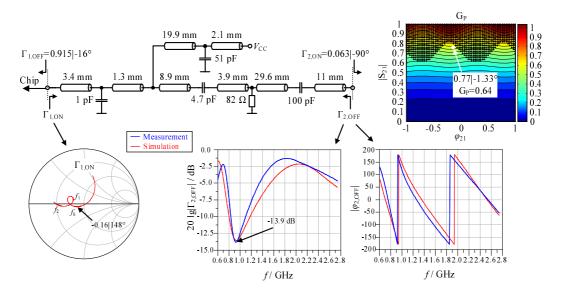

|   |     | 4.4.3  | Experimental optimization                                                                                  | 144 |

|   |     | 4.4.4  | Measurement results                                                                                        | 150 |

#### CONTENTS

| <b>5</b>     | Conclusion and Outlook                                                             |                                            |   |     |     |  |  |

|--------------|------------------------------------------------------------------------------------|--------------------------------------------|---|-----|-----|--|--|

| AĮ           | open                                                                               | dices                                      |   |     | i   |  |  |

| $\mathbf{A}$ | N-P                                                                                | Port Combiner Networks                     |   |     | i   |  |  |

|              | A.1                                                                                | Amplitude and Phase Errors                 |   |     | i   |  |  |

|              | A.2                                                                                | N-Port T-junction                          |   |     | ii  |  |  |

|              | A.3                                                                                | N-Port Lossless transmission line combiner |   |     | vi  |  |  |

|              | A.4                                                                                | N-Port Wilkinson combiner                  |   | v   | iii |  |  |

|              | A.5                                                                                | N-Port transformer based combiner          |   |     | ix  |  |  |

| в            | Reflection and Transmission in N-Port Networks with General Port<br>Impedances xii |                                            |   |     |     |  |  |

|              | B.1                                                                                | Solving the linear system of equations     |   | х   | iii |  |  |

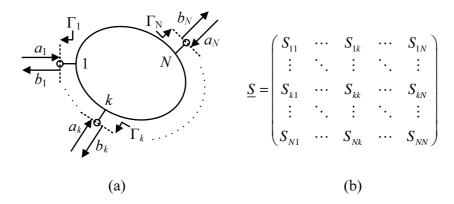

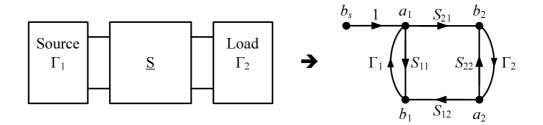

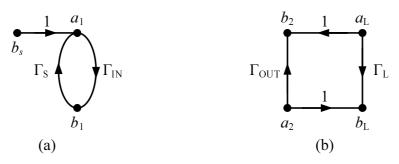

|              | B.2                                                                                | Signal flow graphs and Mason's loop rule   |   | х   | iv  |  |  |

|              | B.3                                                                                | Generalized S parameters                   |   | 2   | ٢V  |  |  |

|              | B.4                                                                                | Reduced multi-port                         |   | х   | vi  |  |  |

| С            | Gai                                                                                | n Definitions                              | 2 | κvi | iii |  |  |

| D            | Mu                                                                                 | lti-Port Network Connection                |   | XX  | ii  |  |  |

| Bi           | bliog                                                                              | graphy                                     |   |     | i   |  |  |

V

## List of Abbreviations

| AC                  | Alternating Current                                          |

|---------------------|--------------------------------------------------------------|

| ACLR                | Adjacent Channel Leakage Ratio                               |

| ACPR                | Adjacent Channel Power Ratio                                 |

| ADC                 | Analog Digital Converter                                     |

| ADS                 | Advanced Design System: Agilent circuit simulation tool      |

| AMPD                | Analog Memoryless Predistortion                              |

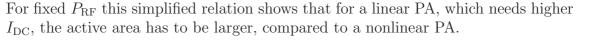

| B7HFP               | Infineon SiGe bipolar technology with $f_T = 33 \text{ GHz}$ |

| BALUN               | BALanced to $UN$ balanced                                    |

| BICMOS              | Bipolar Complementary Metal Oxide Semiconductor              |

| BJT                 | Bipolar Junction Transistor                                  |

| BO                  | Back-Off                                                     |

| CDMA                | Code Division Multiple Access                                |

| CMOS                | Complementary Metal Oxide Semiconductor                      |

| CW                  | Constant Wave (= constant frequency)                         |

| DAC                 | Digital Analog Converter                                     |

| DAT                 | Distributed Active Transformer                               |

| DC                  | Direct Current                                               |

| DCS                 | Digital Cellular System                                      |

| DMPD                | Digital Memoryless Predistortion                             |

| DUT                 | Device Under Test                                            |

| EDGE                | Enhanced Data for GSM Evolution                              |

| EER                 | Envelope Elimination and Restoration                         |

| $\mathrm{EF}$       | Envelope Following                                           |

| $\mathbf{EM}$       | Electromagnetic                                              |

| ESD                 | Electrostatic Sensitive Device                               |

| $\mathrm{ET}$       | Envelope Tracking                                            |

| EVM                 | Error Vector Magnitude                                       |

| $\operatorname{FB}$ | Feedback                                                     |

| FDMA                | Frequency Division Multiple Access                           |

| FET                 | Field Effect Transistor                                      |

| $\mathrm{FF}$       | Feedforward                                                  |

| FOM                 | Figure of Merit                                              |

| FR4                 | Flame Resistance 4                                           |

| GaAs                | Gallium Arsenide                                             |

| GaN                 | Gallium Nitride                                              |

| GMSK                | Gaussian Minimum Shift Keying                                |

| GSM                 | Global System for Mobile Communication                       |

| HB                  | High Band                                                    |

| HBT                 | Heterojunction Bipolar Transistor                            |

| HICUM               | High-Current Model                                           |

|                     | -                                                            |

| HP                   | High Power                                          |

|----------------------|-----------------------------------------------------|

| IC                   | Integrated Circuit                                  |

| IL                   | Insertion Loss                                      |

| IMD                  | Intermodulation Distortion                          |

| LB                   | Low Band                                            |

| LDMOS                |                                                     |

| LDMO5<br>LDNBL       | Laterally Diffused MOS                              |

|                      | Lightly Doped N Buried Layer                        |

| LINC<br>LNA          | Linear Amplification using Nonlinear Components     |

| LOCOS                | Low Noise Amplifier<br>Local Oxidation of Silicon   |

| LOCOS                | Low Power                                           |

| LTE                  | Long Term Evolution                                 |

| MB                   | Mid Band                                            |

| MEMS                 | Micro Electro Mechanical System                     |

| MEXTRAM              | Most Exquisite Transistor Model                     |

| MIM / MIS            | Metal Isolator Metal / Metal Isolator Semiconductor |

| MMIC                 | Monolithic Microwave Integrated Circuits            |

| MOS                  | Metal Oxide Semiconductor                           |

| MP                   | Medium Power                                        |

| OFDMA                | Orthogonal Frequency Division Multiple Access       |

| PA                   | Power Amplifier                                     |

| PAE                  | Power Added Efficiency                              |

| PCB                  | Printed Circuit Board                               |

| PCS                  | Personal Communication System/Service               |

| pHEMT                | Pseudomorphic High Electron Mobility Transistor     |

| PSK                  | Phase Shift Keying                                  |

| QAM                  | Quadrature Amplitude Modulation                     |

| $\mathbf{RF}$        | Radio Frequency                                     |

| RL                   | Return Loss                                         |

| RMS                  | Root Mean Square                                    |

| SGP                  | SPICE Gummel Poon model                             |

| SiGe                 | Silicon Germanium                                   |

| SMA                  | SubMiniatur A : Standard RF connector up to 18 GHz  |

| SMD                  | Surface Mounted Device                              |

| SiP                  | System in Package                                   |

| $\operatorname{SoC}$ | System on Chip                                      |

| SOI / SOS            | Silicon On Insulator / Silicon On Sapphire          |

| SPICE                | Simultion Program with Integrated Circuit Emphasis  |

| SSLA                 | Stage Size- and Load Adaption                       |

| TDMA                 | Time Division Multiple Access                       |

| UMTS                 | Universal Mobile Telecommunication System           |

| VBIC                 | Vertical Bipolar Inter-Company model                |

| VPNP                 | Vertical PNP transistor                             |

| VSWR                 | Voltage Standing Wave Ratio                         |

| WCDMA                | Wideband-CDMA                                       |

## List of Symbols

| A                                                                                                                                                                                                    | Area, unit: $m^2$                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| $a_i$                                                                                                                                                                                                | Incident wave to port i                                   |

| $b_i$                                                                                                                                                                                                | Reflected wave from port i                                |

| C                                                                                                                                                                                                    | Capacitance, unit: F                                      |

| D                                                                                                                                                                                                    | Diameter, unit: m                                         |

| f                                                                                                                                                                                                    | Frequency, unit: Hz                                       |

| $f_{\max}$                                                                                                                                                                                           | Maximum oscillation frequency, unit: Hz                   |

| $f_{\mathrm{T}}$                                                                                                                                                                                     | Maximum transit frequency, unit: Hz                       |

| $f_{ m S}$                                                                                                                                                                                           | Self-resonant frequency, unit: Hz                         |

| G                                                                                                                                                                                                    | Gain                                                      |

| Ι                                                                                                                                                                                                    | Current, unit: A                                          |

| j                                                                                                                                                                                                    | Imaginary unit                                            |

| k                                                                                                                                                                                                    | Coupling coefficient in a transformer                     |

| L                                                                                                                                                                                                    | Inductance, unit: H                                       |

| l                                                                                                                                                                                                    | Length, unit: m                                           |

| n                                                                                                                                                                                                    | Number of input ports in a power combiner                 |

| N                                                                                                                                                                                                    | Total number of ports in a power combiner                 |

| P                                                                                                                                                                                                    | Power, unit: W                                            |

| Q                                                                                                                                                                                                    | Quality factor                                            |

| R                                                                                                                                                                                                    | Resistance, unit: $\Omega$                                |

| r                                                                                                                                                                                                    | Radius, unit: m                                           |

| $S_{ij}$                                                                                                                                                                                             | Scattering parameters                                     |

| $\frac{U}{V}$                                                                                                                                                                                        | Unity matrix: $\underline{U} = \text{diag}(1, \ldots, 1)$ |

| V                                                                                                                                                                                                    | Voltage, unit: V                                          |

| w                                                                                                                                                                                                    | Winding ratio in a transformer                            |

| X                                                                                                                                                                                                    | Reactance, unit: $\Omega$                                 |

| Y                                                                                                                                                                                                    | Complex admittance, unit: $\Omega$                        |

| Z                                                                                                                                                                                                    | Complex impedance, unit: $\Omega$                         |

| - ()                                                                                                                                                                                                 |                                                           |

| $\operatorname{Re}(\cdot)$                                                                                                                                                                           | Real part                                                 |

| $\operatorname{Im}(\cdot)$                                                                                                                                                                           | Imaginary part                                            |

| $\operatorname{diag}(\cdot)$                                                                                                                                                                         | Diagonal matrix                                           |

| $ \frac{\vec{X}}{\hat{X}} \\ \frac{\hat{X}}{\overline{X}} $                                                                                                                                          | Vector X                                                  |

| X                                                                                                                                                                                                    | Peak value of X                                           |

| $\overline{X}$                                                                                                                                                                                       | Average value of X                                        |

| $ \underline{X} $ or $\det(\underline{X})$                                                                                                                                                           | ) Determinant of $\underline{X}$                          |

| $\underline{X}^{\mathrm{T}}$                                                                                                                                                                         | Transpose matrix                                          |

| $\underline{X}^*$                                                                                                                                                                                    | Complex conjugate matrix                                  |

| $\frac{ \underline{X}  \text{ or } \det(\underline{X})}{\underline{X}^{\mathrm{T}}}$ $\frac{\underline{X}^{\mathrm{T}}}{\underline{X}^{*}}$ $\frac{\underline{X}^{-1}}{\underline{X}^{*\mathrm{T}}}$ | Inverse matrix of $\underline{X}$                         |

| $\underline{X}^{*\mathrm{T}}$                                                                                                                                                                        | Transpose conjugate matrix                                |

|                                                                                                                                                                                                      |                                                           |

| $\alpha$        | Conduction angle                       |

|-----------------|----------------------------------------|

| $\beta$         | Phase error, unit: dB                  |

| $\eta$          | Collector/Drain efficiency, unit: $\%$ |

| ε               | Amplitude error, unit: dB              |

| $\varepsilon_r$ | Relative permittivity                  |

| Γ               | Reflection coefficient                 |

| $\lambda$       | Wavelength, unit: m                    |

| $\mu$           | Permeability, unit: Vs/Am              |

| ω               | Angular frequency, unit: Hz            |

| ρ               | Resistivity, unit: $\Omega m$          |

| $\varphi$       | Reflection coefficient angle           |

|                 |                                        |

## Chapter 1

## Introduction

### 1.1 Trends in cellular communication

The recent growth of mobile communication market and increased number of users has pushed demands for modulation standards with higher capacities within the regulated spectrum allocations. Multiple access techniques have developed from simple FDMA (Frequency Division Multiple Access) and TDMA (Time Division Multiple Access) systems to more elaborate CDMA (Code Division Multiple Access) and OFDMA (Orthogonal Frequency Division Multiple Access) systems. These allow a higher number of users in densely populated areas due to higher spectral efficiency and increased data rates. Along with the gained data rate improvements the demand in the wireless market has not been restricted to voice communication, but has also included new services and features such as video and data applications.

The evolution of standards, developed for cellular multiple access, can basically be divided into three generations. The first generation (1G) was based on analog frequency modulation schemes, providing voice communication for a limited number of users. The second generation (2G) comprises the first standards with digital modulation formats and TDMA/FDMA access, which provide higher network capability, higher security and better communication quality. These include GSM (Global System for Mobile Communications) [3GPP 09,a], as first transnational cellular communication standard for voice communication. Due to the constant envelope GMSK (Gaussian Minimum Shift Keying) modulation format very robust and efficient systems could be implemented. By adaption with the packet-switched 2.5G standard GPRS (General Packet Radio Service), network utilization rate could be further improved, while sharing the same network infrastructure with GSM. Higher data rates were achieved by the 2.75G extension EDGE (Enhanced Data for GSM Evolution), operating in the same frequency bands as GSM. The used modulation format 8-PSK (Phase Shift Keying) causes a varying transmit signal envelope, requiring linear systems with respect to amplitude and phase. The third generation (3G) comprises CDMA and OFDMA standards, namely UMTS (Universal Mobile Telecommunication System) / WCDMA (Wideband-CDMA) [3GPP 09,b, 3GPP 07,b] and LTE (Long Term Evolution) [3GPP 07,a]. WCDMA was introduced as first globally standardized multimedia systems. Users occupy the same frequency spectrum, being separated by code orthogonality. The modulation format HPSK (Hybrid Phase Shift Keying) leads to a non-constant signal envelope with even higher requirements on system linearity than EDGE. The 3.5G extension HSPA (High Speed Packet Access) allows higher data rates (28...84 Mbit/s) but at the expense of higher peak to average ratios and more stringent linearity requirements. The latest 3.9G evolution LTE was introduced as an extension to existing 3G systems. It represents a cost-effective radio-access technology, which uses the same frequency allocations as WCDMA (Fig. 1.1), but supplies even time critical applications like online gaming. The spectral efficiency is improved by flexible transmission bandwidths (1.4...20 MHz), which can be adapted to the user's data rate requirements. This is gained by the OFDMA or similar SC-FDMA (Single Carrier-FDMA) technique, where a scalable number of orthogonal frequency subcarriers is used to adapt the occupied bandwidth. The use of many modulated carriers also reduces inter-symbol interference in multipath environments, as the corresponding symbol duration can be made larger than the delay spread of the transmission channel. With a temporal guard interval (cyclic extension) to each symbol the different propagation delays of the subcarriers and thus the inter symbol interference can be completely eliminated. This robustness together with diversity transceivers allows data rates of up to 75 Mbit/s in uplink and 300 Mbit/s in downlink. The used modulation formats QPSK / 16 QAM require high amplitude and phase linearity of the radio equipment as for WCDMA or HSPA. The system specifications of LTE, regarding power range, linearity, and frequency are very similar to WCDMA, why the same RF radio front end will be used.

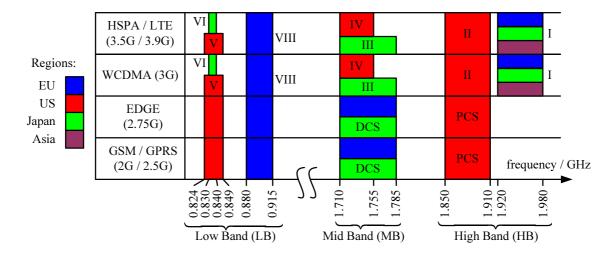

Figure 1.1: Frequency allocation of mobile communication standards. (PCS ... Personal Communication System/Service; DCS ... Digital Cellular System)

Each of the introduced standards offers optimized network utilization for its designated field of application (voice, data or multimedia). The coexisting infrastructure (base stations, telephone switches,...) of 2G and 3G networks currently allows par-

allel operation in areas where available. This requires handsets, with the ability to connect to multiple systems. Having a look at the geographical expansion of 2G and 3G networks it becomes apparent that currently worldwide similar frequency bands are occupied, which can be subsumed as low band (LB), mid band (MB) and high band (HB) (Fig. 1.1). Multi-band radio frequency (RF) systems, which operate in these three bands are required by the market to allow world-wide distribution of handsets. The challenge, however remains on designing multi-mode systems, which fulfill the air interface specifications (Table 1.1) with a minimum number of components for a competitive price.

| Parameters                                                                                                                                        | GSM                         |             | EDGE                        |             | WCDMA                       | LTE                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------|-----------------------------|-------------|-----------------------------|--------------------------------|

|                                                                                                                                                   | LB MB/HB                    |             | LB MB/HB                    |             | LB/MB/HB                    | LB/MB/HB                       |

| Modulation                                                                                                                                        | GMSK                        |             | 8-PSK                       |             | HPSK                        | $\mathrm{QPSK}/\mathrm{16QAM}$ |

| Duplex mode                                                                                                                                       | $\mathrm{TDD}/\mathrm{FDD}$ |             | $\mathrm{TDD}/\mathrm{FDD}$ |             | $\mathrm{TDD}/\mathrm{FDD}$ | TDD/FDD                        |

| Multiple access                                                                                                                                   | TDMA/FDMA                   |             | TDMA/FDMA                   |             | CDMA                        | SC-/OFDMA                      |

| Bandwidth $\Delta f$ (MHz/Channel)                                                                                                                | 0.2                         |             | 0.2                         |             | 5                           | 1.420                          |

| Max. datarate<br>(kbit/s)                                                                                                                         | 22.8                        |             | 384                         |             | 2000                        | 300000                         |

| $P_{\rm out,max}$ (dBm)                                                                                                                           | 33                          | 30          | 27                          | 26          | 24                          | 23                             |

| $P_{\text{out}}$ control range (dB)                                                                                                               | 28                          | 30          | 22                          | 21          | 68                          | 63                             |

| Peak-average ratio<br>(dB)                                                                                                                        | 0                           |             | 3.2                         |             | $3.5 \dots 7$               | 7.5/8.5                        |

| Peak EVM (%)                                                                                                                                      | _                           |             | 20                          |             | 17.5                        | 17.5                           |

| Peak phase Error<br>(degree)                                                                                                                      | 20                          |             | _                           |             | _                           | _                              |

| ACLR (dBc)<br>@±5 MHz<br>@±10 MHz                                                                                                                 | _                           |             | _                           |             | < -33 < -43                 | _                              |

| $\begin{array}{l} \text{ACLR (dBc)} \\ @\pm \frac{(\Delta f + 3.84 \text{ MHz})}{2} \\ @\pm \frac{(\Delta f + 11.52 \text{ MHz})}{2} \end{array}$ | _                           |             | _                           |             |                             | < -33<br>< -36                 |

| Mod. Spec. (dBc)<br>$@\pm 400 \text{ kHz}$<br>$@\pm 600 \text{ kHz}$                                                                              |                             | < -60 < -60 |                             | < -54 < -60 |                             | _                              |

| Noise $\left(\frac{dBm}{100 \text{ kHz}}\right)$<br>@20 MHz                                                                                       | <                           | < -79       |                             | _           | _                           | _                              |

Table 1.1: Transmitter air interface specifications of GSM, EDGE, WCDMA and LTE.

### 1.2 PAs in mobile handsets

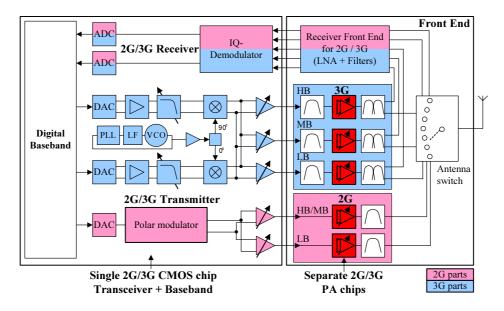

Figure 1.2: Block diagram of a typical GSM/EDGE/WCDMA cellular radio [Infineon Tec 08, Freescale Se 08].

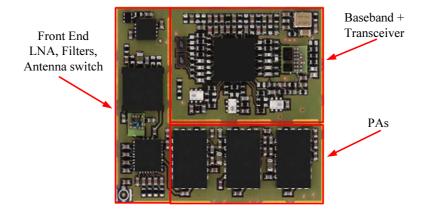

The ability of a mobile handset to connect to multiple systems demands higher integration of functionality, currently obtained by implementation of multiple parallel transmit paths. The block-diagram of a typical multi-mode multi-band cellular radio is shown in Fig. 1.2. This includes the baseband processing, transmitter and receiver (transceiver) and the front end (PA, LNA, filters, duplexers, antenna switch). Due to innovations in design techniques the number of discrete active components has reduced over the years. The focus was laid on full integration of transceiver and baseband using low-cost Si based CMOS technology. The form factors have reduced, as illustrated in Fig. 1.3, but the PA units still consume a remarkable area. An own PA module is necessary for each standard, requiring separate control logic, transmit filters and multi-pole antenna switches. Major attempts are now the higher integration of PA circuits using single chain topologies, to enable transmission of 2G/3G signals by a single PA for each band. In addition trends emerge to replace currently used expensive GaAs technologies for PAs by Si-based technologies to further reduce cost and size by integrating the PA together with the transceiver. This requires not only to be technically feasible but also commercially reasonable to really happen. This will depend on the balance between increased development costs and savings of production costs.

The reason why a separate PA is still used for each standard is its impact on the overall performance of the handset, in particular its talk time. The PA has to amplify the signal, generated by the transmitter, to the necessary output power level with smallest possible current consumption, while fulfilling linearity, stability, robustness and noise specifications. The varying environment of the PA like supply

Figure 1.3: Photograph of a GSM/EDGE/WCDMA cellular phone's RF parts.

voltage changes in the range of 2.5...5.5 V and load impedance variations up to a VSWR=1:10, require a design with high margins for maintaining efficient and stable operation without reducing integrity of the transmit signal. Including standards with different specifications increases the necessary margin, which is then mainly reflected in increased power consumption and reduced talk-time.

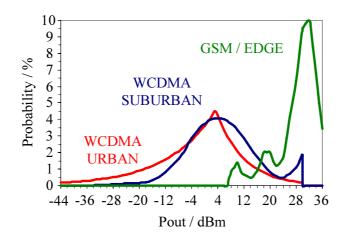

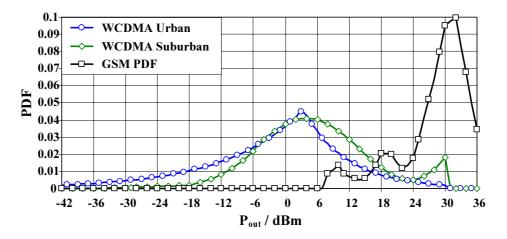

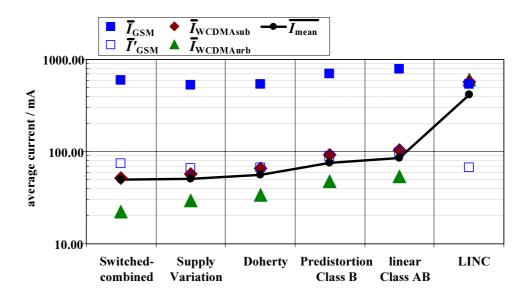

Figure 1.4: Output power probability density function (PDF) for GSM/EDGE/WCDMA [Egolf 07].

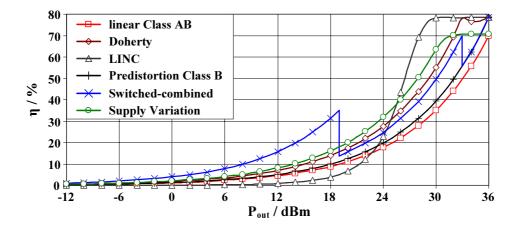

Another reason for the poor efficiency of multi-mode handset PAs is found in system dependent regulation of transmit power. The power transmitted by the mobile unit is adjusted to compensate environmental effects, such as distance to the base station and fading. Statistical analysis provided by service providers [Egolf 07] have shown that 2G systems operate near maximum output power most of the time, in 3G systems the operation at maximum levels is unlikely. The most likely transmit power level is about 30 dB smaller than for 2G systems, as shown in Fig. 1.4. Due to the inherent drop of PA efficiency with reduced output power it is apparent that separate 2G and 3G PAs, optimized for the dedicated power range, can more effectively reduce the system's current consumption. Future multi-mode PAs therefore have to cover a very large dynamic range with high DC to RF conversion efficiency.

Performance degradation and ruggedness under mismatch conditions is another concern for single-chain PA implementation. Separate PA modules, as currently implemented in GaAs technologies, have remarkable RF performance under nominal load conditions and withstand high mismatch conditions without damage. Considering multi-mode PAs in Si technologies, a compromise has to be made between nominal RF performance and operation under mismatch, mostly at cost of efficiency. Multimode PAs therefore also have to adapt concepts for improved insensitivity to load mismatch. For cost reasons (size, number of components) these should be capable of being integrated without additional external active control chips.

The main challenges of achieving the goal of high power, highly efficient, linear single chain PA modules can not only be addressed by technological developments. New concepts and topologies have to be established to improve classical design approaches and increase efficiency and load insensitivity of the PA over a large linear output power range.

The aim of this work is to find new solutions, beyond existing concepts, to achieve better linearity versus efficiency compromises over a large dynamic range with load insensitive behavior. The theoretical findings are of general nature, being applicable to any combination of 2G/3G standards. Due to the strong industrial-related focus of the project, the developed prototype and the experimental evaluation concentrates on GSM, EDGE and WCDMA.

### 1.3 Thesis outline

Chapter 2 will give a brief review of PA characteristics and operation modes.

Chapter 3 introduces several efficiency improvement techniques and discusses impacts of load variations and possibilities for their reduction. The balanced PA is further examined and a novel concept for a multi-mode PA is analyzed in detail.

Chapter 4 concentrates on the implementation of the multi-mode PA in a low cost SiGe technology. The technology is presented and relevant circuit design issues (onchip quadrature hybrid implementation, simulations and experimental optimization) for the prototype realization are considered.

Chapter 5 summarizes the main findings and gives a proposal for further work.

## Chapter 2

## **Power Amplifier Characteristics**

To evaluate the performance of a power amplifier, system dependent parameters have to be defined. While specifications only regulate upper limits, which have to be fulfilled, the parameters are also used for comparing quality of different PAs for the same application. This chapter provides definitions of PA parameters, important for GSM/EDGE/WCDMA systems. Very briefly a review of basic PA operation classes will be given at the end to show the inherent efficiency linearity trade-off in classical PA designs.

### 2.1 Basic Parameters

#### 2.1.1 Output Power and Power Distribution Function

The most important parameter for a PA is the maximum output power  $P_{\text{out,max}}$ , which can be delivered to a specified load  $R_{\text{L}}$ . This can be calculated by  $P_{\text{out,max}} = 1/2$  Re( $V_{\text{max}}I_{\text{max}}^*$ ), which reduces for a sinusoidal signal to  $P_{\text{out,max}} = \hat{V}_{\text{max}}^2/(2R_{\text{L}})$ . When the drive level for the PA is reduced, the voltage peak  $\hat{V}$  reduces and less output power is delivered to the load. This operating condition below  $P_{\text{out,max}}$  is called power back-off BO and the amount of BO is usually given in dB, related to the maximum output power (BO = 10 lg ( $P_{\text{out}}/P_{\text{out,max}}$ ) dB). A statistical analysis of the rate with which a PA is operated at BO leads to the so called power distribution function (PDF). This gives information on the probability for occurrence of specific output power levels, as shown in Fig. 1.4.

#### 2.1.2 Gain and 1 dB compression point

The gain is defined as the relation between output power and input power  $G = P_{\text{out}}/P_{\text{in}}$ . Depending on the kind of measured power there exist four different small signal gain definitions: transducer gain, operating power gain, available power gain and maximum available gain (see Appendix C). The usual definition for PAs is the

transducer gain, which accounts for mismatch loss at the input and the output. At large BO power levels where the gain characteristic versus output power is almost constant the PA is operated in its linear range and the gain value is called linear gain  $G_{\text{lin}}$ . When a PA is driven towards its maximum output power the gain starts to drop. The power level at which the gain is reduced by -1 dB is named the one dB compression point. This can be referred to the input  $P_{\text{in},-1 \text{ dB}}$  or the output  $P_{\text{out},-1 \text{ dB}}$ . At maximum output power the minimum gain value is obtained, which is then called the saturated power gain  $G_{\text{sat}}$ .

#### 2.1.3 Efficiency

The PA is a device, which basically converts the DC power, drawn from a supply (in handsets this is the battery), to an RF signal power. The efficiency, also known as DC to RF efficiency or collector/drain efficiency is defined by:

$$\eta = \frac{P_{\rm out}}{P_{\rm DC}},\tag{2.1}$$

with  $P_{\rm DC}$  as the DC power supplied to the collector/drain contact of the PA. As the contribution of the input drive power can considerably worsen the overall power budget, an alternative definition is given by the power added efficiency:

$$PAE = \frac{P_{out} - P_{in}}{P'_{DC}} = \frac{P_{out}}{P'_{DC}} \left(1 - \frac{1}{G}\right), \qquad (2.2)$$

where  $P'_{\rm DC}$  subsumes the total supply power, including driver stages. The PAE converges to  $\eta$  for very large gain values (> 10 dB) and small pre-driver power consumption. Efficiency in a PA reduces significantly with increased BO power levels. To consider the variations of output power over time, the signal statistics in terms of the PDF can be used to define an average efficiency [Sevic 97]:

$$\overline{\eta} = \frac{\int P_{\text{out}} \cdot \text{PDF}(P_{\text{out}}) \, dP_{\text{out}}}{\int P_{\text{dc}}(P_{\text{out}}) \cdot \text{PDF}(P_{\text{out}}) \, dP_{\text{out}}}$$

(2.3)

This measure is more useful for comparison of PAs, when considering systems with large BO power probability, such as WCDMA.

#### 2.1.4 Linearity

The transmitted information in wireless communication systems is embedded in the amplitude and the phase variation of the RF signal. The tolerated limits of distortion for recovering the information and not interfering with other users can be expressed with different measures, depending on the system specifications. In general the nonlinearities in a PA can be traced back to AM-AM and AM-PM distortion mechanisms [Kennington 00, Vuolevi 03]. The AM-AM characteristic basically describes the compression of output signal amplitude with increasing input signal level. The AM-PM characteristic reflects the undesired nonlinear impact of input amplitude variation on output phase. Common measures deduced from single tone and two tone excitation, such as  $P_{-1dB}$  and intermodulation distortion (IMD), are often insufficient to describe the PA's linearity, when driven with complex modulation signals. Additional electrically and thermally induced memory effects lead to waveform dependent non-linearities [Vuolevi 01]. Therefore other system relevant measures have to be introduced like EVM, modulation spectrum and ACLR/ACPR, which are described in the following.

#### EVM

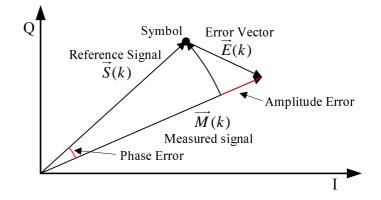

For digital modulation schemes the information data is mapped to so called symbols in a constellation diagram (IQ-diagram). Each symbol is identified by a vector of certain amplitude and phase. Due to various impairments in the system the vector is distorted in amplitude and phase, leading to potential symbol detection errors. The error vector  $\vec{E}(k)$  is a measure of how far the actual detected constellation points  $\vec{M}(k)$  deviate from the ideal locations  $\vec{S}(k)$ :  $\vec{E}(k) = \vec{M}(k) - \vec{S}(k)$ , where k denotes the consecutive number of samples. A graphical illustration is shown in Fig. 2.1.

Figure 2.1: EVM measurement illustration in the IQ-diagram.

Since the deviation is of statistical nature, the root mean square (RMS) EVM is defined as ratio of the mean powers between the error vector and the ideal signal, measured for many samples K:

$$\text{EVM}_{\text{RMS}} = \sqrt{\sum_{k \in K} |\vec{E}(k)|^2} / \sum_{k \in K} |\vec{S}(k)|^2$$

(2.4)

The maximum EVM is also specified for 2G and 3G signals:

$$EVM_{peak} = \max_{k \in K} \sqrt{|\vec{E}(k)| / \frac{1}{K} \sum_{k \in K} |\vec{S}(k)|^2}$$

(2.5)

Details on measurement procedures can be found in [Agilent 02].

#### Phase Error

For signals, where all information is contained in the phase, as in GSM, the signal quality is also specified by the maximum phase error between the transmitted and the expected ideal signal. This is similar to tracing the AM-PM characteristic of the PA, but the complex valued transmit signal is used instead of a single tone.

#### Spectral Mask and Modulation Spectrum

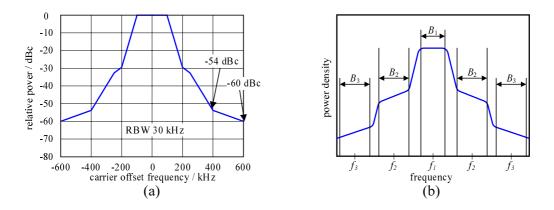

Figure 2.2: Spectral emission measures: (a) Spectral mask, (b) ACLR

Excessive radiation at frequencies beyond the channel bandwidth lead to interference with neighbor channels. To describe this out of band emission, the spectral mask or modulation spectrum (Mod. Spec.) is specified in 2G systems. This is defined as the maximum allowed power density outside the signal band, normalized to the power density within the signal band, as a function of the frequency offset from the carrier. The power density is measured within a certain resolution bandwidth RBW. Fig. 2.2 (a) shows the specification for GSM/EDGE.

#### ACLR/ACPR

A similar measure to the spectral mask is the adjacent channel leakage/power ratio (ACLR/ACPR). This is specified for 3G systems and replaces the definition of spurious out of band emissions for 2G systems. The ACLR is defined as the ratio of the total power in the transmission channel with bandwidth  $B_1$  to the total power within a certain bandwidth ( $B_2$ ) in the channel adjacent to the transmission channel at a certain offset frequency  $f_2$  to the carrier frequency  $f_1$ . An illustration is provided in Fig. 2.2 (b). For WCDMA the bandwidths for power integration are 3.84 MHz.

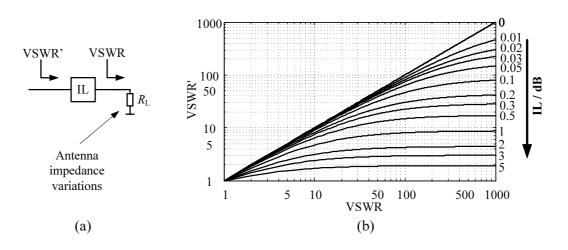

#### 2.1.5 VSWR

In a mobile handset the performance and reliability of a PA is subject to load impedance changes. The load variations occur due to antenna impedance changes caused by use in real life scenarios (e.g. grip of phone). The specifications for output power reduction and device degradation or destruction are usually given for a maximum voltage standing wave ratio (VSWR) of the load. As the load reflection coefficient value  $\Gamma_{\rm L}$  is readily accessible with a network analyzer, the VSWR can be expressed by:

$$VSWR = \frac{1 + |\Gamma_L|}{1 - |\Gamma_L|}$$

(2.6)

As  $\Gamma_{\rm L}$  is related to a nominal load impedance  $Z_0$  (usually 50  $\Omega$ ), the VSWR can be seen as a relative measure of changes in the impedance magnitude.

## 2.2 Parameter table for GSM/EDGE/WCDMA

The air interface system specifications for GSM/EDGE/WCDMA can be found in Table 1.1. These requirements are defined at the antenna of the whole transmitter system. The relation between the system requirements and the PA requirements is determined by the circuit environment of the PA. This typically consists of:

- Output interface circuits such as harmonic and duplex filters, matching network and switch for separation of transmit and receive signals. These components mainly add additional losses and some mismatch, which reduce output power and efficiency of the PA module, which has to be considered in the specification.

- Input transceiver, which generates the transmit signal at a low power level (0...10 dBm). The generated signal has a certain amount of ACLR/EVM and noise, thus decreasing the PA's linearity and noise figure budget compared to system specifications.

- Power supply, which is often coming directly from the battery or stabilized by a DC/DC converter. Allowed supply variations in the charge and discharge cycles of the battery have to be specified.

The signal degradation at the input, the output and through the varying supply has to be considered and the PA is designed with margin to the system specifications. As the actual margin values depend on the specific components and architectures, used for the system, only typical values can be given as indicator for a cellular PA design. Table 2.1 sums up the typical requirements for cellular PAs.

| Parameters                              |    | GSM<br>LB MB/HB |    | EDGE<br>LB MB/HB |    |                 |  |  |

|-----------------------------------------|----|-----------------|----|------------------|----|-----------------|--|--|

| Supply Voltage (V)                      |    | $2.5 \dots 5.5$ |    | $2.5 \dots 5.5$  |    | $2.5 \dots 5.5$ |  |  |

| $P_{\rm out,max}$ (dBm)                 | 36 | 33              | 30 | 29               | 27 | 27              |  |  |

| PAE @ $P_{\text{out,max}}$ (%)          |    | > 50            |    | > 20             |    | > 40            |  |  |

| typ. $G_{\rm lin}$ (dB)                 |    | 40              |    | 30               |    | 30              |  |  |

| ACLR (dBc) $@\pm 5$ MHz                 |    | _               |    | _                |    | -35             |  |  |

| ACLR (dBc) $@\pm 10$ MHz                |    | _               |    | _                |    | -45             |  |  |

| Mod. Spec. (dBc) $@\pm 400 \text{ kHz}$ |    | -64             |    | -58              |    | -               |  |  |

| Mod. Spec. (dBc) $@\pm 600 \text{ kHz}$ |    | -64             |    | -64              |    | _               |  |  |

| Average EVM $(\%)$                      |    | _               | <  | < 59             |    | —               |  |  |

| $VSWR_{max}$ , no damage                |    | 10:1            |    | 10:1             |    | 10:1            |  |  |

Table 2.1: PA module specifications of mobile communication standards (GSM, EDGE and WCDMA).

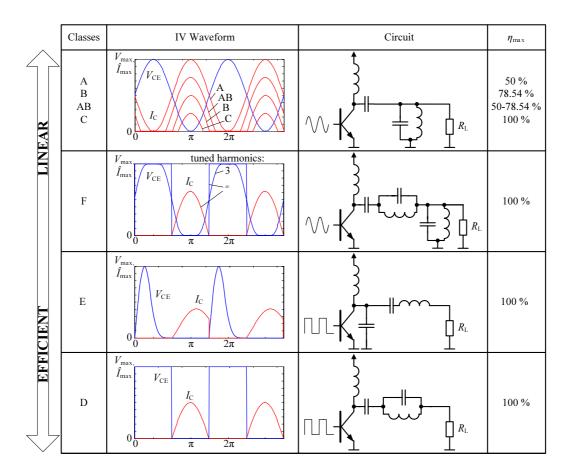

### 2.3 Operation Classes

As the operation modes of power amplifiers are well explained in literature and broadly covered in textbooks such as [Cripps 99, Lee 98, Krauss 80, Shirvani 03], the following section will only give a brief overview of the classification to form an understanding of the inherent tradeoff between linearity and efficiency.

A typical PA circuit consists of an active device and a load or matching network. The classification of PAs can be done on basis of the active device's operation mode: current source or switching mode. A further distinguishing characteristic is the kind of load represented to the PA: filter with load adjustment only at the fundamental frequency or tuning of fundamental and harmonic frequencies.

Current source PAs include classes A, AB, B and C, while classes D, E and F are switching PAs - depending on how hard the active device is driven. For class A, AB, B, C and D only fundamental frequencies are matched, while class E and F operation requires additional tuning of harmonics.

#### 2.3.1 Class A, AB, B and C

This family of PAs has similar circuit configuration, and distinction is based upon the biasing conditions. As shown in Fig. 2.4 the voltage waveform at the collector  $V_{\rm CE}$  is purely sinusoidal, while the current through the transistor  $I_{\rm C}$  is truncated below zero. How long the device is turned on in one RF cycle is expressed by the so called conduction angle  $\alpha$ . It is obvious that dissipation of power at the transistor only occurs, if  $V_{\rm CE}$  and  $I_{\rm C}$  are > 0 at the same time. The main target of reducing  $\alpha$  is the reduction of dissipation and thereby the increase of efficiency. To see the effect on linearity the  $\alpha$  dependent current waveform can be decomposed into its harmonic contents by Fourier analysis [Cripps 99]:

$$I_{\rm DC} = \frac{I_{\rm max}}{2\pi} \int_{-\alpha/2}^{\alpha/2} \frac{\cos\theta - \cos\frac{\alpha}{2}}{1 - \cos\frac{\alpha}{2}} \,\mathrm{d}\theta = \frac{I_{\rm max}}{2\pi} \frac{2\sin\frac{\alpha}{2} - \alpha\,\cos\frac{\alpha}{2}}{1 - \cos\frac{\alpha}{2}} \tag{2.7}$$

$$\hat{I}_{n} = \frac{I_{\max}}{\pi} \int_{-\alpha/2}^{\alpha/2} \frac{\cos\theta - \cos\frac{\alpha}{2}}{1 - \cos\frac{\alpha}{2}} \cos n\theta \, \mathrm{d}\theta = \lim_{n' \to n} \frac{2I_{\max}}{\pi} \frac{\sin(n'\frac{\alpha}{2})\cos(\frac{\alpha}{2}) - n'\cos(n'\frac{\alpha}{2})\sin(\frac{\alpha}{2})}{(n'^{3} - n)(1 - \cos(\frac{\alpha}{2}))}$$

(2.8)

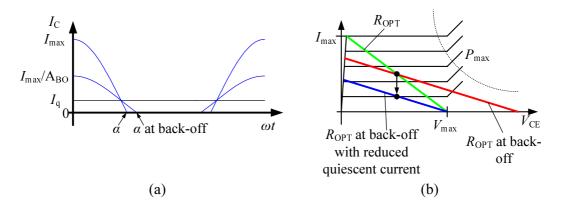

where  $I_{\rm DC}$  is the DC component and  $\hat{I}_{\rm C,n}$  the amplitude of the  $n^{\rm th}$  harmonic. The graphical representation in Fig. 2.3 (a) shows that the DC component is highest at class A bias and decreases monotonically with the conduction angle. The fundamental component increases slightly initially and then drops with the conduction angle. The fundamental at class B bias reaches the same value as for class A bias. Thus, class B is capable of delivering the same amount of output power with a substantially lower DC drain current, which results in improved efficiency. The other frequency components start to grow as the conduction angle decreases and converge to the same level. Whereas out of band harmonics can be filtered, in band distortion due to intermodulation will degrade linearity in terms of signal quality. Hence, special attention has to be paid to odd harmonics, which rise substantially in class C operation and have moderate or even zero value in class A, AB and B, compared to the fundamental. For that reason highest signal amplitude linearity can only be obtained in class A and B, moderate linearity in class AB and almost no linearity in class C operation. Efficiency and output power, achievable by this range of amplifiers is readily computed by:  $P_{\rm out}(\alpha) = V_{\rm DC} I_1(\alpha)$  and  $\eta(\alpha) = I_1(\alpha)/(2I_{\rm DC}(\alpha))$ , using (2.7) and (2.8). The results are illustrated in Fig. 2.3 (b). The efficiency of the amplifier can be increased up to theoretically 100 % by reducing the conduction angle. This is only obtained at the expense of output power, which diminishes rapidly in deep class C operation. In order to obtain higher output power values and achieve additional efficiency it is necessary to allow the voltage waveform to take on non-sinusoidal shapes. This is the basic idea behind the following operation classes. Amplitude modulation of the input signal is then no longer reflected in the output signals, making these classes nonlinear.

#### 2.3.2 Class F

The basic idea is to operate the amplifier in class B bias ( $\alpha = 180^{\circ}$ ) and to add odd harmonics to the voltage waveform so that it begins to increasingly resemble a square wave [Raab 77,a, Raab 02, Kee 03]. This requires a load network that has resonance at one or more harmonic frequencies as well as at the fundamental frequency. With a theoretical load network, which tunes an infinite number of harmonics, the collector voltage approaches a square wave out of phase with the drain current. Therefore efficiency can be increased to 100 %, which is usually associated with poor linearity.

Figure 2.3: Reduced conduction angle classes. (a) Fourier decomposition of current. (b) Output power and collector efficiency.

However the linearity can be improved to meet the design standards by tuning less harmonics and thus compromising on efficiency. It should be further noticed that the current amplitude at the fundamental is the same as in class B operation, but the fundamental voltage amplitude is  $\frac{4}{\pi}$  times higher<sup>1</sup>. Thus, output power will be also 1.05 dB higher. Main drawback of this amplifier class is the complexity of the waveform shaping network and its implementation at microwave frequencies.

#### 2.3.3 Class E

In this class the transistor is driven to act as a switch. The load network is designed to resonate with the collector-emitter capacitance of the transistor, to reduce voltage and current waveform overlap during switching transitions. This is achieved by discharging the capacitance at the collector node at the start of every cycle, consequently generating a voltage across the transistor of zero value and zero slope at the time of turn-on [Sokal 75, Raab 77,b]. Although in theory 100 % efficiency can be expected, this concept has serious disadvantages. The peak collector voltage can be more than 3 times higher than the supply voltage [Krauss 80], causing a potential threat to the amplifier's reliability. The current waveform includes odd harmonics, as indicated in Fig. 2.4, effecting insufficient linearity for most applications.

#### 2.3.4 Class D

This, at microwave frequencies hypothetical class of operation, assumes the device to behave as an ideal switch. While the voltage and current waveforms are similar to ideal class F operation, the output network is only tuned to the fundamental. The collector capacitance being present is not considered. This reduces switching speed

<sup>&</sup>lt;sup>1</sup>Fourier decomposition of the square wave voltage waveform gives:  $1 - \frac{4}{\pi} \sin(\omega_0 t) + \frac{4}{9\pi} \sin(3\omega_0 t) - \frac{4}{25\pi} \sin(5\omega_0 t) \dots$

and efficiency due to an increased voltage-current overlap. On top of that strong amplitude nonlinearity is caused by the hard driven transistor. These drawbacks limit a practical implementation to low frequency applications with phase modulated signals.

Figure 2.4: Amplifier classification: Voltage and current waveforms, simplified circuits and maximum achievable efficiency.

Among the classes of operation it has to be taken into account that a real transistor exhibits a finite saturation voltage (> 0) and intrinsic parasitics, which lead to reduction of efficiency, due to imperfect waveform shaping. Generally spoken the design of highly efficient PAs in reality demands the smallest possible power dissipation in the device. The exact waveforms will differ from the ideal presented, but a small I-V product at the transistor is always desired. Tuning to high efficiency operation can reduce performance significantly with regard to measures as output power or gain (as in class C) and linearity (as in class C, D, E, F). Hence, the level of improved efficiency always has to be weighted against other degradation mechanisms.

## Chapter 3

## Multi-Mode PA Concepts

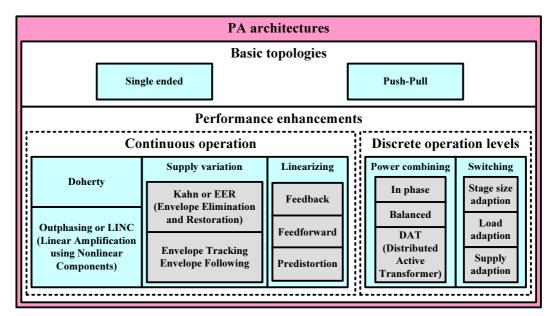

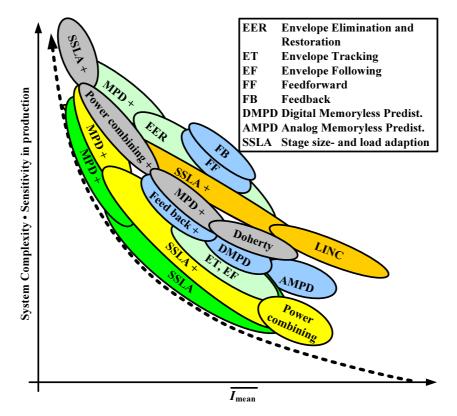

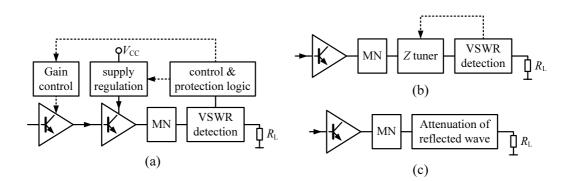

The demand for handset power amplifiers fulfilling more than one cellular standard rises due to expected saving of costs in mobile phone production. The increasing technical requirements for these multi-mode PAs by far exceed the performance limits of conventional amplifier classes, presented in the previous chapter. Besides of output power and bandwidth constraints the limits are primarily given by the fundamental tradeoff between linearity and efficiency. In a stand-alone amplifier only one of these two objectives can be increased at the expense of the other. A variety of enhancement techniques have been developed over the years to overcome this tradeoff. Each of them has use-oriented advantages and disadvantages but a general solution has not been found vet. In this chapter enhancement techniques are classified, shortly described and finally rated for their potential usage in multi-mode handset applications. Further improvements of PA performance can be achieved by using more than one of these techniques simultaneously. The resulting circuit complexity is contrasted with the benefits in this chapter as well. Another important characteristic of the PA is its response to load impedance changes at the antenna. This can have three consequences: reversible performance degradation, irreversible performance degradation due to aging and irreversible destruction of the transistor. Methods for reducing these effects will be discussed.

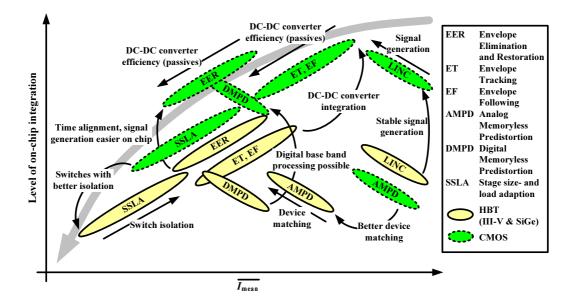

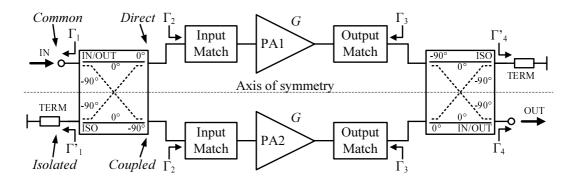

Finally the concept for the implemented multi-mode power amplifier is presented. It is based on novel combinations of some of the presented techniques. The stage sizeand load adaption and the power combining technique turn out to be most promising for optimizing the various parameters in the multi-mode designs. This way efficiency and load independence are improved without degrading linearity. The theoretical performance limits on the efficiency due to different power loss mechanisms caused by dissipation or bad isolation of parallel amplifier paths are derived and discussed for both concepts.

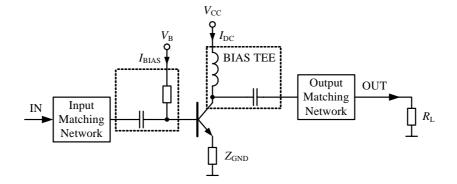

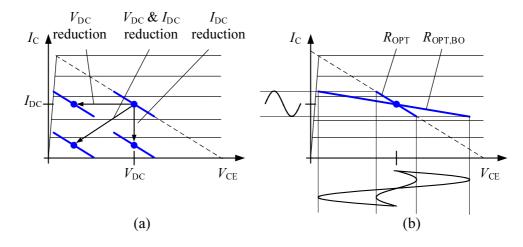

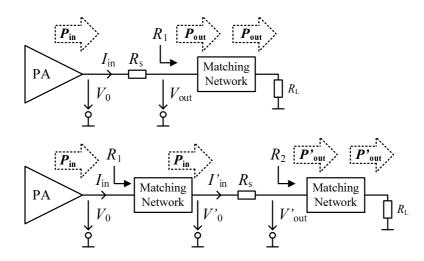

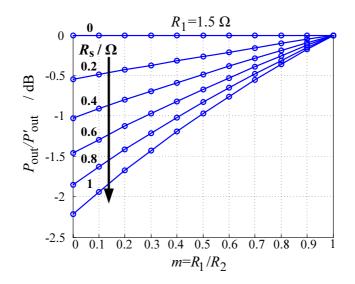

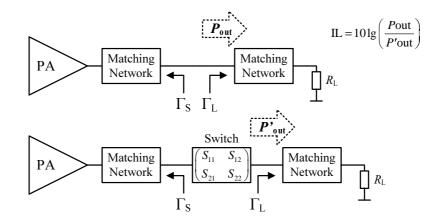

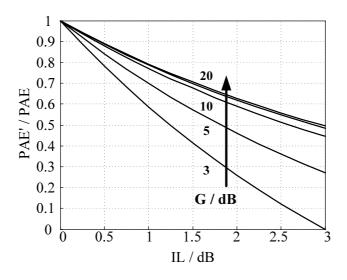

### **3.1** Power amplifier architectures