Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

#### FAKULTÄT FÜR !NFORMATIK

# Fault-Tolerant Hardware Implementation of a Consensus Algorithm

#### DIPLOMARBEIT

zur Erlangung des akademischen Grades

**Diplom-Ingenieur**

im Rahmen des Studiums

**Technische Informatik**

eingereicht von

Thomas Polzer, BSc. Matrikelnummer 0325077

|                                   | Technische Universität \                                |                         |  |

|-----------------------------------|---------------------------------------------------------|-------------------------|--|

| Wien, 24.09.2009                  | (Unterschrift Verfasser)                                | (Unterschrift Betreuer) |  |

|                                   | . DiplIng. Dr.techn. Andreas S<br>DiplIng. Thomas Handl | Steininger              |  |

| an der<br>Fakultät für Informatik | der Technischen Universität Wi                          | ien                     |  |

A-1040 Wien Kai

Karlsplatz 13

Tel. +43/(0)1/58801-0

http://www.tuwien.ac.at

#### Erklärung zur Verfassung der Arbeit

#### Thomas Polzer, Albrechtsgasse 88-94/10/6, 2500 Baden bei Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Baden, 24.09.2009

#### Acknowledgements

I would like to thank my advisors Prof. Andreas Steininger and Thomas Handl for their continuous help and advice. Additionally I want to thank Prof. Steininger for his excellent lectures in the field of Digital Design.

My thanks also go to Prof. Ulrich Schmid for his great lecture in Distributed Algorithms as well as for some very inspiring comments on my work.

Special thanks go to Mathias Függer for his guidance with the proofs.

I want to thank all my fellow students, especially Philipp Jahn, Robert Thullner and Alexandra Schuster, for the great time and companionship.

And of course none of it would have been possible if it was not for the continuous support from my parents and my two brothers.

This master's thesis was funded by the bm:vit FIT-IT project DARTS (proj. no. 809456-SCK/SAI).

# Fault-Tolerant Hardware Implementation of a Consensus Algorithm

#### **Abstract**

This thesis develops a new communication model for digital electronic systems. The proposed scheme is comparable to a GALS (globally asynchronous locally synchronous) system with the difference that the clock sources have a bounded, a-priory known precision. This loose synchrony is exploited to establish a communication that (i) is free of metastability by design and (ii) has a fully predictable temporal behavior. As a consequence the communication scheme presents a synchronous behavior, thus allowing to employ techniques that are restricted to synchronous systems, while avoiding the central clock being a single point of failure. To compensate for the imperfect synchronization of the local clocks (within the defined precision), a FIFO buffer memory is used on each communication link.

Using the theory of distributed systems the correctness of the approach is formally proved. For this purpose the communication activity is modeled as a distributed algorithm. More specifically it is shown that metastability-free and correct communication is possible, given that the buffer is larger than a certain, formally proved minimum. Furthermore an efficient hardware implementation is given and used to experimentally show that the theoretical derived FIFO buffer size requirement represents a tight lower bound. A performance comparison with a traditional GALS system shows that the performance of our solution is superior.

Based on the new communication model, a fault tolerant electronic system, able to tolerate Byzantine faults even in case of non replica deterministic modules, is developed. First the usability of a TMR system in such a setting is analyzed and, as found inadequate, replaced by a hardware implementation of the commonly known Byzantine EIG consensus algorithm.

As the EIG algorithm is lockstep synchronous, the lockstep synchronous model is simulated on top of our communication model. The EIG algorithm is adapted such that it can be efficiently implemented in hardware based on the timings established by the lockstep rounds. The equivalence of the adapted algorithm and the original EIG algorithm is shown. Additionally the hardware implementation for a system tolerating a single Byzantine fault is sketched. Performance and complexity of the implementation are analyzed.

# Fault-Tolerant Hardware Implementation of a Consensus Algorithm

#### **Kurzfassung**

Diese Master-Arbeit entwickelt ein neues Kommunikationsmodell für digitale elektronische Systeme. Das vorgeschlagene Schema ist vergleichbar mit einem GALS (globally asynchronous locally synchronous) System mit dem Unterschied, dass bei unserer Lösung die Taktquellen eine a-prior bekannte, beschrankte Präzision aufweisen. Diese schwache Synchronität wird ausgenutzt um ein Kommunikationssystem welches (i) konzeptuell frei von Metastabilität ist und (ii) ein vollkommen vorhersagbares zeitliches Verhalten hat zu entwickeln. Deshalb stellt das Kommunikationsschema ein synchrones Verhalten zur Verfügung, welches die Anwendung von Techniken gestattet, die auf synchrone Systeme beschränkt sind. Zusätzlich vermeidet dieses Schema den zentralen Clock als Single Point of Failure. Um die nicht perfekte Synchronisation zwischen den lokalen Clock Signalen (innerhalb der Präzision) zu kompensieren wird auf jeder Kommunikationsverbindung ein FIFO Buffer verwendet.

Mittels der Theorie der Verteilten Systeme wird die Korrektheit des Ansatzes formal bewiesen. Dazu werden die Kommunikationsvorgänge als verteilter Algorithmus modelliert. Genauer gesagt wird gezeigt, dass, unter der Voraussetzung dass die Buffergröße über einem gewissen, formal bewiesenen Mindestwert liegt, metastabilitäts- und fehlerfreie Kommunikation möglich ist. Weiters wird eine effiziente Hardware Implementierung vorgestellt und diese zur experimentellen Validierung der theoretischen FIFO Buffer Größe verwendet. Es zeigt sich, dass die bewiesene minimal benötigte Speichergröße eine größte untere Schranke darstellt. Ein Vergleich der Leistungsfähigkeit mit einem traditionellen GALS System zeigt, dass unsere Lösung einen höheren Datendurchsatz hat.

Basierend auf dem neuen Kommunikationsmodell wird ein fehlertolerantes elektronisches System entwickelt, welches auch dann in der Lage ist byzantinische Fehler zu tolerieren, wenn die Module nicht replikations-deterministisch sind. Dazu wird zuerst die Verwendbarkeit von TMR Systemen untersucht. Da diese jedoch als nicht einsetzbar eingestuft werden, muss stattdessen auf eine Hardware-Implementierung des bekannten byzantinischen EIG Consensus Algorithmus zurückgegriffen werden.

Da der EIG Algorithmus ein lockstep synchroner Algorithmus ist, wird basierend auf dem Kommunikationsmodel ein lockstep synchroneres Rundenmodell implementiert. Weiters wird der EIG Algorithmus so angepasst, dass er effizient in Hardware implementierbar ist. Die Äquivalenz des adaptierten Algorithmus mit dem

Original wird gezeigt. Weiters wird die Hardware-Implementierung eines Systems, welches einen byzantinischen Fehler tolerieren kann, beschrieben. Die Leistung und Komplexität der Implementierung werden ebenfalls analysiert.

# **Contents**

| 1 | Intr | oductio | n                                 | 1  |

|---|------|---------|-----------------------------------|----|

|   | 1.1  | Proble  | m Definition                      | 1  |

|   | 1.2  | Structi | ure of the Thesis                 | 2  |

| Ι | The  | eoretic | cal Background                    | 3  |

| 2 | Dist | ributed | Algorithm Basics                  | 5  |

|   | 2.1  | Messa   | ge Passing System                 | 5  |

|   |      | 2.1.1   | Message Passing Network           | 6  |

|   |      | 2.1.2   | Computational Node                | 6  |

|   |      | 2.1.3   | Actions and Events                | 8  |

|   |      | 2.1.4   | Messages                          | 8  |

|   |      | 2.1.5   | Visualization of Executions       | 9  |

|   | 2.2  | Globa   | Notion of Time                    | 10 |

|   |      | 2.2.1   | Properties of a Global Time Base  | 10 |

|   |      | 2.2.2   | Clock Synchronization             | 12 |

|   | 2.3  | Comp    | utational Models                  | 13 |

|   |      | 2.3.1   | Asynchronous Model                | 13 |

|   |      | 2.3.2   | The Lockstep Round Model          | 13 |

|   | 2.4  | Failure | e Handling in Distributed Systems | 14 |

|   |      | 2.4.1   | Failure Models                    | 14 |

|   |      | 2.4.2   | Agreement Problem                 | 16 |

|   |      |         |                                   |    |

*xii* CONTENTS

| 3 | Digi | tal Elec | etronic Circuit Basics                                | 19 |

|---|------|----------|-------------------------------------------------------|----|

|   | 3.1  | Clocki   | ing Schemata                                          | 19 |

|   |      | 3.1.1    | Synchronous Circuits                                  | 19 |

|   |      | 3.1.2    | Asynchronous Circuits                                 | 20 |

|   |      | 3.1.3    | Globally Asynchronous Locally Synchronous (GALS) Cir- |    |

|   |      |          | cuits                                                 | 21 |

|   |      | 3.1.4    | Multisynchronous Circuits                             | 22 |

|   | 3.2  | Interm   | nodule Communication in Electronic Circuits           | 22 |

|   |      | 3.2.1    | Synchronous Communication                             | 23 |

|   |      | 3.2.2    | Sourcesynchronous Communication                       | 24 |

|   |      | 3.2.3    | Asynchronous Communication                            | 25 |

|   | 3.3  | Metas    | tability                                              | 25 |

|   |      | 3.3.1    | Flip-Flop Timings                                     | 26 |

|   |      | 3.3.2    | Avoiding Metastability                                | 27 |

| 4 | Con  | ımunic   | ation Standards                                       | 29 |

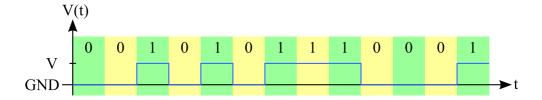

|   | 4.1  | Bit Re   | epresentation                                         | 29 |

|   |      | 4.1.1    | Single-Ended Signaling                                | 29 |

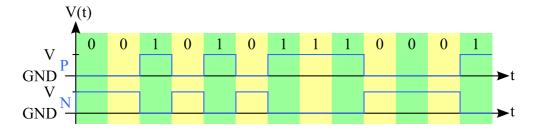

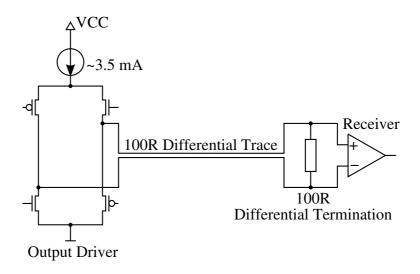

|   |      | 4.1.2    | Differential Signaling                                | 30 |

|   | 4.2  | Line C   | Coding                                                | 31 |

|   |      | 4.2.1    | Additional Clock Line                                 | 31 |

|   |      | 4.2.2    | Data-Strobe Encoding                                  | 32 |

|   |      | 4.2.3    | 8B/10B Encoding                                       | 32 |

|   |      | 4.2.4    | Asynchronous Parallel Communication                   | 33 |

|   |      | 4.2.5    | Asynchronous Serial Communication                     | 33 |

|   | 4.3  | Synch    | ronous Communication Protocols                        | 34 |

|   |      | 4.3.1    | Basic Synchronous Transmission                        | 34 |

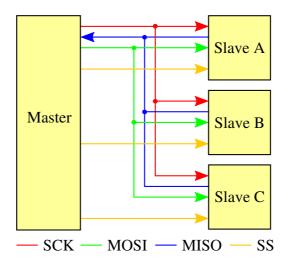

|   |      | 4.3.2    | SPI                                                   | 34 |

|   |      | 4.3.3    | I <sup>2</sup> C                                      | 35 |

|   |      | 4.3.4    | PCI                                                   | 35 |

|   | 4.4  | Source   | esynchronous Communication Protocols                  | 35 |

|   |      | 4.4.1    | Space-Wire                                            | 35 |

| CONTENTS | xiii |

|----------|------|

|          |      |

|    |      | 4.4.2    | PCI-Express                       | 36 |

|----|------|----------|-----------------------------------|----|

|    |      | 4.4.3    | Infiniband                        | 36 |

|    | 4.5  | Async    | hronous Communication Protocols   | 36 |

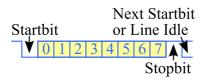

|    |      | 4.5.1    | Serial Port                       | 36 |

|    |      | 4.5.2    | Parallel Port                     | 37 |

|    | 4.6  | Transn   | mission Protocol Comparison       | 37 |

| 5  | Hare | dware I  | Fault Models and Fault Tolerance  | 39 |

|    | 5.1  | Hardw    | vare Fault Models                 | 40 |

|    |      | 5.1.1    | Stuck-At Faults                   | 40 |

|    |      | 5.1.2    | Stuck-Open Faults                 | 40 |

|    |      | 5.1.3    | Bridging Faults                   | 41 |

|    | 5.2  | Fault 7  | Tolerance                         | 41 |

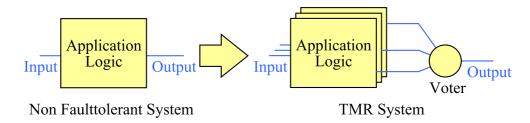

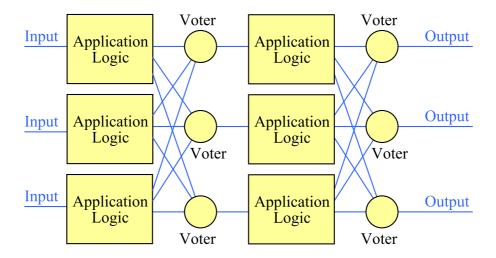

|    |      | 5.2.1    | Triple Modular Redundancy         | 41 |

|    |      |          |                                   |    |

| II | Fr   | amew     | ork Implementation                | 43 |

| 6  | Prob | olem De  | efinition                         | 45 |

| 7  | Circ | uit Mo   | deling                            | 47 |

|    | 7.1  | Creatin  | ng the Model                      | 47 |

|    | 7.2  | Model    | Properties                        | 49 |

|    | 7.3  | Model    | ing Freeness of Metastability     | 49 |

| 8  | Meta | astabili | ty-Free Intermodule Communication | 51 |

|    | 8.1  | Quasi-   | Synchronous Communication Scheme  | 51 |

|    | 8.2  | Pipelin  | ned Communication Scheme          | 53 |

|    |      | 8.2.1    | Algorithmic Model                 | 54 |

|    |      | 8.2.2    | Problem Definition                | 57 |

|    |      | 8.2.3    | Relation Between Actions          | 57 |

|    |      | 8.2.4    | Read–Write Order Proof            | 58 |

|    |      | 8.2.5    | Bounded Buffer Size               | 60 |

|    |      | 8.2.6    | Latency                           | 62 |

|    |      |          | • ·                               |    |

*xiv* CONTENTS

| 9  | Pipe | lined So | cheme Implementation                  | 65         |

|----|------|----------|---------------------------------------|------------|

|    | 9.1  | Circuit  | Design                                | 65         |

|    |      | 9.1.1    | Communication                         | 65         |

|    |      | 9.1.2    | Transmitter                           | 66         |

|    |      | 9.1.3    | Receiver                              | 67         |

|    |      | 9.1.4    | Communication Buffer                  | 67         |

|    | 9.2  | Implen   | nentation Mapping                     | 68         |

|    |      | 9.2.1    | Implementation without Input Register | 68         |

|    |      | 9.2.2    | Implementation with Input Register    | 69         |

|    | 9.3  | Perform  | mance and Efficiency                  | 70         |

|    |      | 9.3.1    | Throughput                            | 70         |

|    |      | 9.3.2    | System Latency                        | 71         |

|    |      | 9.3.3    | Performance Comparison                | 71         |

|    | 9.4  | Comm     | unication Example                     | 72         |

|    | 9.5  | Experi   | ments                                 | 73         |

|    |      | 9.5.1    | Test System                           | 73         |

|    |      | 9.5.2    | Clock Emulation                       | 73         |

|    |      | 9.5.3    | Test Conditions                       | 75         |

|    |      | 9.5.4    | Performed Tests                       | 75         |

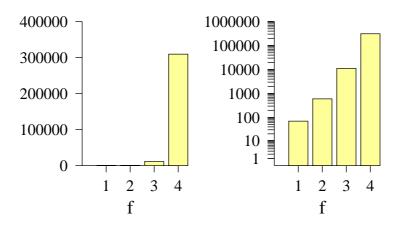

|    |      | 9.5.5    | Results                               | 76         |

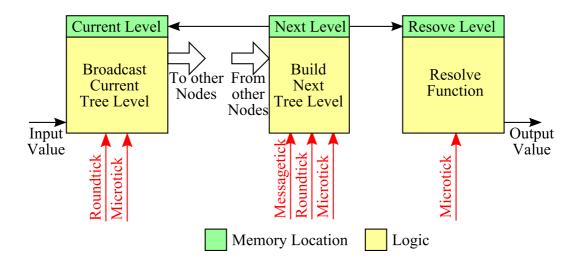

| 10 | Impl | lementi  | ng a Lockstep Model                   | <b>7</b> 9 |

|    | 10.1 | Algorit  | thmic Model                           | 79         |

|    | 10.2 | Correc   | tness Proof                           | 81         |

|    | 10.3 | Time C   | Complexity                            | 83         |

|    | 10.4 | Mappi    | ng the Message Layer Implementation   | 83         |

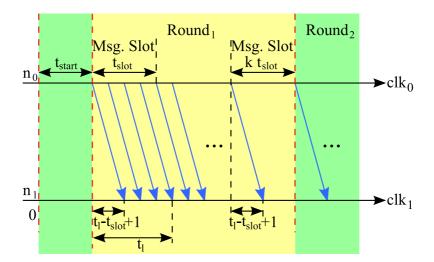

|    | 10.5 | Static I | Round Pattern Algorithm               | 84         |

|    | 10.6 | Messag   | ge Receive Event                      | 85         |

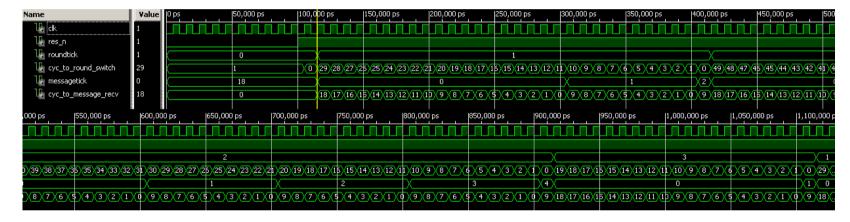

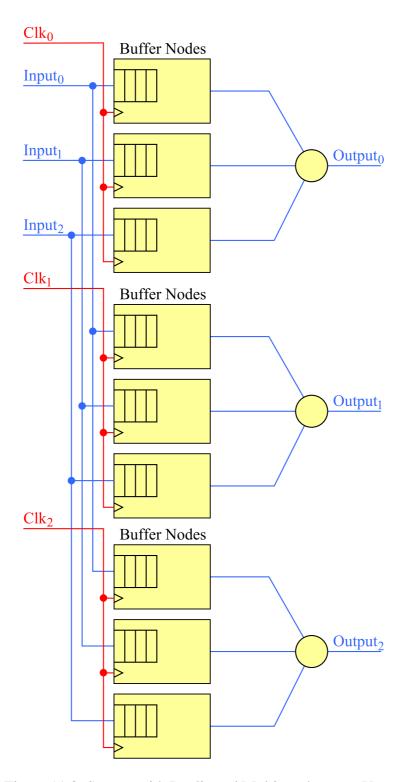

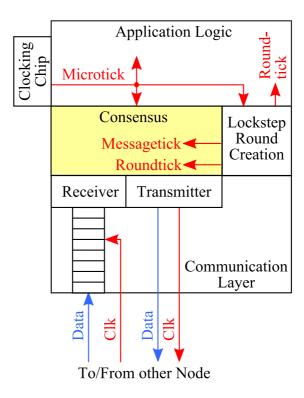

|    | 10.7 | Hardw    | are Implementation                    | 86         |

CONTENTS

| III | <b>C</b> | onsensus                                             | 89  |

|-----|----------|------------------------------------------------------|-----|

| 11  | Prob     | olem Definition                                      | 91  |

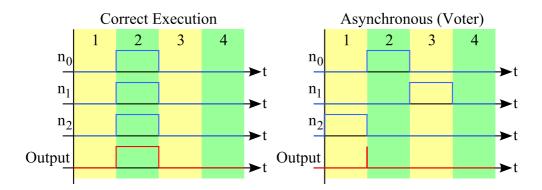

|     | 11.1     | Problems of TMR Systems                              | 91  |

|     | 11.2     | May Hardware Act Non-Benign?                         | 95  |

|     | 11.3     | TMR Systems in Byzantine Environments                | 96  |

|     | 11.4     | Alternatives to TMR Systems                          | 97  |

| 12  | Crea     | ating a Byzantine Fault Tolerant System              | 99  |

|     | 12.1     | The EIG Algorithm                                    | 99  |

|     | 12.2     | Algorithmic Model                                    | 101 |

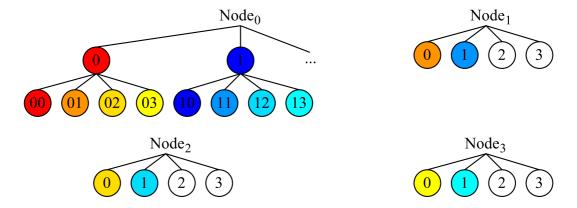

|     | 12.3     | Building the Resolve Tree                            | 103 |

|     | 12.4     | Resolve Function                                     | 106 |

|     |          | 12.4.1 Resolve Function for a Single Byzantine Fault | 106 |

|     | 12.5     | Complexity of the Adapted Algorithm                  | 107 |

|     | 12.6     | Circuit Design                                       | 109 |

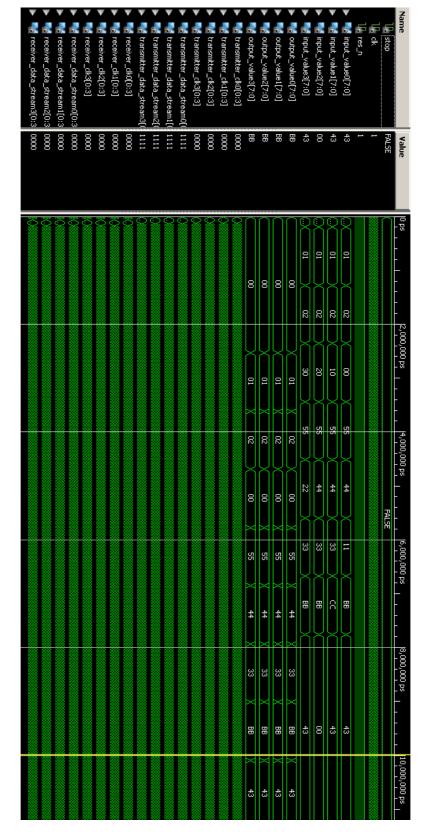

|     | 12.7     | Execution Example                                    | 111 |

| IV  | C        | onclusion and Future Work                            | 115 |

| 13  | Futu     | re Work                                              | 117 |

|     | 13.1     | Flow Control and Error Detection                     | 117 |

|     | 13.2     | Resynchronization at Runtime                         | 117 |

|     | 13.3     | Ring Buffer Integration into the Clocking Chip       | 118 |

|     | 13.4     | Resolve Functions for Stronger Fault Hypotheses      | 119 |

| 14  | Cone     | clusion                                              | 121 |

# **List of Figures**

| 2.1 | Example Message Passing System              | 6  |

|-----|---------------------------------------------|----|

| 2.2 | Example Node with Three Neighbors           | 7  |

| 2.3 | Message Delivery                            | 8  |

| 2.4 | Space-Time Diagram Example                  | 10 |

| 2.5 | Example of Drifting Clocks                  | 11 |

| 2.6 | Precision                                   | 12 |

| 2.7 | Lockstep Synchronous System                 | 14 |

| 2.8 | Failure Model Example                       | 15 |

| 2.9 | EIG Tree for a $f=1$ System                 | 18 |

| 3.1 | Synchronous Model                           | 20 |

| 3.2 | Asynchronous Model                          | 21 |

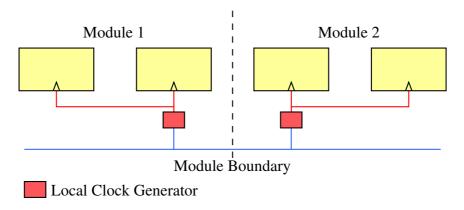

| 3.3 | GALS Model                                  | 21 |

| 3.4 | Multisynchronous Model                      | 22 |

| 3.5 | Synchronous Communication                   | 24 |

| 3.6 | Source Synchronous Communication            | 24 |

| 3.7 | Asynchronous Communication                  | 25 |

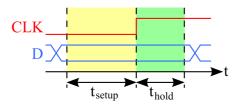

| 3.8 | D-Flip-Flop Timing Constraints              | 26 |

| 3.9 | Metastable D-Flip-Flop                      | 27 |

| 4.1 | Unipolar Single-Ended Signaling (idealized) | 30 |

| 4.2 | Differential Signaling (idealized)          | 30 |

| 4.3 | LVDS Transmitter and Receiver               | 31 |

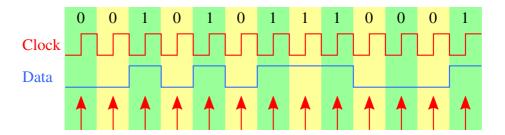

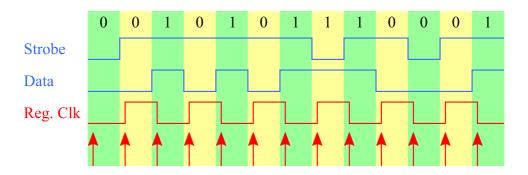

| 4.4 | Linecoding using an Additional Clock Line   | 31 |

| 4.5 | Data-Strobe Encoding                        | 32 |

|     |                                             |    |

xviii LIST OF FIGURES

| 4.6                                                                                   | Asynchronous Serial Communication                                                                                                                                                                                                                                                                                                                                                                                                              | 33                                                       |

|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 4.7                                                                                   | SPI Link                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34                                                       |

| 4.8                                                                                   | I <sup>2</sup> C Bus                                                                                                                                                                                                                                                                                                                                                                                                                           | 35                                                       |

| 4.9                                                                                   | Full Duplex Space Wire Link                                                                                                                                                                                                                                                                                                                                                                                                                    | 36                                                       |

| 5.1                                                                                   | Stuck At Zero Fault                                                                                                                                                                                                                                                                                                                                                                                                                            | 40                                                       |

| 5.2                                                                                   | Stuck-Open Fault                                                                                                                                                                                                                                                                                                                                                                                                                               | 41                                                       |

| 5.3                                                                                   | OR Bridging Fault                                                                                                                                                                                                                                                                                                                                                                                                                              | 41                                                       |

| 5.4                                                                                   | Basic TMR System                                                                                                                                                                                                                                                                                                                                                                                                                               | 42                                                       |

| 5.5                                                                                   | TMR System using Replicated Voters                                                                                                                                                                                                                                                                                                                                                                                                             | 42                                                       |

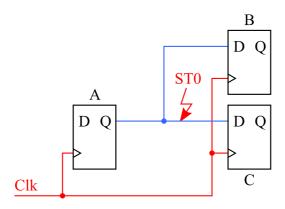

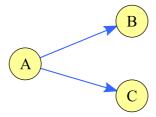

| 7.1                                                                                   | Modeling Example                                                                                                                                                                                                                                                                                                                                                                                                                               | 48                                                       |

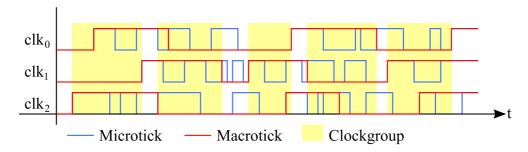

| 8.1                                                                                   | Macrotick Generation                                                                                                                                                                                                                                                                                                                                                                                                                           | 52                                                       |

| 8.2                                                                                   | Macrotick Based Clock Generation                                                                                                                                                                                                                                                                                                                                                                                                               | 52                                                       |

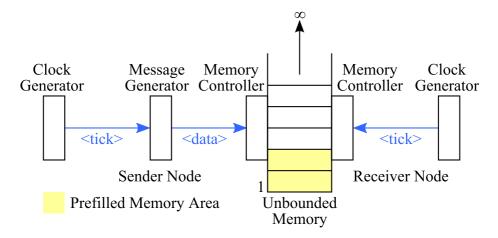

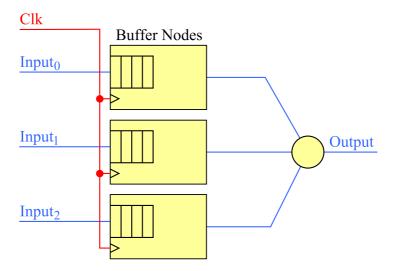

| 8.3                                                                                   | System Model used for the Proof                                                                                                                                                                                                                                                                                                                                                                                                                | 55                                                       |

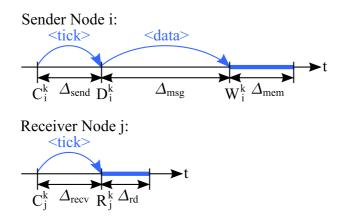

| 8.4                                                                                   | Execution of Tick $k$                                                                                                                                                                                                                                                                                                                                                                                                                          | 57                                                       |

|                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

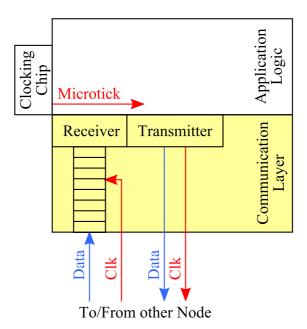

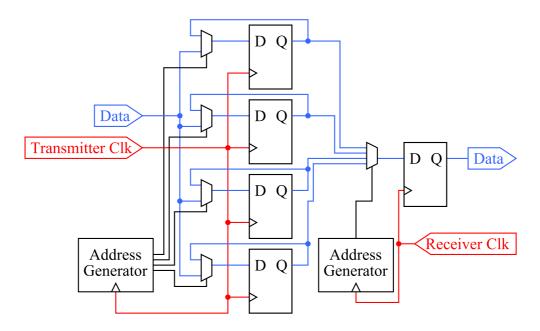

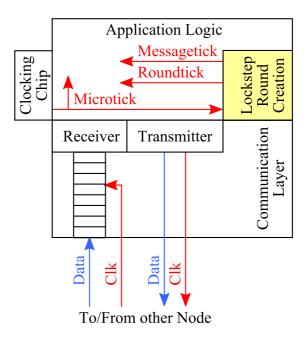

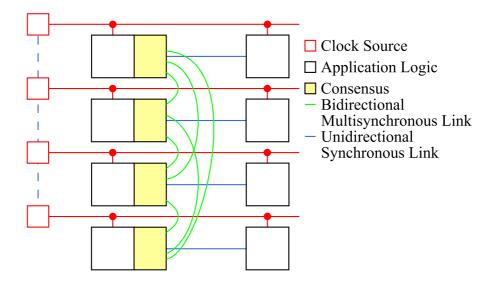

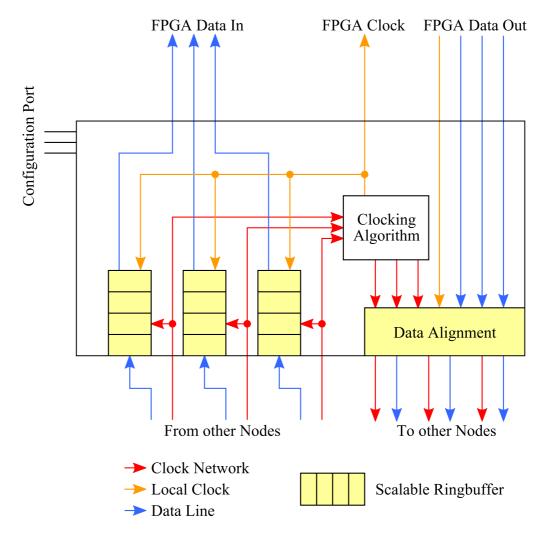

| 9.1                                                                                   | Layout of a Node                                                                                                                                                                                                                                                                                                                                                                                                                               | 66                                                       |

| 9.1<br>9.2                                                                            | Layout of a Node                                                                                                                                                                                                                                                                                                                                                                                                                               | 66<br>68                                                 |

|                                                                                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                          |

| 9.2                                                                                   | Ring Buffer of Depth 4                                                                                                                                                                                                                                                                                                                                                                                                                         | 68                                                       |

| 9.2<br>9.3                                                                            | Ring Buffer of Depth 4                                                                                                                                                                                                                                                                                                                                                                                                                         | 68<br>69                                                 |

| <ul><li>9.2</li><li>9.3</li><li>9.4</li></ul>                                         | Ring Buffer of Depth 4                                                                                                                                                                                                                                                                                                                                                                                                                         | 68<br>69<br>70                                           |

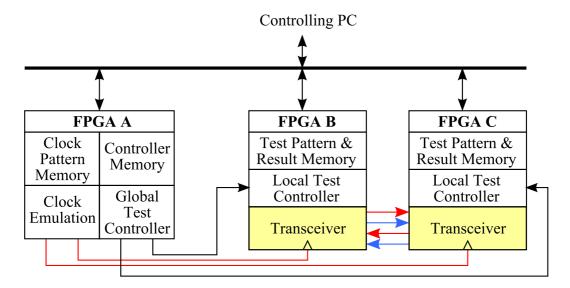

| <ul><li>9.2</li><li>9.3</li><li>9.4</li><li>9.5</li></ul>                             | Ring Buffer of Depth 4                                                                                                                                                                                                                                                                                                                                                                                                                         | 68<br>69<br>70<br>73                                     |

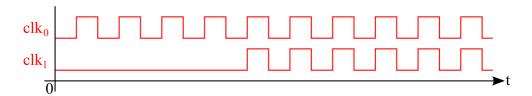

| <ul><li>9.2</li><li>9.3</li><li>9.4</li><li>9.5</li><li>9.6</li></ul>                 | Ring Buffer of Depth 4                                                                                                                                                                                                                                                                                                                                                                                                                         | 68<br>69<br>70<br>73<br>74                               |

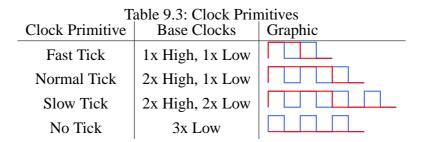

| 9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8                                         | Ring Buffer of Depth 4                                                                                                                                                                                                                                                                                                                                                                                                                         | 68<br>69<br>70<br>73<br>74<br>74                         |

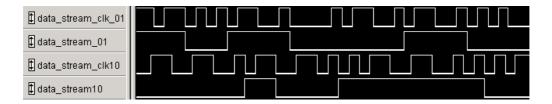

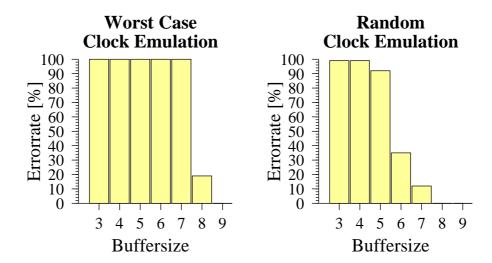

| 9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8                                         | Ring Buffer of Depth 4                                                                                                                                                                                                                                                                                                                                                                                                                         | 68<br>69<br>70<br>73<br>74<br>74<br>77                   |

| 9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>10.1                                 | Ring Buffer of Depth 4                                                                                                                                                                                                                                                                                                                                                                                                                         | 68<br>69<br>70<br>73<br>74<br>74<br>77                   |

| 9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>10.1<br>10.2<br>10.3                 | Ring Buffer of Depth 4                                                                                                                                                                                                                                                                                                                                                                                                                         | 68<br>69<br>70<br>73<br>74<br>74<br>77<br>80<br>82       |

| 9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>10.1<br>10.2<br>10.3                 | Ring Buffer of Depth 4                                                                                                                                                                                                                                                                                                                                                                                                                         | 68<br>69<br>70<br>73<br>74<br>74<br>77<br>80<br>82<br>87 |

| 9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>10.1<br>10.2<br>10.3<br>11.1<br>11.2 | Ring Buffer of Depth 4  Schematic Transmitter Circuit (No Input Register)  Schematic Transmitter Circuit (With Input Register)  Example Communication within the Test System  Layout of the Test System  Worst Case Precision Emulation  Results of the Experiments  Lockstep Round Generation Implementation Hierarchy  Visualization of the Assumptions  Simulation of the Lockstep Algorithm Implementation  Unsynchronized Voter Execution | 68<br>69<br>70<br>73<br>74<br>74<br>77<br>80<br>82<br>87 |

LIST OF FIGURES xix

| 11.5 | Distributed System Model of the Circuit          | 95  |

|------|--------------------------------------------------|-----|

| 12.1 | System Model Tolerating one Byzantine Fault      | 100 |

| 12.2 | Fully Created Resolve Tree for $f=1$             | 101 |

| 12.3 | Structure of the Hardware Implementation         | 102 |

| 12.4 | Building of a Resolve Tree Level                 | 105 |

| 12.5 | Resolve Function for $f=1$                       | 106 |

| 12.6 | Runtime of the Consensus Algorithm [Microticks]  | 109 |

| 12.7 | Node Implementation                              | 110 |

| 12.8 | Execution Example of a Consensus System          | 112 |

| 12.9 | Execution Example of a Consensus System (Detail) | 113 |

| 13.1 | Clocking Chip – Ring-Buffer Integration          | 119 |

# **List of Tables**

| 4.1  | Transmission Protocol Comparison        | 38 |

|------|-----------------------------------------|----|

| 9.1  | Latency                                 | 71 |

| 9.2  | Performance Comparison                  | 72 |

| 9.3  | Clock Primitives                        | 75 |

| 9.4  | Results of the Experiments              | 76 |

| 11.1 | Voter Execution                         | 92 |

| 12.1 | Runtime of the Consensus Implementation | 08 |

## Chapter 1

#### Introduction

#### 1.1 Problem Definition

Currently digital electronic systems are mainly implemented based on the synchronous paradigm. Due to ever increasing clock rates, smaller feature sizes and increasing gate counts the assumptions made by this model are harder and harder to meet. As only a single maximum clock rate is calculated for the whole system, long signal connections, even if only a few are present, decrease the system performance dramatically.

To circumvent these problems globally asynchronous locally synchronous (GALS) systems [Cha84] are used nowadays. Here the system is divided into several modules. Each module is driven by a single, independent clock source. The modules are developed independently and the intermodule signals are therefore not part of any timing analysis as they cross from one clock domain to another. Therefore the setuphold window is not guaranteed to be maintained and the intermodule links may be subjected to metastability and therefore compromise the stability of the system.

The goal of this thesis is to develop a new system model which is (i) free of any potential for metastability and (ii) providing the possibility to implement independent modules. An efficient implementation for this problem is described, its correctness proved and a tight lower bound on the required buffer size is given.

This model is used as basis to implement a fault tolerant system with the ability to tolerate Byzantine faults, even if the implementation of the modules is not replica deterministic. The usability of a TMR system in such a setting is analyzed and, as found inadequate, replaced by a system using a hardware implementation of the widely known EIG consensus algorithm. The equivalence of the hardware implementation and the original EIG algorithm is shown.

#### 1.2 Structure of the Thesis

The thesis is structured into four parts. The first part recapitulates the theory needed to understand the remainder of the thesis. It comprises Chapters 2-5. Chapter 2 gives an overview on the distributed systems theory including message passing systems, clock synchronization and system models. It is followed by a brief introduction into failure modeling and -handling in distributed systems. Chapter 3 introduces different clocking models as well as intermodule communication techniques and describes the problem of metastability. Chapter 4 outlines state of the art communication schemes based on the standards established in Chapter 3. Hardware fault models and fault tolerance mechanism (TMR systems) are discussed in Chapter 5.

Part II is devoted to the implementation of the basic framework including the metastability free communication layer and the simulation of the lockstep synchronous model based on the local microtick clock. Chapter 6 motivates the necessity of a new system model. Our approach for mapping circuits as distributed systems is shown in Chapter 7. Two different approaches for metastability free communication are presented in Chapter 8. Additionally the model with the higher performance is formally proved correct. Its hardware implementation and experimental results are presented in Chapter 9. Part 2 is concluded by defining a method to create lockstep synchronous rounds based on the local clock only (Chapter 10).

The implementation of a Byzantine fault tolerant system forms the focus of Part III. Chapter 11 motivates why such a system is important. It is shown that a naive TMR implementation would surely fail and that a more sophisticated implementation will also fail, if the system is not replica deterministic. The design of a hardware implementable adaptation of the exponential information gathering (EIG) algorithm [AW04] is described in Chapter 12. The equivalence of both algorithms is also shown and its hardware implementation is sketched.

Part IV concludes the thesis. Chapter 13 discusses open questions and future extensions, while Chapter 14 concludes the thesis by summarizing its most important findings.

# Part I Theoretical Background

## Chapter 2

## **Distributed Algorithm Basics**

To be able to prove the correctness of our solutions, we will model them using the theory of distributed systems. Therefore this chapter gives a brief overview on the distributed systems theory. In this chapter, except for Section 2.4, we assume that the system is reliable.

For more in depth information on the subject the very good book "Distributed Computing – Fundamentals, Simulations and Advanced Topics" [AW04] is recommended to the interested reader. Where not referenced otherwise, the information presented within this chapter is based on this book.

#### 2.1 Message Passing System

As already mentioned before, the basis for the formal part of our work is the distributed systems theory, more specifically Message Passing Systems. Such systems consist of the following elements:

- Multiple computational nodes (shortly called nodes) <sup>1</sup>

- Communication links between the nodes (message passing network)

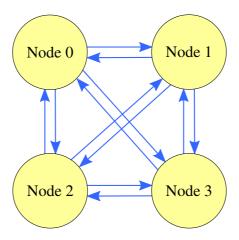

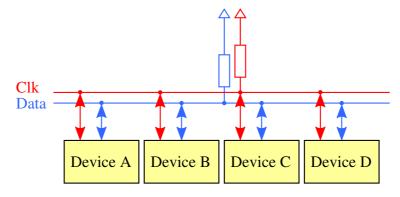

Directed graphs (see [Die05] for details on graph theory) are used to visualize message passing systems. Each computational node is represented by a node within the graph. The links within the message passing network are represented by directed edges. An example for a message passing system consisting of four nodes and using a fully connected message passing network is displayed in Figure 2.1.

<sup>&</sup>lt;sup>1</sup>In difference to [AW04] the computational elements are called nodes and not processors. This differentiation is made because their functionality is not necessarily implemented by a processor.

Figure 2.1: Example Message Passing System

#### 2.1.1 Message Passing Network

The data transmission between any two nodes is modeled as the exchange of messages between these nodes. Each node can send a message to an adjacent node using the message passing network. Theoretically the topology of such a network can be arbitrary. Nevertheless for simplicity reasons it is assumed that the network is fully connected, which means there is a communication channel between any two nodes (see Figure 2.1 as an example).

#### 2.1.2 Computational Node

A computational node is the basic element of a message passing system. A single node is referred to as  $n_i$ , where i is an artificial index identifying the nodes in the system. We introduce the set  $P = \bigcup_i \{n_i\}$ , called the set of nodes, containing all computational nodes of the system.

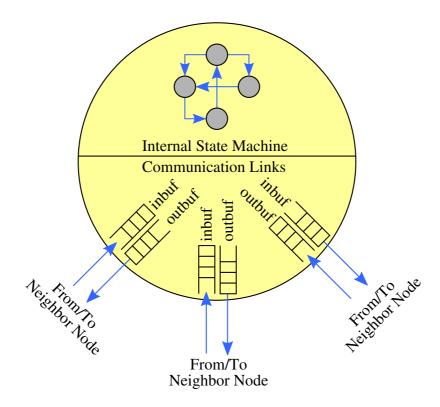

The computational nodes perform all calculations within the system. Figure 2.2 shows an example of a node with three neighbors. The node is modeled using the following three components:

- A state transition table modeling the internal logic of the considered node.

- An input buffer component (shortly called inbuf<sub>j</sub>) for each adjacent node j.

- An output buffer component (shortly called  $\operatorname{outbuf}_j$ ) for each adjacent node j.

Figure 2.2: Example Node with Three Neighbors

The calculations performed by the nodes are modeled as state transitions. For every such state transition the node's state transition table contains an entry. The input to such a state transition is the current state of the node and all messages currently present in the input buffers. Based on this information the successor state is selected from the state transition table. Furthermore a subset (or all) messages can be removed from the input buffer, as well as new messages added to the output buffers of the node (sending messages to adjacent nodes).

The input buffers contain all delivered but not yet processed messages received from adjacent nodes. Messages are added to the input buffer when they are delivered to the node. A message is removed from the input buffer when having contributed to a state transition.

The output buffers contain all messages sent by the node to an adjacent node. Messages are added to the output buffer, when they are generated by a state transition. All messages present in the output buffer are not yet delivered. Nevertheless the node itself can not read from the output buffers. Therefore messages within the output buffers can never affect the selection of a state transition from the state transition table.

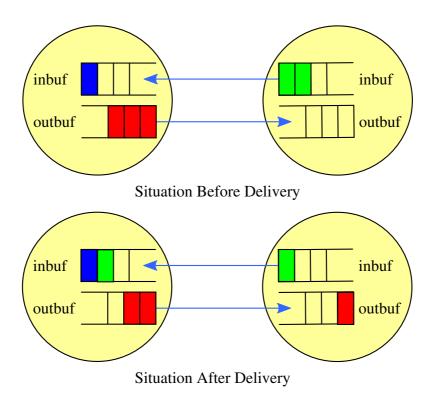

The messages are delivered using the message passing system. This is done by selecting a message from an output buffer of the sender node and placing it into the

Figure 2.3: Message Delivery

input buffer of the receiver node. Figure 2.3 shows an example for the delivery of two messages (one in each direction) between two adjacent nodes.

#### 2.1.3 Actions and Events

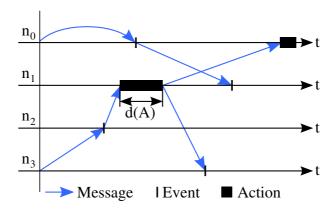

All activities occurring in the system (like state transitions, message delivery,  $\cdots$ ) are modeled as actions.  $A_i^k$  specifies the  $k^{\text{th}}$  action of processor i. The superscript and subscript are omitted, if a general action (A) not bound to any processor is described. Each action (A) has an associated start- and end time (shortly  $t_s(A)$  and  $t_e(A)$ ) and therefore a duration  $(d(A) = t_e(A) - t_s(A) \ge 0)$ . If the duration of an action is zero (d(A) = 0), we call it an event (E). Since its duration is zero, the start- and end time are the same and we only speak of its time of occurrence (t(A)).

#### 2.1.4 Messages

We shortly call a message with contents M  $\langle M \rangle$ . Each message has a specific length called l(M) given in bits. Furthermore a message  $\langle M \rangle$  has the following temporal properties.

#### **End-to-End Delay**

We have already discussed the concepts of sending, delivering and reading (consuming) messages. We will now formalize the message delivery process. Using the terminology of actions and events, we can model the sending, delivery and reading of messages as events. Therefore we can associate a send-, delivery- and read-time with each message  $\langle M \rangle$  calling them shortly  $t_{\rm send}(M)$ ,  $t_{\rm delivery}(M)$  and  $t_{\rm read}(M)$ , respectively.

The whole process of transmitting a message can be seen as an action  $(M_{\rm T})$  starting with the send event and ending with the read event. Therefore its duration is  $d(M_{\rm T}) = t_{\rm e}(M_{\rm T}) - t_{\rm s}(M_{\rm T}) = t_{\rm read}({\rm M}) - t_{\rm send}({\rm M})$  and it is called the message Endto-End delay  $\Delta$ . If available, the upper and lower bound of the end-to-end delay in the system are called  $\Delta^+$  and  $\Delta^-$ , respectively.

#### **Read-Write-Order Problem**

It is important to note, that a message must be delivered before it can be read  $(t_{\rm delivery} < t_{\rm read})$ . Each implementation of a computational model must ensure that this order is met, otherwise the system behavior could become undefined.

#### **FIFO Order**

Without further assumptions messages sent on the same communication link may be delivered in arbitrary order. Nevertheless, it is often convenient to assume FIFO (first in first out) order on the communication links. FIFO order states that messages sent on the same communication link are delivered in the order they were sent. Formally the FIFO property can be written as:  $\forall$  two messages  $M_1$ ,  $M_2$  on the same communication link:

$$t_{\text{send}}(M_1) < t_{\text{send}}(M_2) \Leftrightarrow t_{\text{delivery}}(M_1) < t_{\text{delivery}}(M_2)$$

#### 2.1.5 Visualization of Executions

Execution are visualized using the so called space-time diagram. Each node is represented by a horizontal line within the diagram and the time advances from left to right. For each node the events and actions are shown in the diagram using boxes or short vertical lines. Furthermore all messages are visualized by arrows between the action or events of the nodes. An (annotated) example execution can be found in Figure 2.4.

Figure 2.4: Space-Time Diagram Example

#### 2.2 Global Notion of Time

So far we have discussed message passing systems with all their subcomponents. An important property of such a system is a global notion of time. A consistent view of time is a powerful property when modeling algorithms for distributed systems.

Time in distributed systems is measured in clock ticks. Each clock tick can be seen as an event C in the system having an assigned real time t(C). The  $k^{\rm th}$  clock tick on node i is referenced as  $C_i^k$ .

#### 2.2.1 Properties of a Global Time Base

We will now discuss three major properties of a time base, namely the clock drift, the accuracy and the precision  $(\pi)$ .

#### **Clock Drift**

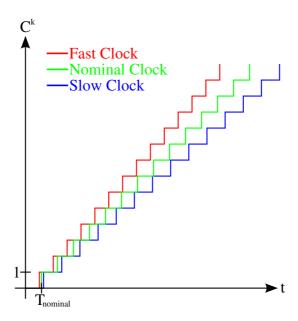

As described in [Kop97], it is possible to deduce from the clock drift, whether a clock is running with its nominal frequency or it runs too fast or slow. As a reference, a fictional optimum clock with the nominal frequency is used. Figure 2.5 illustrates both cases.

The rate a clock runs slower or faster than this nominal clock is called the drift rate and defines how many real clock ticks occur within one clock tick of the fictional nominal clock. The example clocks have a drift rate of 1.14 and 0.89.

Each node in the system can have a clock with a different drift rate. Furthermore the drift rates of the clocks can vary over time.

Figure 2.5: Example of Drifting Clocks

#### **Accuracy**

We use a more restrictive definition of accuracy than the one defined by [Sch87]. We specify the lower- and upper bound of the period length of all clocks in the system over time and therefore bound the rate the clocks may change with. Formally it can be written as:

$$\forall i \in P, k > 0 : \exists \mathbf{T}^- = \min_{i,k} (C_i^{k+1} - C_i^k) > 0$$

(2.1)

$$\forall i \in P, k > 0 : \exists \mathbf{T}^+ = \max_{i,k} (C_i^{k+1} - C_i^k) \ge \mathbf{T}^-$$

(2.2)

As apparent from Equations (2.1) and (2.2), unlike the drift rate, the accuracy is a property of the whole system.

#### **Precision**

Before discussing the last parameter of our global clock system, we need to define the precedence relation  $(\rightarrow)$ . Introduced by Lamport in [Lam03],  $A \rightarrow B$  informally means that action A must have been finished before action B starts.

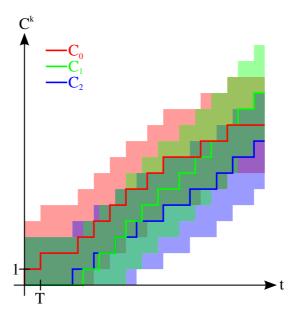

We now can use the precedence relation to describe the last important parameter, namely the precision  $(\pi)$ . It is defined as the maximum value any two clocks of the system can differ at any point in time [Kop97]. Formally the precision can be stated as:

$$\exists \pi : \forall i, j \in P, \forall k \ge 0 : C_i^k \to C_j^{k+\pi}$$

(2.3)

Figure 2.6: Example of a System with Three Clocks having a Precision of Three

To visualize this property Figure 2.6 shows an example clock system with three clocks. For each of the clocks the corresponding precision envelop is shown as a shaded area around the clock. For the system to hold its precision, all clocks must stay in the overlapping area of all three precision envelopes.

#### 2.2.2 Clock Synchronization

Since all clocks of the system can have different, even non constant, drift rates, the precision  $\pi$  of any two clocks in the system changes over time and may, in particular, become arbitrary large. To keep the precision within predefined bounds, a clock synchronization algorithm must be applied, otherwise no global notion of time can be achieved.

There are many commonly known clock synchronization algorithms already available (see e.g. [AW04, ST03, LMS85] and specifically for VLSI implementations [WS05]).

We will assume the presence of a global clock system with a given precision and accuracy already available in our system. Therefore we will not discuss the concepts of clock synchronization algorithms in detail here.

#### 2.3 Computational Models

There are two commonly known computational models that differ with respect to the assumption of a global notion of time.

- The asynchronous model

- The lockstep synchronous model

These models can be considered extreme variants, and there are plenty of other models in between. However, since most algorithms are targeted to one of these two models, we will concentrate on these two.

#### 2.3.1 Asynchronous Model

As the name already suggests, no global notion of time is available in this model. Furthermore there are no local clocks available in the system. The algorithms describable by this model are completely time free and only driven by message delivery events (the message delivery event will trigger the message read event). Therefore there are no write-read order problems within this system.

Since no timing assumptions are made, no timing bounds can be violated. As convenient as this is, the absence of such bounds restricts the implementable algorithms dramatically (see e.g. [AW04] for some impossibility proofs).

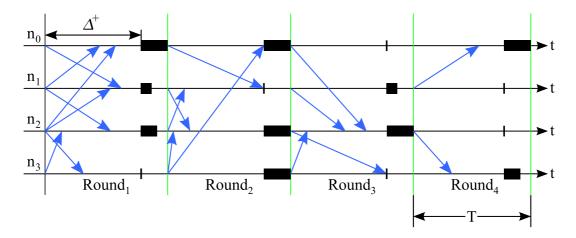

#### 2.3.2 The Lockstep Round Model

This model has a very accurate global notion of time ( $\pi=0$ ) and therefore is a very powerful tool to implement distributed algorithms. The algorithms themselves are easy to describe. The execution of the algorithm is split into successive rounds. Each round starts with a message send event. After the delivery of all messages, each node executes one computational action of specified length (d(A)) before the next round starts. The length of all rounds  $0 < T \le C < \infty$  is known in advance and is normally constant over time. To meet this round duration, all messages must be delivered timely, which means that the message end-to-end delay lies within:

$$\forall i \geq 0, \forall k \in P : 0 \leq \Delta \leq \Delta^{+} < T - \max_{i,k} \left( d\left(A_{i}^{k}\right) \right)$$

An example of an execution within this model can be found in Figure 2.7.

Within this model the write-read problem is solved by the a-priory knowledge of the message end-to-end delay bound and action durations. It will work as long as these

Figure 2.7: Example Execution within a Lockstep Synchronous System

bounds are met. If only once a bound is violated, the behavior of the system may become undefined. With respect to the implementation, the assumption of perfect precision is extremely strong, and therefore in practice additional considerations become necessary when implementing such an algorithm.

#### 2.4 Failure Handling in Distributed Systems

So far we have only considered failure free systems. Unfortunately real system will not always work correctly. Parts of the system may fail over time. To describe such events the distributed system theory has established different failure models. These models can either be used to investigate the behavior of a system in case of a failure or to find mechanisms to make the system fault tolerant. For a fault tolerant system it is important to ensure that it stays operational even if some of the nodes get faulty.

An important function required in many distributed fault tolerant systems is to decide on a common value, even in case some nodes of the system are faulty. In such a setting, each node has its own, private input value. Based on all the input values in the system, each node calculates a result value. All results of non-faulty nodes must be the same. The problem is known as the agreement problem and algorithms solving it as consensus algorithms [AW04].

#### 2.4.1 Failure Models

It is impossible to find and describe each single failure which can occur in a distributed system. Therefore the different failure types are grouped into different failure models. These models describe the manifestation of the failures on the algorithmic level.

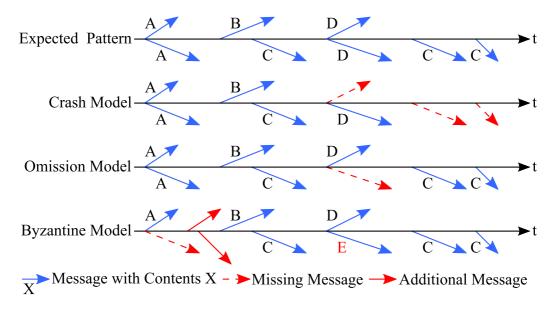

Figure 2.8: Failure Model Example

Depending on the underlying system model, the failures visible at the algorithmic level will be different. Therefore three basic failure models used in distributed systems have been established in literature, namely [DLS88]:

- Crash Failure Model

- Omission Failure Model

- Byzantine Failure Model

They differ in their complexity and the severity of the allowed failures. An important differentiation is, if a failure model allows benign failures [AW04]. In a benign failure model, no illegal operations (like sending additional or conflicting messages) may be executed. For non-benign failure models this constraint does not exist.

Figure 2.8 shows an example execution of a faulty node within the different failure models. It visualizes the differences in the allowed failure patterns. There are more models [AW04], but they are not needed here.

#### **Crash Failure Model**

When using the crash failure model, a faulty processor would behave non-faulty up to a certain point in time. At this point it will crash, which means that it will fail to send any further messages from this time onward. If at the time of crash multiple messages should be sent, only a subset of these messages may be sent. This model is a benign failure model.

#### **Omission Failure Model**

If a node fails to send or receive a message at a certain point in time, an omission failure has occurred. In contrast to the crash failure model, the node may send further messages afterwards. This model is a benign failure model.

#### **Byzantine Failure Model**

Byzantine or arbitrary failures do not limit the nature of the failures in any way. The nodes within the system may even behave malicious and therefore try to actively derail the execution of the algorithm. Additionally faulty nodes can coordinate with each other to maximize the effects of their malicious behavior. It is also possible that conflicting messages are sent to different nodes. Furthermore additional messages, which are not specified by the executed algorithm, may be generated. This model therefore is a non-benign failure model.

#### 2.4.2 Agreement Problem

The calculation of a common (output) value on different nodes is a crucial functionality of a distributed system. No problem in a fault free environment, it becomes more challenging with the power of the used failure model.

An algorithm solving the agreement problem is called a consensus algorithm. Formally such an algorithm is defined as follows [AW04, DLS88].

The system consists of a set P of m nodes  $(\{n_0, n_1, \dots n_m\})$ . Each node  $n_i$  has an input value  $v_i$  out of a value domain V. Goal of the algorithm is to compute a common output value v.

An f-resilient consensus algorithm is considered correct, iff the following properties hold, when at most f nodes are faulty:

- Consistency: All non faulty nodes decide to the same value.

- Termination: In every infinite execution each non faulty node decides eventually.

- Unanimity:

- Strong Unanimity: If all initial values are v and if any non faulty node decides, it decides v.

- Weak Unanimity: If all initial values are v, all nodes are non faulty and if any node decides, it decides v.

Depending on the chosen failure model of the underlying system, different implementations of a consensus algorithm are known [AW04]. It is important to note that there is no consensus algorithm available in the asynchronous model (see [FLP85]).

#### **Byzantine Agreement**

Most interesting is the agreement problem in the presence of Byzantine failures [LSP82]. At most f out of at least 3f+1 nodes (for a lower bound proof see [AW04]) may experience Byzantine failures. Independent of the behavior of the faulty nodes, the non faulty nodes must select a common output value in a bounded amount of time. An algorithm solving this problem is presented below.

#### **Byzantine EIG Algorithm**

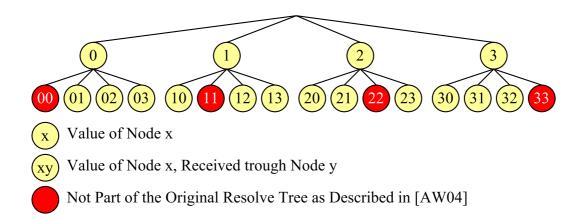

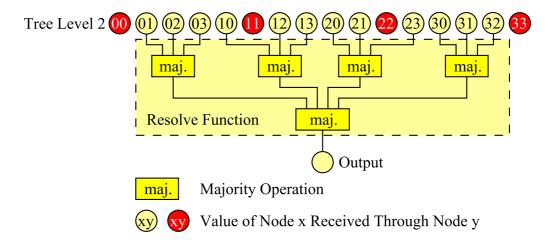

The Byzantine EIG (exponential information gathering) algorithm [AW04] is a lockstep synchronous algorithm which solves the Byzantine agreement problem with strong unanimity, a minimum of required nodes (3f+1), in the minimum number of rounds (f+1), but with messages of exponential size. Its functionality is as described below.

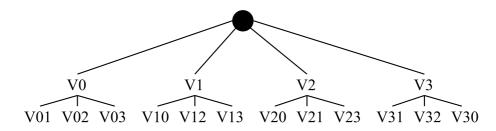

The main component of the algorithm is a tree structure stored by each node. It contains all information gathered about the other nodes. An example of the tree can be found in Figure 2.9. The value  $V_{xy}$  means the value V received from node y, which had received it from node x. No node index will be present more than once in the subscript, therefore no information is processed multiple times by the same node. The tree is built as follows:

- Round 1: In the first round each node sends its input value to all other nodes. When receiving an input value it is stored in the current tree level, if no value is received, a default value is stored.

- Round  $k, 1 < k \le f + 1$ : In each successive round each node sends its current tree level to all other nodes. When receiving a tree level it is again stored in the tree.

After receiving tree level f + 1, the tree is locally used to calculate the output value using a resolve function (mainly a combination of multiple majority votes).

For a detailed description and a correctness proof of the algorithm, please see [AW04].

Figure 2.9: EIG Tree for a f=1 System

## Chapter 3

## **Digital Electronic Circuit Basics**

Digital electronic circuits consist of combinational logic gates (like AND- and OR-gates) and sequential elements (like flip-flops and latches). The circuit function is defined by the interconnection of such gates. In this chapter we will summarize some of the theoretical concepts used to design high speed circuits.

#### 3.1 Clocking Schemata

An important function within digital circuits is the coordination of the sequential elements. Several schemata for accomplishing this task are known.

#### 3.1.1 Synchronous Circuits

The most popular clocking paradigm used today is the synchronous scheme [Wak01, FH90, Sei79]. Although in use for several decades, it is still state of the art. Virtually all commercially designed circuits are implemented using this paradigm.

It uses a centralized clock source (see Figure 3.1), mostly a quartz oscillator, and all operations on the sequential elements are aligned with respect to this global clock and no local synchronization information is needed. Conceptually all sequential elements receive a clock tick at the exactly same point in time.

As appealing as the presence of an ideal global clock is, as problematic the system analysis can get. Increasing clock- and signal frequencies [Con03], therefore decreasing timing safety margins, and increasing gate count tend to make the system analysis more and more challenging. Furthermore increasing error rates [Con03], due to smaller critical charges and lower voltage swings, must be taken into account nowadays when designing synchronous circuits. Thanks to the high degree

Figure 3.1: Synchronous Model

of automation in the design process and the very sophisticated tool support, these problems can still be handled.

Another disadvantage of this paradigm is its single point of failure introduced by the global clock network. A failure within this network can result in the malfunction of the whole system. Interestingly this problem is widely ignored [MFMR04].

Another highly problematic and challenging task, especially in high performance systems, is the design of the clock network. To keep the synchronous abstraction valid, the differences in the delays from the clock source to the different sequential elements (the skew within the clock network) must be rigorously controlled [Fri01]. This is especially problematic for large clock networks. The usage of special topologies, like e.g. forks and trees, nevertheless lead to acceptable results, but render clock routing an art of its own.

As a big advantage, the synchronous paradigm provides a very accurate time base with a precision of significantly less than one (nearly perfect synchronization, 0 in the idealized case).

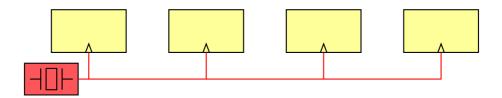

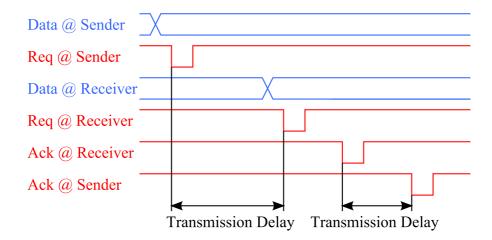

#### 3.1.2 Asynchronous Circuits

A completely different approach is the asynchronous paradigm [Hau95]. The most appealing form of asynchronous logic is the delay insensitive model. It uses local synchronization information, a so called handshake, to coordinate the operation of adjacent sequential elements. A sender uses a request (req) signal (either an explicit signal line or implicitly encoded into the data) to signalize the availability of new data. It does not change the data until the receiver has acknowledge their reception using an explicit acknowledge (ack) signal. Figure 3.2 shows an example of an asynchronous circuit using an explicit request and acknowledge signal.

Due to the absence of any timing bounds and any single point of failure conceptually very appealing, it suffers on the lack of tool support and is therefore commercially scarcely used. Furthermore delay insensitive solutions introduce a significant implementation overhead (like null convention logic (NCL) [FB96]) and/or a timing overhead. Nevertheless there are already working implementation examples available (e.g. [SFGP09]).

Figure 3.2: Asynchronous Model

Unfortunately no global timebase can be established when using the delay insensitive model due to the unknown message delays (infinite uncertainty)[AW04].

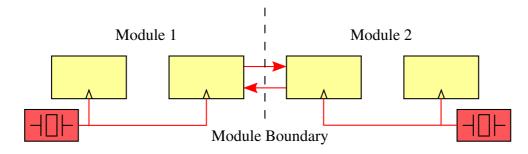

## 3.1.3 Globally Asynchronous Locally Synchronous (GALS) Circuits

An approach to circumvent the restrictions of the synchronous paradigm is the globally asynchronous locally synchronous (GALS) model [Cha84]. The system is split into multiple modules and these modules are internally clocked according to the synchronous model, each using a local clock source. They are unsynchronized. The inter-module communication is implemented asynchronously (see Figure 3.3).

An advantage of this approach is that each module can be implemented as synchronous circuit utilizing the existing powerful toolsets. Due to the small size of the modules, their design and analysis is much easier and faster than the analysis of a large fully synchronous system. A big drawback is the limited communication speed between the modules. Due to the lack of synchronization flow control is needed to enable a secure data transfer between the modules. This limits the communication throughput [TGL07] significantly. Furthermore no global timing information is available.

To circumvent these drawbacks, several approaches have been suggested to loosely synchronize the clocks of the different modules [TGL07]. Unfortunately the wide

Figure 3.3: GALS Model

Figure 3.4: Multisynchronous Model

ranging assumptions made on the clock drift rate to securely implement these approaches may not hold in practice.

#### 3.1.4 Multisynchronous Circuits

A relatively new clocking approach are multisynchronous circuits [SG03]. This model guarantees a bounded clock skew, but in contrast to the synchronous approach the skew can get larger than one clock cycle. To guarantee the skew bound, a certain amount of coordination is needed between the different clock sources.

Like in the GALS model, the circuit is divided into synchronous modules. Each of the modules is driven by a different clock of the multisynchronous ensemble (see Figure 3.4) and can be implemented using the standard synchronous model. Therefore the existing powerful toolsets can be used for the designs.

A big advantage of this paradigm is the presence of a global timebase. Its precision equals the skew bound of the clocking system.

As shown by the DARTS clocking scheme (algorithm introduced in [WS05]), it is possible to implement [FFSK06] such a clocking scheme in a fully distributed and fault tolerant fashion.

## 3.2 Intermodule Communication in Electronic Circuits

The last section has given an overview on how to synchronize different modules of an electronic circuit. Another important question is how to communicate between these modules. In the following we will discuss different approaches for communicating between such modules.

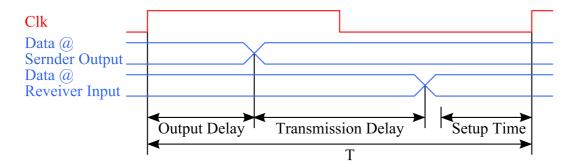

#### 3.2.1 Synchronous Communication

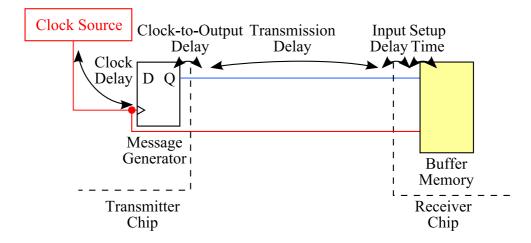

The most commonly used approach for communicating within digital electronic circuits is the synchronous communication scheme [Wak01]. The data transmission is related to a global synchronous clock. This clock defines the validity of the data. Therefore it is only implementable within the synchronous paradigm. At each active clock edge (falling and/or rising edge) a new data item is written by the sender and the receiver reads the data at the next active edge.

Based on the physical implementation of the sequential circuit elements, the following properties arise:

- Output Delay ( $t_{\rm out}$ ): Specifies the time the data needs to appear at the output of a sequential element after an active clock edge.

- Transmission Delay ( $t_{\rm data}$ ): Specifies the time it takes a data bit to move from the sender's output to the receiver's input.

For a save operation the following requirements must be fulfilled:

- Setup Time  $(t_{su})$ : Specifies the time the data must be stable at the receiver input before an active clock edge to guarantee a safe operation.

- Hold Time  $(t_h)$ : Specifies the time the data must be stable at the receiver input after an active clock edge to guarantee a safe operation.

Based on these properties and requirements, the following constraints for a safe operation are important (T is the period length of the clock signal):

$$T > t_{\text{out}} + t_{\text{data}} + t_{\text{su}} \tag{3.1}$$

$$t_{\rm h} < t_{\rm out} + t_{\rm data} \tag{3.2}$$

Note that normally Equation 3.2 is easy to guarantee, while optimizing the period length of the clock signal according to Equation 3.1 is very challenging. To ensure a reliable operation, these constraints must be met at all operational conditions. To guarantee this, a timing analysis has to be done [Sei79, FH90, Fri01, HO71]. All paths in a system are analyzed under worst case conditions and based on the resulting information a maximum clock frequency is calculated. The use of worst case conditions leads to a clock frequency which is much lower than the frequency achievable in the average case.

Figure 3.5: Synchronous Communication

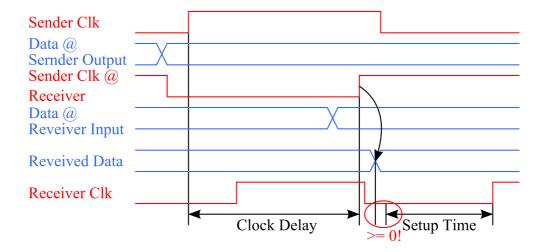

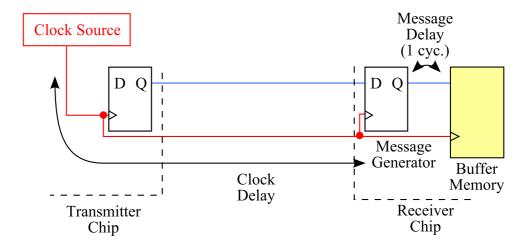

#### 3.2.2 Sourcesynchronous Communication

Due to the relatively inefficient nature of the synchronous communication scheme a new intermodule communication scheme was developed for high speed systems [AJTR98]. The advantage is that the transmission delay of intermodule traces, which is normally much greater than the transmission delays within a module, no longer limits the clock frequency of the system. Additionally this scheme can also be used in conjunction with GALS and multisynchronous clocking schemes.

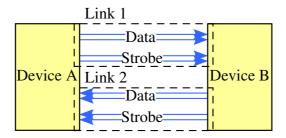

To enable the bit regeneration at the receiver the sender clock signal is transmitted in addition to the data. This can be done either directly, by transmitting the clock signal itself on a separate line, or encoded within the data. In either case, a transition of the sender clock marks the validity of the data. An example can be found in Figure 3.6.

As in the synchronous case, no back pressure mechanism is implemented. Therefore the receiver clock must at least be as high as the sender clock, otherwise data will be lost. Therefore this scheme is usable only with restrictions in conjunction with the

Figure 3.6: Source Synchronous Communication

Figure 3.7: Asynchronous Communication

GALS model. Additional care must be taken to ensure that the timing constraints between the received data and the receiver clock are maintained. For more detailed information on the subject of ensuring the constraints see Section 3.3.

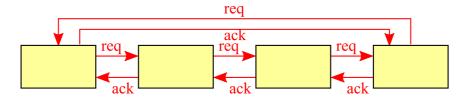

#### 3.2.3 Asynchronous Communication

So far we have seen communication schemes usable in the synchronous, multisynchronous and with some restriction also in GALS model. We will now introduce a completely asynchronous one which can be used in conjunction with each of the presented clocking schemes. The coordination between sender and receiver is done by local handshake signals, namely a request signal (req) to signalize the data validity and an acknowledge signal to confirm the data reception (ack). These signals can be transmitted directly [IEE00] or can be encoded into the data (e.g. null convention logic as described in [FB96]). An example can be found in Figure 3.7. This mechanism also implements a reliable back-pressure mechanism.

The main advantage of this scheme is that its performance is completely adaptive, which means it can react to changes in the transmission delays by itself. Therefore no timing analysis is necessary in advance.

#### 3.3 Metastability

Up to now we have silently assumed that the data is valid when captured by a sequential element. Unfortunately in real systems this is not always true. Consider an external signal read by a sequential element of a synchronous system. Because the signal is external, the system has no control on it at all. What happens, if the signal

Figure 3.8: D-Flip-Flop Timing Constraints

changes at the exact moment the sequential element tries to capture it? The naive answer would be that the value is either the value before or after the transition. Unfortunately this is not true. In this section we will investigate this behavior in more detail.

#### **3.3.1** Flip-Flop Timings

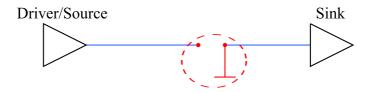

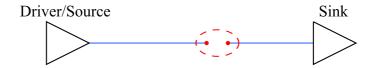

As already mentioned in Section 3.2.1, several timing constraints have to be maintained when working with synchronous sequential elements like flip-flops. As these elements are heavily used in synchronous systems, we will now examine these constraints in more detail. The analysis is based on the standard D-Flip-Flop described in [Wak01]. It can be easily adapted to all other kinds of synchronous sequential elements.

A D-Flip-Flop is controlled by its clock input. The rising or falling edge of the clock signal triggers the capture operation of the data (D) input. To ensure a safe operation, the data input must be stable a certain time before and after each active clock transition [Wak01] (see Figure 3.8). These times are called setup- and hold-time, respectively.

If one of these constraints is violated, the behavior of the flip-flop is undefined and therefore its output (Q) can get undefined, even oscillating, for an unbound range of time (see Figure 3.9) [KC87, CM73]. This behavior is called metastability. It can be transmitted throughout the system [KC87], which means that one flip-flop after another can get metastable. Another problematic possibility is, that two logic elements (combinational and/or sequential) can interpret a metastable input differently due to a slight mismatch of their internal logic thresholds [KC87], resulting in different output values even if they should be the same.

Therefore metastable states are very problematic and must be avoided at all cost. In global synchronous systems only the boundary flip-flops are affected. When using source synchronous or asynchronous communication within synchronous, multisynchronous- or GALS-systems, metastability can arise at each clock boundary.

Figure 3.9: Metastable D-Flip-Flop

#### 3.3.2 Avoiding Metastability

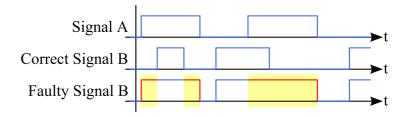

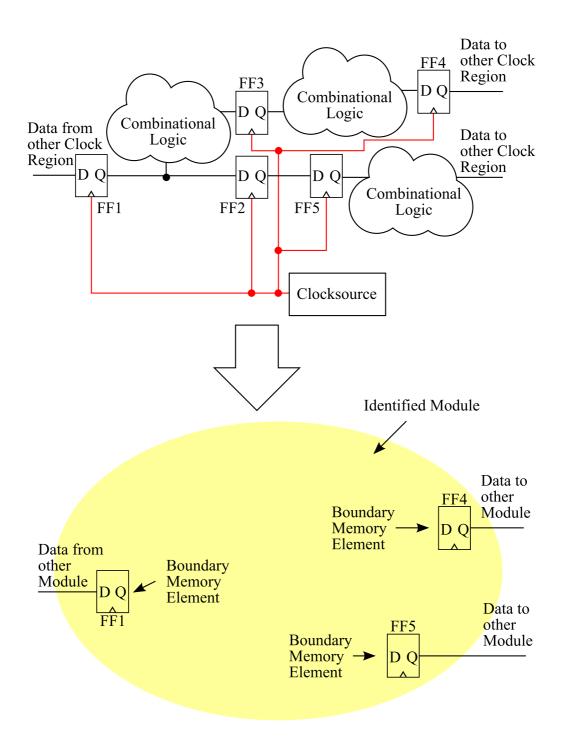

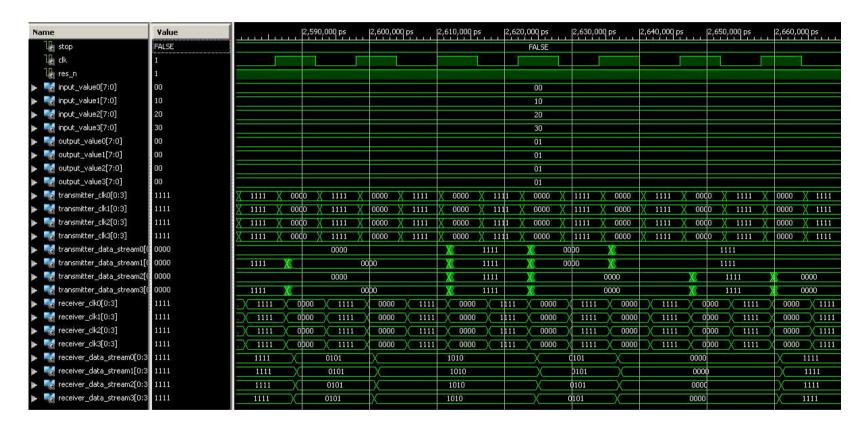

The simplest way to avoid metastability is to use a synchronous system with precalculated timings. As already discussed, in today's high speed systems this is not applicable any more. Furthermore the metastability occurring at the boundary flipflops is not handled by this approach.