Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

Technische Universität Wien

# DIPLOMARBEIT

# Creating a GCC Back End for a VLIW-Architecture

Ausgeführt am Institut für Computersprachen der Technischen Universität Wien

unter Anleitung von Ao.Univ.Prof. Dipl-Ing. Dr. Andreas Krall

durch

Adrian Prantl

Neustiftgasse 45/121070 Wien

7. Mai 2006

Unterschrift

#### Abstract

The Control Processor is a 24-bit, 4-way very long instruction word (VLIW) processor, developed by On Demand Microelectronics. In this work, a port of the back end of the GNU Compiler Collection (GCC) is introduced that takes full advantage of the CPU's parallelism and generates parallel assembler code. Also, the GNU Binutils and the Newlib C runtime library were adopted to support the Control Processor.

The presented GCC back end uses a simple pipeline description to model the functional units of the Control Processor for the instruction scheduler. Based on the results of the scheduler, a separate pass assigns the instructions to the slots of a VLIW bundle. Using this technique an average utilisation of up to 2.5 instructions per bundle is achieved. Special care was taken to support the Control Processor's unusual byte-lengh of 24 bits, which affected many design decisions.

In a second part, the existing assembler for the Control Processor was extended to create object files in the Executable and Linkable Format (ELF). To create a linker and other utilities for these object files, the GNU Binutils were ported to the new target. Based upon this, the GNU Debugger was also extended with an interface to the instruction-level simulator of the Control Processor.

Finally, the C runtime library Newlib was ported to the new target as well, thus completing the cross-development environment for the Control Processor.

#### Kurzfassung

Der Control Processor ist ein 24-Bit, 4-fach VLIW (very long instruction word)-Prozessor, der von On Demand Microelectronics entwickelt wurde. In dieser Arbeit wird eine Portierung der GNU Compiler Collection vorgestellt, die in der Lage ist, den Parallelismus des Prozessors voll auszunützen und parallele Assemblerbefehle auszugeben. Weiters wurden die GNU Binutils und die C-Laufzeitbibliothek Newlib an den Control Processor angepasst.

Das vorgestellte GCC-Backend verwendet eine einfache Pipelinebeschreibung, um die Funktionseinheiten des Control Processors für den Instruction-Scheduler zu modellieren. Anhand der Resultate des Schedulers werden die Befehle in einem eigenen Durchlauf auf die Slots eines VLIW-Bündels aufgeteilt. Durch diese Methode wird eine Slotausnutzung von bis zu 2,5 Befehlen pro VLIW-Bündel erreicht. Eine besondere Herausforderung stellte die ungewöhnliche Wortbreite des Control Processors von 24 Bit dar, die das Design des Backends entscheidend geprägt hat.

In einem zweiten Teil wurde der bereits vorhandene Assembler des Control Processor um die Fähigkeit erweitert, ELF-Objektdateien (Executable and Linkable Format) zu erstellen. Weiters wurden die GNU Binutils auf diese neue Plattform portiert, um den darin enthaltenen Linker mit diesem Format nutzen zu können. Darauf basierend wurde auch der GNU Debugger um die Möglichkeit erweitert, den Simulator für den Control Processor direkt einzubinden.

Um die Entwicklungsumgebung zu vervollständigen, wurde auch die C-Laufzeitbibliothek Newlib für den Control Processor angepasst.

#### Danksagung

Ich möchte mich an dieser Stelle vor allem bei meinem Betreuer Professor Andreas Krall bedanken, der mich während des Designs und der Implementierung des GCC-back ends aber auch später bei der Erstellung dieser Diplomarbeit immer unterstützt hat.

Mein besonderer Dank gilt auch dem gesamten Team von On Demand Microelectronics, allen voran Karl Neumann, der mich während unserer Zusammenarbeit stets ermutigt und viele hilfreiche Ideen beigesteuert hat. Außerdem möchte ich mich bei Julia Ogris bedanken, die mir als Autorin des Simulators sehr viele Fragen beantworten musste.

Schlussendlich möchte ich mich bei meinen Eltern bedanken, die mich bei meinem Studium unterstützt und meine Neugierde gefördert haben, bei meiner Freundin und allen meinen Freunden und Studienkollegen mit denen ich die letzten Jahre sehr gerne verbracht habe.

# Contents

| 1. | Intro | oduction                                     | 8  |

|----|-------|----------------------------------------------|----|

| 2. | The   | On Demand Control Processor                  | 10 |

|    | 2.1.  | Architecture                                 | 10 |

|    | 2.2.  | Instruction pipeline                         | 11 |

|    | 2.3.  | Instruction format                           | 11 |

|    | 2.4.  | Addressing Modes                             | 12 |

|    | 2.5.  | Assembler syntax                             | 12 |

| 3. | The   | GNU Compiler Collection                      | 14 |

|    | 3.1.  | Overview                                     | 14 |

|    |       | 3.1.1. Different configurations of the GCC   | 14 |

|    |       |                                              | 15 |

|    |       | 3.1.3. Compilation with the GCC              | 16 |

|    |       | 3.1.4. The GCC back end                      | 18 |

|    |       | 3.1.5. Further documentation                 | 20 |

|    | 3.2.  | Port specific observations                   | 20 |

|    |       | 3.2.1. Creating code for a 24-bit processor  | 20 |

|    |       | 3.2.2. Machine Modes                         | 21 |

|    |       | 3.2.3. Definition of instruction patterns    | 23 |

|    |       | 3.2.4. Instruction selection                 | 26 |

|    |       | 3.2.5. Instruction scheduling for VLIW slots | 27 |

|    |       | 3.2.6. Defining addressing modes             | 30 |

|    |       | 3.2.7. Function prologue and epilogue        | 30 |

|    |       | 3.2.8. Function calls                        | 31 |

| 4. | Defi  | ning an ABI                                  | 32 |

|    | 4.1.  | Data Types                                   | 32 |

|    | 4.2.  | Memory Layout                                | 32 |

|    | 4.3.  | Register Usage                               | 33 |

|    | 4.4.  | Function Stack Frame                         | 34 |

| 5. | GNL   | J Binutils                                   | 35 |

|    | 5.1.  | Manipulating object files with libbfd        | 35 |

|    |       |                                              | 36 |

|    |       | 5.1.2. Symbols                               | 36 |

|    |       | 5.1.3. Relocations                           | 37 |

|    |                                   | 5.1.4. Porting the BFD library                                                                                 | 37                    |

|----|-----------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------|

|    |                                   | 5.1.5. Debugging                                                                                               | 38                    |

|    | 5.2.                              | The Assembler gas                                                                                              | 39                    |

|    |                                   | 5.2.1. Porting gas                                                                                             | 39                    |

|    |                                   | 1                                                                                                              | 39                    |

|    | 5.3.                              | The Linker ld                                                                                                  | 39                    |

|    |                                   | 5.3.1. The Emulation $\ldots$ | 40                    |

|    |                                   | 5.3.2. The Linker Script                                                                                       | 40                    |

|    |                                   | 5.3.3. Porting ld                                                                                              | 40                    |

| 6. | The                               | GNU Debugger                                                                                                   | 42                    |

|    | 6.1.                              | The structure of GDB                                                                                           | 42                    |

|    | 6.2.                              | Using GDB                                                                                                      | 42                    |

|    | 6.3.                              | Porting the GNU Debugger                                                                                       | 43                    |

| 7. | The                               | New C runtime library                                                                                          | 45                    |

|    | 7.1.                              | Defining system specific issues                                                                                | 45                    |

|    |                                   | 7.1.1. System startup: crt0.o                                                                                  | 46                    |

|    |                                   | 7.1.2. System Calls                                                                                            | 46                    |

|    | 7.2.                              | Porting newlib                                                                                                 | 46                    |

| 8. | Gen                               | erating a complete toolchain                                                                                   | 47                    |

|    | 8.1.                              | Testing with DejaGNU                                                                                           | 47                    |

|    |                                   | 8.1.1. Porting DejaGNU                                                                                         | 48                    |

| 9. | Eval                              | uation of the final product                                                                                    | 49                    |

| -  |                                   | •                                                                                                              | 49                    |

|    |                                   |                                                                                                                | 49                    |

|    |                                   |                                                                                                                | 51                    |

|    |                                   |                                                                                                                | 52                    |

|    |                                   | 9.1.4. Discrete Cosine Transform                                                                               | 52                    |

|    |                                   |                                                                                                                |                       |

|    | 9.2.                              |                                                                                                                | 53                    |

|    | 9.2.<br>9.3.                      | Performance improvements with VLIW bundling                                                                    |                       |

| 10 | 9.3.                              | Performance improvements with VLIW bundling                                                                    | 53                    |

|    | 9.3.<br><b>. Rela</b>             | Performance improvements with VLIW bundling                                                                    | 53<br>53<br><b>58</b> |

|    | 9.3.<br>. Rela<br>. Con           | Performance improvements with VLIW bundling                                                                    | 53<br>53              |

| 11 | 9.3.<br>. Rela<br>. Cone<br>11.1. | Performance improvements with VLIW bundling                                                                    | 53<br>53<br>58<br>60  |

# List of Figures

| 2.1.         | Example of the Control Processor's assembler syntax                        | 13              |

|--------------|----------------------------------------------------------------------------|-----------------|

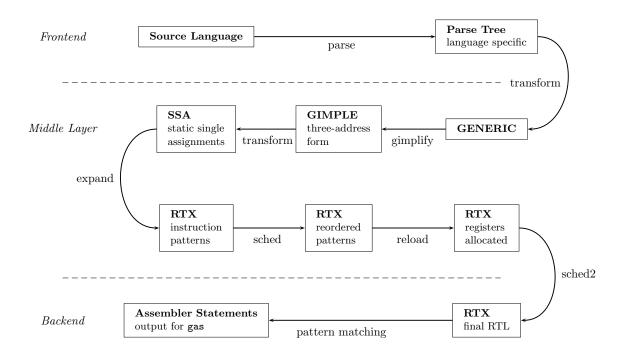

| 3.1.         | Some passes and intermediate representations of the GCC                    | 17              |

| 3.2.         | How to synthesise a push pattern with atomic instructions                  | 24              |

| 3.3.         | How to use an expander pattern to prepare arguments                        | 25              |

| 3.4.         | The GCC instruction pattern for a logical right-shift on the Control Pro-  |                 |

|              | cessor                                                                     | 27              |

| 3.5.         | The GCC instruction pattern for a copy operation the Control Processor .   | 27              |

| 3.6.         | Pipeline description: Reservation of CPU units by an integer instruction . | 28              |

| 3.7.         | Pipeline description: Declaration of integer CPU units                     | 29              |

| 3.8.         | How to fake access to the Program Counter                                  | 31              |

|              |                                                                            |                 |

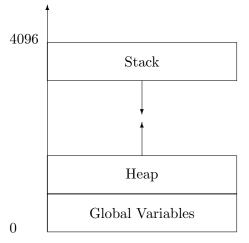

| 4.1.         | Data memory layout for the On Demand Control Processor                     | 33              |

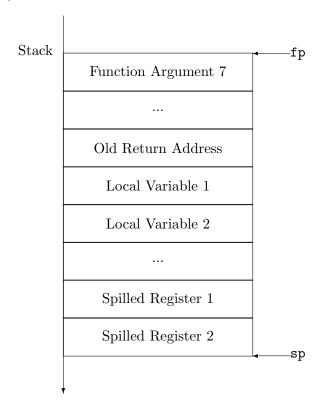

| 4.2.         | layout of the Function Stack Frame                                         | 34              |

| 5.1.         | The components of the GNU Binutils                                         | 35              |

| 5.1.<br>5.2. | Symbols versus Relocations                                                 | $\frac{35}{37}$ |

| 5.2.<br>5.3. | Pointers into two different memories.                                      | 38              |

| 5.3.<br>5.4. | The linker script for the On Demand Control Processor                      | 30<br>41        |

| 0.4.         | The linker script for the On Demand Control Processor                      | 41              |

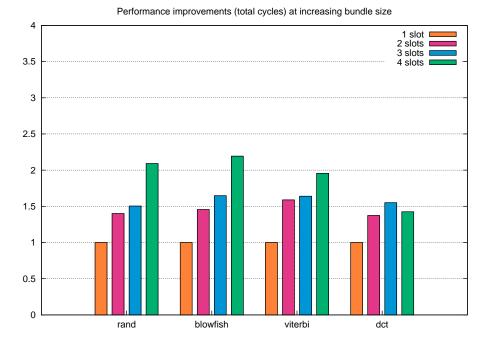

| 9.1.         | Execution time in correlation to VLIW bundle size                          | 54              |

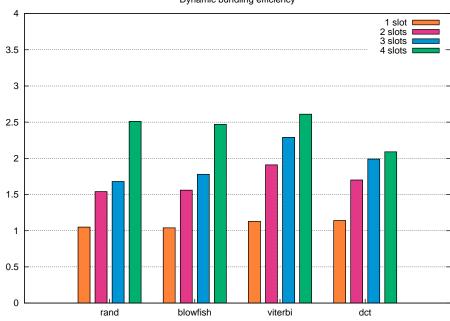

| 9.2.         | Average number of instructions per VLIW bundle at different sizes          | 54              |

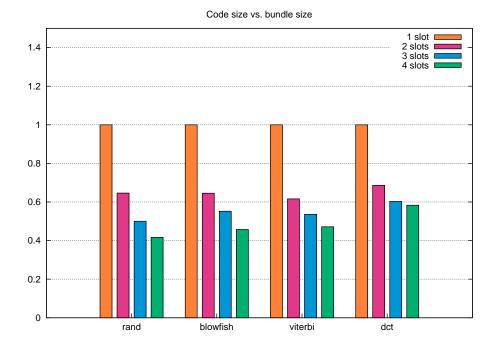

| 9.3.         | Total number of instruction words in correlation to VLIW bundle size       |                 |

|              |                                                                            |                 |

| A.1.         | The source code of the pseudo-random number generator                      | 62              |

| A.2.         | The generated assembler code for the rand() function                       | 63              |

# 1. Introduction

The Control Processor is a 4-way VLIW<sup>1</sup> architecture aimed at parsing next-generation video streams like H.264. The Control Processor was designed by the Vienna-based On Demand Microelectronics who is specialised in high profile digital signal processing applications.

A VLIW architecture is basically a statically scheduled version of a superscalar RISC<sup>2</sup> processor, where the burden of assigning the instructions to execution units lies on the programmer. This has the advantage of eliminating the dispatch logic in the processor and being able to spend more time finding an optimal distribution for the instructions.<sup>3</sup> Programming such a machine in assembler is more challenging compared to a classic RISC processor, because the programmer has to take extra care not to introduce dependencies inside an instruction word. For this reason, it is favourable to provide the programmer with a compiler that will take care of finding the optimal allocation of functional units with instructions and let the programmer specify the tasks of the processor in a high-level language such as C. The high-level language approach is also an advantage for the experimental evaluation of architectural parameters such as the number of parallel functional units in a CPU. A compiler can be constructed in a relatively short timeframe.

The goal of the work presented in this document was to create a cross-development environment for the Control Processor and the C programming language. Already available was an assembler and an instruction-level simulator that could be incorporated in the final toolchain.

The GNU compiler collection was an obvious choice for the task, as it is available in source code, relatively well documented and designed to be highly extendable. Another important point is that it is well integrated with the rest of the GNU toolchain which includes the GNU assembler and linker, but also the widely used GNU debugger, a runtime system and many operating systems. The debugger is an important component of the overall development environment, because it contains the bridge to the instruction level simulator which in turn is necessary to perform any serious testing and development in the absence of actual silicon hardware.

A personal goal that I have for this work is that it serves as a documentation of the steps that are necessary to create a complete development environment for a new processing platform. Most of the components of the toolchain are well documented, but there was not too much documentation about their interaction and the dependencies

<sup>&</sup>lt;sup>1</sup>very long instruction word

<sup>&</sup>lt;sup>2</sup>reduced instruction set

<sup>&</sup>lt;sup>3</sup>[PH98], chapter 6.12, pg. 528

they impose during the development. Wherever possible references to further existing documentation are included throughout the text, so it can be used as a guide during the creation of a new GCC back end.

In the first chapter, the architecture of the On Demand Control Processor is introduced. The description of the toolchain is structured into chapters that discuss each package in detail, at first with a general overview the tool's the mode of operation, then the hands-down description of steps necessary to adopt it to a new architecture, as well as common pitfalls that are to be avoided. Finally, the complete toolchain is presented and some examples of the quality of the final compiler are given.

# 2. The On Demand Control Processor

The On Demand Control Processor is part of On Demand's scalable video engine (SVEN). The Control Processor is meant to be used as a bitstream decoder and in its basic configuration it is powerful enough to handle the parsing of H.264, VC-1 and MPEG2 streams. These are popular formats for the digital distribution of TV broadcasts and feature films.

Its main features are a 4-way VLIW core, 64 general purpose registers, conditional execution, support for various extensions and a 24 bit address space.<sup>1</sup>

### 2.1. Architecture

The Control Processor is in essence a load/store architecture with a reduced instruction set (RISC) and in-order execution. Special to it are four mostly independent instruction units which are fed by very long instruction words (VLIW). These processing units are called slots. It is up to the assembler programmer and the compiler to properly distribute the single instructions across the slots.

In its standard configuration, the processor has a total of 64 general-purpose registers, each with a length of 24 bits. These parameters are meant to be configureable. The pipeline is transparent to the programmer and has three stages: Fetch, Decode and Execute/Writeback. Two of the four slots can be provided with a condition which is evaluated by one of the other two slots. The arithmetic units of the Control Processor do not support multiplication or division of integers; these features are not needed in its key field of application. Of course there is no native support for floating point operations either.

Data memory and program memory live in separate address spaces. The CPU can address  $2^{24}$  independent words in each address space. While one data word is 24 bits long, one instruction word is significantly longer, since it has to hold 4 instructions, including all operands.

The Control Processor supports several extensions for specialised tasks that come up when decoding modern video streams. These include algorithms like Variable Length Coding (VLC), Content Adaptive Binary Arithmetic Coding (CABAC), Content Adaptive Variable Length Coding (CAVLC), and Exponential Golomb Coding which are necessary to decode H.264 streams for example. These extensions are accessed through the port interface, where they appear as data memory addresses and can be made available through library functions in a compiled language such as C.<sup>2</sup>

$<sup>^{1}</sup>$ see [Win05], pg. 7

$<sup>^{2}</sup>$ see [Win05], pg. 8ff

# 2.2. Instruction pipeline

The pipeline of the On Demand Control Processor has three stages which are not visible to the assembly programmer. There are no branch delay slots, but jumps force the pipeline to be emptied, inducing a penalty of two cycles.

- *Fetch:* The first stage is responsible for accessing the code memory in order to fetch the next instruction word.

- *Decode:* In the Decode stage data addresses for the more complex addressing modes are generated and the condition is evaluated. Conditions may be placed for slot 0 and 2 and are executed in slot 1 and 3.

- *Execute:* In the final stage the actual instructions are executed and a possible data memory access is performed. Conditional instructions are only executed if their condition evaluates to true.

The following restrictions emerge from the layout of the pipeline: Only one unconditional jump is possible per bundle. Two conditions may be applied and occupy an extra slot per condition, so up to two conditional instructions are can be placed into an instruction bundle.<sup>3</sup>

# 2.3. Instruction format

The Control Processor uses very long instruction words with 4 instructions per code word in its default configuration. These four instructions are also called an *instruction bundle*. One instruction consists of 6 fields: The operation code (OpCode), an address field, two source registers, a destination register and an immediate field. Both address and immediate value can be up to 24 bit long.

| Slot 0 |         |      |      |     | Slot 1    | Slot 2 | Slot 3 |  |

|--------|---------|------|------|-----|-----------|--------|--------|--|

| OpCode | Address | Src0 | Src1 | Dst | Immediate |        |        |  |

| Table 2.1.: 1 | Format | of a | very | long | instruction | word |

|---------------|--------|------|------|------|-------------|------|

|---------------|--------|------|------|------|-------------|------|

This layout can lead to several inconveniences when using standard tools. The values should be packed in a way that the total size of an instruction word is a power of 2. To perform relocations, the GNU linker needs to convert program-specific word addresses (and especially the immediate field within each micro-instruction) to 8-bit byte addresses inside an object file; if they cannot be converted through a combination of bitshifts and adds, a workaround has to be found. This problem does not exist in the actual hardware implementation; it simply uses a special uncached 216 bit memory for the instruction words.

$<sup>^3 \</sup>mathrm{see}$  [Win05], pg. 9ff

### 2.4. Addressing Modes

The On Demand Control Processor supports a total of four different addressing modes, which include absolute immediate addresses and register relative addresses.

• Immediate: The Address is given as an absolute constant integer.

r0 = port[32];

• *Register:* The Address is the contents of a register.

r0 = port[r62];

• Register + Immediate: The Address is the sum of a register and a constant integer.

r0 = port[r62 + (-1)];

• Register + Register: The Address is the sum of two registers.

r0 = port[r62 + r2];

These addressing modes apply to every command in the group of memory read/write instructions. Due to its load/store architecture, the On Demand Control Processor does not allow memory operands to any other instruction. The jump and jump subroutine (jsr) instructions allow only for constant operands.<sup>4</sup>

### 2.5. Assembler syntax

The syntax of the Control Processor's assembler is different from that of most general purpose CPUs, but it is very programmer friendly and easier to read than most common assembler languages.

The most obvious difference is that operations are not written in prefix but in an infix notation making it look more like a programming language than an assembler. For VLIW instructions a mechanism to mark the beginning and end of an instruction bundle is necessary; this is achieved by putting curly braces around every four operations. Conditions are expressed through the **if** keyword. Assembler source files are preprocessed by the standard C preprocessor (**cpp**).

Data declarations look like typeless C variable and array declarations. The assembler knows only one data type which is a 24-bit, two's complement, signed integer. It does allow the declaration of initialised arrays though.

Figure 2.1 shows a minimalistic example of the assembler's syntax. The fancy syntax has its downsides, too; the performance of the assembler is not as great as the typical GNU assembler implementation that has to parse a much simpler grammar. During the porting of the GNU toolchain, the different syntax was the reason why On Demand's existing lex/yacc based assembler was used instead of the GNU assembler.

$<sup>^4 \</sup>mathrm{see} \ [\mathrm{Neu}05]$  and  $[\mathrm{Ogr}05]$

```

.data

foo = 1;

bar = { 42, 1, 0, 1, 2 }; // Array

.code

{ // instruction bundle

r0 = r1 + 1; // slot 1 (add)

; // slot 2 (nop)

if (r3 < 0) // slot 3 (condition)

port[foo] = 0; // slot 4 (memory access)

}

```

Figure 2.1.: Example of the Control Processor's assembler syntax

# 3. The GNU Compiler Collection

### 3.1. Overview

Work on the GNU Compiler Collection (GCC) began in 1984 when Richard Stallman founded the Free Software Foundation and the GNU Project. The goal of the GNU Project has been to create a software environment consisting entirely of free software. Stallman started with the now famous Emacs text editor and a shell command interpreter, but it was quickly becoming clear that to write free software for a free system there had to be a free compiler. To fill this gap, the GCC project was started. While the GCC started as a C-compiler for the Motorola 68000 CPU it was always designed as a multi-language, multi-platform compiler. It was first released in 1987.<sup>1</sup>

From then the project has grown enormously and by the end of 2005 it supported over 60 host platforms, programming languages such as C, C++, Objective-C, Objective-C++, Java, Fortran and Ada and code generation for almost 40 different architectures.<sup>2</sup> These numbers only cover the official distribution. There are quite a few language front ends (such as PASCAL) and architecture back ends that are maintained separately.

#### 3.1.1. Different configurations of the GCC

The GCC can be configured and installed in different ways, depending on the target platform and the way the compiler is to be used. The configuration system - based on the GNU Autotools - distinguishes three components that define a platform.

- Build System This is the system on which GCC will be compiled on. The configure-script will autodetect this parameter.

- Host This is the system on which GCC is going to run on. It can be specified with the -host= parameter. This parameter decides which compiler will be used to compile the GCC.

- Target This is the architecture for which GCC will compile code. It can be specified with the -target= parameter.

The combination of build system, host and target system determine the type of compiler that is to be build. There are three configurations:

• *Native compiler:* This is the default configuration. In this case the compiler is intended to be run on the same machine as it is being built on and will also

$<sup>^{1}</sup>$ see [Sta06]  $^{2}$ see [Fou06b]

generate code for this very system. The default system compiler is configured in this way.

- *Cross compiler:* This is the common configuration for developing embedded systems, especially when the development machine is more powerful than the target machine. The compiler will generate code for a different architecture than the one it is running on. This configuration is also useful to build a portable project for many architectures at once.

- *Canadian cross compiler:* This more exotic case describes a cross compiler being built by a cross compiler.<sup>3</sup>

Host and target of the new compiler can be specified as flags to the ./configure script of the GCC. As with all GNU development tools, GCC expects to be built in a different directory than the source lies in. This has many advantages: Aside from having an uncluttered source directory, it is also possible to create two different compilers from the same source without having to reconfigure the sources every time.

#### 3.1.2. Important components of the GCC

The GNU Compiler Collection consists of many separate tools which work together during the compilation of a program's sources. The program the user will interact with most of the time is called gcc and is the compilation driver. It is a front end that collects all command line parameters and calls the respective tools in the correct order. Usually a compilation of a C source goes through the following stages:

- gcc: This is the user-visible front end that decides which programs to call. It is responsible for decoding the command line parameters and watches over the different stages of compilation.

- cpp: The C preprocessor. It expands C macros such as **#include** directives and is used for C, C++ and some assembler files.

- cc1: The actual C compiler. Its mode of operation will be discussed in more detail in the next section. Basically, it translates C source into assembler output.

- as: The assembler for the target machine. Its job is to parse the target's assembly language and to create a relocateable binary image or *object file*. The resulting object file will still contain references to symbols that should be defined elsewhere and a list of all addresses that have to be changed when the program will finally be loaded into memory.

- collect2: This tool scans objects for necessary initialisations at startup time and adds pointers to initialisation functions to a table so they can be called before the main() method is executed at runtime.

<sup>&</sup>lt;sup>3</sup>The name "Canadian" derives from Canada having three major political parties in the 1980ies.

• 1d: This is the GNU Linker and (like the assembler as) it is actually not a part of the GCC distribution but part of a package called Binutils. The GNU Binutils are a collection of utilities that handle manipulations of object files such as the the assembler, linker, the strip and objcopy tools.<sup>4</sup> The linker collects all necessary object files and libraries (which in turn are simply archives of multiple object files) and copies them together to form the final executable binary. It most importantly also resolves all references to symbols between all those object files.

Thankfully, not all of these tools have to be rewritten when adding a new machine. In order to support a new target, mostly the code generation back end of cc1 and the assembler need to be extended.

#### 3.1.3. Compilation with the GCC

In this section the process of compiling a (C) source file into assembler will be discussed in detail. A compiler can be divided into three main components: The language front end which understands the source language and constructs a parse tree, a middle layer working with an intermediate representation where optimisations and other program transformations take place and a target machine specific back end handling the actual generation of assembler code.

The compilation of a program happens in many different phases that are too many to describe in detail in this section. The majority of the passes during a compilation are introduced by the optimiser and have to be manually enabled through command line options. For the author of a back end the details of the optimisation passes are not too important, although it must be noted that some errors in the machine description only become apparent with optimisations enabled. The behaviour of the function stack frame allocation is an example for this, as the frame pointer may be omitted and local variables may or may not be stored on the stack, depending on the optimisation settings.

When debugging the machine description it can be helpful to have at least a basic understanding of what happens in the passes that are relevant for the back end. After most of the RTL-based transformations, the GCC provides a dump of the current state of the RTL representation of the program. This feature can be enabled with the -dall command line option. As these dumps are in RTL form<sup>5</sup>, they only reflect changes made by the (RTL-based part of the) optimiser and by back-end-specific passes like the scheduler. A graphical overview of these passes, dataflow inside GCC and the intermediate representations is given in figure 3.1. The following passes are especially relevant to the author of a new back end.

**expand:** This is the first step of the RTL-based component. Here, the intermediate representation is expanded from GIMPLE trees created by the front end to the linear and more machine-near RTL expressions. The *expand*-dump therefore contains the first attempt at converting the source language into the intermediate representation used by the machine description.

<sup>&</sup>lt;sup>4</sup>The Binutils should therefore be installed before trying to compile GCC.

<sup>&</sup>lt;sup>5</sup>An overview of the intermediate representations in GCC is given in chapter 3.1.3

Figure 3.1.: Some passes and intermediate representations of the GCC

- **sched:** The instruction scheduling pass. Here, instructions are reordered to reduce the number of pipeline stalls on processors with instruction latencies, as is the case with many RISC architectures.<sup>6</sup>

- **reload:** The reload pass is where register allocation takes place. This pass marks a dividing line; after the reload is complete, instruction definitions may not introduce any more pseudo registers. The reload process spans a local (in the context of basic blocks) and a global phase.

- **sched2:** Instruction scheduling is performed twice; before and after register allocation. The scheduler dump contains the final allocation of the CPU-units defined in the pipeline automata.

Dumps are also generated for all the optimisations such as common subexpression and dead code elimination. But for the back end above passes should be the most relevant.<sup>7</sup>

#### Intermediate representations within the GCC

The GNU Compiler Collection uses many different kinds of representations for program code. In the front end, the programming language is parsed by the compiler and the

$<sup>^{6}</sup>$ see [S<sup>+</sup>05], chapter 8.5

<sup>&</sup>lt;sup>7</sup>see file gcc/passes.c in [Fou05]

program is stored in a syntax tree. This tree still carries language specific information which is gradually lost during the compilation.

Since the middle layer has to work with every supported language, a language independent representation is constructed by the front end. These trees are called GENERIC. They represent an entire function in an intermediate language.<sup>8</sup>

The GENERIC trees are then converted to so-called GIMPLE trees. GIMPLE is a simplified subset of GENERIC that is used during the optimisation passes.<sup>9</sup> That name is derived from the SIMPLE<sup>10</sup> trees of McGill University's McCAT compiler which they are based on. GIMPLE trees have expressions already broken down into a three address form, which is needed for all later program transformations. GIMPLE trees are a relatively new development and they were added only in the 4.0 branch of the GCC. Data flow analysis brings the trees into a static single assignment (SSA) form, where each modification to a variable creates a new instance of that variable, so each variable is assigned a value exactly once.

Still, the most important intermediate representation is the register transfer language (RTL). RTL expressions - when printed as a debug information - look very much like Lisp expressions. These lists of expressions (called RTX for *register transfer expressions*) are used for most "classic" optimisations and eventually also for the actual code generation.<sup>11</sup>

Code generation works by simple pattern matching of instruction templates (which are - surprise - written in a Lisp-like form) with the register transfer lists.<sup>12</sup>

#### 3.1.4. The GCC back end

To add a new target to the GCC a new configuration directory has to be added to the gcc/config/ subdirectory and to the automake scripts.<sup>13</sup> The description of a target is split into three parts:

- targetname.h: This header file contains the definitions of many macros that define the compiler's behaviour. A complete list of all possible options is given in chapter 14 of [S<sup>+</sup>05]. Not every macro has to be defined for every architecture, but unfortunately, the documentation fails to tell which macros are absolutely needed and which may be omitted. As a rule of thumb, it is good practice to prepare a new header file by copying the documentation and the default values of most important macros from the internals manual.

- targetname.md: This is the machine description. In this file the semantics of every assembler instruction of the target machine should be defined. GCC defines a set of generic instructions which are used by the RTL intermediate representation.

$<sup>^{8}</sup>$ see [S<sup>+</sup>05], chapter 10.1

$<sup>{}^{9}[</sup>S^{+}05]$ , chapter 10.2

$<sup>^{10}</sup>$ see [Mer03]

<sup>&</sup>lt;sup>11</sup>see [S<sup>+</sup>05], chapter 11

$<sup>^{12}[{\</sup>rm Par04}]$  gives a very graphic example of how this process works in chapter 2

<sup>&</sup>lt;sup>13</sup>[Par04], chapter 3.3, pg. 59ff provides a detailed description of the modifications to the make script that are necessary.

The machine description is then used to map each of these generic instructions to an assembler instruction, and it may also define side effects or constraints for each instruction.

There is a basic set of instructions that every back end has to define (mostly move, basic arithmetic and logic operations and jumps), but most other and more complex instructions may be left to the compiler to express through weaker operations. Then there is also the runtime library libgcc where unsupported instructions can be defined. These often include divisions and floating point operations.

• targetname.c: Many macro definitions can get rather complicated and are better implemented as separate functions. These functions handle the many details of the application binary interface (ABI) such as function entry and exit duties.

#### The runtime library libgcc

Not every processor can support the full feature set. It is the compiler's job to generate code for unsupported instruction patterns and in many cases this happens transparently to the programmer of the machine description. For some of these instructions it is more efficient to generate calls to library functions instead of inline code. These library functions form the compiler runtime library libgcc. The libgcc consists of two parts: one part has to be supplied by the author of the machine description (libgcc1) and a generic part libgcc2. Both are written in C, although some functions in libgcc1 may be hardcoded in assembler.

libgcc1 typically contains implementations of basic arithmetic and logic functions such as integer divisions.

Every target machine uses the same libgcc2, but the set of functions differs depending on whether there is a native implementation for a particular feature or not. In libgcc2 there are arithmetic functions for non-native double precision integer modes but also initialisations routines that get called automatically by main() before the user program is run. To perform these initialisation tasks, the compiler inserts a call to a function called \_\_main() right after the function header of the program's main() routine. This function manages an array of function pointers called \_\_CTORS\_\_ that are to be filled in by the linker and point to the constructors of global C++ objects. Since the program cannot know whether it will be linked against a C++ module at a later time, this call has to be inserted into every C program as well.

The libgcc also contains emulation routines for basic floating operations. The implementation of the floating point functions is located in the file gcc/config/fp-bit.c.

#### Future plans

By the end of 2005 a discussion among GCC developers started about replacing the RTL back end with a technologically more advanced version. Currently there exists a proposal from the developers of the low level virtual machine (LLVM) project, some of which are now employed by Apple Computer, about merging the GCC front end with the

20

LLVM optimiser and code generators.<sup>14</sup> The LLVM project is featurewise comparable to the current GIMPLE/RTL back end, but is implemented in C++ and offers additional features such as compiling to a byte code (for later use with a just-in-time compiler, similar to the Java approach) and link-time optimisations.

From the discussion it seems as if consensus is that the RTL back end will be replaced over time but that it will happen gradually and not too fast, since it would be a too great effort to rewrite all back ends for all supported architectures.

#### 3.1.5. Further documentation

A good reading before starting to port the GCC to a new architecture is [Nil00] combined with the official GCC Internals Manual ( $[S^+05]$ ), which serves well as a reference. While the official manual is quite complete, the meaning of some parts is easier to understand when compared to an actual implementation in one of the better documented back ends. One of the best back ends in that concern is the one for the Fujitsu FR-V family of processors, but the Axis CRIS back end is also very interesting to read, especially since it is the basis of [Nil00].

### 3.2. Port specific observations

Porting to specialised hardware can involve solving some tricky problems. Since it has to support almost 40 different architectures, the GCC is written to be easily retargetable, but it makes some assumptions about the target machine that can make porting a bit challenging. In his "Porting GCC for Dunces" Hans-Peter Nilsson writes: "GCC is specifically aimed at CPU's with 32-bit general registers and byte-addressable memory".<sup>15</sup>

This might look intimidating if one sets out to port to a 24-bit word addressable machine, but previous ports have shown that something even harder is possible.<sup>16</sup>

This section contains an overview of the design decisions that were used to create the back end for On Demand's Control Processor. Also, there will be many examples of how to implement certain features in the machine description and a discussion of common fallacies that make the implementation harder than necessary.

#### 3.2.1. Creating code for a 24-bit processor

One obvious problem was that there was no reference back end for a 24-bit architecture in the GCC's standard distribution. Almost all back ends used 8-bit bytes and a wordlength that is a power of two. The only exceptions were the TMS320C3x and TMS320C4x digital signal processors from Texas Instruments which used 32-bit bytes, and the pdp10 back end which used a hack to support 36-bit words and is no longer part of the standard distribution.

$<sup>^{14}</sup>$ [Lat05]

<sup>&</sup>lt;sup>15</sup>[Nil00], pg. 17

$<sup>^{16}[\</sup>mathrm{K\ddot{0}5}]$  shows that you can even port GCC to an 8 bit accumulator architecture that has only two registers

The difficulties with 24-bit words arise from GCC making assumptions like beeing able to calculate consecutive addresses by expressions of the form  $(base\_addr+1) << byteshift$ , for example. But there are some strategies to minimise these problems that will be shown in this chapter.

The 24-bit words are also problematic in the compiled binary, as the GNU linker is not too happy about relocating addresses to targets that are not aligned at a power of two.

#### **About Bytes and Units**

If the smallest addressable unit of an architecture is a *byte*, that architecture is called *byte-addressable*. It is not recommended to try to port GCC to a word-addressable machine and this will cause a lot of problems that will require many of the GCC's internals to be changed.

The size of the smallest addressable unit of the target machine is called a *unit* in the GCC jargon, and can be defined through the BITS\_PER\_UNIT macro in the targetname.h file. The default size of a unit is 8 bits.

The GCC sources tend to use the terms UNIT and BYTE interchangeably which is very confusing and important to remember when browsing through the GCC sources.

#### Word-addressability

Most modern architectures are byte-addressable. There are several variants, though. The DEC Alpha, for example, can only address 32- and 64-bit words, but the addresses are still counted in 8-bit bytes (with the lowest 2 bits ignored), making it a byte-addressable machine in the GCC sense.

So how can the GCC generate code for a machine that counts addresses in steps of 24 bit and whose registers are 24 bit wide? The solution is this that that machine *is* actually byte-addressable, but one byte will be 24 bit long. This implies that all datatypes are at least 24 bit long as well. The common definition of a byte as an 8-bit entity predates the GNU compiler collection, where a byte is simply defined as the smallest accessible unit of a certain processor.

The gist of this dilemma is summed up by the following statements:

- 1. The GCC does not really distinguish between a Unit and a Byte.

- 2. The GCC can only generate code for byte-addressable machines.

- 3. The size of a unit = byte is not necessarily 8, although it should be a power of 2.

#### 3.2.2. Machine Modes

The GCC distinguishes a number of *machine modes* that correspond to the data types in the programming language. On 32-bit architectures the machine modes default to the setup shown in figure 3.1.

| Name    | Length          | Description                       |

|---------|-----------------|-----------------------------------|

| QImode  | 8 bit           | Quarter-Integer                   |

| HImode  | 16 bit          | Half-Integer                      |

| SImode  | 32 bit          | Single Integer                    |

| DImode  | 64 bit          | Double Integer                    |

| SFmode  | 32 bit          | Single Precision Float            |

| DFmode  | 64 bit          | Double Precision Float            |

| BLKmode | everything else | Arbitrary <i>blocks</i> of memory |

Table 3.1.: Common machine modes and their default sizes on a 32-bit processor

Although the name suggests something different, especially libgcc depends on QImode to be defined, and to be the smallest available mode for the target processor. For this reason, the Control Processor back end defines QImode as the register-wide 24-bit mode and HImode as the double precision integer mode with a length of 48 bit.

Selecting the floating point modes is not as critical as the integer modes; on the Control Processor the QFmode and the HFmode and the floating point format of the back end for the TMS320C4x from Texas Instruments were chosen.

#### Floating point emulation

Even if the target machine is integer-only, most programming languages expect that floating point operations are available. On architectures that support a numerical coprocessor, like the Intel 80386, this is solved by using an FPU simulator, that handles the illegal instruction interrupt. But for processors that do not support floating point instructions the compiler has to generate calls to an emulation library. The GCC comes with such a library, which is part of libgcc. The necessary functions are located in the gcc/config/fp-bit.c file, which is to be included in the *Makefile fragment* of the back end, gcc/config/targetname/t-targetname.

The author of the back end only needs to choose one of the supported storage formats, and the GCC will substitute library calls for all floating point operations. Also, an instruction pattern to copy floating point numbers needs to be defined.

Again, the floating point emulation library of the GCC makes some assumptions about the target machine that may be in conflict with platforms where the size of a byte is different from 8. The data type declarations expect the machine mode of int to be SImode, which is only true for byte-addressable 32-bit platforms. Another problem that may be encountered is that the generated floating point functions have the wrong modesuffix; likely sf, for single-precision floats, where it should read qf, as it would make sense for a register-sized machine mode. This can be fixed by registering the floating point functions in the TARGET\_INIT\_LIBFUNCS, just as it is done with the integer functions of libgcc1, by a call to the set\_optab\_libfunc() function.

#### How to implement double-sized integers

Programming languages tend to offer many different data types to the programmer; processors sometimes don't. Large integers are necessary to hold the result of an integer multiplication, but also have uses for filesystem pointers and other things.

The GCC encourages the definition of data types that are unsupported by the target processor. Once the machine mode has been specified, it is sufficient to define the move operations using shorter instructions, and GCC will synthesise every other operation. It does so by splitting the data and storing it into consecutive registers. The resulting code will not be very efficient if the processor does not have a carry flag, though.

The back end for the On Demand Control Processor defines a 48-bit integer datatype that way.

#### 3.2.3. Definition of instruction patterns

There are different kinds of instruction patterns that can be defined in the machine description. In the most straightforward case, a compiler-known instruction pattern would map directly to an assembler instruction on the target machine. For these cases, the define\_insn patterns can be used. Examples for define\_insn patterns are Figure 3.4 and 3.5. The define\_insn expression takes five parameters:

- 1. The name of the instruction. In case of a compiler-known pattern (like movqi), it is used by the code generator to identify the instruction and its machine mode<sup>17</sup>.

- 2. The RTL expression pattern. It defines the semantics of the instruction, and is also used by the code generator to match RTL expressions of unnamed expressions. RTL expressions consist of an operation whose operands may contain subexpressions. Each operand should have a postfix declaring its machine mode. The match\_operand expression is used to refer to an operand of the instruction pattern.<sup>18</sup>

- 3. A condition. Conditions control the availability of an instruction on the current sub-target or in a specific pass of the compilation.

- 4. The assembler template. This is either a string that has to be processed and output to the Assembler, or a piece of C-code that returns the correct assembler template. It can also span several lines to provide different templates for every alternative specified by the constraints. See [S<sup>+</sup>05], chapter 13.6, for a more detailed explanation.

- 5. An optional vector of attributes. Attributes are used by the instruction scheduler to specify the type of an instruction (integer, jump), for instance.

Sometimes a standard pattern translates to a sequence of assembler instructions. In this case a **define\_expand** pattern should be used. An example for this is the **pushqi** pattern on the Control Processor. During code generation, expand patterns are not

$<sup>^{17}\</sup>mathrm{GCC}$  jargon for: data type

$<sup>^{18}</sup>$ A detailed explanation is given in [S<sup>+</sup>05], chapter 13.4

```

; PUSH

; sp = r62

;

(define_expand "pushqi"

[(set (mem:QI (plus:QI (reg:QI 62) (const_int -1)))

(match_operand:QI 0 "regimm_operand" "ri"))

(set (reg:QI 62) (minus:QI (reg:QI 62) (const_int 1)))]

""

""

)

```

Figure 3.2.: How to synthesise a push pattern with atomic instructions

identified through their RTL pattern (the second parameter), but by their name. The RTL sequence that follows the name is then used to describe the operations that the instruction should be *expanded* to. They will then replace the pattern that had the instruction's name in the program and a new round of pattern matching will start.

Then, there is sometimes the necessity to generate different code for the same standard instruction depending on the circumstances. An example for this would be the prologue pattern. This is the other variant of *expander* definitions. In this variant the RTL template part is left empty and the RTLs are generated by C-code that is placed in the last parameter. This C function can deliberately stop the pattern matcher from trying to find another pattern for the current template via the DONE; macro. This is the way the function prologue instruction is implemented, for example. If the expander definition is only used to prepare or check some of the instruction's parameters, the DONE; macro can be omitted and the code generator will continue to look for a pattern that matches the one in the RTL template.

The branch instructions on the On Demand Control Processor are an example for the second variant of expander definitions. The problem is that the GCC expects the target processor to use a *condition code* (CC) register to save the result of a comparison instruction. On the Control Processor, conditions may be applied to any instruction, so the compare and branch instructions form a single more complex assembler line. In the approach taken, the pattern for the cmpqi operations just stores the parameters into global variables that are later used by the branch pattern which in fact only prepares the parameters for the real branch pattern that is specified in the RTL template as shown in figure 3.3.

A third kind of instruction patterns are *split* patterns. These patterns show the code generator how to replace a complex instruction with several simpler ones. Note that this is very similar to the expander definitions: In fact, both patterns are used for the same purpose, but they are evaluated in different stages of the compilation. Expander definitions are expanded very early, and are very flexible, whereas splits are performed in a later pass and impose stricter rules. For instance, it is unsafe to introduce new pseudo registers after the reload pass has completed. Splits behave almost like peephole

```

ilvy.md:

(define_expand "cmpqi"

[(set (reg 60)

(compare (match_operand:QI 0 "register_operand" "r")

(match_operand:QI 1 "regimm_operand"

"ri")))]

.....

{

ilvy_cmp_op0 = operands[0];

ilvy_cmp_op1 = operands[1];

DONE;

})

(define_expand "bgeu"

[(set (pc)

(if_then_else (match_dup 1)

(label_ref (match_operand 0 "" ""))

(pc)))]

.....

"{ operands[1] = ilvy_emit_conditional_branch (GEU); }"

)

ilvy.c:

rtx ilvy_emit_conditional_branch (enum rtx_code code)

{

/* Use the operands stored by the preceding cmp insn */

rtx op0 = ilvy_cmp_op0, op1 = ilvy_cmp_op1;

/* Zero the operands. */

ilvy_cmp_op0 = ilvy_cmp_op1 = NULL_RTX;

/* Return the branch parameters */

return gen_rtx_fmt_ee (code, Pmode, op0, op1);

}

```

Figure 3.3.: How to use an expander pattern to prepare arguments

optimisations. They also play an important role with delay slot filling.<sup>19</sup>

#### 3.2.4. Instruction selection

As mentioned before, the GCC's instruction selection works by simple pattern matching, but it does provide mechanisms to control the selection process. One consequence of the pattern matching algorithm is that the order of the pattern definitions matters; if more than one pattern matches the RTL template one that was defined earlier will be used.

If no suitable pattern can be found, the expand pass tries to generalise the operation by using a mathematical equivalent expression or by splitting a complex operation into smaller sub-operations (an example for this would be a copy operation of an entity in BLKmode). If this does not work the expander tries to generate a call to a compilerknown function. A list of these functions is kept in the **optabs** which can be modified by the back end to let the compiler know of functions that are specified in the back-endspecific part of **libgcc**.

Unlike Burg-based code generators which use a tree-pattern matching algorithm, the GCC does not offer a too sophisticated cost model, though there is the TARGET\_RTX\_COSTS hook that lets the back end assign costs to specific RTL expressions.<sup>20</sup> The scheduler interprets the *cost* value that is assigned here as the latency of the instruction.

A more important role in the instruction selection process is occupied by *predicates* and *constraints*. While they both fulfill very similar tasks, which is to impose constraints on the possible usage of a specific instruction pattern, they are evaluated at different times. Their relationship could be described as predicates doing a rough preselection and constraints performing the fine tuning of the operands.

#### Predicates

A Predicate is used to describe the types of *operands* a certain instruction may take. Common predicates are **memory\_operand** or **register\_operand**. But of course the back end may define machine-specific predicates, like the often used **regimm\_operand** on the On Demand Control Processor, which was used to denote operations that accept both a register or an immediate value. Figure 3.4 shows the use of predicates for the logical shift right operation on the Control Processor. While the destination and source operands need to be registers, the shift amount can either be given in a register or as an immediate value.

#### Constraints

Constraints allow for much more detail in the instruction selection process. As with the predicates, it is possible to have user defined constraints, too. A constraint is a short string that is used to define several variations of the same instruction. The example in figure 3.5 shows a *move* operation. Moves write to the first operand; thus the "=" in

$<sup>^{19}</sup>$ see [S<sup>+</sup>05], chapter 13

$<sup>^{20}</sup>$ see [S<sup>+</sup>05], chapter 14

```

Figure 3.4.: The GCC instruction pattern for a logical right-shift on the Control Processor

```

the first line. The alternatives are separated by commas: If the destination is a register, the source may be a register (r), a memory location (m) or an immediate value (i). Memory-memory moves are not permitted.

Figure 3.5.: The GCC instruction pattern for a copy operation the Control Processor

#### 3.2.5. Instruction scheduling for VLIW slots

A relatively new addition to the GNU Compiler Collection is the inclusion of a *pipeline* hazard generator. To improve performance, modern processors come with many identical functional units that can process the instruction stream in parallel. On many processors this happens transparently, like the superscalar and out-of-order architectures, but some designs take a different approach and let the compiler do the work of assigning the instructions to functional units of the CPU.

An example for these are the very long instruction word (VLIW) architectures, like the Intel Itanium or the Fujitsu FR-V family of processors. The On Demand Control Processor also uses an explicit VLIW encoding.

The GCC provides a powerful description language for processor pipelines which integrates nicely with the rest of the machine description. This language allows the definition of the processor's functional units and the constraints that are imposed on the assignment of instructions to those units.

The instruction scheduler depends on an exact description of the processor's pipeline. It has to decide on whether an instruction may be issued at the current time, and how to order the instructions so that idle cycles can be minimised.

To see if it is legal to issue an instruction, two kinds of constraints must be met:

- 1. Data dependency: All operands of an instruction must be available. This implies that an instruction may not depend on the result of any instruction that belongs to the same instruction bundle.

- 2. Instruction latency: Often the result of a more complicated calculation or a memory access will not be available immediately, but takes a fixed number of cycles to arrive. This is not an issue with the On Demand Control Processor.

To determine the availability of functional units at a certain time, the pipeline description is transformed into a deterministic finite-state automata (DFA) with the following mapping: States depict issue cycles with the assignment of functional units and transitions correspond to the possibility of issuing a certain instruction at this point in time.<sup>21</sup>

The machine description has to be extended to assign instruction class attributes to the particular instruction patterns, so the scheduler knows which processing units are going to be used, and what the latency of the instruction will be. The pipeline description is made up of regular expressions which are later used to create the DFA. The expressions describe how functional CPU units are allocated by each class of instructions. Figure 3.6 shows how an integer operation can execute in each of the units slot0-slot3 and how the result will be available by the start of the next instruction bundle.

The statement declares that the "integer"-class units will be used and that the default latency is 1. The statement only applies to instructions that have the attribute "int" set. The final string parameter contains a regular expression that defines the possible allocation of the functional units. An expression like "slot2+slot2" means that for two consecutive cycles the unit "slot2" will be allocated. A "\*" is shorthand for multiple applications of the "+" operator. Alternatives can be specified with the "|" operator.

```

(define_insn_reservation "integer" 1 (eq_attr "type" "int")

"(slot0) | (slot1) | (slot2) | (slot 3)"

)

```

Figure 3.6.: Pipeline description: Reservation of CPU units by an integer instruction

The relationship between the functional units of the CPU would be declared as in figure 3.7.

The names of the units are declared in the define\_query\_cpu\_unit statement. Two sets define the sequence in which the units may be allocated. The *presence set* of a given unit defines a set of slots that have to be already allocated to make the unit available. The *absence set* does the opposite and defines units that must not be allocated before.

The code that uses the DFA to perform the actual instruction scheduling is back end specific; luckily the back end for the FR-V family of processors contains a very general

<sup>&</sup>lt;sup>21</sup>see [S<sup>+</sup>05], chapter 13.19.8

```

(define_query_cpu_unit "slot0, slot1, slot2, slot3")

(presence_set "slot1" "slot0")

(presence_set "slot2" "slot1")

(presence_set "slot3" "slot2")

(absence_set "slot0" "slot1 slot2 slot3")

(absence_set "slot1" "slot2 slot3")

(absence_set "slot2" "slot3")

```

Figure 3.7.: Pipeline description: Declaration of integer CPU units

implementation that can be reused with little modification. It even supports multiple instruction groups which is a nice feature in case the CPU is not built out of identical units.

#### The instruction scheduling algorithm

The bundling of instructions to VLIW packets is a process that happens in three steps $^{22}$ :

- 1. The GCC scheduling passes: The standard scheduler takes care of instruction latencies and tries to reorder the instructions in a way that pipeline stalls are minimised. This pass is only enabled at the optimisation levels -02, -03 and -0s.

- 2. TARGET\_MACHINE\_DEPENDENT\_REORG: This hook is called at all optimisation levels.<sup>23</sup> Here, the necessary nops are inserted and the labels are aligned at the instruction word boundaries.

- 3. TARGET\_ASM\_FUNCTION\_PROLOGUE: The actual bundling is performed in this hook. This hook was originally intended to output the assembler code for the function prologue, but has been superseded by the more powerful prologue instruction pattern. It is being hijacked for the bundling process because it is called just before a function is output to the assembler. The function prologue hook clears a flag for each instruction that should start a new bundle. It also reorders the instructions for processors that have different instruction classes associated with the instruction slots. Because this reordering process can destroy the meaning of the RTL stream and thus confuse the code generator, it can only be performed right before the assembly output happens.

Eventually, the ASM\_OUTPUT\_OPCODE hook interprets the bundling flag and adds the curly braces that indicate instruction bundles before printing the instructions to the assembler. While the DFA of the pipeline description is not used to assign the instructions to execution slots, all three passes use it to determine the correctness of a possible

$<sup>^{22}{\</sup>rm see}$  the documentation in file gcc/config/frv/frv.md of  $[{\rm Fou05}]$

$<sup>^{23}</sup>$ see [S<sup>+</sup>05], chapter 14.29

combination of instructions in a VLIW bundle. The Control Processor back end uses a simplified version of the FRV back end's algorithm, because it has only one uniform class of integer execution units. The scheduler will add an instruction to the current bundle if the following conditions are satisfied:

- The total number of instructions in a bundle is < 4.

- The DFA allows to add the current instruction. This is done through the query interface of the pipeline description.

- There are no register or memory conflicts between the current instruction and all other instructions in the current bundle. For this check, internal data structures of the GCC can be used.

Unlike the FRV back end, the Control Processor back end currently does not reorder the instructions. For the reordering, the GCC's instruction scheduler is used.

#### 3.2.6. Defining addressing modes

The decision wether a specific addressing mode is legal for the target processor is made by the LEGITIMATE\_ADDRESS\_P macro, which should be defined in the targetname.h file. This macro gets called twice for each address during the compilation. The first time it is invoked with an RTL expression that may still contain pseudo registers; the second time, a stricter check is needed, which means that the address will be used in that exact form as it is passed to LEGITIMATE\_ADDRESS\_P.

The GCC can and will use very complex addressing modes that may include side effects, like a post-increment of the address register - a feature that was included in an earlier version of the Control Processor. It will also try to generate memory indirect addresses and *address* + *offset* modes. The LEGITIMATE\_ADDRESS\_P may be used to restrict the size of the offset or displacement to 12 bit, as needed by the Control Processor.

#### 3.2.7. Function prologue and epilogue

The prologue and epilogue instruction patterns are generated at the beginning and end of each function. There are also the older TARGET\_ASM\_FUNCTION\_PROLOGUE and TARGET\_ASM\_FUNCTION\_EPILOGUE macros that are called before a function is written to the assembler, but it is recommended to use the instruction patterns instead. However, the macros are still used as a trigger to perform instruction bundling.

The prologue and epilogue patterns are ideally written as expander definitions that generate the necessary code to set up the function stack frame and save the callee-saved registers. This code has to be supplied by the back end, as it depends heavily on the ABI.

In the Control Processor's back end the function prologue does the following things:

- 1. Push the old Frame Pointer to the stack.

- 2. Set the frame pointer (fp) to the value of the current stack pointer (sp)

- 3. Decrement the stack pointer by the size of the stack frame.

- 4. Save the return address on the stack.

- 5. Push every callee-saved register that will be used<sup>24</sup> by the function.

The epilogue performs the complimentary actions in reverse order. Eventually, it emits a return instruction.

#### 3.2.8. Function calls

In order to implement call tables, virtual functions or function parameters it is necessary that the target processor supports a call to a non-constant address. The Control Processor does not have such an instruction. The jump() operation, on the other hand, would take the destination address in a register, but this approach would still leave the return address to be written to register 63. This leads to yet another problem: On the Control Processor, the program counter is not directly accessible either.

To solve this problem a label is emitted just before the jump to the function. Then, in order to get the program counter (PC) into r63, as the callee function expects it, a load-immediate of the label is issued. While the actual jump is made, r63 is increased by one, to point to the address of the next instruction. Figure 3.8 shows the relevant piece of the machine description.

The XEXP() is just there to cope with an oddity of the assembler's syntax. Usually memory references are indicated by enclosing them in a port[] expression, but this does not apply to the targets of jump instruction. So the operand is de-referenced, to convert a (mem:qi(reg:qi)) RTX into a (reg:qi) expression.

Figure 3.8.: How to fake access to the Program Counter

<sup>&</sup>lt;sup>24</sup>the regs\_ever\_live[regno] predicate can be used to decide this

# 4. Defining an ABI

The application binary interface (ABI) defines the way that functions communicate with each other. It defines the calling conventions, the basic data type layout and the way a function stack frame is set up. The definition of an ABI should be the first step when porting a compiler. Often the ABI is already existent, but many times it has to be defined from scratch.

The ABI for the On Demand Control Processor was changed a few times during the design of the GCC back end. In the beginning the feasibility of 8-bit data types was evaluated. Since there is not much to gain by having the programming language support a non-native data type, this idea was discarded.

This chapter describes the final ABI for the On Demand Control Processor.

# 4.1. Data Types

The Control Processor has 64 registers with a wordlength of 24 bits. The ILVY assembly language allows for 24- and 12-bit immediate values. See [Win05] for more information. The standard C data types are defined as follows:

| C Type    | Length  |

|-----------|---------|

| int       | 24  bit |

| short int | 24 bit  |

| long int  | 48  bit |

| char      | 24 bit  |

| float     | 24 bit  |

| double    | 48  bit |

Table 4.1.: Common C data types and their respective sizes on the Control Processor

Characters are represented by 24 bit. While this is inefficient, text processing is not the key field of application of the Control Processor. The Control Processor has no support for floating point operations; they have to be emulated in software.

### 4.2. Memory Layout

The data memory can be addressed in steps of 24 bits. Thus, all data structures should be aligned on 24 bit boundaries. Bytewise addressing modes have to be emulated by the compiler. Variables are stored at address port[0] and upwards, the stack is located at port[4095] and grows downwards.

Figure 4.1.: Data memory layout for the On Demand Control Processor

# 4.3. Register Usage

| Name    | Usage                            | Comments                   |

|---------|----------------------------------|----------------------------|

| r0      | function return value            |                            |

| r1-r6   | argument registers               |                            |

| r7-r14  | callee-saved registers           |                            |

| r15-r60 | caller-saved temporary registers |                            |

| r61     | frame pointer                    | (or callee-saved register) |

| r62     | stack pointer                    | (grows downwards)          |

| r63     | return address                   |                            |

Table 4.2.: The purpose of the Control Processor's registers

Register r0 holds the return value of a function. If the return value is larger than the size of r0, a pointer to a location on the stack is passed. The first six arguments are passed in registers r1-r6.

Starting at r7, there are 8 *callee-saved* registers. If a function wants to use these registers, it has to save them onto the stack and restore their original values before returning to the caller function.

The bulk of the registers, r15-r60 are *caller-saved* registers. They may get overwritten when a function is called. It is good practice to always have more caller-saved registers than callee-saved registers. To fully utilise the many registers of the Control Processor, an interprocedural register allocation mechanism would be of advantage. Unfortunately,

the GCC does not yet support this. Function inlining is one way to increase the register usage, but it also increases the code size significantly.

The *frame pointer* is stored in r61. It points to the beginning of the function stack frame and is used in the function epilogue to restore the original layout of the stack on function return. It may be omitted in some cases<sup>1</sup>, in which it is used as an additional callee-saved register.

The stack pointer marks the current bottom end of the stack, and is stored in r61.

Finally, the return address for the current function is passed in r63. This is the address of the instruction after the last function call.

# 4.4. Function Stack Frame

The first 6 function arguments are passed in r1-r6, all other parameters are pushed to the stack. In functions with variable numbers of arguments (such as ",..." parameters in C) these parameters are passed on the stack to ensure array-like behavior.<sup>2</sup>

Local Variables reside in temporary registers where possible, and are spilled to the stack when necessary.

Figure 4.2.: layout of the Function Stack Frame

$<sup>^1</sup> see$  the documentation of the GCC compiler switch <code>-fomit-framepointer</code>  $^2 see [Nil00] pg. 66f$

# 5. GNU Binutils

The GNU Binutils is a collection of utilities that operate on binary files. They include tools that are essential for building programs, like the GNU Assembler (gas) and the GNU Linker (1d).

| Subdirectory | Description                                               |

|--------------|-----------------------------------------------------------|

| bfd          | The BFD library - the basis of all the Binutils           |

| binutils     | A collection of various binary utilities, such as objdump |

| gas          | The GNU Assembler                                         |

| gprof        | The GNU Profiler                                          |

| ld           | The GNU Linker                                            |

| libiberty    | A tiny subset of the C standard library                   |

| opcodes      | The disassembler library                                  |

Figure 5.1.: The components of the GNU Binutils

The Binutils can be ported independently from the compiler and ideally two people or teams could work on the compiler and the binutils at the same time.