#### DISSERTATION

# SSA-Based Code Generation Techniques for Embedded Architectures

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

a.o.Univ.-Prof. Dipl.-Ing. Dr. Andreas Krall E185/1 Institut für Computersprachen

eingereicht an der Technischen Universität Wien Fakultät für Informatik

von

Dipl.-Ing. Dietmar Ebner Matr.Nr.: 9926321 Schlagergasse 6/15 A-1090 Wien

# Kurzfassung

Eingebettete Systeme sind in zahlreichen Gebieten wie Unterhaltungselektronik, mobile Kommunikation, Bildverarbeitung oder Fahrzeugbau längst allgegenwärtig. Entwickler sind heute mit Rechenanforderungen konfrontiert, die vor nicht allzu langer Zeit noch Stand der Technik im Supercomputing-Bereich waren. Immer kürzere Entwicklungszyklen bei gleichzeitig steigender Komplexität erfordern optimierende Übersetzer, die Hochsprachen möglichst optimal auf die jeweilige Zielarchitektur übersetzten.

Nahezu in jedem modernen Ubersetzer wird die Quellsprache zumindest an ausgewählten Punkten in eine Zwischendarstellung basierend auf sogenannter SSA-Form (static single assignment) transformiert. Dabei wird das Quellprogramm in eine Form gebracht, in der jede skalare Variable genau einmal im gesamten Programm definiert wird. Dadurch wird die Analyse und Verwaltung von erreichbaren Definitionen überflüssig und zahlreiche Analysen und Optimierungen werden erheblich vereinfacht. Bisher wurde SSA-Form hauptsächlich für maschinenunabhängige Optimierungen verwendet. Eine Reihe interessanter Eigenschaften macht sie jedoch auch zu einer vorteilhaften Basis für maschinenabhängige Codegenerierungstechniken. In dieser Arbeit werden im Speziellen zwei Teilprobleme betrachtet, die erheblichen Einfluss auf die Qualität optimierender Übersetzer haben: Instruktionsauswahl und Registerzuteilung. In beiden Fällen ziehen heute vorherrschende Techniken noch keinen Nutzen aus den Vorteilen von SSA-Form.

Die Aufgabe der Instruktionsauswahl ist es, die Zwischendarstellung des Übersetzters auf Instruktionen der Zielarchitektur in effektiver Art und Weise zu übersetzen. Eine weit verbreitete Technik dafür ist so genanntes Pattern Matching. Dabei wird der Befehlssatz der Zielarchitektur mit Hilfe mehrdeutiger Grammatiken modelliert. Diese werden verwendet, um eine kostenminimale Überdeckung des Eingabeprogramms in Form von Datenflussbäumen zu berechnen. Eine solche Überdeckung entspricht einer konkreten Auswahl von Instruktionen der Zielarchitektur. Traditionelle Techniken sind auf Datenflussbäume beschränkt. In den letzten Jahren wurden jedoch Ansätze vorgeschlagen, die es erlauben, die Techniken für ganze Funktionen mit im Allgemeinen zyklischem Kontrollfluss zu erweitern. Die verwendeten Muster müssen jedoch in einer Baumgrammatik vorliegen, in der jede Produktion eine einfache baumartike Struktur hat. Zahlreiche Instruktionen verbreiteter Architekturen können nicht mit derartigen Grammatiken modelliert werden. Diese Arbeit stellt eine Generalisierung bestehender Techniken vor, die es erlaubt, allgemeinere Graphgrammatiken zu verarbeiten um damit den Befehlssatz verbreiteter Architekturen vollständig zu beschreiben.

Das zweite in dieser Arbeit behandelte Optimierungsproblem ist Spilling – ein Teilproblem der Registerzuteilung. Ziel is es, die beliebig große Menge an temporären Variablen, die während der Instruktionsauswahl generiert wurden, einer endlichen Anzahl von Maschinenregistern zuzuordnen. Im Allgemeinen muss eine Teilmenge dieser Variablen in den Hauptspeicher ausgelagert werden. Dieser Vorgang ist in der Literatur unter dem Begriff Spilling bekannt und hat wesentlichen Einfluss auf das Laufzeitverhalten des erzeugten Maschinencodes aufgrund der hohen Speicherlatenzzeiten. Üblicherweise wird das Registerzuteilungsproblem erst nach Elimination der SSA-Form behandelt. Entwicklungen der letzten Jahre auf dem Gebiet der SSA-basierten Registerzuteilung ermöglichen jedoch eine getrennte Betrachtung der einzelnen Teilprobleme, insbesondere Spilling. Diese Arbeit stellt einen neuen flexiblen Ansatz für Spilling vor. Die neue Technik bietet wesentliche Vorteile, insbesondere für Architekturen mit sehr wenigen Registern.

Anstatt problemspezifischer Algorithmen werden beide betrachteten Teilprobleme mit Hilfe von allgemeinen kombinatorischen Optimierungsproblemen modelliert und gelöst. Im Fall der Instruktionsauswahl verwenden wir Partitioned Binary Quadratic Programming (PBQP) – ein generalisiertes quadratisches Zuordnungsproblem. Für das Spilling-Problem entwickeln wir ein Schnittproblem unter Nebenbedingungen, das so genannte Constrained Min-Cut (CMC) Problem. Beide betrachteten Probleme sind NP-vollständig. Nichtsdestotrotz zeigen Experimente mit umfangreichen Testprogrammen, dass beweisbar optimale Lösungen unter akzeptablen Zeitvorgaben berechnet werden können.

## **Abstract**

Embedded systems have become prevalent in various areas such as mobile communication, consumer electronics, image processing, and automotive. Often, the complexity of these systems has reached a point that would have been state-of-the-art in the supercomputing domain not long ago. With decreasing time-to-market cycles and increased software complexity, optimizing compilers that effectively translate applications written in high-level languages to a particular target platform have already become indispensable tools.

Almost all modern compiler infrastructures translate high-level programming languages at some point to an internal intermediate representation based on static single assignment (SSA) form. The main idea is to transform a program such that each scalar variable has exactly one definition in the program. Explicitly maintaining so-called usedef chains becomes dispensable and several traditional optimization and analysis passes simplify to a great extent. While SSA form has been traditionally used for high-level optimizations, it has some interesting properties that make it also a valuable tool for backend code generation techniques. In this thesis, we consider two subproblems that are vital for high-quality code generators: instruction selection and register allocation. In both cases, the prevalent techniques are based on traditional program representations that do not take advantage of SSA form.

Instruction selection aims to translate a compiler's intermediate code representation to a target-dependent form in a way that is efficient for a particular micro-architecture. A popular algorithmic approach is pattern matching: the target instruction set is modeled using ambiguous cost-annotated graph grammars such that a cover of the program represented in the form of data flow trees can be used to obtain a favorable and semantically equivalent machine representation. Previous work extends the scope of these techniques to the computational flow of a whole function using so-called SSA graphs. However, these techniques are confined to simple tree grammars where each production has tree structure. In this thesis, we show that numerous architectural features of popular embedded architectures cannot be modeled using tree grammars and present a generalization of previous work that is able to deal with generalized graph grammars.

The second subproblem considered in this thesis is spilling for programs in SSA form. Spilling is a subtask of register allocation, which aims to map an unlimited set of temporaries produced by the instruction selector to a finite set of machine registers. In general, a subset of these variables has to be deferred to main memory. This process is known as spilling in register allocation literature and has profound effects on the code quality of compilers for embedded systems due to large memory access latencies. Traditionally, compilers eliminate SSA form prior to register allocation. However, recent work shows that programs in SSA form have several interesting properties. In particu-

lar, these properties allow for a decoupled approach of spilling that is independent from the remaining register allocator. We propose a new approach to the spilling problem in the most-flexible spill-everywhere model and demonstrate its advantage compared to traditional heuristic techniques, especially for machines with few registers.

In both cases, the proposed techniques are based on a modeling of the problem in the form of generic combinatorial optimization problems. In the case of instruction selection, the underlying problem is partitioned binary quadratic programming (PBQP), which is a generalized quadratic assignment problem. Our approach to spilling is based on constrained min-cut (CMC) problems. In both cases, we proof that the underlying decision problem is NP complete. However, we present experimental evidence using major benchmark suites showing that algorithms delivering optimal or near-optimal results are feasible, even for very large programs.

## **Acknowledgments**

First of all, I want to thank my advisor Andreas Krall for his outstanding support during the last years. He motivated me to pursue a Ph.D. in this field and I owe him most of my knowledge about compilers and embedded systems.

Special thanks also belong to Bernhard Scholz from the University of Sydney. Almost all of the research work in this thesis has been done together with him and his excellent ideas and his enthusiasm often helped me through the hard times.

Thanks also to Christoph Keßler from Linköping University for reviewing this thesis. My thanks also belong to Jens Knoop, the head of the computer languages group, who has always been supportive and encouraging and who contributed invaluable contacts to the international scientific community.

Most of the work in this thesis was partially funded by the Christian Doppler Foundation, which is an excellent source of funding for application-oriented research. Thanks also to OnDemand Microelectronics for their input, their funding, and their contributions during our three-year research project.

Many people contributed to the instruction selector that is part of this thesis. Thanks to Peter Wiedermann, who was an exceptional masters student, for the port to LLVM. Thanks also to Albrecht Kadlec and Florian Brandner for helping out with the ARM grammar.

Last but not least, I want to thank Anna for the love she has given me, all my friends for the time we spent together, and my parents for their support during all those years.

# **Contents**

| 1 | Intr         | roduction                                    |  | -    | Ĺ |

|---|--------------|----------------------------------------------|--|------|---|

|   | 1.1          | The Embedded Computing Landscape             |  | . !  | 5 |

|   |              | 1.1.1 Types of Embedded Processors           |  |      | 3 |

|   |              | 1.1.2 Application Areas                      |  |      | 7 |

|   | 1.2          | Example Architectures                        |  | . 6  | 3 |

|   |              | 1.2.1 ARM                                    |  |      | 9 |

|   |              | 1.2.2 CHILI                                  |  | . 15 | 2 |

|   | 1.3          | The LLVM Compiler Infrastructure             |  | . 14 | 1 |

|   |              | 1.3.1 Overview                               |  |      | 1 |

|   |              | 1.3.2 LLVM Virtual Instruction Set           |  | . 1  | 5 |

|   |              | 1.3.3 Backend Infrastructure                 |  | . 1' | 7 |

|   | 1.4          | Preliminaries                                |  | . 18 | 3 |

|   |              | 1.4.1 Static Single Assignment Form          |  | . 18 | 3 |

|   |              | 1.4.2 Integer Linear Programming             |  | . 23 | 3 |

|   |              | 1.4.3 Network Flow Theory                    |  | . 23 | 3 |

| 2 | Part         | titioned Boolean Quadratic Programming       |  | 26   | ì |

| _ | 2.1          | Problem Definition                           |  |      |   |

|   | 2.1          | 2.1.1 Related Problems                       |  |      | - |

|   |              | 2.1.2 Complexity                             |  |      |   |

|   | 2.2          | Algorithms for $PBQP$                        |  |      |   |

|   |              | 2.2.1 Heuristic Algorithm                    |  |      |   |

|   |              | 2.2.2 Branch & Bound                         |  |      |   |

|   | 2.3          | Applications                                 |  |      |   |

|   | 2.4          | Experimental Evaluation                      |  |      |   |

| 3 | Cod          | de Generation for SSA Graphs                 |  | 43   | ) |

| J | 3.1          | Introduction                                 |  |      |   |

|   | $3.1 \\ 3.2$ | Related Work                                 |  |      |   |

|   | 3.2          | 3.2.1 RTL-Based Instruction Selection        |  |      |   |

|   |              |                                              |  |      |   |

|   |              | 0                                            |  |      |   |

|   | 2.2          | 3.2.3 PBQP-Based Instruction Selection       |  |      |   |

|   | 3.3          | Motivation                                   |  |      |   |

|   | 3.4          | Instruction Selection using Complex Patterns |  |      |   |

|   |              | 3.4.1 Identifying Patterns in SSA Graphs     |  |      |   |

|   |              | 3.4.2 Problem Transformation                 |  | . 5! | 1 |

| Contents | vii |

|----------|-----|

|          | V11 |

| 3.5 | Implementation Details                               |

|-----|------------------------------------------------------|

| 3.6 | Experimental Results                                 |

| Spi | ling in the Context of SSA-Based Register Allocation |

| 4.1 | Introduction                                         |

| 4.2 | SSA-Based Register Allocation                        |

| 4.3 | Motivation and Modeling                              |

| 4.4 | Constrained Min-Cut                                  |

| 4.5 | Lagrangian Relaxation                                |

| 4.6 | Experimental Evaluation                              |

| 4.7 | Related Work                                         |

| Cor | nclusions                                            |

# **List of Figures**

| 1.1  | Phase layout of optimizing compilers                                                                                                                | 2        |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2  | Schematic layout of a reference design for mobile multimedia decoding (SVENM)                                                                       | 9        |

| 1.3  | Developer board with multiple VLIW cores, peripherals, off-chip memory,                                                                             | 9        |

| 1.0  | and a general purpose control processor (ARM)                                                                                                       | 10       |

| 1.4  | Overview of the CHILI architecture                                                                                                                  | 12       |

| 1.5  | Overview of the <i>LLVM</i> compiler infrastructure                                                                                                 | 14       |

| 1.6  | Example LLVM bitcode corresponding to a simple c-function computing                                                                                 |          |

|      | a vector dot product                                                                                                                                | 16       |

| 1.7  | SSA form (right) for the program fragment to the left. So-called $\Phi$ - functions are used to disambiguate multiple definitions at join points in |          |

|      | the control flow graph                                                                                                                              | 19       |

| 1.8  | Example SSA graph for the control flow graph fragment shown Figure 1.7.                                                                             | 22       |

| 2.1  | Example $PBQP$ represented as a $PBQP$ -graph. The optimal solution is                                                                              |          |

|      | highlighted and has objective value 59                                                                                                              | 28       |

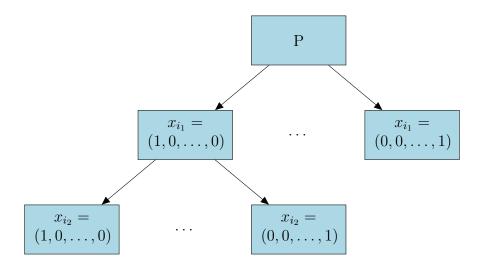

| 2.2  | A fragment of the search tree for a $B\&B$ based $PBQP$ algorithm                                                                                   | 34       |

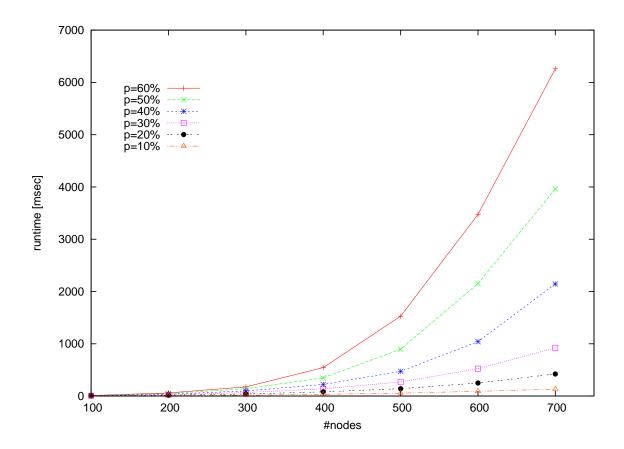

| 2.3  | Average runtime for the heuristic algorithm on a large set of randomly                                                                              |          |

|      | generated $PBQP$ problems for various densities                                                                                                     | 39       |

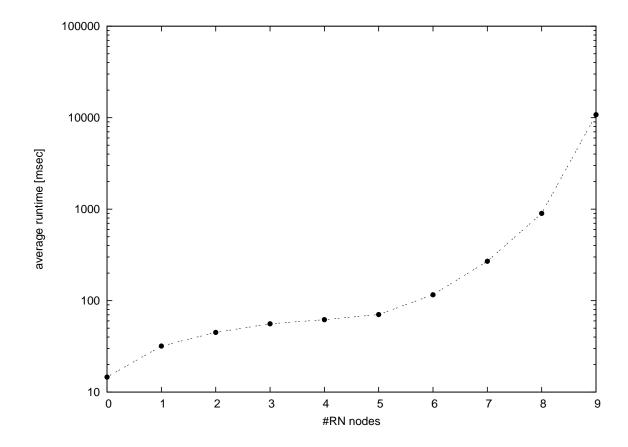

| 2.4  | Average runtime for the $B\&B$ algorithm compared to the number of irre-                                                                            |          |

|      | ducible nodes. Note the logarithmic scale on the y-axis                                                                                             | 42       |

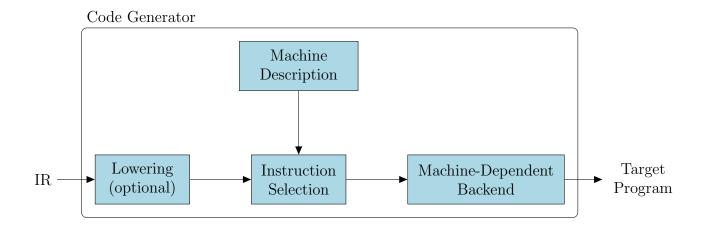

| 3.1  | An instruction selector translates a compiler's IR to a low-level machine-                                                                          |          |

|      | dependent representation                                                                                                                            | 44       |

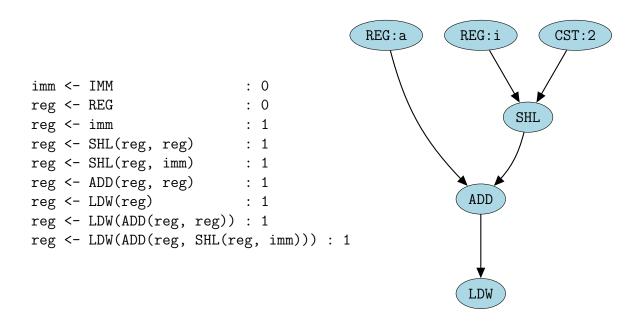

| 3.2  | Example of a data flow tree and a rule fragment with associated costs                                                                               | 46       |

| 3.3  | PBQP-instance derived from the example shown in Figure 3.2. The gram-                                                                               |          |

| 0.4  | mar has been normalized by introducing additional nonterminals                                                                                      | 49       |

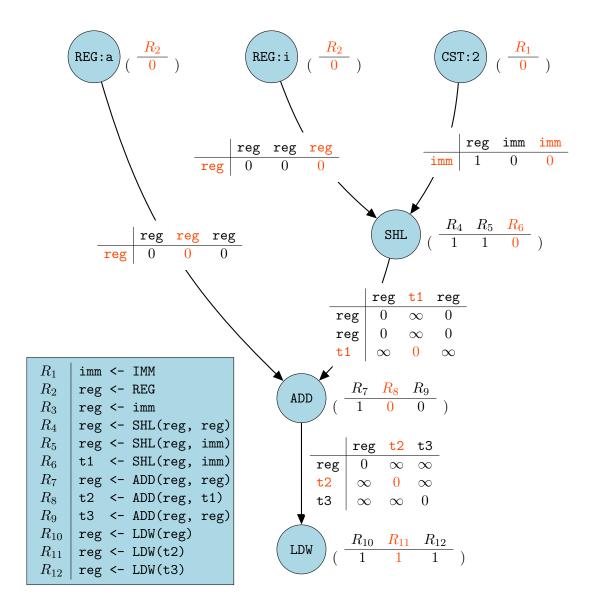

| 3.4  | Motivating example showing a number conversion route.                                                                                               | 50       |

| 3.5  | SSA-graph of the motivating example introduced in in Figure 3.4                                                                                     | 51       |

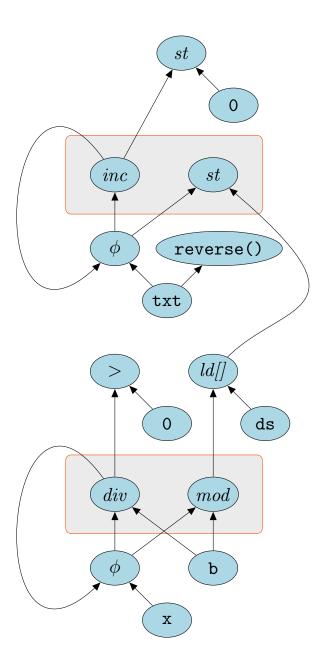

| 3.6  | Fragment of rules with complex patterns for div-mod and postincrement store instructions                                                            | 52       |

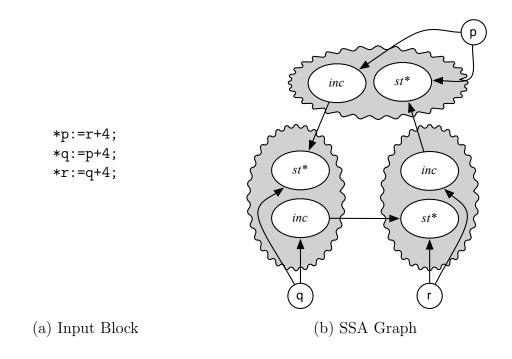

| 3.7  | Example: topology constraints.                                                                                                                      | 53       |

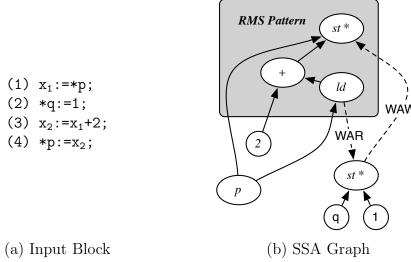

| 3.8  | Example: memory dependencies                                                                                                                        | 54       |

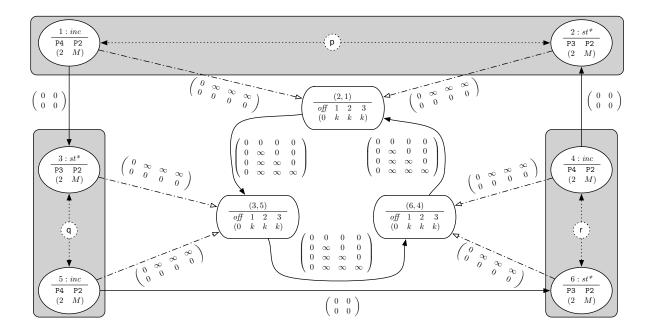

| 3.9  | PBQP graph for the example shown in Figure 3.7. We use $k$ as a short-                                                                              | <b>J</b> |

|      | hand for the term $3-2M$                                                                                                                            | 59       |

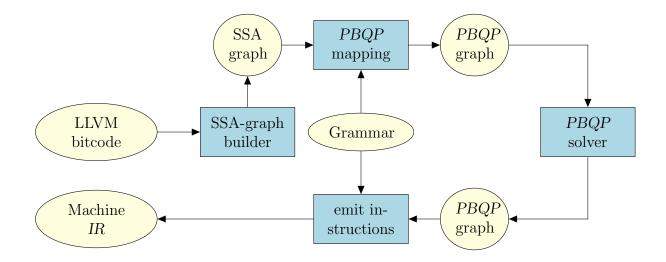

| 3.10 |                                                                                                                                                     | 60       |

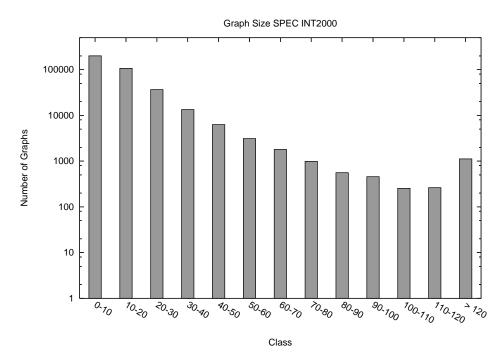

| 3 11 | Number of instances per graph size                                                                                                                  | 63       |

List of Figures ix

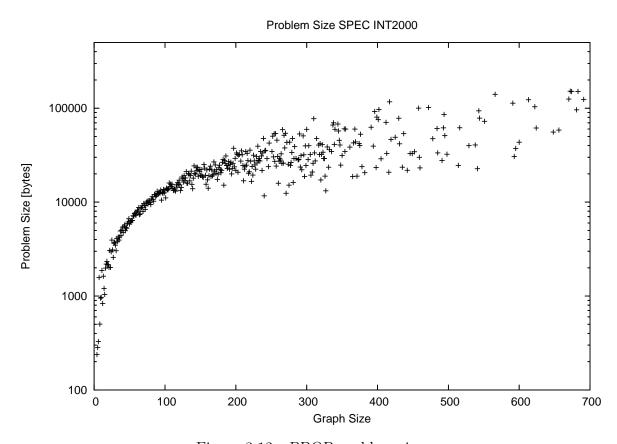

| 3.12 | PBQP problem size                                                                                                                               | 66         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|

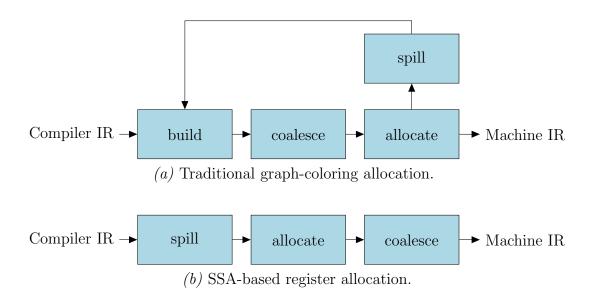

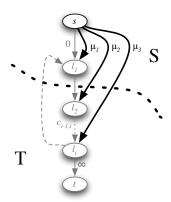

| 4.1  | Properties of programs in SSA form allow to execute the spilling phase only once (b) instead of the typical iteration scheme found in graph-    | <b>7</b> 0 |

|      | coloring allocators (a)                                                                                                                         | 72         |

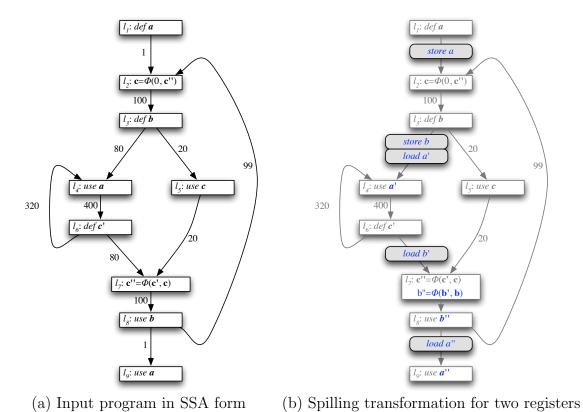

| 4.2  | Motivating example                                                                                                                              | 74         |

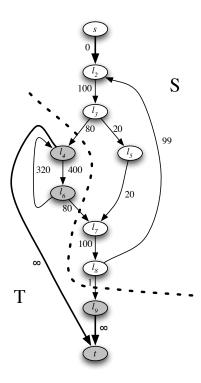

| 4.3  | Modeling for a single variable                                                                                                                  | 76         |

| 4.4  | Accounting for store costs                                                                                                                      | 77         |

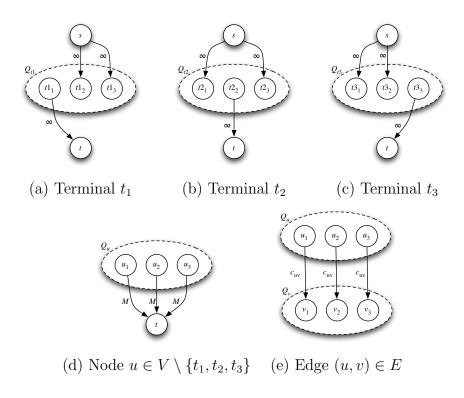

| 4.5  | Reduction of multi-way cut to CMC                                                                                                               | 79         |

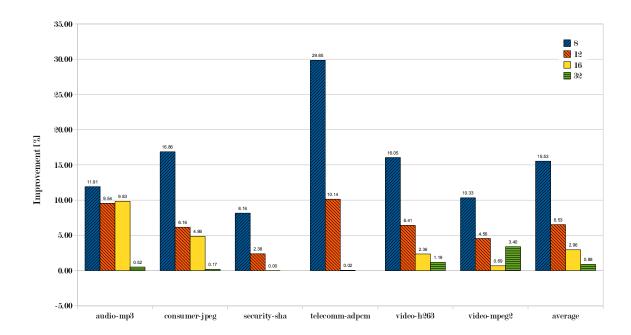

| 4.6  | Reduction of the relaxed problem $L(\mu)$ to a standard s-t min-cut instance.                                                                   | 82         |

| 4.7  | Improvement for a varying number of registers for spill code placement compared to the linear scan allocator of LLVM. Execution times have been |            |

|      | gathered using a cycle-accurate simulator for a 4-way VLIW processor                                                                            | 86         |

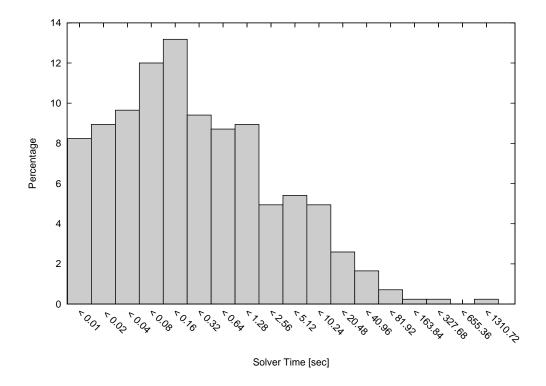

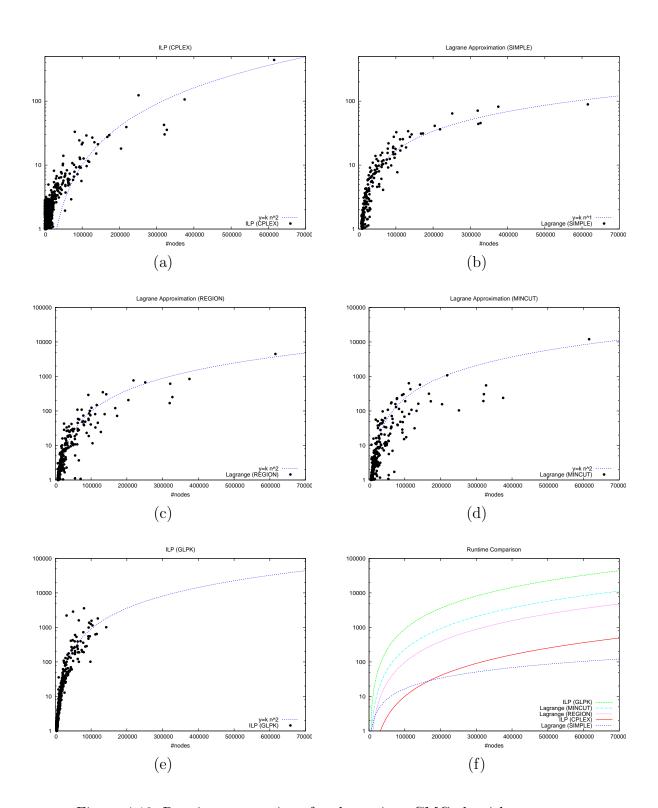

| 4.8  | Distribution of ILP solver times for SPECINT 2000 with 14 general pur-                                                                          |            |

|      | pose registers (ARM) using ILOG CPLEX 10                                                                                                        | 87         |

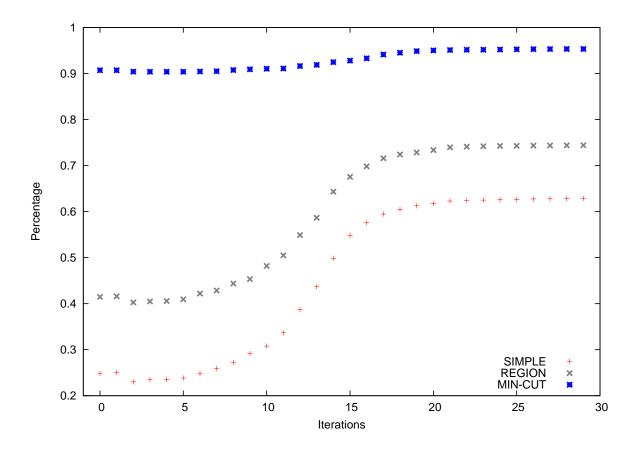

| 4.9  | Average quality of three different Lagrange heuristics compared to the precomputed optimal solution over the whole SPECINT 2000 benchmark       | ٠.         |

|      | set. The x-axis denotes the number of iterations for the subgradient                                                                            |            |

|      |                                                                                                                                                 | 00         |

| 4.10 | optimization algorithm                                                                                                                          | 88         |

| 4.10 | Runtime comparison for the various CMC algorithms                                                                                               | 90         |

## 1 Introduction

Embedded systems have become a prevalent part of our everyday life and it is very unlikely that this trend is going to decline anytime soon. In fact, general-purpose computing accounts for less than 1% of the microprocessors sold every year [Tur99]. The vast majority of microprocessors are employed in embedded applications accounting for about half of the annual microprocessor revenue. Application areas for those systems range from consumer electronics to the communications and automotive market, frequently imposing real-time requirements and heavy computational workloads.

As a consequence, demands imposed on embedded systems are fundamentally different from the general-purpose computing domain. Depending on the particular application area, energy requirements, production costs, or physical dimensions are often the determining aspects. On the other hand, common requirements from the general-purpose computing domain such as binary backward compatibility and standard compliance are much less of an issue. Embedded systems are often designed to run a single application for their entire live range. These applications are tailored to the underlying hardware. Instead of binary compatibility, embedded system designers are thus more concerned with source code and tool compatibility. Thus, the compiler becomes a critical tool gluing more and more complex applications written in high-level languages to specialized target architectures.

At the same time, applications such as media processing impose computational workloads that stretch system capabilities to their limits. Traditional superscalar techniques require for a 2-3x speedup in performance very roughly an increase of about 80x in area and, maybe even more important, about 12x in power consumption [KTJR05]. For numerous mobile applications with critical energy and cost requirements, this is a cost too high to bear. Embedded system designers thus frequently employ application specific accelerators and simple explicit parallel RISC architectures. The latter architectural paradigm –  $\underline{V}$ ery  $\underline{L}$ arge  $\underline{I}$ nstruction  $\underline{W}$ ord ( $\underline{V}$ LIW) – originated in the supercomputing domain and gradually found its way into today's embedded system architectures, e.g., ST2xx, TI C6xxx, NXP TriMedia. For those systems, the burden to effectively discover and exploit  $\underline{I}$ nstruction- $\underline{I}$ evel  $\underline{I}$ parallelism ( $\underline{I}$ LP) is solely left to the compiler, thus emphasizing the vital role of optimizing compilers for embedded systems.

While both the superscalar and *VLIW* paradigm have their advocates, it is often overlooked that the complex problems in analyzing and exploiting the available parallelism is common to both architectural styles. Thus, compiler complexity depends rather on the amount of *ILP* that has to be obtained than on the particular architectural style [FFY05]. The main difference is that *VLIW* architectures usually make more fine grained parallelism practical.

Today, compilers mainly rely on highly tuned and computationally efficient heuris-

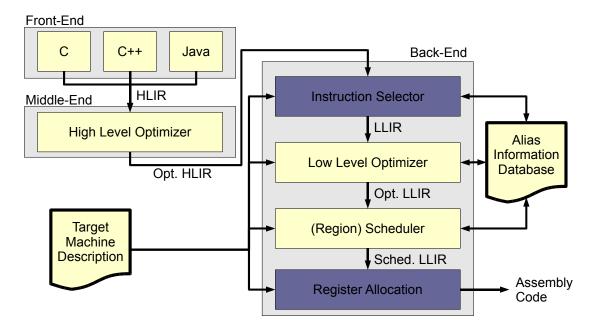

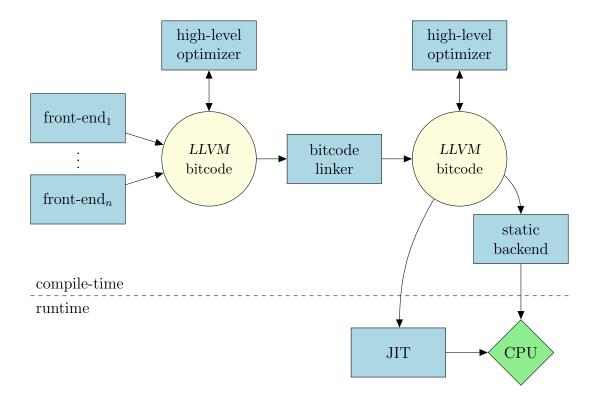

Figure 1.1: Phase layout of optimizing compilers.

tics that produce reasonably good code quality in a short amount of time. However, in the context of embedded systems where application-specific extensions and architectural variants are employed to tune those systems for a single or a small number of applications, compilers have to fulfill additional requirements that are hard to meet using heuristic approaches. First, hardware architectures and application-specific extensions usually evolve much faster than the corresponding compilers. Therefore, easily retargetable backends that are capable to cope with architectural peculiarities and asymmetries are required. Second, heuristic techniques often fail to effectively exploit architectural features requiring significant amount of engineering to tune applications to a particular hardware platform.

Optimizing compilers are huge and complex software projects, e.g., recent versions of gcc contain about 1.2 million lines of C-code, disregarding the large C++ and Java runtime libraries. Modern compilers are composed of several components, each of them operating on different intermediate representations of the original source code; see Figure 1.1. The front-end is responsible to transform the input program into a high-level intermediate representation that is largely independent of the particular source language. So-called high-level optimizers perform the traditional set of scalar and loop optimizations, do function inlining and cache re-organizations, and remove dead code and redundant computations. Some compilers go through various forms of high-level intermediate representations with decreasing abstraction level. Finally, the back-end is responsible to convert the source and target independent intermediate representation into machine-dependent instructions, perform target-dependent optimizations and code re-organizations, and to do static instruction scheduling and register allocation.

As depicted in Figure 1.1, most compiler backends are structured into several phases that concentrate on a particular subproblem, e.g., instruction selection, register allocation, or scheduling. This approach, which we follow in this thesis, is beneficial from a software engineering point of view as it allows for a separation of concern. Also, with most of these subproblems being NP complete in general, performance requirements are an even stronger argument for this separation. However, it is important to note that these advantages come for significant costs. Interdependencies among the particular phases are usually ignored, leading to suboptimal code. This dilemma – known as phase ordering problem – is difficult to resolve since several phases have conflicting goals. One prominent example are interdependencies among scheduling and register allocation. Allocating machine registers to program variables introduces additional "false" dependencies that limit the freedom for the instruction scheduler. On the other hand, scheduling may overlap otherwise independent live ranges and thus increase the register pressure, which may lead to additional spill code. Likewise, there are interdependencies among instruction selection and scheduling as the costs of a particular instruction in general depend on interference and resource constraints imposed by a particular schedule.

One approach proposed in literature is to account for phase ordering issues heuristically, e.g., Goodman and Hsu [GH88] propose different scheduling techniques that favor pipeline delays and register demand respectively and that are applied dynamically according to the estimated register pressure. Similar but more sophisticated techniques have been proposed more recently by Norris et al. [NP98]. Another approach is to combine several phases to a single optimization problem. Bednarski and Keßler [BK04, KB06] propose dynamic programming for combined instruction selection, scheduling, and register allocation. Likewise, both Wilson et al. [WGB94] and Chang et al. [CCK97] propose techniques that simultaneously perform these subproblems using integer linear programming. However, for large programs, the complexity of the formulations results in prohibitively high computation times. Despite significant amount of research, phase ordering issues are thus still considered to be an open research question.

Most modern compiler frameworks transform intermediate code, at least at some stage in the compilation process, into so called static single assignment (SSA) form [CFR<sup>+</sup>91a]. The basic idea which was proposed by researchers from IBM in the late eighties is to transform a program such that each scalar variable has exactly one point of definition in the program. Thus, explicitly maintaining use-def chains is dispensable and several traditional optimization and analysis passes simplify to a great extent. While SSA form has been traditionally used for high-level optimizations, it has some interesting properties that make it also a valuable tool for backend code generation techniques.

In this thesis, two subproblems of code generators are considered: instruction selection and spilling. The corresponding stages in the phase diagram are highlighted in purple in Figure 1.1. While those are very different problems in general, there are two important characteristics in the approach presented in this thesis that are common to both:

1. Both techniques are based on properties for programs in SSA form and can be

used to maintain SSA form until late in the compilation process.

2. While traditional techniques are based on problem specific heuristics, we use in both cases a reduction to general combinatorial optimization problems. This allows us to exploit well-known results from graph theory and to apply generic solver libraries for different subproblems.

#### **Contributions**

The contributions of this work are two-fold. First, we propose new SSA-based algorithms for two important subproblems of optimizing compilers: instruction selection and spilling. For the instruction selection problem, we propose a generalization of previous work that allows to use general graph grammars instead of tree grammars for the modeling of the target architecture. For the spilling problem, we introduce a new mathematical formulation for the most-general spill-everywhere model and develop effective algorithms that deliver optimal or near-optimal solutions. For both techniques, we present experimental results that show significant improvements compared to previous techniques. Experiments with large benchmark sets show that our techniques scale even to very large programs. We consider two example architectures representing different architectural paradigms from the embedded systems domain, i.e., an embedded VLIW architecture designed for video and audio decoding and a traditional ARM core as representative for simple RISC architectures.

The second major category of contributions in this work are theoretical results for the underlying combinatorial optimizations problem. We implement and extend previously proposed algorithms for the so-called partitioned binary quadratic programming problem. The work for spilling is based on a new variant of the well-known min-cut problem with additional side constraints. We present an exact ILP formulation and a Lagrange relaxation that is used to guide simple greedy heuristics towards the optimal solution. Both problems are NP complete. Nevertheless, optimal solutions can be found within reasonable time limits, even for very large programs.

#### Guide to this Thesis

Chapter 1 gives a short introduction to embedded systems and compilers, in particular LLVM [LA04] which is used throughout this thesis for the evaluation of the proposed techniques. Preliminaries for the remaining chapters and summaries of results that are important for the rest of the thesis are given in Section 1.4. Chapter 2 introduces partitioned binary quadratic programming (PBQP) – a generalized combinatorial optimization problem that is used later on as an algorithmic vehicle for the instruction selection problem. Several algorithms are presented and evaluated for problem instances from various applications such as address mode selection, register allocation, and instruction selection. We present a new approach to generalized instruction selection that is able to cope with complex machine instructions in Chapter 3. The problem is solved by reducing the problem of matching SSA graphs with generalized graph grammars to

PBQP. We hereby achieve both improved code quality and improved retargetability to new architectures or variants. The latter is achieved by supporting more expressive graph grammars that are flexible enough to describe popular embedded instruction set architectures to their full extend. Chapter 4 summarizes recent advances in SSA based register allocation and presents a new formulation of the spilling problems to the so-called constrained min-cut problem. The latter is a special variant of the well-known min-cut problem with additional knapsack constraints. We implemented and evaluated several algorithms and present results for two examples of real-world architectures using major benchmark suites. Conclusions and an outlook to future work is given in Chapter 5.

## 1.1 The Embedded Computing Landscape

Embedded Computing is a very wide field stretching from tiny 8-bit micro-controllers to full-featured parallel RISC architectures for mobile multimedia applications. Lifetimes span from less than a year for average mobile phones to often more than thirty years for infrastructure such as telephone switches. Consequently, there is no sharp definition that distinguishes embedded systems from general-purpose computing. As a result, most definitions found in literature characterize embedded systems by what they are not rather than what they are.

One of these features that distinguish embedded computing is the lack of versatility. Usually, embedded devices serve few or even only a single purpose. Software is often closely tied to the hardware and pre-installed by the manufacturer with no or only limited ways of changing it, e.g., firmware upgrades. However, this distinction becomes more and more fuzzy with PDAs and mobile phones capable to execute third-party applications and Java bytecode.

Another characteristic property that is typical for embedded systems is the lack of binary backward compatibility. In the general purpose computing, strict binary compatibility has been the only viable path to commercial success. This is hardly an issue in the embedded domain. Developers are willing to adopt and recompile the application for each new product generation. Many systems are built using very simple operating systems that are closely tied to the underlying hardware or even no operating system at all. However, with rising complexity of the applications used within embedded systems, rewriting the whole software stack for each hardware generation becomes quickly infeasible. Thus, compilers and tools form the compatibility layer that matters most for embedded system development.

A very informal but probably the most concise definition for embedded systems is in terms of their intended *use*. Usually, embedded devices are commodities that serve a particular purpose that is very different from "computing". This is also the main reason for the very different requirements imposed on embedded systems. While higher performance is almost always an appealing goal in the general-purpose computing domain, this is not necessarily the case for embedded applications. The main goal is to be as fast as necessary using the minimum amount of resources possible. Apart from produc-

tion costs, mobile applications are also often constrained by two more aspects that are hardly an issue for general purpose computing, i.e., energy demand and physical dimensions. For several applications such as mobile communications or mobile multimedia processing, these are usually the determining "performance" criteria rather than raw computational power.

#### 1.1.1 Types of Embedded Processors

Processing cores used in embedded systems are usually divided into four main categories that range from very small serial controllers to full-blown micro-processors. In increasing complexity, these categories can be summarized as follows:

- 1. Microcontrollers These cores are commodity components that can be found in almost all electronic devices. Usually, they include small memories, I/O buses, and peripherals and are based on very simple 8- or 16-bit microprocessors.

- 2. **Digital Signal processors (DSPs)** These are processing units built for very special compute-intensive loop-oriented kernels. They are designed with a small family of signal processing algorithms in mind and are optimized for very efficient arithmetic operations. Usually, full floating arithmetic is replaced with simple fixed-point representation. Special instructions, e.g., multiply-accumulate, are very common to allow for efficient implementation of common vector and matrix operations such as dot products.

- 3. Embedded General-Purpose Microprocessors These are often general purpose processor designs or scaled-down versions of former architectures from the general purpose domain such as ARM, MIPS, PowerPC, or Motorola 68K. Characteristics are 32-bit datapaths, complete and standardized instruction set architectures, and relatively large external memories. Most of these processors are sold in the form of *soft-cores*, i.e., licensed building blocks that are combined by the application designer to larger systems-on-a-chip (SoCs).

- 4. Computational Microprocessors These are devices that can be found in highend portable devices and are usually close descendants of full-featured workstation designs such as PowerPC, SPARC, or Alpha. With companies such as VIA and Intel entering the embedded market with specialized micro-architectures for x86, their adapted designs also fall into this category, e.g., VIA Nano, Intel Atom. They adopt full 32 or 64-bit datapaths and are usually combined with peripherals and memory management units in order to support full-featured operating systems. Application areas are commodity devices such as PDAs or netbooks.

Traditionally, DSPs have been the fastest growing sector in the embedded semiconductor market. Modern designs found in applications such as mobile communication, filtering, audio compression, or signal synthesis, combine one or more traditional DSPs with general-purpose microprocessors. DSPs hereby often execute a single program on a

stream of data. The irregular datapaths and designs make it hard to compile high-level programs efficiently. Thus, even today, it is not uncommon to develop code in assembly language, which is a very cost and labor intensive endeavor. Thus, several analysts predict that classic DSPs will migrate into designs that are much closer to general purpose microprocessors and VLIW designs.

The techniques proposed in this thesis mainly apply to the last two groups of processing cores: computational microprocessors and embedded general-purpose microprocessors. However, the borders to classical DSPs become more and more blurred and some techniques might also be relevant for this field. This is true especially for the part on instruction selection where the additional flexibility compared to traditional techniques might help to cope with the irregularities found in typical DSP designs.

#### 1.1.2 Application Areas

In this section, we briefly summarize a rough taxonomical characterization for 16-bit and wider architectures based on their application area as given by Fisher et al. [FFY05]. The authors identify three major embedded computing markets with distinct requirements:

- 1. Image Processing and Consumer Electronics This market is among the fastest growing segments of embedded computing and includes consumer electronics such as printers, digital cameras, and (mobile) video and audio devices. These devices operate on digital media, which is today comprised of huge amounts of data that has to be transferred and processed within embedded systems. Most systems thus employ embedded general purpose microprocessors with a large amount of RAM and fast memory connectors. The high computational requirements of modern digital video codecs such as H264 or VC-1 requires significant computational power. Several companies such as ST Microelectronics or Texas Instruments thus offer specialized designs based on VLIW principles with special accelerator units and large memory bandwidth. Consumer electronics are high-volume commodities that have to cope with huge cost pressure and often sell for less than the cheapest computational microprocessor available. This fact as well as size and power constraints are important factors for the choice of microprocessors in this field.

- 2. **Communications** This is a very diverse market ranging from wired and cellular phone network infrastructure to mobile cellular phone handsets and networking infrastructures such as routers. All this application have very different requirements and characteristics.

Wired and mobile phone infrastructure has to support a huge number of relatively low bandwidth clients, summing up to vast data rates. Additionally, wired networks are based on analog signal transmission, requiring the analog-to-digital and digital-to-analog conversion in the data center. On the other hand, cellular networks are based on various digital encoding and protocol techniques such as GSM or UMTS.

Even larger data rates can be found in typical network backbones. A typical router has about 32 interfaces with a bandwidth of about 10 Gbit/s each, translating to several hundred million routing decisions per interface on smaller package sizes. Routing decisions are based on so-called routing tables with about 50.000 to 100.000 entries. Almost all components exceed the capabilities of general purpose microprocessors. Thus, systems are usually based on customized processors, so-called application specific integrated circuits (ASICs), or field-programmable gate arrays (FPGAs).

A very different set of characteristics can be found in cellular phone handsets. These systems are usually based on a combination of general purpose microprocessors and DSPs, e.g., Texas Instruments OMAP series. Processors traditionally run on relatively low clock rates of a few hundred MHz and include a relatively small number of RAM. This trend has changed with recent developments in the smartphone market where more powerful systems are adopted that can be used to drive built-in digital cameras and multimedia decoders. A limiting factor in this market is energy consumption. Typical standby power is a few milliwatts while transmission power rises drastically to several hundred milliwatts.

3. Automotive The use of embedded microprocessors in the automotive market has grown dramatically in the last decade. Today, it is not uncommon to find between 50 to 100 processors in a single vehicle. These chips are used for a wide range of applications such as controlling, safety features, instrumentation, and entertainment. Consequently, different architectural styles are used. Fault tolerant low level real time systems are often based on DSPs or simple RISC microprocessors. High-end microprocessors are usually based on traditional RISC architectures such as PowerPC and are designed for relatively low frequencies.

A distinguishing characteristic of the automotive market is the high degree of integration among the different subsystems, e.g., self-diagnostic and reporting, sensor networks, or controlling. Individual components, so-called "smart-nodes", hook up to standardized communication systems such as CAN or FlexRay.

## 1.2 Example Architectures

The techniques presented in this thesis have been evaluated using two example architectures for embedded general purpose microprocessors. One of which is ARM, a simple 32-bit RISC core that is by far the most widely used architecture in the mobile electronics market. The second architecture, OnDemand CHILI, is a representative for explicitly parallel VLIW architectures that are frequently found within numerically intensive applications such as video en-/decoding.

Embedded processors are hardly sold on their own. Instead, multiple processing cores along with external memories and peripherals are combined to a single system-on-a-chip (SoC). A reference design for such a system for mobile multimedia applications is shown

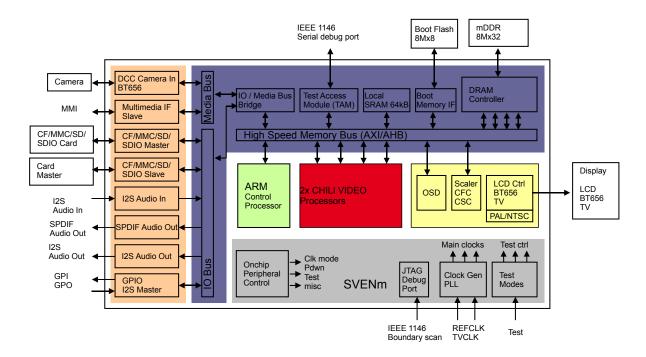

Figure 1.2: Schematic layout of a reference design for mobile multimedia decoding (SVENM).

in Figure 1.2. The system combines an ARM control processor capable to drive full-featured operating systems such as Linux with two CHILI *VLIW* cores that are used to run computationally intensive video decoders such as H264. There is a small amount of on-chip core memory on each of the VLIWs and all the processing cores are connected to a global mobile DRAM controller. Additionally, there is a large number of peripheral controllers and interfaces such as audio and video connectors, flash memory controller, and debug interfaces. A picture of the reference design shown in Figure 1.2 in real silicon is given in Figure 1.3<sup>1</sup>.

#### 1.2.1 ARM

ARM processors today account for approximately 90% of all 32-bit microprocessors found in embedded systems. The architecture has been developed by ARM Ltd. – a spin-off of Acorn Computers founded in the late nineties. It is important to note that ARM Ltd. does not fabricate real silicon itself but licenses ARM cores to semiconductor partners that include them into customized SoCs.

Basic Architecture ARM is a simple 32-bit Von Neumann architecture featuring 16 general purpose registers (two of which are reserved for the stack pointer and link register and r15 denotes the program counter). A so-called program status register (CPSR)

<sup>&</sup>lt;sup>1</sup>Image included with permission of OnDemand Microelectronics

Figure 1.3: Developer board with multiple VLIW cores, peripherals, off-chip memory, and a general purpose control processor (ARM).

reflects the current processor state. There are four condition code flags (negative/zero result, carry, overflow) that allow for conditional execution of instructions. This can be used to improve code density and to reduce the number of branch instructions using if-conversion, i.e., the conversion of control into data dependencies by the compiler. Dedicated flags are used to enable/disable interrupts and switch among two operations modes, i.e., ARM mode and Thumb mode.

**ARM Mode** In ARM mode, all instructions are 32-bit wide and have to be word aligned. All instructions have full access to the available general purpose registers. Instructions can be executed conditionally by post-fixing them with the corresponding condition code field. A special field (signify bit) in the instruction word defines if data processing instructions affect the processor status word.

ARM Thumb Mode Thumb mode has been introduced to improve code density for compiler generated code (marketing data claims code size reductions of about 65%). ARM Thumb is a 16-bit instruction set implementing only a subset of the functionality available in ARM mode. A special branch instruction (bx) can be used to switch among the two operation modes. For most instructions, one source and the destination register have to be identical. With few exceptions, instructions are only allowed to address the lower half of the register file.

|           |                              | $[, \#\pm < imm12>]!$            |

|-----------|------------------------------|----------------------------------|

|           | $LDR STR \{B\} < Rd>,$       | $[, \pm ]!$                      |

| pre-      |                              | $  (, \pm   \# ]!  $             |

| increment |                              | $[, \#\pm < imm8>]!$             |

|           | $LDR STR \{H SH SB\} < Rd>,$ | $[, \pm ]!$                      |

|           |                              | [ <rn>], #± <imm12></imm12></rn> |

|           | $LDR STR \{B\} < Rd>,$       | $[], \pm $                       |

| post-     |                              | $[], \pm   \#$                   |

| increment |                              | [ <rn>], #± <imm8></imm8></rn>   |

|           | $LDR STR \{H SH SB\} < Rd>,$ | $[], \pm $                       |

Table 1.1: Available ARM pre-/postincrement addressing modes with implicit address calculation.

A major adjustment has been proposed in 2003 with the introduction of Thumb-2. The instruction set extends the Thumb mode with some additional 32-bit instruction and can be seen as a compromise between ARM and ARM Thumb mode with the goal to achieve both high code density and decent performance.

The Barrel Shifter The 32-bit barrel shifter is only available in ARM mode and can be used without performance penalty in combination with most arithmetic instructions and address calculations. The shift amount can be specified either using a 5-bit immediate value or using the least significant byte of an additional source register. The operation can be a logic or arithmetic shift operation or a rotate right operation (with and without carry bit).

Addressing Modes Powerful indexed addressing modes are available for both load and store operations. There are variants operating on signed/unsigned bytes, half-words, or words. Addresses are specified using a base register plus an optional offset, which can either be added to or subtracted from the base registers. The offset can be a register optionally shifted by an immediate value or an unsigned 12-bit immediate. For half-word and signed half-word/byte operations, the offset is restricted to 8-bit immediates or an unshifted register. Additionally, ARM supports a large range of pre- and post-increment addressing modes with implicit address calculation; see Table 1.1.

**Core Extensions** The ARM architecture has gradually evolved from the early ARM1 series to ARM11 and, most recently, the ARM Cortex family. Discussing the differences among all the available variants is beyond the scope of this work, but there is a number of widely-used core extensions that are important in practice.

Many embedded applications do not require floating point at all and are based on (saturated) integer arithmetic. For those that do, several instruction set extensions are available that provide full single and double precision IEEE 754 floating point arithmetic.

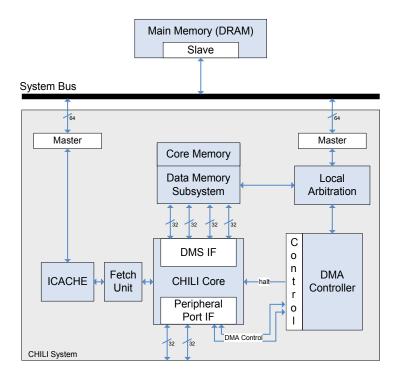

Figure 1.4: Overview of the CHILI architecture.

The most popular of which is VFP, which even supports short vector instructions.

Another core extensions is an advanced 128-bit SIMD (single instruction multiple data) unit marketed under the term *NEON*. It features a separated register file and additional functional units that support integer and single-precision floating point operations from 8 to 64-bits, processing up to 16 operations in the same cycle. The primary market for NEON are mobile media and signal processing applications.

Further extensions such as *TrustZone* are found in a few variants only and target niche markets with security-sensitive applications.

#### 1.2.2 CHILI

The CHILI processor is a good example for wide-issue *VLIW* cores that are popular for media processing applications with high computational requirements. The architecture has been developed by OnDemand Microelectronics, an Austrian start-up company, and features 4 parallel execution units. Each slot has access to an unclustered general purpose register file offering 64 32-bit registers. The instruction set is a general load/store RISC architecture extended with a small number of general purpose instructions for multimedia processing and limited support for SIMD processing.

A block diagram for the CHILI architecture is given in Figure 1.4. As common for VLIW architectures, encoding and instruction memory bandwidth is a critical issue. Thus, each processing core is connected to a relatively large instruction cache that is managed by a dedicated fetch unit, which pre-fetches and aligns instructions from main

memory. Each core has a small on-chip memory (SRAM) and is connected to a DMA controller using a peripheral port interface.

Memory Subsystem The CHILI core is split into the processing core and the data memory subsystem (DMS). The latter is responsible for DMA transfers among core memory and external DRAM and provides non-blocking memory accesses for the processing core, i.e., an issued load instruction does not stall the processing core unless the value is actually required to proceed with the calculations. This allows to pre-fetch required values from slow external memories while the core is busy with other operations and helps to hide the long access latencies. Each load and store operation supports direct addressing modes using a register or a fully qualified 32-bit immediate value as value as register indirect addressing modes. In the latter case, the offset can be specified using another source register or a 32-bit immediate value. The DMS allows transparent access to off-chip external memories. However, in general it is more efficient to transfer larger blocks to the core memory using the DMA engine, which is controlled using a peripheral port interface.

Conditional Execution Most existing general purpose architectures have either only partial support for predicated execution (mostly restricted to conditional moves, e.g., DEC Alpha, Sun Sparc v9) or nullify the result based on the value of an additional boolean source predicate (Itanium, ARM), which has to be evaluated beforehand. The CHILI differs from these architectures in that conditions are evaluated alongside to the instruction to be predicated within the same bundle. Therefore, the full range of binary comparisons is provided in addition to special test instructions that evaluate to true if a particular bit is set or unset respectively. However, these computations require an additional slot in the instruction word. In particular, even slots can be used to evaluate the predicate for the instruction in the directly succeeding slot. The only exception are currently load and store instructions, which cannot be executed conditionally. If multiple instructions are defining a register within the same bundle, the value produced in the slot with the highest index is kept.

**SIMD Extensions** CHILI's SIMD extensions allow to perform parallel 8-bit and 16-bit arithmetic on each of the processor's 32-bit wide execution units. This allows to execute up to 16 8-bit operations and up to 8 16-bit operations in a single cycle. Special permute instructions can be used to efficiently pack and unpack values into registers. Permutations can either be specified using immediate values or can be programmed using special permute registers that can be loaded using dedicated instructions. These extensions are especially valuable for video and audio decoding algorithms that often operate on vectors of 8-bit values.

**Instruction Set Extensions** Apart from the SIMD extensions, there are some additional instruction set extensions that are uncommon for RISC machines and which are mainly heritages from the DSP world. These instruction include multiply-accumulate

Figure 1.5: Overview of the *LLVM* compiler infrastructure.

operations, clip instructions that can be used to enforce upper and lower bounds, or sum of absolute differences, which is very common within signal processing algorithms. Furthermore, there are specialized instructions for alignment and rounding and for counting of leading zeros/ones. All of which have applications in the architecture's target market.

## 1.3 The LLVM Compiler Infrastructure

This section gives a short introduction to the LLVM compiler infrastructure – a modern, open source compiler framework that originated at the University of Illinois and that served as the framework for the experimental evaluation of the techniques proposed in this thesis.

LLVM is an acronym for "low-level virtual machine" and is both a well-defined virtual instruction set as well as a set of components that can be used to build various tools such as static code generators, just-in-time translators (JITs), static code analyzers, or dynamic simulators.

#### 1.3.1 Overview

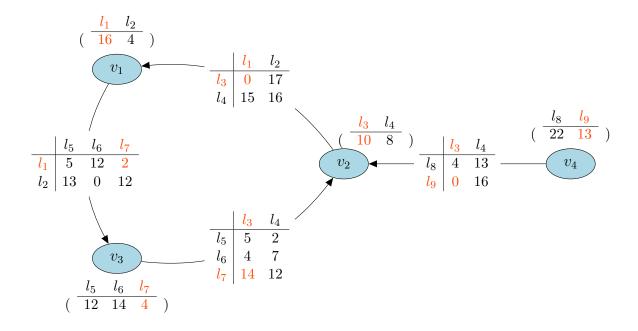

LLVM is based on a modular design of loosely coupled libraries that operate on a well-defined intermediate representation. The main purpose of LLVM is the development of

static and dynamic compilers. Figure 1.5 show the basic structure of code generators based on LLVM. Various front-ends translate high-level languages such as C, C++, Objective C, or Fortran into so-called LLVM bitcode. In addition, there are active projects implementing LLVM front-ends for virtual machine languages such as Java Bytecode or Microsoft's CLI. At the time of writing, the main front-end for LLVM is based on the gcc compiler infrastructure and translates gcc's intermediate representation (GIMPLE) into LLVM bitcode. This is a relatively simple task and abstracts away much of the complexity of dealing with the various source languages. Most features of modern high-level programming languages are hereby lowered to very simple constructs.

LLVM bitcode serves as both input and output format for various readily available analysis and optimization passes. This includes most of the traditional scalar optimizations, loop transformations, code motion and redundancy elimination, and sophisticated analysis passes such as alias analysis or loop dependence tests. Theses optimizations can be applied in the traditional way separated to each translation unit. Alternatively, the design of LLVM allows for transparent link-time optimizations by linking LLVM bitcode modules together before optimizations are applied.

The backend infrastructure permits code generation ahead-of-time as well as during runtime. The latter allows to ship LLVM bitcode files instead of machine dependent binaries. These can be translated for a particular machine on-the-fly (JIT) or on the first execution (install-time optimization). Furthermore, there is limited support for profile-guided optimizations, i.e., training data is used to gather additional information for a particular application that can be used to improve the code quality of a subsequent translation pass.

#### 1.3.2 LLVM Virtual Instruction Set

The intermediate representation used by LLVM modules is a fully-typed RISC-like virtual instruction set. In contrast to many other compiler infrastructures, there is no hierarchy of intermediate representations with varying abstraction level. Instead, all analyzers and optimization passes operate on the same representation, which is light-weight and low-level while being rich enough for most interesting tasks. The language is universal in that it is independent of the particular source language and comes with its own basic type system.

It is important to note that LLVM bitcode is fundamentally different from virtual machines such as Java bytecode or CLI. First, LLVM bitcode is *not* target machine independent. Peculiarities defined by the particular application binary interface (ABI) or by the target machine such as alignment, mapping of high-level types, or calling conventions, are explicitly represented by the front-end. Thus, object code represented by LLVM bitcode is not portable from one architecture to another in general. Another characteristic that distinguishes LLVM bitcode is the lack of features such as garbage collection, that one would expect from virtual machines. However, it is possible to implement those features on-top of LLVM.

LLVM bitcode can be represented in one of different forms, all of which are semantically equivalent. First, there is an in-memory compiler intermediate representation

```

float

define float @dot_product(float * %a,

float * %b,

dot_product(float *a,

i32 %n) nounwind {

float *b.

unsigned n) {

entry:

br label %bb1

float sum = .0 f;

unsigned i;

; preds = \%bb1

for (i=0; i < n; ++i)

bb:

sum += a[i] * b[i];

\%0 = \mathbf{getelementptr} \ \mathbf{float} * \% \mathbf{a}, \ \mathbf{i32} \ \% \mathbf{i}.0

\%1 = load float * \%0, align 4

return sum:

\%2 = \mathbf{getelementptr} \ \mathbf{float} * \%b, \ \mathbf{i32} \ \%i.0

\%3 = load float * \%2, align 4

\%4 = mul float \%1, \%3

\%5 = add float \%4, \%sum.0

\%6 = add i32 \%i.0, 1

br label %bb1

; preds = \%bb, \%entry

bb1:

%i.0 = phi i32 [ 0, %entry ], [ %6, %bb ]

%sum.0 = phi float [ 0.0, %entry ], [ %5, %bb ]

\%7 = icmp \text{ ult } i32 \% i.0, \%n

br i1 %7, label %bb, label %bb2

preds = \%bb1

bb2:

br label %return

; preds = \%bb2

return:

ret float %sum.0

}

```

Figure 1.6: Example LLVM bitcode corresponding to a simple c-function computing a vector dot product.

that is used by LLVM analyzers and optimization passes. It is represented in a C++ class hierarchy and there are various methods for in-memory construction and debugging. Next, there is an efficient on-disk representation that is suitable for fast loading for just-in-time compilers. The third form is a human readable text representation that is very helpful for debugging and can even be used to write LLVM code by hand using an assembly-like language. There are tools to convert among all these forms without loss of information.

A verification pass asserts that LLVM bitcode is well-formed, i.e., it adheres LLVM syntax and its type system and each scalar value is in strict SSA form. There are no restrictions concerning reads from and writes to memory locations. However, a dedicated pass (mem2reg) identifies memory locations whose address is never taken and promotes them to virtual registers, inserting phi functions where appropriate. This effectively removes burden of SSA construction from the front-end by mapping local variables to stack references that are processed by mem2reg later on.

A simple example showing LLVM bitcode for a vector dot product is shown in Figure 1.6. Note, that all variables are fully typed. A special function (getelementptr) is used to obtain the address of an aggregate data structure in a type-safe way. Memory access instructions are represented explicitly by loads and stores. The example is in strict SSA form, i.e., each variable is defined exactly once and each use is dominated by

its definition. Phi-functions are used to disambiguate different values at join points, e.g., at the beginning of basic block bb1. Note that the actual semantics of each operation depend on the type of its arguments, e.g., floating-point versus integer add.

#### 1.3.3 Backend Infrastructure

A "backend" translates LLVM bitcode into a usually equivalent program representation. In most cases, this is the assembly language for a particular hardware platform. However, there are also backends that translate LLVM bitcode to C or virtual machines. The C-backend is interesting as it allows to use the LLVM infrastructure on platforms that are not explicitly supported by applying a generic vendor compiler to LLVM's output.

At the time of writing, LLVM supports about a dozen different target architectures and variants such as X86(\_64), PowerPC (32/64), Alpha, Sparc, Itanium, ARM, or Cell. A *VLIW* backend and the necessary additions for the OnDemand CHILI core has been developed by our group. All backends are based on a target independent code generator infrastructure, which consists of five main components:

- Abstract Target Machine Descriptions Target machine characteristics that are important for code generation such as descriptions of the particular instruction set architecture, functional units, or register files, are defined using a dedicated description language called TableGen. Descriptions are independent from a particular component and can be effectively organized in a class hierarchy to obtain concise descriptions by factoring out common information, e.g., most arithmetic operations such as add or sub differ only in their opcode while the set of operands and register constraints remains the same. TableGen descriptions are independent of a particular algorithm. However, there are different "backends" that are used to generate target specific data structures and algorithms at compiler compile time.

- Machine Code Infrastructure LLVM provides a set of classes to represent target specific machine instructions in a target independent way. Some components such as the set of valid opcodes or registers are generated from backend descriptions at compiler compile time. Code is organized in the form of classical control graphs while straight line segments without control flow are, as usual, represented by basic blocks. Apart from few exceptions, the semantics of a particular operation are not known any more. It is the job of the instruction selector to convert LLVM bitcode into a semantically equivalent machine representation for a particular target.

- Target-Independent Components Almost all major backend components are implemented in the form of target-independent algorithms that make use of the backend descriptions during runtime or that are partially generated for a particular target at compiler compile time. This includes instruction selection, register allocation, and scheduling. For several tasks, multiple algorithms are implemented that can be selected using command line options.

• Abstract Interfaces for Target-Specific Hooks The generic LLVM backend infrastructure provides a small number of abstract target interfaces that are implemented for each of the available target architectures. These interfaces provide functionality that cannot be derived from the abstract machine descriptions, e.g., construction of frequently used machine instructions, folding of memory operands, or abstract interpretation of branch instructions. In addition, several backends implement target-specific low-level optimizations and transformations that are important for effective code generation.

• JIT Infrastructure The LLVM JIT is largely target-independent and shares most of the backend infrastructure that is also required for the static code generator. The main additional requirement is a description of the encoding of machine instructions in the corresponding TableGen description.

#### 1.4 Preliminaries

This section gives a brief introduction into related areas that are heavily used in the subsequent chapters. For a more detailed description, the reader is referred to the provided citations.

#### 1.4.1 Static Single Assignment Form

Static single assignment (SSA) form is a program representation in which each variable has a single static assignment in the source code [CFR<sup>+</sup>91a]. This property does in general not hold for intermediate representations derived from generic imperative programming languages. Thus, multiple definitions of the same variable are usually disambiguated by sub-scripting them with unique version numbers. The main advantage of SSA form is that so-called use-def chains, i.e., a datastructure that maps a use of a variable to the set of potential reaching definitions, are explicit in SSA form. This simplifies several analyses and optimizations, e.g., constant propagation, dead code elimination, partial redundancy elimination, strength reduction, or value numbering. In practice, SSA form is usually linear in the size of the original program while use-def chains in general require a quadratic amount of space<sup>2</sup>.

The conversion of generic programs into SSA form is well-understood and, in general, requires the insertion of so-called  $\Phi$ -nodes to disambiguate definitions of the same variable at program join points. These  $\Phi$ -nodes always have as many arguments as a particular basic block has predecessors and its semantics are such that the result is the 1-th argument if and only if control flow entered the block via the 1-th predecessor.

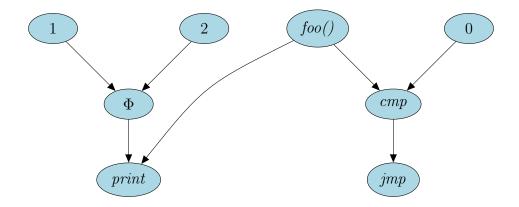

To illustrate these concepts with an example, consider the code fragment in Figure 1.7, which shows the result of SSA conversion of the example to the left. The input program has two assignments for variable i. Therefore, it is not in SSA form. The code is

$<sup>^2</sup>$ There are worst-case examples for which SSA form is also quadratic in the size of the original program.

```

x = \text{foo}(); if(x > 0) i = 1; else i = 2; i_2 = 2; i_3 = \Phi(i_1, i_2); print(x, i); x_0 = \text{foo}(); if(x_0 > 0) i_1 = 1; else i_2 = 2; i_3 = \Phi(i_1, i_2); print(x_0, x_0);

```

Figure 1.7: SSA form (right) for the program fragment to the left. So-called  $\Phi$ -functions are used to disambiguate multiple definitions at join points in the control flow graph.

transformed into SSA form by splitting variable i into variable  $i_1$  and  $i_2$ . A  $\Phi$ -function merges the values of program variable  $i_1$  and  $i_2$  and assigns the result to variable  $i_3$ .

It is important to note that  $\Phi$ -functions have special semantics that have to be carefully considered.

- Event though  $\Phi$ -functions are usually denoted as a sequence of individual statements at the beginning of a linear code sequence, they have parallel semantics, i.e., *all* the arguments of  $\Phi$ -functions in a particular block are read *before* they are written.

- Liveness is usually defined by the existence of a path from a given program point to

a use of a particular variable that does not containing a definition. This does not

hold for Φ-functions as a particular argument is only used when control flow enters

via the corresponding predecessor. However, we can maintain the usual definition

of liveness by thinking of Φ-functions as parallel copies of the corresponding right

hand side to the variables at the left hand side at the very end of the particular

predecessor block.

A simple SSA construction algorithm might attempt to insert  $\Phi$ -functions at *every* join point. This is clearly unfeasible in practice as there will be a large number of unnecessary  $\Phi$ -functions. Thus, most compilers generate so-called *pruned* SSA form, which contains  $\Phi$ -functions only for variables that are actually live at a potential insertion point.

Several analyses and transformations require to insert code along *edges* in the control flow graph. This can be accomplished easily if either the source has only a single successor block or the target has only a single predecessor block by inserting the code in one of these blocks. If both conditions are violated, an edge is called *critical*. Critical edges can easily be removed by inserting an empty block along the edge. Programs in SSA form where all critical edges have been removed are in so-called *edge-split* SSA form.

**Notation** In the following, we consider control flow graphs  $CFG(\mathcal{N}, \mathcal{E})$  in SSA form. The nodes  $\mathbf{s}$  and  $\mathbf{e}$  are distinguished nodes denoting the (artificial) start and end vertex

respectively. Edges  $\mathcal{E} \subseteq \mathcal{N} \times \mathcal{N}$  denote the transfer of control in the program. We denote with  $\mathcal{V}$  the set of program variables in CFG. Each node in CFG corresponds to a labeled single instruction  $\ell$  of the form

$$\ell:(d_1,\ldots,d_m)\leftarrow\operatorname{op}(u_1,\ldots,u_n).$$

The sets  $\mathcal{D}_{\ell} \subseteq \mathcal{V}$  and  $\mathcal{U}_{\ell} \subseteq \mathcal{V}$  denote the subset of variables used and defined at  $\ell$  respectively. For each  $v \in \mathcal{V}$ ,  $\operatorname{def}(v)$  denotes the unique label defining v. Each label  $\ell$  has an ordered set of predecessors  $\operatorname{preds}(\ell)$  which are denoted by  $(\operatorname{pred}_{\ell}^{1}, \ldots, \operatorname{pred}_{\ell}^{k})$ . As usual, confluence points of multiple reaching definitions are disambiguated using  $\Phi$  functions. A label  $\ell$  dominates a label  $\ell'$  (denoted by  $\ell \succeq \ell'$ ) if all paths from  $\mathbf{s}$  to  $\ell'$  contain  $\ell$ . Label  $\ell$  strictly dominates  $\ell'$ , if  $\ell \succeq \ell'$  and  $\ell \neq \ell'$ .

We say a variable v is live at label  $\ell$ , if there is a path from  $\ell$  to a usage of v that does not contain a definition of v. This definition is not precise in the context of  $\Phi$ -functions as their result depends on the particular predecessor by which a label has been reached. Therefore, we treat  $\Phi$ -arguments like virtual usages right after at the corresponding predecessor. The set of variables live at label  $\ell$  is denoted by  $\mathcal{L}_{\ell}$ . Two variables  $v, v' \in \mathcal{V}$  are said to *interfere* iff there exists a label in the program where both are live.

A program in SSA form is called strict, if each usage of a variable v is dominated by its definition def(v). The usage of strict SSA form is no restriction as we can easily add artificial definitions for undefined values without altering the program semantics. For some languages such as Java, strictness is even a requirement.

**SSA Construction** SSA form can be computed efficiently. The most widely used algorithm which is also used in this thesis is based on work by Cytron et al. [CFR<sup>+</sup>91a]. The algorithm can be divided into three basic steps:

- (1) Compute the so-called dominance frontier from the control flow graph

- (2) For each variable, determine the location for  $\Phi$ -functions

- (3) Rename the original variables by sub-scripting them with unique version numbers

The dominance frontier for a label  $\ell$  is the set of all nodes  $\ell'$  such that  $\ell$  dominates a predecessor of  $\ell'$ , but does not strictly dominate  $\ell'$ . Loosely speaking, the dominance frontier describes the "border" between dominated and undominated labels. The dominance frontier can be computed efficiently in time proportional to the size of the original control flow graph plus the size of the dominance frontiers. Aside from pathological worst-case examples with very large dominance frontiers, the execution time of the algorithm is usually dominated by the size of the graph and thus runs in "practically" linear time. The required dominator tree can be easily computed using a classic bitvector data-flow algorithm. However, this might be very slow in the worst-case. A more efficient algorithm, which has been implemented for the experimental evaluation in this thesis, is the so-called Lengauer-Tarjan algorithm [LT79], which has time complexity  $O((|\mathcal{N}| + |\mathcal{E}|)\log(\mathcal{N}| + |\mathcal{E}|))$ .

The SSA construction algorithm outlined above is based on the observation that whenever a label  $\ell$  contains a definition of a variable a, then any node  $\ell'$  needs a  $\Phi$ -function for a (iterated) dominance-frontier criterion). Thus, the insertion of  $\Phi$ -functions outlined in step (2) can be accomplished by a simple worklist algorithm. In the worst-case, the number of inserted  $\Phi$ -functions can be quadratic in the size of the graph. Again, there is strong experimental evidence that, in practice, the number of inserted  $\Phi$ -functions grows only linearly.

After  $\Phi$ -functions have been inserted, the algorithm walks the dominator tree in step (3), renaming different definitions with a fresh sub-scripted version. Uses of a variable are renamed to reflect the closest definition of the variable that is above in the dominator tree. The algorithm has time complexity proportional to the size of the control flow graph after insertion of  $\Phi$ -functions.