DISSERTATION

# Wakeup Receiver for Wireless Sensor Networks

Submitted at the Faculty of Electrical Engineering, Vienna University of Technology in partial fulfillment of the requirements for the degree of Doktor der technischen Wissenschaften

under supervision of

Prof. Dr. Dietmar Dietrich Institute of Computer Technology

and

Prof. Dr. Keith Dimond Senior Lecturer University of Kent

and

Dr. Stefan Mahlknecht Institute of Computer Technology

by

Dipl.-Ing. Marco Spinola Durante Matr.Nr. 0226697 Hahngasse 18/15, A-1090 Wien

#### Kurzfassung

Die sinkenden Kosten der Produktion von Low-Power Silikon Technologien und intelligente Strategien zur Verringerung des Leistungsverbrauchs haben zu einer hohen Wünschbarkeit der schnurlosen Kommunikation für Sensornetzwerke geführt. Zwischen den verschiedenen Anwendungsgebieten für solche Netzwerke, unter anderem Gebäudeautomation, Fahrzeugautomation sowie Container Tracking, gibt es einen gemeinsamen Bedarf an Knoten, die komplett eigenständig sind und mehrere Jahre mit einem Akkumulator funktionieren. Ein langes Leben ist normalerweise mit der zeitlichen Einteilung der aktiven und inaktiven Periode der Knoten und mit der Synchronisation der Kommunikation erreichbar. Die vorliegende Arbeit schlägt einen besonderen Funkempfänger vor, genannt "Wakeup Receiver", der eine Kommunikation ohne zeitliche Einteilung ermöglicht, und der keines komplizierten Synchronisationsverfahrens bedarf. Diese Entwicklung ermöglicht das Aktivieren der Knoten auf Verlangen und ergibt eine viel energieeffizientere Strategie und Kommunikation. Die Auswirkung auf die ganze Energie des Netzwerks wird durch eine integrierte Schaltung analysiert. Zum Schluss wird eine Implementierung des Empfängers vorgestellt, die im Rahmen des erwarteten Leistungsverbrauchs funktioniert. Mit der vorgeschlagenen Lösung werden Sensornetzwerke in Leistungsverbrauch und Kommunikation an Effizienz gewinnen, damit werden die Implementierungen und Anwendungen in ihren Anwendungsgebieten viele Vorteile bringen.

#### Abstract

Sinking costs in the production of low power silicon technologies and intelligent energy saving strategies have lead to wireless communication for sensor networks becoming highly desirable. In the different fields of application for such networks, which include building automation, car automation or container tracking, there is a common need to have nodes which are completely self-sufficient and last several years on battery operation. A long life is usually realized by scheduling periodical power-ups and power-downs of the node and synchronizing the communications. This work proposes a particular radio receiver called Wakeup Receiver, which allows incoming communication without schedule, removing the constraint of complicated synchronization protocols. This design allows for powering up the nodes on-demand, resulting in much more efficient energy saving strategies and communications. The impact on the overall network energy is also analyzed using a proof of concept custom integrated circuit. Finally, the implementation of the receiver is presented, which performs within the range of expected power consumption. With the proposed solution, sensor networks will achieve efficiency in energy consumption and communication, such that their implementation and utilization will bring great advantages to their application fields.

#### Vorwort

Das erste Kapitel gibt einen generellen Überblick über Funksensornetzwerke und leitet diese Arbeit ein. Ebenso sind die Aufgabenstellung und die Ziele dieser Dissertation hier zu finden.

Das zweite Kapitel präsentiert den Stand der Technik von Sensorknoten und den verschiedenen entsprechenden Vorschlägen. Die technologischen Aspekte der Integration von Sensorknoten werden analysiert und die Systemarchitektur dargestellt. Diese Analyse deckt alle Basisaspekte und Bausteine von Sensorknoten, inklusive Mikrocontrollern, Sensoren, Glue Logic, Energiemanagement und Scavenging. Der zweite Teil des Kapitels präsentiert einige publizierte Wakeup Empfänger und analysiert diese um eine Basis für die Dissertation zu bilden. Es stehen für diese Thematik nur wenige Publikationen zu Verfügung; nichtsdestotrotz sind alle relevanten Publikationen vorhanden und analysiert um einen Überblick über die (noch) kleine Welt der Wakeup Empfänger zu schaffen.

Kapitel drei erklärt die vorgestellte Architektur, die den Sensorknoten erlaubt ihren Stromverbrauch unter die Schwelle, die viele Lebensjahre ermöglicht, zu senken. Dieses Konzept deckt die beiden ersten Schichten des Protokolls, wobei die zweite Schicht normalerweise von der CPU abgehandelt wird. Es wird eine Architektur für beide Schichten zusammen mit einem allgemeinen Systemkonzept vorgeschlagen, das einen extrem geringen Stromverbrauch erlaubt.

Kapitel vier zeigt die Implementierung dieser Arbeit, die im vorherigen Kapitel vorgestellt wird. Die erste Hälfte des Kapitels deckt alle realisierten funktionellen Tests und diskreten Implementierungen. In diesem Teil der Arbeit wurde die Realisierbarkeit des Konzeptes getestet und einige Schaltkreise wurden realisiert und gemessen, obwohl sie noch nicht für niedrigen Stromverbrauch optimiert wurden. Die zweite Hälfte des Kapitels behandelt die integrierte Implementierung des Wakeup Empfängers, dank den Ergebnissen der vorherigen diskreten Implementierungen.

Kapitel fünf zeigt die Ergebnisse, die durch die Implementierung erreicht wurden, und vergleicht diese mit den erwarteten Resultaten von Kapitel drei. Die Effizienz aller Bausteine des Wakeup Empfängers wurden gemessen und mit den erwarteten Werten verglichen. Eine allgemeine Evaluierung des Empfängers als Teil des Sensorknotens wird durchgeführt.

Kapitel sechs schliesst die Arbeit mit einem Überblick und einem Ausblick für zukünftigen Arbeiten basierend auf dem Konzept des Wakeup Empfängers ab.

#### Preface

Chapter 1 gives a general background to Wireless Sensor Networks and introduces them to this work. The problem statement and the objectives of this thesis are also found in this chapter.

Chapter 2 presents the state of the art of sensor nodes and the various proposals that are pertinent to this work. The technological aspects in sensor integration are analyzed and the system architecture is presented. This analysis covers all the fundamental aspects and building blocks of sensor nodes works, including microcontrollers, sensors, glue logic, energy management and scavenging. The second part of the chapter presents some proposed wakeup receivers and analyzes them to build a basis to the work of this dissertation. There are not many sources on this thematic; nonetheless all relevant publications are represented and analyzed to give a picture on the (still) small world of the wakeup receivers.

Chapter 3 explains the proposed architecture that enables sensor nodes to reduce their power consumption under the threshold that makes years of life possible. This concept covers both the physical layer of the communication stack, the radio transceiver as the second layer which is normally a task of the CPU. An architecture for both layers is proposed together with an overall system concept that enables ultra low power consumption.

Chapter 4 shows the implementation of the work as explained in the previous chapter. The first half of the chapters covers all the functional test and discrete implementation realized. In this part of the work, the capability of the concept was tested and some proof circuits were realized and measured, for they were not yet optimized for ultra low power. The second half of the chapter covers the implementation on-chip of the wakeup receiver. This is based on the results of the discrete implementations with main focus on the power consumption of the circuit.

Chapter 5 shows the results reached by the implementation and compares them to the expected results from chapter 3. All the performance of the building blocks of the wakeup receiver are measured and compared to the expected values. An overall evaluation of the wakeup radio as part of the sensor nodes is given.

Chapter 6 concludes this work with an overview and the vision for future works based on the concept of wakeup receivers.

#### Acknowledgements

My first thanks go to my advisor, Prof. Dietmar Dietrich, who has provided me with invaluable feedback throughout the course of my thesis. I would also like to thank Prof. Keith Dimond for his expert opinion on the thesis. Special thanks go to Stefan Mahlknecht, Johann Glaser, Christian Hambeck and Daniel Weber for their support and help during my time at the institute. I would also like to thank Thomas Herndl, Infineon Austria, for his support of the realization of this work. Last but not least I would like to thank my wife Johanna, my parents and my brother, my family-in-law, my near and far friends (you know who you are) for the help and support, constantly showing me through your faces what matters in life.

# Table of Contents

| 1        | Intr | roduction 1                                           |

|----------|------|-------------------------------------------------------|

|          | 1.1  | Fields of application                                 |

|          | 1.2  | Problem statement                                     |

|          | 1.3  | Tasks and objectives    7                             |

| <b>2</b> | Sta  | te of the Art: wireless sensor networks nodes 9       |

|          | 2.1  | Node Architecture                                     |

|          |      | 2.1.1 Microcontrollers                                |

|          |      | 2.1.2 Sensors                                         |

|          |      | 2.1.3 Low power glue logic and analog building blocks |

|          |      | 2.1.4 Energy sources                                  |

|          |      | 2.1.5 Power management                                |

|          |      | 2.1.6 Antennas                                        |

|          |      | 2.1.7 The TinyMote, an example sensor node            |

|          | 2.2  | Wakeup Receivers and Protocols                        |

| 3        | Pro  | posed Solution 36                                     |

| 0        | 3.1  | Solution Development                                  |

|          | 3.2  | System Architecture                                   |

|          | 0.2  | 3.2.1 Wakeup Receiver MAC Protocol                    |

|          |      | 3.2.2 The Complete transceiver                        |

|          | 3.3  | Simulations                                           |

| 4        | т    | blementation of the Wakeup Receiver 49                |

| 4        | -    |                                                       |

|          | 4.1  |                                                       |

|          |      | *                                                     |

|          |      |                                                       |

|          | 4.0  | 4.1.3 Hardware                                        |

|          | 4.2  | Integrated solution                                   |

|          |      | 4.2.1 Concept                                         |

|          |      | 4.2.2 Protocol                                        |

|          |      | 4.2.3 Wakeup Receiver packet format                   |

|          |      | 4.2.4 Hardware Wakeup Receiver                        |

| 5                          | Results and performance5.1Discrete Wakeup Receiver measures5.2Integrated Wakeup Receiver measures5.3Figure of merit for the wakeup receiver5.4Data throughput and latency | 76<br>81 |  |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| 6                          | Conclusion and future work                                                                                                                                                | 86       |  |

| $\mathbf{Li}^{\mathbf{r}}$ | terature                                                                                                                                                                  | 101      |  |

| In                         | internet References 10                                                                                                                                                    |          |  |

# Acronyms

| ADC    | Analog to Digital Converter        |

|--------|------------------------------------|

| ALU    | Arithmetical Logical Unit          |

| API    | Application Programming Interface  |

| ASK    | Amplitude Shift Keying             |

| BAW    | Bulk Acoustic Wave                 |

| BER    | Bit Error Ratio                    |

| CAD    | Computer Aided Design              |

| CHLL   | Configurable High Level Logic      |

| CPLD   | Complex Programmable Logic Device  |

| CPU    | Central Processing Unit            |

| CSMA   | Carrier Sense Multiple Access      |

| DLL    | Delay Locked Loop                  |

| DSP    | Digital Signal Processor           |

| EMU    | Energy Management Unit             |

| FEC    | Forward Error Correction           |

| FPGA   | Field Programmable Gate Array      |

| FSK    | Frequency-Shift-Keying             |

| GPS    | Global Positioning System          |

| IDE    | integrated Development Environment |

| $I^2C$ | Inter-Integrated Circuit           |

| ISM    | Industrial Scientific Medical      |

| LDO    | Low Drop Output voltage regulator  |

| LNA    | Low Noise Amplifier                |

| LUT    | Look Up Table                      |

| MAC    | Medium Access Control              |

| MCU    | Microcontroller Unit               |

| MEMS   | Micro Electromechanical Systems    |

| OOK    | On-Off-Keying                      |

| PAWiS  | Power Aware Wireless Sensors       |

| PCB    | Printed Circuit Board              |

| PLL    | Phased Locked Loop                 |

| PWM    | Pulse Width Modulation             |

| RF     | Radio Frequency                    |

| RFID   | Radio Frequency Identification     |

| RTC    | Real Time Clock                    |

| -      |                                    |

- SAR Successive Approximation Register

- SBER Synchronized Bit Error Ratio

- SIP System-in-Package

- SMD Surface Mounted Device

- SNR Signal to Noise Ratio

- SoC System-on-Chip

- SPI Serial Peripheral Interface

- TPMS Tire Pressure Monitoring System

- UART Universal Asynchronous Receiver Transmitter

- USB Universal Serial Bus

- VCO Voltage Controlled Oscillator

- WSN Wireless Sensor Network

- WUR Wakeup Receiver

# 1 Introduction

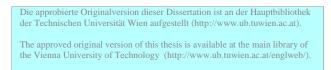

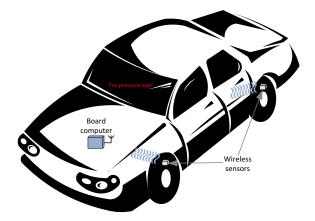

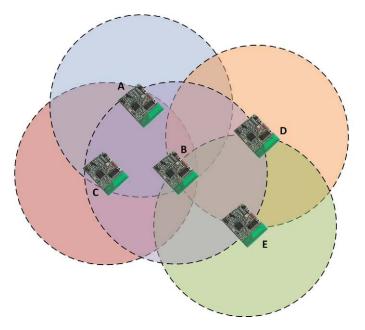

A Wireless Sensor Network (WSN) is a network consisting of devices that collect environmental data and transmit it with a radio to a higher hierarchal elaboration unit (as shown in figure 1.1 from [4]). Such networks are typically deployed in environment monitoring applications [Pot98]; although the initial motivation thrust of research in this field was military battlefield surveillance, contributing to the ubiquitous computing concept. The typical node is equipped with a micro controller, a wireless communication physical layer and at least one sensor. Such nodes are required to be small scaled so that they can be hidden practically anywhere in the environment.

Some research projects, like EU founded eCubes [RTW08] [12], are willing to integrate a whole sensor with chip stacking techniques in a single minute silicon box. Due to the small dimensions, energy which can be stored or harvested (e.g. from solar panels or piezoelectric elements) is actually very limited. The different environments where a node can be deployed require it to be resistant to harsh stress conditions, such as extreme temperatures or high accelerations. Some sort of redundancy in the positioning of nodes must be taken into account because node failures are likely to happen. Fixed routing in such networks makes less sense because the communication itself represents about 75%-80% of the total power consumption of such nodes [Mah04, p. 136]; therefore it makes sense for routing to choose the best path dynamically, otherwise the consumption can not be balanced between nodes. Because the node is completely unwired from power sources, the energy management must be accurately planned. The energy will be typically stored in a battery or scavenged from the environment through solar panels or mechanical energy generators. The mobility of the nodes and the energy management result in a dynamic network topology, where the nodes can dynamically route messages in the most efficient way to the destination, taking the own energy reserve into account, but also the reserve of the surrounding nodes.

Figure 1.1: Wireless Sensor Network example from [4]

Because of the small energy reserve a node can have, it is not always possible for the nodes to communicate directly with the data collecting base station. Communication failures which can occur also demonstrate the need of dynamical routing. Such types of networks do not constrain the construction and functionality of such nodes, but enhance their application fields by allowing complete heterogeneity. This also allows large scales of deployment (hundreds of nodes) without affecting operation, which in each case should work unattended.

This chapter will to give an overview of the present and future use of WSNs, and a description of the goals of this work. The many fields where WSNs are a key to success in realizing the intelligent environment are the justifications to the great research efforts that have been done. This work will contribute to the field of wireless sensor networks by presenting an innovative architecture for radio communication, which will extend the projected lifetime of a node relying on limited energy sources such as batteries. The result, matched with improvements in network protocols that take into account the energy of the nodes and of the whole network will be a wireless sensor network that is capable of relying on limited energy sources for years, not sacrificing throughput and latency for lifetime.

## 1.1 Fields of application

The main application scenarios in WSN include building automation, car automation, health care applications, traffic control and container tracking. A small overview of the huge range of different applications that can be made possible will be given here.

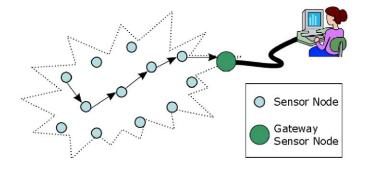

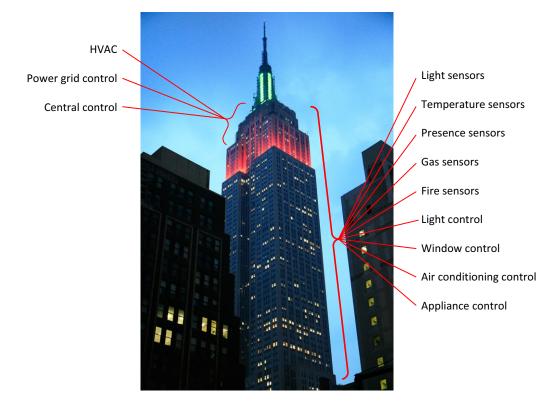

In the case of building automation [RKNG07] (figure 1.2), it is possible to imagine modern skyscrapers with hundreds of floors, fifty rooms each floor. Monitoring the environment of each room means measuring, for instance, temperature, humidity, human presence, which are easy tasks with modern electronics. Such a cabled network needs kilometres of copper, precise planning and installation during the construction of the building, leaving no chance for later radical changes in the system at low effort and cost. Using self-powered nodes communicating via radio would represent a valid substitution to wired networks and increase the flexibility and expansibility of the system. Maintenance would be reduced to battery change, which would occur each five to ten years, and would not require a technician to do the job. Substitution of meters of cable is in contrast a complicated and expensive job. Such complex systems have begun to find their way in the commercial market, as shown in [Whe07] and [Gut04].

Another completely different scenario is represented by car automation (e.g. figure 1.3 by [29]). The weight of copper cables in a car can reach 50 kg of weight, 5 km length and mounting costs comparable to the mounting costs of the engine [Chi96], [Kop97]. Maintenance is also in this case very complicated, due to the high density and related work to replace cables. In this field there are a lot of sensors which are not strictly safety related; therefore, they are for the time being eligible to be substituted from their wireless equivalents. Some obvious examples are temperature and humidity sensors, but also seat presence sensors, parking sensors or Tire Pressure Monitoring System (TPMS), which is the main driver for the Power Aware Wireless Sensors (PAWiS) research project related to this work.

Pervasive WSN seem to be a very interesting topic for the health care industry (as [SCL<sup>+</sup>05], [MEEE06] and [BA07]). Patients could constantly carry small and imperceptible sensors that would collect data such as blood pressure, body temperature or pharmaceutical intake. This data could be collected and mined at home or in the clinic for monitoring purposes, analyzed

Figure 1.2: Building automation example

Figure 1.3: Sensors in car automation, photo from [29]

by the doctor while in visit, benefiting not only the patient, but also research on biological and pharmaceutical effects on the human being. As human beings get older, a more discrete and more efficient control of medical parameters could be vital in cases of emergency.

Traffic control could be enhanced by car-to-car communication or dynamic traffic light operation embedding sensors on roads, signs and vehicles (as shown in [RS07], [LL07] and [CCV04]). This could enhance the fluidity of the traffic and prevent traffic jams by transferring live information on car accidents or other causes of problems directly to the in-car navigation systems based on Global Positioning System (GPS) or other positioning systems. Heavily busy road crossings could be optimized for higher car "throughput" instead of normal fixed time behavior by measuring how long the queue on each direction is.

Container tracking, on the other hand, is an application where wireless solutions begin to be developed (see [Sch06], [MM07b] and [BBC<sup>+</sup>07]) because of their complexity and number, as shown in figure 1.4. The idea is to equip containers with GPS sensors, intrusion detection or temperature sensors. The containers located on a port or on a ship could communicate their status to a controlling service or to the owner through on-site infrastructure. While being transported

Figure 1.4: Container terminal from [2]

on a ship, some elected containers could connect via satellite communication, or through ship infrastructure, to transmit data relevant to the owners of the carried goods [MM07a].

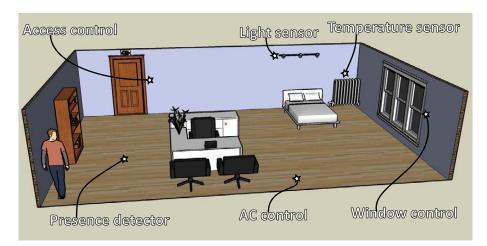

This work has been realized as part of the PAWiS project [16], a great contribution to the topic of WSN, which are indeed a very promising market. The outputs of the project are directed to different levels of support to the realization of network nodes. The main subprojects of PAWiS are the simulation framework, the Energy Management Unit (EMU), the Configurable High Level Logic (CHLL) and the Wakeup Receiver (WUR) which is the subject of this work.

For the realization of nodes and networks, a simulation framework [GW07] based on Omnet++ [Var01] has been implemented. The framework helps simulate the behaviour of the nodes and then the behavior of the whole network, focusing especially on the energy resources of both software and hardware issues. This allows an estimation of the projected life of the nodes and of the whole network. The framework supports high modularization of the nodes, such that it is possible to try different implementation of some building blocks of the node (e.g. the Medium Access Control (MAC) layer) without changing the rest of the simulation environment and is intended to be used in a cyclic development scenario. Classes to handle the inter-node communication that considers spatial distribution and noise within the network are provided as well as bit error rate and behaviour of the communication facilities. The CPU can be accurately modeled with power states and interrupts, and the power consumption can be parameterized in integer, float, flow and memory access operations. The normal node is divided generally in the following blocks: the application, the (possibly hierarchical) power supply, the MAC layer, the sensors and the physical communication layer. The application is responsible for the control of each other block. It acts as a controller for each action that occurs in the node. For example, it decides how much and how long the CPU is used to elaborate any incoming packets. In this way, it is possible to accurately model the power consumption of hardware only, software only or mixed tasks. The framework cares for the parallelization of tasks and the queuing of interrupts. On the other hand, the application must ensure that the CPU is not overloaded, since it could be possible to schedule two tasks at the same time, but the framework is aware of CPU utilization and will warn in this case.

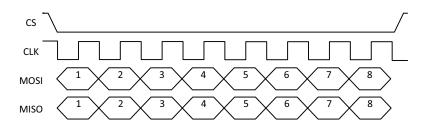

The EMU is a complex controller that is able to generate from one source all possible supply voltages that are needed by a sensor node. There are many possible sources that can supply such a node: a battery, a solar panel, a piezoelectric generator (generates electric energy from mechanical energy) and other energy scavenging sources. All these sources have actually not much in common in matter of total energy available and source resistance (which is sometimes energy dependent); therefore, the EMU must be equipped with all sorts of voltage regulators: buck converter, boost converter and Low Drop Output voltage regulator (LDO). The input voltage is converted to a temporary storage and then converted to multiple outputs. The unit is fully controllable via digital interface, for example with a Serial Peripheral Interface (SPI) bus, and the operation can be modeled in multiple power modes. The EMU should contain some facilities to better control the sensor node such as a watchdog timer or a Real Time Clock (RTC). The EMU will be realized on silicon.

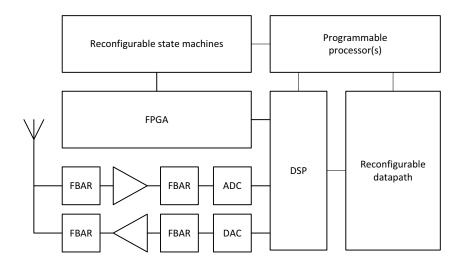

The main task of the CHLL is the building of a library of hardware digital blocks that realize a customizable and dynamically reconfigurable high level logic function. The idea is to create a sort of Field Programmable Gate Array (FPGA) which does not rely on the basic Look Up Table (LUT), but on coarse grained functions, such as adders or multipliers. Together with high level functions, a concept for the routing, that is also a high power consuming part, is also included. On the software side the logic is supported by a custom tool chain. A methodology to develop such libraries is also focus of the subproject. The main focus of the library is of course on ultra low power consumption, but also flexibility, such that simple control logic for a mixed-signal device can be developed in short times.

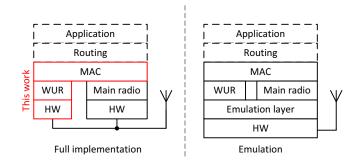

This work focuses on the WUR which will be explained later in chapter 3. The WUR is the hardware implementation of a MAC and physical layer protocol that enables a node of a WSN to save energy not putting any constraints on the responsiveness of the whole network. The work has been proofed on silicon.

## 1.2 Problem statement

The realization and integration of such pervasive sensor networks is of obvious interest for both the scientific and industrial world. All possible advantages of wireless sensor networks are realizable if the nodes are able to survive relying on low energy sources such as a battery or solar panel for several years. This constraint is actually a very diffused research topic in electronic as a whole, but

Figure 1.5: Framework and Omnet++ simulation

is also moved by social and economical reasons. Using such networks to prevent wasting Earth's energy resources are certainly of great importance, but also better care for human life can be achieved. The driver for TPMS [TLR<sup>+</sup>08] (see figure 1.6) systems is actually a bill of the United States of America that was disclosed based on the statistics that a high proportion of car accidents is due to tire failure, and that it could be prevented by accurate monitoring of the pressure. The PAWiS project focuses on researching hardware solutions to improve energy consumption of integrated sensor nodes and on simulation of power consumption for such networks. As stated in [MGH05] "...the goal of this project is to develop both efficient system architectures and the related design methodology for power aware Wireless Sensor and Actor Network nodes that allow for capturing inefficiencies in every aspect of the system. These aspects include all layers of the communication system, the targeted class of the application itself, the power supply and energy management, the digital processing unit and the sensor-actuator interface. The evaluation will be based on a prototype system that allows a future integration in a single System-in-Package (SIP) or System-on-Chip (SoC) package.". The evaluation of the system will of course be based not only on a prototype but on reliable simulation results.

The main challenge developing such nodes is to achieve real ultra-low power consumption by preserving low hop-to-hop delay and high data rate transmissions. The normal way of economizing the reserve of energy is to power-down all the devices which are unused except for those vital functions which must have, in each case, ultra-low power consumption. To reach such low power consumption, an optimization of each building block of the single node must be done, as well as an overall optimization, which indicates the need of developing SIP or SoC to realize such nodes, but also network-level energy preservation techniques.

Figure 1.6: Tire Pressure Monitoring System (TPMS)

Using state of the art batteries such as Lithium-Ion or NiMH, energy between 5 and 6 Wh can be stored using 2 to 4 AA sized batteries (see 2.1.4.1). If we consider that a complete node should consume a mean power of 50  $\mu$ W to reach a 10 year lifetime, the maximum mean power budget that the radio communication is allowed to use should be limited to around 10  $\mu$ W<sup>1</sup>, to leave enough energy for the other parts of the system. This is obviously a great challenge as state of the art transceivers need tens of milliwatts when active and must be managed to be off the most the time to lower the power consumption. This leads to great limitations in the communication

<sup>&</sup>lt;sup>1</sup>see chapter 4

capability, which can be circumvented if the radio is always active. This is why the goal of this work is a receiver that consumes less than  $10 \,\mu\text{W}$  in active mode.

## **1.3** Tasks and objectives

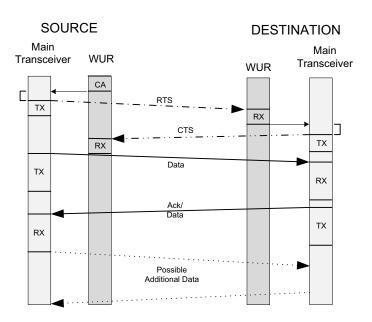

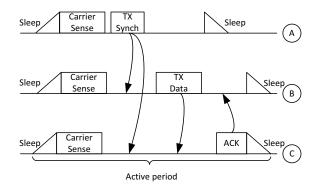

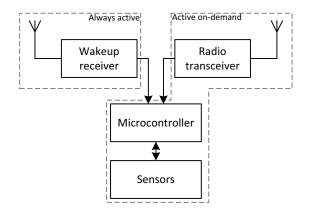

This work proposes a solution as to how to lower both power consumption and latency in peerto-peer wireless sensor networks. These are usually strictly connected when using the protocols which will be presented in chapter 2. As usual practice power consumption can be lowered by switching off parts of a system which are not being used. For communication, this means switching the radio receiver on and off periodically; otherwise, no communication is possible. This introduces us to the problem of synchronization: if the nodes are synchronized, then the power consumption can be reduced by growing the time the radio receiver is switched off. In this manner, virtually any power consumption goal can be achieved. Perfect synchronization is not possible, but reasonable results can be achieved by updating the timer periodically. This needs additional protocols and obviously increases power consumption, although it can also be seen as additional network traffic, therefore can be easily quantified. Obviously no communication occurs when the radio is switched off, thus the system has intrinsical latency. This is extended by the fact that depending on how many packets can be processed each period, it can be said that for a state of the art protocol that each hop needs a full time period to forward a packet. In this case, the latency is related to the hop count and to the periodicity of the radio protocol. If the radio is active once each second, then each hop needs at least one second. Clearly, such constraints lower considerably the responsiveness of the network. The proposed work uses a second radio receiver that is used to remote control the main radio. In this way the power consumption can be reduced to a minimum and the radio can be used only when needed, without unnecessary periodical switching on-off. This second radio must consume at least three orders of magnitude less of the main radio otherwise no advantage in its use can be achieved. As this second radio is always active, the latency for each hop is reduced in the best case to the sum of the duration of the packets including all overhead and resides in the range of the millisecond, whereas with state of the art protocols this is a key parameter to power consumption and usually resides in the second range, i.e. three orders of magnitude longer.

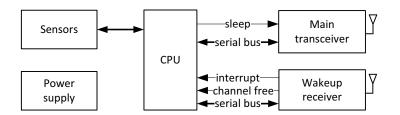

Figure 1.7: Proposed sensor node

The problem to be solved is the engineering of new MAC and physical layer protocols, which allows the activation of neighbouring nodes without a time-schedule mechanism. This would break the trade off mechanism between power consumption and hop-to-hop delay resulting in a highly enhanced responsiveness in forwarding requests and responses in a WSN preserving long life of the nodes. The problem involves particular attention to low-power circuit integration of the physical layer as well to communication protocols to enhance the overall life of the network.

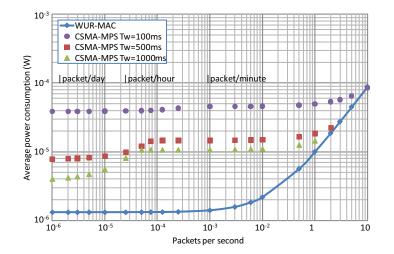

Most of the power consumption of single nodes of wireless sensor networks is dissipated from the RF-transceiver. To reduce this to the minimum, it is necessary to power up the node and particularly the radio transceiver exclusively for successful communication. This introduces the problem of synchronization between nodes, which practically means using particular protocols and handshake procedures, which rely on enabling the receiver periodically, to check if communication is occurring. In such wireless sensor networks the traffic is sparse, resulting in wasting the receiver's energy if no transmission occurs. In order to make such communication really efficient, some type of mechanism is needed to act as a *remote controller*, which is able to activate the receiver on the destination node, such that energy is used only when a communication is effectively needed. This remote controller is a radio receiver called wakeup receiver. A power consumption of  $10 \,\mu\text{W}$  in lowest-power state would allow a life of several years for a typical node. To reach this ultra-low power consumption, the receiver must be as simple as possible, completely passive if possible. Such a simple receiver simply needs a diode and a capacitor, in the same way the very first AM receivers were realized. Such simple circuit converts RF power in voltage, rectifying the signal. If the transmission is modulated with On-Off-Keying (OOK), the signal is demodulated directly from such a circuit. The low efficiency of such rectifiers and the low power involved in radio transmission show the need of some signal processing. Analog signal processing is expensive in term of power consumption if compared to similar tasks which can be performed in the digital domain. Various simulation results point out the benefit of such a module on the whole network life. The simulations at network level show that the medium life of the single node improves by 50% compared to the same node with CSMA-MPS MAC protocol [MB04] implementation.

The proposed solution is a receiver that is always powered on, waiting for incoming communication coupled to a simple yet very efficient MAC protocol. This receiver must consume some  $\mu$ W to achieve several node life years. Normally a standard receiver for the 2.4 GHz Industrial Scientific Medical (ISM) band consumes 30 mW [26]. The architecture is the typical super-heterodyne that needs some basic building blocks, such as a mixer or the Phased Locked Loop (PLL) that are very power consuming. The approach to the solution is, for this work, the relaxation of some constraints in the robustness of the receiver and in the amount of exchanged data by simplifying the architecture of the power consuming building blocks. The simplified receiver (WUR) does not replace the main receiver for the data communication, but acts as a controller for the remote activation of the node. The complete concept for the node architecture is presented in this work and also the implementation of the wakeup receiver and of the required protocols.

# 2 State of the Art: wireless sensor networks nodes

A sensor network node is a complex system realized mostly with separated microcontroller units (MCU), sensors, wireless communication layers and other building blocks, although the trend integrates more of these blocks on a System-on-Chip (SoC) solution. It has already been stated that 75%-80% of the power consumption of such nodes comes from the wireless communication [Mah04, p. 136], but this is related to the strategy of the Medium Access Control (MAC) layer protocol. Usually, for this type of network, all data is sent to one master node (also called sink node) which has the task of collecting data and taking actions, such as reporting unexpected changes in the measured values. The energy of the node can be preserved using intelligent routing protocols that take remaining energy into account to decide the best route to the destination. A typical application for Wireless Sensor Network (WSN) is building automation. As battery based sensor nodes are capable to transmit indoors in a range of 10 m, not every node will connect directly to the sink node. Each node can act, as well as measure station or as router for incoming packets. Publications such as [MMR06] or others show routing protocols developed for low power sensor networks. The routing is dynamically adjusted based on information of energy, position or higher level data. If nodes are deployed all over the rooms of a building, then there are multiple paths through which a packet can travel to the sink node. An intelligent network preserves its overall energy, not only the energy of the single node, but this task is achieved through intelligent use of communication channel. In the next sections, a bottom-up description of typical wireless sensor nodes will be given. The focus on each building block (hardware or software) is mainly set on the energy consumption as it influences the usability of the network. Up to now, home automation is a luxury feature which could be transformed from niche-market to mass-market if sensor nodes are built to consume much less energy.

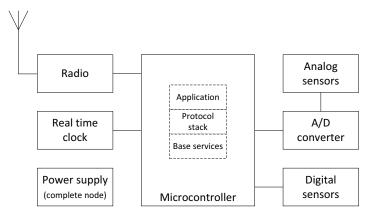

## 2.1 Node Architecture

The architecture of sensor nodes will be analyzed in depth in this chapter, as it is compelling to detect which are the weak spots in matter of power consumption and what possible workplaces would optimize them. The following subsection presents each block that composes sensor nodes, analyzing its implementation found in the mass-scale market. The general architecture of a sensor node (figure 2.1) must be simple because the energy aspects are of great importance. Energy supply is usually limited to a small battery that cannot supply more than some Ah. Typically

Figure 2.1: Example node architecture

the node will be built out of a Serial Peripheral Interface bus or other serial buses because they are less energetically expensive compared to parallel buses, but also because they need fewer connection pins resulting in smaller footprints on the devices, also saving Printed Circuit Board (PCB) production costs. On the other hand, the protocol overhead is given using such buses that cannot be underestimated because it results in longer use of the MAC-PHY interface. These buses normally allow one master and some slaves, although Inter-Integrated Circuit  $(I^2C)$  is also specified for a multi master environment. The Microcontroller Unit (MCU) needs to start the sensor and the Analog to Digital Converter (ADC) starts the conversion of the measured value, makes some calculations on the data, verifying a divergence from the old measured value and in the case send the data. At this point, all measurement devices can be set to sleep and the communication phase begins. The Radio is started, the oscillator locks the frequency, and meanwhile the Central Processing Unit (CPU) calculates the best route for the data to the sink. If the channel can be accessed successfully then the packet is sent. This is a simplified procedure of the simple task of sending a data packet, but to build a functioning multi-hop network, routing packets must also be sent to fill the routing tables of each node. Energy efficiency is achieved mainly by optimizing the communications intra-node but also inter-node because heavy service network traffic also has a negative influence on the life of the node.

#### 2.1.1 Microcontrollers

Although there are some implementations in the literature (see [WP04]) of microcontrollers specifically implemented for a sensor node, this section will analyze commercial solutions. The first low power architecture analyzed is the 4-bit MARC4 [6] from Atmel Corporation. The target of this core (that is embedded in some differently equipped microcontrollers) are wireless applications such as remote keyless entry, immobilizer systems, wireless keyboards for PC and multimedia, wireless sensors and other data control applications, using wireless communications. The core is a RISC architecture that runs at 2 clock cycle instructions. In active mode, the current consumption is specified at 180  $\mu$ A. The whole controller integrates special peripherals such as high performance oscillators, power on reset, watchdog, serial parts, multifunction timers-counters and flexible I/O structures with key interrupt functions and EEPROM modules. The MARC4 instruction set is optimized for a high level programming language called qForth that actually is a 4-bit version of the FORTH-83 standard. The choice of this language is that the MARC4 core and qForth are both stack oriented. qForth is a high-level programming language that has an

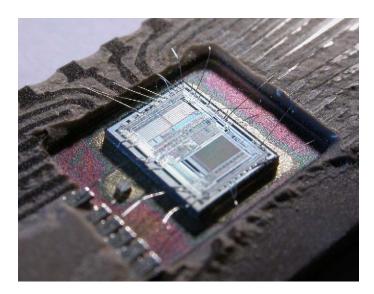

Figure 2.2: Microcontroller die photograph from [18]

efficient memory usage strategy and many of the qForth instructions are directly implemented into the MARC4 instruction set. The development of qForth was focused on real-time instruction execution. The language has instructions for arithmetical and logical operations, control structures like loops and conditional branches, memory operations, 4-bit and 8-bit comparisons, stack operations and compiler directives. Many qForth instructions can be found in other programming languages such as C and Pascal. Most of the MARC4 instructions are single byte instructions that can be executed in one instruction cycle and their values are taken from the stack. The ATAR080 is an example of microcontroller that embeds the MARC4 core. This microcontroller supports supply voltages between 1.8 V and 6.5 V, has a watchdog timer, has power on reset and brown-out function, has two multi-functional timers-counters, has 2048 byte ROM and 1024 bytes for test purposes, has 256 nibbles (4-bit words) RAM, has twelve bi-directional ports including four high-current outputs, has a 8-bit synchronous serial interface, has battery-low detection, has a comparator for zero cross detection, has three internal and four external interrupts, has an internal 32 kHz quartz oscillator, has an internal 4 MHz oscillator and works at operating temperatures from  $-40\,^{\circ}\text{C}$  to  $+85\,^{\circ}\text{C}$ .

Another example from Atmel Corporation is the AVR 8-bit MCU [5] that offers a true RISC architecture, single cycle execution  $(\frac{1MIPS}{MHz})$ , 32 general purpose registers, Harvard architecture, 1.8 V to 5.5 V operation, a variety of sleep modes, and On-Chip Debugging. The AVR core combines an instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetical Logical Unit (ALU) allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The ATmega644 (taken as example) provides the following features: The power saving features are interesting; idle mode stops the CPU while allowing the SRAM, Timer-Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents, but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I-O modules except Asynchronous Timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the Crystal-Resonator Oscillator is running while the rest of the device is sleeping. This allows fast start-up combined with low power consumption. In Extended

| In-System Programmable Flash              | $64\mathrm{k}Bytes$                 |

|-------------------------------------------|-------------------------------------|

| EEPROM                                    | 2 kBytes                            |

| SRAM                                      | 4 kBytes                            |

| General purpose I-O lines                 | 32                                  |

| General purpose working registers         | 32                                  |

| Real time clocks                          | $1  { m running}$ at $32  { m kHz}$ |

| Timer-Counters with compare modes and PWM | 3                                   |

| USARTs                                    | 2                                   |

| 2-wire Serial Interface                   | 1                                   |

| 10-bit ADC                                | 1 with 8 channels                   |

| Watchdog Timer                            | 1                                   |

| SPI serial port                           | 1                                   |

| JTAG test interface                       | IEEE std. 1149.1 compliant          |

| Power saving modes                        | 6 (software selectable)             |

Table 2.1: ATmega644 features

Standby mode, both the main Oscillator and the Asynchronous Timer continue to run.

The device is manufactured using Atmel's high-density non-volatile memory technology. The Onchip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional non-volatile memory programmer, or by an On-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation.

The MSP430[27] family of ultra-low-power 16-bit RISC mixed-signal processors from Texas Instruments is also targeted to battery-powered measurement applications. Typical applications include measuring instrumentation, electronic sensors, and consumer electronics. The architecture is a 16-bit RISC CPU, peripherals and flexible clock systems are combined by using a von-Neumann common memory address bus and memory data bus. The key features are ultralow-power architecture: 0.1  $\mu$ A RAM retention, real-time clock mode and 250  $\frac{\mu A}{MIPS}$  active mode. The MCU is equipped by many and offers a wide range of capabilities from a simple low power controller with a comparator, to complete systems on a chip including high-performance data converters, interfaces and multiplier. The MSP430F1132 is used in the Tinymote sensor node, as described in section 2.1.7.

Cypress PSoC [11] Mixed-Signal Arrays are programmable systems-on-chips that integrate a microcontroller and the analog and digital components that typically surround it in an embedded system. A single PSoC device can integrate as many as 100 peripherals with a microcontroller. Its main features are Rail-to-Rail configurable analog blocks that provide up to 14-Bit Serial Peripheral Interface (SPI) masters and slaves. The MCU provide 32K bytes flash memory, 2K bytes SRAM, internal oscillator crystal, two 8x8 multiply, 32 bit accumulator, I<sup>2</sup>C slave and master and full speed Universal Serial Bus (USB) 2.0.

#### 2.1.2 Sensors

There is a huge variety of sensors available off-the-shelf and many of them are already optimized for low power consumption. These are used in mostly different applications and are typically provided with a digital interface (a serial bus) that makes the integration in a microcontroller

Figure 2.3: Electronic sensors from [9] and [24]

based system seamless. A good example of light sensor is represented by Intersil's ISL29020 [17]. The sensitivity of this sensor is set in the human eye range: the maximum current draw in active mode is  $65 \,\mu\text{A}$  at 3.3 V and the measured range is divided into sub ranges that span 0.015 to 64000 lx. The sensors are packaged in  $2.0 \text{ mm} \cdot 2.1 \text{ mm}$  and use the I<sup>2</sup>C bus as interface. Pressure sensors are usually micromechanical elements and are practically equivalent to a resistor bridge. An ADC and some analog signal treatment are needed to digitalize the measured ambient pressure. Various working ranges are offered from 0 to over 1000 kPa. Temperature sensors are the most common digital sensors, most measure the forward voltage of a calibrated diode to calculate ambient temperature. Many sensors are also not provided by diodes and offer a connection for diodes included in other integrated circuits, such as modern CPU. The measured temperature ranges equal the working range of the IC and accuracy lies in the order of  $\pm 0.5^{\circ}$ C (but usually not over the whole temperature range). These sensors are also interfaced by SPI or I<sup>2</sup>C buses but also voltage or Pulse Width Modulation (PWM) is available. Acceleration sensors are also widely used in many systems, ranging from airbag system to home entertainment consoles. Measured accelerations ranges lie typically between  $\pm 1 g$  and  $\pm 2000 g$ , and the sensor is equipped with one, two or three orthogonally arranged axes. The interfaces are analog or digital. Contact sensors are more mechanical than electronic devices and can be seen as normal switches. Presence sensors are typically used for security purposes and are infrared light sensors. A change in the response of the mean infrared power measured is signalled as alarm. These sensors also provide a switch like interface. Gyroscopic sensors detect rotation and return a value representing the number of degrees per second of rotation. This sensor can measure up to  $\pm 360^{\circ}$  per second of rotation and are used for example by navigation purposes. The interface is usually analog. The Hall Effect sensor is capable of measuring magnetic field and to convert it to voltage. These are used in some applications where proximity must be measured, but no contact is allowed mainly for security reasons.

#### 2.1.3 Low power glue logic and analog building blocks

This section reviews some commercially available low power analog and digital integrated circuits that are used in wireless sensor nodes.

The MAX95x is manufactured by Maxim [3] and features combinations of a micro power operational amplifier, comparator, and reference in an 8-pin package. In this component the compara-

Figure 2.4: ADC architecture from [SBP03]

tor's inverting input is connected to an internal  $1.2V \pm 2\%$  bandgap reference. Variants of this comparator are also offered without internal bandgap reference. The MAX95x equipped with bandgap operates from a single 2.7 V to 7 V supply with a typical supply current of 7 µA, while the versions without reference operate from 2.4 V to 7 V with a 5 µA typical supply current. Both the op amp and comparator feature a common-mode input voltage range that extends from the negative supply rail to within 1.6V of the positive rail, as well as output stages that swing rail-to-rail. The operational amplifiers offered are both internally compensated to be unity-gain stable and uncompensated with 125 kHz typical bandwidth, 66  $\frac{V}{ms}$  slew rate, and stability for gains of 10  $\frac{V}{V}$  or greater. These operational amplifiers have an output stage that operates with ultra low bias current while maintaining linearity under loaded conditions. The comparator output stage of these devices continuously sources at maximum 40 mA.

As example ADC the MAX1108 low-power, 8-bit, dual-channel is chosen. It features an internal track/hold voltage reference, clock, and serial interface. The MAX1108 is specified from 2.7 V to 3.6 V and needs only 105  $\mu$ A. All analog inputs are software configurable, allowing unipolar/bipolar and single-ended/differential operation; battery monitoring capability is also included. The ADC features a software power-down mode that reduces current consumption to 0.5  $\mu$ A when the device is not in use. The device is accessed directly through industry standard 4-wire serial interface without external logic. Conversions up to 50  $\frac{samples}{s}$  are performed using either the internal clock or an external serial-interface clock.

There are some interesting approaches to the architecture of ADCs for WSNs; one is presented in [SBP03]. This design offers ultra-low power consumption and was developed bearing in mind the following constraints:

- Energy consumption  $< 1 \frac{nJ}{8 \, bit \, sample}$

- Low-power deep-sleep standby mode

- Supply voltage  $\sim 1 \,\mathrm{V}$

- At least 8 bit resolution

- Maximum sampling rate at least 10 kHz

- Rail-to-rail conversion range

• Reduced resolution function as digital comparator (e.g.  $X < V_{in} < Y$ )

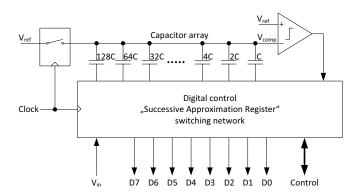

The design requires a Successive Approximation Register (SAR) architecture because it enables both ultra-low power consumption due to the low use of analog blocks and because of its flexibility that comes from the configuration of the binary search. The binary search can be linear starting from the first code or reconfigured to other starting points and code jumps rendering the ADC flexible. The normal operation samples the reference voltage on the capacitor array and compares it to the input voltage. Depending on the result the next approximation code is chosen via binary search. These operations are iterated until the required resolution is reached. For an N-bit resolution N iterations are required. The results of this design are resumed in table 2.2.

| Voltage Supply    | 1 V                      |

|-------------------|--------------------------|

| Sampling rate     | 100 kHz                  |

| Power dissipation | $3.1\mu\mathrm{W}$       |

| Energy per sample | 31 pJ                    |

| Standby Power     | $70\mathrm{pW}$          |

| Die area          | $0.053\mathrm{mm^2}$     |

| Process           | $0.25\mu\mathrm{m}$ CMOS |

Table 2.2: ADC performance from [SBP03]

Complex logic circuits are sometimes realized by the means of a Field Programmable Gate Array (FPGA) or a Complex Programmable Logic Device (CPLD) because of flexibility in changing the design. These devices are re-programmable and allow successive adaptation if design changes are needed. FPGA are usually focused on high performance and are not suitable for sensor nodes because of the power consumption. CPLDs offer low power consumption allowing realization of smaller circuits. An example of ultra low power CPLD is based on Lattice's ispMACH 4000 architecture: the family of devices delivers both low static power and high speed. Devices operate from a 1.8 V supply providing low dynamic power. The 1.8 V ispMACH 4000Z family supports a wide range of 3.3 V, 2.5 V and 1.8 V I/O standards and features 5 V tolerant I/Os when using the LVCMOS 3.3 V interface. Devices are available in commercial, industrial and automotive temperature ranges. This product offers the performance resumed in table 2.3.

| Standby current               | $10-13\mu\mathrm{A}$                          |

|-------------------------------|-----------------------------------------------|

| Standby power                 | $18-23\mu\mathrm{W}$                          |

| Pin-to-pin delay              | $3.5\mathrm{ns}$                              |

| Max clock frequency           | 267 MHz                                       |

| Pin-to-pin delay              | $3.5\mathrm{ns}$                              |

| Global Clocks                 | 4                                             |

| Inputs per Logic Block        | 36                                            |

| Product Terms (PT) per Output | up to 80                                      |

| Boundary Scan Test            | IEEE 1149.1                                   |

| In-System Programmable        | IEEE 1532                                     |

| Automotive temperature range  | $-40130^{\circ}\mathrm{C}$ at Junction        |

| PCI compatibility             | 3.3 V                                         |

| I/O Support                   | $1.8\mathrm{V}, 2.5\mathrm{V}, 3.3\mathrm{V}$ |

| Power supply operating range  | $1.6-1.9\mathrm{V}$                           |

Table 2.3: ispMACH 4000Z family typical performance

Figure 2.5: Battery comparison from [20]

#### 2.1.4 Energy sources

As wireless sensor nodes cannot rely on wired power supply from the outlet, this section will give a broad overview of the various energy sources that are eligible to supply a low power sensor node. There are two main categories of energy supplies that can be considered for sensor nodes: energy storages, such as a battery or a capacitor, and energy scavenging units, such as solar panels or piezoelectric elements.

#### 2.1.4.1 Rechargeable batteries

The most common energy source for portable devices is the rechargeable battery. This fundamental object for the modern connected world has developed quite a bit in the latest years and although this is not the place for an accurate analysis of its developments, it can be stated that battery technology did not hold the size shrink and performance rise of integrated circuits. As a matter of fact, the cost and energy available from a battery imply the designer of sensor nodes have to use power management strategies if the nodes are to last ten years or more.

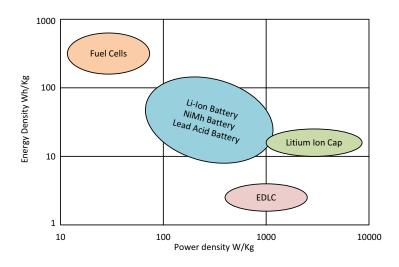

As figure 2.5 shows, different chemical components and materials result in different power and energy density, which are parameters that have quite a bit of weight in the choice of the appropriate energy source. The key design factors that need to be evaluated when choosing the appropriate battery for wireless sensor nodes can be summarized here:

- Self discharge rate

- Capacity (depending on current draw)

- Energy storage

- Energy density

The use of rechargeable batteries does require some sort of circuitry if charging is somehow done from the node, but in this case particular sources are employed, such as those explained in the

Figure 2.6: Bullith battery

next sections. Issues and challenges facing Lithium Ion rechargeable batteries can be found in [TA01]. An example of a commercially available battery that would fit WSNs is the Energizer L91 [13]. Its details are shown in table 2.4. This is an off-the-shelf product that can be considered in WSN applications thanks to its low discharge rate. This is a non-rechargeable battery; therefore replacement is needed when the battery drains. Commercially-available rechargeable batteries in AA size offer from 1500 mAh to 2500 mAh that can be used to supply a sensor node by using a combination of two or more batteries, either in series or in parallel. As shown in [Röt04], there are many energy supply devices that fit the power need of a sensor node. Although there is apparently not much development in battery technology, an exception is presented from Bullith Batteries AG [10] with their foil accumulator. This accumulator (see figure 2.6) can be manufactured at customer's choice dimensions. Typical design values are presented in table 2.5. This battery was evaluated and used for Tinymote nodes (see section 2.1.7) and the results are resumed in [Röt04].

| Chemical system             | Lithium/iron disulfide $(Li/FeS_2)$                        |

|-----------------------------|------------------------------------------------------------|

| Nominal voltage             | $1.5\mathrm{V}$                                            |

| Typical weight              | 14.5 g                                                     |

| Typical volume              | $8\mathrm{cm}^3$                                           |

| Max discharge               | $2.0\mathrm{A}$ DC and $3.0\mathrm{A}$ 20% pulsed          |

| Typical Li content          | $0.98\mathrm{g}$                                           |

| Typical internal resistance | 90 to $150\mathrm{m}\Omega$                                |

| Shelf life                  | 15 years at $21^{\circ}\mathrm{C}$ (90% of rated capacity) |

| Typical capacity            | 3000 mAh                                                   |

Table 2.4: Energizer L91 specification

| Anode           | Lithium-Titanium                   |

|-----------------|------------------------------------|

| Kathode         | Lithium-Cobalt                     |

| Energy density  | $140 - 180 \frac{Wh}{L}$           |

| Specific energy | $> 65 \frac{\text{Wh}}{\text{kg}}$ |

| Nominal voltage | 2.3 V                              |

| Capacity        | $10-5000\mathrm{mAh}$              |

Table 2.5: Bullith Foil Accumulator specifications

Figure 2.7: Fraunhofer ISE solarcell, used with the TinyMote (see 2.1.7)

#### 2.1.4.2 Solar Cells

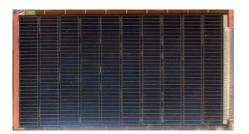

Solar cells (figure 2.7 shows a cell used in the TinyMote node, produced from the Fraunhofer ISE [RHEW04]) are interesting yet difficult to commercialize because of their high production costs and relatively low energy efficiency. Nonetheless these are used in many applications where power consumption is not so high that batteries are required, like portable calculators. From the wireless sensor point of view, a node equipped with a solar cell for energy scavenging needs some sort of energy storage for the time where no light is present. Circuits to transform and store this energy will be presented later.

As a commercial example IXYS' [19] Solar Cells will be analyzed. The IXOLAR solar cells are IXYS' monocrystalline, high efficiency products that incorporate an advanced light trapping surface. There are various cell sizes available and are targeted for charging battery powered products, such as mobile phones, cameras, PDAs, MP3 players and toys. Thanks to their typical efficiency of 17%, these cells have good energy scavenging capability even in low light condition, making them also suitable for industrial applications, wireless sensors networks, instrumentation and for charging backup batteries.

The electrical characteristics (as found in [19]) of these solar cells are resumed in the following list:

- Open circuit voltage: 630 mV

- Short circuit current density: 35 mA/cm2

- Voltage at max. power point: 505 mV

- Current density at max. power point: 32.5 mA/cm2

- Maximum peak power: 16.6 mW/cm2

- Fill factor > 75%

- Efficiency 17 %

- $\bullet$  Open circuit voltage temp. coefficient: -2.1 mV/K

- Short circuit current temp. coefficient: 0.12 mA/(cm2K)

- $\bullet~$  Cell thickness: 250  $\mu m$

Figure 2.8: Epcos UltraCaps, used with the TinyMote (see 2.1.7)

#### 2.1.4.3 Ultracaps

An UltraCap (as shown in figure 2.8 and presented in [BMP04]) is an electrochemical capacitor consisting of two carbon electrodes separated by a foil and immersed into an electrolyte. The high energy capacity of UltraCaps (in the kFrange) in comparison to electrolytic capacitors originates in the electrodes' material, which has an extremely high specific surface area of about  $2000 \frac{m^2}{g}$  and the extremely short distance in the range of 2-5 nm between the opposite plates of the capacitor. A capacitance of some thousand Farads is realized in small devices since the dielectric is extremely thin. UltraCaps store charge relying on an electrostatic effect, that is per nature highly reversible, much better than batteries.

Although the UltraCap offers high capacity, their maximum voltage is very limited (the capacitors on figure 2.8 are rated at 2.3V) and still on this voltages the leakage currents are in the  $10-20 \,\mu\text{A}$  range that is way too much for a sensor node power supply. The leakage depends on the voltage so an easy solution is to connect two UltraCaps in series although this halves the total capacity and doubles the cost.

#### 2.1.4.4 Other energy scavenging sources

Another way of supplying wireless sensor nodes is the use of Micro Electromechanical Systems (MEMS) devices (such as in [MMMA<sup>+</sup>01]) that convert mechanical or thermal energy in electrical energy [14]. The most typical scavengers use vibration energy to be transformed in electricity by piezoelectric effect. Other scavengers are targeted at transforming rotational energy in electric energy. With all these devices the main problem is the actual efficiency and the interface to the power supply that is indeed an interesting research topic.

#### 2.1.5 Power management

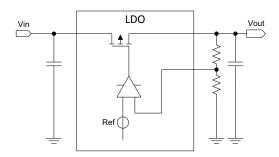

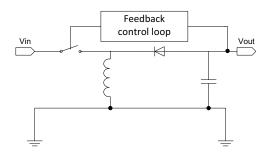

Power management is of course fundamental to the supply of the different devices that are found in a sensor node. This power management is realized by the MCU that controls the power state of all other devices (as presented in [SC01]), but also from the power conditioning devices that transform energy from one level to another. There are typically two ways to adapt the voltage level coming from the battery or from other sources: a Low Drop Output voltage regulator (LDO) and a switching supply. The LDO circuit uses a feedback loop to control a variable resistor (see figure 2.9). The resistor connects the input voltage to the output and dissipates the power for lowering the voltage. LDO s can only reduce the input voltages and are therefore not always preferred because of their high dissipation and therefore comparatively low efficiency.

Figure 2.9: LDO power supply

The TPS780 from TI is a LDO regulator that offers the benefits of ultra-low quiescent current (500 nA), small footprint and selectable dual-level output voltage levels. Its main features are resumed here from the datasheet [28]:

- Low quiescent current: 500 nA

- 150 mA, low dropout regulator with pin-selectable dual voltage level output

- $\bullet\,$  Low dropout:  $200\,\mathrm{mV}$  at  $150\,\mathrm{mA}$

- 3% accuracy over load/line/temperature

- Adjustable version from 1.22 V to 5.25 V or a dual-level output

- Vset pin toggles output voltage between two factory-programmed voltage levels

- Stable with a  $1.0 \,\mu\mathrm{F}$  ceramic capacitor

- Thermal shutdown and overcurrent protection

- CMOS logic level-compatible enable pin

- Dimensions:  $2 \text{ mm} \cdot 2 \text{ mm}$

Switching power supplies rely on a completely different concept as LDOs. This sort of power supply stores the energy in a passive component like a capacitor or an inductance. The name comes from the main non linear component which is the switch. This is used to transfer energy from the storage to the load in such way that the voltage or current match the chosen values. The important feature of switching power supplies is that they do not use dissipative components such as resistors and therefore reach high efficiencies (even over 90%). Another important feature is the load voltage: it can be generated from higher or lower input voltages.

The LTC3531 from Linear is a synchronous buck-boost switching converter that operates at above, below or equal input to the output voltage. The converters operate in a proprietary mode that reduces component count as well as providing high efficiency. The main features of this low-power DC-DC converter are resumed here:

- Regulated output with input above, below or equal to the output

- Single inductor

Figure 2.10: Switching power supply

- Up to 90% efficiency

- Vin range: 1.8V to 5.5V

- 200mA at 3.3Vout from 3.6V input

- 125mA at 3Vout from 2.5V input

- Ultra low quiescent current: 16  $\mu$ A, shutdown current < 1  $\mu$ A

- Only 3 external components required

- Short-circuit protection

- Output disconnect in shutdown

- $3 \,\mathrm{mm} \cdot 3 \,\mathrm{mm}$  DFN packages

#### 2.1.6 Antennas

Antennas play an important role in all wireless application because they are responsible for the transmission of the electrical waves over the air. Without going into too much in detail, this section wants will to give a short overview on the possibility of using a an on-chip integrated antenna, a PCB antenna and a stand-alone antenna.

The use of on-chip antennas is not yet commercially available as it is a difficult task to implement an antenna with enough radiation capacity. This technique is yet interesting and promising for its costs and dimensions, but considering that IC technologies change frequently, it could be a challenging task to redesign the antenna.

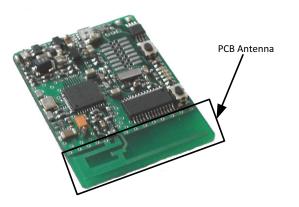

Designing a PCB antenna involves a lot of design effort if the antenna needs to be designed from scratch, but if a design is already available, the antenna can be manufactured at negligible PCB production costs. This happens because in the 2.4 GHz band the dimensions of the antennas are in the cmrange. This solution is adopted by many Bluetooth and WLAN adapters and becomes interesting also for sensor networks located in the same band. Figure 2.11 shows the PCB antenna from the TinyMote (section 2.1.7) sensor node.

Other interesting antenna implementations are represented by chip antenna. These are disguised in small Surface Mounted Device (SMD) devices resembling resistors. These are antenna elements embedded in a ceramic substrate, which is extremely stable on temperature changes over the time.

Figure 2.11: PCB antenna example

The small dimensions enable the high frequency range for these antennas and also allow for high integration on the PCB.

The CHP Series from Linx Technologies is an attractive high-performance chip antenna as its features show:

- Cost-effectiveness

- Compact SMD package

- Ceramic technology

- Low loss

- Wide bandwidth

- 50-ohm characteristic impedance

- Linear polarization

- No external matching required

- Highly stable over temperature and time

- Fully hand- and reflow-assembly compatible

#### 2.1.7 The TinyMote, an example sensor node

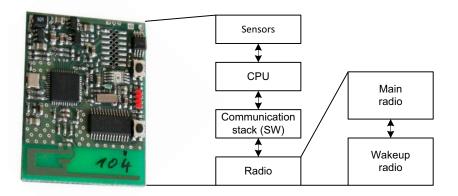

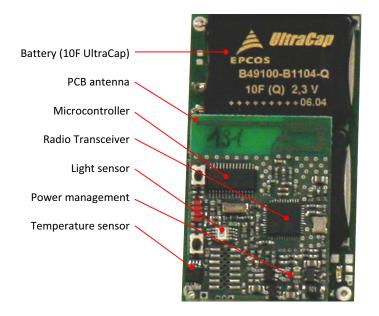

The TinyMote is senor node developed at the Institute of Computer Technology of the Vienna university of technology. It is in many ways the predecessor to this dissertation. The TinyMote is an ultra low power sensor node for multi-hop peer to peer wireless sensor networks. Its main features are resumed in this section.

The wireless interface is of course of main importance and is defined as follows:

- $\bullet~2400\,\mathrm{MHz},\,79$  frequencies of  $1\,\mathrm{MHz}$

- Data rate: 10,250,1000  $\frac{kbit}{s}$

Figure 2.12: The TinyMote sensor node

- RF wakeup time around 1 ms

- Antenna on board

- Ultra low quiescent current voltage regulator (<  $2 \,\mu A$ )

The microcontroller on board is a model of the TI MSP430 family described in section 2.1.1:

- Model MSP430F1232

- 16Bit RISC-CPU, On-Chip Osc. 4 MHz Max

- JTAG interface at connector

- Real-time clock

- 8 KBytes flash

- 256 bytes ram

The node is equipped with a temperature sensor with  $\pm 0.5^{\circ}$ C precision and optionally mountable analog sensor that can be sampled with 10 Bit resolution by the onboard ADC, e.g. a brightness sensor with samples in the 10-10000 LUX range. The printed circuit board has two buttons and four signalization LEDs and connects to an external serial port for debug purposes. The node is realized in two versions, one needing 24 x 19 mm with double sided component placement and one with 30 x 24 mm using single sided component placement. The standby current consumption of the entire node is measured to the following values (RTC is active):

- $< 700 \,\mathrm{nA}$  at 2 V (RF-Chip turned off)

- $< 3.7 \,\mathrm{nA}$  at 2 V (RF-Chip in power down)

The hop-to-hop maximum delay of <2 second results from the use of the CSMA-MPS protocol [MB04] at a wakeup period of 2 seconds, giving an average hop delay 300 ms The average power consumption in the a typical environment (one packet received and transmitted each 5 seconds) is about 100  $\mu W$  that should result in almost 9 years of operation with a lithium battery of 3200 mAh.

## 2.2 Wakeup Receivers and Protocols

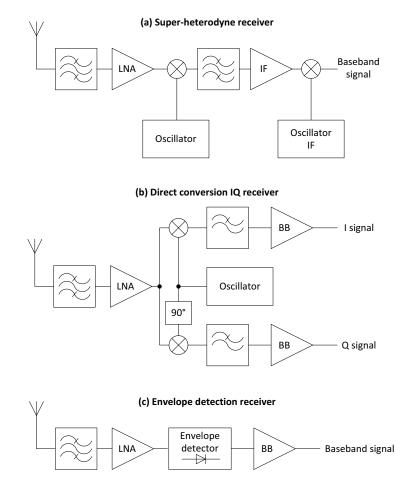

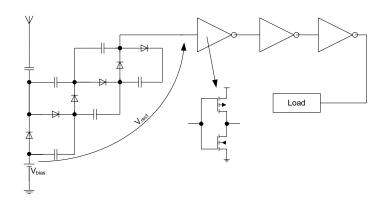

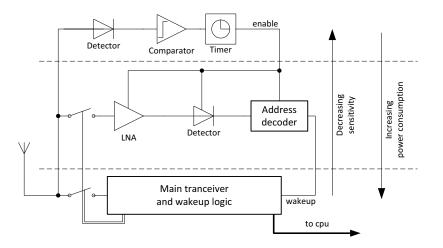

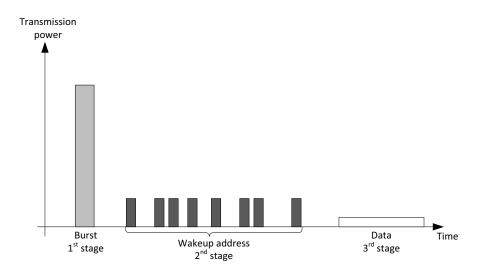

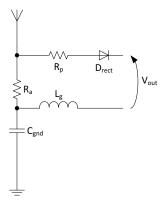

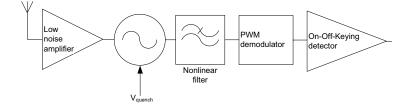

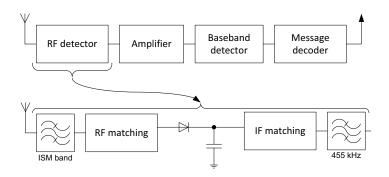

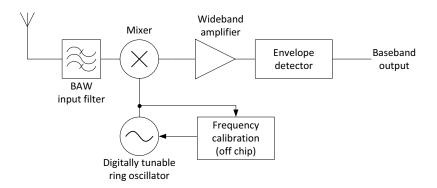

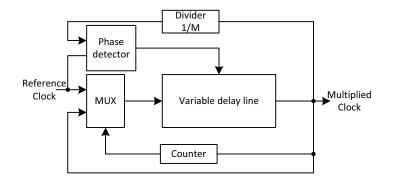

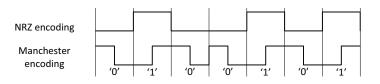

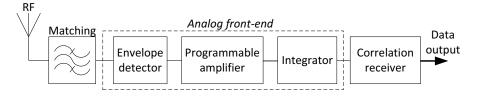

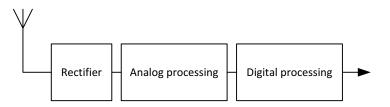

General architectures of receivers (as shown in figure 2.13) are chosen as starting points to develop new types of receivers, as their features and drawback are well known and analyzed into depth. Focus is then put on optimization of the power consumption. This task is not trivial and of utmost importance for receivers targeted at utilization in WSNs. Sampling directly at RF frequency is by no means a low power technique; therefore the RF band is usually shifted to baseband by the receiver's front-end.

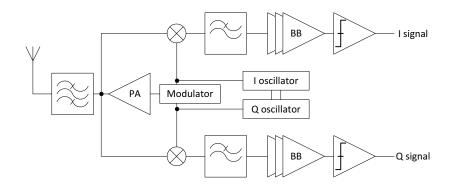

The super-heterodyne architecture [Arm24] (figure 2.13a shows a dual conversion type) is a typical frequency conversion receiver for multi channel reception. After some gain from a Low Noise Amplifier (LNA), the useful RF signal band is shifted by a mixer to an intermediate frequency after being filtered for a broad range that includes all channels. At intermediate frequency, the channels can be selected by a tuneable filter followed by mixing the signal to baseband with a tuneable oscillator. This double conversion eases the noise requirements on the signal path.

The direct conversion receiver (figure 2.13b) uses quadrature down conversion to demodulate two baseband (I and Q) signals. This receiver needs a highly spectral purity oscillator and a precise  $90^{\circ}$  phase shifting to accurately separate the two components. The mixers and oscillator

Figure 2.13: Popular receiver architectures

are indeed high power consuming, but this architecture achieves high performance, particularly sensitivity and transfer rates and is used e.g. for satellite communications or telephone cellular networks.

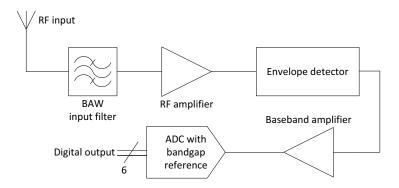

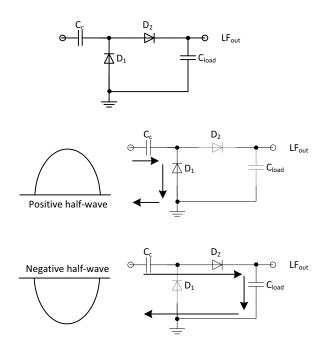

As the main focus in WSNs is put on low power consumption, conversion architectures are not good candidates because of their need for high frequency oscillators and mixers, which are power hungry components of such designs. A much simpler architecture (figure 2.13c) uses the well known rectification to demodulated information contained in the envelope of the carrier signal, such as in the standard AM receivers, which were realized at first completely passive. This technique is used e.g. in RFID tags and uses less components than the other two architectures and is therefore chosen for many implementations of wakeup receivers because of promising power saving features.

The most significant implementations of wakeup receivers are presented here. All the efforts in optimizing the proposed receiver architectures are directed to realize acceptable sensitivity, robustness and data rate for a particular power consumption goal. This objective comes from the fact that no great enhancements are possible in battery technology such that maintaining a node active for years is possible at low cost and space. Therefore each publication tends to reduce at most the consumption of the radio transceiver, as it is shown that it is the most power hungry component of the sensor node.

In [LSGR01]], the first concept of wakeup receiver as resource to reduce power consumption extending node's life can be found. The goal of the Pico Radio (figure 2.14 shows a Pico Node architecture) project referenced in this publication is to realize a node that consumes  $100 \,\mu\text{W}$  enclosed in 1 cm<sup>3</sup> space. To realize this intent optimization both between the layers of the protocol stack and between nodes is considered. At this power consumption however, considering high volumetric energy density (such as Li-ion batteries) is the projected life under 200 days. So the power consumption budget must be reduced if node life (and network life) of several years is required. The MAC protocol proposed is an extension of Carrier Sense Multiple Access (CSMA) into multi-channel CSMA. A channel for communication is chosen randomly and sensed for a present carrier. If busy, the channel is rejected and another between the remaining is chosen for

Figure 2.14: Pico Node from [LSGR01]

the same procedure until one free channel is found, otherwise the node backs off for a random time for each channel and begins the search again for those of which the timer has expired.

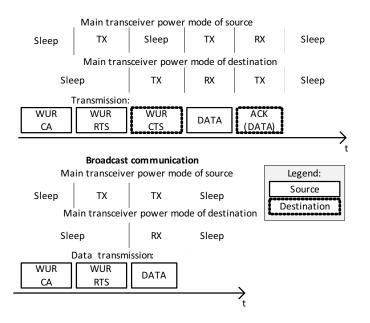

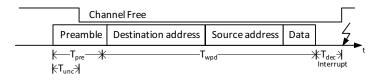

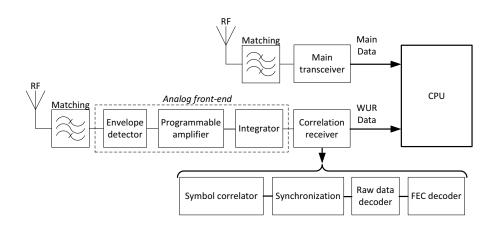

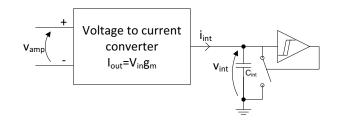

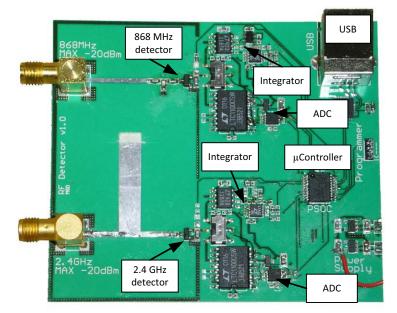

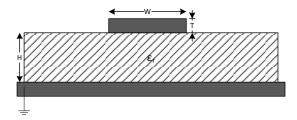

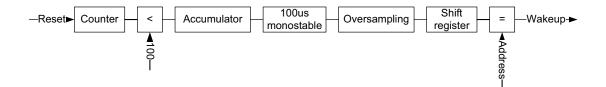

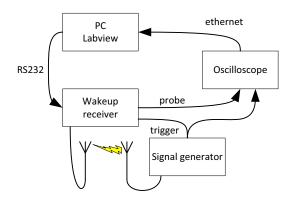

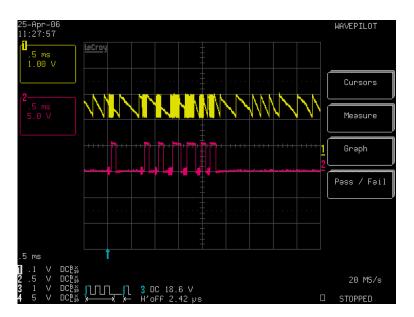

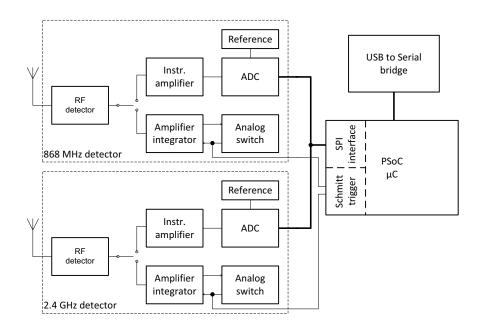

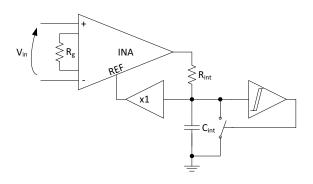

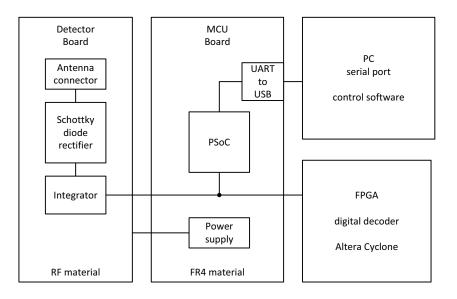

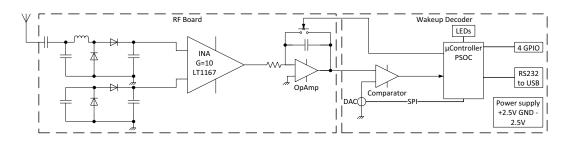

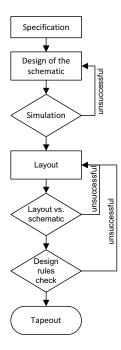

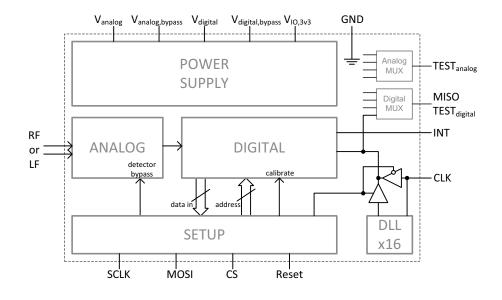

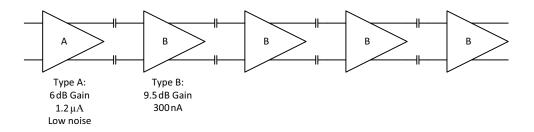

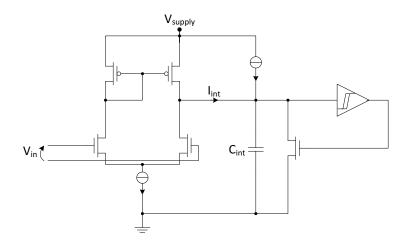

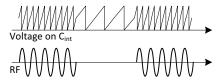

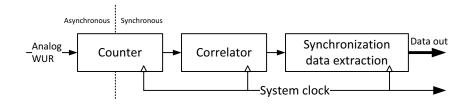

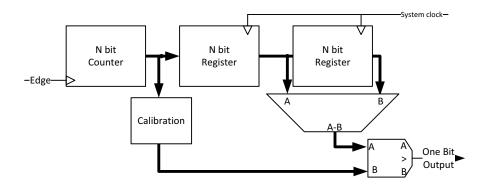

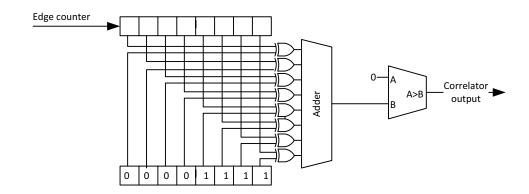

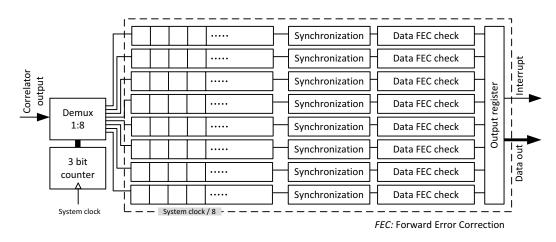

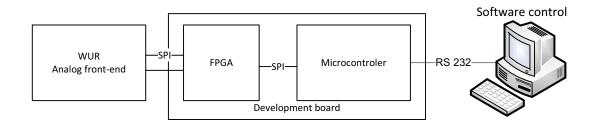

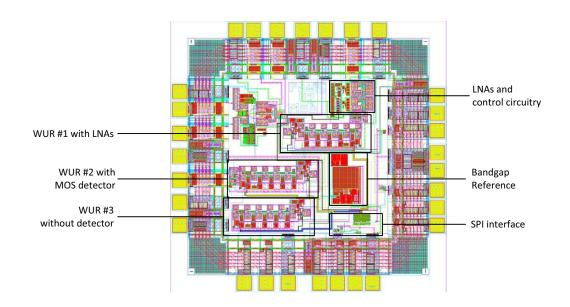

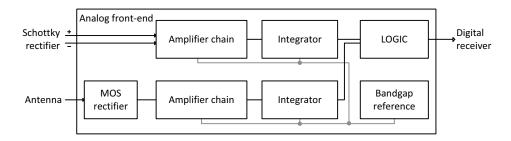

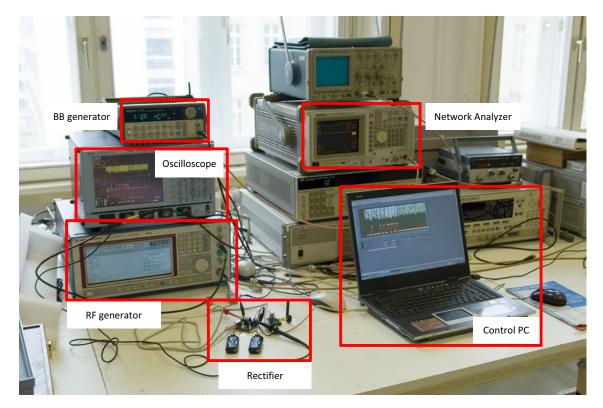

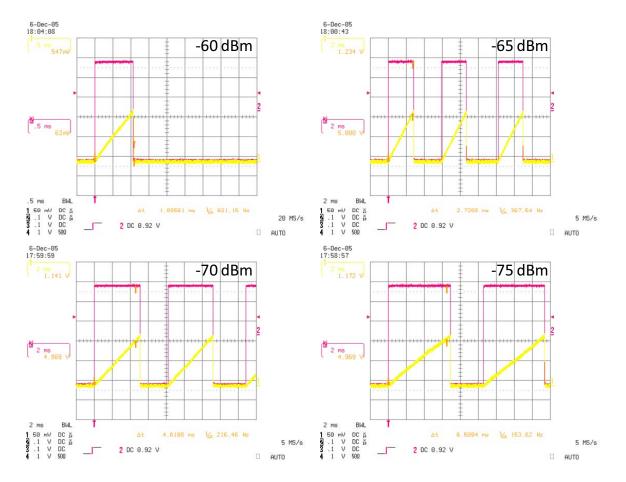

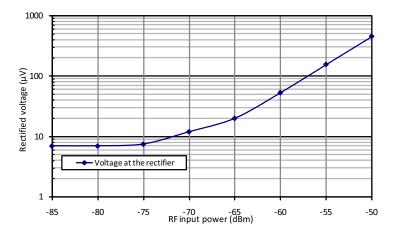

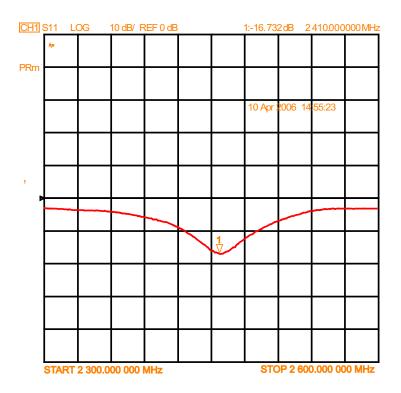

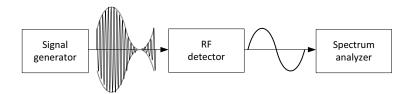

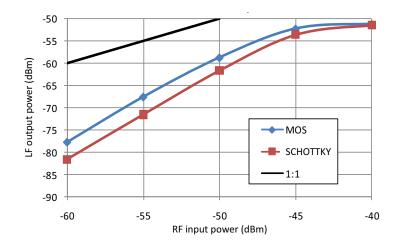

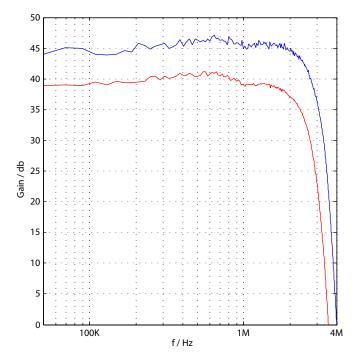

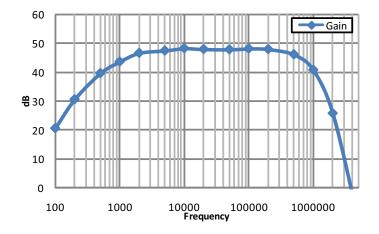

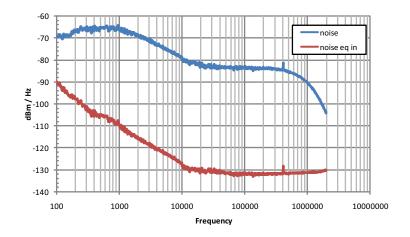

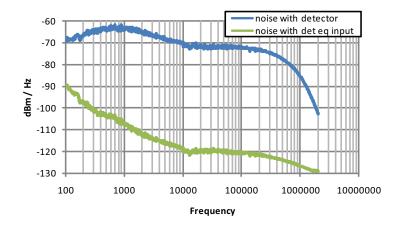

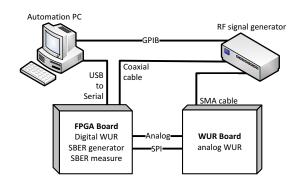

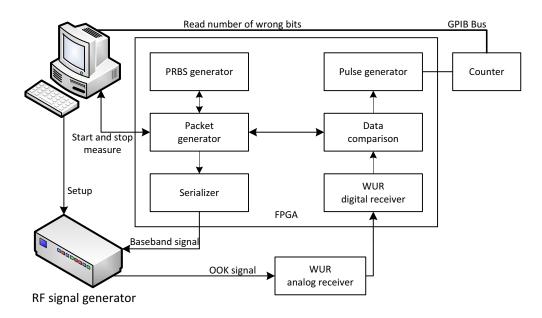

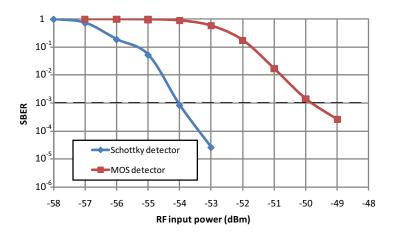

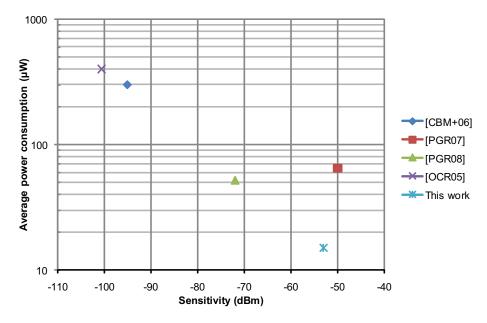

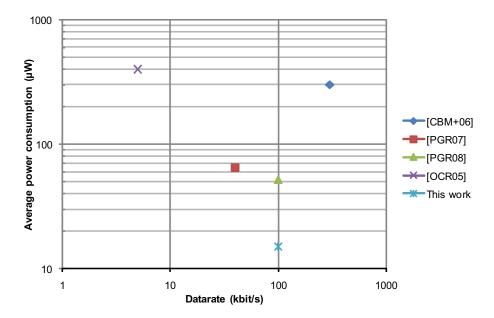

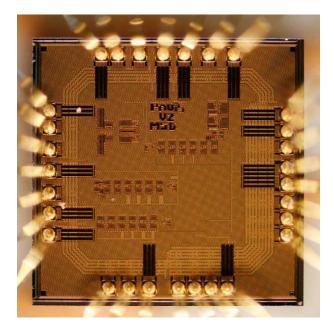

The algorithm is fully distributed as there is no higher hierarchy entity that controls it. No synchronization is needed as each communication is asynchronous because this means less power, which is the strong point of this publication. If no synchronization is required then no power is wasted for it and no power for handshaking is needed. To suppress the need for synchronization and handshaking, this paper envisions a wakeup radio that consumes less than  $1 \,\mu\text{W}$  when fully active in receive modus. Most of the time the node is in sleep mode with all components in power down so that ultra low power consumption can be achieved. The wakeup radio is the only active device in the node besides power supply. This is needed because state of the art radios consume in the mW range. The task of the wakeup radio is to activate the main radio when the node is selected for reception, as its address is modulated in the wakeup signal.