Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

## **DIPLOMARBEIT**

# Real-time Communication Systems for Small Autonomous Robots

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Diplom-Ingenieurs am

Institut für Computertechnik 384 der

Technischen Universität Wien

unter der Leitung von

O. Univ. - Prof. Dr. Dietmar Dietrich

und

Univ. Ass. Dr. Stefan Mahlknecht

Univ. Ass. Dr. Wilfried Elmenreich

als verantwortlich mitwirkende Assistenten durch

Stefan Krywult Matr. - Nr. 9827121 Anton-Bosch-Gasse 4/Stg. 1/5, 1210 Wien

Wien, im Oktober 2006 .....

# Abstract

Autonomous systems perform complex tasks to analyse and to react on their environment. One way to handle this complexity is distributing the functionality on several hardware modules. Even in small autonomous systems the predictability of the communication and the synchronization of all modules is vitally important.

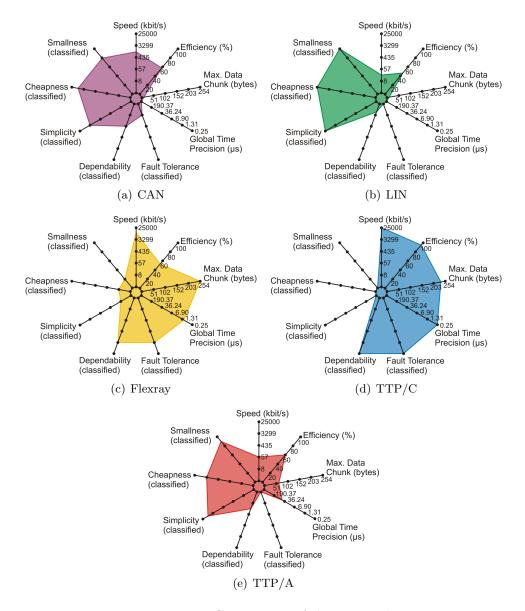

This thesis provides a survey of five protocols that play a major role in the automotive industry and in the domain of real-time communication: CAN, LIN, Flexray, TTP/C, and TTP/A. The protocols are compared and analysed regarding their suitability for small autonomous systems.

Following the results of this investigation, TTP/A is ported to the hardware of the Tinyphoon robot, a research platform for small autonomous and distributed systems. On the basis of the outcome of the case study enhancements and adoptions of TTP/A are proposed. To address the diversity of hardware a general concept of making TTP/A more portable is elaborated.

# Kurzfassung

Autonome Systeme analysieren ihr Umfeld und reagieren entsprechend darauf. Um die Komplexität dieser Funktionalität besser handhabbar zu machen, wird sie auf mehrere Hardwaremodule aufgeteilt. Auch für kleine autonome Systeme sind die Vorhersagbarkeit der Kommunikation zwischen diesen Modulen und die Synchronisierung des gesamten Systems von großer Bedeutung.

Diese Arbeit beschreibt die Protokolle CAN, LIN, Flexray, TTP/C und TTP/A, die in der Automobilindustrie und im Bereich der Echtzeitkommunikation eine wichtige Rolle spielen und vergleicht sie bezüglich ihrer Verwendbarkeit für kleine autonome Systeme.

Den Resultaten dieser Untersuchung entsprechend wird TTP/A auf die Hardware des Tinyphoon Roboters, eine Forschungsplattform für kleine autonome und verteilte Systeme, portiert. Basierend auf den Ergebnissen dieser Fallstudie werden Erweiterungen und Anpassungen für TTP/A vorgeschlagen. Um der Vielfältigkeit der Hardware in verteilten Systemen Rechnung zu tragen, wird ein Konzept erstellt, wie die aktuelle TTP/A Implementierung portabler gestaltet werden kann.

# Contents

| C             | onter                  | $_{ m nts}$             |                      | i            |

|---------------|------------------------|-------------------------|----------------------|--------------|

| $\mathbf{Li}$ | $\operatorname{st}$ of | Figure                  | es                   | iv           |

| $\mathbf{Li}$ | st of                  | Tables                  | S                    | $\mathbf{v}$ |

| $\mathbf{Li}$ | $\operatorname{st}$ of | Listin                  | ${f gs}$             | vi           |

| 1             | Intr                   | oducti                  | ion                  | 1            |

|               | 1.1                    | Backg                   | round                | 1            |

|               | 1.2                    | Proble                  | em Statements        | 2            |

|               | 1.3                    | Outlin                  | ne of Thesis         | 3            |

| 2             | Rea                    | $\mathbf{l}	ext{-time}$ | Protocols            | 4            |

|               | 2.1                    | Conce                   | pts                  | 4            |

|               |                        | 2.1.1                   | Basic Terms          | 4            |

|               |                        | 2.1.2                   | Real-Time            | 6            |

|               |                        | 2.1.3                   | Fault Tolerance      | 7            |

|               | 2.2                    | CAN                     |                      | 7            |

|               |                        | 2.2.1                   | Mode of Operation    | 7            |

|               |                        | 2.2.2                   | Additional Services  | 8            |

|               |                        | 2.2.3                   | Packet Format        | 9            |

|               |                        | 2.2.4                   | Data Encoding        | 11           |

|               |                        | 2.2.5                   | Physical Layer       | 11           |

|               |                        | 2.2.6                   | Real-Time Extensions | 12           |

|               |                        | 2.2.7                   | Efficiency           | 14           |

|               |                        | 2.2.8                   | Availability         | 15           |

|               | 2.3                    | LIN                     |                      | 16           |

|               |                        | 2.3.1                   | Mode of Operation    | 16           |

|               |                        | 2.3.2                   | Additional Services  | 17           |

|               |                        | 2.3.3                   | Frame Format         | 18           |

|               |                        | 2.3.4                   | Data Encoding        | 19           |

|               |                        | 2.3.5                   | Physical Layer       | 19           |

|               |                        | 2.3.6                   | Host Interface       | 20           |

|   |             | 2.3.7         | Efficiency                                      |

|---|-------------|---------------|-------------------------------------------------|

|   |             | 2.3.8         | Availability                                    |

|   | 2.4         | Flexra        | ·                                               |

|   |             | 2.4.1         | Mode of Operation                               |

|   |             | 2.4.2         | Additional Services                             |

|   |             | 2.4.3         | Frame Format                                    |

|   |             | 2.4.4         | Data Encoding                                   |

|   |             | 2.4.5         | Physical Layer                                  |

|   |             | 2.4.6         | Host Interface                                  |

|   |             | 2.4.7         | Efficiency                                      |

|   |             | 2.4.8         | Availability                                    |

|   | 2.5         | TTP/0         |                                                 |

|   |             | 2.5.1         | Mode of Operation                               |

|   |             | 2.5.2         | Additional Services                             |

|   |             | 2.5.3         | Frame Format                                    |

|   |             | 2.5.4         | Data Encoding                                   |

|   |             | 2.5.5         | Physical Layer                                  |

|   |             | 2.5.6         | Host Interface                                  |

|   |             | 2.5.7         | Efficiency                                      |

|   |             | 2.5.8         | Availability                                    |

|   | 2.6         | TTP/A         | e e e e e e e e e e e e e e e e e e e           |

|   | 2.0         | 2.6.1         | Mode of Operation                               |

|   |             | 2.6.2         | Additional Services                             |

|   |             | 2.6.3         | Frame Format                                    |

|   |             | 2.6.4         | Data Encoding                                   |

|   |             | 2.6.5         | Physical Layer                                  |

|   |             | 2.6.6         | Application Interface                           |

|   |             | 2.6.7         | Efficiency                                      |

|   |             | 2.6.8         | Availability                                    |

|   | 2.7         |               | Protocols                                       |

|   | 2.1         | 2.7.1         | Real-time Ethernet                              |

|   |             | 2.7.1         |                                                 |

|   | 20          |               | USB                                             |

|   | 2.8         | Compa         | rison                                           |

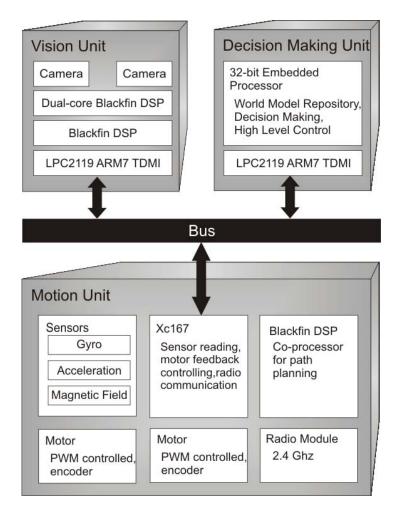

| 3 | Tiny        | yphoon        | 55                                              |

| • | 3.1         | Subsys        |                                                 |

|   | 0.1         | 3.1.1         | Motion Unit                                     |

|   |             | 3.1.2         | Vision Unit                                     |

|   |             | 3.1.3         | Decision Making Unit                            |

|   | 3.2         |               | unication                                       |

|   | J. <u>-</u> | 3.2.1         | Data Provided/Needed by the Subunits 60         |

|   |             | 3.2.2         | Real-Time Requirements                          |

|   |             | 3.2.3         | Fault Tolerance / Dependability Requirements 62 |

|   |             | 3.2.3 $3.2.4$ | Data Throughput                                 |

|   |             | 0.2.4         |                                                 |

|    |       | 3.2.5   | Maintainability                 | 63 |

|----|-------|---------|---------------------------------|----|

|    |       | 3.2.6   | Debugging and Monitoring        | 63 |

|    |       | 3.2.7   | Cost                            | 64 |

|    |       | 3.2.8   | Implementation Effort           | 64 |

|    |       | 3.2.9   | Comprehensibility of Interfaces | 64 |

| 4  | Ana   | lysis   |                                 | 65 |

|    | 4.1   | Curren  | at Communication                | 65 |

|    | 4.2   | Feature | es vs. Complexity               | 66 |

|    | 4.3   |         | ersus SW                        | 66 |

|    | 4.4   |         | mmunication in SW               | 67 |

|    |       | 4.4.1   | Time-Triggered CAN              | 67 |

|    |       | 4.4.2   | LIN                             | 68 |

|    |       | 4.4.3   | TTP/A                           | 68 |

|    | 4.5   | Results | s <sup>′</sup>                  | 69 |

| 5  | TTI   | P/A on  | the Tinyphoon                   | 70 |

| _  | 5.1   | ,       | ng TTP/A                        | 70 |

|    |       | 5.1.1   | Source Code                     | 70 |

|    |       | 5.1.2   | Architecture                    | 71 |

|    |       | 5.1.3   | Bus Subsystem                   | 74 |

|    | 5.2   | HW U.   | · ·                             | 75 |

|    |       | 5.2.1   | Receiving                       | 75 |

|    |       | 5.2.2   | Sending                         | 78 |

|    | 5.3   | Portab  | ole TTP/A                       | 80 |

|    |       | 5.3.1   | Compiler Independence           | 80 |

|    |       | 5.3.2   | Hardware Abstraction Layer      | 80 |

|    |       | 5.3.3   | Linker Script                   | 83 |

|    | 5.4   | Evalua  | tion                            | 86 |

|    |       | 5.4.1   | TTP/A on the LPC 2119           | 86 |

|    |       | 5.4.2   | Suggested Improvements          | 87 |

| 6  | Con   | clusion | 1                               | 89 |

|    | 6.1   |         | bution                          | 89 |

|    | 6.2   | Outloo  |                                 | 90 |

| Bi | bliog | graphy  |                                 | 91 |

# List of Figures

| Z.1  | Structure of a Node                                            | į  |

|------|----------------------------------------------------------------|----|

| 2.2  | Examples for Cluster Topologies                                | Ę  |

| 2.3  | CAN Frame Format                                               |    |

| 2.4  | TT-CAN System $Matrix[FMD^+00]$                                | 13 |

| 2.5  | Structure of a LIN Frame[LIN03]                                | 18 |

| 2.6  | Structure of a Flexray Communication Cycle[Fle05b]             | 22 |

| 2.7  | Flexray Frame Format                                           | 26 |

| 2.8  | TTP/C Cluster Cycle[TTA03]                                     | 33 |

| 2.9  | TTP/C Frame Formats[TTA03]                                     | 36 |

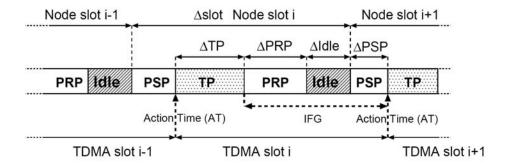

|      | TTP/C Slot Timing[TTA03]                                       | 40 |

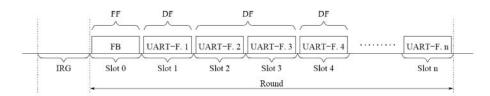

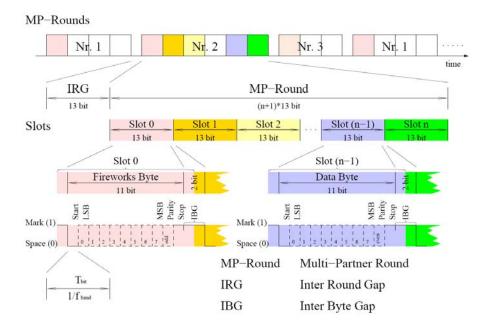

|      | TTP/A Multi Partner Round[EHK <sup>+</sup> 02]                 | 42 |

| 2.12 | Structure of a TTP/A Communication Cycle[EHK <sup>+</sup> 02]  | 45 |

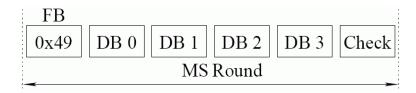

|      | Structure of a TTP/A Master – Slave Round[EHK <sup>+</sup> 02] | 45 |

| 2.14 | Structure of a TTP/A Frame[EHK <sup>+</sup> 02]                | 46 |

| 2.15 | Comparison of the Protocols                                    | 52 |

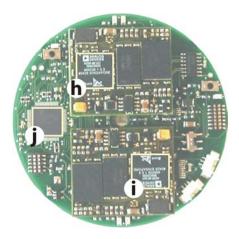

| 3.1  | The Tinyphoon Robot                                            | 55 |

| 3.2  | System Architecture of the Tinyphoon Robot                     | 56 |

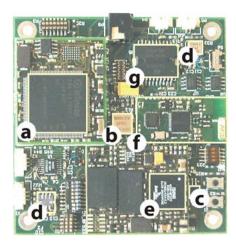

| 3.3  | The Motion Unit                                                | 57 |

| 3.4  | The TinyVision subsystem                                       | 59 |

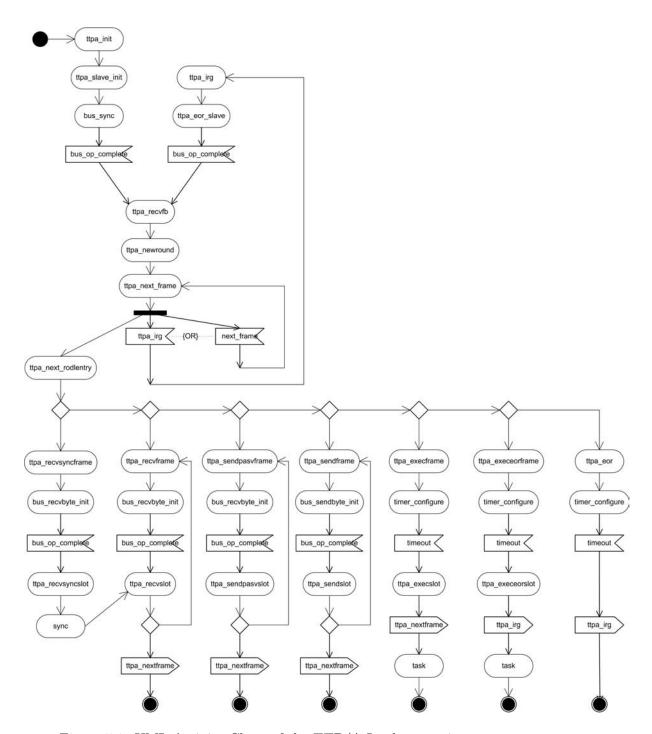

| 5.1  | UML Activity Chart of the TTP/A Implementation                 | 72 |

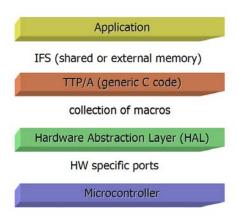

| 5.2  | Layers of the Portable TTP/A implementation                    | 81 |

# List of Tables

| 2.1 | CAN Physical Layers                                | 12 |

|-----|----------------------------------------------------|----|

| 2.2 | Flexray Physical Layer Characteristics             | 29 |

| 2.3 | Comparison of Protocol Characteristics             | 51 |

| 3.1 | Input/Output Data of the Vision Unit               | 61 |

| 3.2 | Input/Output Data of the Motion Unit               | 61 |

| 3.3 | Input/Output Data of the Decision Unit             | 62 |

| 3.4 | Tinyphoon Communication Requirements               | 63 |

| 5.1 | Timer HAL Macros                                   | 82 |

| 5.2 | Additional Timer HAL Macros for the Software UART  | 83 |

| 5.3 | UART HAL Macros                                    | 84 |

| 5.4 | HAL Macros for Memory Access                       | 84 |

| 5.5 | HAL Macros for En-/Disabling Interrupts            | 85 |

| 5.6 | HAL Macros for the Node and I/O Configuration      | 85 |

| 5.7 | HAL Macros for Controlling an External Transceiver | 85 |

# List of Listings

| 5.1 | Interface of the Bus Subsystem  | 4 |

|-----|---------------------------------|---|

| 5.2 | Structure for Bus Operations    | 4 |

| 5.3 | HW UART Receive Initialization  | 5 |

| 5.4 | HW UART Receive Setup           | б |

| 5.5 | HW UART Handle Received Byte    | 7 |

| 5.6 | HW UART Receive Time-Out        | 7 |

| 5.7 | HW UART Receive Interrupt       | 8 |

| 5.8 | HW UART Initialize Transmission | 9 |

| 5.9 | HW UART Perform Transmission    | 9 |

How wonderful it is that nobody need wait a single moment before starting to improve the world.

Anne Frank (1929 - 1945), 1952 Diary of a Young Girl

# Chapter 1

# Introduction

In many applications embedded systems take over even security and safety relevant tasks. Small integrated computer systems have been developed for controlling their environment (e.g., drive/fly by wire). The logical consequence is the development of completely autonomous systems. They explore their environment and cope with their tasks without a human user's action. Autonomous systems need to be able to collect relevant data of their environment with sensors, to make decisions based on that data and to influence the environment using actuators.

# 1.1 General Issue and Background

With the increasing computing power the complexity of embedded systems grows. Handling this complexity is a difficult issue that can be managed using distributed systems i.e., the system is subdivided in smaller parts that act jointly. The success and the quality of the collaboration highly depends on the communication system.

The communication system that connects the parts of an autonomous distributed system has to guarantee that the required pieces of information are delivered to the various subsystems with an almost constant delay and early enough, so that the autonomous system can react on changes of its environment in time i.e., real-time communication.

The case study and target platform of this work is the Tinyphoon research platform, a small robot for playing robot soccer in the Mirosot league. Because of its modular design a high performance real-time protocol is needed, which permits a communication suitable for such an autonomous system in a highly dynamic environment.

# 1.2 Problem Statements and Methodology

This work shows the applicability of a time-triggered approach as a solution to the problem of real-time communication in small real-time systems with special communication requirements.

The limited resources, the need of fast real-time communication and the variety of the involved platforms leads to high requirements:

- real-time: guaranteed transmission before a specified deadline

- performance: communication speed and efficiency

- integration: connection of the subsystems to the communication system

- availability: available in software and/or in hardware as chip or as intellectual properties

- portability: implementation for all platforms are available or source code can be ported easily

- resource-saving: low usage of Flash memory and Random Access Memory (RAM), small geometrical footprint and low power consumption

- licence: cost and conditions of licencing should allow the use in non-mass products with total system costs of less than Euro 2000.-

Two ways are chosen in this work to come up with a solution to this problem: Firstly, widely used popular protocols and decided real-time protocols are compared and analyzed. Secondly the open real-time protocol Time-Triggered Protocol – Class A (TTP/A) that has a small footprint and is designed to be implemented on off-the-shelf microcontrollers, is implemented keeping the source code portable. TTP/A is then used on a platform of the Tinyphoon project. This case study is expected to reveal, which features are missing, which features are not used at all and which issues have to be solved when making a real-time communication system portable to many different hardware platforms.

The outcome of this work is relevant for the fast growing domain of high performance distributed real-time systems with low resource requirements e.g., in the automotive industry and small autonomous systems.

# 1.3 Outline of Thesis

This thesis is divided in two parts. The first one (chapter 2) explains the basic terms and concepts and discusses the advantages and disadvantages of various real-time communication systems (TTP/A, TTP/C and Flexray). Moreover, Controller Area Network (CAN) and Local Interconnect Network (LIN) are included within this discussion because of their importance in the automotive sector. The basic features of the USB protocol and some real-time Ethernet variants are also explained.

The second part gives an overview of the target platform and the communication requirements of its subsystems (chapter 3). Then the applicability of the protocols that are discussed in the first section, for small automotive distributed systems is analyzed (chapter 4). Finally, a design of a platform independent and enhanced version of the TTP/A protocol is proposed as a solution for the Tinyphoon robot and similar systems (chapter 5).

The thesis ends with a conclusion that sums up the contributions of this work and gives an outlook on future developments (chapter 6).

A man with a watch knows what time it is.

A man with two watches is never sure.

Segal's Law

# Chapter 2

# Real-time Protocols

This chapter explains basic concepts of real-time communication protocols, provides a survey of protocols that play a major role in the automotive industry. In contrast to LIN, Flexray, Time-Triggered Protocol – Class C (TTP/C), and TTP/A the CAN protocol has not been designed as real-time protocol but an extension exists that allows its use in a real-time environment. Each protocol is described for its own then main attributes of the protocols (e. g., performance, efficiency,...) are compared.

# 2.1 Concepts

In this section some basic terms are explained that are used in the following descriptions of the real-time communication protocols. Then the meaning of *real-time* and *fault-tolerance* is discussed.

### 2.1.1 Basic Terms

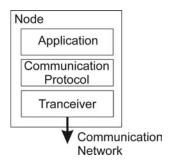

A node is an entity with a processor that runs an application. The application uses a communication protocol either in form of a software layer or in form of a piece of hardware. The bus transceiver converts logical signals in according voltage levels. In figure 2.1 the general structure of a node is shown. The bus is the medium (e.g., a kind of wire or fiber), which all nodes are connected to. The whole network, including the nodes an the bus, is called cluster. The data packet that is transported through the network is called frame. Message can be used as synonym for frame and is often used on a higher abstraction level.

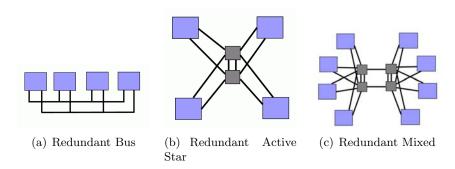

The manner how the nodes are connected to each other is called *topology*. Common network topologies for real-time communication are the *bus topology*, the *star topology* and combinations of these two topologies. Star

Figure 2.1: Structure of a Node

topologies can be passive (the branchings of the star are just connected at a central point) or active (the branchings of the star are connected to a central electronic device). In normal networks there is only one bus. To ensure that in case of a bus failure the communication can be continued, the bus can be replicated. In figure 2.2 three examples for redundant topologies are shown.

Figure 2.2: Examples for Cluster Topologies

Babbling idiots are faulty nodes that transmit data on the bus constantly and detain other nodes from sending. Bus guardians can be used to avoid this if the communication schedule is defined a priori. The bus guardians can be situated on the nodes (local bus guardians) or in a central device like a star coupler (central bus guardian). The bus guardians check on the basis of the communication schedule, if a node is allowed to write on the bus at a given time and detain faulty nodes from monopolizing the bus.

If communication is triggered by the occurrence of a particular event, it is *event-triggered* (e.g., everytime the temperature of a room changes a frame is transmitted). In *time-triggered* communication networks only the progression of time determines when a frame is sent (e.g., the temperature of the room is transmitted every 30 seconds). The time-triggered approach has two major advantages: The communication is predictable (e.g., one frame every 30 seconds) and it supports a defined error detection latency

for omission failures (in our example a node is detected faulty, if no frame has been sent for 31 seconds). The major disadvantages of time-triggered communication is that in many cases bandwidth is wasted, because redundant information is transmitted (e.g., five frames are sent with the information "24°C", then with "25°C"; in an event-triggered system only two frames are needed instead of six). Moreover, events can be missed is the time-triggered communication is too slow (e.g., the room temperature increases from 24°C to 26°C within 30 seconds; the time-triggered system only sends two messages, the event-triggered three). However, it depends on the application whether this is a problem and whether it can be avoided by increasing the update rate of the time-triggered system.

The efficiency of a communication protocol is the proportion of the durations of the transmission of the plain payload and of the complete data frame. The efficiency strongly depends on the actual application. In the following the best case efficiency of the protocols is calculated.

## 2.1.2 Real-Time

In a *real-time* systems the correctness of a result does not only depend on its value but also on the time[Kop97]. The error in the time domain can be as severe as an error in the value domain.

Every communication protocol delays the messages that it transports. Real-time protocols ensure that this delay is predictable and that the deadline for the arrival of the message is not missed. Moreover, by using a real-time protocol the jitter of that delay can be kept small. That means, that from one communication round to another the delay is almost constant. This is important for the implementation of feedback control algorithms, which are in general unable to handle varying delays.

If the clocks of all nodes in a cluster are synchronized, a *global time* is established. In a cluster with a global time a time stamp refers to the same moment in time on all nodes. The clocks of a cluster cannot be synchronized perfectly [Kop97]. The greatest difference between two clocks in a cluster is the *precision* of the cluster.

Three types of real-time systems can be distinguished based on the consequences when a deadline is missed[Kop97]:

**Soft Real-Time** In soft real-time systems the violation of a deadline causes only a degradation of the service that is provided by the system (e.g., voice-over-IP, video streaming, ...).

Firm Real-Time In a firm real-time system the violation of a deadline

prevents the system from working correctly but the malfunction has no drastic consequences (e.g. small robots)

Hard Real-Time In hard real-time systems the violation of a deadline causes a catastrophe (e.g., fly-by-wire system, nuclear plant automatization, break-by-wire, ...).

#### 2.1.3 Fault Tolerance

A fault-tolerant system continues being fully operational even if faults occur. The type and number of faults that have to be tolerated are specified in the fault hypothesis. Faults that are not covered by the fault hypothesis, could cause a malfunction. To prevent the system from a steady malfunction a never-give-up strategy can be implemented. It tries to bring the system back to an operational state even after an unexpected fault.

## 2.2 Controller Area Network

The first CAN specification was released by the Robert Bosch GmbH in the year 1985. It describes the implementation of the first (physical) and the second (data link) layer of the Open System Interconnect (OSI) model. Currently various implementations for the application layer of CAN communication systems exist (e.g. CANopen, SDS, DeviceNet and CAL) and CAN has become an International Organization for Standardization (ISO) standard. This standard with the number 11898 is divided in four parts: 1. data link layer and physical signalling, 2. high-speed medium access unit, 3. low-speed, fault-tolerant, medium dependent interface, 4. time-triggered communication.<sup>1</sup>

#### 2.2.1 Mode of Operation

CAN nodes do not have addresses, but Instead every message has an identifier. The nodes of a cluster have to know, which messages they are interested in and how to interpret them.

The medium access in a CAN cluster is controlled in a decentralized way. Data is encoded using a recessive and a dominant voltage level where a dominant level always prevails a recessive one. Every node of the cluster listens on the bus and verifies, that no other node is currently sending. Then the node starts the transmission of the message identifier field. After applying the appropriate voltage level (recessive or dominant) according to the bit being transmitted, the node checks the state of the bus. If it is equal

<sup>&</sup>lt;sup>1</sup>available at www.iso.org

to the state aimed by the node the transmission of the bit is successful. If the node tries to transmit a recessive symbol but the bus stays at a dominant level, another node is transmitting a dominant Symbol simultaneously. That is the other node has started transmitting a message with a higher priority at the same time.

This technique of distributed arbitration is called Carrier Sense Multiple Access/Collision Avoidance (CSMA/CA). If messages collide, the message with the identifier starting with the most dominant bits has the highest priority and is transmitted successfully. The transmission of all other messages is canceled. They are retransmitted as soon as the bus is idle again.

CAN defines four different types of frames. Remote frames are used to request data from another node, which responds with the according data frame with the same identifier. Data frames may also be sent spontaneously. Error and overflow frames are used to signal error conditions on the bus.

#### 2.2.2 Additional Services

Beyond the normal data transportation CAN provides two additional services.

# Acknowledgement

During the transmission of a frame a recessive bit is sent, the acknowledgement slot. This bit is overwritten with a dominant one by a receiver, if the frame has been received successfully. By checking the acknowledgement slot a sender can notice if its transmission has been received successfully by at least one node.

#### Error Signaling and Fault Confinement

All nodes perform tests to detect various errors (bit monitoring, bit stuffing check, frame check, acknowledgement and Cyclic Redundancy Check (CRC)). A detected error can be signaled to the other nodes by transmitting an error frame. Thus, all nodes of the clusters are informed about the error and may discard the received message to keep the data consistent within the cluster. The transmitters will try to resend the message as soon as the bus is available again.

The reception of an error frame and the results of the own error detection are used to maintain two counters, one for receiving and one for transmitting errors. The current value of these counters represents the quality of the

communication. Their values are increased in case of an error and decreased whenever communication is performed successfully.

Depending on these two values the CAN is one of the three states:

**Error active** The controller participates in the communication and sends error frames when it detects an error.

**Error passive** The controller participates in the communication and suspends communication for the time of one error frame when it detects an error.

Bus off The controller does not participate in the communication at all.

## 2.2.3 Packet Format

Four different frame formats are defined in the CAN specification:

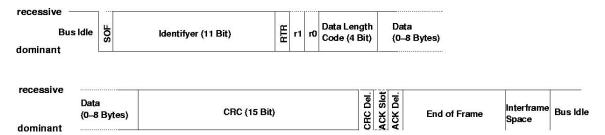

**Data frame** Data frames are used for sending application data from one node to another. In figure 2.3 the structure of the CAN data frame is shown.

Figure 2.3: CAN Frame Format

**SOF** The start of frame field is a single dominant bit that marks the start of the data or remote frame.

**Identifier** The identifier is used for classifying the type of the message. This field is also used for prioritizing the frames using the CSMA/CA technique.

RTR The Remote Transmission Request (RTR) bit is used to distinguish data (RTS bit is dominant) and remote frames (RTR bit is recessive). This bit is also used for Carrier Sense Multiple Access/Collision Detection (CSMA/CD).

**r1** and **r0** The bits r0 and r1 are reserved. They have to be transmitted as dominant bits but are ignored by the receiver.

Data Length Code The data length code stores the length of the payload. It is encoded as standard binary number from zero to eight. The first bit is the Most Significant Bit (MSB) and dominant bits represent a binary zero and recessive bits a binary one.

**Data** The data field contains the payload and is transferred MSB first.

**CRC** The CRC code is 15 bits long and is generated from all fields described above using the generator polynomial shown in equation 2.1.

$$x^{1}5 + x^{1}4 + x^{1}0 + x^{8} + x^{7} + x^{4} + x^{3} + 1$$

(2.1)

**CRC Delimiter** This single recessive bit delimits the CRC.

**Acknowledge Slot** This single recessive bit is overwritten by the receiver, if a correct frame has been received.

Acknowledge Delimiter Another single recessive bit.

**End of Frame** The end of the frame is signaled by 7 recessive bits.

Remote frame This type of frames is used for polling other nodes. The structure of these frames is almost the same as the structure of the data frames. But remote frames do not have a payload, the Remote Transmission Request (RTR) bit is recessive and the data length code is interpreted as the length of the requested data.

**Error frame** Error frames are used for signaling errors. It consists of six to twelve dominant bits and eight recessive ones.

Overload frame These frames consist of six dominant and twelve recessive ones. They can only be distinguished from error frames because of the context they occur in.

Two data or remote frames are always divided by at least three recessive bits if no overload or error frame is transmitted.

Part B of the CAN specification introduces extended frames. These frames have a 29 bit long identifier field. The additional 18 bits of the identifier are prefixed with the substitute remote request bit (SRR, recessive) and the identifier extension bit (IDE, also recessive) and are filled in after the eleven identifier bits of the standard frame.

In this way the SRR bit replaces the RTR bit of the standard frame and the IDE bit the reserved bit r1. Standard and extended frames are distinguished by the IDE bit. Thus, both type of frames can be used within the same cluster.

# 2.2.4 Data Encoding

CAN uses the Non-Return to Zero (NRZ) encoding. A bit is signaled by applying a dominant voltage level to the bus or releasing it for the complete bit time.

On all fields of data or remote frames except the delimiters, the acknowledgment slot and the end of frame field *bit stuffing* is applied. Whenever five equal bits are transmitted consecutively a complementary bit is filled in.

Some error and overflows violate the bit stuffing rule and can thus be identified as bit stuffing errors.

# 2.2.5 Physical Layer

Multiple standards describe a physical layer for CAN . The most important ones are:  $^2$

**ISO 11898-2 high speed** This physical layer specification provides a communication speed of up to 1 Mbit and is the most common physical layer for CAN networks. Signals are transmitted differentially on two wires using -2 V and +7 V. Only bus topology is allowed. Each end of the bus has to be terminated with a  $120\Omega$  resistor.

ISO 11898-3 fault-tolerant This specification targets applications where fault tolerance is required. It needs no termination resistors and supports various topologies. During normal operation differential communication is used as in ISO 11898-2 at a speed of up to 125kbit/s. But communication can be performed even using only one of the two wires in a degraded mode with reduced communication speed. This fact makes this physical layer fault-tolerant. The ISO 11898-3 specification is mainly used in the automotive industry for car body electronics.

SAE J2411 single wire This specification has been designed for the control of comfort electronics in cars. Short single wire networks of almost any topology can be created. A maximum of 32 nodes can communicate in this network with a speed of 33.3 kbit/s. A high speed diagnostic mode allows speeds up to 83.3 kbit/s.

**ISO 11992 point-to-point** In this specification a physical layer is defined using daisy-chaining to connect the nodes. The networks must have a bus topology and must not exceed 40m of length. The communication

<sup>&</sup>lt;sup>2</sup>http://www.can-cia.org/can/physical-layer/

|             | ISO 11898-2  | ISO 11898-3    | SAE J2411    | ISO 11992             |  |  |

|-------------|--------------|----------------|--------------|-----------------------|--|--|

| type        | high speed   | fault-tolerant | single wire  | point-to-point        |  |  |

| maximum     | 1 Mbit       | 125  kbit/s    | 33.3  kbit/s | $125 \mathrm{kbit/s}$ |  |  |

| speed       |              |                |              |                       |  |  |

| max. nodes  | 110          | 32             | 32           | 2                     |  |  |

| max. net-   | 6500m        | 500m           |              | 40 m                  |  |  |

| work length |              |                |              | i                     |  |  |

| topology    | bus          |                |              | daisy-chain           |  |  |

| fault-      | no           | yes            | no           | yes                   |  |  |

| tolerant    |              |                |              |                       |  |  |

| connection  | 2 wires      | 2 wires        | 1 wire       | unshielded            |  |  |

|             |              |                |              | twisted pair          |  |  |

| voltage     | -2V/+7V      | -2V/+7V, sup-  |              | supply: 12V or        |  |  |

|             |              | ply: 5V        |              | 24V                   |  |  |

| termination | 120 Ω        | none           |              | -                     |  |  |

| usage       | standard     | car body elec- | car comfort  | vehicle with          |  |  |

|             | applications | tronic         | electronic   | trailer(s)            |  |  |

Table 2.1: CAN Physical Layers

speed is up to 125 kbit/s. The ISO 11992 standard has been developed to electrically connect vehicles with their trailers.

Many other physical layers are also used for CAN (e.g., optical physical layers), but those mentioned above are the most popular ones. Because of the need of a high bit rate in the field of application of this thesis, *CAN physical layer* refers to the ISO 11898-2 standard unless otherwise noted.

The length of the bus is limited by the communication speed, because of the bit-wise arbitration in CAN. It has to be ensured, that every CAN node reads the same bit value from the bus, if two nodes start sending simultaneously. Thus, the propagation delay between two arbitrary nodes must not exceed a certain value. This value depends on the configuration of the cluster, but is allowed to be at most  $\frac{11}{8}$  of the length of a bit.

## 2.2.6 Real-Time Extensions

The basic CAN is not suitable for the communication in hard real-time systems. The Carrier Sense Multiple Access/Collision Detection (CSMA/CD) medium access strategy introduces a non-deterministic jitter of the latency. Only the message with the highest priority has a fixed, defined latency, if it can be presumed, that the system design inhibits a collision of two frames

with the highest priority. The jitter of the latency is undetermined even for messages with the second highest priority, because the whole capacity of the bus may be used for messages with the highest priority and starvation of nodes that try to send messages with a smaller priority, might occur.

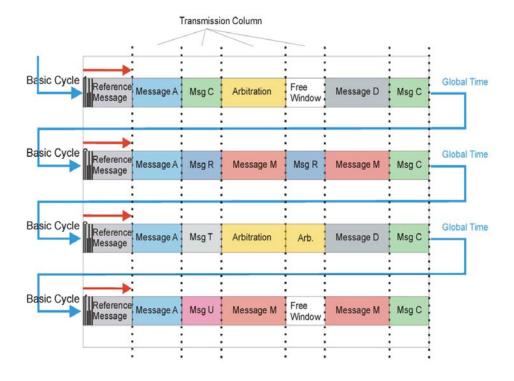

Time-Triggered CAN (TT-CAN)[ISO04] (ISO standard 11898-4) solves this problem by introducing a time-triggered additional medium access strategy that is time-triggered. A time master node starts the communication cycle by transmitting a reference message. The falling edge of the start of frame bit of this message marks the start of the communication cycle, the basic cycle. The basic cycle is divided in time windows (slots) of various lengths. In exclusive time windows only one node is allowed to transmit a message. In arbitrating time windows all nodes are allowed to send and CSMA/CA is used for bus arbitration.

Every node has to know, in which slot it has to transmit or receive a certain message. The schedule of a cluster may have various basic cycles of the same structure, which are grouped to the system matrix. In figure 2.4 an example for a TT-CAN system matrix is shown. The lines are formed by the basic cycles. The rows are the time windows. Adjacent arbitrating time windows may be combined to a single large one.

Figure 2.4: TT-CAN System Matrix[FMD<sup>+</sup>00]

Two levels of TT-CAN are defined. TT-CAN level one the time is measured in bit times of the CAN bus. Thus, the timeliness of the of the communication can be guaranteed, but no global time is established. Level 2 of TT-CAN addresses this feature. The time master includes its current time in the reference message. The other nodes measure the time between two reference messages and correct their clocks to match the values sent by the master. The time in TT-CAN level 2 clusters is measured in Network Time Unit (NTU). The duration of a NTU is in the same order as the duration of one bit time. A global time with a precision of one NTU can be established.

The time master is obviously a single point of failure. Therefore, the time master can be replicated in a TT-CAN cluster. If no traffic is received a potential time master starts sending reference frames with a certain priority. If it receives a reference frame with a lower priority, it transmits a reference frame at the start of the next basic cycle. The other time master loses the arbitration because of the CSMA/CA algorithm. Thus, conflicts between potential time masters that start sending coinstantaneously are resolved and the potential time master with the highest priority succeeds. When an expected reference frame is not sent within a certain time-out, potential time masters start transmitting reference frames.

Though TT-CAN can be build in software using a CAN controller, the hardware of this controller at least has to be equipped with an additional circuitry for time-stamping incoming messages[HMFH00].

#### 2.2.7 Efficiency

The maximum length of the payload of a CAN frame is eight bytes (= 64 bits =  $T_{payload\_max}$ ). The overhead caused by wrapping the payload in a frame ( $T_{framing}$ ) is calculated according to equation 2.7.

$$n_{header} = n_{sof} + n_{id} + n_{rtr} + n_{reserved} + n_{lengthcode} =$$

(2.2)

$$= 1 + 11 + 1 + 2 + 4 = 19 \tag{2.3}$$

$$n_{trailer} = n_{crc} + n_{crcdel} + n_{ackslot} + n_{ackdel} + n_{eof} =$$

(2.4)

$$= 15 + 1 + 1 + 1 + 7 = 25 \tag{2.5}$$

$$T_{framing} = (n_{header} + n_{trailer}) \cdot T_{bit} = \tag{2.6}$$

$$= (19 + 25) \cdot T_{bit} = 44 \cdot T_{bit} \tag{2.7}$$

Another overhead  $(T_{coding})$  is added because bit stuffing is performed and the bus has to be released for at least three bit times before a new frame is

started. The amount of bits that are stuffed in the frame depends on the content of the frame and the identifier. Thus, an upper and a lower bound are calculated for the coding overhead.

$$T_{coding\_max} = n_{stuffbits\_max} \cdot T_{bit} + T_{interframe} =$$

(2.8)

$$= \frac{n_{header} + n_{maxpayload} + n_{crc}}{5} \cdot T_{bit} + 3 \cdot T_{bit} = \tag{2.9}$$

$$= \frac{n_{header} + n_{maxpayload} + n_{crc}}{5} \cdot T_{bit} + 3 \cdot T_{bit} =$$

$$= (\frac{19 + 64 + 15}{5} + 3) \cdot T_{bit} = (\frac{98}{5} + 3) \cdot T_{bit} = 22 \cdot T_{bit}$$

(2.10)

$$T_{coding\ min} = (0+3) \cdot T_{bit} = 3 \cdot T_{bit} \tag{2.11}$$

$$efficiency_{max} = \frac{T_{payload\_max}}{T_{payload\_max} + T_{framing} + T_{coding\_min}} = (2.12)$$

$$= \frac{64 \cdot T_{bit}}{(64 + 44 + 3) \cdot T_{bit}} = \frac{64 \cdot T_{bit}}{111 \cdot T_{bit}} = 0.5766$$

(2.13)

$$= \frac{64 \cdot T_{bit}}{(64 + 44 + 3) \cdot T_{bit}} = \frac{64 \cdot T_{bit}}{111 \cdot T_{bit}} = 0.5766 \tag{2.13}$$

$$efficiency'_{max} = \frac{T_{payload\_max}}{T_{payload\_max} + T_{framing} + T_{coding\_max}} =$$

(2.14)

$$= \frac{64 \cdot T_{bit}}{(64 + 44 + 22) \cdot T_{bit}} = \frac{64 \cdot T_{bit}}{130 \cdot T_{bit}} \cdot T_{bit} = 0.4923 \quad (2.15)$$

Depending on content and the identifier of the frames from zero to 19 bits are stuffed in the frame. The maximum efficiency of CAN is 57.66% if no bit stuffing occurs. The TT-CAN protocol is less efficient because an additional overhead is caused by embedding the communication in time slots.

#### 2.2.8 Availability

CAN controllers are available in many different versions: as Intellectual Property (IP) (e.g. net list), as stand-alone controller or integrated in various microcontrollers.

Due to this variety and the low costs of these hardware implementations, software implementations of CAN are not common.

Manufactures of CAN enabled Integrated Circuits (IC) have to license CAN from the Robert Bosch GmbH.

# 2.3 Local Interconnect Network

The Local Interconnect Network (LIN) is developed by the LIN consortium<sup>3</sup>. This protocol has been designed to satisfy the needs of the automotive industry for cheap and simple communication protocol for multiplexing various signals on a single bus. LIN can be used for real-time communication, but it does not offer a global-time or fault-tolerance features. The protocol can be implemented in hardware and in software even on low performance off-the-shelf microcontrollers using a standard Universal Asynchronous Receiver and Transmitter (UART). This description of the LIN protocol is based on the LIN specification 2.0 issued in 2003[LIN03].

# 2.3.1 Mode of Operation

LIN is a master-slave protocol. In every cluster a single master polls the slaves for a certain information according to its internal schedule. The polling process is implemented by splitting the LIN frame. The header is sent by the master. It contains unique mark for the frame start and an identifier that informs the nodes about the length and the meaning of the data. The actual data is then sent in the response field by the slaves, which is responsible for sending this type of messages. Every LIN master node also incorporates a client implementation, which is used for sending and receiving data as well as for error detection.

Beyond 60 identifiers (0 - 59) for data frames special identifiers exist for diagnostic frames (60 and 61) and user defined frames (62). The identifier 63 is reserved for future use. The payload has a maximum length of eight bytes and is divided in signals. A signal is a value of a certain meaning and a certain length. LIN frames with the same identifier always contain the same signals at the same position.

Each node has to be configured to read the frames, it is interested in, from the bus, and to respond to headers of frames it has to transmit. The complete schedule of the communication is only known by the master and is processed cyclically.

The LIN specification defines three modes a frame can be transmitted:

Unconditional frames These frames are standard way of transmitting frames. When the transmission of a certain frame is scheduled, the master sends the header and the according node completes the frame with its data and a checksum.

**Event-triggered frames** To reduce the average bandwidth requirements for rarely changing signals, event-triggered frames have been intro-

<sup>3</sup>http://www.linlin-subbus.org

duced. Multiple nodes may react on the same identifier. The slaves only respond on the header if they have something to transmit (e.g., an event has occurred). If none of the slaves responds, the master knows that no event happened. If one of the slaves replies, the frame is received correctly. However, another slave also may have started a transmission and stopped sending as it noticed the ongoing bus activity. Therefore, the master has to schedule another event triggered frame to ensure that there are no other events pending. If more than one slave responds on the header, the frame is corrupted, the master detects a checksum error and has to poll all slaves using unconditional frames. The answers of the slaves contain the identifier of the related unconditional frame. Thus, it can be distinguish, which event occurred.

**Sporadic frames** Sporadic frames can be scheduled by the master in free slots of the predefined, fixed communication schedule, whenever needed. Usually the slave implementation of the master node transmits the data of this frame.

#### 2.3.2 Additional Services

Beyond the standard communication features, LIN offers means for diagnostic communication and status management is able wake-up a sleeping cluster.

#### **Diagnostic Communication**

The LIN consortium has defined a special diagnostic transport layer. Diagnostic communication is performed using special frames, master request frames (identifier 60) and slave response frames (identifier 61).

The nodes of a LIN cluster have a node address for diagnostic communication. Slaves can be addressed and messages up to 4095 bytes can be exchanged. The diagnostic transport layer fragments and defragments the messages accordingly, so they can be transported using the diagnostic frames that carry at most eight bytes. Thus, the same diagnostic protocols can be used in the LIN cluster and on a higher level communication systems that the cluster might be connected to.

#### Status management

Every node has to report its state with at least one bit in one of the unconditional frames, which it transmits. This bit is set, if an error occurred during sending or receiving the response fields. The bit is cleared after its transmission. The master processes these bits an deduces the state of the nodes.

But also the slave nodes use this information and the information about successful data transfers to appraise their current status.

### Cluster Wake-up

The master can put the cluster in sleep mode by sending a master request frame with the invalid node address zero. Once the cluster is asleep every node can wake it up by keeping the bus in the dominant state for  $250\mu s$  to 5ms. After the end of the wake-up signal all salves are ready for participating in the communication within 100ms. The master starts executing its communication schedule not longer than 150ms after this signal.

# 2.3.3 Frame Format

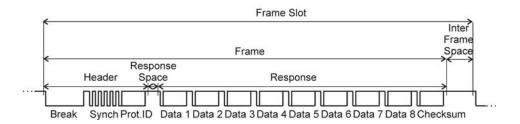

Figure 2.5 shows the structure of a LIN frame.

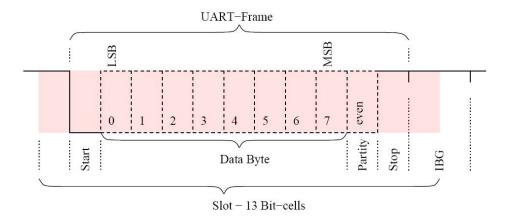

Figure 2.5: Structure of a LIN Frame[LIN03]

**Header** The master starts a new frame by sending the header.

**Break symbol** The break symbol consists of at least 13 dominant bits, followed by a single recessive one. It is a unique symbol that signals the start of a new frame and that can not occur within a regular frame.

**Synch byte** The synch byte is a single byte with the value 0x55. It forms a pattern of alternating bit values that can be used by the slaves to synchronize their bit clock to the bit timing of the master.

**Protected identifier** The protected identifier consists of a six bit long identifier (0-63) and two parity bits that are calculated as shown in equation 2.17.  $\oplus$  is the operator for the exclusive-or

operation and ID[i] is the bit number i of the ID.

$$Bit6 = ID[0] \oplus ID[1] \oplus ID[2] \oplus ID[4] \tag{2.16}$$

$$Bit7 = \neg (ID[1] \oplus ID[3] \oplus ID[4] \oplus ID[5]) \tag{2.17}$$

**Response** A slave responds to the header and completes the frame by transmitting the response field.

**Data** The data field contains at least one at most eight bytes of data. Signals with a length of more than one byte are transmitted in little-endian order.

Checksum In the LIN specification two types of checksums are defined. The classic checksum is calculated using the bytes of the data field only. The calculation of the extended checksum also includes the protected identifier. Both types of checksums are calculated in the same way: All bytes are added in a eight bit register. In case of an overflow, the carry bit is also added. The inverted result of this calculation is then used as checksum.

# 2.3.4 Data Encoding

LIN uses standard UART frames with NRZ encoding. The frames have one start, one stop bit and eight data bits that are sent Least Significant Bit (LSB) first.

There is only one exception. The break field consists of at least of 13 consecutive dominant bits. This pattern is not a valid UART frame.

Every two bytes of a frame may be separated with an additional space. The total length of the space must be smaller than 40% of the total frame length.

Two frames are separated by an inter frame space.

# 2.3.5 Physical Layer

LIN uses an improved version of the physical layer defined in the ISO standard  $9141^4$ . The bidirectional bus consists of a single wire and supports a data rate of up to 20 kbit/s. The LIN bus forms a wired AND gate. Every LIN transmitter has a built-in pull-up resistor and can pull the bus down to ground level with a transistor. The recessive state ( $\geq 0.6$ V) signals a logical one and the dominant state ( $\leq 0.4$ V) signals a logical zero.

The maximum length of the LIN bus is 40 meters and up to 16 LIN nodes may be connected.

<sup>&</sup>lt;sup>4</sup>available at http://www.iso.org

#### 2.3.6 Host Interface

The LIN specification defines a set of C-functions as interface to the host application. This set includes functions for initialization, for manipulating and querying the predefined signals, for managing the schedule in the master node and for controlling the bus interface. A configuration and a diagnostic Application Programming Interface (API) are also available.

Beyond the programming interface the LIN specification specifies a file formats that store all communication-relevant settings, e.g., signals, frames and the master schedule (LIN description file) as well as a description of LIN nodes (node capability file). These file formats ensure the correct collaboration of development tools of various companies.

# 2.3.7 Efficiency

The maximum efficiency of a LIN frame can be calculated from the transferred bytes of data and the minimal slot length that is needed to schedule this message.

$T_{header}$  is the amount of time for transmitting the header that has always the same length.  $T_{data\_max}$  is the time needed for transferring the payload data of the maximum length of eight bytes.  $T_{response\_max}$  includes  $T_{data\_max}$  and the time needed to transmit the checksum. Header and response transmission time are added to get the minimum time  $T_{frame\_max}$  for transmitting a LIN frame with a payload of maximum length.

$$T_{header} = (T_{break} + T_{synch} + T_{id}) \cdot T_{bit} = \tag{2.18}$$

$$= (14 + 10 + 10) \cdot T_{bit} = 34 \cdot T_{bit} \tag{2.19}$$

$$T_{data\_max} = N_{data\_max} \cdot 10 \cdot T_{bit} = \tag{2.20}$$

$$= 8 \cdot 10 \cdot T_{bit} = 80 \cdot T_{bit} \tag{2.21}$$

$$T_{response\_max} = T_{data\_max} + T_{crc} = (2.22)$$

$$= 80 \cdot T_{bit} + 10 \cdot T_{bit} = 90 \cdot T_{bit} \tag{2.23}$$

$$T_{frame\_max} = (T_{header} + T_{response\_max}) \cdot T_{bit} =$$

(2.24)

$$= (34 + 90) \cdot T_{bit} = 124 \cdot T_{bit} \tag{2.25}$$

According to the LIN specification, the minimum length of a frame slot is 40% longer than the minimum length of the packet that is sent in the slot.

$$T_{frame\_slot} = T_{frame\_max} \cdot 1.4 = \tag{2.26}$$

$$= 124 \cdot T_{bit} \cdot 1.4 = 173.6 \cdot T_{bit} \tag{2.27}$$

The efficiency of LIN is calculated by opposing the minimum time for a frame slot  $(T_{frame\_slot})$  and the time for sending the actual payload  $(T_{data\_max})$ .

$$efficiency_{max} = \frac{T_{data\_max}}{T_{frame\_slot}} =$$

(2.28)

=  $\frac{80 \cdot T_{bit}}{173.6 \cdot T_{bit}} = \frac{80}{173.6} = 0.4608$  (2.29)

$$= \frac{80 \cdot T_{bit}}{173.6 \cdot T_{bit}} = \frac{80}{173.6} = 0.4608 \tag{2.29}$$

The upper bound for the efficiency of the LIN protocol is thus 46.08%.

#### 2.3.8 Availability

LIN is often implemented in software, but there are also hardware implementations and LIN IPs.

Only members may use intellectual properties of the LIN consortium. To become an associated member an admission fee of \$10,000.- and an annual fee has to be paid. Members do not have to pay any license fees for their products that use LIN. The specification is openly available for download on the website of the consortium<sup>5</sup>.

#### 2.4 Flexray

Flexray is an upcoming standard for real-time communication in the automotive industry. It is developed by the Flexray consortium<sup>6</sup>. This section is based on the Flexray Protocol Specification[Fle05b] and the Flexray Physical Layer Specification[Fle05a].

#### 2.4.1 Mode of Operation

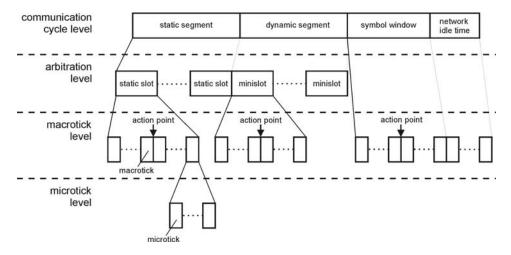

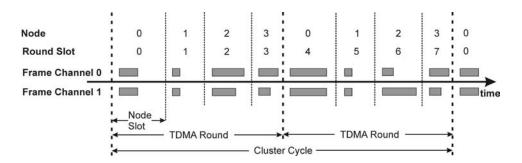

The Flexray protocol is executed in communication cycles. Each cycle consists of a static segment, a dynamic segment, a symbol window and a network idle time. The length of each segment is specified in macroticks. If no dynamic segment or the symbol is not used the length of the respective segment can be set to zero. The static and dynamic segments are divided into time slots. The clocks of all nodes are synchronized. Therefore, every node knows the number of the current slot and when a new slot starts. An action point is defined by specifying the number of macroticks since the start of a slot. The transmitting node starts sending at the according action point.

<sup>&</sup>lt;sup>5</sup>http://www.lin-subbus.org/frontend/stylesheets/request\_doc.htm, visited on 2006-10-06

<sup>&</sup>lt;sup>6</sup>http://www.flexray.org

Every frame has an identifier that specifies the number of the slot, which it has to be sent in. For every channel each identifier must not be used more than once within one communication cycle.

Figure 2.6 shows the structure of a Flexray communication cycle.

Figure 2.6: Structure of a Flexray Communication Cycle[Fle05b]

There are three possibilities how communication in a Flexray cluster can be performed:

- 1. The dynamic segment is not used. All communication is performed within the static segment.

- 2. Only one static slot is used for synchronization. The actual communication is performed within the dynamic segment.

- 3. Both, the static and the dynamic segment are used for communication.

It depends on the requirements of the application, which of these modes of operation is adequate.

#### Static Segment

The static segment is used to exchange information with a guaranteed maximum delay and jitter. Time Division Multiple Access (TDMA) is used for arbitration within the static segments. The segment is divided into time slots with the same length that is equal for both channels.

The application can decide to send the same frame on both channels. Thus, faults on one channel can be tolerated. If fault tolerance is not needed the communication speed can be doubled for particular slots by sending different frames on each channel.

### Dynamic Segment

The dynamic segment is used to exchange information that has to be transmitted in varying and unknown intervals, efficiently. However, generally it is not possible to determine a maximum delay for frames that are transmitted within the dynamic segment. Mini-slotting is used for the arbitration within this segment. The segment is divided into mini-slots. Dynamic slots are superimposed on them. If no data is transmitted in a dynamic slot, it only consists of one single mini-slot. Otherwise the dynamic slot is expanded over as many mini-slots as needed for the transmission of the complete frame. The number of mini-slots depends on the length of the dynamic segment and must not be exceeded. The smaller the identifier of a frame, the smaller is the number of the slot a message is assigned to and the higher is the priority of this message.

#### Symbol Window

In this segment symbols (such as the Media Access Test Symbol) may be transmitted. The protocol performs no arbitration for this segment. This has to be handled by the application.

#### Network Idle Time

No communication is allowed during the network idle time. The length of the idle time is the total length of the communication cycle minus the length of the static segment, of the dynamic segment and of the symbol window.

# **Addressing Modes**

The nodes of a Flexray cluster do not have an address on the protocol layer. But all frames have an identifier that enables the receiving nodes to filter incoming messages. Only those important for the application layer are stored.

#### **Clock Synchronization**

The right timing is crucial for the communication within a Flexray cluster. All nodes must agree on the number and the start of the current macrotick. This can only be guaranteed by performing a clock synchronization.

Within a Flexray cluster this is performed using the Fault-Tolerant Midpoint Algorithm [LL84]. Every node saves the arrival time of data frames that are transmitted in the static segment and have a special bit set. These frames are called Sync Frames and are transmitted from nodes that have a reliable

clock that should be used for synchronization. Then the sender's action point (the point in time when the sender started transmitting the frame) is estimated by considering propagation delay. The difference between the estimated action point of the sending nodes and the action point of the receiving node are stored in a sorted list. If a frame is transmitted an both channels, the smaller difference is stored in the list.

The k smallest and the k largest values are removed from the list, where k is calculated from the number of stored differences (n) using equation 2.30.

$$k = \begin{cases} 0 & \text{if } 1 \le n \le 2\\ 1 & \text{if } 3 \le n \le 7\\ 2 & \text{if } 8 \le n \end{cases}$$

(2.30)

The largest and the smallest of the remaining values are averaged to calculate the midpoint value. This value interpreted as the deviation of the node's clock from the global time. Offset and rate error are calculated from the deviation and corrected every second communication cycle during the network idle time.

In a Flexray cluster with a communication speed of 10Mbit/s the clocks can be synchronized with a precision better than  $1\mu s$ .[Fle05b]

#### **Node Integration**

When a new node is connected to a cluster it has to adopt the current timing of the cluster to be able to join the communication. The process of integration differs for normal nodes and nodes that can initiate a cluster start-up (coldstart nodes)

Normal nodes These listen on both Flexray channels and tries to receive two valid startup frames from a coldstart node, adopts its timing and performs clock synchronization. Then it searches for startup frames from two distinct coldstart nodes and checks whether they fit in the own schedule. If this is the case for four cluster cycles and clock synchronization can be performed without errors the node enters the normal operation mode.

Coldstart nodes These perform a very similar procedure of integration, but they start normal operation after synchronizing themselves with at least one coldstart node for three cluster cycles.

#### Cluster Startup

If coldstart nodes do not receive any Flexray frames during the process of integration they initiate a cluster startup. The application may veto the startup.

The startup is initiated by sending a Collision Avoidance Symbol (CAS). Then the coldstart node starts sending startup frames accordingly to its schedule. If a startup frame is received between the transmission of the CAS and the first transmission of the startup frame the node stops the startup and tries to integrate on the other coldstart node that transmitted this frame. Thus, the scheduling of the startup frame decides, which coldstart node performs the startup if more then one node initiated the cluster startup simultaneously by sending the CAS.

#### **Fault Handling**

A fatal error within the protocol engine or the product specific part causes the Flexray node to stop participating in the communication immediately. This stop can also be encompassed by the application through the Controller Host Interface (CHI) .

Non fatal errors may cause the protocol engine to only degrade the communication service that means it receives data frames from the bus but does not transmit any. However, the exact behavior in such cases depends on the configuration.

#### 2.4.2 Additional Services

Beyond the basic data transportation features Flexray provides following additional services.

# Fault Tolerance

Flexray supports the implementation of a fault-tolerant communication. The dual-channel topology provides means to implement communication systems that can tolerate the breakdown of one channel. But Flexray does not provide a complete ready-to-use solution.

Also the clock synchronization algorithm, the node integration and cluster start-up process of Flexray are designed to tolerate faults. However, a fault hypothesis is not part of the Flexray specification.

In an additional specification bus guardians for Flexray controller are described. These guardians are are used locally, directly on the Flexray node. The bus guardians protect only the static segment against timing violations.

#### Global Time

To synchronize the medium access of the nodes within the TDMA scheme the clocks of the communication controllers have to be synchronized as described earlier. All communication controller of a Flexray cluster agree with a limited deviation on this time. It is made available to the host application and can be used for performing actions synchronously to the communication or for time-stamping.

### Membership

Flexray supports the implementation of a membership service but does not provide a ready-to-use solution.

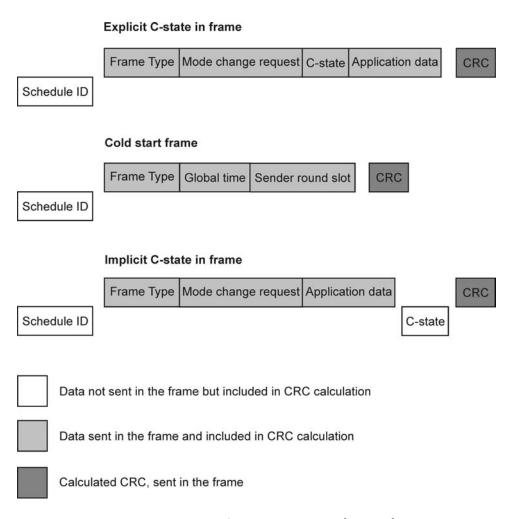

The frame format defines a flag that specifies whether a membership vector is included within the payload or not. During a communication cycle Flexray controllers process the vector from all valid incoming frames from both channels and perform an or-operation. The result can be used by the application for implementing a membership service. It is the responsibility of the application software to calculate and to transmit an appropriate network management vector.

## Cluster Wake-Up

To save energy a cluster can be set to sleep mode. Every node of the cluster can wake it up by sending the wake-up symbol. The transmission of this symbol is triggered by the host application. The bus drivers of the other nodes detect the wake-up symbol and wake the communication controller that inform the host processor. The wake-up is only sent on one of the two channels to ensure that communication is still possible, in case a faulty node sends wake-up symbols continuously.

## 2.4.3 Frame Format

The Flexray frame format is shown in figure 2.7.

| Header (5 Bytes) |             |        |               |                | Payload (0-254 Bytes) |           |  | Trailer (3 Bytes) |         |        |        |

|------------------|-------------|--------|---------------|----------------|-----------------------|-----------|--|-------------------|---------|--------|--------|

| Byte             | 0 Byte 1    | Byte 2 | Byte 3        | Byte 4         | Byte 5                | Byte 6    |  | B. n+5            | B. n+6  | B. n+7 | B. n+8 |

| Bits             | Frame<br>ID | Length | Header<br>CRC | Cycle<br>Count | Duta                  | Data<br>1 |  | Data<br>n         |         | CRC    |        |

| 5 B.             | 11 Bits     | 7 Bits | 11 Bits       | 6 Bits         | 0-254 Bytes           |           |  |                   | 24 Bits |        |        |

Figure 2.7: Flexray Frame Format

**Header segment** This segment contains important information about the frame.

Bits These bits are used to mark special frames.

**Reserved Bit** This bit is reserved for future use, must be transmitted as 0 and must be ignored when it is received.

Payload Preamble Bit This bit indicates that additional information is stored at the beginning of the payload segment.

**Null Frame Indicator** If this bit is set the data in the payload segment is invalid.

**Sync Frame Indicator** If this bit is set, the node should use the timing of this frame for its synchronization process.

**Startup Frame Indicator** This bit indicates whether the frame is a startup frame or not. Frames having this bit set are used for cluster startup and also have to be sync frames.

**Frame ID** The frame identifier specifies the slot, which the frame has to be transmitted in. Therefore, every identifier may only be used once per communication round and per channel. 0 is an invalid frame identifier.

**Length** The length of the payload segment in words (two bytes).

Header CRC Some parts of the data in the header (sync and startup frame indicator, frame identifier and payload length) is relevant for the right operation of the protocol. Hence, it is protected with this additional header CRC. The CRC code is 11 bits long and is generated using the polynomial shown in equation 2.31.

$$x^{1}1 + x^{9} + x^{8} + x^{7} + x^{2} + 1 = (x+1) \cdot (x^{5} + x^{3} + x^{1}) \cdot (x^{5} + x^{4} + x^{3} + x + 1)$$

$$(2.31)$$

0x01A is used as initialization vector of the header CRC.

**Cycle Count** This field contains the the value of the communication cycle counter of the sending node.

Payload segment In this segment the actual application data is transmitted. According to the value the state of the payload preamble bit in the header segment additional administrative information might precede the payload.

For frames transmitted within the static segment this information is a network management vector. With network management vectors that are received during a communication cycle a bitwise OR operation is performed and the result is made available to the application layer at the end of the cycle. The length of the network management vector has to be configured in the communication controller. All additional

network management functionality has to be performed by the application software.

For frames within the dynamic segment the additional information is a 16 bit long message identifier. This identifier may be used by receiving nodes for filtering certain packages. However, it is the task of the application to set the identifier and the payload preamble indicator correctly.

The maximum length of the payload is limited by the number of bits that are used for encoding it. The seven bit long length field limits the maximum size of the payload to  $(2^7 - 1) \cdot 2 = 127 \cdot 2 = 254$  Bytes.

**Trailer segment** The trailer segment contains a 24 bit CRC code. It is 11 bits long and is generated using the polynomial shown in equation 2.32.

$$x^{24} + x^{22} + x^{20} + x^{19} + x^{18} + x^{16} + x^{14} + x^{13} + x^{11} + x^{10} + x^8 + x^7 + x^6 + x^3 + x + 1 =$$

$$= (x+1)^2 \cdot (x^{11} + x^9 + x^8 + x^7 + x^5 + x^3 + x^2 + x + 1) \cdot (x^{11} + x^9 + x^8 + x^7 + x^6 + x^3 + 1)$$

$$(2.32)$$

0xFEDCBA is used as initialization vector for frames sent through channel A and 0xABCDEF for those on channel B.

### 2.4.4 Data Encoding

The bits of the Flexray data frames are transmitted using the NRZ encoding. Before and after the actual frame data and between every two transmitted bytes special bit sequences are inserted to support synchronization between sender and receiver.

**Transmission Start Sequence** Each transmission is started by pulling the data line low for a predefined amount of time. This period is used for setting up active star coupler accordingly.

Frame Start Sequence Each data frame is preceded with one high bit.

Byte Start Sequence Each data byte is preceded with one high and one low bit.

**Frame End Sequence** One low bit and one high bit are appended to each frame

**Dynamic Trailing Sequence** After the transmission of the last bit of a frame within the dynamic segment, the data line is hold low until the next minislot. Then, a single high bit is transmitted.

Three different bit sequences may be transmitted as symbols:

|                                    | point-to-point | passive bus | passive star | active star      |

|------------------------------------|----------------|-------------|--------------|------------------|

| maximum distance between two nodes | 24m            | 24m         | 24m          | 24m to/from star |

| minimum number of stubs            | 0              | 4           | 3            | 2                |

| maximum number of stubs            | 0              | 22          | 22           | -                |

| minimum number of splices          | 0              | 2           | 1            | -                |

| maximum number of splices          | 0              | _           | 1            | -                |

Table 2.2: Flexray Physical Layer Characteristics

Collision Avoidance Symbol This symbol is transmitted by pulling the data line low for a certain amount of time. It is preceded by a transmission start sequence. The symbol is used during the cold start to determine the leading cold start node. All other nodes integrate on this node and synchronize their communication on it.

Media Access Test Symbol This symbol looks like the collision avoidance symbol. However, they can be distinguished because the media access test symbol is sent within the symbol window. The transmission of this symbol is triggered via the CHI.

Wakeup Symbol This symbol consists of alternating sequences of low and high bits. The sequences have a predefined length. The number of signal changes also can be configured. The symbol is used to wake up the sleeping nodes of a cluster. It may only be transmitted on one channel at a time. Its transmission is triggered by the host.

## 2.4.5 Physical Layer

A passive bus, a passive star, or an active star topology can be used in a Flexray cluster. It is also possible to use a combination of the active star and the bus topology. The nodes of a Flexray cluster can be interconnected with one or two busses. If two busses are used, both have to belong to one single cluster. Bridges between different clusters can only be built using a second communication controller.

A dedicated electrical physical layer specification for Flexray systems exists [Fle05a]. It defines a differential transmission using  $\pm$  600mV.

The maximum distance between two active stars is limited to 24m. Only two active stars are allowed to be placed on every signal path.

The information is sent over the network using the NRZ coding and a maximum speed of 10 Mbit/s.

#### 2.4.6 Host Interface

The Flexray host interface is divided in two parts, the protocol data interface and the message data interface. The protocol data interface allows to configure the protocol parameters, to control the protocol execution (e.g., change the execution state, perform external clock synchronization), and to read the status of the protocol execution (e.g., slot counter, macro tick counter, clock rate correction).

Through the message data interface the received data can be accessed and the data that has to be transmitted, is be handed over to the communication controller. This interface is also used for configuring the handling of incoming and outgoing data (e.g., in which time slot data is stored in which buffer).

Beyond, the host interface offers additional services: Received messages can be filtered using the first two bytes of their payload. A powerful, configurable interrupt logic can provide interrupts on all important protocol events. Moreover, the network management service preprocesses all incoming network management vectors (all vectors of a communication cycle are or-ed and the result is made available to the application).

#### 2.4.7 Efficiency

For the calculation of the efficiency, only the static segment is considered. The maximum length of the payload of a Flexray frame is 240 bytes (= 1920 bits =  $n_{payload\_max}$ ). The overhead caused by wrapping the payload in a frame ( $T_{frameing}$ ) is calculated according to equation 2.34.

$$T_{framing} = (n_{header} + n_{trailer}) \cdot T_{bit} =$$

$$= (5 \cdot 8 + 3 \cdot 8) \cdot T_{bit} = 64 \cdot T_{bit}$$

$$(2.33)$$

Another overhead  $(T_{coding})$  is added because additional bits have to be transmitted at the start of a transmission, of a frame, and of a byte, as well as at the end of each frame.

$$T_{coding} = (n_{transmission\_start} + n_{frame\_start} + n_{byte\_start} \cdot n_{bytes\_max} + n_{frame\_end}) \cdot T_{bit} = (2.35)$$

$$= (3 + 1 + 2 \cdot 240 + 2) \cdot T_{bit} = 486 \cdot T_{bit}$$

(2.36)

$$efficiency_{max} = \frac{T_{maxpayload}}{T_{maxpayload} + T_{frameoverhead} + T_{coding}} =$$

$$= \frac{1920 \cdot T_{bit}}{(1920 + 64 + 486) \cdot T_{bit}} = 0.7773$$

(2.38)

$$= \frac{1920 \cdot T_{bit}}{(1920 + 64 + 486) \cdot T_{bit}} = 0.7773 \tag{2.38}$$